NASA/TM-2008-215444

# Channel Temperature Determination for AlGaN/GaN HEMTs on SiC and Sapphire

Jon C. Freeman Glenn Research Center, Cleveland, Ohio

Wolfgang Mueller Research 2000, Inc., Cleveland, Ohio

## NASA STI Program . . . in Profile

Since its founding, NASA has been dedicated to the advancement of aeronautics and space science. The NASA Scientific and Technical Information (STI) program plays a key part in helping NASA maintain this important role.

The NASA STI Program operates under the auspices of the Agency Chief Information Officer. It collects, organizes, provides for archiving, and disseminates NASA's STI. The NASA STI program provides access to the NASA Aeronautics and Space Database and its public interface, the NASA Technical Reports Server, thus providing one of the largest collections of aeronautical and space science STI in the world. Results are published in both non-NASA channels and by NASA in the NASA STI Report Series, which includes the following report types:

- TECHNICAL PUBLICATION. Reports of completed research or a major significant phase of research that present the results of NASA programs and include extensive data or theoretical analysis. Includes compilations of significant scientific and technical data and information deemed to be of continuing reference value. NASA counterpart of peer-reviewed formal professional papers but has less stringent limitations on manuscript length and extent of graphic presentations.

- TECHNICAL MEMORANDUM. Scientific and technical findings that are preliminary or of specialized interest, e.g., quick release reports, working papers, and bibliographies that contain minimal annotation. Does not contain extensive analysis.

- CONTRACTOR REPORT. Scientific and technical findings by NASA-sponsored contractors and grantees.

- CONFERENCE PUBLICATION. Collected

papers from scientific and technical conferences, symposia, seminars, or other meetings sponsored or cosponsored by NASA.

- SPECIAL PUBLICATION. Scientific, technical, or historical information from NASA programs, projects, and missions, often concerned with subjects having substantial public interest.

- TECHNICAL TRANSLATION. Englishlanguage translations of foreign scientific and technical material pertinent to NASA's mission.

Specialized services also include creating custom thesauri, building customized databases, organizing and publishing research results.

For more information about the NASA STI program, see the following:

- Access the NASA STI program home page at http://www.sti.nasa.gov

- E-mail your question via the Internet to *help@ sti.nasa.gov*

- Fax your question to the NASA STI Help Desk at 301–621–0134

- Telephone the NASA STI Help Desk at 301–621–0390

- Write to: NASA Center for AeroSpace Information (CASI) 7115 Standard Drive Hanover, MD 21076–1320

# Channel Temperature Determination for AlGaN/GaN HEMTs on SiC and Sapphire

Jon C. Freeman Glenn Research Center, Cleveland, Ohio

Wolfgang Mueller Research 2000, Inc., Cleveland, Ohio

National Aeronautics and Space Administration

Glenn Research Center Cleveland, Ohio 44135

Level of Review: This material has been technically reviewed by technical management.

Available from

NASA Center for Aerospace Information 7115 Standard Drive Hanover, MD 21076–1320 National Technical Information Service 5285 Port Royal Road Springfield, VA 22161

Available electronically at http://gltrs.grc.nasa.gov

# Channel Temperature Determination for AlGaN/GaN HEMTs on SiC and Sapphire

Jon C. Freeman National Aeronautics and Space Administration Glenn Research Center Cleveland, Ohio 44135

> Wolfgang Mueller Research 2000, Inc. Cleveland, Ohio 44145

#### Abstract

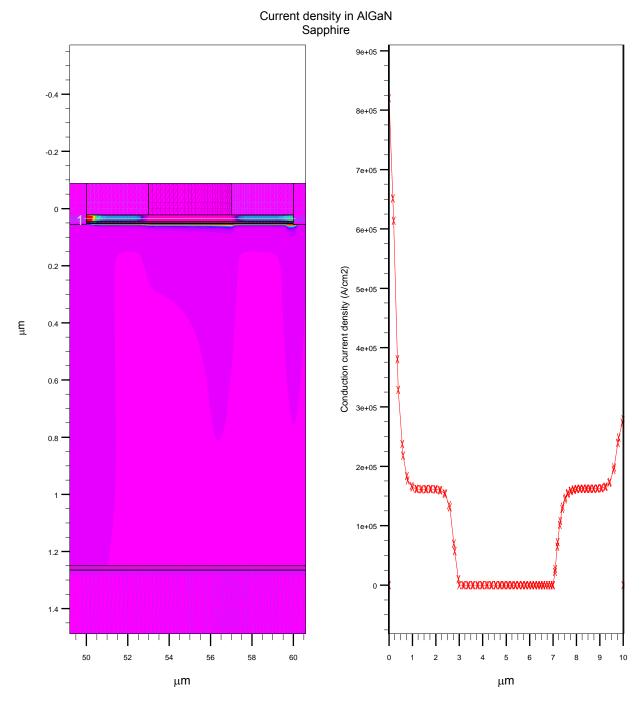

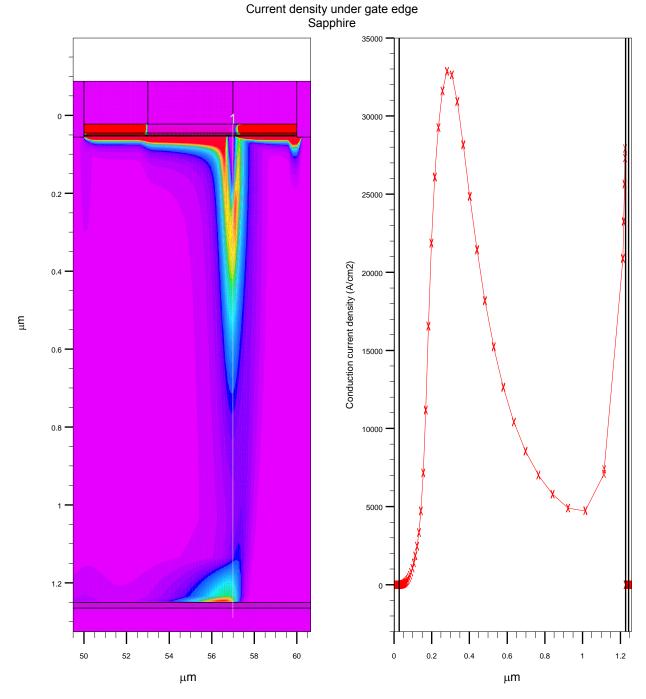

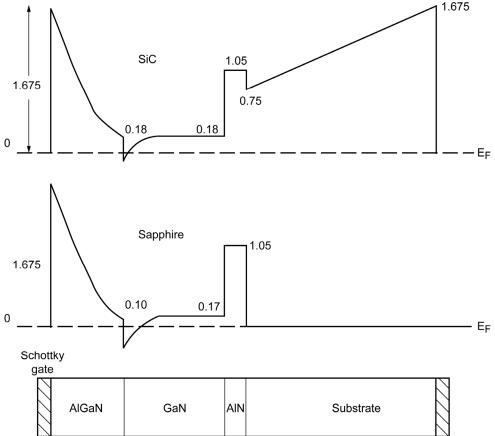

Numerical simulation results (with emphasis on channel temperature) for a single gate AlGaN/GaN High Electron Mobility Transistor (HEMT) with either a sapphire or SiC substrate are presented. The static I–V characteristics, with concomitant channel temperatures ( $T_{ch}$ ) are calculated using the software package ATLAS, from Silvaco, Inc. An in-depth study of analytical (and previous numerical) methods for the determination of  $T_{ch}$  in both single and multiple gate devices is also included. We develop a method for calculating  $T_{ch}$  for the single gate device with the temperature dependence of the thermal conductivity of all material layers included. We also present a new method for determining the temperature on each gate in a multi-gate array. These models are compared with experimental results, and show good agreement. We demonstrate that one may obtain the channel temperature within an accuracy of ±10 °C in some cases. Comparisons between different approaches are given to show the limits, sensitivities, and needed approximations, for reasonable agreement with measurements.

### **I. Introduction**

AlGaN/GaN HEMT amplifiers have achieved record power densities at microwave frequencies (refs. 1 and 2). Many of these "hero" devices have been small, and the aim of the experiments was to determine the power generation capability. The small units often consisted of one or two gates, so the problems of heat dissipation were not addressed. The large power density generated in power amplifiers causes considerable self-heating, and an accurate estimate for the channel temperature is needed for both design purposes and reliability estimates. For a practical device that will develop power at the multiple watt level, self-heating in the channel will be extreme. For power densities of 10 W/mm, the thermal management schemes will need to be more robust than those for other existing technologies, since the power density dealt with in AlGaN/GaN HEMTs is an order of magnitude larger. Knowledge of the strength of the self-heating is essential as increasing temperature reduces the mobility (it decreases as  $T^{-2.3}$ ), and other basic material parameters, with resulting decrease in DC and RF performance (ref. 3). Thus severe reduction occurs in the output power, transconductance, cutoff and maximum oscillation frequencies, and the reliability. Preliminary results (refs. 4 to 6) for device failure or permanent damage, have indicated failures occur when the channel temperature rises into the 200 to 300 °C range. However, reports of undamaged devices after operation at 600 °C have been reported (ref. 7). Both the long and short period output power changes measured in many devices under stress testing are related to the device temperature. The trade-off in the number of fingers in a MMIC cell is controlled to some extent by the thermal hot spots that develop near the edge of the gate in the gate-drain access regions in the center of a multi-finger cell. These factors show the need for reasonably accurate estimates of the channel temperature in multi-gate devices.

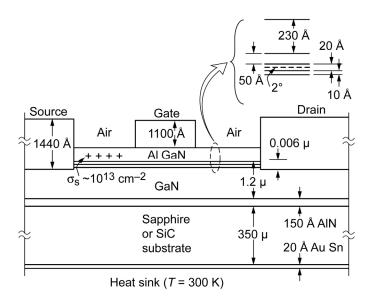

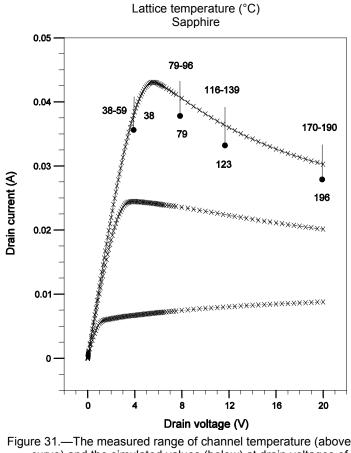

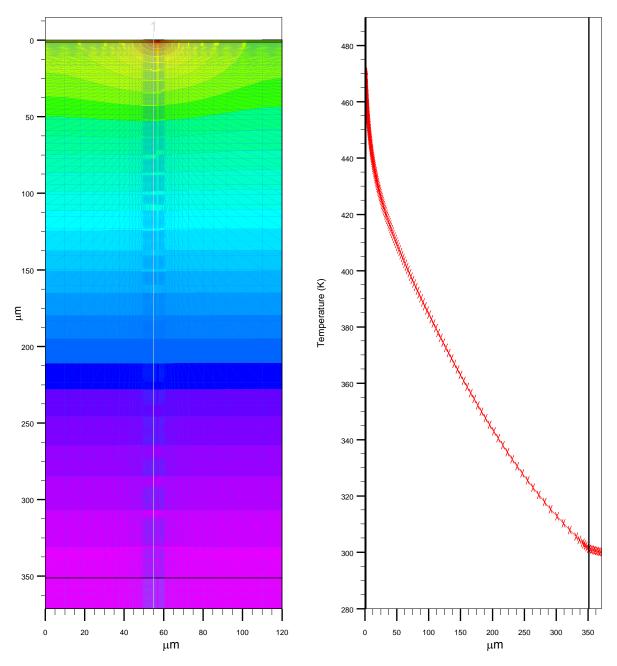

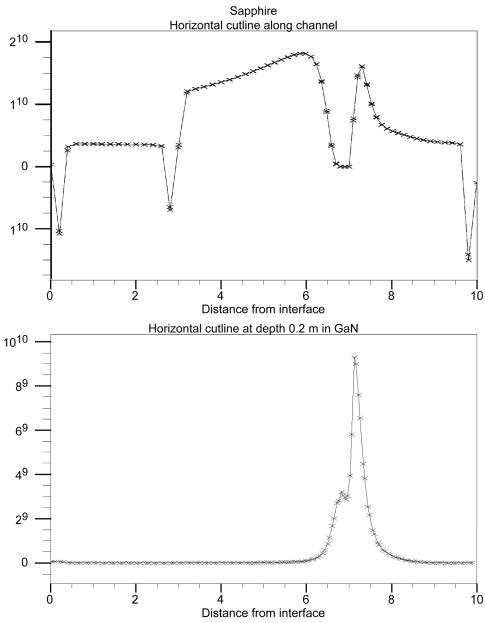

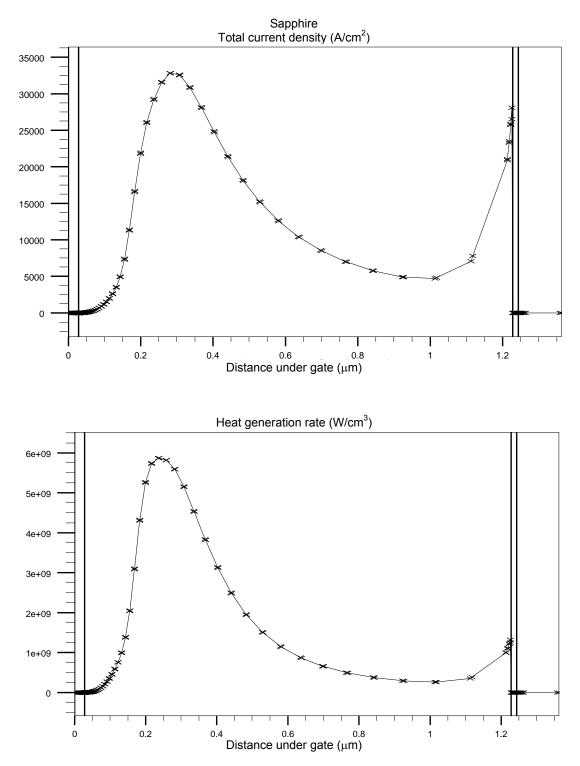

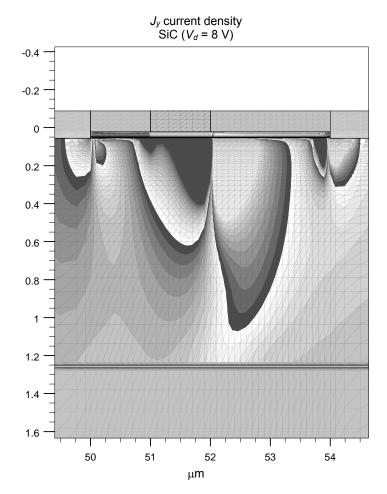

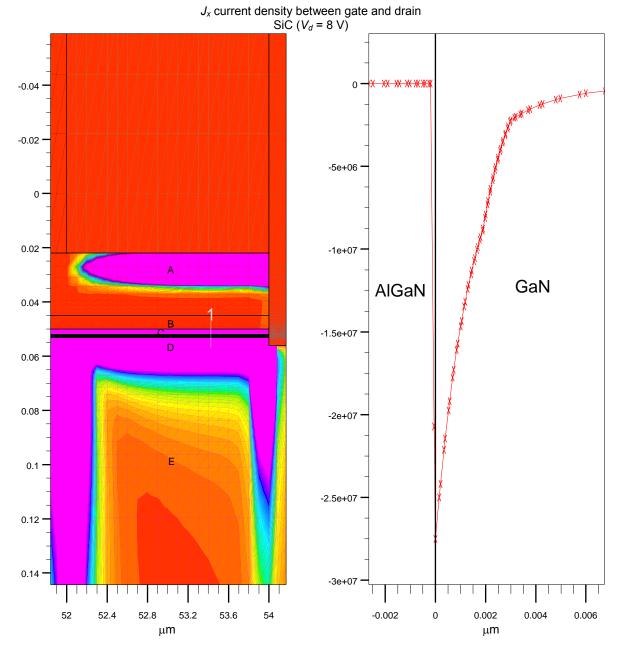

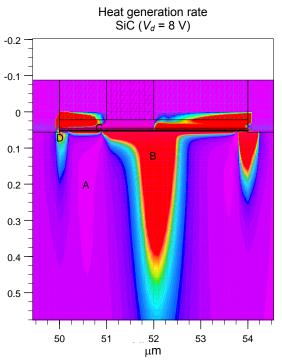

The calculation of the channel temperature is, however, a difficult task for the following reasons. In principle, one should use a 2–D electro-thermal solver which performs a self-consistent calculation for

currents and temperatures for at least the basic cell (one source-gate-drain section). However, due to the large scale differences in the dimensions of the two-dimensional electron gas (2DEG) and the overall structure (substrate on the order of 350  $\mu$ m), the simulations require complex meshing, and subsequently run for up to 15 hr. The 2–D self-consistent solver provides the initial estimate of the temperature field and the heat generation function g(x,y) at the chosen bias point. The 2–D slice is 1  $\mu$ m thick and is assumed to be in the center portion (with respect to z) of the device. Next one should use a 3–D thermal simulator with g(x,y,z) as the source function, to obtain a more refined estimate for the temperature field. However, the prescription of generating g(x,y,z) from g(x,y) depends on the particular device geometry, etc. This approach has been emphasized in (ref. 8), as large inaccuracies from the 2–D runs may be present. Apparently the heat flow from the ends of the gate fingers can significantly affect the temperature field near the center (by up to 43 percent). One must also accurately define the boundary conditions; so the details of the top surface (passivation and metal layers) are needed. This information is usually not known precisely. This is a problem, as the heat generation region is sensitive to changes in physical details, bias, and the baseplate temperature. In any situation one must include the change in thermal conductivity with temperature of all material layers, or large errors will quickly accumulate.

Several 2–D and 3–D simulators (refs. 9 to 12) are available to determine temperature profiles. A 2–D electro-thermal package, MINIMOS-NT (ref. 13) considers the coupling between the current and heat transport equations, and thereby performs a self-consistent calculation. The SILVACO (ref. 14) software package, which we use, is also a self-consistent 2–D electro-thermal simulator.

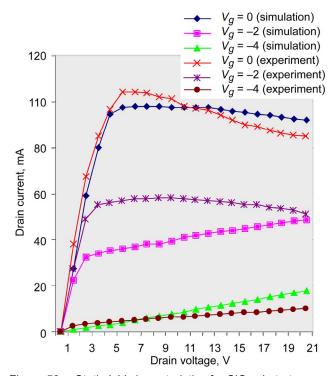

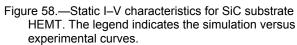

In this memo we first present analytical models for channel temperature determination, and compare their predictions with measurements and simulations found in the literature. The accuracy is generally within 10 percent of measurements, and in some cases much better. These analytical methods are for both single and multiple gate devices, with any epitaxial layer sequence. We can handle effects of package dimensions, chip separations, and include the dependence of the thermal conductivity on temperature for all materials. Then we present results from the 2–D self-consistent electro-thermal solver ATLAS from SILVACO. We simulate I–V curves and measured temperatures from the only set of publications in the literature that have presented simultaneous I–V characteristics, and concomitant thermal measurements (refs. 15 to 18). We find good to excellent agreement. We have, for the first time, replicated measured I–V characteristics and channel temperatures for AlGaN/GaN HEMTs on both sapphire and SiC substrates.

As stated earlier, the calculation of the channel temperature is not easy, and its measurement is also not easy. Achieving both accuracy and spatial resolution is difficult, so a reasonably simple analytical prediction for amplifier/device level design purposes can be very helpful. When using such approximations, it is helpful to know the sensitivity of the final temperature with the many parameters involved. This sensitivity is investigated here. A final comment concerns the uncertainty in many of the critical device parameters. One can question the use of sophisticated software packages, when some of the material parameters are unknown by as much as an order of magnitude. Unfortunately this is the case, as the critical parameter (thermal conductivity) depends on a given layer's doping, growth procedure, process steps, and physical condition (cracks, etc.). This bolsters the need for a reasonably accurate analytical treatment.

#### **II. Previous Analytical Methods**

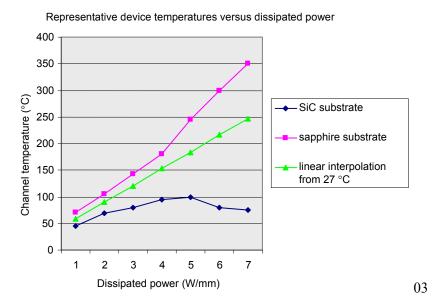

At the present time many investigators have studied the thermal properties of AlGaN/GaN HEMTs and GaN FETs under various conditions (refs. 19 to 31). They have presented combinations of measured data, 2–D and 3–D simulations, Monte Carlo results, and analytical schemes. The aim was to determine the channel temperature  $T_{ch}$  as the dissipated power changed. The change in  $T_{ch}$  may be due to changes in the bias point, baseplate temperature, or power added efficiency (PAE). In many cases constant thermal conductivity values were assumed, as this simplifies the problem (treats the system as linear). Figure 1

displays two possible plots of the channel temperature versus dissipated power. By definition,  $\Delta T_{ch}$  (the increase in channel temperature) and the dissipated power  $P_{diss}$  are related by the "thermal resistance"  $R_{th}$ ,

$$\Delta T_{ch} = R_{th} \cdot P_{diss} \tag{1}$$

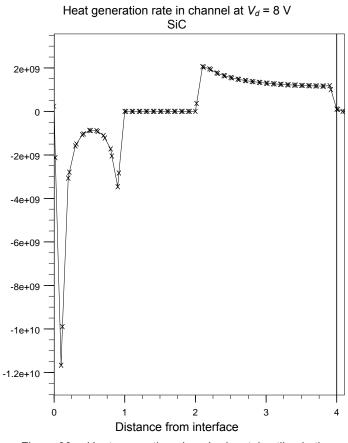

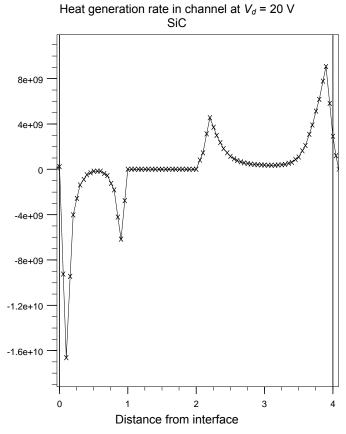

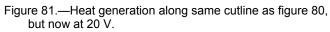

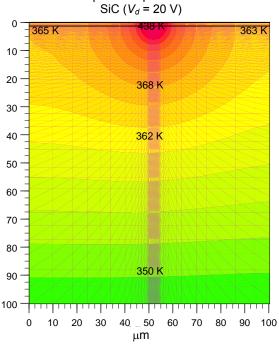

The final temperature  $T_{ch}$ , is  $\Delta T_{ch}$  + reference temperature. The reference temperature is generally the baseplate's value. From inspection of the figure one sees that  $R_{th}$  is not constant, but varies with  $P_{diss}$ . This variation is due to many factors. One is the change in thermal conductivity as the temperature increases (it decreases with increasing temperature), and another is the change in the heat generation function g(x,y,z) as the dissipated power increases. Generally g(x,y,z) increases in magnitude and the volume over which this region extends gets more sharply defined. Also, the location of the peaks of g(x,y,z) change as the current path through the device changes with bias and RF drive. The nonlinearity may be concave up or down, depending on circumstances. These differences may be due to the geometry of the finger layout, the edge effects, or the rise in the baseplate temperature with increasing power dissipation. For example, for a sapphire substrate, the channel temperature may be in the 320 to 370 °C range for dissipation near 6 W/mm. This temperature may be about 100° higher than the extrapolation from the low temperature linear assumption. For SiC at this same dissipation, the temperature may be only 95 °C. But in both cases, one cannot extrapolate from the low temperature line. In general then,  $R_{th}$  is a function that depends on many parameters, such as thermal conductivity and the detailed device geometry. This functional dependence will be explored in detail in subsequent sections.

The determination of channel temperature from analytical expressions is very difficult at the present time for many reasons. One complication is the appropriate form for the thermal conductivities  $\kappa(T)$  as a function of the temperature *T*, for the various material layers. While assuming constant  $\kappa$  simplifies the analysis (treats the system as linear), we will show that the error is quite large for AlGaN/GaN HEMTs on either sapphire or SiC substrates. Even when this dependency is included, uncertainty exists for the proper values of  $\kappa(T)$  in each layer. Since different growth methods and doping levels produce very different material properties, the reported measured values for  $\kappa(T)$  have a large dispersion. For GaN (refs. 32 to 37), for sapphire (refs. 38 to 40), and for SiC (refs. 41 to 44). A second problem is the choice of the

Figure 1.—Representative channel temperatures versus dissipated power for devices on sapphire or SiC substrates. The secants to the curves (originating from  $T_{ch}$  = 27 °C) are representative of the thermal resistances. The fact that the slopes are not constant reflects the changes in thermal resistance with dissipated power.

best approximate equations to use, as many have been published, and in many cases they don't all converge to a common value. We have also found that the discrepancies are due in part to errors in published equations and mislabeling of plots. We list a few problem areas:

1. In self-consistent 2–D simulators, does it matter that one uses the simpler drift-diffusion (D-D) approximation, or the more basic hydro-dynamic model? However, for the latter, what are the appropriate relaxation times? In the D-D formulation, one does not treat hot carrier effects (due to large electric fields) adequately. Also, what is the proper form for the mobility as a function of field, temperature, and doping? What is the effect of changing scatter-limited velocity with temperature? We assume some of these effects are minor, as will be shown later when we show excellent agreement with experiment.

2. Shorter gates enhance self-heating, and this is a very strong function of gate length.

3. Some experiments have shown variation of temperature *along* the gate fingers to be as much as  $100 \text{ }^{\circ}\text{C}$ .

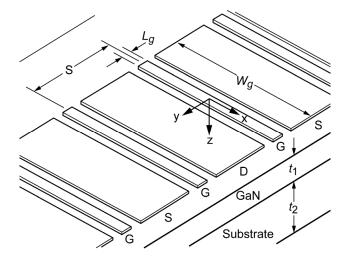

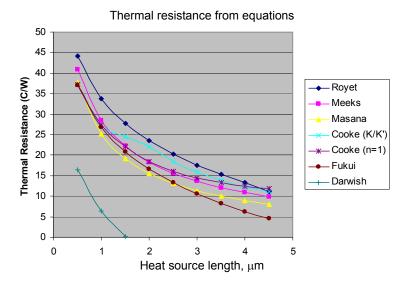

While many papers have appeared with methods to calculate the channel temperature, we will only concentrate on a few in this section. Recently Darwish, Bayba, and Hung (refs. 45 to 47) presented original closed-form expressions for calculating the thermal resistance of multi-finger AlGaN/GaN HEMTs and FETs. The two papers are complementary (one primarily for HEMTs, the other for FETs) in that somewhat different assumptions were used in each. The model consists of a vertical slice through a multi-fingered device, wherein the slice width is determined by inclusion of the source and drain pads with the gate in the center. The HEMT model specifies the GaN layer as region I, and the substrate is divided into two layers; regions II and III. In the first paper the isotherms were assumed to be circular cylinders, prolate spheroids, and elliptic cylinders, in regions I, II, and III, respectively. In the second paper, only a single layer is considered (appropriate for FETs), and the isotherms were assumed to be confocal ellipsoids and elliptical cylinders, as one moves from the gate to the heat sink. Attempts to verify the model included comparison with numerical simulation using ANSYS (for shapes of the isotherms and thermal resistance), and experimental data. The calculation assumes constant thermal conductivity and is restricted to multiple finger (greater than about 5) devices. They state the effects of non-constant thermal conductivity may be included by using the Kirchhoff transform; however they do not demonstrate the calculation. The wafer is assumed to be large in lateral extent, so end effects are neglected. The heat is generated by the gate electrode, and the thermal resistance is calculated assuming adiabatic boundary conditions on the vertical walls of the slice. This assumption implies that a few identical cells must exist on either side, so good results should be expected for devices with at least 5 or more gates. The demonstration of the close fit between the analytical equations and the shapes of the isotherms and thermal resistances as determined by the simulator ANSYS, makes the use of their results very compelling. There are, however, some drawbacks. The dependence on gate length is questionable; by this we mean the model for the gate shape is not completely convincing. The fact that the analytical equations results agree with the numerical simulations, means that the analytical model is correct. It does not mean that the model correctly reflects the heat source shape in actual HEMTs. The neglect of  $\kappa(T)$  may have some effect on the shape of the isotherms as the temperature increases, and the resultant thermal resistance. In other words, the change in  $R_{th}$  with dissipation level (due to changes in g(x,y,z) and  $\kappa(T)$ ) is omitted. Also the variation of  $R_{th}$  with the number of fingers is eliminated by the nature of the calculation. Their equations are given below; see figure 2 for clarification of parameters. Note that Darwish et al. uses the symbol  $\Theta$  for the thermal resistance  $R_{th}$ .

$$R_{th}(\text{total}) = R_{th}(I) + R_{th}(II) + R_{th}(III)$$

$$R_{th}(\text{total}) = \frac{1}{\pi w_g k_{\text{Gan}}} \ell n \left( \frac{4t_1}{\pi L_g} \right) + \frac{1}{\pi w_g k_{\text{sub}}} \ell n \left\{ \frac{f\left( w_g/2\rho_{t_1} \right)}{f\left( \sqrt{1 + \left( \frac{w_g}{\sqrt{2s}} \right)^2 - \left( \frac{\rho_{t_1}}{\sqrt{2s}} \right)^2 \right)} \right\}} + \frac{1}{\pi s k_{\text{sub}}} \ell n \left\{ \frac{h\left[ \left( \frac{w_g}{\pi t_2} \right)^2 - 4 \left( \frac{\rho_{t_1}}{\pi t_2} \right)^2 \right]}{h\left[ \left( \frac{w_g}{\sqrt{2s}} \right)^2 - 4 \left( \frac{\rho_{t_1}}{\sqrt{2s}} \right)^2 \right]} \right\}$$

(2)

where

$$\rho = \frac{4k_{\text{GaN}}}{\pi^2 k_{\text{sub}}}$$

$$f(x) = \frac{\sqrt{x+1} + \sqrt{x-1}}{\sqrt{x+1} - \sqrt{x-1}}$$

$$h(x) = \sqrt{\frac{\sqrt{x+1}+1}{\sqrt{x+1}-1}}$$

Figure 2.—Geometry for calculating thermal resistance,  $R_{th} \equiv \Theta$ , as given by Darwish, Bayba, and Hung (refs. 45 to 47).

### **III. Thermal Resistance Formulas for Single and Multigate HEMTs**

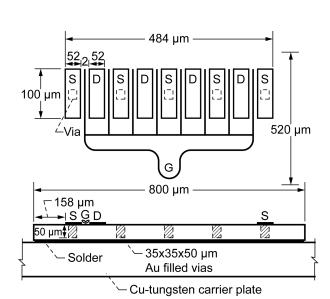

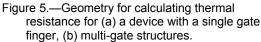

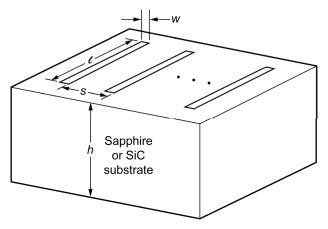

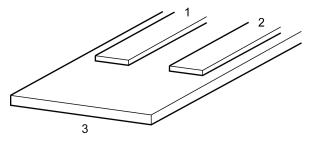

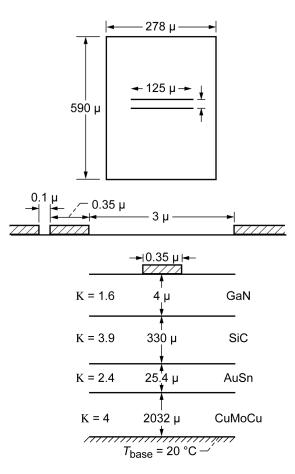

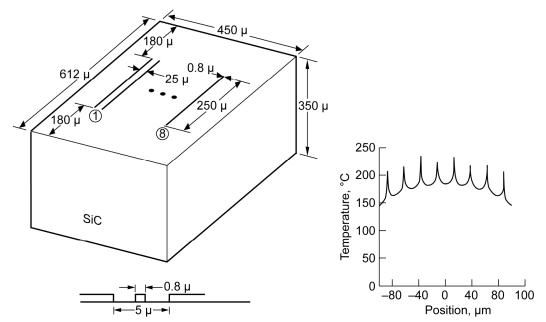

In this memo we consider both single and multiple gate devices and include the dependence on temperature of the thermal conductivity as well as the actual size of the MMIC chip (end effects). The general layer structure for a typical device is shown in figures 3 and 4. Figure 3 gives a top view of an eight gate device, while figure 4 shows the approximate layer thicknesses and thermal conductivity ranges for all materials. Our procedure to determine the temperature of the gate electrode (which we assume is nearly the same as the temperature in the GaN channel) is a series of about nine steps. In general we determine the thermal resistance of each layer of the device, and from that along with the I–V product of the bias point, the temperature is determined. The schematic in figure 5 gives the geometry for both single and multiple gate situations for the calculation of the thermal resistance,  $R_{th}$ . The following list of steps gives a detailed explanation of our calculation procedure.

Figure 3.—Schematic of an eight gate AlGaN/GaN

| 6000  | maionauraura |       | a manual life a m |

|-------|--------------|-------|-------------------|

| tor a | microwave    | DOwer | amoimer.          |

| <br>  |              | p =   | epe               |

| - |                |                                       |                                                                        |                  |

|---|----------------|---------------------------------------|------------------------------------------------------------------------|------------------|

|   | 0.1175 μm      | Si3 N4<br>(passivation layer)         | к = 0.0096                                                             |                  |

|   | <b>0.02</b> μm | GaN (cap layer)                       | к = 1.6                                                                |                  |

|   | 0.022 μm       | Al0.2 Ga0.8 N<br>(barrier layer)      | к = 1.6                                                                |                  |

|   |                | GaN /<br>(buffer layer) /<br>2 deg*/  | к(To) = 1.6<br>к(T) = calculated                                       | - T<br> <br>     |

| ſ | 0.015 μm       | AIN (nucleation layer)                | к = 0.1                                                                | I                |

| Í | 100 μm         | SiC                                   | Au source<br>via κ = 3.18<br>κ(T0) = 3.4<br>κ(T) = calculated<br>35 μm | + <b>–</b> – – – |

| Í | 20 µm          | AuSn<br>AuGe<br>Epoxy<br>Silver epoxy | κ = 2.4<br>κ = 0.9<br>κ = 0.36<br>κ = 0.016075                         |                  |

| [ | 1000 μm        | Cu-tungsten<br>(carrier)              | к = 4                                                                  |                  |

Note: The units for thermal conductivity  $\kappa$  are W/(cm-K)  $\,^*$  Two dimensional electron gas

Figure 4.—Cross-section model of the HEMT device, showing approximate layers of material with average, or ranges, of thermal conductivities.

#### **Thermal Analysis Procedure**

1. For a single gate device, start at the bottom surface and assume the baseplate temperature  $T_b$  is known. Assume the temperature drop across the adhesive (solder) layer is small, so the bottom of the substrate is near  $T_b$ .

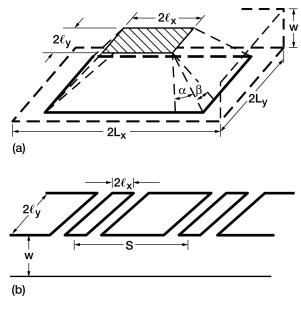

2. Calculate  $\kappa(T_b)$  for either the sapphire or SiC substrate.

3. Calculate  $R_{th}$  for the substrate. We recommend the formulas published by Masana (ref. 48), which are valid for a single heat source with the overall size of the chip considered. See figure 5(a) for the geometry. The equations are:

$$L_g = 2l_x$$

$$W_n = W/L_x$$

$$\gamma_e = l_y/l_x$$

$$\gamma_s = L_y/L_x$$

$$l_{xn} = l_x/L_x$$

$$\rho_s = \kappa_i/\kappa_{i+1}$$

$$\tan \alpha = \left(1 - l_{x_n}\right) \frac{w_n + \frac{\rho_s}{1 + \rho_s} l_{x_n}}{w_n + \frac{1}{1 + \rho_s} l_{x_n}}$$

$$\tan \beta = \left(1 - l_{x_n} \frac{\gamma_e}{\gamma_s}\right) \frac{w_n + \frac{\rho_s}{1 + \rho_s} l_{x_n} \gamma_e}{w_n + \frac{1}{1 + \rho_s} l_{x_n} \gamma_e}$$

$$R_{th}(T) = \frac{1}{4\kappa(T)l_x} \frac{1}{[\gamma_e \tan \alpha - \tan \beta]} \ell n \left[ \frac{l_x + w \tan \alpha}{l_x + \frac{w \tan \beta}{\gamma_e}} \right]$$

(3)

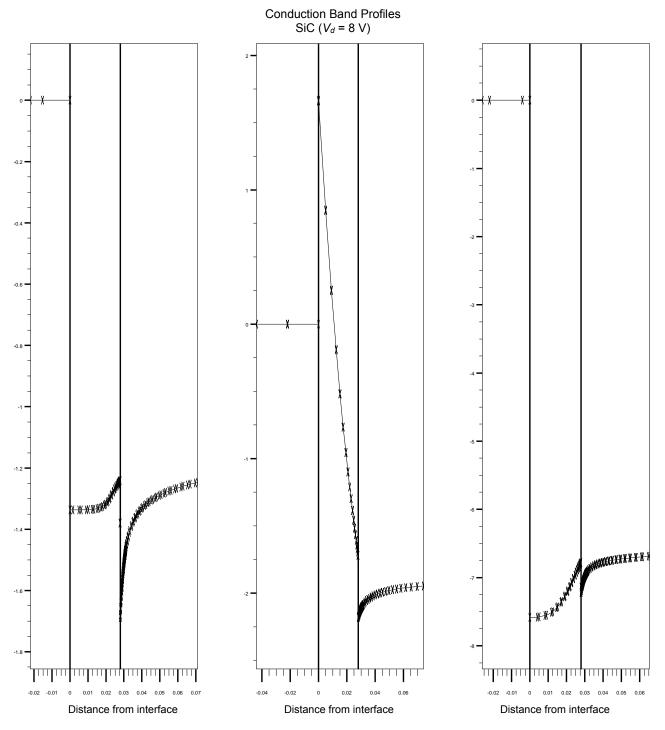

4. In the previous step one needs the dimensions  $(2l_x, 2l_y)$  of the effective flat strip heat source on the top surface of the substrate. The critical parameter is the effective gate length  $2l_x$ . For SiC use 4.5 (gate length), and for sapphire use 6.5 (gate length). There is some question as to the sensitivity of this assumption, as the actual size of the heat source is dependent on the bias point and the geometry of the structure. This is a critical step, as the final temperature is sensitive to the size of the heat source. All simulators that are not coupled electro-thermal calculators suffer with this problem, as they require the user to define the heat generation region g(x,y,z). The formula for  $R_{th}$  is for constant  $\kappa$ , and the value is that for the temperature of the lower surface. With  $R_{th}$  determined, calculate the linearized or "equivalent temperature"  $\theta$  at the top of the substrate (called the interface, int)

$$\theta_{\text{int}} = R_{th} \cdot P_{diss}$$

where  $P_{diss}$  is the power dissipated for the single gate device,  $P_{diss} = V_d \cdot I_d$ , i.e., the product of the quiescent drain voltage and current.

5. Find the actual temperature at the interface using the inverse Kirchhoff transform (discussed in more detail later)

$$T_{\text{int}} = K^{-1}(\theta_{\text{int}})$$

6. Calculate  $\kappa(T_{int})$  for the bottom of the GaN layer.

7. Calculate  $R_{th}$  for the GaN layer similar to the above, but now use  $2l_x = 1.125$  (gate length) for sapphire or (gate length + gate-drain access) for SiC.

8. Calculate the linearized temperature at the top of the GaN layer, which we assume (define) to be the channel value,

$$\theta_{top} = R_{th}(GaN) \cdot P_{diss}$$

9. Calculate the channel temperature

$$T_c = K_{\text{GaN}}^{-1} \left( \theta_{\text{top}} \right)$$

where the inverse transform used is that which is appropriate for the form of the thermal conductivity variation in GaN.

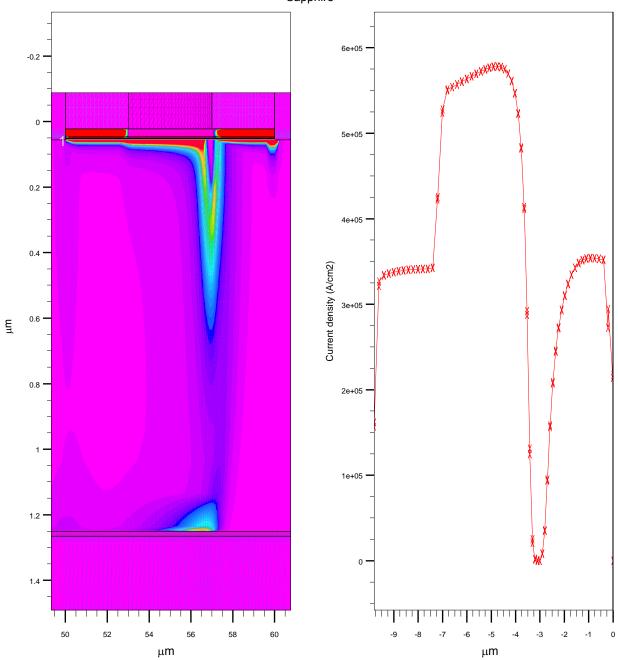

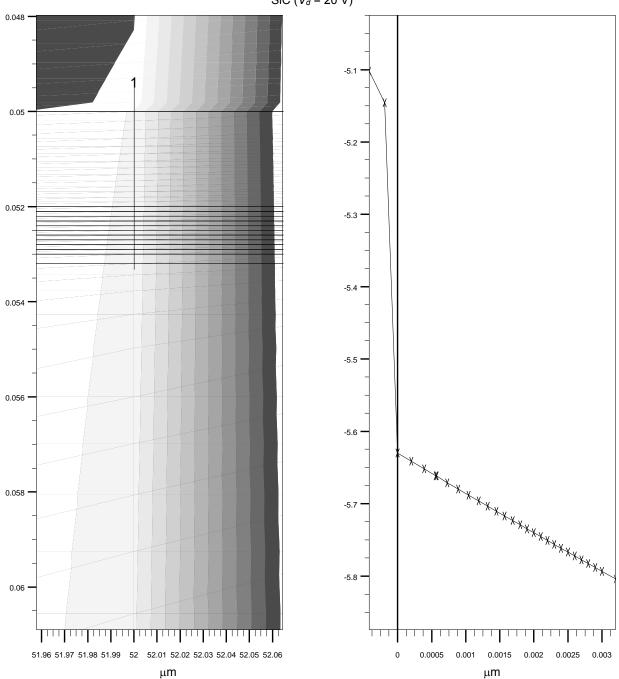

Observe  $\rho_s = \kappa_i(T)/\kappa_{i+1}(T)$ , for the *i*-th layer above the *i*-th +1 layer, thus the spreading angles  $\alpha$  and  $\beta$  depend on the temperature *T*. We neglect the AlN layer which exists at the interface, as only a few

degrees exist across it in most cases. The effect of the low thermal conductivity of the AlN layer is reflected in the effective gate lengths used in the calculation. The low  $\kappa$  of the AlN tends to funnel the heat entering the top surface from the higher conductivity GaN layer into a narrower region than a spherical spread would be expected to do, before it enters the substrate.

For the multi-gate problem, we suggest the following procedure; first use the equations of either Darwish et al. (ref. 45), or Cooke (refs. 49 to 51, and 26). In these equation sets, use either the actual gate lengths for the heat source regions, or those indicated above. Next, use our more detailed calculation method; which will be described in detail in the following section. This procedure gives the temperature on each finger, unlike that of the above schemes, which can only give an "average" channel temperature. The formulas from (ref. 49), with typos corrected, are as follows (again refer to fig. 5):

$$u = \frac{\cosh\left[\frac{\pi}{4}\left(\frac{s+2l_x}{w}\right)\right]}{\cosh\left[\frac{\pi}{4}\left(\frac{s-2l_x}{w}\right)\right]}$$

$$M = \frac{2\sqrt{u+1}}{\sqrt{u-1}}$$

$$P = 2\sqrt{\frac{\cosh\left[\frac{\pi}{4}\frac{2l_x}{w}\right]+1}{\cosh\left[\frac{\pi}{4}\frac{2l_x}{w}\right]-1}}$$

$$R_{th}(T) = \frac{\frac{n}{2l_y\kappa(T)\pi}}{\left[\frac{2(n-1)}{\ln M} - \frac{(n-2)}{\ln P}\right]}$$

(4)

We digress here to review the Kirchhoff transform. In principle, in any heat transport problem, one solves for the temperature field from the heat flow equation

$$\nabla \cdot \{\kappa(T)\nabla T\} = -g(x, y, z),\tag{5}$$

where  $\kappa(T)$  is the temperature dependent thermal conductivity in the *i*-th layer, *T* is the temperature, and g(x,y,z) is the dissipated power density in W/cm<sup>3</sup>. This quantity is also called the heat generation density (source) region. The equation is altered by defining an equivalent, artificial, "linearized" temperature via the Kirchhoff transform (refs. 53 and 54),

$$\theta = T_o + \frac{1}{\kappa(T_o)} \int_{T_o}^T \kappa(\xi) d\xi$$

(6)

which relates the three temperatures T,  $T_o$ ,  $\theta$ ; the actual, reference, and linearized or transformed value, respectively. The transformed, linearized, or effective, temperature on the top surface of the substrate is

$$\theta_2 = T_b + R_{th} (\text{substrate}) \times P_{diss} , \qquad (7)$$

where the known constant value for  $\kappa(T_o)$  has been used in the determination of  $R_{th}$ (substrate). The real, or actual, or physical temperature at the top surface is determined from the inverse of the Kirchhoff transform

$$T_2 = K_{\text{sub}}^{-1} \{ \Theta_2 \}$$

(8)

For the functional form

$$\kappa(T) = \kappa(T_o)(300/T)^r, \qquad (9)$$

where  $T_o = 300$  K unless stated otherwise. The inverse Kirchhoff transform formula is

$$T_{\text{actual}} = \left\{ \left[ \theta - r(\theta - T_o) \right] / T_o^r \right\}^{\left( 1/(1-r) \right)}$$

(10)

and the inverse is

$$\theta = 1/(r-1)[rT_o - T_o^r T^{1-r}].$$

(11)

When r = 1, we have

$$T_{\text{actual}} = T_o \exp(\left[\theta - T_o\right]/T_o), \qquad (12)$$

where  $\theta$  is the effective temperature, and  $T_o$  is the temperature at the bottom surface (the reference value). The temperature on the AlN top surface is

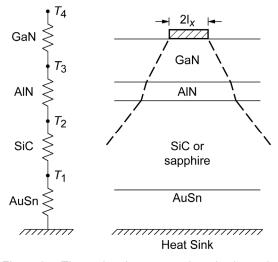

$$T_3 = T_2 + R_{th} (AIN) \times (P_{diss}/n), \qquad (13)$$

where n is the number of gates. This assumes each gate dissipates the same power. Experimentally we know the gates near the middle are the hottest, and they probably dissipate the largest power. Finally, the junction, or channel temperature, at the AlGaN/GaN interface is found by

$$\theta_4 = T_3 + R_{th} (\text{GaN}) \times (P_{diss}/n)$$

(14)

$$T_4 = K_{\text{GaN}}^{-1} \{ \theta_4 \}.$$

(15)

Figure 6 summarizes the approximate heat flow pattern and the temperatures in the thermal resistance stack. Observe the AlGaN layer is neglected as it is extremely thin (up to maybe 500 Å at most).

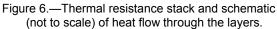

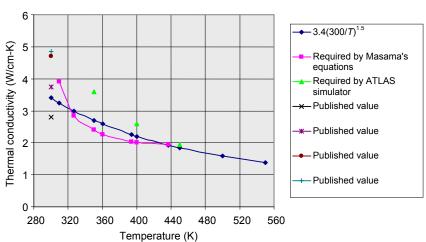

At this stage of development of GaN technology, the actual values of the thermal conductivities of the various epitaxial layers, and their variations with temperature are not known to great accuracy. This necessitates that we must generate reasonable expressions to continue with the calculation. We choose the following expressions:

GaN:

Old

$$\kappa(T) = 1.6 \left(\frac{300}{T}\right)^{1.4}$$

(16)

$$\kappa(T) = 1.97 \left(\frac{300}{T}\right)^{0.48} \tag{17}$$

New

Kuball's (ref. 15)

$$\kappa(T) = 1.6 \left(\frac{300}{T}\right)$$

(18)

$\kappa(T) = 5.2 \left(\frac{300}{T}\right)^{2.4}$

SiC:

$$\kappa(T) = 3.4 \left(\frac{300}{T}\right)^{1.5} \tag{19}$$

(20)

For doping levels near 10<sup>17</sup> cm<sup>-3</sup>

Sapphire:

GaAs:

Si:

$$\kappa(T) = \frac{73.9}{T - 159} \approx 0.49 \left(\frac{300}{T}\right).$$

(21)

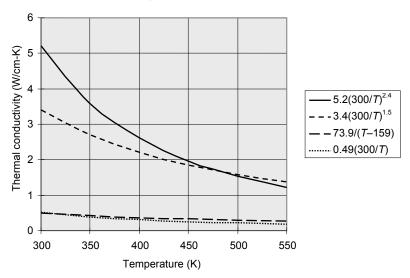

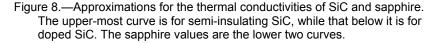

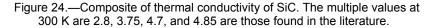

Figures 7 and 8 display the variations with temperature for GaN, and SiC, and sapphire, respectively. For GaN, the old expression was developed by assuming the coefficient was similar to that of GaP (which was measured), and averaging published room temperature values. The new equation utilizes some recently measured data. Observe at 300 K they differ by 18 percent. The expression by Kuball assumes a 1/T variation, and was used in his simulations. The value for SiC is an average of many experimental determinations. For sapphire, the first expression is a curve-fit of experimental data, while the second is an approximation for the basic 1/T form. Figure 9 gives the variations of GaAs, Si, and InP; and the analytical expressions are:

$$\kappa(T) = 0.47 \left(\frac{300}{T}\right)^{1.2}$$

(22)

$$\kappa(T) = 1.45 \left(\frac{300}{T}\right)^{1.324} \approx 1.45 \left(\frac{300}{T}\right)^{1.2} \approx 1.7 \left(\frac{300}{T}\right)^{1.4}$$

(23)

InP:

$$\kappa(T) = .658 \left(\frac{300}{T}\right)^{1.48}$$

(24)

It is obvious that the value for all materials at room temperature, is uncertain by 8 to 18 percent, and the variation with temperature has some dispersion. The reasons are due to the quality of the tested films, and the range over which the fit was obtained. Thus we must be prepared to predict temperatures only to within 5 to 10 percent of measured values due to these uncertainties.

Figure 7.—Approximations for the temperature dependence of the thermal conductivity of GaN.

Thermal conductivity approximations for SiC and sapphire

Semiconductor thermal conductivities

Figure 9.—Approximations for the thermal conductivities of Si, InP, and GaAs.

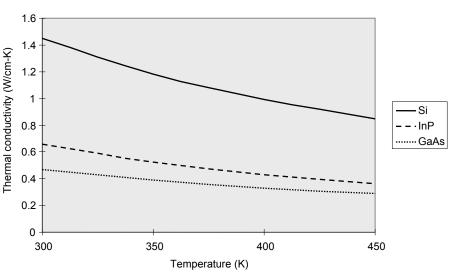

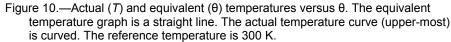

Figure 10 gives an indication of the differences between  $\theta$  and *T* for our situation. The dotted curve is the actual temperature *T* versus  $\theta$  for the specific form for  $\kappa(T)$  given on the plot. The form is that for SiC, the best heat conductor of all considered substrates. The reference temperature is  $T_o = 300$  K. A similar shaped (displaced) curve would occur for a different value for the reference. The lower line has unity slope that would correspond to the actual temperature equaling the transformed value (i.e., constant  $\kappa$ ). It is there to aid the eye to show how rapidly the actual temperature climbs as the equivalent one increases. The increase above the  $T = \theta$  line shows the effect of the decrease of  $\kappa(T)$  from its value at  $T_o$ . For example, the conductivity at 300 K is 3.3 W/(cm·K). If the conductivity were constant at this value, the thermal resistance would be calculated with this value for  $\kappa$ . For a given heat flux, suppose one calculates

$\theta$  to be 450 K, then the actual value would be 534 K (see the plot). Observe the increase is 84 K, which is extremely large! This shows the need to include the variation of  $\kappa(T)$  in the calculation. One difficulty with the transform method is that jumps in the effective temperature occur at material interfaces, unless the forms for  $\kappa(T)$  satisfy certain constraints (ref. 54). The constraint is that the ratio of conductivities of adjacent layers must be independent of temperature. In other words, the nonlinearity in the basic heat equation is removed with the transform, but makes itself felt, and must be dealt with, in the boundary conditions. For our case of multiple layers and sequential calculation steps, we calculate the actual temperature in each layer, and thus avoid any complications.

The following table provides a compilation of reported values for thermal conductivities for components that are of interest to one studying the field of high temperature amplifiers.

| MATERIALS USED IN HIGH POWER AMPLIFIERS    |                                                                                                                                  |  |  |  |

|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Material                                   | $\kappa(W/(cmK))$                                                                                                                |  |  |  |

| GaAs                                       | $\kappa(T) = \kappa(300)(300/T)^{1.2} \kappa(300) = 0.44$<br>= 745 T <sup>-1.3</sup><br>= 56 T <sup>-0.87</sup> 350 K< T < 500 K |  |  |  |

| SiC                                        | $3.3(T_o/T)^{1.5}$ (doped)<br>~ 5 for S.I.                                                                                       |  |  |  |

| Si <sub>3</sub> N <sub>4</sub>             | 0.016                                                                                                                            |  |  |  |

| Sapphire (Al <sub>2</sub> O <sub>3</sub> ) | $\kappa(300) = 0.25 - 0.5$<br>$\kappa(T) = \kappa(300) (T/T_o)^{0.8}$                                                            |  |  |  |

| Au                                         | 2.95 to 3.18                                                                                                                     |  |  |  |

| AuSn solder                                | 0.573                                                                                                                            |  |  |  |

| Silver epoxy                               | 0.0714 to 0.075                                                                                                                  |  |  |  |

| Epoxy cements                              | 0.0188 to 0.0376                                                                                                                 |  |  |  |

| Solders                                    | 1.88 to 2.4                                                                                                                      |  |  |  |

| Copper                                     | 4                                                                                                                                |  |  |  |

| Si                                         | $\kappa(T) = \kappa(300)(T/T_o)^{1.324}$<br>= 1.54(300/T) <sup>4/3</sup>                                                         |  |  |  |

| TABLE 1.—THERMAL CONDUCTIVITIES FOR     |

|-----------------------------------------|

| MATERIALS USED IN HIGH POWER AMPLIFIERS |

Figure 11.—Geometry for multiple gate (heat sources) on a substrate.

#### **IV. Multiple Gate Thermal Resistance Via Multiconductor Coupling Model**

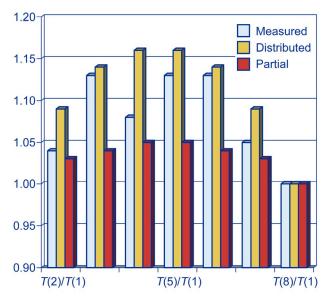

The previous sections presented the accurate model from Masana for single stripes, and the two methods for multiple gates (Cooke and Darwish et al.). The equations of Cooke yield a single temperature, which is apparently an average value of all fingers involved. The formula is dependent on the number of gate fingers. Those of Darwish also give an average temperature, which is apparently that of the central region. The equation is assumed valid for a device with at least five fingers, as the number of fingers is not considered.

Since the layout of gates is similar to the arrangement of multiple conductors above a ground plane, concepts from multiple conductor theory should be applicable for our problem. The problem to be solved is the determination of  $R_{th}$  and temperature for each gate electrode as shown in figure 11. In general, the Source-Drain (S-D) spacing is much smaller than the separation between each S-D region, so the heat generated in each GaN section can be assumed to not couple to heat generated by adjacent sections in the uppermost part of the device. Therefore, we are considering rectangular sources (the appropriate footprints) on the substrate top surface. Once the temperature on this surface is determined, then similar calculations, as given previously, will determine the temperature at the channel. Recall the equation for steady state heat conduction (assume constant  $\kappa$ ) is

$$\nabla^2 T = -\frac{g(x, y, z)}{\kappa},\tag{25}$$

Where g(x,y,z) is the heat generation function. Poisson's equation is  $\nabla^2 V = -\frac{\rho(x,y,z)}{\epsilon}$ , and the

similarities are obvious.

We will use developments in electrical theory to ascertain corresponding results for temperature. This is the same motivation utilized in Cooke's formula; his model uses the capacity for strips above a ground plane. For a finite number of conductors above a ground plane we know the charges and potentials are related by the Maxwell capacitance matrix [C].

$$\begin{bmatrix} Q_{1} \\ Q_{2} \\ \vdots \\ \vdots \\ Q_{N} \end{bmatrix} = \begin{bmatrix} C_{11} & C_{12} & \vdots & C_{1N} \\ C_{21} & \vdots & \vdots & \vdots \\ \vdots & \vdots & \vdots & \vdots \\ C_{N1} & \vdots & \vdots & C_{NN} \end{bmatrix} \begin{bmatrix} V_{1} \\ V_{2} \\ \vdots \\ \vdots \\ V_{N} \end{bmatrix}$$

where the matrix [P] is the inverse of [C], and is called the potential coefficient matrix. If the conductors are assumed to propagate a pure TEM mode, then an inductance matrix is defined where

$$[L][C] = \mu_{\circ} \in_{\circ} [I]$$

(26)

(27)

or

$$[L][C] = \mu_{\circ} \in_{\circ} [C^{-1}] [I] = \mu_{\circ} \in_{\circ} [P]$$

or

Now we make the analogy  $V \leftrightarrow T$ ,  $Q \leftrightarrow P_{diss}$  where  $P_{diss}$  is the dissipated power (no relation to the potential coefficient matrix). Now assume  $p_{ij} \leftrightarrow R_{ij}$ , where  $R_{ij}$  are the self and mutual coupling thermal resistances of the gates; then

$[P] = \frac{1}{\mu_0 \in \Omega} [L]$

| $\int T_1$    | 7 | $\int R_{11}$   | $R_{12}$ |   | $R_{\rm IN}$ | $\begin{bmatrix} P_{dISSI} \\ P_{dISS2} \\ . \\ . \\ P_{dISSN} \end{bmatrix}$ |      |

|---------------|---|-----------------|----------|---|--------------|-------------------------------------------------------------------------------|------|

| $T_2$         |   | R <sub>12</sub> |          |   |              | P <sub>dISS2</sub>                                                            |      |

|               | = |                 |          | • |              |                                                                               | (28) |

|               |   |                 |          |   |              |                                                                               |      |

| $\lfloor T_N$ |   | $R_{\rm NI}$    |          |   | $R_{\rm NN}$ | [P <sub>dISSN</sub> ]                                                         |      |

We assume all gates dissipate the same power, so the temperature on any gate is

$$T_k = (R_{k1} + R_{k2} + R_{k3} + \ldots + R_{kN}) P_{dissk}$$

<sup>(29)</sup>

or just the sum of all thermal resistances in row k. Here  $P_{dissk}$  is the dissipated power in gate k, which is the same for all gates. We then assume

$$\frac{R_{11}}{R_{12}} = \frac{p_{11}}{p_{12}},\tag{30}$$

or

that is, the ratios of the self and mutual terms are the same. This should be exact due to the analogy. We will determine  $R_{ij}$  for any single conductor; then scale all other  $R_{ij}$  accordingly. For our typical cases the parameter ranges are:

$$W \sim 24 \ \mu m$$

$h \sim 350 \ \mu m$   $W/h \sim 7.10^{-2}$   $S/W \sim 2$

$S \sim 40 \ \mu m$   $l \sim 200 \ \mu m$   $l/h \sim 0.6$   $S/h \sim 0.1$ ,

which are not typical for most microstrip coupled line structures.

Notice the thermal conductivity  $\kappa$  and  $\varepsilon$  correspond in the analogy. The analogy holds for homogenous materials, but for the inhomogeneous case, problems arise. Our case is inhomogeneous as we are assuming strips on a material with air above in the electrical case. The thermal case is that for finite thermal conductivity below the strips, but zero above. The electrical case cannot have zero for the permittivity of the air. Recall that microstrip is quasi-TEM and an effective permittivity  $\varepsilon_{re}$  is used. There are flux lines and potential contours in the air above the substrate, and  $\varepsilon_{re}$  is a measure of this effect. For the electrical case we have

$$\mu_o \varepsilon_o \varepsilon_{re}[P] = [L], \tag{31}$$

and thus we might replace  $\kappa$  of the substrate with some effective value. We don't have to deal with this however, as we are using ratios, and all terms carry the same  $\kappa$ . Actually the gate footprints on the substrate are about 1  $\mu$ m below the actual air (i.e., beneath the GaN and AlN layers), so we can assume we are dealing with an almost completely homogeneous region. Then the analogy will hold, i.e., we are solving Laplace's equation in a source-free homogenous region. Recall that we use  $\kappa(T_o)$  to treat the problem as linear, then obtain the true temperature via the Kirchhoff transform.

Our task is to determine the self and mutual inductance entries in the [L] matrix

Due to symmetry  $L_{ij} = L_{ji}$  and for say a 5×5 array we have

$$\begin{bmatrix} L \end{bmatrix} = \begin{bmatrix} L_{11} & L_{12} & L_{13} & L_{14} & L_{15} \\ L_{12} & L_{11} & L_{12} & L_{13} & L_{14} \\ L_{13} & L_{12} & L_{11} & L_{12} & L_{13} \\ L_{14} & L_{13} & L_{12} & L_{11} & L_{12} \\ L_{15} & L_{14} & L_{13} & L_{12} & L_{11} \end{bmatrix} .$$

(33)

Observe all entries on any diagonal (top left to bottom right) are the same. The actual determination of the  $L_{ij}$  is a complex problem. For one thing, inductance requires closed loops, whereas the [L] entries which are in units of H/m are distributed values for assumed infinitely long lines. We choose two alternate methods to calculate [L]; the distributed, and the partial inductance approach. The partial inductances

depend on the length of the conductors as opposed to the distributed idea for infinitely long conductors. Therefore we are including the 3–D effect for heat emerging from the ends of the fingers.

For N circular wires spaced S meters apart, the self inductance  $L_{ii}$  and mutual inductances  $L_{ij}$  (distributed) are (refs. 55 and 56)

$$L_{ii} = \frac{\mu_{\circ}}{2\pi} \ell n \left(\frac{2h}{a}\right) \quad h \rangle a , \qquad (34)$$

where a = radius, h = height above ground plane, and

$$L_{ij} = \frac{\mu_{\circ}}{4\pi} \ell n \left\{ \frac{S_{ij}^2 + (2h)^2}{S_{ij}^2} \right\}.$$

(35)

For a 5 conductor array we have,  $S_{12} = S$ ,  $S_{13} = 2S$ ,  $S_{14} = 3S$ ,  $S_{15} = 4S$ ; thus

$$L_{12} = \frac{\mu_{\circ}}{4\pi} \ell n \left\{ \frac{S^2 + (2h)^2}{S^2} \right\}$$

(36)

$$L_{13} = \frac{\mu_{\circ}}{4\pi} \ell n \left\{ \frac{(2S)^2 + (2h)^2}{(2S)^2} \right\}$$

(37)

$$L_{14} = \frac{\mu_{\circ}}{4\pi} \ell n \left\{ \frac{(3S)^2 + (2h)^2}{(3S)^2} \right\}$$

(38)

$$L_{15} = \frac{\mu_{\circ}}{4\pi} \ell n \left\{ \frac{(4S)\mathbf{l} + (2h)^2}{(4S)^2} \right\}.$$

(39)

Due to symmetry of [L], we need only generate the first row terms. Observe

$$L_{1k} = \frac{\mu_o}{4\pi} \ell n \left\{ \frac{\left[ (k-1)s \right]^2 + (2h)^2}{\left[ (k-1)s \right]^2} \right\}.$$

(40)

For rectangular conductors:

$$L_{ii} = \frac{\mu_{\circ}}{2\pi} \ell n \left\{ 1 + 2\pi \frac{h}{(w+t)} \right\}, \tag{41}$$

where w = width of stripe, t = thickness, and

$$L_{ij} = \frac{\mu_{\circ}}{4\pi} \ell n \left\{ \frac{S_{ij}^2 + \left[ 2\left(h + \frac{t}{4}\right) \right]^2}{S_{ij}^2} \right\}.$$

(42)

We can also use the self inductance of microstrip to express  $L_{ii}$ ,

$$L_{ii} = \frac{\mu_{\circ}}{4\pi} \ell n \left\{ 1 + 32 \left( \frac{h}{w} \right)^2 \left[ 1 + \sqrt{1 + \left( \frac{\pi w}{8h} \right)^2} \right] \right\}.$$

(43)

All of the above formulas are for external inductances, which should be appropriate for our case of widely separated gates. The previous formulas may be found scattered in the literature with slight modifications. One basic assumption is that  $L_{ij}$ , the mutual inductance between conductors *i* and *j*, depends only on the distance between them. The presence of the other conductors is ignored. Experimentally this has been verified, and for our case of not strong coupling, it should hold well. Numerical solutions in the literature shows the errors incurred with this assumption (ref. 56); and for our parameter ranges the errors are a few percent at most.

As stated earlier, our lines are not extremely long with respect to spacing and ground plane distance, so perhaps partial inductances could make for a better model. We choose only two forms; those for self and mutual inductances of rectangular conductors and filaments, respectively.

$$L_{ii}^{p} = 0.2\ell \left[ \ell n \left( \frac{2\ell}{w+t} \right) + 0.5 + .2235 \frac{(w+t)}{\ell} \right] \mu \mathrm{H}$$

$$\tag{44}$$

$$L_{ij}^{p} = 0.2\ell \left[ \ell n \left( \frac{\ell}{S_{ij}} + \sqrt{1 + \left( \frac{\ell}{S_{ij}} \right)^{2}} \right) - \sqrt{1 + \left( \frac{S_{ij}}{\ell} \right)^{2}} + \frac{S_{ij}}{\ell} \right] \mu H$$

$$\tag{45}$$

Then the entries in the [L] distributed matrix are (ref. 57)

\_

$$L_{ij} = L_{ij}^{p} - L_{ik}^{p} - L_{kj}^{p} + L_{kk}^{p} \qquad i, j = 1, 2, \dots N$$

*i, j* not equal to *k*, (46)

where the superscript *p* means partial inductance value. For example see figure 12.

$$\begin{bmatrix} L \end{bmatrix} = \begin{bmatrix} \left( L_{11}^p - L_{13}^p - L_{31}^p + L_{33}^p \right) & \left( L_{12}^p - L_{13}^p - L_{31}^p + L_{33}^p \right) \\ \left( L_{21}^p - L_{23}^p - L_{31}^p + L_{33}^p \right) & \left( L_{22}^p - L_{23}^p - L_{32}^p + L_{33}^p \right) \end{bmatrix}$$

(47)

For the ground plane partial self inductance  $L_{33}^p$ , we will use the image of a single conductor, i.e., 1 or 2.

Figure 12.—Notation for calculation of self and mutual partial inductances for two conductors over a ground plane.

All of the equations presented in this section have been checked with reports in the literature (refs. 58 to 65), and we found good agreement in most cases. The worst cases were numerical simulations with tight coupling (not our case). For geometries close to our range (ref. 56), the error was ~3 percent.

### V. Comparison of Analytical Models—Single Finger

This section compares the theoretical predictions for thermal resistance and channel temperature for single gate (finger) devices with the measurements of Kuball (ref. 15).

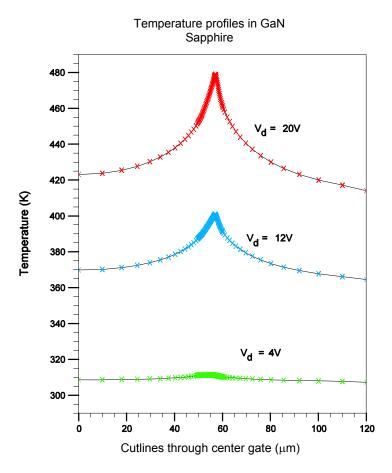

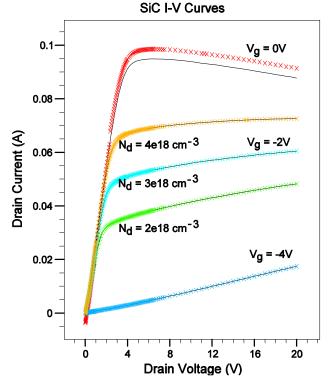

#### **One Stripe on Sapphire**

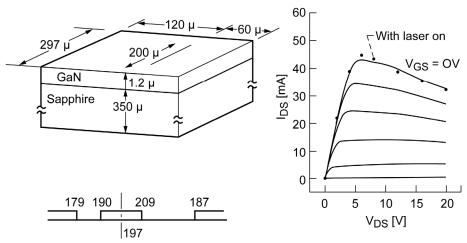

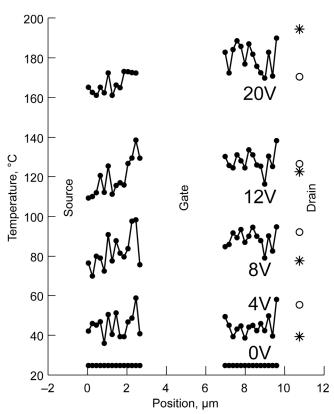

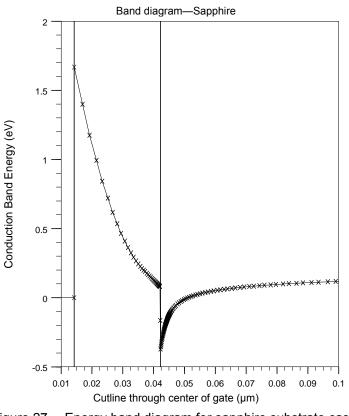

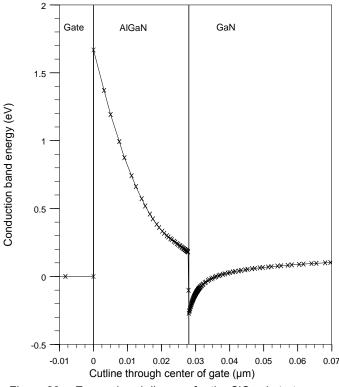

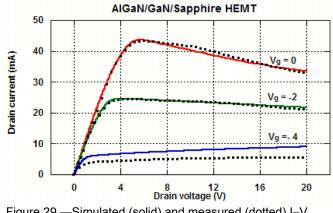

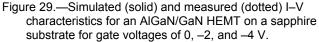

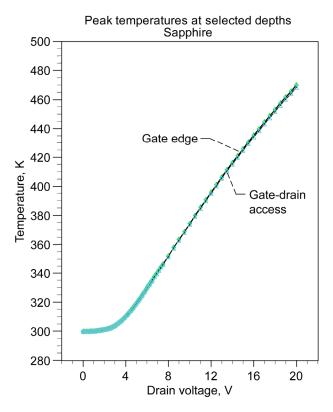

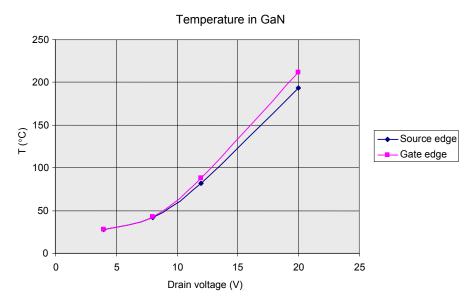

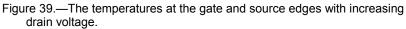

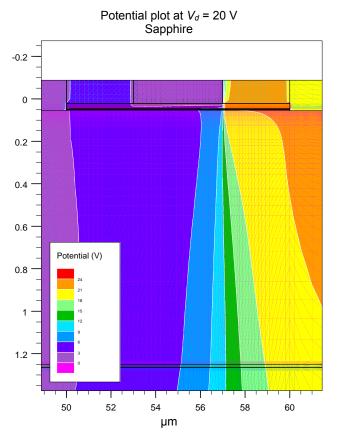

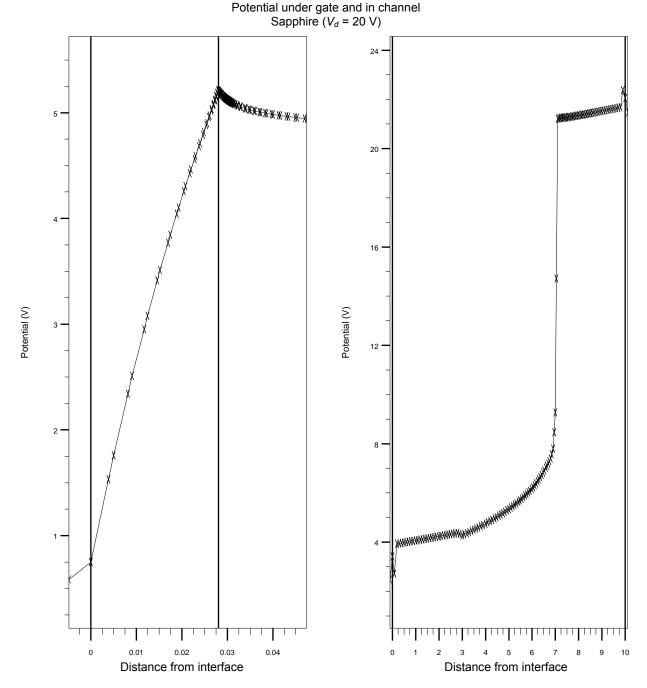

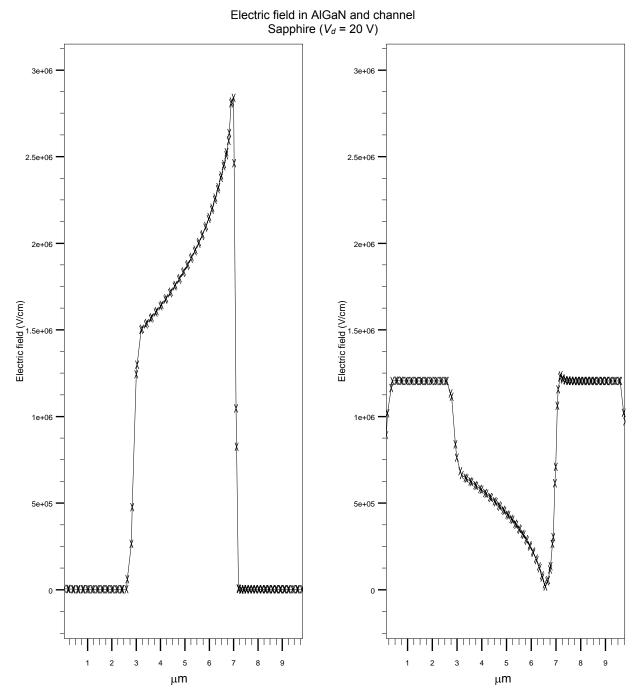

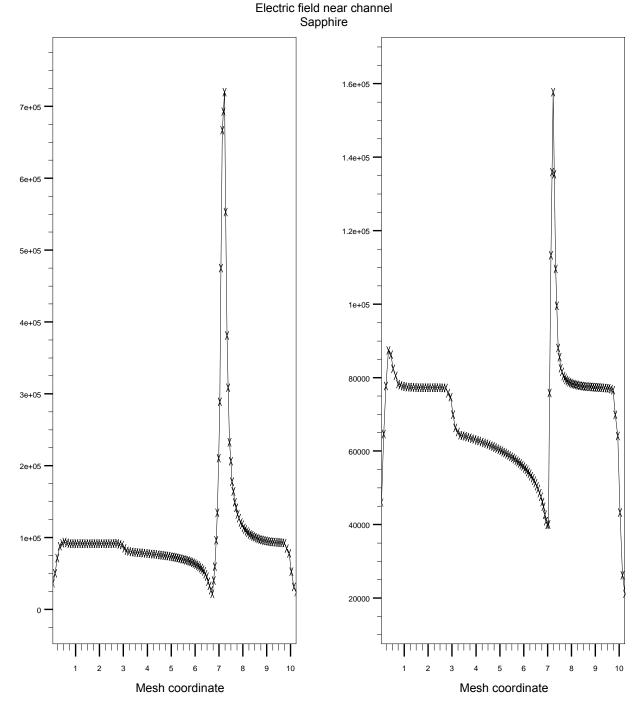

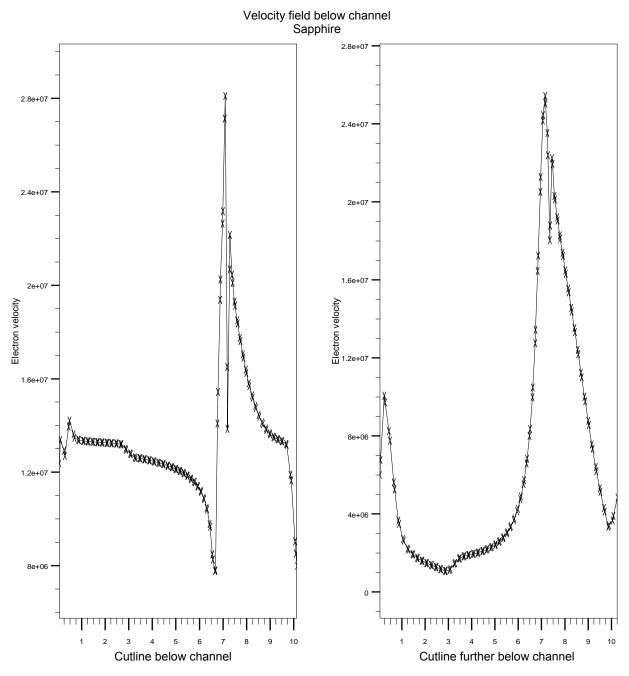

Kuball's group simultaneously measured the channel temperature using Raman spectroscopy and the I–V characteristics of AlGaN/GaN HEMTs. Figure 13 gives the schematic of a single 200  $\mu$ m wide gate on a GaN layer grown on sapphire. The gate length is 4  $\mu$ m. The source and drain pads are omitted for clarity, and their shape and presence did not have any affect on the channel temperature, as stated by the authors. The measured I–V characteristics are also shown.

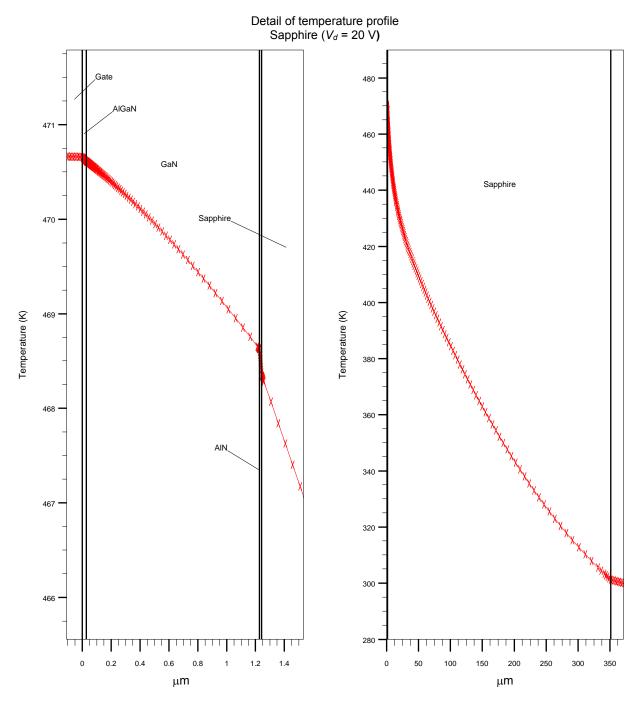

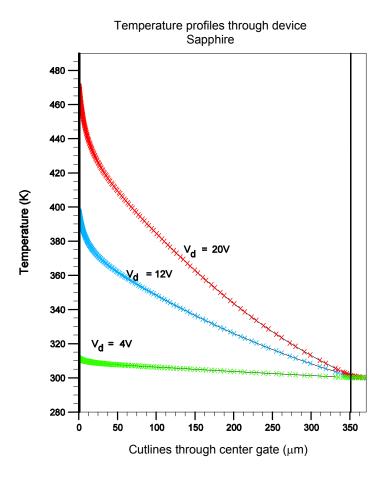

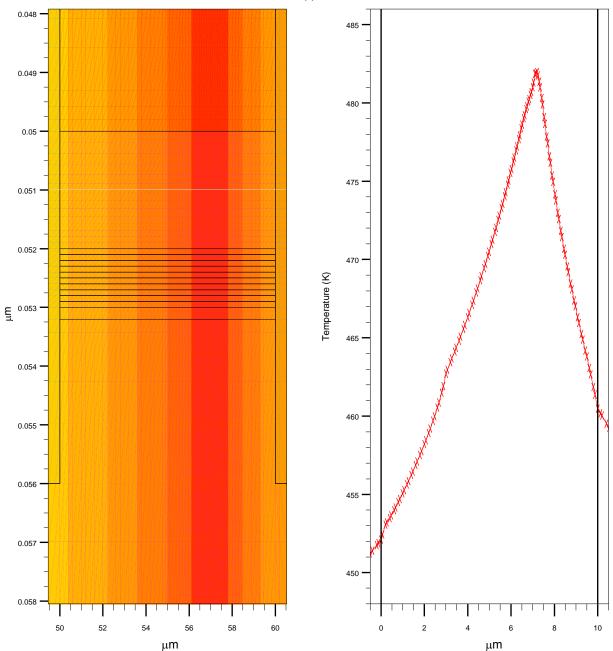

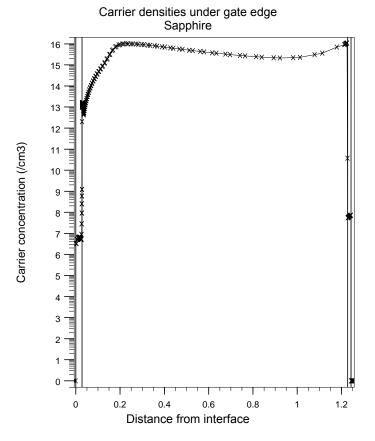

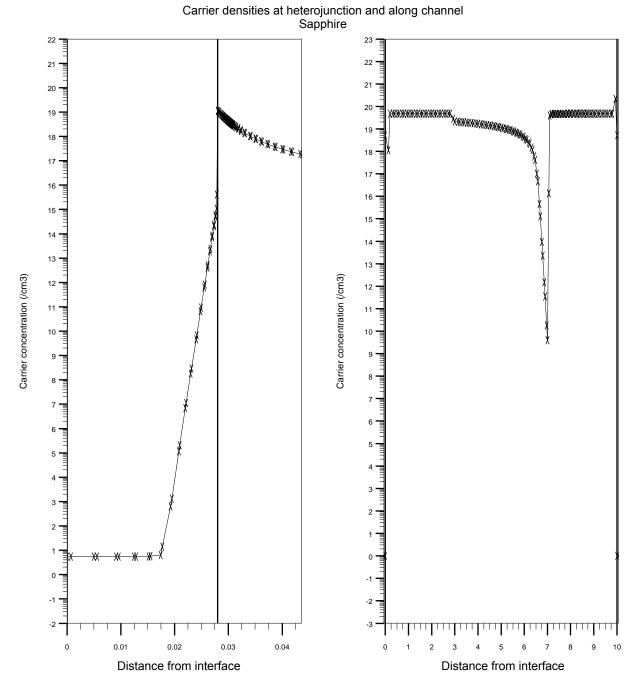

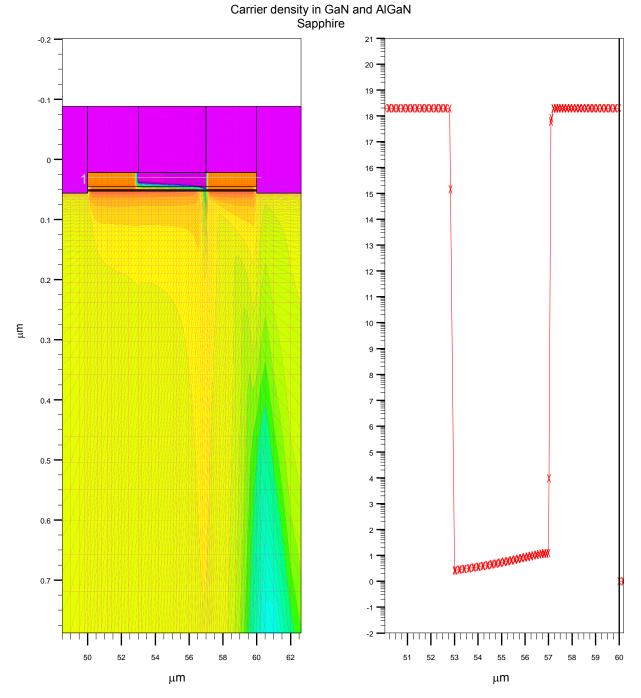

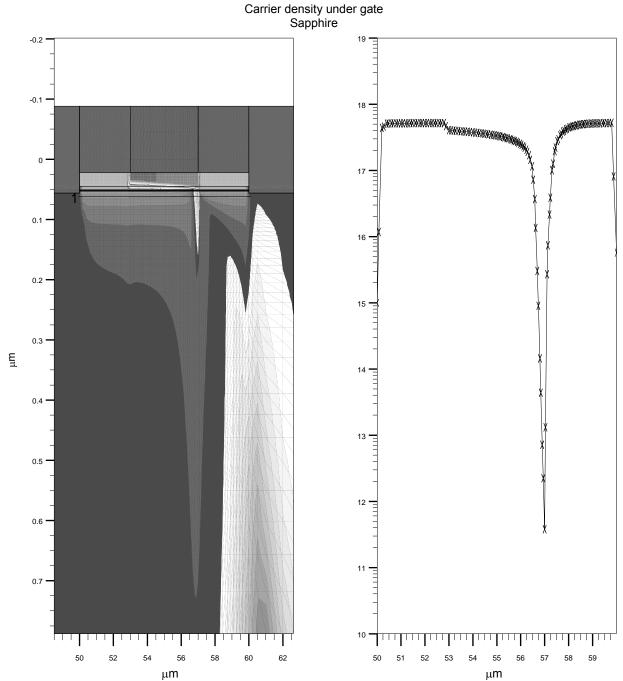

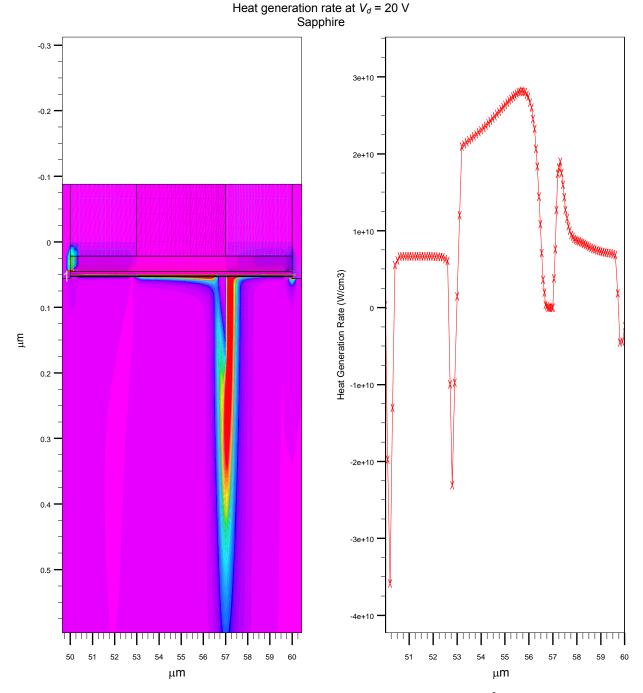

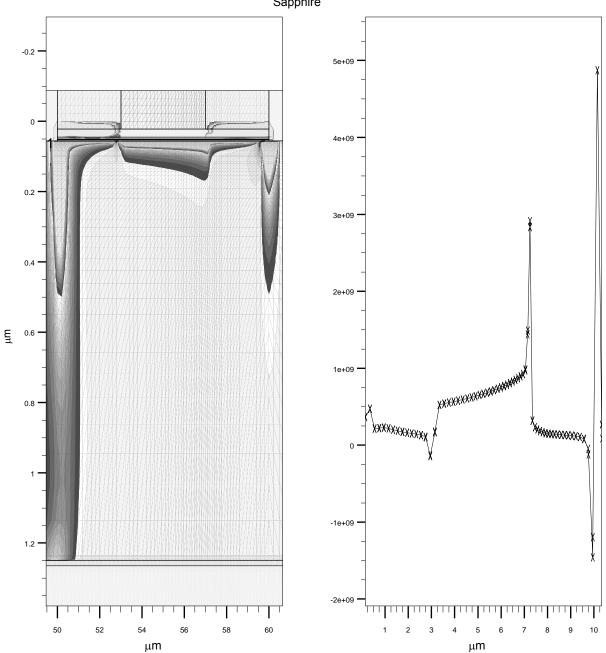

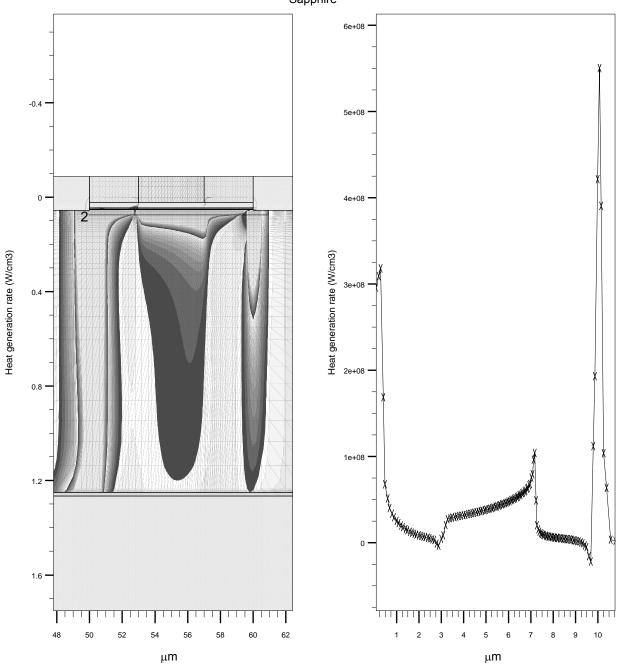

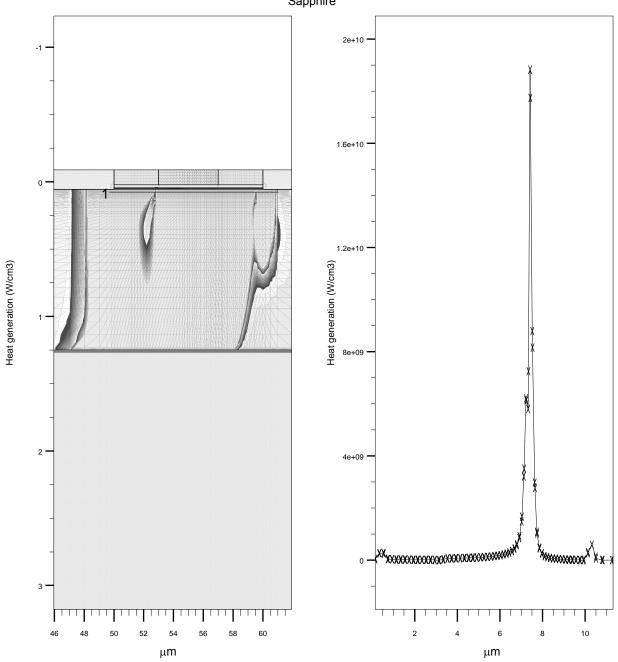

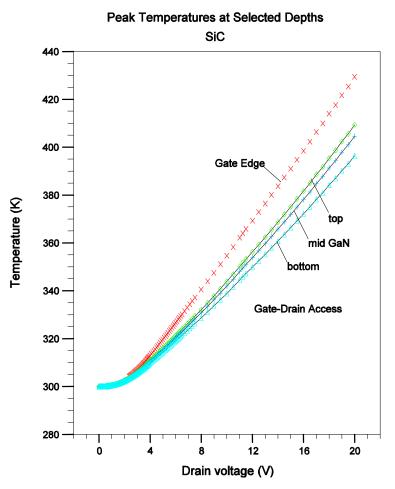

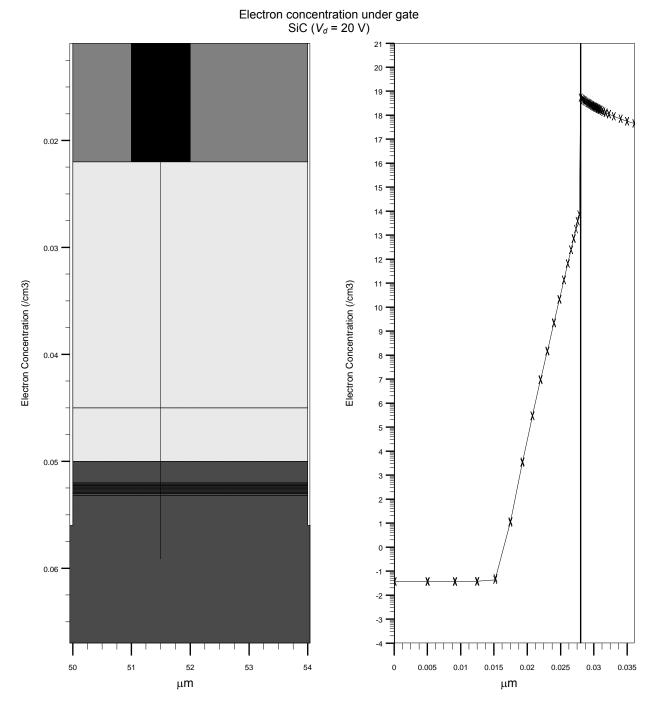

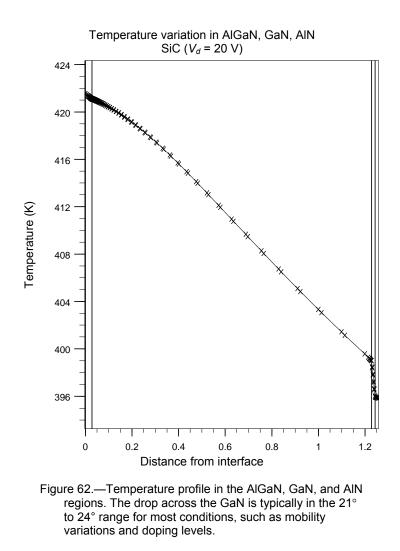

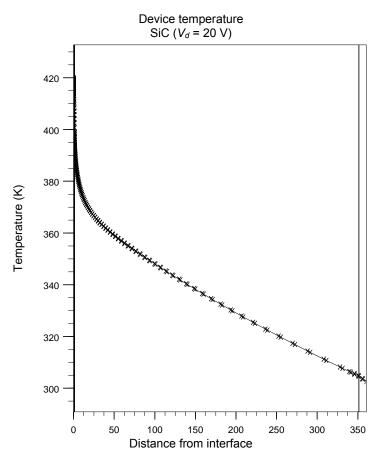

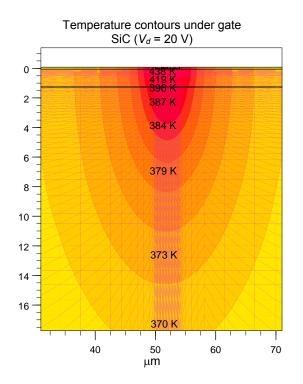

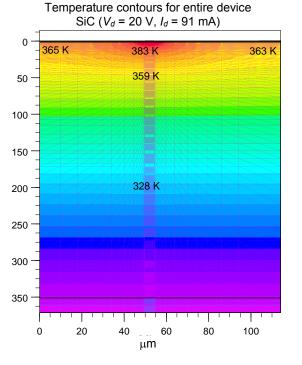

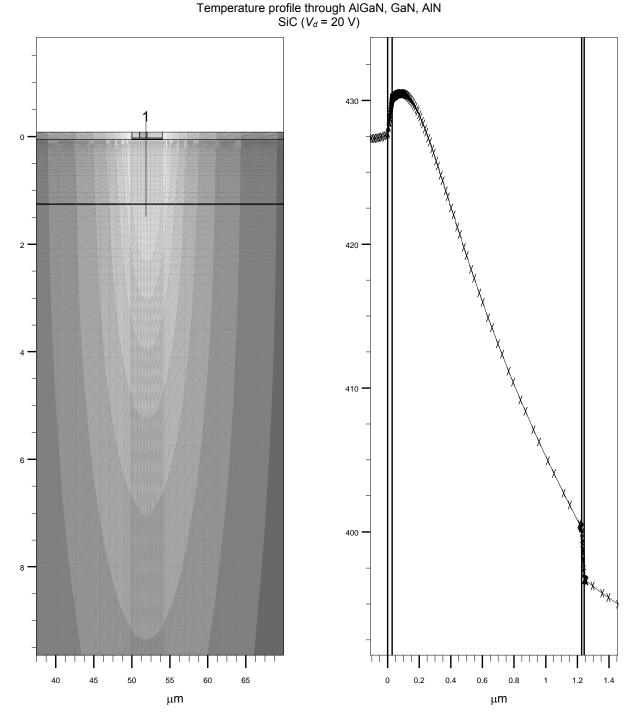

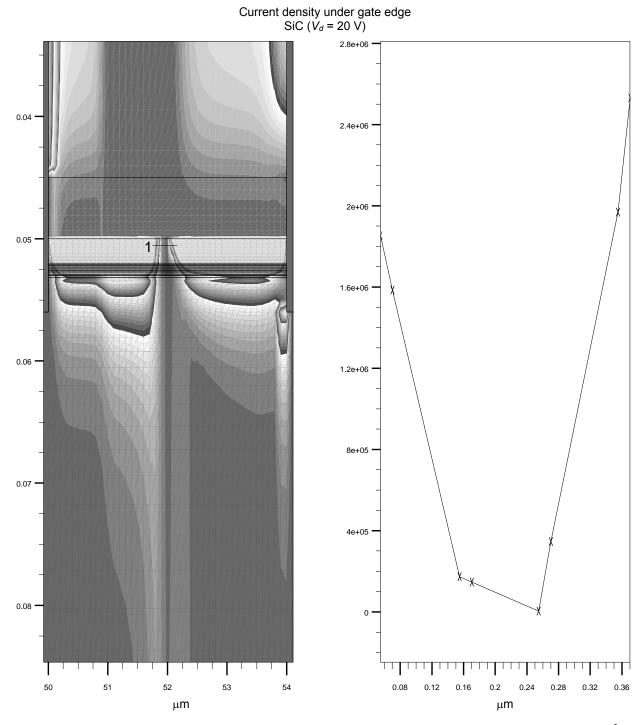

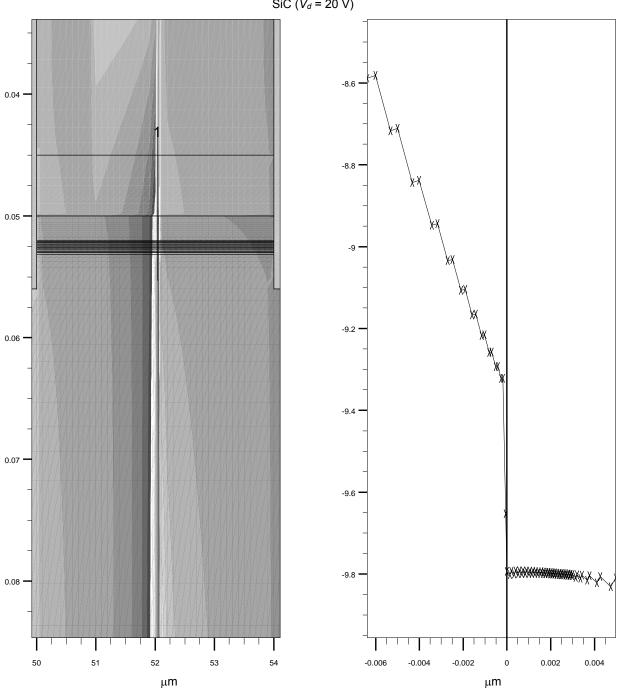

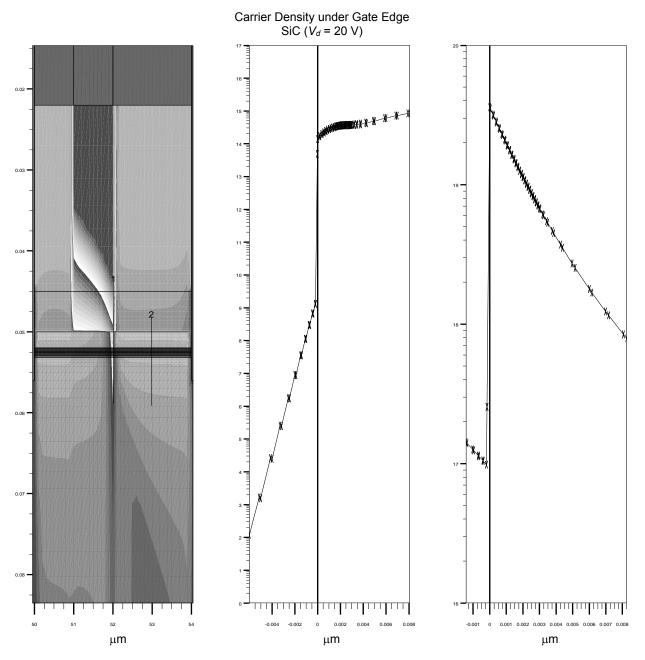

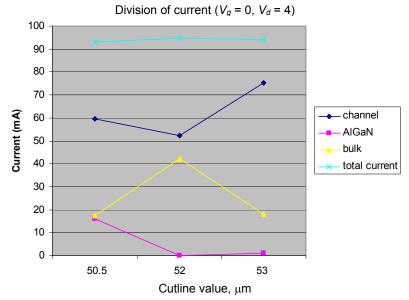

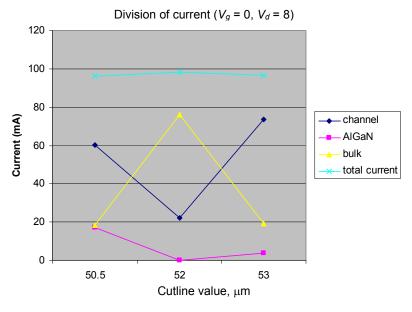

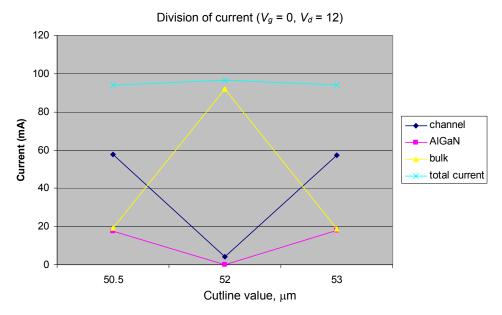

Table 2 summarizes the measured channel temperature, the drain current, and the dissipated power, for several drain voltages  $V_d$ , all for the gate at 0 V. Notice that the dispersion in the data is from 10° to 20°. At the bottom of figure 13 is a schematic of the gate region with the temperatures at several points determined by simulation (which will be discussed in detail in section VIII) at  $V_d = 20$  V. Observe the simulation values fall into the measured range of 179 to 190 °C.

TABLE 2.—DATA FOR A SINGLE STRIPE HEMT ON A SAPPHIRE SUBSTRATE

| $V_d, \mathbf{V}$                | 4        | 8        | 12         | 20         |

|----------------------------------|----------|----------|------------|------------|

| T, ℃                             | 40 to 60 | 80 to 95 | 120 to 140 | 179 to 190 |

| < T > avg. temperature           | 45       | 90       | 129        | 180        |

| $I_d$ , mA, drain current        | 39       | 42.5     | 39.5       | 32.5       |

| $P_{diss}$ , W, dissipated power | 0.156    | 0.34     | 0.474      | 0.65       |

Figure 13.—Schematic of single gate HEMT and the measured I–V curves. Notice the gate is not centered on the chip.

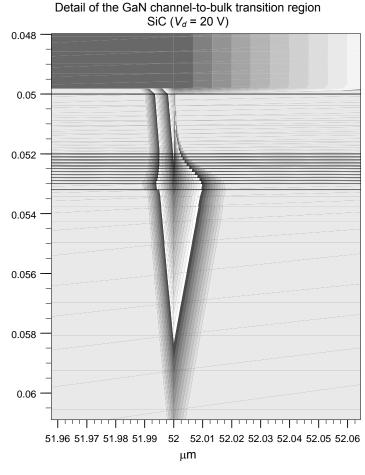

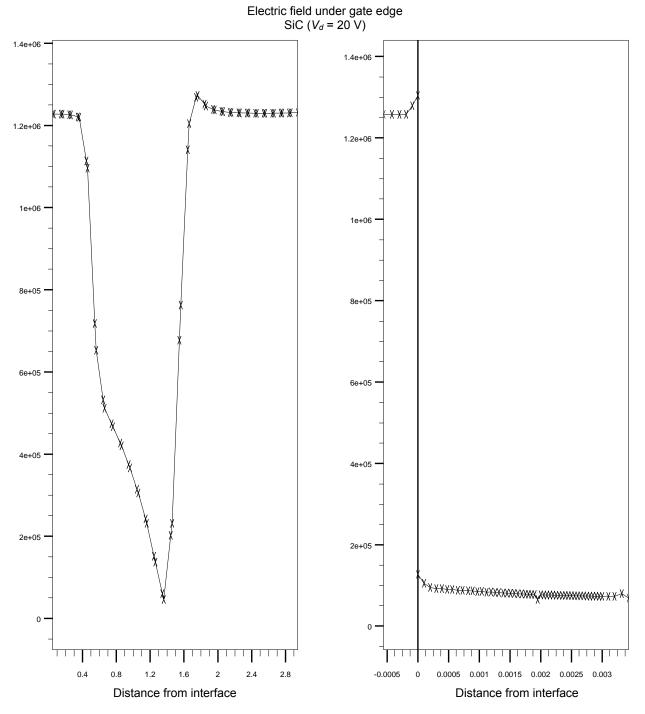

The procedure to calculate the channel temperature is simplified by noting that over 95 percent of the thermal drop occurs in the sapphire substrate due to its thickness. The sapphire constitutes 350/351.2 = 99.7 percent of the thickness of the device. The key step is the determination of the effective gate length footprint on the top surface of the sapphire. For this case the actual gate length is 4 µm. If we assume the heat is generated uniformly under the gate, and it diffuses downward at 45° angles from the gate edges, the footprint at the bottom of the GaN layer is 6.4 µm. The assumption of 45° implies no edge effects, so the heat moves away into an unbounded semi-infinite half-space. Now passing through the AlN region causes some change in the heat flow, and we obtain best results by assuming the footprint on the sapphire to be 6 µm. This focusing effect in the AlN is demonstrated in section VIII. The parameters in section III, the *Thermal Analysis Procedure*, section II, for this case are:

$$2l_x = 6 \ \mu m$$

$2l_y = 200 \ \mu m$

$2L_x = 180 \ \mu m$

$2L_y = 300 \ \mu m.$

$W_n = 3.89$

Then

$W_n = 3.89$   $\gamma_{\varepsilon} = 33.3$   $\gamma_s = 1.67$  $l_{xn} = 0.033 \ \rho_s = 0.49/4 = 0.123$ ,

where we assume the solder layer on the copper heatsink is so thin as to be negligible. The thermal conductivity of copper is taken to be 4 W/(cm K). We find  $\alpha = 43.8^{\circ}$ ,  $\beta = 15.7^{\circ}$ , and  $R_{th} = 174.3$  K/W. Table 3 provides the sensitivity of  $R_{th}$  for several effective footprints.

| α AND $β$ WITH THE FOOTPRINT ON THE SAPPHIRE LAYER |      |       |      |       |       |       |  |  |  |

|----------------------------------------------------|------|-------|------|-------|-------|-------|--|--|--|

| $2l_x(\mu m)$                                      | 0.5  | 1.25  | 2    | 4     | 6     | 8     |  |  |  |

| $R_{th}$ (K/W)                                     | 294  | 248.6 | 226  | 193   | 174.3 | 161.7 |  |  |  |

| α (°)                                              | 44.9 | 44.8  | 44.6 | 44.24 | 43.8  | 43.5  |  |  |  |

| β (°)                                              | 15   | 15.1  | 15.7 | 15.7  | 15.7  | 15.7  |  |  |  |

TABLE 3.—THE SENSITIVITY OF  $R_{th}$  AND THE SPREADING ANGLES

It will be shown later that only a few degrees are dropped across the GaN and AlN layers, so we can estimate  $R_{th}$  (sapphire) from the measured data. The procedure is the following. For the 4 V case the measured average channel temperature was 45 °C (318 K). Assume 2 °C dropped across the GaN and AlN layers, then the top of the substrate is at 316 K. Then the corresponding transformed temperature is therefore 315.6 K (from eq. (12)). The drop in the transformed temperature across the sapphire is thus 315.6 K – 300 K = 15.6 K. Then  $R_{th}$  (4 V) =  $\Delta \theta/P_{diss}$  = 15.6 K/0.156 W = 100 K/W. Table 4 gives the results for all drain values.

TABLE 4.—THERMAL RESISTANCE AT SELECTED DRAIN VOLTAGES

| EATRACTED FROM MEASURED RESULTS OF RUBALL |     |     |     |     |  |  |  |

|-------------------------------------------|-----|-----|-----|-----|--|--|--|

| $V_d(\mathbf{V})$                         | 4   | 8   | 12  | 20  |  |  |  |

| $R_{th}$ (K/W)                            | 100 | 163 | 182 | 188 |  |  |  |

Observe the average for the last three entries is 177.7 which is slightly less than 2 percent different from our calculated value. Using  $R_{th} = 174.3$  K/W we find the channel temperature at  $V_d = 20$ V as follows. The linear drop across the sapphire is  $\Delta \theta = (174.3) (0.65) = 113.3$  K, so the top surface is at 300 + 113.3 K = 413.3 K. The actual temperature from equation (12) is 437.7 K (164.7 °C). For the 1.2 µm GaN channel with  $2l_x = 4$  µm and using  $\kappa$ (GaN) at 438 K, we obtain  $\kappa = 1.97(300/438)^{0.48} = 1.64$ . Then the thermal resistance of the GaN layer is  $R_{th} = 6.1$  K/W, and the change across the GaN is  $\Delta \theta = (6.1) (0.65) = 3.79$  K. Using equation (10) with  $T_o = 437.7$  K,  $\theta = 441.67$  K, and r = 0.48 yields 441.6 K, or 168.6 °C. So the drop across the GaN layer is just 3.9° as anticipated. This final temperature compares favorably with the average of 180 °C of the measurements.

Table 5 summarizes the estimated temperatures for drain voltages of 4, 8, 12, and 20 V. Figure 14 is reproduced from Kuball's paper and shows the temperature measurements in the access regions about the gate. The circles to the right of the data in the gate – drain access region are the values given in table 5. The asterisks are the values in the channel region obtained by simulation. The uncertainty in Kuball's data was  $\pm$ 5 °C. We conclude that the outlined procedure works very well.

TABLE 5.—COMPARISON BETWEEN AVERAGE MEASURED CHANNEL TEMPERATURES <7> AND CALCULATED ONES T<sub>cale</sub> FOR SINCLE STRIPE HEMT ON SADDUBE SUBSTRATE

| SINGLE STRIPE HEMT ON SAPPHIRE SUBSTRATE |    |    |     |     |  |  |  |

|------------------------------------------|----|----|-----|-----|--|--|--|

| $V_d$ , V                                | 4  | 8  | 12  | 20  |  |  |  |

| <7>, °C                                  | 45 | 90 | 129 | 180 |  |  |  |

| $T_{\text{calc,}}$ °C                    | 56 | 92 | 125 | 169 |  |  |  |

Figure 14.—The measured and calculated temperatures in the S-G and G-D access regions. The simulated values at the AlGaN/GaN junction are shown as asterisks at 4, 8, 12, and 20 V. The calculated values are the circles. The uncertainty of any measured value is 10 °C. (sapphire substrate).

At this point we discuss some of the problems associated with this series of publications. For the results in these papers, the heat sink was not held at room temperature, but allowed to rise as the dissipated power increased. Thus the measured channel temperature value includes the thermal rises across the layers along with the unknown reference temperature of the sink. For the sapphire case the edge went up about 20 °C. Kuball states we can assume the sink rose by that amount. Our calculated temperature is about 12° low, which we can surmise is due to the fact that we assumed the sink to remain at room temperature (27 °C). The data in (ref. 18) suggest that the sink rose to 40 °C, which would boost our values approximately 13°! Then we would agree to within 1°, which of course is beyond our anticipated accuracy. Nevertheless, we can apparently get rather good results with judicious approximations. Kuball states his system accuracy to be within 10 °C.

Now  $\kappa_{AIN}$  is temperature independent and we assume its value to be 0.1. This is about 1/10<sup>th</sup> of its bulk value, but typical for thin films grown on sapphire or SiC. As a matter of fact, the authors in (ref. 66) have reported measurements that show the thermal conductivity may be two orders of magnitude below the bulk value, when grown on Silicon. Kuzmik et al. (ref. 67) have used different values for  $\kappa_{AIN}$  in simulations, depending on the layer upon which it was grown. Since we do not know the specifics of their AlN layer, some small error exists. However, the thermal resistance formula is insensitive to  $\rho_s$ , so the error should be very small. Assuming a parallel isotherm flow pattern in the AlN, (and the thickness to be 0.015 µm) we obtain  $R_{th}$  (AlN) = 0.75 K/W, with a corresponding thermal drop of 0.49°; which we have neglected.

While we have been able to get results that agree with Kuball's data, we still have some reservations. The first issue is the reliability of the measurements. In a recent paper (ref. 68) concerning the measurement of temperature in AlGaN/GaN devices using Raman scattering, it was shown that very different results are obtained when different phonon lines are observed. Specifically, the UV line recorded temperatures which were consistently higher by as much as 70 °C as that found using a line in the visible. The reason is the depth of penetration of the light into the sample. For a device similar to the one investigated here, the difference in measured temperature was about 70 °C for the dissipated power of 0.65 W. Kuball's group used the line in the visible, which averages the temperature in the GaN.

Table 6 compares the thermal resistances calculated by the equations of Masana along with the corresponding channel temperatures. In these calculations we used the following approach. First start with the actual gate length and calculate the thermal resistance using the room temperature value for thermal conductivity. Use the calculated spreading angles to determine the footprint. Calculate the substrate thermal resistance. Then calculate the temperature rise across both layers using the dissipated power. Next recalculate  $R_{th}$  using the values of  $\kappa$  corresponding to the average of its values at the new temperature and room temperature. Then calculate the channel temperature.

| TEMPERATURES USING THE EQUATIONS OF MASANA |             |                                          |       |            |  |  |  |  |

|--------------------------------------------|-------------|------------------------------------------|-------|------------|--|--|--|--|

| $V_d$ ,                                    | $P_{diss},$ | $P_{diss}$ , $R_{th}$ (GaN), $R_{th}$ (s |       | $T_{ch}$ , |  |  |  |  |

| V                                          | W           | K/W                                      | K/W   | °C         |  |  |  |  |

| 4                                          | 0.156       | 5.37                                     | 165.4 | 53.6       |  |  |  |  |

| 8                                          | 0.34        | 5.62                                     | 172.3 | 87.5       |  |  |  |  |

| 12                                         | 0.474       | 5.81                                     | 176.8 | 113.6      |  |  |  |  |

| 20                                         | 0.65        | 6.06                                     | 182.6 | 149.6      |  |  |  |  |

TABLE 6.—THERMAL RESISTANCES AND RESULTING CHANNEL TEMPERATURES USING THE FOUATIONS OF MASANA

Table 7 shows the results of a similar calculation, this time using the equations of Cooke. In this case we assume the spreading angles are  $45^\circ$ , since the edges are sufficiently far away. The final footprints in the two calculations are  $4.064 \times 203.15$  versus  $6.4 \times 202.4 \ \mu\text{m}^2$ . The final channel temperatures are 149.6 and 93.4 °C, a difference of 56.2°, which we consider significant. Observe they differ from that in table 5 by unacceptable amounts.

| TEMPERATURES USING THE EQUATIONS OF COOKE |                                               |      |                  |            |  |  |  |  |

|-------------------------------------------|-----------------------------------------------|------|------------------|------------|--|--|--|--|

| $V_d$ ,                                   | $P_{diss}$ , $R_{th}$ (GaN), $R_{th}$ (sapp), |      | $R_{th}$ (sapp), | $T_{ch}$ , |  |  |  |  |

| V                                         | W                                             | K/W  | K/W              | °C         |  |  |  |  |

| 4                                         | 0.156                                         | 3.47 | 92.5             | 42         |  |  |  |  |

| 8                                         | 0.34                                          | 3.56 | 94.6             | 60.4       |  |  |  |  |

| 12                                        | 0.474                                         | 3.63 | 96.5             | 74.8       |  |  |  |  |

| 20                                        | 0.65                                          | 3.72 | 98.4             | 93.4       |  |  |  |  |

TABLE 7.—THERMAL RESISTANCES AND RESULTING CHANNEL TEMPERATURES USING THE EQUATIONS OF COOKE

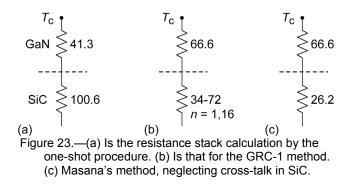

### VI. Comparison Between Darwish et al., and the GRC-1 Model

The previous section compared the predictions of Masana and Cooke for the thermal resistance of a single gate. Masana's equations are only valid for a single gate, whereas those for Cooke are valid for either single or multiple gates. The formulas by Darwish, et al. (ref. 45) are only valid for the multiple gate case, and should be accurate for about five or more gates. The multi-conductor method of section IV should be applicable to either single or multiple gate cases. For brevity we will call the analysis method and final equation by Darwish, the one-shot result. The iterative approach, which uses Masana's equations for the single gate where appropriate (in the GaN layer), and Cooke's equation for the multiple gate case (in the substrate) will be labeled the GRC-1 method. The results from the multi-conductor equations will just be called the multi-conductor results.

As stated previously the models are complementary, but they can be compared in their regions of overlap. We will determine a value for  $R_{th}$  for the following data set:

$$L_g = 2l_x = 0.25 \ \mu m$$

$w_g = 2l_y = 250 \ \mu m$

$t_{GaN} = 1 \ \mu m$

$t_{SiC} = 100 \ \mu m$

$S = 40 \ \mu m$

$\kappa_{SiC} = 3.3 \ W/(cm \cdot K)$

$\kappa_{GaN} = 1.5 \ W/(cm \cdot K).$

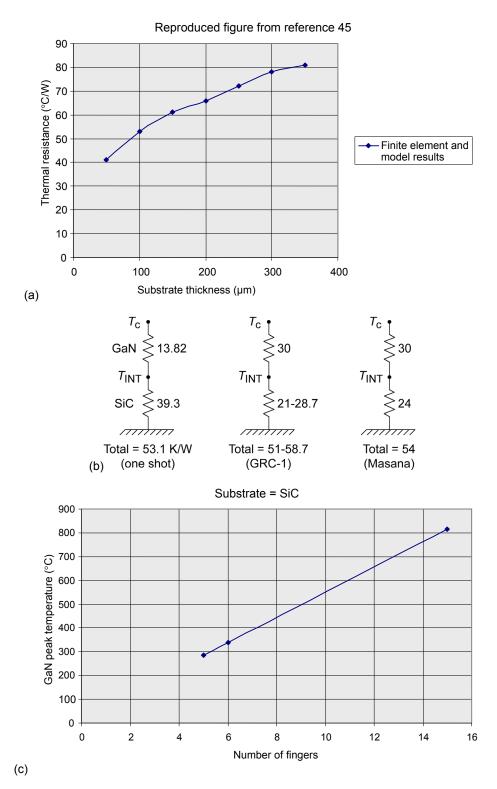

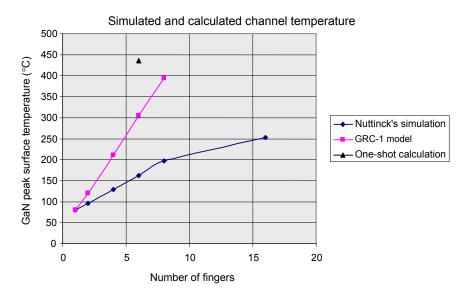

which is that given in (ref. 45) as an example, and plotted in their figure 4. The one-shot method finds the thermal resistance of the GaN layer (region 1) to be  $\Theta_{r}=13.82$  K/W, and that for the two portions of region 2 to be 19.37 and 19.95 K/W. The total resistance is 53.1 K/W, which agrees exactly with the plotted curve in their figure 4, which is reproduced here as figure 15(a). The figure shows nearly perfect correlation between the analytical calculation and the finite element results. The GRC-1 method obtains  $R_{th}$  in the GaN to be 30 K/W. This is assumed to be valid as the gates are separated by 40  $\mu$ m, and will not interact in the 1  $\mu$ m GaN layer. We have some leeway on the calculation of the thermal resistance of the SiC layer. Since the thickness is 100 µm and the spacing between fingers is 40 µm, and if we assume spreading is at 45°, then each finger interacts with four of its neighbors (two on each side). Using Cooke's formula, the resistance of the SiC layer changes from  $R_{th}$ =21 to 28.7 K/W, as the number of fingers varies from 1 to 20. Then the total resistance is 30 + (21 thru 28.7) = 51 thru 58.7 K/W. If we use Masana's equation for a single finger, we obtain  $R_{th}$  =24 K/W. The total resistance is now 30 + 24 = 54 K/W, see figure 15(b), which agrees closely with the previously found value from Darwish (53.1 K/W). While we hope for agreement, this result is surprising, and we are not sure if this is just a coincidence for this particular case. The fact that they give different values for the GaN and SiC layers, yet the total is the same, is unclear. The determination of the channel temperature is different for the one-shot versus the other two methods. For example; the temperature change for the one-shot case is  $(R_{th})(P_{diss})(n)$  where  $P_{diss}$  is the power dissipated per gate, and *n* is the number of gates. For *n* varying from 5 to 15 with  $P_{diss}$  assumed to be 1.0 W, the channel temperature is shown in figure 15(c). The temperature varies from 286 to 817  $^{\circ}$ C.

Figure 15.—(a) Reproduced figure from reference 45; showing the excellent agreement between the finite element code and their model's results. (b) Observe that all three models give the same net thermal resistance; however, the distribution over the GaN and SiC layers in the one-shot case is very different. (c) The channel temperature from the one-shot calculation.

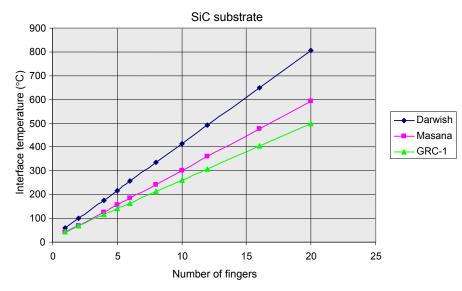

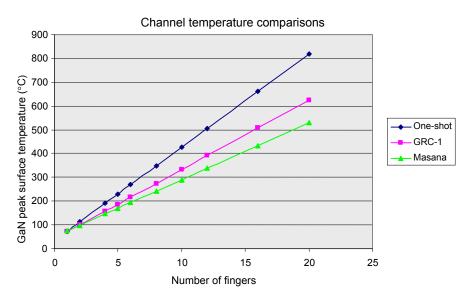

The GRC-1 and Mansana (only) method calculates the channel temperatures as follows. Assume the dissipated power is 4 W/mm, and each finger is 0.25 mm wide; thus the power dissipated per finger is 1.0 W. The temperature change across the channel  $\Delta T_{ch} = R_{th}(\text{GaN})(1.0 \text{ W})$ , and that across the substrate is  $R_{th}(\text{SiC})(P_{diss})(n)$ . The final channel temperature  $T_{ch}$  is the sum of the changes across the substrate and channel +20 °C. Figure 16 gives the interface temperature as the number of fingers varies from 1 to 16, while figure 17 gives the corresponding channel temperature. The upper curve, (one-shot), is derived from the one-shot calculation, while the lower two curves are for Masana's equations in the GaN and Cooke's in the SiC, or Masana's in both layers (neglecting any crosstalk in the SiC layer) respectively. Observe that this channel temperature calculation procedure gives the range of 270 to 663 °C as the number of fingers varies from 6 to 16 for the one-shot case. The upper temperature is around 150 °C lower for this case than the previous method. Table 8 summarizes the temperatures at the GaN/SiC interface and the channel, which are shown in figures 16 and 17.

Figure 16.—Interface temperature rise as the number of fingers increases. The base is held at 20  $^\circ\text{C}.$

Figure 17.—Corresponding increase in channel temperature with change in the number of fingers.

| 1012 | MASANA ONE I (M), ORC-I, AND ONE-SHOT RESI LETIVEET |               |               |          |          |          |  |  |  |  |

|------|-----------------------------------------------------|---------------|---------------|----------|----------|----------|--|--|--|--|

| п    | $T_{\rm int}$                                       | $T_{\rm int}$ | $T_{\rm int}$ | $T_{ch}$ | $T_{ch}$ | $T_{ch}$ |  |  |  |  |

|      | М                                                   | GRC-1         | One-shot      | М        | GRC-1    | One-shot |  |  |  |  |

| 1    | 44                                                  | 41            | 59            | 74       | 71       | 73       |  |  |  |  |

| 2    | 68                                                  | 69            | 99            | 98       | 99       | 112      |  |  |  |  |

| 4    | 116                                                 | 127           | 177           | 146      | 157      | 191      |  |  |  |  |

| 5    | 140                                                 | 156           | 216           | 170      | 186      | 230      |  |  |  |  |

| 6    | 164                                                 | 185           | 256           | 194      | 215      | 270      |  |  |  |  |

| 8    | 212                                                 | 243           | 334           | 242      | 273      | 348      |  |  |  |  |

| 10   | 260                                                 | 302           | 413           | 290      | 332      | 427      |  |  |  |  |

| 12   | 308                                                 | 361           | 492           | 338      | 391      | 505      |  |  |  |  |

| 16   | 404                                                 | 478           | 649           | 434      | 508      | 663      |  |  |  |  |

| 20   | 500                                                 | 594           | 806           | 530      | 624      | 820      |  |  |  |  |

TABLE 8.—INTERFACE AND CHANNEL TEMPERATURES (°C) FOR A GIVEN DATA SET AS COMPUTED BY THREE DIFFERENT METHODS. THEY ARE: MASANA ONLY (M), GRC-1, AND ONE-SHOT RESPECTIVELY

Before considering more comparisons with published results, we discuss the various functional dependencies upon which the thermal resistance depends. One may write the thermal resistance as follows.

$$R_{th} = f(t_{\text{GaN}}, t_{\text{sub}}, \kappa^{\text{GaN}}(T), \kappa^{\text{sub}}(T), W_g, l_x, n, S)$$

The eight parameters are the GaN and substrate thicknesses, their thermal conductivities, the gate width (per finger), the gate length, the number of fingers, and their separation. In general,  $R_{th}$  decreases with increasing  $W_g$ , increasing S, and increasing  $l_x$ . It increases with increasing substrate thickness, and with the number of fingers, n. The strength of the variations depends on the geometry and the heat generation function g(x,y,z).

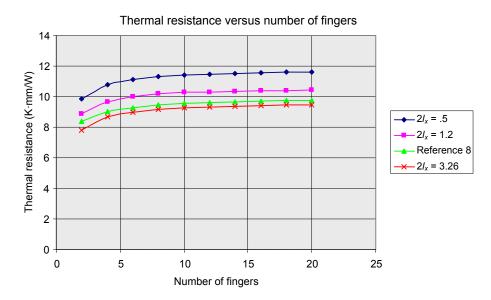

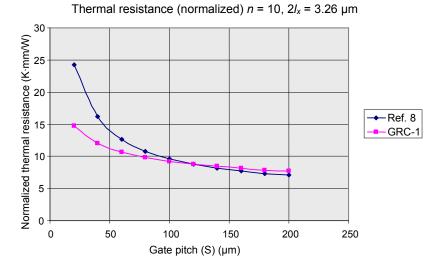

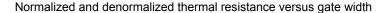

The paper by Bertilsson et al. (ref. 8) concerning lattice heating in SiC MESFETs is illuminating for our purposes. Their figure 4 gives normalized thermal resistance versus finger width  $W_g$ , n, and S. The reference values are 200, 10, and 100  $\mu$ m respectively. Figure 18 gives  $R_{th}$  (normalized to the gate width) as a function of the number of fingers, with the gate length  $(2l_r)$  as a parameter. The physical gate length was 0.5 µm, and the active layers constituted 1.38 µm. Using the footprint method, we determine the effective gate length on the SiC substrate to be 3.26 µm. The curve labeled reference 8 is extracted from figure 4 of the paper. The curve below it is that derived using the GRC-1 method, with gate length =  $3.26 \,\mu\text{m}$ . We consider the agreement to be excellent. The two upper curves show the result if the actual gate length, or the gate-drain spacing is used. This reveals the sensitivity to gate length as well as the agreement obtained using the actual length and determining its footprint. For the given gate length of 0.5 µm, the one-shot methods gives the value of 9.6 K-mm/W. The agreement of both methods with the reference 8 results is aided in part by the thermal conductivity being the same in all regions; the 1.38 µm epitaxial layer and the 330 µm substrate. Figure 19 gives the variation of the thermal resistance with gate pitch S; the diamonds are from reference 8, and the squares are the GRC-1 results. Some values obtained with the one-shot method are stated in the caption. Figure 20 depicts the dependence on gate width; the triangles show the GRC-1 result, and one-shot values are stated in the caption. The denormalized thermal resistance curve shows the true decrease with gate width. The one-shot results match the normalized curve closely, but the GRC-1 curve is too flat.

Figure 18.— $R_{th}$  versus the number of gate fingers for different gate lengths ( $2I_x$ ), based on simulations by Bertilsson (ref. 8). The value predicted by Darwish is 9.6 K-mm/W (independent of the number of fingers).

Figure 19.—Variation of  $R_{th}$  (normalized) with gate pitch. The values by Darwish are 28.1, 9.6, and 7.7 at *S* = 20, 100, and 200 µm, respectively.

Figure 20.—Change in  $R_{th}$  (normalized) (diamonds), and denormalized (squares) with gate width  $W_g$ . Here n = 10 and  $2I_x = 3.26 \mu m$ . The values from Darwish are 6.3, 9.6, and 11.4 at  $W_g = 40$ , 200, and 400  $\mu m$ , respectively.

The next comparison considers the work from Nuttinck et al. (ref. 19). This is one of the few papers wherein the variation with the number of fingers has been shown. The results are those from a simulation. thus we must proceed with some caution. First of all, some of the dimensions, values used for thermal conductivity, etc., were not given, but from study of other publications by the authors, we have been able to develop a reasonable interpretation of their results. In figure 21 the dimensions of the device are shown schematically. The configuration is highly asymmetrical as the source-gate separation is only  $0.1 \,\mu m$ , whereas the gate-drain spacing is 3 µm. The thermal conductivity for SiC at 300 K was assumed to be 3.9 (from one of their other publications). The remaining ones were chosen to be typical values. The simulated channel temperature versus the number of fingers is given in figure 22. Notice the temperature increases linearly as n varies from 1 to 8. However, the value at n=16 falls well below an extrapolated value from the line developed for small *n*. Apparently the temperature given is that of the center finger, and the authors state that above 10 to 12 fingers, additional fingers do not lead to a significant modification of the horizontal heat flow. After 14 fingers, a plateau is reached. Apparently this plateau is the value that the one-shot calculation should produce. We choose n=6 for the one-shot calculation. At that point the channel temperature is 435 K and the thermal conductivity of GaN is calculated to be 1.65. The thermal resistance for the GaN layer is found to be 41.3 K/W. For the SiC layer we find it to be 100.6 K/W. The ratio of thermal resistances is then 0.41. From the transient simulation reported in (ref. 69), that ratio was 0.6. Using the total thermal resistance of 141.9 K/W, and the dissipated power of 0.625 W/finger, the calculated channel temperature is (lower value method)  $41.3 \times 0.625 + 100.6 \times 6 \times 1000$ 0.625 + 20 = 423 °C. Then for *n*=12 we have 800 °C. These are very high compared with the simulations. The GRC-1 method gives thermal resistances of 66.6 for GaN and 34 to 72 for SiC as n varies from 1 to 16. Figure 23 summarizes these calculations. The prediction of the channel temperature for the GRC-1 method is also shown as the line in figure 22. Both calculations do not correlate well with the simulated curve. However, we can get complete correlation with the GRC-1 method in the following way. Starting with the single finger case we obtain the footprint at the GaN/SiC interface to be  $8.35 \times 127 \,\mu\text{m}^2$ . Then with the data set obtained from their publications, we calculate  $R_{th}$  for the SiC as follows:

$2l_x = 8.35 \ \mu m$

$$2l_y = 127 \ \mu m$$

$2L_x = 590 \ \mu m$

$2L_y = 278 \ \mu m$

$W = 330 \ \mu m$

$\rho_s = 3.9/2.4 = 1.625$

$\gamma_e = 15.2$

$$\gamma_s = 0.47.$$

Figure 21.—Top and cross-sectional views of device simulated by Nuttinck et al. (ref. 19).

Figure 22.—Channel temperature of simulated device. The lower curve is derived from Nuttinck's simulation. The straight line is the GRC-1 prediction, while the single point (n = 6, T = 435) is the one-shot prediction.

We obtain the thermal resistance for SiC to be 26.2 °C/W. The temperature determined by the simulator was 78 °C, and subtracting the base plate value of 20 °C, yields a net drop across both the GaN and SiC layers to be 58 °C. The drop across the SiC is calculated to be  $26.2 \times 0.625 = 16.4$  °C. Therefore the drop across the GaN is 41.6 °C. This gives the thermal resistance across the GaN the value 66.56 °C/W, with corresponding thermal conductivity 1.8 W/(cm·K). This value is well within the range for GaN. Now assuming the change in temperature drop across the GaN is constant as the number of fingers increases (since the fingers are sufficiently separated to eliminate any cross-talk in the GaN). We obtain the following equation for the channel temperature:

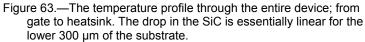

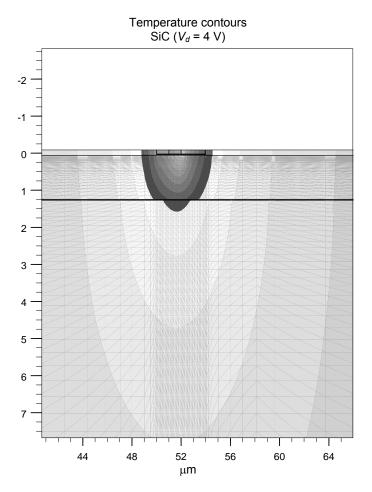

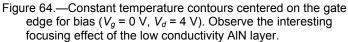

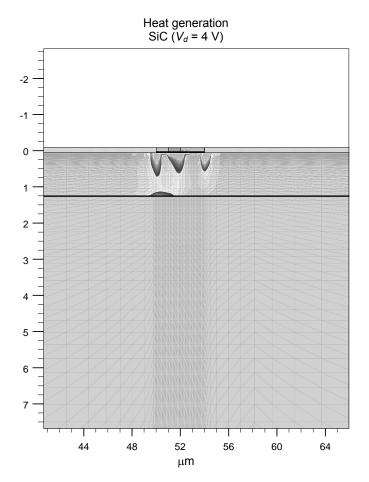

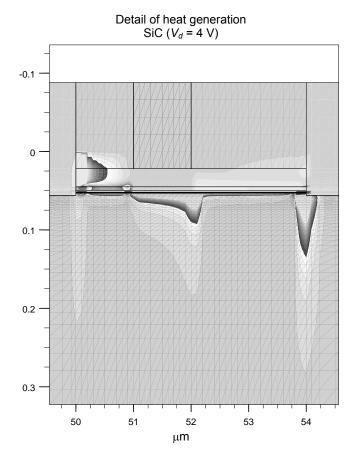

$$T_{ch} = R_{th}(n) (0.625)n + 20 + 41.6.$$