NASA/CP-2008-215309

# Proceedings of the Sixth NASA Langley Formal Methods Workshop

Edited by

Kristin Yvonne Rozier Langley Research Center, Hampton, Virginia Since its founding, NASA has been dedicated to the advancement of aeronautics and space science. The NASA Scientific and Technical Information (STI) Program Office plays a key part in helping NASA maintain this important role.

The NASA STI Program Office is operated by Langley Research Center, the lead center for NASA's scientific and technical information. The NASA STI Program Office provides access to the NASA STI Database, the largest collection of aeronautical and space science STI in the world. The Program Office is also NASA's institutional mechanism for disseminating the results of its research and development activities. These results are published by NASA in the NASA STI Report Series, which includes the following report types:

- TECHNICAL PUBLICATION. Reports of completed research or a major significant phase of research that present the results of NASA programs and include extensive data or theoretical analysis. Includes compilations of significant scientific and technical data and information deemed to be of continuing reference value. NASA counterpart of peerreviewed formal professional papers, but having less stringent limitations on manuscript length and extent of graphic presentations.

- TECHNICAL MEMORANDUM. Scientific and technical findings that are preliminary or of specialized interest, e.g., quick release reports, working papers, and bibliographies that contain minimal annotation. Does not contain extensive analysis.

- CONTRACTOR REPORT. Scientific and technical findings by NASA-sponsored contractors and grantees.

- CONFERENCE PUBLICATION. Collected papers from scientific and technical conferences, symposia, seminars, or other meetings sponsored or co-sponsored by NASA.

- SPECIAL PUBLICATION. Scientific, technical, or historical information from NASA programs, projects, and missions, often concerned with subjects having substantial public interest.

- TECHNICAL TRANSLATION. Englishlanguage translations of foreign scientific and technical material pertinent to NASA's mission.

Specialized services that complement the STI Program Office's diverse offerings include creating custom thesauri, building customized databases, organizing and publishing research results ... even providing videos.

For more information about the NASA STI Program Office, see the following:

- Access the NASA STI Program Home Page at *http://www.sti.nasa.gov*

- E-mail your question via the Internet to help@sti.nasa.gov

- Fax your question to the NASA STI Help Desk at (301) 621-0134

- Phone the NASA STI Help Desk at (301) 621-0390

- Write to: NASA STI Help Desk NASA Center for AeroSpace Information 7115 Standard Drive Hanover, MD 21076-1320

NASA/CP-2008-215309

# Proceedings of the Sixth NASA Langley Formal Methods Workshop

Edited by

Kristin Yvonne Rozier Langley Research Center, Hampton, Virginia

> Proceedings of a workshop sponsored by the National Aeronautics and Space Administration and held in Newport News, Virginia April 30-May 2, 2008

National Aeronautics and Space Administration

Langley Research Center Hampton, Virginia 23681-2199

May 2008

Trade names and trademarks are used in this report for identification only. Their usage does not constitute an official endorsement, either expressed or implied, by the National Aeronautics and Space Administration.

Available from:

NASA Center for AeroSpace Information (CASI) 7115 Standard Drive Hanover, MD 21076-1320 (301) 621-0390 National Technical Information Service (NTIS) 5285 Port Royal Road Springfield, VA 22161-2171 (703) 605-6000

### Preface

Today's verification techniques are hard-pressed to scale with the ever-increasing complexity of safety critical systems. Within the field of aeronautics alone, we find the need for verification of algorithms for separation assurance, air traffic control, auto-pilot, Unmanned Aerial Vehicles (UAVs), adaptive avionics, automated decision authority, and much more. Recent advances in formal methods have made verifying more of these problems realistic. Thus we need to continually re-assess what we can solve now and identify the next barriers to overcome. Only through an exchange of ideas between theoreticians and practitioners from academia to industry can we extend formal methods for the verification of ever more challenging problem domains.

The goal of this workshop on formal methods for verification is to examine formal verification techniques, their theory, application areas, current capabilities, and limitations. This format is designed to introduce researchers, graduate students, and partners in industry to those topics that are of fundamental interest and importance, to survey current research, and to discuss major unsolved problems and directions for future research.

This volume contains the extended abstracts of the talks presented at LFM 2008: The Sixth NASA Langley Formal Methods Workshop held on April 30 - May 2, 2008 in Newport News, Virginia, USA. The LFM Workshop series was incepted in 1990 as a local meeting centered around NASA Langley's formal methods projects. It was held sporadically in the years 1992, 1995, 1997, and 2000 and gradually expanded into an international venue for the presentation of a broad range of formal methods research topics. The topics of interest that were listed in the call for abstracts were: advances in formal verification techniques; formal models of distributed computing; planning and scheduling; automated air traffic management; fault tolerance; hybrid systems/hybrid automata; embedded systems; safety critical applications; safety cases; accident/safety analysis.

The committee decided to accept 24 submissions to be presented at the workshop and included in the proceedings. Each submitted abstract was reviewed and voted on by the entire programme committee with ties broken by the vote of the PC chair. Following the programme committee decision on each submission, one member of the PC was elected to summarize the thoughts of the entire programme committee and send this composite review to the authors. The LFM 2008 programme also includes five absolutely stellar invited talks, spanning the range of topics addressed by LFM. Gerard J. Holzmann, Amy R. Pritchett, John Rushby, Moshe Y. Vardi delivered the four keynote talks. I also invited Ricky W. Butler, the leader and founder of the Langley Formal Methods research group, to give a talk on FM research at LaRC. LFM 2008 was well-attended by a range of participants from academia, industry, and government; there were a total of 74 registered participants.

LFM 2008 is proudly sponsored by the NASA Integrated Vehicle Health Management (IVHM) and Airspace Systems Programs and by the National Institute of Aerospace (NIA). In particular, I would like to thank Brian T. Baxley, Raymond S. Calloway, Eric G. Cooper, and Michael C. Lightfoot for their advocation and financial support. I would like to thank all of the members of the programme committee for their help in composing a strong program for LFM 2008, for serving as session chairs, and for the other support and helpful suggestions they lent to ensure the workshop ran smoothly. I am grateful to Deborah L. Ford and Marie W. Hamann for procurement

services and to Charles A. "Pete" Polen for legal consultation and for helping me navigate NASA's legal framework to accomplish everything I wanted for this workshop. I would also like to thank Raymond V. Meyer for designing our logo, posters, and other artwork associated with LFM, and Lisa F. Peckham and Eric W. D. Rozier for invaluable help and advice along the way.

April 2008

Kristin Yvonne Rozier

# **Conference Organization**

#### General Chair

Kristin Yvonne Rozier

### Programme Committee

Ricky W. Butler Eric G. Cooper Benedetto L. Di Vito Jeffrey M. Maddalon Mahyar R. Malekpour Paul S. Miner César A. Muñoz Kristin Y. Rozier Radu L. Siminiceanu

# Table of Contents

# Session 1. Logic Into Practice

| NASA Langley's Formal Methods Research in Support of the Next<br>Generation Air Transportation System (invited talk)<br>Ricky W. Butler and César A. Muñoz | 3  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| From Philosophical to Industrial Logics (invited talk)<br>Moshe Y. Vardi                                                                                   | 6  |

| From Informal Safety-Critical Requirements to Property-Driven Formal<br>Validation                                                                         | 7  |

| Verification and Planning Based on Coinductive Logic Programming<br>Ajay Bansal, Richard Min, Luke Simon, Ajay Mallya, Gopal Gupta                         | 9  |

| Assessing Requirements Quality Through Requirements Coverage<br>Ajitha Rajan, Mats Heimdahl, Kurt Woodham                                                  | 12 |

| Session 2. Verification Under Constraints                                                                                                                  |    |

| Monitoring IVHM Systems Using a Monitor-Oriented Programming<br>Framework                                                                                  | 17 |

| Self-* Programming Run-Time Parallel Control Search for Reflection Box<br>Olga Brukman, Shlomi Dolev                                                       | 20 |

| Getting Somewhat Formal with CSP and C++<br>William B. Gardner                                                                                             | 23 |

| Challenges and Demands on Automated Software Revision<br>Borzoo Bonakdarpour, Sandeep S. Kulkarni                                                          | 26 |

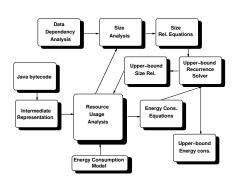

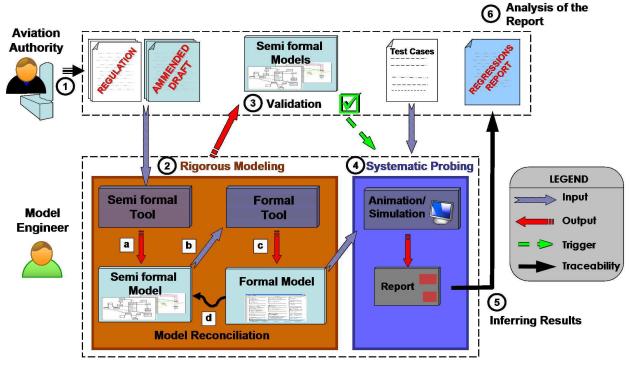

| Safe Upper-bounds Inference of Energy Consumption for Java Bytecode<br>Applications<br>Jorge Navas, Mario Méndez-Lojo, Manuel V. Hermenegildo              | 29 |

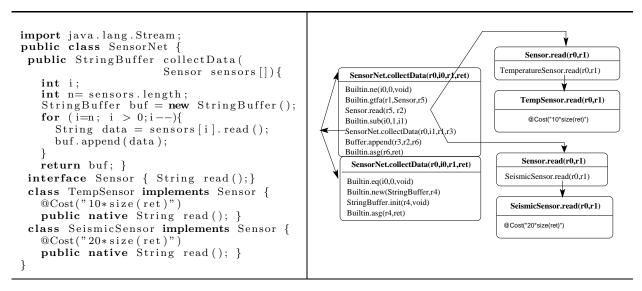

| Toward a Formal Evaluation of Refactorings<br>John Paul, Nadya Kuzmina, Ruben Gamboa, James Caldwell                                                       | 33 |

| The Nation's Needs in Aviation Formal Methods (invited talk)<br>Amy R. Pritchett                                                                           | 36 |

| Session 3. Certification and Practical Formal Methods                                                                            |    |

|----------------------------------------------------------------------------------------------------------------------------------|----|

| Formal Methods and Certification (invited talk)<br>John Rushby                                                                   | 39 |

| Certifying Auto-Generated Flight Code<br>Ewen Denney                                                                             | 40 |

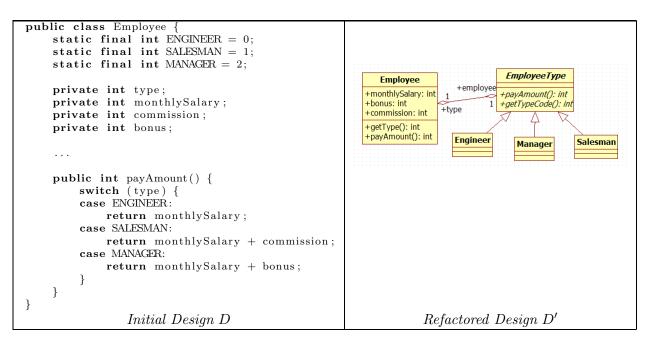

| Aeronautical Regulations Should Be Rigorously Developed Too!<br>Eduardo Rafael López Ruiz, Yves Ledru, Michel Lemoine            | 41 |

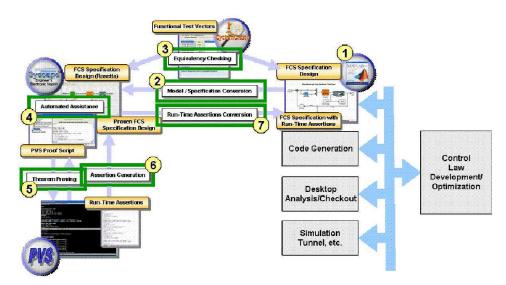

| Use of Intelligent Assistants in Practical Theorem Proving<br>David L. Barton                                                    | 44 |

| Combining Predicate and Numeric Abstraction for Software Model<br>Checking<br>Arie Gurfinkel, Sagar Chaki                        | 47 |

| Session 4. Component-Based Verification                                                                                          |    |

| Reuse versus Reinvention: How Will Formal Methods Deal with<br>Composable Systems?                                               | 53 |

| Automating System Assembly of Aerospace Systems<br>Panagiotis Manolios                                                           | 55 |

| Formal Verification of Gate-Level Computer Systems<br>Sergey Tverdyshev, Andrey Shadrin                                          | 56 |

| Proving Correctness for Pointer Programs in a Verifying Compiler<br>Gregory Kulczycki, Amrinder Singh                            | 59 |

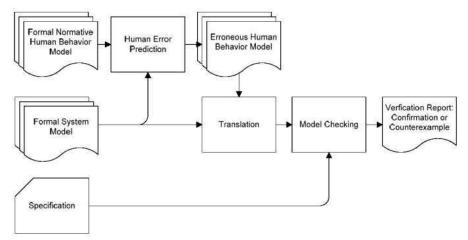

| Formal Modeling of Erroneous Human Behavior and its Implications<br>for Model Checking<br>Matthew L. Bolton, Ellen J. Bass       | 62 |

| A Framework for Stability Analysis of Control Systems Software at the<br>Source Code Level<br><i>Fernando Alegre, Eric Feron</i> | 65 |

| Mise en Scene : A Scenario-Based Medium Supporting Formal Software<br>Development                                                | 66 |

| Session 5. The Future of Tools for Verification                                                                                  |    |

| On Limits (invited talk)<br>Gerard J. Holzmann                                                                                   | 69 |

| An Update on Yices<br>Bruno Dutertre                                                                | 70 |

|-----------------------------------------------------------------------------------------------------|----|

| Distributing Formal Verification: The Evidential Tool Bus<br>Florent Kirchner                       | 71 |

| Model Checking for the Practical Verificationist: A User's Perspective<br>on SAL<br><i>Lee Pike</i> | 74 |

| An Overview of Starfish: A Table-Centric Tool for Interactive Synthesis<br>$Alex\ Tsow$             | 76 |

Session 1: Logic Into Practice

Ricky W. Butler et al.: NASA Langley's Formal Methods Research in Support of the Next Generation Air Transportation System, Proceedings of The Sixth NASA Langley Formal Methods Workshop, p.3–5

# NASA Langley's Formal Methods Research in Support of the Next Generation Air Transportation System

Ricky W. Butler<sup>1</sup>, César A. Muñoz<sup>2</sup>

<sup>1</sup> NASA Langley Research Center, Hampton, Virginia 23681, USA

<sup>2</sup> National Institute of Aerospace, Hampton, Virginia 23666, USA

R.W.Butler@nasa.gov, munoz@nianet.org

http://www.shemesh.larc.nasa.gov/fm

#### Extended Abstract

This talk will provide a brief introduction to the formal methods developed at NASA Langley and the National Institute for Aerospace (NIA) for air traffic management applications. NASA Langley's formal methods research supports the Interagency Joint Planning and Development Office (JPDO) effort to define and develop the 2025 Next Generation Air Transportation System (NGATS). The JPDO was created by the passage of the Vision 100 Century of Aviation Reauthorization Act in Dec 2003. The NGATS vision calls for a major transformation of the nation's air transportation system that will enable growth to 3 times the traffic of the current system. The transformation will require an unprecedented level of safety-critical automation used in complex procedural operations based on 4-dimensional (4D) trajectories that enable dynamic reconfiguration of airspace scalable to geographic and temporal demand.

The goal of our formal methods research is to provide verification methods that can be used to insure the safety of the NGATS system. Our work has focused on the safety assessment of concepts of operation and fundamental algorithms for conflict detection and resolution (CD&R) and selfspacing in the terminal area. Formal analysis of a concept of operations is a novel area of application of formal methods. Here one must establish that a system concept involving aircraft, pilots, and ground resources is safe. The formal analysis of algorithms is a more traditional endeavor. However, the formal analysis of ATM algorithms involves reasoning about the interaction of algorithmic logic and aircraft trajectories defined over an airspace. These trajectories are described using 2D and 3D vectors and are often constrained by trigonometric relations. Thus, in many cases it has been necessary to unload the full power of an advanced theorem prover. The verification challenge is to establish that the safety-critical algorithms produce valid solutions that are guaranteed to maintain separation under all possible scenarios. Current research has assumed perfect knowledge of the location of other aircraft in the vicinity so absolute guarantees are possible, but increasingly we are relaxing the assumptions to allow incomplete, inaccurate, and/or faulty information from communication sources.

The following is a list of the projects that the Langley/NIA formal methods team have been involved with:

- Airborne Information for LateralSpacing (AILS)

- CD3D and KB3D Conflict Detection and Resolution algorithms

- Runway Incursion Prevention System (RIPS)

Ricky W. Butler et al.: NASA Langley's Formal Methods Research in Support of the Next Generation Air Transportation System

- Small Aircraft Transportation System (SATS)

- Enhanced Oceanic Operations (EOO)

- Loss of Separation (LoS) Recovery Algorithms

In this talk we will look at three of these: SATS, KB3D, and LoS.

The goal of the SATS program was to significantly increase the capacity of regional airports. One of the most revolutionary aspects of the SATS approach is the use of a software system to sequence aircraft into the SATS airspace with no air traffic controller present. Obviously, there are serious safety issues associated with these software systems and their underlying key algorithms. A formal finite-state machine model of the SATS operational procedures using 24 transition rules was developed. This enabled an exhaustive analysis of the entire state space of the concept of operations and the proof of six safety properties. Nine issues were identified during the formal analysis. Two issues required changes to the rules of the ConOps, five issues were due to implicit or explicit omissions, and two were clarifications. All recommendations from formal methods team were adopted by SATS Conops Team.

The KB3D project developed and formally verified a new algorithm for conflict detection and resolution. The KB3D algorithm is a generalization of Karl Bilimoria's CD&R algorithm to 3 dimensions. The algorithm (KB3D) produces multiple solutions that only require a change in only one state parameter (i.e. heading, ground speed, or vertical speed). The algorithm has been formally verified to produce correct solutions when either one or both aircraft use the algorithm. KB3D is guaranteed to generate at least one valid solution for two aircraft with arbitrary trajectories. Usually the algorithm generates six different solutions. For two aircraft executing the CD&R algorithm, a proof has been completed that shows that the algorithm is implicitly coordinated. That is the algorithm produces solutions that send the two aircraft in opposite directions without any explicit communication between the aircraft. For the perfectly symmetric situation, KB3D uses a symmetry breaking mechanism. All of the proofs were accomplished using the Prototype Verification System (PVS) developed by SRI International.

Recent work at Langlev has been developing a formal framework for the mathematical analysis of conflict resolution algorithms that recover from loss of separation. This work is motivated by some recent TMX simulation studies of the KB3D algorithm. The TMX studies explored the capabilities of KB3D to deal with multiple aircraft in complex traffic situations. The traffic density was approximately 3 times today's traffic and was generated by extrapolation from existing traffic patterns. There were almost no situations where a loss of separation occurred. But, it became clear to us that the KB3D algorithm should be generalized to recover from those situations. In this work we have developed a rigorous definition of correctness for vertical and horizontal maneuvers and simple criteria for loss of separation recovery algorithms that are sufficient to guarantee correctness. We have sought to make the criteria simple so that algorithms can be checked against the criteria in a straight-forward way. The criteria only uses information available to the local aircraft, but are powerful enough to prove distributed system properties. In particular, we propose rigorous definitions of horizontal and vertical maneuver correctness that yield horizontal and vertical separation, respectively, in a bounded amount of time. We also provide sufficient conditions for independent correctness, e.g., separation under the assumption that only one aircraft maneuvers, and for implicitly coordinated correctness, e.g., separation under the assumption that both aircraft maneuver. An important benefit of this approach is that different aircraft can execute different algorithms and implicit coordination will still be achieved, as long as they all meet the explicit Ricky W. Butler et al.: NASA Langley's Formal Methods Research in Support of the Next Generation Air Transportation System

criteria of the framework. The mathematical framework has been formalized and mechanically verified using the Prototype Verification System (PVS) developed by SRI International.

#### References

- [1] SATS project publications, http://research.nianet.org/fm-at-nia/SATS/

- [2] KB3D project publications, http://research.nianet.org/fm-at-nia/KB3D/

- [3] FM publications, http://shemesh.larc.nasa.gov/fm/fm-main-research.html

Moshe Y. Vardi: From Philosophical to Industrial Logics, Proceedings of The Sixth NASA Langley Formal Methods Workshop,  ${\rm p.6-6}$

### From Philosophical to Industrial Logics

Moshe Y. Vardi

Rice University, Houston, Texas 77005, USA vardi@cs.rice.edu

#### Invited Talk

One of the surprising developments in the area of program verification is how several ideas introduced by logicians in the first part of the 20th century ended up yielding at the start of the 21st century industry-standard property-specification languages called PSL and SVA. This development was enabled by the equally unlikely transformation of the mathematical machinery of automata on infinite words, introduced in the early 1960s for second-order arithmetics, into effective algorithms for industrial model-checking tools. This talk attempts to trace the tangled threads of this development.

Alessandro Cimatti et al.: From Informal Safety-Critical Requirements to Property-Driven Formal Validation, Proceedings of The Sixth NASA Langley Formal Methods Workshop, p.7–8

# From Informal Safety-Critical Requirements to Property-Driven Formal Validation

Alessandro Cimatti, Marco Roveri, Angelo Susi, Stefano Tonetta

Fondazione Bruno Kessler - Istituto per la Ricerca Scientifica e Tecnologica, Trento, Italy {cimatti,roveri,susi,tonettas}@fbk.eu

#### Extended Abstract

Most of the efforts in formal methods have historically been devoted to comparing a design against a set of requirements. The validation of the requirements themselves, however, has often been disregarded, and it can be considered a largely open problem, which poses several challenges.

The first challenge is given by the fact that requirements are often written in natural language, and may thus contain a high degree of ambiguity. Despite the progresses in Natural Language Processing techniques, the task of understanding a set of requirements cannot be automatized, and must be carried out by domain experts, who are typically not familiar with formal languages. Furthermore, in order to retain a direct connection with the informal requirements, the formalization cannot follow standard model-based approaches.

The second challenge lies in the formal validation of requirements. On one hand, it is not even clear which are the correctness criteria or the high-level properties that the requirements must fulfill. On the other hand, the expressivity of the language used in the formalization may go beyond the theoretical and/or practical capacity of state-of-the-art formal verification.

In order to solve these issues, we propose a new methodology that comprises of a chain of steps, each supported by a specific tool. The main steps are the following. First, the informal requirements are split into basic fragments, which are classified into categories, and dependency and generalization relationships among them are identified. Second, the fragments are modeled using a visual language such as UML. The UML diagrams are both syntactically restricted (in order to guarantee a formal semantics), and enriched with a highly controlled natural language (to allow for modeling static and temporal constraints). Third, an automatic formal analysis phase iterates over the modeled requirements, by combining several, complementary techniques: checking consistency; verifying whether the requirements entail some desirable properties; verify whether the requirements are consistent with selected scenarios; diagnosing inconsistencies by identifying inconsistent cores; identifying vacuous requirements; constructing multiple explanations by enabling the fault-tree analysis related to particular fault models; verifying whether the specification is realizable.

The methodology aims at increasing the confidence in the correctness of the requirements. On one hand, with the adoption of a property-based approach, every requirement is associated with a formal counterpart; on the other hand, a semi-formal language is exploited to narrow the gap with the natural language. The verification techniques are optimized in order to deal with large sets of requirements. The granularity of the formalization allows to focus on different types and levels of abstraction based on the hierarchy and on the modularity of the requirements; furthermore, it makes it possible to perform what-if analysis, based on hypothetical changes to the specification; finally, the diagnostic information helps in localizing the formalization mistakes and the corresponding specification ambiguities.

This methodology has been proposed in response to the call to tender ERA/2007/ERTMS/OP/01 "Feasibility study for the formal specification of ETCS functions". The European Train Control System (ETCS) is a huge set of requirements that defines a control system to guarantee the inter-operability between the European rail system and trains. Due to its complexity, ETCS presents the mentioned issues at a high level of magnitude.

Ajay Bansal et al.: Verification and Planning Based on Coinductive Logic Programming, Proceedings of The Sixth NASA Langley Formal Methods Workshop, p.9–11

# Verification and Planning Based on Coinductive Logic Programming

Ajay Bansal, Richard Min, Luke Simon, Ajay Mallya, Gopal Gupta

Department of Computer Science, University of Texas at Dallas, USA Contact author: Gopal Gupta, e-mail: gupta@utdallas.edu

#### **Extended Abstract**

Coinduction is a powerful technique for reasoning about unfounded sets, unbounded structures, infinite automata, and interactive computations [6]. Where induction corresponds to least fixed points semantics, coinduction corresponds to greatest fixed point semantics. Recently coinduction has been incorporated into logic programming and an elegant operational semantics developed for it [11, 12]. This operational semantics is the greatest fix point counterpart of SLD resolution (SLD resolution imparts operational semantics to least fix point based computations) and is termed co-SLD resolution. In co-SLD resolution, a predicate goal  $p(\bar{t})$  succeeds if it unifies with one of its ancestor calls. In addition, rational infinite terms are allowed as arguments of predicates. Infinite terms are represented as solutions to unification equations and the occurs check is omitted during the unification process: for example, X = [1 | X] represents the binding of X to an infinite list of 1's. Thus, in co-SLD resolution, given a single clause

p([1 | X]) := p(X).

the query ?- p(A) will succeed with the (infinite) answer:

A = [1 | A]

Coinductive Logic Programming (Co-LP) and Co-SLD resolution can be used to elegantly perform *model checking* and *planning*. A combined SLD and Co-SLD resolution based LP system forms the common basis for planning, scheduling, verification, model checking, and constraint solving [9, 4]. This is achieved by amalgamating SLD resolution, co-SLD resolution, and constraint logic programming [13] in a single logic programming system. Given that parallelism in logic programs can be implicitly exploited [8], complex, compute-intensive applications (planning, scheduling, model checking, etc.) can be executed in parallel on multi-core machines. Parallel execution can result in speed-ups as well as in larger instances of the problems being solved.

In the remainder we elaborate on (i) how planning can be elegantly and efficiently performed under real-time constraints, (ii) how real-time systems can be elegantly and efficiently modelchecked, as well as (iii) how hybrid systems can be verified in a combined system with both co-SLD and SLD resolution. Implementations of co-SLD resolution as well as preliminary implementations of the planning and verification applications have been developed [4].

**Co-LP and Model Checking:** The vast majority of properties that are to be verified can be classified into *safety* properties and *liveness* properties. It is well known within model checking that safety properties can be verified by reachability analysis, i.e., if a counter-example to the property exists, it can be finitely determined by enumerating all the reachable states of the Kripke structure. Checking for reachability amounts to finding the least fixed-point, which is relatively straightforward to compute (for example, using *tabled logic programming* [2]). Verification of

liveness properties is however problematic because counterexamples to liveness properties take the form of infinite traces, which are semantically expressed as greatest fixed-points. Co-LP can be directly used to verify liveness properties by constructing counterexamples using greatest fixed-point temporal logic formulae. Intuitively, a state S is not live if there is an infinite loop (cycle) intervening between the current state and S. In a coinductive formulation, liveness also reduces to the reachability problem. Liveness counterexamples are elegantly found by (coinductively) enumerating all possible states that can be "reached" via infinite loops.

**Co-LP and Planning:** Coinduction can also be used to develop methods for goal-directed execution of non-monotonic logics, traditionally used for developing planners. In particular, top-down, goal-directed execution methods can be designed for answer set programs, a popular formalism for non-monotonic reasoning [1, 5]. Developing such a goal-directed reasoner has been an open problem for some time. It turns out that one can use co-SLD resolution to solve this problem [3]. In planning, a domain description D is given along with a set of observations about the initial state O and a collection of fluent literals  $G = \{g_1, \ldots, g_l\}$ , which is referred to as a goal. The problem is to find a sequence of actions  $a_1, \ldots, a_n$  such that  $\forall i, 1 \leq i \leq l, D$  entails  $g_i$  from initial state O, after actions  $a_1, \ldots, a_n$ . The sequence of actions  $a_1, \ldots, a_n$  is called a plan for goal G w.r.t. (D,O) [5]. Action Description Languages have been designed to encode the domain descriptions [1]. These Action Description Languages are implemented through rules of non-monotonic logic, in particular, answer set programming; these languages can be elegantly and efficiently implemented using co-LP and used for solving planning problems [4].

**Timed Planning and Verification:** Within logic programming, continuous time and timedeadlines can be modeled as constraints over reals [7]. Together with co-induction, this ability can be used to perform verification of timed-systems as well as perform planning under time constraints. Elsewhere we illustrate the verification of timed-systems by considering a formulation of the dining philosophers problem with stop-watches and proving that it is deadlock free (safety) and starvation free (liveness) [4]. We also illustrate the solution of time constrained planning problems using the soccer-playing planning domain extended with real-time constraints [4]. Note that a combination of generalized constraints and coinduction leads to a general framework for verifying hybrid systems as well as performing *hybrid planning*, i.e., planning under discrete and continous constraints.

#### References

- M. Balduccini, M. Gelfond, et al. An A-Prolog Decision Support System for the Space Shuttle-I. In Lecture Notes in Computer Science: Proceedings of Practical Aspects of Declarative Languages '01, Vol. 1990, pp 169-183, 2001.

- [2] Y.S. Ramakrishna, C.R. Ramakrishnan, I.V. Ramakrishnan, S.A. Smolka, T. Swift, and D.S. Warren. Efficient Model Checking Using Tabled Resolution. Proc. CAV'97, Haifa, Israel, Lecture Notes in Computer Science, Vol. 1243.

- [3] A. Bansal, R. Min, G. Gupta. Goal-directed Execution of Answer Set Programs. UTD Technical Report. Feb. 2008.

- [4] A. Bansal. Towards next generation logic programming systems. Ph.D. thesis. University of Texas at Dallas. Dec. 2007.

- [5] C. Baral, Knowledge Representation, Reasoning and Declarative Problem Solving, Cambridge University Press, 2003.

- [6] J. Barwise, L. Moss. Vicious Circles: On the Mathematics of Non-Wellfounded Phenomena. CSLI Publications, 1996.

- [7] G. Gupta, E. Pontelli. Constraint-based Specification and Verification of Real-time Systems. In Proc. IEEE Real-time Symposium (RTSS'97). pp. 230-239.

- [8] G. Gupta et al. Parallel Execution of Prolog Programs: A Survey. In ACM Transactions on Programming Languages and Systems, Vol 23, No. 4, pp. 472-602.

- [9] G. Gupta, A. Bansal, R. Min, L. Simon, A. Mallya. Coinductive Logic Programming and Its Applications. Invited Tutorial. Proc. Int'l Conf. on Logic Programming (ICLP'07). pp. 27-44.

- [10] L. Simon, A. Bansal, A. Mallya, and G. Gupta. Co-Logic Programming. Proc. Int'l Conf. on Automata, Languages and Programming (ICALP'07), pp. 472-483.

- [11] L. Simon, A. Mallya, A. Bansal, and G. Gupta. Coinductive Logic Programming. Int'l Conf. on Logic Prog. (ICLP'06). Springer Verlag LNCS 4079. pp. 330-344.

- [12] Luke Simon. Extending Logic Programming with Coinduction. University of Texas at Dallas. Ph.D. Thesis. 2006.

- [13] K. Marriott and P. Stuckey. Prog. with Constraints: An Introduction. MIT Press, 1998.

Ajitha Rajan et al.: Assessing Requirements Quality Through Requirements Coverage, Proceedings of The Sixth NASA Langley Formal Methods Workshop, p.12–14

# Assessing Requirements Quality Through Requirements Coverage<sup>\*</sup>

Ajitha Rajan<sup>1</sup>, Mats Heimdahl<sup>1</sup>, Kurt Woodham<sup>2</sup>

<sup>1</sup> University of Minnesota <sup>2</sup> L-3 Communications

arajan@cs.umn.edu, heimdahl@cs.umn.edu, kurt.woodham@l-3com.com

#### **Extended Abstract**

In model-based development, the development effort is centered around a formal description of the proposed software system—the "model". This model is derived from some high-level requirements describing the expected behavior of the software. For validation and verification purposes, this model can then be subjected to various types of analysis, for example, completeness and consistency analysis [6], model checking [3], theorem proving [1], and test-case generation [4, 7]. This development paradigm is making rapid inroads in certain industries, e.g., automotive, avionics, space applications, and medical technology. This shift towards model-based development naturally leads to changes in the verification and validation (V&V) process. The model validation problem determining that the model accurately captures the customers' high-level requirements—has received little attention and the sufficiency of the validation activities has been largely determined through ad-hoc methods. Since the model serves as the central artifact, its correctness with respect to the users' needs is absolutely crucial. In our investigation, we attempt to answer the following two questions with respect to validation (1) Are the requirements sufficiently defined for the system? and (2) How well does the model implement the behaviors specified by the requirements? The second question can be addressed using formal verification. Nevertheless, the size and complexity of many industrial systems make formal verification infeasible even if we have a formal model and formalized requirements. Thus, presently, there is no objective way of answering these two questions. To this end, we propose an approach based on testing that—when given a set of formal requirements—explores the relationship between requirements-based structural test-adequacy coverage and *model-based* structural test-adequacy coverage.

The proposed technique uses requirements coverage metrics defined in [9] on formal high-level software requirements and existing model coverage metrics such as the Modified Condition and Decision Coverage (MC/DC) used when testing highly critical software in the avionics industry [8]. Our work is related to Chockler et al. [2], but we base our work on traditional testing techniques as opposed to verification techniques.

To objectively assess whether the high-level requirements have been sufficiently defined for the system, we produce a set of test cases that achieve a certain level of structural coverage of the high-level requirements, and then measure coverage achieved by the test suite over the model. If a test suite provides high requirements coverage but yields poor coverage of a model, it may be

$<sup>\</sup>star$  This work has been partially supported by NASA Ames Research Center Cooperative Agreement NNA06CB21A, NASA IV&V Facility Contract NNG-05CB16C, and the L-3 Titan Group.

due to one or more of the following: (a) there are missing or implicit requirements, (b) there is behavior in the model that is not derived from the requirements, or (c) the set of tests derived from the requirements was inadequate. On the other hand, to objectively assess how well the model implements the behaviors specified in the requirements, we generate a set of test cases that achieve structural coverage of the model, and then measure requirements coverage achieved. Poor requirements coverage is an indicator of either (a) the model does not adequately implement the behaviors specified in the requirements, or (b) the model is correct and the requirements are poorly written.

To illustrate the technique, we use a rigorous requirements coverage metric Unique First Cause (UFC) coverage defined in over requirements formalized as Linear Temporal Logic (LTL) properties [9]. We use the Modified Condition/Decision Coverage (MC/DC) criterion [5] to measure structural coverage over the model. In a preliminary study, we use five industrial case examples from the civil avionics domain. For each of these systems, we perform two kinds of assessment—(1) generate test suites to provide UFC coverage over the requirements and measure MC/DC achieved over the model, and (2) generate test suites to provide MC/DC over the model and measure UFC coverage achieved over the formal requirements. We analyze the relationship between requirements as well as the models.

On three of the five case examples, test suites generated to provide UFC coverage of the requirements provided reasonably good MC/DC of the models. This indicates that for these case examples, the requirements are well defined. Nevertheless, the test suites provided 10%-20% less than achievable MC/DC over the models. This is somewhat expected since the requirements (representing DO-178B high-level requirements) are typically less detailed than the model (representing DO-178B low-level requirements). Another reason may be that the UFC metric used for requirements coverage is not sufficiently rigorous and we thus have an inadequate set of requirements-based tests. On the remaining two case examples, test suites providing requirements UFC coverage gave very poor MC/DC on the model. Closer investigation revealed that on one example, there were many missing requirements. In the final case example, the requirements were good, however, their structure was so that the complexity of conditions in the requirements were hidden. For such requirements, the UFC metric that we use is not effective since the structure of the formalized requirements effectively "cheated" the UFC metric. One solution to this would be to restructure the requirements to reveal condition complexity. Another possible solution is to use a requirements coverage metric that is not as sensitive to the structure of the requirements. We hope to investigate this issue further in our future work.

We found that on all but one of the industrial systems, test suites providing MC/DC over the model achieved close to achievable requirements UFC coverage. This implies that the model exercises almost all the behaviors specified by the requirements for these systems. Nevertheless, on one model the MC/DC test suites did poorly, only achieving 30% of the achievable requirements coverage. This may either be because the model does not implement all the behaviors or the MC/DC metric is not rigorous enough. At this time we have not been able to determine the cause more closely, but we hope to do so in our future work.

To summarize, we found that analyzing the relationship between requirements coverage and model coverage provides a promising means of assessing requirements quality. Nevertheless, the effectiveness of this approach is highly dependent on the rigor and effectiveness of the coverage metrics used, and awareness of the pitfalls of structural coverage metrics is essential. For instance, in this experiment we found that the UFC metric was surprisingly sensitive to the structure of the requirements, and one has to ensure that the requirements structure does not hide the complexity of conditions for the metric to be effective.

#### References

- S. Bensalem, P. Caspi, C. Parent-Vigouroux, and C. Dumas. A methodology for proving control systems with Lustre and PVS. In Proceedings of the Seventh Working Conference on Dependable Computing for Critical Applications (DCCA 7), pages 89–107, San Jose, CA, January 1999. IEEE Computer Society.

- [2] H. Chockler, O. Kupferman, and M. Y. Vardi. Coverage metrics for formal verification. In 12th Advanced Research Working Conference on Correct Hardware Design and Verification Methods, volume 2860 of Lecture Notes in Computer Science, pages 111–125. Springer-Verlag, October 2003.

- [3] Edmund M. Clarke, Orna Grumberg, and Doron Peled. Model Checking. MIT Press, 1999.

- [4] Angelo Gargantini and Constance Heitmeyer. Using model checking to generate tests from requirements specifications. Software Engineering Notes, 24(6):146–162, November 1999.

- [5] K.J. Hayhurst, D.S. Veerhusen, and L.K. Rierson. A practical tutorial on modified condition/decision coverage. Technical Report TM-2001-210876, NASA, 2001.

- [6] Mats P. E. Heimdahl and Nancy G. Leveson. Completeness and consistency in hierarchical state-base requirements. *IEEE Transactions on Software Engineering*, 22(6):363–377, June 1996.

- [7] A. Jefferson Offutt, Yiwie Xiong, and Shaoying Liu. Criteria for generating specification-based tests. In Proceedings of the Fifth IEEE International Conference on Engineering of Complex Computer Systems (ICECCS '99), October 1999.

- [8] RTCA. DO-178B: Software Considerations In Airborne Systems and Equipment Certification. RTCA, 1992.

- [9] Michael Whalen, Ajitha Rajan, Mats Heimdahl, and Steven Miller. Coverage metrics for requirementsbased testing. In *Proceedings of International Symposium on Software Testing and Analysis*, July 2006.

# Session 2: Verification Under Constraints

Sudipto Ghoshal et al.: Monitoring IVHM Systems Using a Monitor-Oriented Programming Framework, Proceedings of The Sixth NASA Langley Formal Methods Workshop, p.17–19

# Monitoring IVHM Systems Using a Monitor-Oriented Programming Framework

Sudipto Ghoshal<sup>1</sup>, Solaiappan Manimaran<sup>1</sup>, Grigore Rosu<sup>2</sup>, Traian Florin Serbanuta<sup>2</sup>, Gheorghe Stefanescu<sup>2</sup>

Qualtech Systems Inc., Wethersfield, CT, USA

<sup>2</sup> Department of Computer Science, University of Illinois at Urbana-Champaign, USA

{sudipto,mani}@teamqsi.com, {grosu,tserban2,stefanes}@cs.uiuc.edu

#### Abstract

We describe a runtime verification approach to increase the safety of IVHM systems by an integration of TEAMS models and MOP (Monitor-Oriented Programming). The TEAMS model is used to automatically extract relevant runtime information from the controlled system by means of events. This information is passed on-line to the MOP engine, allowing to verify complex temporal properties and to discover running patterns which are of interest in detecting and preventing faulty behaviors.

#### 1. Monitor-Oriented Programming (MOP)

MOP [2, 1] has its roots in a runtime verification system, PathExplorer (PAX) [6, 5], developed jointly with former NASA colleagues. PAX has found mission critical errors in NASA software. In a recent OOPSLA'07 paper [2], it was shown that the MOP framework can monitor large programs against complex parametric temporal specifications at a typically unnoticeable runtime overhead.

Many properties can be monitored in parallel in MOP. The execution trace against which the various properties are checked is extracted via automatic code instrumentation from the running program as a sequence of events – state snapshots. Events produce sufficient information about the concrete program state in order for the monitors to correctly check their properties.

In MOP, the runtime monitoring of each property consists of two orthogonal mechanisms: observation and verification. The observation mechanism extracts property-relevant and filtered system states at designated points, e.g., when property-specific events happen. The verification mechanism checks the obtained abstract trace against the property and triggers desired actions in case of violations or validations. Observation and verification are therefore independent: the algorithm used within the monitor does not affect how the execution is observed, and vice versa. MOP is a highly configurable and extensible runtime verification framework. Depending upon configuration, the monitors can be separate programs reading events from a log file, from a socket or from a buffer, or can be in-lined within the program at the event observation points.

Properties can be specified in MOP by means of *logic plugins* which essentially encapsulate and standardize monitor synthesis algorithms for various formalisms of interest. Here are several logic plugins currently provided by MOP:

— Design by Contract: A JAVA logic plugin for JASS has been implemented in MOP. JASS supports the following types of assertions: method pre-conditions and post-conditions, loop variants and invariants, and class invariants.

— Temporal Logics: Temporal logics proved to be indispensable expressive formalisms in the field of formal specification and verification of systems. Many practical safety properties can be naturally expressed in temporal logics, making them desirable specification formalisms in the MOP framework. Login plugins for both future and past time temporal logics are available.

— Extended Regular Expressions: Software engineers and programmers understand easily regular patterns, as shown by the interest in and the success of scripting languages like PERL. We believe that regular expressions provide an elegant and powerful specification language also for monitoring requirements, because an execution trace of a program is a string of states. Extended regular expressions (ERE) add complementation to regular expressions, allowing one to specify patterns that must not occur. An ERE logic plugin is available in MOP.

#### 2. TEAMS Models

TEAMS [4] is a model-based diagnosis system. The TEAMS model of a system is a dependency model capturing relationships between failure modes of the system and their observable effects.

QSI's TEAMS Tool Set [4] consists of four software applications: TEAMS Designer, TEAMS-RT, TEAMATE and TEAMS-RDS, using a diagnostic data knowledge base called TEAMS-KB. The model is created in TEAMS Designer, or imported into TEAMS Designer from other data capture environments, and then analyzed and converted into run-time versions for export to the run-time reasoners TEAMATE and TEAMS-RT. The TEAMS Designer application provides a user-friendly graphical environment for developing dependency models of systems while allowing the specification of several additional practical aspects about the system that are required by the run-time inference engines to provide efficient diagnosis. It does so by allowing the modeler to specify cause-effect dependencies using a hierarchical, multi-layered, directed graph representation of the system. In this representation, the system's physical elements are represented as module nodes; the physical locations, where the measurements of the system's performance or other attributes are made are represented as test-point nodes; and the dependency relationships are represented as directed links.

Once a TEAMS model specification is complete, a reachability analysis can be performed in TEAMS to internally generate the dependency matrix model of the system subject to analysis constraints specified by the user. When the dependency-matrix model is available, diagnosis becomes the process of using the dependency relationships and the observed failures or anomalies to infer their possible causes. The TEAMS-RT inference engine processes failure events (exceedances, built-in test failures, performance anomalies, etc.), as they become available. It uses the data to infer the status of the root causes (the identification of one or more component faults). Thus, TEAMS-RT is appropriate for processing on-board data that is either received in real time or downloaded post-mission/operation. The TEAMATE diagnosis reasoner not only performs inference of component health status, but also computes an optimal sequence of tests that needs to be performed for fault isolation, given the current inferred health status, the allowable set of tests, and any precedence constraints on the tests. Thus, TEAMATE is appropriate for ground-based deployment where troubleshooting is performed interactively.

#### 3. Monitoring TEAMS Specifications using MOP

We report partial work on developing a TEAMS logic plugin for MOP, which will automatically generate monitoring code from the TEAMS temporal specifications.

In a system where requirements are monitored and recovery code is executed when violations are detected, the correctness of the entire system relies only on the guarantees provided by the monitor and the recovery code. Verification of the entire system can be decomposed into checking the correctness of the monitor and of the recovery code, which are expected to be much simpler and cheaper than verifying the original program. Currently, we are working on developing an integrated framework for IVHM system monitoring, control and verification. In this framework, the TEAMS tools will be used to capture the requirements specifications of the flight system. The MOP framework, extended with a TEAMS logic plugin, will process the captured system specifications and generate monitoring code automatically. The generated monitors will check the flight system at runtime via the monitoring mechanism provided by TEAMS, steering the system if failures are detected. This way, system models and runtime verification together are expected to form a solid foundation for developing reliable aviation systems.

#### References

- F. Chen, M. D'Amorim, and G. Rosu. A formal monitoring-based framework for software development and analysis. In: *Proc. ICFEM 04*, volume 3308 of LNCS, 2004, pp. 357–373.

- [2] F. Chen and G. Rosu. Mop: An efficient and generic runtime verification framework. In Proc. OOP-SLA'07, ACM Press, 2007, pp. 569-588.

- [3] F. Chen, T.F. Serbanuta and G. Rosu. jPredictor: A predictive runtime analysis tool for Java In: Proc. ICSE'08, to appear.

- [4] S. Deb, S. Ghoshal, V. N. Malepati, and D. L. Kleinman. Tele-diagnosis: Remote monitoring of large-scale systems. In: Proc. The IEEE Aerospace Conference, 2000.

- [5] K. Havelund and G. Rosu. Monitoring Java programs with Java PathExplorer. In: Proc. 1st Workshop on Runtime Verification (RV 01), ENTCS, Vol. 55, 2001.

- [6] K. Havelund and G. Rosu. Monitoring programs using rewriting. In: Proc. International Conference on Automated Software Engineering (ASE 01), IEEE, 2001, pp. 135-143.

Olga Brukman et al.: Self-\* Programming: Run-Time Parallel Control Search for Reflection Box, Proceedings of The Sixth NASA Langley Formal Methods Workshop, p.20–22

# SELF-\* PROGRAMMING: Run-Time Parallel Control Search for Reflection Box\*

Olga Brukman, Shlomi Dolev

Department of Computer Science, Ben-Gurion University of the Negev, Beer-Sheva, 84105, Israel {brukman, dolev}@cs.bgu.ac.il

#### Extended Abstract

In the early attempts to reach supersonic speeds, flight pilots experienced a strange phenomenon that made their control surfaces useless, and their aircraft uncontrollable. The airplanes were saved by either reducing the speed or changing the usual control procedure. Flying an airplane in a volcano ash cloud may stop the operation of the airplane. The airplane can still be saved if the pilots direct it out of the ash cloud, let the engines cool and then restart them. These two examples demonstrate the type of dramatic control changes that are sometimes required to be made on-line without prior experience, when the environment changes unexpectedly.

Today, when a programmer creates a program, he/she designs the program for a certain environment. When the program encounters unanticipated environmental behavior, program performance may degrade drastically, it may continue to execute while producing a faulty (unexpected) output, or it may crash. Programmers and system administrators use their accumulated knowledge of the system and of the environment to investigate and solve problems by patching up the system each time a new problem is detected. In many cases, the solution is post mortem and off-line. Ideally, systems would be autonomous, i.e., the systems would be able to cope with unexpected situations dynamically and independently, without human intervention.

In the example of the plane in the volcano ash cloud, imagine that the plane is able to release miniature replicas of itself into the air. Each replica is set to try a different control program. The replicas that manage to successfully get out of the ash cloud report back to the plane. The plane uses the obtained successful control to overcome the problem. This is an example of an autonomic system that is able to deal with unexpected changes in the environment.

**Our contribution.** We assume that an environment is very large, sophisticated and dynamic. We do not make any assumptions on changes the environment may undergo. On-line learning and modeling of the typically unbounded environment automaton for every change is impossible. We choose to learn a control for a *plant* only, where the plant is part of the environment with which the control interacts. A plant can be either a *black box* or an *rs-box* (reflection and set box). In case of a *black box* plant, only the plant inputs and output are observable. Otherwise, when the plant is a *rs-box* plant we are able to observe the plant state and/or set the plant to a certain state.

The environment is *reentrant* and *history oblivious* for long enough periods. A *reentrant* environment allows several copies of a plant to interact with the environment independently; A *history*

$<sup>\</sup>star$  Partially supported by the Lynne and William Frankel Center for Computer Sciences, by a Deutsche Telecom grant, the Israeli Ministry of Science, and the Rita Altura Trust Chair in Computer Sciences

*oblivious* environment ensures a repetition of a plant-environment interaction (in the probabilistic case with the same probability) when the plant is set to the same beginning state.

Our settings differ from the common approach where the whole environment is considered with no distinction between the machinery the control interacts with and the rest of the universe [3]. When the whole environment is considered, the environment can only be modeled by a nondeterministic infinite automaton. Making a distinction between a plant and an environment allows us to assume that a plant can be modeled by a deterministic or probabilistic finite automaton. We use testing techniques to obtain a control for the plant dynamically in an efficient manner.

The control search engine receives specifications as an input. No *realizable* specifications [1] exist for unpredictable dynamic environments. The control specifications are *unrealizable*. We assume that unrealizable specifications are potentially more abstract and short than realizable specifications, and, therefore, less prone to human mistakes. Thus, the inherit human-specifications interface is more robust than the human-program interface.

We search for a control that satisfies unrealizable specifications [1] by on line experimentation on the plant replicas. During the on line experimentation, we implicitly check whether the unrealizable specifications define *weakly realizable* specifications, given the behavior restriction on the current environment. A successful search for a control implicitly identifies the *weakly realizable* specifications, and explicitly identifies the implementation that respect the specifications.

We suggest a control search engine that finds a supervisory control dynamically and automatically by experimenting on plant replicas. The program search engine continuesly produces a control which respects a set of desired specifications in the presence of dynamic changes in an environment. In order to detect the deterioration of an executed control due to a change in the environment, the control search engine constantly monitors the current control execution by obtaining a reliable record of the control-plant-environment interaction from a dependable entity called an *Observer* and evaluating the quality of the interaction. A search for a new control is initiated if performance of the existing control is not satisfactory.

We design control search algorithms for various settings and capabilities of the plant state observation and manipulation. In particular, the plant state manipulation capabilities are: (i) plant state reflection which allows a control search algorithm to learn a connected component of a current plant state in the plant automaton graph (ii) plant state set that generalizes the reset capability, allows setting the plant to each of its states and exploring all connected components of the plant automaton graph, and (iii) (static or dynamic) plant replication capability that allows instantiation of new replicas, or use of preexisting replicas for parallelizing testing algorithms. Figure 1 summarizes the complexity of the algorithms we have designed for different settings: the total number of steps in all experiments and the length of the longest experiment (i.e., the longest execution of a plant replica).  $N_{max}$  is the upper bound on the number of plant automaton states N,  $\Sigma_{in}^{pc}$  is an alphabet of values of the plant input variables in the plant-control interaction, and P is the length (number of steps in a system execution) of a period in which the system repeats once a certain behavior (achieves some goal).

We consider two cases. In the first case the plant and the environment (at every given moment) are deterministic (algorithms I - IV). In the second case probabilistic transition functions for the environment and for the plant are considered (algorithm *Probabilistic*). See [2] for more details.

In our work, we concentrate on showing how parallelization and the capabilities for observing and manipulating the plant state allow us to improve the control search complexity. The use of parallelization makes the search time reasonable for on line systems, trading off (possibly exponential

| Algorithm     | Reflection | $\mathbf{Set}$ | Total Number Of Steps                           | Longest       |

|---------------|------------|----------------|-------------------------------------------------|---------------|

|               |            |                | In All Experiments                              | Experiment    |

| Ι             | ¬Available | ¬Available     | $O((PN_{max}) \Sigma_{in}^{pc} ^{N_{max}+P+1})$ | $O(PN_{max})$ |

| II            | Available  | ¬Available     | O(PN)                                           | O(P)          |

| III           | ¬Available | Available      | $O(N \Sigma_{in}^{pc} )$                        | O(N)          |

| IV            | Available  | Available      | $O(N \Sigma_{in}^{pc} )$                        | O(1)          |

| Probabilistic | Available  | Available      | $O(N^3 \Sigma_{in}^{pc} )$                      | O(1)          |

| <b>F</b> . | -            | 0.1    |          |        |               |

|------------|--------------|--------|----------|--------|---------------|

| Figure 1   | Properties   | of the | control  | search | algorithms.   |

| I ISUIC I. | 1 10per ties | or uno | 00110101 | Dearon | angor runnin. |

or polynomial) time with a (exponential or polynomial) number of plant replicas. The plant state capabilities allow reduction of the number of experiments on the plant replicas from exponential (for a *black box* plant) to polynomial (for *rs*-box plant) in the number of plant automaton states. **Acknowledgments.** We thank Moshe Vardi and Doron Peled for useful inputs and discussions.

#### References

- M. Abadi, L. Lamport, P. Wolper. "Realizable and Unrealizable Specifications of Reactive Systems". Proceedings of the 16th International Colloquium on Automata, Languages and Programming (ICALP'89), pp. 1-17, Stresa, Italy, July 1989.

- [2] O. Brukman, S. Dolev. "Self-\* Programming Run-Time Reflection&Set&Replication-Box Control Synthesis". *Technical Report #08-08*, Ben-Gurion University of the Negev, Beer-Sheva, Israel, February, 2008.

- [3] A. Pnueli, R. Rosner. "On the Synthesis of a Reactive Module". Proceedings of the 16th ACM Symposium on Principles of Programming Languages (POPL'89), pp. 179-190, Austin, Texas, USA, January 1989.

William B. Gardner: Getting Somewhat Formal with CSP and C++, Proceedings of The Sixth NASA Langley Formal Methods Workshop, p.23–25

### Getting Somewhat Formal with CSP and C++

William B. Gardner

Modeling & Design Automation Group, Dept. of Computing & Information Science, University of Guelph, Ontario, Canada wgardner@cis.uoguelph.ca

#### 1. Introduction

Concurrent systems present special design challenges due to their complex interactions, both with their environment, and internally in terms of synchronization and communication among their constituent processes. This is the case whether they are single-host systems, distributed systems, or embedded systems with hardware and software components. Formal methods have been advocated as a way to verify system properties at the design stage, but industry practitioners have not been eager to adopt abstruse mathematical notations, uncommon programming languages, or additional costly engineering process steps. Thus concurrent systems often continue to be designed and tested on an ad hoc basis.

There is a "spectrum of formality" in system development that ranges from (1) largely ad hoc vs. (2) mature, repeatable development processes at the minimal end, through (3) the use of formal specifications vs. (4) full formal development processes at the maximal end, with correspondingly greater development costs moving along the spectrum. The goal of our approach is to occupy ground between points (3) and (4): utilizing verifiable formal specifications written in CSP (Communicating Sequential Processes) for *selected portions* of a system-particularly the control backbone where interprocess synchronization and communication take place-and proceeding to an implementation via automated software synthesis instead of via hand translation. Modules to perform computation and I/O may be written in ordinary C++ and linked to the control backbone through CSP events and channels. This approach, based on the tool called CSP++, is described in [3] as a method of bridging the typically separate worlds of formal methods and conventional programming.

Advantages of this approach, compared to hand implementation of formal specifications, include code that embodies the specification's verified properties; and, compared to full formal development, reduced cost and development time due to less reliance on formal methods "gurus," and a role for widely-available C++ programmers.

#### 2. Outline of approach

The design flow will be described, starting from tools (from Formal Systems Europe, Ltd.) used for checking CSPm specifications, exploring their state space, and formally verifying their properties, through the automatic translation step, and execution via the CSP++ object-oriented application framework (OOAF), to checking actual system traces for trace refinement against the specification. CSPm is a commonly-used machine-readable form of CSP, which our tools now support for translation [4], thus providing a "straight through" design flow from commercial

verification tools to executable code. Run-time execution is based on Gnu Pth (Portable Threads). Recently, support for operators from Timed CSP-timed prefix, timeout, and interrupt-has been added to CSP++. This approach is targeted at soft real-time systems, but not currently suitable for hard real-time, due to the inability to guarantee maximum latencies.

#### 2.1. Technical challenges

Making a direct translation from CSP to a conventional programming language is difficult because a language like C++ lacks all the key elements of the CSP computational model: concurrent processes (or threads), interprocess communication, and interprocess synchronization. These elements are typically obtained from third-party packages, such as POSIX Pthreads, and introducing them in an informal fashion is what gets programmers into trouble. Rather than attempting a direct translation, an OO framework was constructed to be a high-level translation target with classes providing the execution semantics of CSP processes, events, and channels, including deterministic choice. (The most challenging aspect was multiprocess synchronization, which has barrier semantics, combined with choice operators active in any or all processes.) The translator tool of CSP++ inputs a user's specification written in CSPm, and outputs a C++ program that is an "instantiation" of the OOAF. When compiled with the framework's header files and linked with its library, the resulting program is an executable form of the CSPm specification.

At the above stage, the program is useful for simulating the CSP specification. It is intended to form the control backbone for an application, and, by itself, is only capable of limited interaction with a user at a console. For example, the CSP channel input operation option?x would prompt the user to enter an integer for channel "option" and store the result in the specification's variable x. To go beyond this stage, a programmer would prepare C++ functions to link with selected channels and events in the CSP control backbone. If the programmer links a user-coded function (UCF) to channel *option*, then the framework will call the function at run time. It will in turn obtain actual input-from a console, sensor, file, etc.-and pass it back to the framework.

UCFs must be under some restrictions in order to avoid violating the verified properties of the CSP specification: they cannot perform interprocess communication, nor maintain state between invocations that is not provided by the framework (because a UCF may be called from multiple threads). Furthermore, any given CSP event or channel can be used internally within the specification, or for linking to a UCF, but not both. Currently, UCF-linked events and channels can only participate in choice operations to a limited extent, because they do not implement the necessary try-and-backout capability. This restriction may be lifted in the future.

UCFs are intended to perform computations that would be awkward or inefficient to express in CSPm, to carry out I/O with the application's environment, or, in general, to do any processing that a designer considers not worthwhile to formally specify.

In terms of formal verification, the CSP++ tool chain is designed to leverage third-party verification tools. CSP++ is used to make an already-verified specification executable; it does not do verification itself, other than to help prove trace refinement.

#### 2.2. Alternative approaches

The main alternative for combining CSP-style formal interprocess communication semantics with conventional programming languages is the family of xCSP libraries: JCSP [6] for Java, C++CSP for C++, CCSP for C. The programmer codes in the target language, utilizing library objects to construct channels, launch processes, etc. Thus concurrency is provided for C and C++, while in Java, its native concurrency mechanisms are overlaid with primitives having formal semantics. This approach can be considered more readily accessible than CSP++, in that programmers need not know any CSP at all (though, in that case, they may misuse the components). To start with a verified specification, it would have to be hand-translated into, say, JCSP, with the risk of incorrect construction, or utilize some other complex steps of formal refinement [5].

### 3. Case studies

Several case studies created using CSP++ will be outlined: a point-of-sale register [1] developed to run on a Xilinx Microblaze core with uClinux; an automated teller [2] containing 22 UCFs with socket connections to a MySQL simulated bank database; and an automated vacuum cleaner (demonstrating new timed operators).

#### 4. Future work

CSP++ is being enhanced for hardware/software codesign with the ability to communicate using CSP channels from the software control backbone to hardware "IP" blocks. The objective is to use CSP++ for system-on-programmable-chip applications.

### References

- J. Carter, M. Xu, and W. B. Gardner. Rapid prototyping of embedded software using selective formalism. In Proc. 16th IEEE International Workshop on Rapid System Prototyping (RSP'05), pages 99-104, Washington, DC, USA, 2005. IEEE Computer Society.

- [2] S. Doxsee and W. Gardner. Synthesis of C++ Software from Verifiable CSPm Specifications. In Proc. 12th IEEE International Conference and Workshops on the Engineering of Computer-Based Systems, 2005. ECBS '05., pages 193-201, 2005.

- [3] W. B. Gardner. Converging CSP specifications and C++ programming via selective formalism. ACM Trans. on Embedded Computing Sys., 4(2):302-330, 2005.

- W. B. Gardner. CSP++: How Faithful to CSPm? In Proc. Communicating Process Architectures 2005 (WoTUG-27), pages 129-146, Eindhoven, Sept. 2005. IOS Press.

- [5] A. A. McEwan. A Calculated Implementation of a Control System. In I. R. East, D. Duce, M. Green, J. M. R. Martin, and P. H. Welch, editors, *Communicating Process Architectures* 2004, pages 265-280, 2004.

- [6] P. H. Welch, N. C. C. Brown, J. Moores, K. Chalmers, and B. H. C. Sputh. Integrating and Extending JCSP. In A. A. McEwan, W. Ifill, and P. H. Welch, editors, *Communicating Process Architectures 2007*, pages 349-370. IOS Press, July 2007.

Borzoo Bonak<br/>darpour et al.: Challenges and Demands on Automated Software Revision, Proceedings of The Sixth NASA Langley Formal Methods Workshop, p.26–28  $\,$

### Challenges and Demands on Automated Software Revision

Borzoo Bonakdarpour, Sandeep S. Kulkarni

Department of Computer Science and Engineering, Michigan State University, East Lansing, Michigan 48824, USA {borzoo, sandeep}@cse.msu.edu

### 1. Motivation

In the past three decades, automated program verification has undoubtedly been one of the most successful contributions of formal methods to software development. However, when verification of a program against a logical specification discovers bugs in the program, manual manipulation of the program is needed in order to repair it. Thus, in the face of existence of numerous unverified and uncertified legacy software in virtually any organization, tools that enable engineers to automatically verify and subsequently *fix* existing programs are highly desirable. In addition, since requirements of software systems often evolve during the software life cycle, the issue of *incomplete specification* has become a customary fact in many design and development teams. Thus, automated techniques that *revise* existing programs according to new specifications are of great assistance to designers, developers, and maintenance engineers. As a result, incorporating *program synthesis* techniques where an algorithm generates a program, that is *correct-by-construction*, seems to be a necessity.

The notion of manual program repair described above turns out to be even more complex when programs are integrated with large collections of sensors and actuators in hostile physical environments in the so-called *cyber-physical systems*. When such systems are safety/missioncritical (e.g., in avionics systems), it is essential that the system reacts to physical events such as faults, delays, signals, attacks, etc, so that the system specification is not violated. In fact, since it is impossible to anticipate all possible such physical events at design time, it is highly desirable to have automated techniques that revise programs with respect to newly identified physical events according to the system specification. Thus, one can observe that while formal software verification plays an important role in ensuring the correctness of systems, it is equally important to address the following fundamental question:

> In the face of constant evolution of existing computing systems and their physical environment, how should we revise them according to their specification and how should we cure their vulnerabilities (e.g., failures, time unpredictability, insecurity, etc) in an incremental and automated fashion?

### 2. Current Results

The notion of program revision (repair) was independently introduced by Bonakdarpour, Ebnenasir, and Kulkarni [FMICS'06, OPODIS'05] and Jobstmann, Griesmayer, and Bloem [CAV'05]. In our work, we have focused on developing a theory of automated program revision from different perspectives such as time-predictability, fault-tolerance, and distribution. The main focus of this theory is to identify instances where sound and complete automated revision of programs can be achieved in polynomial-time, and, where it is hard in some class of complexity. Complexity analysis identifies cases where program revision is (1) likely to be successful via developing efficient algorithms and heuristics, or (2) unlikely to have an impact. Completeness of a revision algorithm is important in the sense that if the algorithm fails to revise a program with respect to a property, it implies that the program in its current form is not *fixable* and, hence, a more comprehensive approach (e.g., synthesis from specification) must be applied. Thus far, the theory has been established in the following contexts:

- 1. We concentrated on automatic addition of untimed (respectively, real-time) UNITY properties to programs in the form of a finite state automata (respectively, timed automata) such that revised programs continue to satisfy universally quantified properties of the original program [FMICS'06, OPODIS'05].

- 2. We have extended the basic theory by considering systems where programs are subject to a set of uncontrollable *faults* [Sss'06]. We considered synthesizing three levels of fault-tolerance, namely *failsafe*, *nonmasking*, and *masking*, based on satisfaction of safety and liveness properties in the presence of faults. For failsafe and masking fault-tolerance, we considered two additional levels, namely *soft* and *hard*, based on satisfaction of timing constraints in the presence of faults. In our case studies, besides the factual benefits of automated addition of fault-tolerance, we observed that our synthesis methods can be potentially used to determine incompleteness of specification as well. We also introduced the notion of *bounded-time phased recovery* [FM'08] where simple recovery to the program's normal behavior is necessary, but not sufficient. For such programs, it is necessary to accomplish recovery in a sequence of phases, each ensuring certain constraints.

- 3. In order to make synthesis algorithms efficient so that they can be used in tools in practice, we have developed a set of symbolic heuristics for automatic synthesis of fault-tolerant distributed untimed programs [ICDCS'07]. Our experimental results on synthesis of classic fault-tolerant distributed problems showed that synthesis for these problems is feasible for state space of size 10<sup>30</sup> and beyond. The tool SYCRAFT (SYmboliC synthesizeR and Adder of Fault-Tolerance) implements the aforementioned heuristics.

The correctness of a selection of our synthesis algorithms is verified by the theorem prover PVS [AFM'06, LOPSTR'04]. This verification essentially shows that any program synthesized by our algorithms is indeed correct-by-construction.

### 3. Related Work