# United States Patent [19]

## Bergman

[11] Patent Number: 5,115,497

Date of Patent: [45]

May 19, 1992

#### [54] OPTICALLY INTRACONNECTED COMPUTER EMPLOYING DYNAMICALLY RECONFIGURABLE HOLOGRAPHIC **OPTICAL ELEMENT**

[75] Inventor: Larry A. Bergman, Van Nuys, Calif.

[73] Assignee: California Institute of Technology,

Pasadena, Calif.

[21] Appl. No.: 103,192

Oct. 1, 1987 [22] Filed:

[51] [52] 364/232.2; 364/261; 364/261.1; 364/263.1;

364/262.4; 364/262.9; 364/264 [58] Field of Search ... 364/200 MS File, 900 MS File, 364/736, 741

[56]

#### References Cited

#### U.S. PATENT DOCUMENTS

| 3,916,383 | 10/1975 | Malcolm 364/200          |

|-----------|---------|--------------------------|

| 4,136,383 | 1/1979  | Takesue 364/200          |

| 4,172,281 | 10/1979 | Gordon 364/200           |

| 4,332,008 | 5/1982  | Shima et al 364/200      |

| 4,342,082 | 7/1982  | Brown et al 364/200      |

| 4,384,324 | 5/1983  | Kim et al 364/200        |

| 4,395,758 | 7/1983  | Helenius et al 364/200   |

| 4,454,578 | 6/1984  | Matsumoto et al 364/200  |

| 4,641,275 | 2/1987  | Hatakeyama et al 364/900 |

| 4,705,344 | 11/1987 | Hinton et al 350/3.73    |

| 4,811,210 | 3/1989  | McAulay 364/200          |

| 4,831,519 | 5/1989  | Morton 364/200           |

| 4,859,012 | 8/1989  | Cohn 350/96.24           |

|           |         |                          |

#### OTHER PUBLICATIONS

Wu, W. H. et al., "Implementation of Optical Interconnections for VLSI", IEEE Transactions on Electron Devices, vol ED-34, No. 3, Mar. 1987, pp. 706-126. Bergman, L. A. et al., "Holographic Optical Interconnects For VLSI", Optical Engineering, vol. 25, No. 10, Oct. 1986, pp. 1109-1118.

Primary Examiner—Kevin A. Kriess Attorney, Agent, or Firm-Edward O. Ansell

#### **ABSTRACT**

An optically intraconnected computer and a reconfigurable holographic optical element employed therein. The basic computer comprises a memory for holding a sequence of instructions to be executed; logic for accessing the instructions in sequence; logic for determining for each the instruction the function to be performed and the effective address thereof; a plurality of individual elements on a common support substrate optimized to perform certain logical sequences employed in executing the instructions; and, element selection logic connected to the logic determining the function to be performed for each the instruction for determining the class of each function and for causing the instruction to be executed by those the elements which perform those associated the logical sequences affecting the instruction execution in an optimum manner. In the optically intraconnected version, the element selection logic is adapted for transmitting and switching signals to the elements optically.

#### 35 Claims, 4 Drawing Sheets

#### OPTICALLY INTRACONNECTED COMPUTER **EMPLOYING DYNAMICALLY** RECONFIGURABLE HOLOGRAPHIC OPTICAL **ELEMENT**

### ORIGIN OF THE INVENTION

The invention described herein was made in the performance of work under a NASA contract, and is subject to the provisions of Public Law 96-517 (35 USC 10 202) in which the Contractor has elected to retain title.

#### BACKGROUND OF THE INVENTION

The present invention relates to digital computer architectures and internal communications thereof and, 15 more particularly, to an optically intraconnected computer comprising, a memory for holding a sequence of instructions to be executed; logic for accessing the instructions in sequence; logic for determining for each instruction the function to be performed and the effec- 20 tive address thereof; a plurality of individual elements on a common support substrate optimized to perform certain logical sequences employed in executing the instructions; and, element selection logic connected to the logic determining the function to be performed for  $^{25}$ each instruction for determining the class of each function and for causing the instruction to be executed by those elements which perform the associated logical sequences affecting the instruction execution in an optimum manner; wherein, the element selection logic in- 30 cludes means for transmitting and switching signals to the elements optically comprising, a holographic optical element including a holographic reflective surface mounted adjacent and parallel to the common support substrate; a plurality of light source means carried by 35 the common support substrate for directing signalmodified light beams towards the holographic reflective surface to be reflected thereby back towards the common support substrate; and, a plurality of light detecting means carried by the common support sub- 40 strate and operably connected to respective ones of the elements to provide electrical signals thereto for detecting selected ones of the light beams as reflected by the holographic reflective surface and providing associated electrical signals derived from the reflected light beams. 45

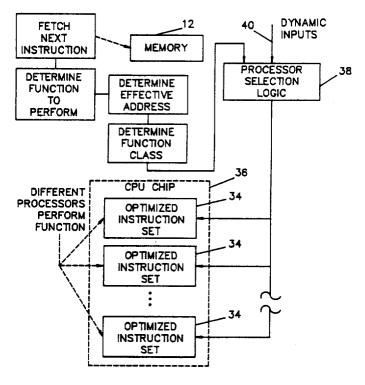

In its simplest description, a digital computer is a device which executes a series of instructions relative to a set of data to accomplish a result. A very basic prior art digital computer is generally indicated as 10 in FIG. tions and data and an arithmetic and logic unit (ALU) 14 connected to a clock 16. The ALU 14 includes registers and logic to repetitively perform the functions shown in FIG. 2. As part of performing its computing functions, the ALU 14 can read from and write to the 55 family which is fast, compact, easily reconfigurable, memory 12 on an individually addressable basis; that is, the memory 12 comprises a matrix of individually addressable locations containing binary (digital) information which can be employed as either an instruction or a piece of data by the ALU 14. The operation of the 60 ALU 14 and its accesses to the memory 12 are controlled by the clock 16 in that the pulses of the clock 16 determine the points in time when the functional elements of the ALU 14 can perform and the memory 12 can be read from and written to.

As depicted by FIG. 2, the ALU 14 sequentially fetches the next instruction to be executed from the memory 12. The instruction is then inspected to deter-

mine the function to be performed (i.e. add, multiply, etc.) and the effective address of the data (i.e. one of the registers, a location in memory 12, etc.). The ALU 14 then performs the indicated function employing preestablished hardware instruction performance logic 18.

As can be appreciated, the design and construction of a "new" digital computer operating as above was a time consuming task. As vacuum tubes gave way to discrete component transistors, and the like, and then to integrated circuits; and, as the evolutionary period between new integrated circuits and the technology of producing them became less and less, the designing and implementing of the pre-established hardware instruction performance logic 18 as described above became more and more impractical. Microprocessor design traditionally involves much combinational (random) custom logic in the layout of the ALU. In such an implementation, the basic instruction set of the central processing unit (CPU) which executes the CPU's instruction set is embedded in difficult-to-modify logic which is not programmable, being embodied in immutable hardware. This approach suffers from unpredictable logic errors, delays caused by the impedance of the conductors, and requires excessive space on the CPU's chip. Thus, the instruction execution rate—and the clock speed—are degraded significantly from that attainable by the CPU.

Attempts to make programmable instruction sets have resulted in the development of micro-coded CPUs operating as depicted in FIG. 3. Whereas the basic instructional fetching and evaluation procedure of prior computers is retained, a micro-coded CPU's hardwareimplemented instructions are minimized to a set of "standard" operations which can be performed in various combinations to accomplish more complex "instructions". The instruction definitions are embodied in sequences of "micro-code" instructions or firmware 20 typically contained in erasable programmable read only memory (EPROM) 22. The EPROM memory 22 may be erased by flooding with ultraviolet light, or electrically (EEPROMS). This family of machines is easily modified, but also suffers similar speed degradation. Moreover, while "easily" modifiable to a new configuration, such modification is a bench top undertaking and is not adaptable to on-line and/or real-time reconfiguration.

In one approach to the residual problems of microcoded computers, reduced instruction set computers (RISC) have been designed. They are compact and fast, 1. The computer 10 has a memory 12 containing instruc- 50 but can only be customized for a limited group of opera-

#### STATEMENT OF THE INVENTION

This invention provides a new computer architecture and, in some cases, even dynamically reconfigurable as to its performed instruction definitions.

The foregoing is accomplished in a computer including a memory for holding a sequence of instructions to be executed, logic for accessing the instructions in sequence, logic for determining for each instruction the function to be performed and the effective address thereof, and logic for executing each instruction, by the improvement of the present invention comprising, the logic for executing instructions comprising a plurality of individual elements on a common support substrate optimized to perform certain logical sequences employed in executing instructions; and, element selection

logic connected to the logic determining the function to be performed for each instruction for determining the class of each function and for causing the instruction to be executed by those elements which perform the associated logical sequences affecting the instruction execution in an optimum manner.

3

In the preferred embodiment, the element selection logic includes means for accepting dynamic inputs designating changes in the operating environment of the computer and means for changing the ones of the ele- 10 ments which execute each instruction whereby instruction execution is affected in an optimum manner for the present dynamic conditions.

Optionally, the elements can comprise individual arithmetic and logic units contained on a single central 15 processor unit chip; or, the elements can comprise individual reduced instruction set computers contained on a single central processor unit chip.

Further in the preferred embodiment, the element selection logic portion for causing the instruction to be 20 referenced articles is incorporated into various embodiexecuted by the elements which perform those associated logical sequences affecting the instruction execution in an optimum manner includes means for transmitting and switching signals to the elements optically.

The preferred means for transmitting and switching 25 signals to the elements optically comprises, a holographic optical element including a holographic reflective surface mounted adjacent and parallel to the common support substrate; a plurality of light source means carried by the common support substrate for directing 30 art computer architecture. signal-modified light beams towards the holographic reflective surface to be reflected thereby back towards the common support substrate; and, a plurality of light detecting means carried by the common support substrate and operably connected to respective ones of the 35 elements to provide electrical signals thereto for detecting selected ones of the light beams as reflected by the holographic reflective surface and providing associated electrical signals derived from the reflected light beams.

In one embodiment, there are means for switching the 40 light source means on and off to determine which ones of the light detecting means received the reflected light beams whereby the sequence of the elements receiving and processing the signals is determined.

In the preferred embodiment, light modulation means 45 are disposed between the light source means and the light detecting means for selectively blocking and passing the light beams whereby the sequence of the elements receiving and processing the signals is determined.

The preferred light modulation means is a novel reconfigurable holographic optical element including a holographic reflective surface mounted adjacent and parallel to the common support substrate and light modulation means disposed adjacent the holographic reflec- 55 the passive operation of a prior art HOE and active tive surface for selectively blocking and passing light beams from reflecting from the holographic reflective surface at individual pixel positions thereof; and, means for switching the light modulation means on and off at the individual pixel positions thereof to determine 60 of the present invention being used to control the transwhich ones of the light detecting means receive the reflected light beams whereby the sequence of the elements receiving and processing the signals is determined.

### List of Cited References

A device called a holographic optical element (HOE) is incorporated into several of the embodiments of the present invention and forms the heart of the preferred

embodiments thereof. The HOE and its use in conjunction with VLSI is described in great detail in the following publications, of which copies are being filed contemporaneously herewith:

- 1. HOLOGRAPHIC OPTICAL INTERCON-NECTS FOR VLSI by L. A. Bergman, et al. as reprinted from "Optical Engineering" 25(10), 1109-1118 (October 1986).

- 2. IMPLEMENTATION OF OPTICAL INTER-CONNECTIONS FOR VLSI by L. A. Bergman, et al. as reprinted from "IEEE Transactions on Electron Devices", Vol. ED-34, No. 3, (March

- 3. APPLICATIONS AND DESIGN CONSIDER-ATIONS FOR OPTICAL INTERCONNECTS IN VLSI by L. A. Bergman, et al. as reprinted from "SPIE", Vol. 625, 117-126 (1986).

Discussion of the Cited References

The HOE device as described in the abovements of the present invention and a novel variation is disclosed herein as part of the present invention. The above-referenced articles do not show or suggest the use of a HOE as in the present invention or the novel variation of a HOE (i.e. a dynamically reconfigurable HOE) as is part of this invention.

#### BRIEF DESCRIPTION OF THE DRAWINGS

FIG. 1 is a simplified block diagram of a basic prior

FIG. 2 is a functional block diagram of the operation of the computer architecture of FIG. 1.

FIG. 3 is a functional block diagram of the operation of another prior art computer architecture of the microcode executing variety.

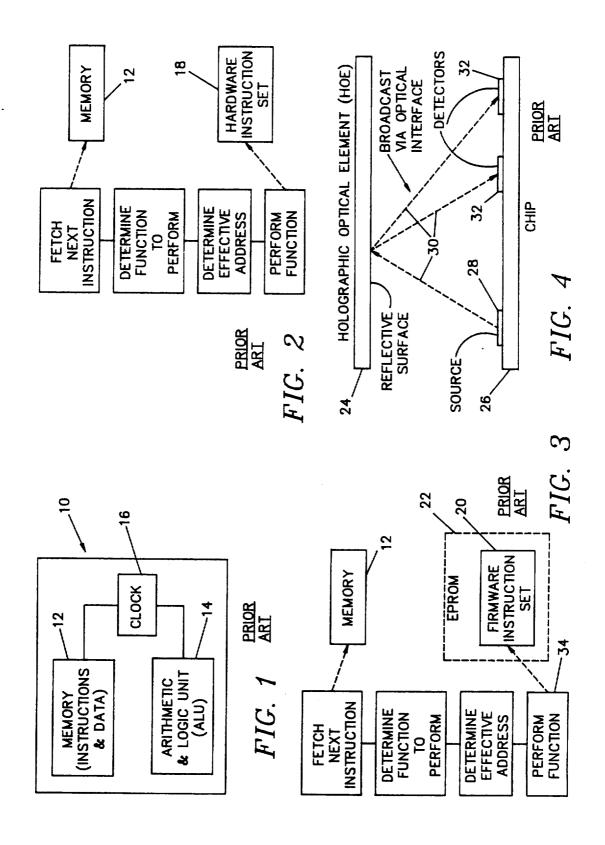

FIG. 4 is a simplified side view of a HOE being used to broadcast signals from one part of an adjacent computer chip to other parts of the chip optically.

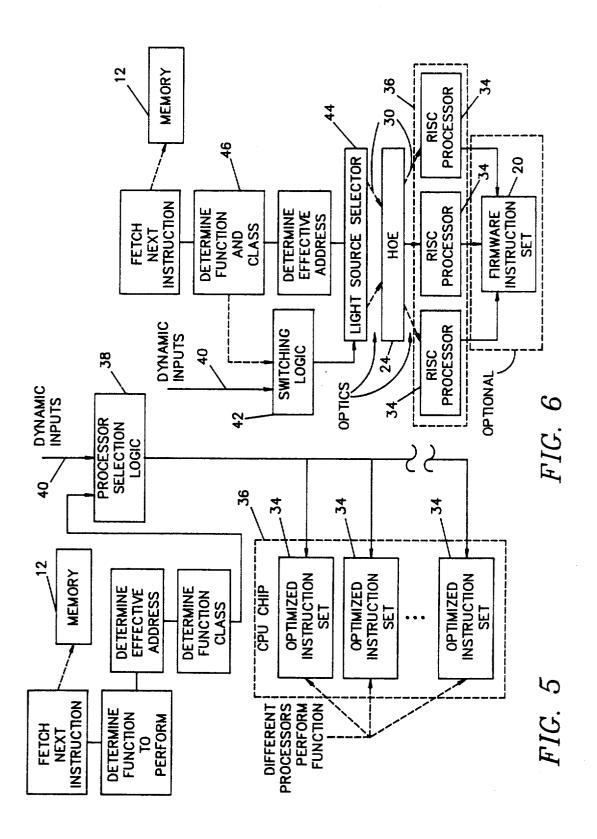

FIG. 5 is a semi-functional block diagram of a computer architecture according to the present invention in a basic embodiment thereof not employing a HOE

FIG. 6 is a semi-functional block diagram of a computer architecture according to the present invention in a basic embodiment thereof employing a prior art HOE therein.

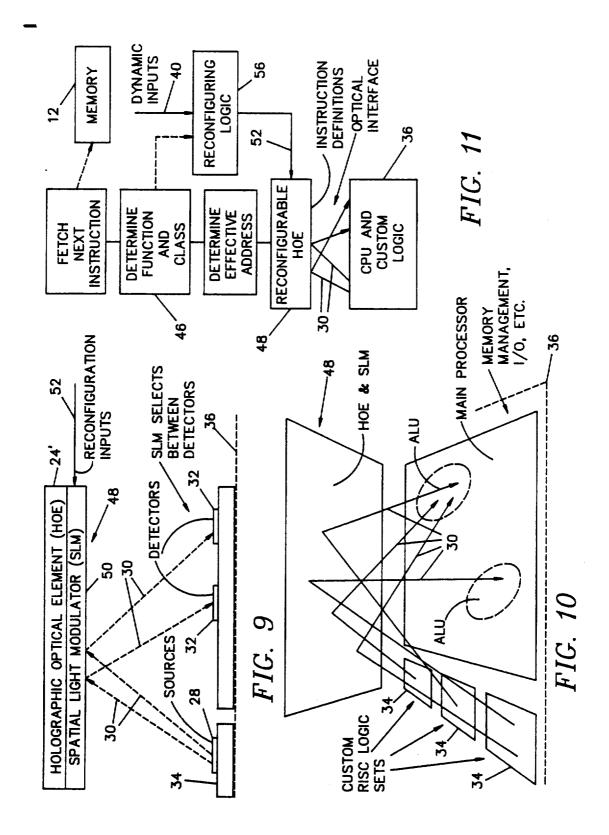

FIG. 7 is a semi-functional block diagram of a computer architecture according to the present invention in a semi-preferred embodiment thereof employing a 50 reconfigurable HOE of the present invention therein.

FIGS. 8(a)-8(d) are simplified side views of a HOE being used to transmit signals from one part of an adjacent computer chip to another part of the chip optically in the manner of FIG. 4 and showing the difference in operation of a dynamically reconfigurable HOE according to the present invention.

FIG. 9 is a simplified side view in the manner of FIGS. 4 and 8 of the dynamically reconfigurable HOE mission of signals from one part of an adjacent computer chip to another part of the chip optically.

FIG. 10 is a perspective representation of the manner of operation of the reconfigurable HOE of the present 65 invention as shown in FIG. 9.

FIG. 11 is a semi-functional block diagram of a computer architecture according to the present invention in its preferred embodiment employing a reconfigurable

HOE of the present invention therein responding to both internal and external influences in the dynamic reconfiguration of the HOE.

# DETAILED DESCRIPTION OF THE INVENTION

Prior to an actual description of the various computer architectures which form the family of the present invention, brief mention should be made of the HOE device employed therein. While those interested can get 10 detailed information about HOEs and their use from the above-referenced articles, the aspects thereof of particular interest to the present invention are shown in simplified form in FIG. 4. Basically, the HOE 24 can be thought of as an optical switching surface. The chip 26 15 and HOE 24 are physically juxtaposed in parallel spaced relationship to one another. The chip 26 contains one or more sources 28 of a laser beam 30 which is directed towards the surface of the HOE 24. The laser beam(s) 30 are reflected by the holographic surface of 20 the HOE 24 back towards the chip 26 to be detected by one or more optical detectors 32 wherein an electrical signal is created for further use by the logic of the chip 26. Thus, signal transmissions can be made at light speed without the delays, and the like, associated with electri- 25 cally conductive paths. Moreover "broadcast" transmissions can be made to multiple points simultaneously and the problems of complex interconnection layout between points on the chip 26 are eliminated. Again, this procedure and the physiology required therefor are 30 described in detail in the above-listed documents provided herewith.

Turning now to FIG. 5, a basic implementation of the present invention is shown in simplified form. In essence, the computer of FIG. 5 operates in the manner of 35 the prior art computer of FIG. 2; that is, the function performance is accomplished by hardware instruction logic. In this embodiment of the present invention, however, the hardware instruction logic is contained in individualized RISC processors 34 contained on the 40 CPU chip 36. Each of the RISC processors 34 is configured to perform an optimized instruction set. When the next instruction to perform has been fetched from memory 12, its function class is determined and input to processor selection logic 38, which determines which of 45 the RISC processors 34 is best suited (i.e. specifically designed) to perform that function. In the preferred embodiment, the processor selection logic 38 also responds to dynamic inputs at 40 whereby the selection of the RISC processor(s) 34 can be modified as a function 50 of changing dynamic conditions. It should be noted in this regard that the embodiment of FIG. 5 is different from a multi-processor computer architecture wherein functional sequences of instructions or "programs" are assigned to different ones of interconnected computers 55 (CPUs) for execution. In this embodiment of the present invention, the execution of each instruction in sequence is selectably and switchably accomplished by an appropriate RISC processor 34 contained within a single **CPU 36.**

The functional operation of another embodiment of the present invention is shown in FIG. 6 wherein multiple RISC processors 34 are again employed and a HOE 24 is employed in its switching capacity to cause performance, in each case, through an optical interface by the 65 RISC processor 34 best suited to the circumstances at the time. The HOE 24 is controlled by the switching logic 42 which controls which of the laser beams 30

6

from the light source selector 44 are directed to the reflecting surface of the HOE 24 to be reflected thereby to the desired RISC processor 34. The switching logic 42 is, in turn, basically controlled by the logic at 46 which determines the function to perform and its functional class; but, preferably, can be controlled as well by dynamic inputs 42 responding to changed conditions as in the prior embodiment. Both this embodiment and the prior embodiment of FIG. 5 can be totally hardware oriented; or, if desired, either embodiment can be operated as a microcoded computer by having the RISC processors access microcode firmware 20 as depicted in FIG. 6.

In the semi-preferred embodiment of the present invention shown in the functional block diagram of FIG. 7, the firmware/semi-software instruction sets of the prior embodiments are eliminated along with their physical interconnections and the problems associated therewith. The "micro-code" is embodied within the holographic surface of the reconfigurable HOE 48 and is "executed" by sequentially directing the laser beam containing the execution data from one area of the juxtaposed CPU chip 36 to another.

Before continuing to the preferred embodiment of the present invention, it is necessary to digress briefly to the drawings of FIGS. 8-10 wherein a novel dynamically reconfigurable HOE 48, as is part of the present invention and necessary thereto, is shown and distinguished over the basic HOE 24 in simplified form. The reconfigurable HOE 48 comprises a basic HOE 24' having a spatial light modulator (SLM) 50 disposed over (or as part of) the holographic reflective surface of the HOE 24' facing the chip 26'. The spatial light modulator 50 (or light valve) is a device presently known in the art by which each pixel position of a two-dimensional matrix can be individually modified as to its light passage qualities through electrical, magnetic, or other, means. A common example of such devices is familiar from socalled "liquid crystal" displays as employed in wristwatches, and the like. As with the HOE itself, the spatial light modulator art is a dynamic art changing and improving daily and those interested in the specifics of the latest developments in that art are directed to the literature generally available. In the interest of simplicity and the avoidance of redundancy, details of spatial light modulators and their operation will be omitted herein. It is sufficient to say for purposes of the present invention that, either as a replacement for or in addition to the holographic surface of the HOE 24', the dynamically changable SLM 50 can be changed under the control of reconfiguration inputs at 52 to, in turn, change the switching sequence of the HOE 24'. It should also be noted that while the spatial light modulation takes place on or directly adjacent to the holographic reflective surface of the HOE in the example depicted and described herein, as those skilled in the art will recognize and appreciate, the SLM could be interposed in the path of the light beam at a distance and its operation affected through the use of focusing optics well known in the art. While not preferred, a device operating as what could be referred to as a transmitting HOE (i.e. a form of pixel-oriented, matrix, spatial light modulator), as is known in the art, could also be employed in place of a reflective HOE. Also, the reflective surface of the HOE could comprise a plurality of reflective angles instead of a holographic surface, per se, within the scope and spirit of the present invention.

The difference in operation between a prior art HOE 24 as employed in the present invention in the embodiment of FIG. 6 and the novel reconfigurable HOE 48 employed in the preferred embodiments can be understood best with reference to FIGS. 8(a) through 8(d). 5 FIGS. 8(a) and 8(b) show the operation of a standard HOE 24. To communicate with detector "A", the laser beam 30 from laser source "A" is turned on and reflected from the holographic reflective surface of the HOE 24 at point "A" as depicted in FIG. 8(a). To com- 10 each instruction, the improvement wherein: municate with detector "B", on the other hand, the laser beam 30 from laser source "B" is turned on and reflected from the holographic reflective surface of the HOE 24 at point "B" as depicted in FIG. 8(b). Thus, since the HOE 24 is a passive device, switching through 15 its use can only be accomplished through the control of the source(s) 28 of the laser beam(s) 30.

By contrast, as depicted in FIGS. 8(c) and 8(d), the reconfigurable HOE 48 is a dynamic or active device. Multiple laser beams 30 from multiple sources 28 can be 20 directed at the reflective holographic surface of the HOE 24' continually. Switching is accomplished by controlling the light passing qualities of the pixel positions of the SLM 50. For example, as shown in FIG. 8(c), To communicate with detector "A", the laser 25 wherein: beam 30 from laser source "A" is allowed to reflect from the holographic reflective surface of the HOE 24 at point "A" while the pixel 54 of the SLM 48 at point "B" is darkened to prevent the laser beam 30 from source "B" to pass through and be reflected. To com- 30 municate with detector "B", on the other hand, the pixels 54 are reversed so that the laser beam 30 from laser source "B" is reflected from the holographic reflective surface of the HOE 24 at point "B" and the laser beam 30 from laser source "A" is blocked, as de- 35 wherein: picted in FIG. 8(d).

Turning now to FIG. 11 in combination with FIG. 10, the preferred embodiment of the present invention will now be described functionally. In this embodiment, the instruction sets are physically removed from the 40 wherein: CPU and instructions are to one or more ALUs (as appropriate) via light signals, with input and output signals routed point-to-point by the reconfigurable HOE 48 under the control of the reconfiguration logic 56 with inputs from the logic determining the function 45 wherein: and class 46 as well as dynamic inputs 40. The light signals are preferably generated by laser diodes and received by photodiodes as described in the abovereferenced literature. Functionally, this embodiment may be envisioned as several RISC designs overlaid on 50 a common VLSI substrate with each RISC being designed specifically for a specific operation such as Boolean operations, control, convolution, and the like in the manner previously described with respect to FIGS. 5-7. Each subset of instructions is mapped onto one of the 55 ALUs by the HOE 50, the specific subset desired being switched by turning on one set of laser diodes while switching off all the other sets, and/or by electronically selecting signals to be sent via a single set of laser diodes, etc. Thus, instruction set changes may be made 60 fairly rapidly. In basic form, the foregoing description also applies to the embodiment of FIG. 7 as previously discussed. In this embodiment, however, in addition to having multiple ALUs on the CPU portion of the chip so as to take advantage of specialized "hardware" capa- 65 bilities in each case as appropriate, the HOE 48 itself is dynamically reprogramable by the reconfiguration logic 56 in response to dynamic inputs at 40. As a result,

8

changes can be made very rapidly; in fact, it is contemplated that, possibly, changes will be able to be affected at clock speed.

- 1. In a computer including a memory for holding a sequence of instructions to be executed, logic for accessing the instructions in sequence, logic for determining for each instruction a function to be performed and an effective address thereof, and logic for executing

- (a) the logic for executing instructions comprises:

- a plurality of individual elements on a common support substrate optimized to perform certain logical sequences employed in executing instructions; and

- (b) the computer comprises:

- element selection logic means connected to the logic determining the function to be performed for each instruction for determining a class of each function and for causing the instruction to be executed by those of said elements which perform those of said logical sequences affecting the instruction execution in an optimum manner.

- 2. The improvement to a computer of claim 1

- said element selection logic means includes means for accepting dynamic inputs designating changes in an operating environment of the computer and means for changing the ones of said elements which execute each instruction as a function of said dynamic inputs whereby instruction execution is affected in an optimum manner for the present dynamic conditions.

- 3. The improvement to a computer of claim 1

- said elements comprise individual arithmetic and logic units contained on a single central processor unit chip.

- 4. The improvement to a computer of claim 1

- said elements comprise individual reduced instruction set computers contained on a single central processor unit chip.

- 5. The improvement to a computer of claim 1

- said element selection logic means portion for causing the instruction to be executed by those of said elements which perform those of said logical sequences affecting the instruction execution in an optimum manner includes means for transmitting and switching signals to said elements optically.

- 6. The improvement to a computer of claim 5 wherein said means for transmitting and switching signals to said elements optically comprises:

- a) a holographic optical element including a holographic reflective surface mounted adjacent and parallel to said common support substrate;

- b) a plurality of light source means carried by said common support substrate for directing signalmodified light beams towards said holographic reflective surface to be reflected thereby back towards said common support substrate; and,

- c) a plurality of light detecting means carried by said common support substrate and operably connected to respective ones of said elements to provide electrical signals thereto for detecting selected ones of said light beams as reflected by said holographic reflective surface and for providing associated

electrical signals derived from said reflected light beams to said elements.

- 7. The improvement to a computer of claim 6 and additionally comprising:

- means for individually and selectively switching said 5 light source means on and off to determine which ones of said light detecting means receive said reflected light beams whereby the sequence of said elements receiving and processing said signals is determined.

- 8. The improvement to a computer of claim 6 and additionally comprising:

- light modulation means disposed between said light source means and said light detecting means for said light beams whereby the sequence of said elements receiving and processing said signals is determined.

- 9. The improvement to a computer of claim 8 wherein:

- said light modulation means is disposed adjacent said reflective surface of said holographic optical ele-

- 10. The improvement to a computer of claim 5 wherein said means for optically transmitting and 25 switching signals to said elements comprises:

- a) a reconfigurable holographic optical element device including a holographic reflective surface mounted adjacent and parallel to said common support substrate and including light modulation 30 means disposed adjacent said holographic reflective surface for selectively blocking and passing light beams from reflecting from said holographic reflective surface at individual pixel positions thereof;

- b) a plurality of light source means carried by said common support substrate for directing signalmodified light beams towards said holographic reflective surface to be reflected thereby back towards said common support substrate;

- c) a plurality of light detecting means carried by said common support substrate and operably connected to respective ones of said elements to provide electrical signals thereto for detecting selected ones of said light beams as reflected by said holographic 45 reflective surface and for providing associated electrical signals derived from said reflected light beams to said elements; and,

- d) means for switching said light modulation means on and off at said individual pixel positions thereof 50 to determine which ones of said light detecting means receive said reflected light beams whereby the sequence of said elements receiving and processing said signals is determined.

- 11. In a computer including a memory for holding a 55 sequence of instructions to be executed, logic for accessing the instructions in sequence, logic for determining for each instruction a function to be performed and an effective address thereof, and logic for executing each instruction, a method of operation by said com- 60 puter, wherein said logic for executing each instruction comprises a plurality of individual elements on a common support substrate with each element optimized to perform certain logical sequences employed in executing instructions, said method comprising for each in- 65 struction the steps of:

- (a) determining the function to be performed;

- (b) determining a class of each function;

10

- (c) causing the instruction to be executed by those elements which perform the associated logical sequences affecting the instruction execution in an optimum manner.

- 12. The method of claim 11 and additionally comprising the steps of:

- a) accepting dynamic inputs designating changes in an operating environment of the computer; and,

- b) changing the ones of the elements which execute each instruction as a function of the dynamic inputs whereby instruction execution is affected in an optimum manner for the present dynamic conditions.

- 13. The method of claim 11 wherein said step of causindividually and selectively blocking and passing 15 ing the instruction to be executed by the elements which perform the associated logical sequences affecting the instruction execution in an optimum manner includes the step of:

- optically transmitting and switching signals to the elements.

- 14. The method of claim 13 wherein said step of optically transmitting and switching signals to the elements comprises the steps of:

- a) disposing a holographic optical element including a holographic reflective surface adjacent and parallel to the common support substrate;

- b) disposing a plurality of light sources on the common support substrate for directing signal-modified light beams towards the holographic reflective surface to be reflected thereby back towards the common support substrate;

- c) disposing a plurality of light detectors on the common support substrate and operably connecting them to respective ones of the elements to provide electrical signals thereto;

- d) selectively switching the light sources on and off to determine which ones of the light detector receive the reflected light beams; and,

- e) detecting selected ones of the light beams as reflected by the holographic reflective surface and providing associated electrical signals derived from the reflected light beams whereby the sequence of the elements receiving and processing the signals is determined.

- 15. The method of claim 13 wherein said step of transmitting and switching signals to the elements optically comprises the steps of:

- a) disposing a reconfigurable holographic optical element including a holographic reflective surface and light modulation means adjacent the holographic reflective surface for selectively blocking and passing light beams from reflecting from the holographic reflective surface at individual pixel positions thereof adjacent and parallel to the common support substrate;

- b) disposing a plurality of light sources on the common support substrate for directing signal-modified light beams towards the holographic reflective surface to be reflected thereby back towards the common support substrate;

- c) disposing a plurality of light detectors on the common support substrate and operably connecting them to respective ones of the elements to provide electrical signals thereto;

- d) selectively switching the light modulation means on and off at the individual pixel positions thereof to determine which ones of the light detecting means receive the reflected light beams; and,

- e) detecting selected ones of the light beams as reflected by the holographic reflective surface and providing associated electrical signals derived from the reflected light beams to the associated elements whereby the sequence of the elements 5 receiving and processing the signals is determined.

- 16. A computer comprising:

- (a) a memory for holding a sequence of instructions to be executed:

- (b) logic for accessing said instructions in sequence; 10

- (c) logic for determining for each said instruction a function to be performed and an effective address thereof:

- (d) a plurality of individual elements on a common support substrate optimized to perform certain 15 logical sequences employed in executing said instructions; and,

- (e) element selection logic means connected to said logic determining the function to be performed for each said instruction for determining a class of each 20 function and for causing the instruction to be executed by those of said elements which perform those of said logical sequences affecting the instruction execution in an optimum manner.

- 17. The computer of claim 16 wherein:

- said element selection logic means includes means for accepting dynamic inputs designating changes in an operating environment of the computer and means for changing the ones of said elements which execute each instruction as a function of said 30 dynamic inputs whereby instruction execution is affected in an optimum manner for the present dynamic conditions.

- 18. The computer of claim 16 wherein:

- said elements comprise individual arithmetic and 35 logic units contained on a single central processor unit chip.

- 19. The computer of claim 16 wherein:

- said elements comprise individual reduced instruction set computers contained on a single central processor unit chip.

- 20. The computer of claim 16 wherein:

- said element selection logic means portion for causing the instruction to be executed by those of said elements which perform those of said logical sequences affecting the instruction execution in an optimum manner including means for transmitting and switching signals to said elements optically.

- 21. The computer of claim 20 wherein said means for transmitting and switching signals to said elements optically comprises:

- a) a holographic optical element including a holographic reflective surface mounted adjacent and parallel to said common support substrate;

- b) a plurality of light source means carried by said 55 common support substrate for directing signalmodified light beams towards said holographic reflective surface to be reflected thereby back towards said common support substrate; and,

- c) a plurality of light detecting means carried by said 60 common support substrate and operably connected to respective ones of said elements to provide electrical signals thereto for detecting selected ones of said light beams as reflected by said holographic reflective surface and providing associated electrical signals derived from said reflected light beams.

- 22. The computer of claim 21 and additionally comprising:

- 12

- means for switching said light source means on and off to determine which ones of said light detecting means receive said reflected light beams whereby the sequence of said elements receiving and processing said signals is determined.

- 23. The computer of claim 21 and additionally comprising:

- light modulation means disposed between said light source means and said light detecting means selectively blocking and passing said light beams whereby the sequence of said elements receiving and processing said signals is determined.

- 24. The computer of claim 23 wherein:

- said light modulation means is disposed adjacent said reflective surface of said holographic optical element.

- 25. The computer of claim 20 wherein said means for transmitting and switching signals to said elements optically comprises:

- a) a reconfigurable holographic optical element including a holographic reflective surface mounted adjacent and parallel to said common support substrate and light modulation means disposed adjacent said holographic reflective surface for selectively blocking and passing light beams from reflecting from said holographic reflective surface at individual pixel positions thereof;

- b) a plurality of light source means carried by said common support substrate for directing signalmodified light beams towards said holographic reflective surface to be reflected thereby back towards said common support substrate;

- c) a plurality of light detecting means carried by said common support substrate and operably connected to respective ones of said elements to provide electrical signals thereto for detecting selected ones of said light beams as reflected by said holographic reflective surface and providing associated electrical signals derived from said reflected light beams to said elements; and,

- d) means for switching said light modulation means on and off at said individual pixel positions thereof to determine which ones of said light detecting means receive said reflected light beams whereby the sequence of said elements receiving and processing said signals is determined.

- 26. An optically intraconnected computer comprising:

- a) a memory for holding a sequence of instructions to be executed:

- b) logic for accessing said instructions in sequence;

- c) logic for determining for each said instruction the function to be performed and the effective address thereof;

- d) a plurality of individual elements on a common support substrate optimized to perform certain logical sequences employed in executing said instructions; and,

- e) element selection logic means connected to said logic determining the function to be performed for each said instruction for determining the class of each function and for causing the instruction to be executed by those said elements which perform those associated said logical sequences affecting the instruction execution in an optimum manner, said element selection logic means including means for transmitting and switching signals to said elements optically comprising,

e1) a holographic optical element including a holographic reflective surface mounted adjacent and parallel to said common support substrate;

e2) a plurality of light source means carried by said common support substrate for directing signal-modified light beams towards said holographic reflective surface to be reflected thereby back towards said common support substrate; and,

- e3) a plurality of light detecting means carried by said common support substrate and operably 10 connected to respective ones of said elements to provide electrical signals thereto for detecting selected ones of said light beams as reflected by said holographic reflective surface and providing associated electrical signals derived from 15 said reflected light beams to said elements.

- 27. The optically intraconnected computer of claim 26 wherein:

said element selection logic means additionally includes means for accepting dynamic inputs designating changes in the operating environment of the optically intraconnected computer and means for changing the ones of said elements which execute each instruction whereby instruction execution is affected in an optimum manner for the present 25 dynamic conditions.

28. The optically intraconnected computer of claim 26 wherein:

said elements comprise individual arithmetic and logic units contained on a single central processor 30 unit chip.

29. The optically intraconnected computer of claim 26 wherein:

said elements comprise individual reduced instruction set computers contained on a single central processor unit chip.

30. The optically intraconnected computer of claim 26 and additionally comprising:

means for switching said light source means on and off to determine which ones of said light detecting 40 means received said reflected light beams whereby the sequence of said elements receiving and processing said signals is determined.

31. The optically intraconnected computer of claim 26 and additionally comprising:

light modulation means disposed between said light source means and said light detecting means for selectively blocking and passing said light beams whereby the sequence of said elements receiving and processing said signals is determined.

32. The optically intraconnected computer of claim 31 wherein:

said light modulation means is disposed adjacent said reflective surface of said holographic optical element

33. The optically intraconnected computer of claim 26 wherein:

a) said holographic optical element of said means for transmitting and switching signals to said elements optically comprises a reconfigurable holographic 60 optical element including a holographic reflective surface mounted adjacent and parallel to said common support substrate and light modulation means disposed adjacent said holographic reflective sur14

face for selectively blocking and passing light beams from reflecting from said holographic reflective surface at individual pixel positions thereof; and additionally comprising,

b) means for switching said light modulation means on and off at said individual pixel positions thereof to determine which ones of said light detecting means receive said reflected light beams whereby the sequence of said elements receiving and processing said signals is determined.

34. In a computer including a memory for holding a sequence of instructions to be executed, logic for accessing the instructions in sequence, logic for determining for each instruction a function to be performed and an effective address thereof, and logic for executing each instruction, the improvement wherein:

a) the logic for executing instructions comprises:

a plurality of individual elements on a common support substrate optimized to perform certain logical sequences employed in executing instruction; and

b) the computer comprises:

element selection logic means connected to the logic determining the function to be performed for each instruction for determining a class of each function and for causing the instruction to be executed by those of said elements which perform those of said logical sequences affecting the instruction execution in an optimum manner, said element selection logic means including means for accepting dynamic inputs designating changes in an operating environment of the computer and means for changing the ones of said elements which execute each instruction as a function of said dynamic inputs whereby instruction execution is affected in an optimum manner for the present dynamic conditions.

35. A computer comprising:

- (a) a memory for holding a sequence of instructions to be executed;

- (b) logic for accessing said instructions in sequence;

- (c) logic for determining for each said instruction a function to be performed and an effective address thereof;

- (d) a plurality of individual elements on a common support substrate optimized to perform certain logical sequences employed in executing said instructions; and.

- (e) element selection logic means connected to said logic determining the function to be performed for each said instruction for determining a class of each function and for causing the instruction to be executed by those said elements which perform those associated said logical sequences affecting the instruction execution in an optimum manner, said element selection logic means including means for accepting dynamic inputs designating changes in the operating environment of the computer and means for changing the ones of said elements which execute each instruction as a function of said dynamic inputs whereby instruction execution is affected in an optimum manner for the present dynamic conditions.