. 1

## An Overview of MCC and its Research

Dr. Stephen F. Lundstrom

Consultant PARSA (415) 723-0140

Consulting Associate Professor, Electrical Engineering Computer Systems Laboratory Stanford University

## Microelectronics and Computer Technology Corporation (MCC)

**a**/

l

The Microelectronics and Computer Technology Corporation is a cooperative enterprise whose mission is to strengthen and sustain America's competitiveness in information technologies. Their objective is excellence in meeting broad industry needs through application-driven research, development and timely deployment of innovative technology.

MCC was chartered in August, 1982. Austin was selected as its headquarters in May, 1983 and research was underway by late that year.

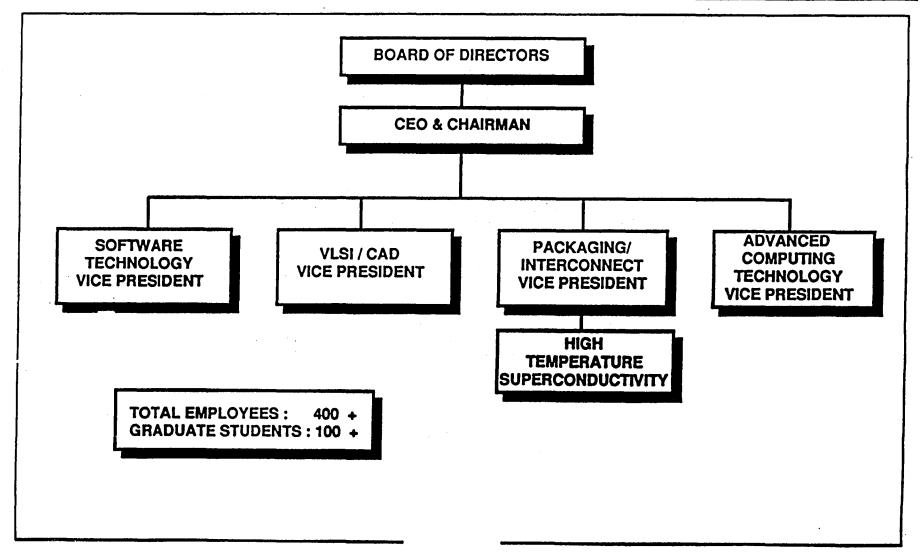

#### **Research** Programs

#### Software Technology

To develop technology which will bring about extraordinary increases in software productivity, quality and life-cycle costs

VLSI/Computer Aided Design

To provide a means to greatly reduce the design time and improve the resulting design quality of complex micro-electronic circuits and systems

#### Packaging/Interconnect

To improve shareholder competitiveness in electronic manufacturing

#### **Electronic Applications of High Temperature Superconductors**

To understand the implications and potential impact of newly discovered superconductivity materials to electronics

#### Advanced Computing Technology

1

To develop technologies that will allow MCC shareholders and their customers to design very complex knowledge-based systems for any enterprise that is centered on information

Ł.,

## **MCC ORGANIZATION & STAFFING**

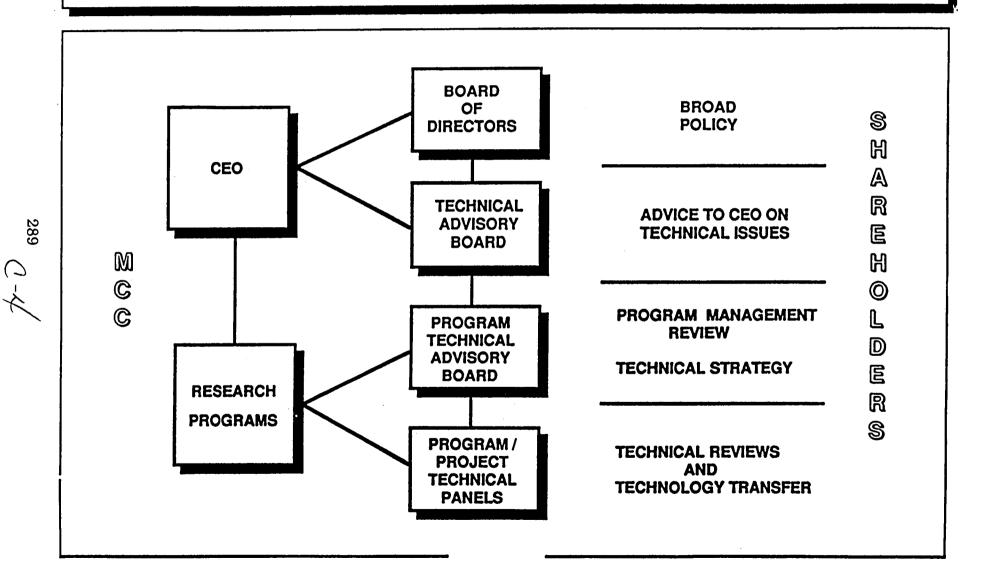

## MCC Governance

#### **Board of Directors**

One director from each of the shareholder companies. The board sets broad policy and meets regularly to consider important new strategic directions.

#### **Technical Advisory Board**

One senior technical advisor or manager from each of the shareholder companies. The TAB reviews the general technical progress of MCC and identifies new and emerging directions which should be considered for new programs. Provides advice to the CEO on technical issues.

#### Program Technical Advisory Board

Each of the research programs has an associated Program Technical Advisory Board which consists of members from each of the companies who participate in sponsoring the research in that program. This board monitors progress of the program and recommends technical strategy with respect to the directions of the program.

### Program / Project Technical Panels

3 1 1 1 1 1

Panels associated with each research program conduct detailed reviews of research progress and assist in identifying technology transfer opportunities in the participant organizations.

1

## MCC GOVERNANCE

### SHAREHOLDERS

MCC shareholders each own one share of stock in MCC, participate on the Board of Directors, and in at least one of the research programs. Participation in a research program involves sharing research costs with the others who are also participating, providing at least one researcher as a program liaison or assignee (who work as Members of the Technical Staff or in management positions, depending on their qualifications), and closely following the research progress in order to transfer technology back to the shareholder organization as quickly as possible. Shareholder participants have paid-up licenses for use of the technology developed in the programs in which they participate. They have general knowledge of activities in other programs (through the TAB.)

$\mathcal{N}^{+}$

1 2

1

Į

ſ

1

J

ł

1

**Shareholders**

· 1

**Advanced Micro Devices** Bellcore Boeing **Cadence Systems Control Data Digital Equipment** Eastman Kodak **General Electric Harris Corporation** Hewlett-Packard Honeywell Hughes/GM Lockheed Martin Marietta Motorola National Semiconductor NCR Corporation **Rockwell International** Westinghouse **3m Corporation**

### ASSOCIATES

The MCC Associates Program offers a unique opportunity for U.S. and Canadian firms and organizations to participate in the MCC effort short of full-fledged equity participation. The Associates become part of the MCC community of world-class researchers, high technology corporations and supporting organizations committed to maintaining North American competitiveness in the global technology marketplace. For a modest participation fee, the Associates are kept abreast of progress in the MCC research programs and global technology developments. Associates may participate as non-equity participants in any of the research programs. The Associates Program opens the MCC effort to as many other organizations as possible in a pro-competition, pro-cooperation spirit.

MCC Associates membership offers qualification to join the MCC research programs as a non-equity participant. MCC is being restructured to allow more selective and lower cost ways of participating in their research. The basic differences between Shareholders and Associates are the Shareholders have governance rights over MCC and receive distributions of royalty income from third-party technology licensing. Associates have limited governance rights only for those projects in which they have elected to participate. Specific rights to technology for both Shareholders and Associates are detailed in the Research and Development Agreement for each program or project.

MCC Associates are invited to two or three seminars a year - designed specifically for the Associates - for a detailed look at progress in the MCC Technical Programs. These events provide an excellent opportunity to meet the researchers for a more in-depth assessment of the technology. Special meetings with researchers can be arranged from time to time.

MCC Associates have access to all proprietary technology monitoring and forecasting products of the MCC International Liaison Office. The ILO produces a highly-regarded monthly Newsletter on foreign technology developments, maintains an on-line database on foreign technology, writes occasional detailed technical reports on particular foreign technologies of interest and translates a large volume of Japanese-language technical papers from its unique database of Japanese technical literature. The ILO is in frequent contact with MCC Shareholders and Associates to answer their specific questions. The ILO can save an Associate a substantial part of the overhead of monitoring foreign technologies or advise Associates on how to establish their own monitoring programs. The ILO is also sponsoring a technology forecasting program, focussing on user needs for technology 5 to 10 years out.

1

1

1

{

1

ſ

### <u>Associates</u>

Allied-Signal, Inc. **Apple Computer Dell Computer Corporation E.I. Dupont Denemours E-Systems General Dynamics** LTV Missiles and Electronics Group Magnavox Government and Industrial Systems Mitre National Security Agency Northrop **Olin Corporation Power Electronics Application Center** Software Engineering Institute Sun Microsystems **Symbolics Texas Instruments** Tracor TRW **United Technologies**

## **PACKAGING / INTERCONNECT PROGRAM**

Packaging/Interconnect refers to the process of assembling integrated circuits into systems and providing the systems with power and cooling. Recently, rapid advances in integrated circuit technology have caused many of today's packaging and interconnect techniques and processes to become obsolete. New technologies are needed to assure that the potential of complex circuits is realized.

The aim of MCC's Packaging/Interconnect (P/I) Program is to develop processes for yielding high performance at low cost, thus contributing to the competitiveness of MCC shareholders. The overall mission of the P/I Program is to provide U.S. semiconductor, materials, component and systems companies with superior technology through sharing of talent and material resources. The work includes the processing of ceramics and plastics, deposition of electrical conductors, development of bonding metallurgies, thermal management, laser-processing, and thin-film fabrication. It also includes the development of test technology.

The P/I Program will develop technology which is directed toward a ten-million gate computer/signal processor which can be packaged, assembled and tested at a cost of less than \$1,000. This would double the performance of today's supercomputers at a small fraction of their cost. The technology will be completed and transferred to the shareholders by the end of 1992.

The Packaging/Interconnect Program is divided into four areas: a core and three satellites. Core research projects are longer range and intended to provide shareholders with a window on future technology, proving concepts and providing valuable know-how. Current satellites are:

1

T

ł

I

1

ſ

Bonding and Assembly Development

1 1 1

I

- Multi-Chip System Technology

- Interconnect Technology

# MCC / Packaging/Interconnect

(-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (-, -) + (

- Enable electronic packaging to keep pace with rapid advances in chip integration and speed

- Develop low cost, high performance and reliability, dual use technology

- Multi-chip modules provide improved performance at a lower cost and an increased reliability

- MCC P/I work in substrates, bonding, test and systems

## Performance Potential of Multi-Chip Packaging

The goal of the Multi-Chip System Technology Satellite is to solve several problems related to the application of multi-chip packaging. Issues that are being addressed include heat removal, power handling and regulation capabilities, high performance connections, and testing.

Within this satellite, the Quick Turn Around Time (QTAT) interconnect project is providing design and process for generic or programmable interconnect techniques using a standard "blank." The blank is later customized to specific applications within 24 hours of design completion. MCC P/I is developing both substrate and board level QTAT techniques, so that most packaging levels within a system may be implemented more rapidly and at a lower cost. The project will allow wiring densities up to 500 lines per inch. This compares to current technologies which allow wiring densities of less than 100 lines per inch.

The satellite is conducting technology integration studies, is developing technology in a Chip on Substrate Test (COST) project which will verify that electrical objectives of the interconnect technology are met, and is developing liquid-cooled heat exchangers which can be integrated with MCC TAB (Tape Automated Bonding) and substrate technologies in a multi-chip module. The liquid-cooled heat exchangers will remove 50 watts of heat per square centimeter with low pressure and low flow requirements with either water or organic liquids. Novel air cooling technology which permits the removal of 30 watts of heat per square centimeter has already been developed.

ł

Î

}

]

ſ

1)

(1,1), (2,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1), (1,1),

# Performance potential of Multi-Chip Packaging

- improve system performance, reliability and cost

- chip technologies are too costly

- don't solve performance and density

- do not address the major reliability factors

- reliability limiting parts

- interconnection and packaging

- substantial improvement possible

- high density chip-on-board

- centimetres to mm.

### CONCLUSIONS (P&I)

Packaging and Interconnect continues to be the main gating factor to achieving cost effective systems. Packaging and Interconnect technology is the primary limitation to speed, reliability, testability, and affordability. Therefore, MCC believes that P&I will be a dominant force in the 1990's which will contribute to the competitiveness of the sponsors of the P&I program. The MCC P&I program will continue to emphasize multichip modules with vertically integrated R&D which addresses the issues of design, fabrication, assembly and test. The result is expected to be computers that are fast (3 ns cycle time), large (10 million gate) and low cost (\$5000.)

٦ ۱

}

1 1

1

5 ) [

J

J

## Conclusions

(-1, -2) + (-1, -1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1, -1) + (-1,

- PI continues to be main gating factor to cost effective systems

- PI limits speed, reliability, testability, and affordability

- It will be dominant force in the 1990's

- MCC approach emphasizes MCM

- Vertically Integrated R&D to participants

- Design, Fabrication, Assembly & Test

- Computers that are fast (3 ns cycle time), large (10 million gate) and low cost (\$5000)

## THE MCC CAD PROGRAM

## GOALS

The complexity of integrated circuits (ICs) continues to increase by as much as 50 percent per year. By the mid-1990s, complex ICs will contain upwards of 10 million devices and the resulting systems will be at least an order of magnitude more complex. This trend continues to affect chip and system makers alike. Electronic system manufacturers and IC suppliers are now designing ICs that have rapidly decreasing line widths and employ increasingly complex processes. In order to remain competitive in the next decade, these companies demand a shorter time-to-market for new products and require lower relative design costs than they have today. Breakthroughs in both CAD application tools and systems are required.

The MCC CAD Program performs state-of-the-art research into CAD tools and systems that will deal effectively with these technology challenges. The program provides computer-aided design tools and an integrating CAD system framework to its participants, which will help them resolve key design time, quality, and resource bottlenecks in the design of complex integrated circuits and electronic systems.

To carry out this objective, the CAD Program identifies targets of opportunity for its research and development (R&D) projects. The CAD Program only undertakes R&D efforts in which CAD technology from other sources available to the participant (CAD vendors, universities, internal participant projects) is projected to be inadequate. MCC monitors new CAD developments in the commercial arena and within universities to target opportunities. The CAD Program also acquires and evaluates the most current commercial tools. MCC CAD constantly evaluates new and ongoing R&D projects from other organizations and monitors its own projects to ensure that at least one of the following criteria is met at the time the company delivers software to its participants: (1) The CAD tool or system to be produced will be functionally superior to software available from other sources to reduce design time and/or cost, or (2) The CAD tool or system will be more cost effective to the MCC CAD participants than other sources of that technology.

I

1 1

i de la companya de la

## THE MCC CAD PROGRAM

(1,1) = 1 = (1,1) = (1,1) = (1,1) = (1,1) = (1,1) = (1,1) = (1,1) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) = (1,2) =

GOALS

- Develop a "<u>best in class</u>" CAD framework that facilitates development and execution of native tools while providing easy integration of external tools.

- Play a <u>leadership</u> role in the creation of <u>industry</u> <u>standards</u> for design data representation, tool management and communication, and other important CAD framework issues.

- Deliver <u>advanced CAD tools</u> in areas that will advance the state of design and are <u>not adequately</u> addressed by commercial efforts.

## THE MCC CAD PROGRAM

## Short Term Plans

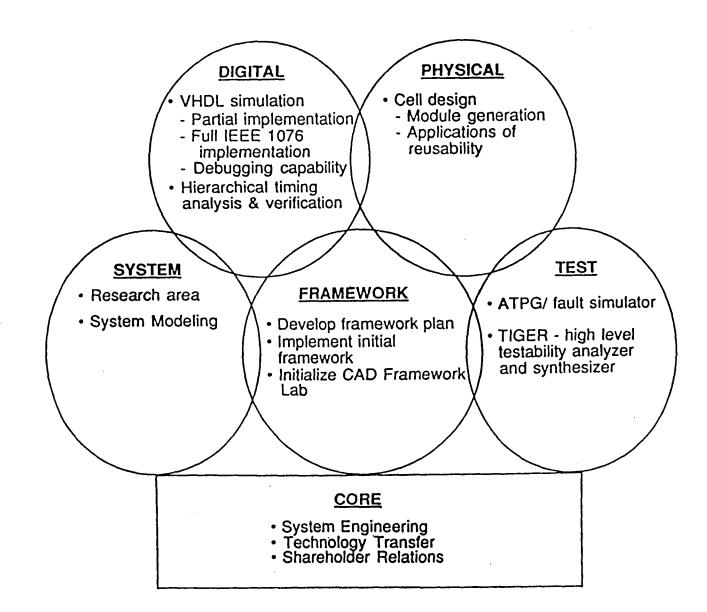

MCC organizes its CAD Program resources as a Core and four Satellites: System Design, Digital Design, Test Design and Physical Design. Each area has its defined targets of opportunity that result in short and long term goals. The responsibilities of the Core include development of a "best-in-class" CAD framework, coordination of technology tracking and forecasting activities, and code release preparation for all CAD Program deliverables. In addition, a system engineering function integrates the framework and individual application tools.

Each of the four satellites concentrates on a specific range of tasks in the design process. The System Design satellite addresses high-level problems of designing multi-chip systems, starting from informal requirements or specifications and evolving to component design specifications.

Projects in the Digital Design satellite help create and verify gate-level design, given a system architecture as an input. Current projects in this satellite include: VHDL analysis and simulation tools, hierarchical timing analysis, and mathematical verification of design correctness.

Projects in the Physical Design satellite take a functionally-verified, gate-level description as input and create a mask-level IC design. The satellite continues its work on the C Module Editor (CME) tool, a symbolic IC layout system that employs a unique graphical programming paradigm and a powerful compaction algorithm. The CME is design-rule independent. The Physical Design satellite is also addressing the layout synthesis problem.

The Test satellite focuses on the need to rapidly generate tests for complex systems. Current projects include a comprehensive fault simulation/automatic test pattern generation (FS-ATPG) tool that incorporates key new algorithms to handle high complexity, and the Testability Insertion Guidance ExpeRt (TIGER), a knowledge-based expert system that guides the designer to improve a design's testability at the register-transfer level and above.

) [ ]

I

1

##

# THE MCC CAD PROGRAM

SHORT TERM PLANS

## SOFTWARE TECHNOLOGY PROGRAM

Most large, complex computer systems of the future will be **distributed systems**. In a widely distributed network of hundreds - even thousands - of low-cost, high-performance individual workstations, data can be shared, available, and correct, when and where it is needed. These systems will offer two dramatic benefits:

- Teamwork and cooperation. The distributed network will provide tools that greatly assist users in planning, coordinating, and managing resources including human resources.

- **Reliability.** The effective replication and management of shared data will ensure that a breakdown in one part of the distributed network does not significantly interfere with the smooth functioning of another.

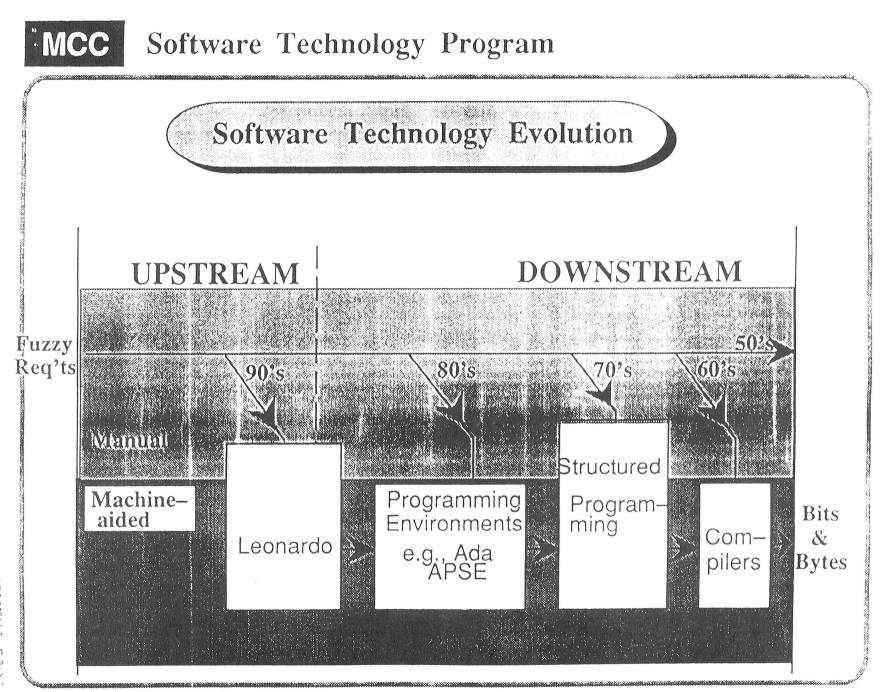

Other work in Software Technology focused on **downstream** activities. Compilers were developed in the 1960s. Structured programming was the focus of the 1970s. Programing environments was the new major issue of the 1980s.

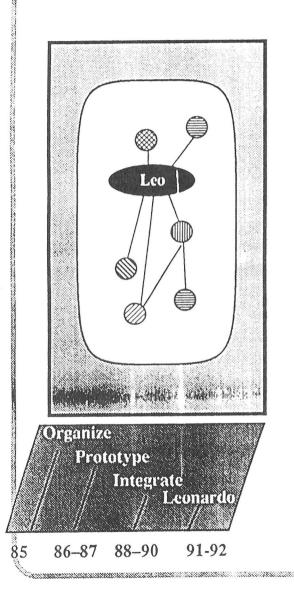

In creating *Leonardo*, STP is focusing its efforts on the *upstream* of the software systems design process. Upstream activities encompass the period from a project's "fuzzy requirements" phase, through its design, to the point at which formal specifications can emerge.

These early, creative phases of design offer great leverage in ensuring a given project's eventual success. Downstream outcomes are, in fact, determined by upstream decision - decisions about customer needs and design assumptions, about resources and components, and about how the system's vision matches its requirements. Indeed, study after study reveals that over half of the development effort typically is spent on these and other upstream activities.

Yet currently, the upstream remains unquantified, unarticulated, and poorly addressed by technology. Management and technical tasks are seldom coordinated; communication is haphazard and unfocused. The price, in both human and economic terms, is this: fixing design defects and adding functionality currently account for *over 80 percent* of the cost of maintaining a system once it is in operation.

*Leonardo* computer-aids the upstream, so that everybody involved in a complex system's design - developers, managers, and targeted users alike - can function as a coordinated, focused team. This unique environment promises extraordinary gains in the productivity of the designers and in the quality of the systems they produce.

1

ORIGINAL POOR QUALIT 1.2

## THE LEONARDO VISION

### · COORDINATING THE DESIGN TEAM

The group design of a typical, large complex software system requires the simultaneous efforts of many specialists working cooperatively. Like the system it is designing, this team is often widely distributed in space and time. Like the individual computer processes being created to drive the emerging system, the team must function smoothly.

In most large project teams, the issue of coordination tends to be minimized or ignored. Poor communication - both between processes and between members of the design team - is widely acknowledged to cause rework and inefficiency, and chasing new code-writing technology has not worked as the remedy of choice. The problem is this: until now, there have been no conceptual models of systems design coordination, much less the tools for achieving that coordination. Major work is underway at STP for ensuring that *Leonardo* provides both. Powerful hypermedia tools which represent data in an associative, rather than a linear, way - in graphical networks of nodes and links - have been developed. The data can be text, graphics, or synthesized speech. *Leonardo* includes tools which support the notions of *process teams* and *multiple-party process interactions.* Visual environments are available to edit the coordination scripts which organize the multi-design interactions are organized by allowing for explicitly written, graphically represented descriptions of the design process. Each member's "electronic desk" serves as an interface to the overall process and to the status of the member's current role in the organization. A graphical tools which allow design argumentation into a hypermedia network that can be constructed, analyzed, and edited by the design team members have been developed.

#### SUPPORTING THE SOFTWARE DESIGNER

· •

The software design process continues to be poorly understood - particularly the process of designing large, complex systems in project teams. Little empirical research has examined the cognitive foundation for this process or pinpointed specific components. No theories formally describe or organize the information used by designers. Consequently, information reused across the design process typically remains unidentified and is often redeveloped during a single project. STP conducts **empirical studies** to determine what design tasks must be supported in order for *Leonardo* to have maximum value for its shareholders. A major focus is **Computer-Aided Design Deliberation and Reuse**. One project is focusing on how a designer makes and records design decisions as the project progresses from requirements to code. A graphically oriented technology has been created to capture and represent information about a project's history and about the dependencies between system components. A **reuse** system provides the designer with two reusable libraries - a library of abstract design schemas and one of abstract algorithms. A design schema is the way in which early design structures are captured. The designer can pull up, edit and refine a design schema to pin down precise elements of the target system's architecture. Once these elements are defined, the *Leonardo* designer will use the abstract algorithm library to customize the abstract designs into code.

$(1) \quad (1) \quad (1)$

# MCC Software Technology Program

# The Leonardo Vision

- Integrated System Design Environment

- -Upstream Emphasis (Symbolic Comp.)

- -Prototyping & Simulation

- 1 Mission: Extraordinary Productivity& Quality

- 1 Long Range/High Risk Research

- 1 Team Focus

- 1 Visual/Human Orientation to Tools

- Distributed/Embedded Target Systems

- Reuse of Designs

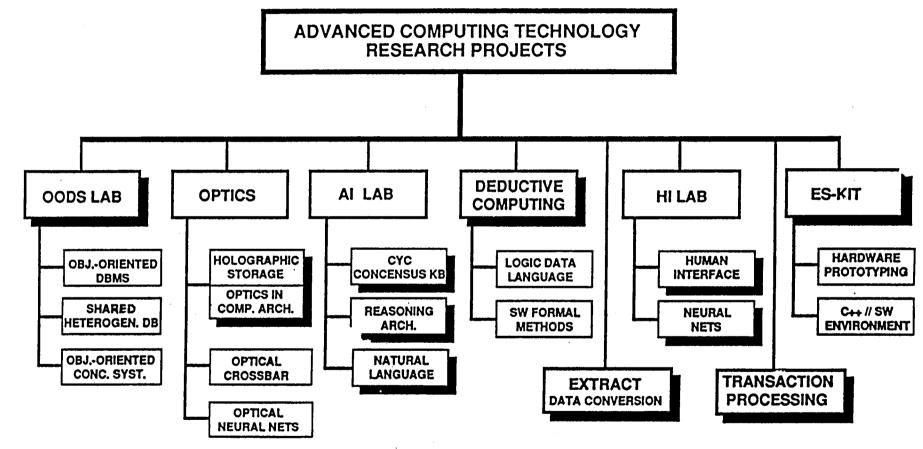

## ADVANCED COMPUTING TECHNOLOGY (ACT) Projects and Organization

#### Organization

Shareholders and Associates can choose to participate in each of the programs shown as shaded blocks in the figure. Recently, the Neural Nets program has been moved to the same level as the HI Lab in the organization.

### OODS (Object Oriented and Distributed Systems) LAB

The ODBS project provides rich database software capabilities to both object oriented programming environments and data-intensive, symbolic applications, such as CAD/CAM, artificial intelligence, and office information systems. The ODBS project has already delivered ORION, a prototype of an object oriented database system on a single workstation. This system is being extended into a distributed database. In addition, the group is working to design and demonstrate a high-performance system architecture to support the concurrent object model by exploiting parallel processing opportunities.

#### OPTICS

The optics group is conducting research into the application of optics technology in high performance computing systems. These studies are currently focused in high performance interconnects for highly parallel systems and a high capacity, low latency holographic storage technology (with no moving parts.)

#### AI LAB

This group is generating a very large knowledgebase called CYC, that contains a foundation of general (encyclopedic) and common-sense knowledge. The work in Reasoning Architectures is creating expert system shells that provide rich development facilities for the language as well as efficient run-time environments. The Knowledge Based Natural Language group is working to extend computer interaction and understanding capabilities to include unrestricted natural language.

#### **DEDUCTIVE COMPUTING**

This group has designed and implemented a Logic Data Language (LDL). This is a logic-based language intended for data and knowledge intensive applications. The LDL system combines the expressive power and the supporting technologies of logic programming and relational databases. Future extensions will support richer knowledge representation primitives and constraint-based programming.

#### HUMAN INTERFACE

The Human Interface Lab is focused on dramatically improving the *usability* of complex systems. The mission of the lab is to develop the scientific and technological foundations for principled and efficient construction of effective interfaces. HITS, a Human Interface Tool Suite, provides tools to support the design of intelligent, multimedia interfaces.

#

## **ACT PROJECTS & ORGANIZATION**

**NOTE : PROJECTS SHOWN IN SHADOW BOXES ARE SEPARATELY FUNDABLE**

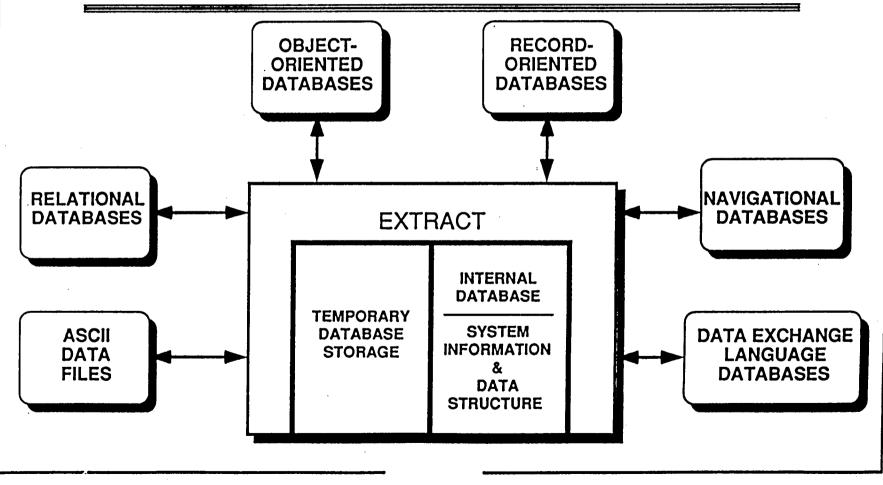

## DATA CONVERSION (EXTRACT) Project Focus

The EXTRACT project has developed tools which allow data conversion or migration from one or more databases and file structures into others. The user describes the databases or file structures to be connected and the data to be handled with a formal notation. The system then automatically generates code which connects the EXTRACT system to those databases and file structures. The EXTRACT system includes a temporary database storage and automatic management of the movement of data from one place to another. The work of this project is nearly completed.

· ]

# DATA CONVERSION (EXTRACT)

**PROJECT FOCUS**

## ALLOW DATA CONVERSION / MIGRATION FROM ONE OR MORE DATABASES / FILE STRUCTURES INTO OTHERS

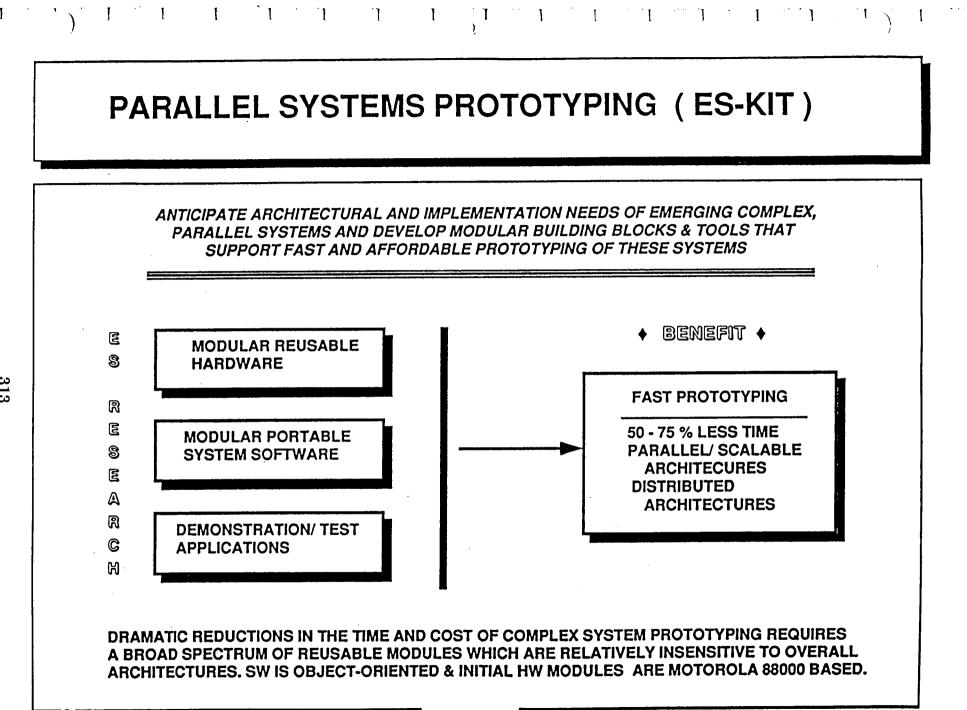

### PARALLEL SYSTEMS PROTOTYPING (ES-KIT)

The Experimental System Builders Kit (ES-KIT) group is developing technologies which allow rapid, low-cost prototyping of experimental high-performance computing systems. The ES-KIT is a set of compatible hardware and software technologies that can be used to very quickly construct unique high-performance systems - parallel systems in particular. The hardware modules include processor, memory, hard disk, message-passing communications, and instrumentation modules. The initial modules are Motorola 88000 based. New modules based on the Intel i860 are under development. The software support includes a parallel C++ compiler, UNIX operating system modules which connect the hardware modules to the UNIX environment in a workstation host, software instrumentation insertion support, and tools to support the presentation of data collected from builtin hardware and software instrumentation. The work of this group has been sponsored by DARPA and is currently being distributed to other researchers around the United States for use in a wide variety of projects.