·in.

### GALLIUM PHOSPHIDE HIGH TEMPERATURE DIODES\*

R. J. Chaffin, Division 5133 L. R. Dawson, Division 5154 Sandia National Laboratories Albuquerque, New Mexico 87185

### SUMMARY

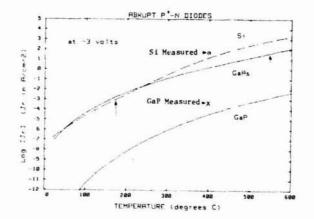

The purpose of this work is to develop high temperature (>300°C) diodes for geothermal and other energy applications. A comparison of reverse leakage currents of Si, GaAs and GaP is made. Diodes made from GaP should be usable to >500°C. An LPE process for producing high quality, grown junction GaP diodes is described. This process uses low vapor pressure Mg as a dopant which allows multiple boat growth in the same LPE run. These LPE wafers have been cut into die and metallized to make the diodes. These diodes produce leakage currents below  $10^{-3}$ A/cm<sup>2</sup> at 400°C while exhibiting good high temperature rectification characteristics. High temperature life test data is presented which shows exceptional stability of the V-I characteristics.

#### I THEORY

The choice of semiconductor material used to fabricate diodes is dominated by the reverse leakage characteristics desired. The reverse leakage current density of an abrupt  $P^+$  -N junction is given by:<sup>1,2</sup>

$$J_{R} = e \sqrt{\frac{D_{p}}{\tau_{p}}} \cdot \frac{n_{i}^{2}}{N_{p}} + \frac{en_{i}W}{2\tau_{o}}$$

(1)

where  $D_p = hole$  diffusion coefficient

- $\tau_p$  = hole lifetime (in the n region)

- $\tau_{0}$  = depletion region carrier lifetime

- n<sub>i</sub> = intrinsic carrier concentration

- e = electronic charge

- $N_{D} = donor concentration$

- W = depletion layer width

The first term on the right side of Eq. (1) represents the diffusion of minority carriers within a diffusion length of the junction which produces a reverse leakage current. This component is independent of bias. The second term on the right of Eq. (1) represents generation-recombination current in the depletion region and is dependent on bias through the depletion width. Generally the recombination current term will dominate at low temperatures and the diffusion current term will dominate at higher temperatures. The crossover point is primarily dependent on the semiconductor band gap and carrier lifetime. The appropriate parameters for Silicon (Si), Gallium Arsenide (GaAs) and Gallium Phosphide (GaP) were used to evaluate Eq. (1) as a function of temperature for the three materials. The results for reverse leakage current density at -3V are shown in Figure 1. The arrows on the curves mark the crossover temperature of the two components of leakage current. For temperatures to the left of the arrows generationrecombination current dominates and diffusion current dominates at temperatures to the right.

\*This work sponsored by the U. S. Department of Energy (D.O.E.) unler Contract DE-AC04-/6-DP00789 The figure shows that for temperatures in the  $20-300^{\circ}$ C range GaAs and Si have similar leakage currents. (The high depletion region generation-recombination current in GaAs offsets its wider bandgap.) Calculations show that GaP diode reverse leakage should be dominated by generation-recombination current up to  $650^{\circ}$ C and is at least 5 orders of magnitude lower than Si. Hence it can be seen that GaP should be an excellent choice for high temperature semiconductor devices.

This fact is demonstrated in Figure 2. This figure shows a V-I characteristic of a Sandia-made  $P^+$  -N GaP diode at 400°C. The leakage of the GaP diode is not discernable on the figure. The measured current density at -3V and 400°C was 7 x 10<sup>-4</sup> amp/cm<sup>2</sup> for the GaP diode.

Figure 2. CaP grown junction diode characteristic at 400°C. (Horizontal = 5V/div, vertical = 1 mA/ div.)

# II DIODE FABRICATION

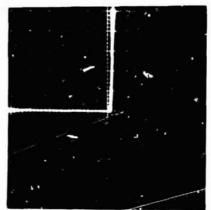

To realize a device whose operation will not be degraded by the high density of chemical impurities and structural defects present in typical bulk GaP substrate material, the all-epitaxial structure of Figure 3 is used. The N side of the junction is

<sup>&</sup>quot;A. U. S. Department of Energy facility.

lightly doped to provide as high reverse breakdown voltage as possible. The P side can then be relatively highly doped to facilitate ohmic contacting of the top surface.

This structure was prepared using liquid phase epitaxy for the growth of both layers during a single growth cycle.

Figure 3. Grown Junction GaP Diode.

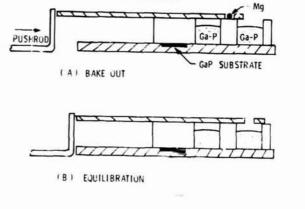

The growth apparatus shown in Figure 4 is a sliding boat assembly constructed from high purity graphite. The body of the assembly contains wells for two growth solutions, one for the growth of the N layer, a second for the growth of the P layer. To maintain background (no intentional doping) carrier co..centration as low as the 1 x  $10^{16}$  cm<sup>-3</sup> level desired for the N layer, the growth temperature used was 850°C. At this relativel. low growth temperature, Si contamination of the growin solutions from the quartz walls of the system is minimal. To ensure that no cross contamination of the N solution occurs from the heavily doped P solution, relatively non-volatile Mg is used as the P dopant in place of the highly volatile In normally used to dope GaP P type. 3 Since Mg possesses a stable oxide, provision is made for adding this depant after a pre-bake cycle removes residual oxygen from the growth solutions, as in Figure 4A. The system is then permitted to equilibrate at the growth temperature (850°C) for 2 hours, as in 4B, after which the slider is translated to bring the GaP substrate into contact with the first growth solution, as in 4C. Cooling then causes the solution to become super-saturated and epitaxial growth occurs on the substrate. When the N- layer is sufficiently thick, the slider is again translated to bring the substrate in contact with the second melt for growth of the P layer, after which further translation of the slider separates the substrate from the liquid.

### The diode metallization system used was:

- P<sup>+</sup> contact Be/Au (3000Å ∿ 1% Be by weight)

- (7 mil dot) followed by 3000Å of pure Au

- (vacuum evaporated)

- N contact The contact was sputtered (full surface) in the following sequence: Au/Ge (8P/12) 1000 Å, Au  $\sim 250$ Å, Ni  $\sim 600$  Å, Au  $\sim 4000$  Å, Contacts annealed at 450°C (10 minutes) in H<sub>2</sub>

The first lot of diodes tested were mounted in ceramic flat pack headers (N<sup>+</sup> side down) with a high temperature, polymide silver loaded adhesive. Gold wires (1.5 mil) were used to make contact to the top of the die. However, this configuration was found to be unsatisfactory due to deterioration of the adhesive at high temperatures. The scheme finally chosen was a

stress-free configuration using 1.5 mil diameter gold wires bonded to each side of the chip. This was done to eliminate any die attach stresses or material interactions due to the header attachment scheme. These devices are shown in Figure 5. It should be emphasized that the mounting configuration shown in Figure 5 is not propose ' for fielded devices, but rather it is a scheme used to remove any contribution of header stress or bonding agent reactions for testing device characteristics.

Figure 4. Liquid Phase Epitaxial Growth System.

Figure 5. Stress-Free Diode Mount.

# III DIODE CHARACTERISTICS

A typical I-V characteristic of a GaP diode was shown in Figure 2. The breakdown voltage was measured to be 90V at 400°C; the breakdown characteristic remains fairly sharp even at this elevated temperature. The fact that the leakage current is larger than the value predicted (see Figure 1) means that there is some leakage at the sawed edges of the dir.

The zero bias capacitance of the 15 mil square chips was measured to be 22 pF. This corresponds to a 0.56 µ zerc bias depletion width.

## IV ENVIRONMENTAL TESTS

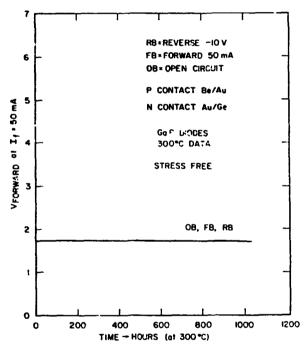

The GaP diodes were subjected to a life test under bias. Three bias conditions were used; forward bias (5 mA), reverse bias (-10 V) and open circuit (zero bias). The diodes were placed in ovens at  $3CO^{\circ}C$ . The devices were not sealed and the oven contained room air. The parameters of the diodes were checked as a function of time in the oven.

The results of this test are summarized in Figure 6. This figure shows that no detectable degradation in series resistance occurred in any of the three bias states. The room temperature reverse leakage did show a slight increase, increasing from nominally  $10^{-2}$  amps to  $10^{-8}$  amps after 991 hours at  $300^{\circ}$ . There was not a strong correlation between bias state and leakage increase. The reverse leakage at  $300^{\circ}$ C showed a slight <u>decrease</u> after 991 hours. This stability in diode parameters is interpreted as meaning that the diode metallizations and junction dopants are stable at  $300^{\circ}$ C with bias for atleast 1000 hours.

Figure 6. 300<sup>O</sup>C Life Test Data on Stress Free GaP Diodes.

### V CONCLUSIONS

This paper has presented data on galliumphosphide, grown junction diodes for high temperature applications. Information on fabrication methods were presented. Evaluation data shows: good low leakage rectification characteristics at  $400^{\circ}$ C and stable junction and metallization parameters at  $300^{\circ}$ C for at least 1000 hours. The only problem encountered was the "high temperature" polyimide adhesive used to bond the diode chips to the headers. A new eutetic chip bonding procedure is presently being developed to solve this problem.

# "I ACKNOWLEDGEMENTS

This work was supported in part by the Dept. of Energy, Division of Geothermal Energy. The authors would also like to thank J. B. Snelling and T. A. Plut for their assistance in tabricating and testing the devices.

1

# REFERENCES

- A. S. Grove, <u>Physics and Technology of Semi-</u> <u>conductor Devices</u>, John Wiley & Sons, NY 1967, p. 174.

- S. M. Sze, <u>Physics of Semiconductor Devices</u>, John Wiley & Sons, NY, 1969, p. 103.

- L. R. Dawson, "Doping Control in the LPE Growth of GaP", paper presented at <u>Electronics Materials</u> Conference, Cornell Univ., 6/24/80.

ţ