brought to you by CORE

# NASA TECH BRIEF

NASA Pasadena Office

NASA Tech Briefs announce new technology derived from the U.S. space program. They are issued to encourage commercial application. Tech Briefs are available on a subscription basis from the National Technical Information Service, Springfield, Virginia 22151. Requests for individual copies or questions relating to the Tech Brief program may be directed to the Technology Utilization Office, NASA, Code KT, Washington, D.C. 20546.

# Trigger Circuit Forces Immediate Synchronization of Free-Running Oscillator

#### The problem:

Many devices powered by an externallysynchronized inverter require it to operate without loss of synchronism. One example is the 2,400-Hz inverter flown on spacecraft, powering onboard gyroscopes, flight data subsystems, science data tape recorders, and telemetry systems. Any glitch fouling inverter synchronization could result in loss of significant data, a condition most likely to occur during periods of power source switchover from one unit to another.

#### The solution:

The free-running frequency of a new integratedcircuit (IC) oscillator may be higher, lower, or the same as that of the sync pulse and is always synchronized by the first clock pulse.

#### How it's done:

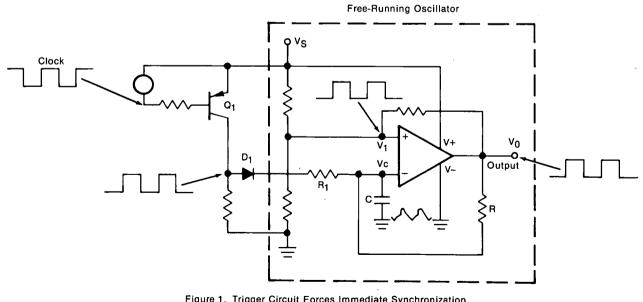

The oscillator is shown in Figure 1. The input triggering from the clock source resets the charge level on the timing capacitor C to a fixed positive level above ground potential. When transistor  $Q_1$  is cut off, the oscillator operates in the free-running mode. Back-biased diode  $D_1$  isolates the oscillator from spurious transients.

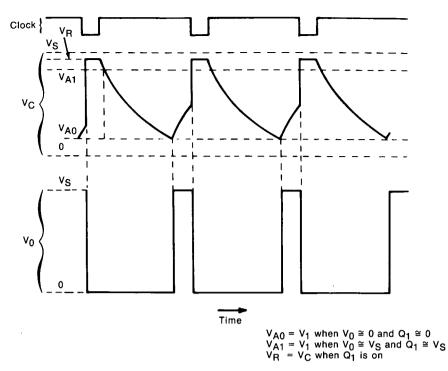

A negative-going clock pulse applied to the base of  $Q_1$  turns it on. Capacitor C is charged from supply voltage V<sub>S</sub> through D<sub>1</sub> and resistor R<sub>1</sub>. The charge on the capacitor rises to voltage level V<sub>R</sub>. This occurs regardless of the previous charge level on the capacitor. Since V<sub>R</sub> is initially set at a level higher than V<sub>A1</sub> (Figure 2), the output voltage shifts to ground potential. After passage of the clock pulse, the capacitor discharges to V<sub>A0</sub>, causing the output

Figure 1. Trigger Circuit Forces Immediate Synchronization of Free-Running Oscillator

(continued overleaf) a

This document was prepared under the sponsorship of the National Aeronautics and Space Administration. Neither the United States Government nor any person acting on behalf of the United States Government assumes any liability resulting from the use of the information contained in this document, or warrants that such use will be free from privately owned rights.

Figure 2. Synchronization Waveforms of Free-Running Oscillator

voltage to shift up to a level almost that of VS.

The output voltage is driven to ground on the next negative-going clock pulse, and the cycle repeats. Applications of positive triggering may be useful in TV-camera and other circuits, for video recording, facsimile transmission and reception, and uninterruptible power supplies.

## Note:

Requests for further information may be directed to:

Technology Utilization Officer NASA Pasadena Office 4800 Oak Grove Drive Pasadena, California 91103 Reference: TSP75-10337

### Patent status:

NASA has decided not to apply for a patent.

Source: Satoshi Nagano of Caltech/JPL (NPO-13646)