brought to you by T CORE

## D/4-10203

Langley Research Center

NASA Tech Briefs announce new technology derived from the U.S. space program. They are issued to encourage commercial application. Tech Briefs are available on a subscription basis from the National Technical Information Service, Springfield, Virginia 22151. Requests for individual copies or questions relating to the Tech Brief program may be directed to the Technology Utilization Office, NASA, Code KT, Washington, D.C. 20546.

## Low-Temperature Electrostatic Silicon-to-Silicon Seals Using Sputtered Borosilicate Glass

A new method for sealing two silicon surfaces together produces an all-silicon package. The package has advantages which are especially important for compensating the effects of temperature upon piezoresistive and piezojunction sensors. The silicon members are hermetically sealed to each other at a temperature  $\gtrsim 500^{\circ}$  C. The process produces no measurable deformation of the silicon surfaces and is compatible with package designs of tight tolerance.

The surfaces of the silicon members to be sealed are polished, cleaned, and stripped of any residual oxide. They are then coated with sputtered borosilicate glass to a minimum glass thickness of approximately 4  $\mu$ m. Prior to sealing, each coated silicon substrate is annealed at 600° to 900° C. A slightly higher yield is obtained when this annealing is carried out in steam, but successful seals are formed after annealing in either nitrogen or oxygen.

Silicon-to-Silicon Electrostatic Seal Under Hermetic Test

To achieve the silicon-to-silicon electrostatic seal, a second polished silicon chip is alined in the desired orientation on top of the first silicon member, which is already coated with borosilicate glass. The combination is then heated and stabilized to a temperature of  $450^{\circ}$  to  $550^{\circ}$  C. A slowly-increasing dc voltage is then applied across the silicon-borosilicate glass-silicon sandwich, the uncoated silicon member being positively biased. After reaching a maximum voltage (50 V), the sandwich is left at the process temperature and the maximum voltage for 5 minutes. To complete the sealing operation, the substrate heater is removed, and the sandwich is returned to near room temperature before removing the voltage.

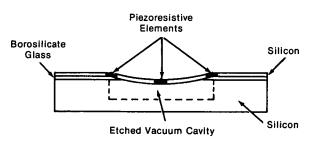

To test the hermeticity of such a seal, a number of silicon-to-silicon seals were prepared in which one silicon member of the silicon-borosilicate glass-silicon sandwich had a deep cavity etched part way through it. The second silicon member was then thinned to a total thickness of 0.025 to 0.1 mm (1 to 4 mils), and the sealing operation was carried out in a vacuum chamber at a pressure of approximately  $10^{-5}$  torr. Upon completing the seal and removing the unit from the chamber, atmospheric loading on the thin top member produced a visible depression above the cavity, as shown in the illustration.

Such an evacuated cavity has been measured as essentially leak free by helium leak testing. Even after 63 thermal cycles between  $+100^{\circ}$  and  $-40^{\circ}$  C, the unit showed no loss of dimple or measurable leak rate.

(continued overleaf)

This document was prepared under the sponsorship of the National Aeronautics and Space Administration. Neither the United States Government nor any person acting on behalf of the United States Government assumes any liability resulting from the use of the information contained in this document, or warrants that such use will be free from privately owned rights.

## Notes:

- 1. Seals have been made with glass coatings in the 10-mm to 20-mm thickness range without any prior annealing of the coated silicon substrates. Higher maximum sealing voltages can be tolerated with the thicker glass coatings without the danger of breakdowns.

- 2. Requests for further information may be directed to:

Technology Utilization Officer Langley Research Center Mail Stop 139-A Hampton, Virginia 23665 Reference: B74-10263

## Patent status:

NASA has decided not to apply for a patent.

Source: C. A. Hardesty Langley Research Center and A. D. Brooks and R. P. Donovan of Research Triangle Institute under contract to Langley Research Center (LAR-11589)

Categories: 08 (Fabrication Technology) 04 (Materials) 01 (Electronics - Components and Circuitry)

B74-10263