| TE AN                 | 10 SPA   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | provided by NASA Technical Rep    |

|-----------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

|                       | TO INASA | NATIONAL AERONAUTICS AND SPACE<br>Washington, D.C. 2054<br>Case-ERC-10285) PHASE CONTROL<br>CASE OF THE STATE OF THE S | N73-1620                          |

| U.S.<br>Y TO<br>N OF: | GP 13 P  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SA) Unclas<br>SCL 09C 00/10 52690 |

| ·                     | TO:      | KSI/Scientific & Technical Inf<br>Attention: Miss Winnie M. Mor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                   |

| •                     | FROM:    | GP/Office of Assistant General<br>Patent Matters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | l Counsel for                     |

| · .                   | SUBJECT: | Announcement of NASA-Owned U.S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5. Patents in STAR                |

|                       | and Code | lance with the procedures agreed<br>KSI, the attached NASA-owned U.<br>I for abstracting and announceme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | S. Patent is being                |

|                       | The foll | owing information is provided:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                   |

| ,                     | U.S      | , Patent No. : <u>3, 7/0</u> ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 329                               |

|                       |          | ernment or<br>porate Employee : <u>(1,5,0</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Goueenment                        |

|                       |          | plementary Corporate<br>rce (if applicable) :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                   |

|                       |          | A Patent Case No. : ERC-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0285                              |

|                       | NAS      | A Patent Case No. : <u>CKC<sup>2</sup>/C</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <u></u>                           |

Pursuant to Section 305(a) of the National Aeronautics and Space Act, the name of the Administrator of NASA appears on the first page of the patent; however, the name of the actual inventor (author) appears at the heading of column No. 1 of the Specification, following the words ". . . with respect to an invention of . .

ARTER KC1290eth

Elizabeth A. Carter Enclosure Copy of Patent cited above

# United States Patent 191

Mailloux et al.

## [54] PHASE CONTROL CIRCUITS USING FREQUENCY MULTIPLICATION FOR PHASED ARRAY ANTENNAS

- [75] Inventors: Robert J. Mailloux, Wayland, Mass. 01778; Paul R. Caron, Tiverton, R.I. 02878

- [73] Assignee: The United States of America as represented by the Administrator of the National Aeronautics and Space Administration

- [22] Filed: July 16, 1970

- [21] Appl. No.: 55,333

- 343/853 [51] Int. Cl......H01q 3/26

#### [56] **References Cited**

### UNITED STATES PATENTS

| 2,920,284 | 1/1960 | Beagles et al  |

|-----------|--------|----------------|

| 3,501,764 | 3/1970 | Mailloux et al |

# [11] 3,710,329 [45] Jan. 9, 1973

Primary Examiner—Benjamin A. Borchelt Assistant Examiner—Richard E. Berger Attorney—Monte F. Matt, Paul F. McCaul, Wilfred Grifka and John R. Manning

#### [57] ABSTRACT

The disclosure describes a phase control coupling circuit for use with a phased array antenna. The coupling circuit includes a combining circuit which is coupled to a transmission line, a frequency multiplier circuit which is coupled to the combining circuit, and a recombining circuit which is coupled between the frequency multiplier circuit and phased array antenna elements. In a "doubler" embodiment, the frequency multiplier circuit comprises frequency doublers and the combining and recombining circuits comprise four-port hybrid power dividers. In a generalized embodiment, the multiplier circuit comprises frequency multiplier elements which multiply to the Nth power, the combining circuit comprises four-port hybrid power dividers, and the recombining circuit comprises summing circuits. In a quadrupler embodiment, the multiplier circuit comprises frequency quadrupler elements, the combining circuit comprises four-port hybrid power dividers and the recombining circuit comprises two levels of four-port hybrid power dividers.

#### 20 26ł 25 180° HYBRID 180° HYBRID 180° HYBRID <u>23</u>a 2<u>3b</u> <u>23c</u> 21a 216 2lc 2ld 2ie X2 X2 X2 X2 X2 X2 180° HYBRID IBO° HYBRID 180° HYBRID 190 19b 19c 37b S 37n. si 37d-15 37 396 390 39d τí 2S<sub>1</sub> 2S2 0 PHASE 17 SHIFTER N73-16206 •11 40% TRANS-MITTER

.331/45

#### 13 Claims, 5 Drawing Figures

# PATENTED JAN 9 1973

3,710,329

SHEET 1 OF 4

BY Herbert (. Jam

ATTORNEY

ROBERT J. MAILLOUX PAUL R. CARON

PATENTED JAN 9 1973

3,710.329

FIG. 3

# PATENTED JAN 9 1973

INVENTORS ROBERT J. MAILLOUX PAUL R. CARON

**FIG. 5**

INVENTORS ROBERT J. MAILLOUX PAUL R. CARON 5

#### PHASE CONTROL CIRCUITS USING FREQUENCY MULTIPLICATION FOR PHASED ARRAY **ANTENNAS**

## **ORIGIN OF THE INVENTION**

The invention described herein was made by employees of the United States Government and may be manufactured and used by or for the Government for governmental purposes without the payment of any royalties thereon or therefor.

## **BACKGROUND OF THE INVENTION**

This invention relates generally to the art of coupling circuits used for phasing signals. More particularly, this invention relates to the art of phase control coupling circuits for phased array antennas.

In recent years, phased array antennas have been used with increasing frequency, particularly phased array antennas employing high frequency antenna ele- 20 ments such as slot antenna elements. A phased array antenna normally comprises a matrix of antenna elements which are arranged according to a pattern; for example, some phased array antenna elements are arranged in crossed columns to form a square. Each an- 25 tenna element in a phased array antenna usually handles a signal which is phase shifted from the signals handled by other antenna elements in the array. The reason for this is that a combined radiation field developed by a phased array antenna at a distant point 30 is the vector sum of radiation fields produced by individual antenna elements in the phased array. By properly controlling the respective phases of signals handled by phased array antenna elements, it is possible to concentrate a combined radiation field very 35 strongly in a desired direction. To do this, however, requires high accuracy of phase control between individual antenna elements.

Phase control of a phased array antenna is normally accomplished by an antenna coupling circuit. That is, a 40 transmitter or a receiver, depending on whether the system is transmitting or receiving, is coupled to the antenna elements of the phased array antenna through a power dividing chain which has phase shifting elements connected at some point or points in it. Many prior art 45 phase controllers employ phase shifters connected at the ends of power dividing chains, prior to their connections with the antenna elements. An example of such a phase control coupling circuit is disclosed in U.S. Pat. No. 3,480,958 to Tcheditch. Other prior art 50 signals which are separated from one another by highly phase controllers involve phase shifters connected in series along power dividing chains. An example of this type phase controller is found in U.S. Pat. No. 3,255,450 to Butler. The major difficulty with such 55 phase control coupling circuits is that they are not accurate enough. When a phase shifter is connected at each antenna element, the phase shifter must be coordinated with other phase shifters to achieve the proper phase coordination between the antenna elements. 60 When phase shifters are connected in series in power dividing chains, there is an additional problem in that errors are cumulative as signals travel along the power dividing chains.

Some sophisticated phase control circuits provide 65 relatively accurate phase control, such as the system described by Johnson in an article "Phased-Array Beam Steering by Multiplex Sampling," Proceedings of

the IEEE, Vol. 56, No. 11, pp. 1,801-1,811, November 1968. The difficulty with most such systems is that they require relatively expensive and generally "nonstandarized" components.

It is therefore an object of this invention to provide a novel phase control coupling circuit suitable for use with a phased array antenna.

It is a further object of this invention to provide a phase control coupling circuit which is accurate. 10

It is still a further object of this invention to provide a phase control coupling circuit which is relatively inexpensive.

It is yet another object of this invention to provide a phase control coupling circuit which is relatively uncomplicated and is generally composed of standardized components.

#### SUMMARY OF THE INVENTION

In accordance with the principles of this invention, a phase control coupling circuit suitable for use with a phased array antenna is provided. The antenna may be operating in either a transmitting or receiving mode. The phase control coupling circuit of the invention employs frequency multiplying elements to create multiplied signals (assuming the system is transmitting). The phase control coupling circuit then separates out, from these multiplied signals, antenna element signals which have desirable phase angles and respectively feeds them to the antenna elements of the phased array antenna.

More particularly, the phase control coupling circuit of the invention employs a first combining circuit which receives two signals (one signal having a zero phase angle and the other signal having a  $\theta$  phase angle) from a transmission line (assuming the system is transmitting), subdivides these signals into two groups of smaller signals, and combines the smaller signals in various ways so as to create a plurality of combined signals. Frequency multiplying elements respectively multiply each of the combined signals by a multiple N thereby creating a plurality of the combined signals. A recombining circuit recombines the "multiplied combined signals" in such a manner as to separate out signals which have phase angles equal to integers of N times  $\theta$ . Thus, a phase control coupling circuit employing the principles of this invention receives two signals separated by a phase angle and emits more than two accurate incremental phase angles.

#### **BRIEF DESCRIPTION OF THE DRAWINGS**

The foregoing and other objects, features and advantages of this invention will become more apparent from the following more particular description of the preferred embodiments of the invention illustrated in the accompanying drawings wherein:

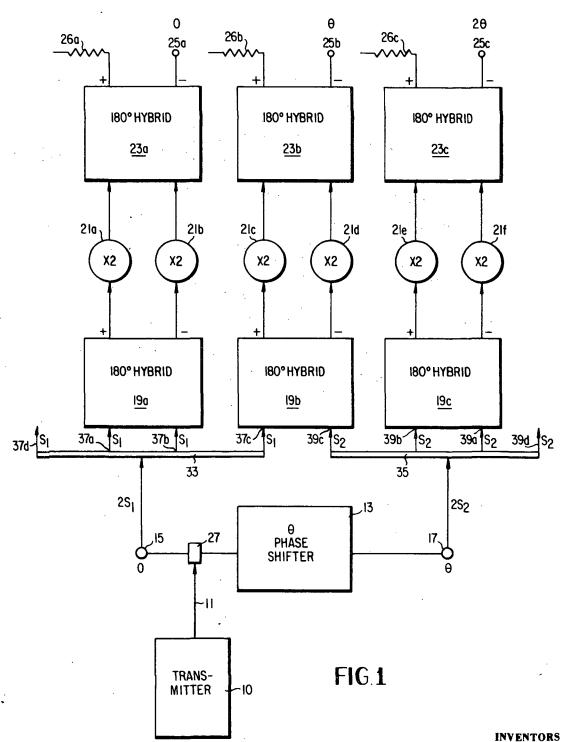

FIG. 1 is a block diagram of an antenna system which utilizes a doubler phase control circuit employing the principles of this invention;

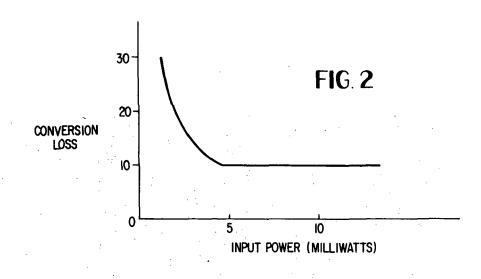

FIG. 2 is a graphical representation of a conversion loss characteristic similar to conversion loss characteristics of many commercially available doublers;

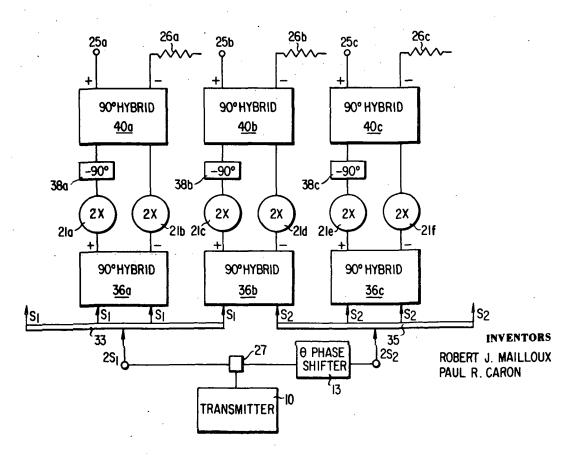

FIG. 3 is a block diagram of an antenna system which utilizes another doubler phase control circuit employing the principles of this invention;

10

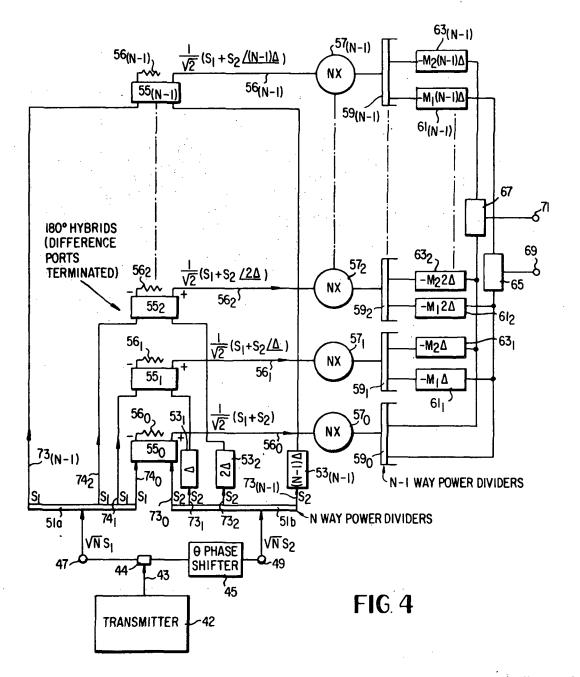

FIG. 4 is a block diagram of an antenna system which utilizes a generalized phase control circuit employing the principles of this invention; and,

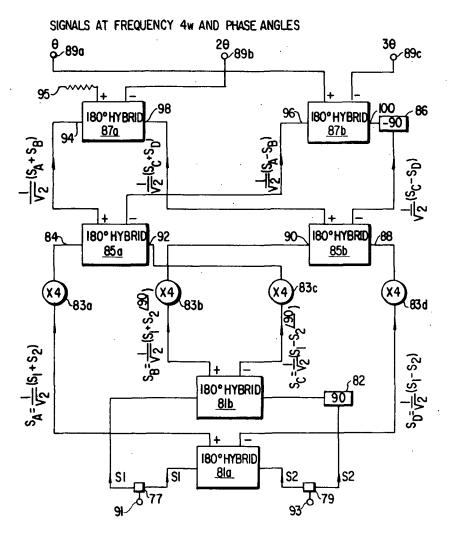

FIG. 5 is a block diagram of an antenna system which utilizes a quadrupler phase control circuit employing 5 the principles of this invention.

### **DESCRIPTION OF THE PREFERRED EMBODIMENTS**

For clarity and convenience of description, the invention is firstly described below in a relatively uncomplicated embodiment (doubler phase control circuit), secondly in a more generalized embodiment (generalized phase control circuit), and thirdly, in a particularized embodiment (quadrupler phase control circuit). Also, throughout the following description, it is assumed, for ease of description, that the phase control circuits are used to couple "transmitters" to phased array antennas; however, it should be understood that 20 phase control circuits employing the principles of this invention can be used to couple "receivers" to phased array antennas as well as transmitters.

#### DOUBLER PHASE CONTROL CIRCUIT

FÍG. 1 illustrates a "doubler" phase control circuit employing the principles of this invention. Essentially, the doubler phase control circuit shown in FIG. 1 receives two phase shifted transmitter signals and emits three phase shifted antenna element signals (assuming 30the phase control circuit shown is being used with a transmitting system). The phase control circuit accomplishes this by combining the two transmitter signals in various ways, doubling the combined signals, and then separating out, from the doubled combined signals, signals having the desired phase angles.

Referring now to FIG. 1, there is shown a transmitter circuit comprising: a transmitter 10; a two-way power divider 27; and a  $\theta$  phase shifter 13. The transmitter cir-40 cuit feeds a doubler phase control coupling circuit which comprises: left and right multi-output power dividers 33 and 35; three combining 180° hybrids 19a-c; six frequency doublers 21a-f; and three recombining 180° hybrids 23a-c. The recombining 180° 45 frequency doublers 21a-f; recombines the doubledhybrids 23a-c, respectively feed antenna elements 25a-c.

A signal applied by the transmitter 10 on transmitter line 11 passes through the two-way power divider 27 and a  $\theta$  phase shifter 13 to a right terminal 17 and 50 through the two-way power divider 27 to a left terminal 15. Thus, a signal  $2S_1$  which has a zero relative phase shift appears on the left terminal 15, and a signal 2S<sub>2</sub> which has a  $\theta$  relative phase shift appears on the right terminal 17. The signals,  $2S_1$  and  $2S_2$ , are fed into the 55 left and right multi-output dividers 33 and 35 and these power dividers respectively provide outputs  $S_1$  and  $S_2$ . In the embodiment illustrated in FIG. 1, the multi-output power dividers 33 and 35 are four-way power 60 dividers and their input to output amplitude ratios are 2, i.e.,  $\sqrt{4}$ ; thus, their input signals are designated as  $2S_1$ ,  $2S_2$  and their output signals are designated as  $S_1$ , S<sub>2</sub>. Signals S<sub>1</sub> appearing at first, second and third outputs 37a-c of the left multi-output power divider 33 are 65 respectively connected to first and second inputs of a first combining 180° hybrid 19a and to a first input of a second combining 180° hybrid 19b. Signals S<sub>2</sub> appear-

ing at first, second and third outputs 39a-c of the right multi-output power divider 35 are respectively connected to first and second inputs of a third combining 180° hybrid 19c and to a second input of the second combining 180° hybrid 19b. Signals appearing at a fourth output 37d of the left multi-output power divider 33 and a fourth output 39d of the right multi-output power divider 35 are used to feed additional output signals  $S_1$  and  $S_2$  to additional combining hybrids which, for simplicity, are not shown.

The combining 180° hybrids 19a-c each have a sum port, which are represented in FIG. 1 by "plus" symbols, and a difference port, which are represented in FIG. 1 by "minus" symbols. The output signals appearing at the sum and difference ports of the first combining 180° hybrid 19a are respectively connected, through first and second frequency doublers 21a and 21b to separate inputs of a first recombining 180° hybrid 23a. The output signals appearing at the sum and difference ports of the second combining 180° hybrid 19b are respectively connected, through third 25 and fourth frequency doublers 21c and 21d, to separate inputs of a second recombining 180° hybrid 23b. The output signals appearing at sum and difference ports of the third combining 180° hybrid 19c are respectively connected, through fifth and sixth frequency doublers 21e and 21f, to separate inputs of a third recombining 180° hybrid 32c. The difference ports of the three recombining 180° hybrids 23a-c respectively feed active antenna elements 25a-c. The sum ports of the 35 recombining 180° hybrids 23a-c are applied to terminating resistors 26a-c.

Effectively, the doubler phase control circuit receives two signals, 2S<sub>1</sub> and 2S<sub>2</sub>, 2S<sub>2</sub> being separated from  $2S_1$  by a phase angle of  $\theta$ ; subdivides these signals,  $2S_1$  and  $2S_2$  into two groups of smaller signals  $S_1$  and  $S_2$ ; combines these smaller signals in various ways (i.e., by summing and subtracting) in the combining 180° hybrids 19a-c; doubles the combined signals using the combined signals in the recombining 180° hybrids 23a-c and thereby separates out three signals, one each at the respective antenna elements 25a-c, the first having a zero phase angle, the second a  $\theta$  phase angle and the third a  $2\theta$  phase angle.

The theory involved in the operation of the doubler phase control circuit shown in FIG. 1 is hereinafter described. For ease of understanding, sine waves are used to trace the signals through the phase control circuit. Thus, equations which represent the signals from the outputs of the left and right four-way power dividers 33 and 35 are respectively expressed as:

$$S_1 = \cos \omega t \tag{1}$$

$$S_2 = \cos\left(\omega t + \theta\right) \tag{2}$$

where  $\theta$  is the angular velocity of the signals  $S_1$  and  $S_2$ and  $\theta$  is the angle by which  $S_2$  leads  $S_1$ .

At the respective sum and difference ports of the combining 180° hybrid 19b, the signals are expressed by the following equations:

sum signal =

$$(1/\sqrt{2})(S_1 + S_2)$$

(3)

difference signal =  $(1/\sqrt{2})(S_1 - S_2)$ (4) If the doublers are ideal, then the respective outputs of doublers 21c and 21d are proportional to the squares of 5 the inputs or are proportional to  $\frac{1}{2}(S_1 + S_2)^2$  and  $\frac{1}{2}(S_1 + S_2)^2$  $(-S_2)^2$ . The difference term at the output of the recombining 180° hybrid 23b (which goes to the antenna element 25b) is similarly proportional to:

$$\sqrt{2} S_1 S_2 \tag{5}$$

The corresponding signal having a frequency of 2  $\omega t$  is expressed as follows:

$$(1/\sqrt{2})\cos(2\omega t + \theta).$$

(6) 14

The outputs of the difference ports for the recombining 180° hybrids feeding antenna elements 23a and 23b can be shown respectively to be:

$$(1/\sqrt{2})\cos(2\omega t)$$

and  $(7)_{20}$

$$(1/\sqrt{2})\cos\left(2\,\omega t + 2\theta\right) \tag{8}$$

Thus the doubler phase control coupler circuit shown in FIG. 1 provides three outputs, one each on the antenna elements 25a-c. Each of the signals has a frequency of 2  $\Phi t$ , which is double the frequency of the input signals  $S_1$  and  $S_2$ . The signal appearing at antenna element 25a has a zero relative phase shift, the signal appearing at antenna element 25b has a  $\theta$  relative phase shift, and the signal appearing at antenna element  $25c_{-30}$ has a  $2\theta$  relative phase shift.

Generally, each of the combining 180° hybrids 19a-c combines two signals. Each of the frequency doublers 21a-f respectively doubles a combined signal, and each of the recombining 180° hybrids 23a-c respectively 35 separate out a desired signal to be applied to an antenna element 25a-c.

Thus, the doubler phase control circuit shown in FIG. 1 provides phase shifted signals which are shifted one from the other by highly accurate increments. 40 Further, this circuit employs standard interchangeable components and is relatively uncomplicated to construct.

A unique feature of the "doubler" phase control cir-45 cuit of the invention is that it may be used even when the frequency doubler conversion loss is a variable function of power input: Many commercially available doublers have conversion loss characteristics similar to those shown in FIG. 2. FIG. 2 is a plot of conversion 50 loss vs. input power of a doubler. It can be seen in FIG. 2 that as input power drops below 5 milliwatts the conversion loss varies greatly. Normally, this conversion loss characteristic is important because when the relative phase angle  $\theta$  between  $S_1$  and  $S_2$  is zero, all of the 55 control circuit, as well as of all phase control circuits signal arrives at the sum port of the combining 180° hybrid 19b and no signal arrives at its difference port. Similarly, when  $\theta$  equals 180°, all of the signal arrives at the difference port and none at the sum port. The power appearing at each doubler 21c and 21d is, there-60fore, a function of the phase angle  $\theta$ . From this it appears that the conversion loss characteristics of the doublers 21c and d would cause a phase error and amplitude modulation of their output signals as a function 65 of the phase angle between signals  $S_1$  and  $S_2$  when the power input is below 5 milliwatts. However, this is not so.

The foregoing advantage of the doubler phase control circuit of the invention will be better understood by the following technical analysis; assuming that the doublers are identical and have phase shift characteristics independent of power, the output signal of any of the doublers 21a-f whose input signal is S (where S =|S| cos ( $\omega t + \theta_s$ ) and  $\theta_s$  is the relative phase shift of S) can be expressed as:

$$S^2 A(|S|) \tag{9}$$

where A ([S]) is a transmission factor for a doubler. Referring to FIG. 1 and plugging in the sum and difference signals obtained from the 180° hybrid 19b, the output from doubler 21c is therefore:

$$\frac{1}{2}(S_1+S_2)^2 A\left(\left|\frac{S_1+S_2}{\sqrt{2}}\right|\right) \tag{10}$$

and the output from doubler 21d is:

$$1/2(S_1-S_2)^2 A\left(\left|\frac{S_1-S_2}{\sqrt{2}}\right|\right)$$

(11)

The signal appearing at the antenna element 25b is 1/22 times the first of these minus the second. Combining these terms and writing the frequency components at 25  $2\omega$ , the following output signal is obtained:

$$\frac{1}{4\sqrt{2}} \left[ \left[ A\left( \left| \frac{S_1 + S_2}{\sqrt{2}} \right| \right) - A\left( \left| \frac{S_1 - S_2}{\sqrt{2}} \right| \right) \right] \cos 2\omega t$$

$$+ \left[ A\left( \left| \frac{S_1 + S_2}{\sqrt{2}} \right| \right) - A\left( \left| \frac{S_1 - S_2}{\sqrt{2}} \right| \right) \right] \cos (2\omega t + 2\theta)$$

$$+ 2 \left[ A\left( \left| \frac{S_1 + S_2}{\sqrt{2}} \right| \right) + A\left( \left| \frac{S_1 - S_2}{\sqrt{2}} \right| \right) \right] \cos (2\omega t + \theta) \right]$$

The third term of this expression is the only term with a phase angle of  $\theta$ , however, the resultant phase angle of the first two term is also  $\theta$  because the bracketed portions of both these terms are identical. Moreover, it can be shown that the resultant signal of the first two terms varies as a function of power in such a manner as to substantially cancel out variations in the third term as a function of power input into the doublers. Thus, the output signal indicated above can be written as:

$1/\sqrt{2A}(|r|)\cos(2\omega t+\theta)$ (13)where r varies between a maximum of 1.414 and a minimum of 1.0 (assuming that the input signals  $S_1$  and  $S_2$  have been normalized to 1.0). Hence, even if the signals  $S_1$  and  $S_2$  are in the range of saturation in the curve of FIG. 2, the doubler phase control circuit will operate with essentially no phase error and only 3db of amplitude modulation even though the doublers' conversion losses differ considerably for changes in input power.

Another interesting feature of the doubler phase employing the principles of this invention, is that it "up-converts" a signal's frequency. That is, the phase control circuit receives a signal from a transmitter having a frequency of  $\omega$  and emits signals at antenna elements 25a-c having frequencies of  $2\omega$ . Normally, the phase control circuits of this invention multiply the frequency of a signal coming from a transmitter by the multiple of a multiplying element before they deliver signals to antenna elements. For example, in the doubler phase control circuit shown in FIG. 1 the transmitter signal frequency is doubled before it is delivered to the antenna elements 25a-c.

FIG. 3 shows another "doubler" phase control circuit employing the principles of this invention which is quite similar to the embodiment shown in FIG. 1. The doubler phase control circuits shown in FIGS. 1 and 3 differ from one another in that the FIG. 3 embodiment <sup>5</sup> employs: 90° hybrids rather than 180° hybrids as in the FIG. 1 embodiment; 90° phase delay elements connected in series to sum port frequency doublers; and antenna elements which are connected to sum ports of 10 recombining 90° hybrids rather than to difference ports, as in the FIG. 1 embodiment. Otherwise, the FIG. 3 embodiment functions essentially the same as the FIG. 1 embodiment. That is, it receives two signals  $S_1$  and  $S_2$  separated by an angle  $\theta$ , and emits three 15 signals having respective phase angles of zero phase shift,  $\theta$  phase shift and  $2\theta$  phase shift. Also, the circuit shown in FIG. 3 has the same "conversion loss" feature described above for the circuit shown in FIG. 1.

More particularly FIG. 3 shows a transmitter circuit 20 comprising: a transmitter 10; a two-way power divider 27; and a  $\theta$  phase shifter 13. The transmitter circuit feeds a doubler phase control coupling circuit which comprises: left and right multi-output power dividers 33 and 35; three combining 90° hybrids 36a-c; six 25 frequency doublers 21a-f; three 90° phase delay elements 38a-c; and three recombining 90° hybrids 40a-c. The recombining 90° hybrids 40a-c feed antenna elements 25a-c.

The transmitter 10 is coupled to the two-way power divider 27, and one output of the two-way power divider 27 is coupled directly to the left multi-output power divider 33 while the other output is connected through the  $\theta$  phase shifter 13 to the right multi-output 35 power divider 35. First and second outputs of the left multi-output power divider 33 are respectively coupled to first and second inputs of a first combining 90° hybrid 36a, and a third output of the left multi-output power divider 33 is coupled to a first input of a second 40 combining 90° hybrid 36b. First and second outputs of the right multi-output power divider 35 are respectively coupled to first and second inputs of a third combining 90° hybrid 36c, and a third output of the right multioutput power divider 35 is coupled to a second input of <sup>45</sup> the second combining 90° hybrid 36b.

The sum port of the first combining 90° hybrid 36a is coupled through the first doubler 21a and a first phase delay element 38a to a first input of a first recombining 50 90° hybrid 40a; and the difference port of the first combining 90° hybrid 36a is coupled through the second doubler 21b to a second input of the first recombining 90° hybrid 40a. The sum port of the second combining 90° hybrid 36b is coupled through the third doubler 21c 55 and a second phase delay element 38b to a first input of a second recombining 90° hybrid 40b; and the difference port of the second combining 90° hybrid 36b is coupled through the fourth doubler 21d to a second input of the second recombining 90° hybrid 40b. The  $^{60}$ sum port of the third combining 90° hybrid 36c is coupled through the fifth doubler 21e and a third phase delay element 38c to a first input of a third recombining 90° hybrid 40c; and the difference port of the third 65 combining 90° hybrid 36c is coupled through the sixth doubler 21f to a second input of the third recombining 90° hybrid 40c.

The sum ports of the three recombining 90° hybrids 40*a*-*c* are respectively coupled to active antenna elements 25*a*-*c*. The difference ports of the recombining 90° hybrids 40*a*-*c* are terminated at terminating resistors 26*a*-*c*.

As is mentioned above, the 90° hybrid doubler phase control circuit functions similarly to the 180° hybrid doubler phase control circuit described in detail above, hence, its operation will not be further described here.

#### GENERALIZED PHASE CONTROL CIRCUIT

A generalized phase control circuit, shown in FIG. 4, employs the same principles as the doubler phase control circuits shown in FIGS. 1 and 3. However, it uses a higher order of multiplication and produces more output phase shifted signals than the doubler phase control circuits of FIGS. 1 and 3.

The doubler phase control circuits of FIGS. 1 and 3 accomplish their function by combining two phase shifted input signals, doubling the combined signal and separating out of the doubled-combined signal an integral phase shift signal of the highest phase shift in the system. In the doubler circuits there is only one integral phase shift, namely,  $\theta$ . This is because  $\theta$  is the only one integral between zero and the highest phase shift of the system  $2\theta$ . In the system shown in FIG. 4, essentially what is done is two signals, which are out of phase by angle  $\theta$ , are subdivided into two groups of smaller signals and the smaller signals are combined to produce 30 various combined signals; each combined signal is multiplied by N. Then the combined signals are recombined and thereby separated into N-1 phase shifted integral signals, each being phase shifted from a zero reference by a multiple of  $\theta$  times an integral integer M of N, covering a range of M from 1 to N-1.

Referring now to FIG. 4, there is shown a transmitter circuit comprising: a transmitter 42; a two-way power divider 44; and a  $\theta$  phase shifter 45. The transmitter circuit feeds a generalized phase control coupling circuit which comprises: left and right N-way power dividers 51a and b; phase shifters  $53_1-53_{(N-1)}$ ; combining  $180^{\circ}$ hybrids  $55_0-55_{(N-1)}$ ; frequency multipliers  $57_0-57_{(N-1)}$ : (N-1)-way power dividers  $59_0-59_{(N-1)}$ ; N-1 phase delay elements  $61_1-61_{(N-1)}$ ; N-1 phase delay elements  $63_1-63_{n31}$ ; an M<sub>1</sub> summing circuit 65; and an M<sub>2</sub> summing circuit 67. The summing circuits 65, 67 respectively feed antenna elements 69, 71.

A signal applied by the transmitter 42 on a transmitter line 43 passes through the two-way power divider 44 and  $\theta$  phase shifter 45 to a right terminal 49 and through the two-way power divider 44 to a left terminal 47. Signals appearing at the left and right terminals 47 and 49 are respectively fed into left and right N-way power dividers 51*a* and 51*b*. The input to output amplitude ratios for the left and right N-way power dividers 51*a* and 51*b* are  $\sqrt{N}$ ; thus, their input signals are designated as  $\sqrt{N} S_1$ ,  $\sqrt{N} S2$  and their output signals are designated as  $S_1, S_2$ .

Except for a first output  $73_0$  of the right N-way power divider 51b, each output of the right N-way power divider 51b is connected to a separate phase shifter  $53_1-53_{n31}$ . First phase shifter  $53_1$  shifts its signal,  $S_2$ ,  $\Delta$ degrees forward where  $\Delta = (2 \pi)/N$ ; second phase shifter  $53_2$  shifts its signal,  $S_2$ ,  $2\Delta$  degrees forward; and so on up to the phase shifter  $53_{(N-1)}$  which shifts its signal,  $S_2$ ,  $(N-1)\Delta$  degrees forward.

The signal  $S_2$  coming from the first output  $73_0$  of the right N-way power divider 51b, is combined with a signal  $S_1$  coming from a first output 74<sub>0</sub> of the left Nway power divider 51a in a first combining 180° hybrid 55<sub>0</sub>. A signal  $S_2$  coming from a second output 73, of the 5 right N-way power divider 51b, after passing through a phase shifter 53, is combined with a signal  $S_2$  coming from a second output 74, of the left N-way power divider 51a in a second combining  $180^{\circ}$  hybrid  $51_{1}$ . In a 10 similar manner, signals  $S_2$  coming from outputs  $73_2-73_4$  $_{N-1}$  of the right N-way power divider 51b are respectively combined with signals  $S_1$  coming from outputs  $74_2 - 74_{n31}$  of the left N-way power divider 51a in combining 180° hybrids 552-55(N-1).

The difference ports of the combining 180° hybrids 15 55<sub>0</sub>-55<sub>n31</sub> are terminated into resistors 56<sub>0</sub>-56<sub>(N-1)</sub>.

The sum ports of the hybrids  $55_0-55_{(N-1)}$  are connected through lines  $56_0-56_{(N-1)}$  to separate frequency multipliers  $57_0-57_{(N-1)}$ , each of which multiplies its input signal by N. 20

Frequency multipliers  $57_0-57_{(N-1)}$ , respectively feed their multiplied signals into separate (N-1)-way power dividers  $59_0-59_{(N-1)}$ .

Each of the N-1 outputs of a second (N-1)-way 25 power divider 59, respectively feeds a separate phase delay element  $61_1$ - $63_1$ , etc., with only two being shown for clarity. Each of these phase delay elements delays its input signal by an amount equal to the forward phase shift caused by the series connected phased 30 shifter 53, multiplied by an integral integer M of N; e.g., the phase delay element  $63_1$  is in series with a phase shifter 53, having a forward phase shift of  $\Delta$ . Therefore, the phase delay caused by  $63_1$  is  $\Delta$  times  $M_2$ . Similarly each of the N-1 outputs of a third (N-1)-way 35 power divider 59<sub>2</sub> respectively feeds a separate phase delay element 612, 632, etc., with only two being shown for clarity. As for the phase delay elements of the (N-1)-way power divider 59<sub>1</sub>, each of these delay elements delays a signal by an amount equal to the for- 40 ward phase shift caused by the series connected phase shifter  $53_2$  multiplied by an integral integer M of N. For example, the phase delay element  $63_2$  is in series with a phase shifter  $53_2$  having a forward phase shift of 2  $\Delta$ . Therefore, the phase delay caused by  $63_2$  is 2  $\Delta$  times 45  $M_2$ . A similar description is applicable for all of the phase delay elements attached to the outputs of the (N-1)-way power dividers  $59_0 - 59_{(N-1)}$ . The (N-1)-way power divider 59<sub>0</sub> does not have phase delay elements connected to its outputs because it is not in series with a phase shifter  $53_{1}-53_{(N-1)}$ .

Each of the (N-1)-way power dividers  $59_0-59_{(N-1)}$ has N-1 phase delay elements 61, 63, etc., connected to its respective outputs, and the M integral integers of N utilized by the phase delay elements of each one of 55the (N-1)-way power dividers  $59_0-59_{(N-1)}$  covers the range of from 1 to N-1. It can be seen in FIG. 4 that the phase delay elements  $61_1-61_{(N-1)}$  are connected in parallel to a M<sub>1</sub> summing circuit 65. In this regard, all 60 of the phase delay elements  $61_{1}-61_{(N-1)}$  have a phase delay which is a multiple of the integral integer  $M_1$ . Further, all of the phase delay elements  $63_1-63_{(N-1)}$  are connected in parallel to a M<sub>2</sub> summing circuit 67. In this regard, all of the phase delay elements  $63_1-63_{(N-1)}$  65 delay the phase by an angle which is a multiple of the integral integer M2. Similarly, there are phase delay elements feeding N-1 summing circuits (only combining

elements 65 and 67 are shown for clarity), with the phase delay elements feeding each summing circuit being a multiple of an integral integer M of N, covering the range from  $M=M_1=1$  to  $M=M_{(N-1)}=N-1$ .

The signals coming from the phase delay elements  $61_1-61_{n311}$  are combined at the  $M_1$  summing circuit 65 and feed into an antenna element 69 and the signals coming from the phase delay elements  $63_1-63_{(N-1)}$  are combined at the  $M_2$  summing circuit 67 and feed into an antenna element 71. Similarly, there are N-1 antenna elements, each being fed by a summing circuit, however, only two antenna elements are shown for clarity.

Effectively, the generalized phase control circuit shown in FIG. 4 receives two phase shifted signals, one shifted from the other by an angle  $\theta$ , and converts them into N-1 signals, each being phase shifted from a reference signal by an integral integer M of the number N times  $\theta$ . That is, the output signals are respectively shifted from a reference signal by angle  $\theta$ ,  $2\theta$ ,  $3\theta$ ... (N-1). The general theory behind the operation of this circuit is as follows:

The input signals  $S_1$  and  $S_2$  are expressed by the equations:

$$S_1 = \cos \omega t$$

(14)

$$S_2 = \cos\left(\omega t + \theta\right) \tag{15}$$

Similarly, the signals emitted from the sum ports of the combining 180° hybrids  $55_{0}-55_{N-1}$  (the difference ports are terminated as previously mentioned above) onto their respective lines  $56_{0}-56_{(N-1)}$  are expressed by the equations:

$$_{160} = (1/\sqrt{2})(S_1 + S_2)$$

(16)

$$S_{56_1} = (1/\sqrt{2})(S_1 + S_2/\Delta)$$

(17)

$$S_{Se_{2}} = (1/\sqrt{2}) (S_{1} + S_{2}/2\Delta)$$

(18)

-----

43  $S_{56(N-1)} = (1/\sqrt{2}) (S_1 + S_2/(N-1) \Delta)$  (19) where the notation  $S_2/p \Delta = \cos(\omega t + \theta + p\Delta)$ , with p= integral integers of N covering the range from 1 to N-1; and  $\Delta = (2\pi)/N$ . These signals are fed into the 50 frequency multipliers  $57_0-57_{(N-1)}$  of the order N. The multipliers  $57_0-57_{(N-1)}$ , respectively, raise the signals  $\overline{S}_{560}$  $-\overline{S}_{56(n-1)}$  to the power N and filter out all components except those at frequency N $\omega$ . It can be shown from binomial expansion that the term in each  $(S_{56})^N$  which 55 has its phase angle equal to some general integral integer M of N times  $\theta$  is

$$[N(N-1)(N-2)\dots(N-M+L)/M](S_1)^{(N-M)}\cos(\omega t+\theta +p\Delta)^M$$

(20)

Apart from the amplitude factor which is common to each  $(S_{56})^2$ , the component of this expression which emerges from each of the multipliers  $57_0-57_{(N-1)}$  at the frequency N $\omega$  is expressed as

$$\cos(N\omega t + M\theta + Mp\Delta) \tag{21}$$

It can be shown that the following mathematical relationship exists: 5

$$\sum_{P=0}^{P-(N-1)} n \cos [N\omega t + M\theta + p\Delta(M-K)]$$

$$= \begin{cases} 0 \text{ at } K \neq M \\ N \cos (N\omega t + M\theta) \text{ at } K = M \end{cases}$$

(22)

11

It is desirable to obtain a final output expressed as N $\cos(N \omega t + M\theta)$  which is a multiple of an angle  $\theta$  by anintegral integer of N. To separate out this term with a phase angle of  $M\theta$ , it is necessary to subtract, or delay, 10 a phase angle  $Mp \Delta$  from each of the signals  $(S_{56})^N$  coming from the multipliers  $57_{0}-57_{(N-1)}$  and then add all of the difference signals together. The notation  $(S_{56})^N/$  $-Mp \Delta$  is used to indicate that an angle  $Mp \Delta$  is subtracted from each of the signals  $(S_{56})^N$  coming from the 15 doublers  $57_{0}-57_{(N-1)}$ . The sum of these signals is then expressed as  $N \cos (N\omega t + M\theta)$ . To get this result using the circuit shown in FIG. 4, each signal  $(S_{56})^N$  is divided into N-1 parts (using the power dividers  $59_0-59_{(N-1)}$ ) and the appropriate phase delay elements, for example 20 phase delay elements  $61_1-61_{(N-1)}$ , have a phase delay of  $M_{1p} \Delta$  and are respectively inserted between the power dividers  $59_{1}-59_{(N-1)}$  and the summing circuit 65. In this case the sum of the signals which are combined by the summing circuit, and therefore appear on the antenna<sup>25</sup> element 69, is expressed as  $N \cos (N \omega t + M_1 \theta)$ . This summing operation is similarly carried out for all values of M as follows:

$M_1 = 1$  $M_2 = 2$  $M_3 = 3$

$M_{(N-1)} = N-1$

The summing operations for each of these values of M can be generally expressed as:

$\Sigma(M\theta) = \frac{1}{\sqrt{N-1}} \sum_{p=0}^{p=(N-1)} (S_{56})^{N} / -Mp\Delta$ (23)

Each of the sums is respectively free of all terms at phase angles other than  $M_1\theta$ ,  $M_2\theta$ ... $M_{(N-1)}\theta$ , as the 45 case may be. The generalized phase control circuit has therefore yielded a set of signals with phase angles of  $\theta$ ,  $2\theta$ ... $(N-1)\theta$  which lie equally spaced between the extreme phases 0 and  $N\theta$ .

Thus, this circuit has converted two phase shifted 50 signals into many phase shifted signals, each phase shifted from the others by highly accurate increments. Again, the circuit uses standardized interchangeable components which makes it economical and relatively uncomplicated. 55

Unlike the doubler phase control circuit described above, the generalized phase control circuit does not exhibit the same invariance to multiplier power sensitivity. Indeed, it can be shown that if the multiplier parameters do vary with power, then both amplitude modulation and phase error are evident at the antenna elements 69, 71, etc.

The generalized phase control circuits also "up-convert" the input signals' frequencies from lower transmitter frequencies to higher broadcasting frequencies at the antenna elements **69**, **71**, etc., as do the doubler phase control circuits.

Another feature of importance with regard to generalized phase control circuits is that the various antenna signals are of different amplitude for N > 3. This arises because of the binomial coefficient amplitude factor multiplying the various terms is a multiplier extension  $(S_{56})^N$ . This factor limits the practical upper boundary to the order of multiplication. Beyond the order 5, the amplitude ratio of a center signal,  $(N\theta/2$ for N even, or  $(N-1)\theta/2$  for N odd) to those at the angle  $\theta$  and  $(N-1)\theta$ , exceeds 2.0. Beyond the order of 10 this ratio exceeds 25.0. Directional couplers, attenuators or limitors may be used to equalize the signals, but when the difference in signal amplitude becomes too great, this too becomes impractical.

#### **QUADRUPLER PHASE CONTROL CIRCUIT**

FIG. 5 illustrates a "guadrulpler phase control circuit" employing the principles of this invention. Essentially, the quadrupler phase control circuit shown in FIG. 5 receives two phase shifted transmitter signals, a first at zero phase shift and a second at  $\theta$  phase shift, and emits three phase shifted antenna element signals; a first at  $\theta$  phase shift, and a second at  $2\theta$  phase shift, and a third at  $3\theta$  phase shift. The quadrupler phase control circuit accomplishes this by subdividing the two received signals into two groups of smaller signals, combining the smaller signals, in various ways, doubling the combined signals so as to separate out, from the doubled combined signals, signals having the desired phase angles.

Referring now to FIG. 5, there is shown a quadrupler phase control coupling circuit which comprises: left and right two-way power dividers 77 and 79; two combining 180° hybrids 81a and 81b; a 90° forward phase shifter 82; four frequency quadruplers 83a-d; two recombining 180° hybrids 85a and 85b; a 90° phase delay element 86 and two re-recombining 180° hybrids 87a and 87b. The re-recombining 180° hybrids 87a and 87b. The re-recombining 180° hybrids 87a and 87b feed three antenna elements 89a-c. A transmitter circuit is not shown in FIG. 5, however it should be understood that the quadrupler phase control circuit is 45 normally fed by a transmitter circuit similar to the transmitter circuits shown in FIGS. 1, 3 and 4 and described in conjunction therewith.

More particularly, a transmitter circuit, not shown, feeds a zero phase angle signal to input 91 of the left two-way power divider 77 and a  $\theta$  phase angle signal to input 93 of the right two-way power divider 79. First and second outputs of the left two-way power divider 77 are respectively coupled to first inputs of first and second combining 180° hybrids 81*a* and 81*b*. A first output of the right two-way power divider 79 is coupled to a second input of the first combining 180° hybrid 81*a*. A second output of the right two-way power divider 79 is coupled through the 90° forward phase shifter 82 to a second input of the second combining 180° hybrid 81*b*.

The sum port of the first combining 180° hybrid 81*a* is coupled through a first frequency quadrupler 83*a* to a first input 84 of a first recombining 180° hybrid 85*a*. The difference port of the first combining 180° hybrid 81*a* is coupled through a fourth frequency quadrupler 83*d* to a second input 88 of a second recombining 180° hybrid 85*b*. The sum port of the second combining 180°

30

hybrid 81b is coupled through a second frequency quadrupler 83b to a first input 90 of the second recombining 180° hybrid 85b. The difference port of the second combining 180° hybrid 81b is connected through a third frequency quadrupler 83c to a second 5 input 92 of the first recombining 180° hybrid 85a.

The sum and difference ports of the first recombining 180° hybrid 85a are respectively connected to first inputs 94, 96 of first and second re-recombining 180° hybrids 87a and 87b. The sum port of the second com- <sup>10</sup> bining 180° hybrid 85b is coupled to a second input 98 of the first re-recombining 180° hybrid 87a and the difference port of the second recombining 180° hybrid 85b is coupled through the phase delay element 86 to a 15 second input 100 of the second re-recombining 180° hybrid 87b.

The sum port of the first re-recombining 180° hybrid 87a is terminated into a resistor 95 and the difference port of the first re-recombining 180° hybrid 87a is cou- 20 pled to a second antenna element 89b. The sum port of the second re-recombining 180° hybrid 87b is coupled to a first antenna element 89a and the difference port of the second re-recombining 180° hybrid 87b is coupled to a third antenna element 89c.

Effectively, the quadrupler phase control circuit receives two input signals which are separated from one another by a phase angle  $\theta$ ; divides each of the input signals into two  $S_1$  signals and two  $S_2$  signals; combines the  $S_1$  signals and the  $S_2$  signals in various ways 30 (i.e, by summing and subtracting) in the two combining 180° hybrids 81a and 81b; quadruples the combined signals using the frequency quadruplers 83a-d; recombines the quadrupled-combined signals in the recombining 180° hybrids 85a and 85b; re-recombines the 35recombined-quadrupled-combined signals in the rerecombining 180° hybrids 87a and 87b and thereby separates out three signals, one each at the three antenna elements 89a-c. The signal appearing at the first an-40tenna element 89a has a relative phase angle of  $\theta$ , the signal appearing at the second antenna element 89b has a relative phase angle of  $2\theta$ , and the signal appearing at the third antenna element 89c has a relative phase angle of  $3\theta$ . 45

Equations which express the signals appearing on various lines in the quadrupler phase control circuit are included in FIG. 5.

It will be appreciated by those skilled in the art that the phase control array antenna circuits specifically 50 disclosed in this application offer advantages of lack of complexity and accuracy over prior art phase control array antenna coupling circuits. However, it will be appreciated that various changes in form and detail may be made in the specifically disclosed embodiments 55 without departing from the spirit and scope of the invention.

What is claimed is:

1. A phased array antenna coupling circuit of the type used for coupling a transmission circuit with a plurality of more than two phased array antenna elements comprising:

- a multiplier circuit, means for multiplying the frequencies of at least two signals supplied thereto;

- 65 combining circuit means for interconnecting said transmission circuit and said multiplier circuit means, said combining circuit means being

- adapted to combine in a preselected manner at least two signals which are separated by a phase angle; and,

- a recombining circuit means for interconnecting said multiplier circuit means and said more than two phased array antenna elements.

2. A phased array antenna coupling circuit as claimed in claim 1 wherein:

said combining circuit means includes phase shifting means connected to said transmission circuit first and second input terminal means, each of which handles a signal which is separated by a phase angle from the signal handled by the other.

3. A phased array antenna coupling circuit as claimed in claim 2 wherein:

- said multiplier circuit comprises a plurality of frequency multiplier elements each being connected between said combining and recombining circuits; and,

- said combining circuit comprises first and second multi-output power dividers, said first multi-output power divider being connected to said first input terminal means and said second multi-output power divider being connected to said second input terminal means.

4. A phased array antenna coupling circuit as claimed in claim 3 wherein said combining circuit and said recombining circuit each combine at least two signals which are separated from one another by a phase angle.

5. A phased array antenna coupling circuit as claimed in claim 4 wherein:

- said combining circuit includes a four port hybrid power divider which is connected to both said first. and said second multi-output power dividers and is further connected to two of said frequency multiplier elements;

- said frequency multiplier elements are frequency doublers; and,

- said recombining circuit includes a four port hybrid power divider which is connected between at least two of said frequency doublers and at least one of said antenna elements.

6. A phased array antenna coupling circuit as claimed in claim 4 wherein:

- there are three four port hybrid power dividers in said combining circuit, a first of which has two inputs connected to said first multi-output power divider, a second of which has a first input connected to said first multi-output power divider and a second input connected to said second multi-output power divider, and a third of which has two inputs connected to said second multi-output power divider;

- there are six doublers, a pair of said doublers being attached to each of said three four port hybrid power dividers in said combining circuit; and,

- there are three four port hybrid power dividers in said recombining circuit, each one being attached to a separate pair of said doublers.

7. A phased array antenna coupling circuit as claimed in claim 6 wherein:

said four port hybrid power dividers in said combining circuit and said recombining circuit are 90° hybrids; and,

25

there is further included three 90° delay elements which are respectively connected between one frequency doubler in each frequency doubler pair and a four port hybrid in said recombining circuit.

8. A phased array antenna coupling circuit as 5 claimed in claim 4 wherein:

- said combining circuit includes a 180° four port hybrid power divider which is connected to both said first and said second multi-output power dividers and is further connected to two said 10 frequency multiplier elements;

- said frequency multiplier elements are frequency doublers; and,

- said recombining circuit includes a 180° four port hybrid power divider which is connected between <sup>15</sup> at least two of said frequency doublers and at least one of said antenna elements.

9. A phased array antenna coupling circuit as claimed in claim 4 wherein:

- said frequency multiplier elements each multiply <sup>20</sup> signals to the Nth power; and,

- said combining circuit includes N four port hybrid power dividers which are respectively connected to both said first and said second multi-output power dividers and which are respectively further <sup>25</sup> connected to separate ones of said multiplier elements.

10. A phased array antenna coupling circuit as claimed in claim 9 wherein:

said multi-output power dividers are N-way power <sup>30</sup> dividers, each having N outputs;

- there are N-1 phase shifting elements, each connected between a separate output of one of said Nway power dividers and a separate one of said N  $_{35}$  four port hybrid power dividers;

- there are N multiplying elements, each one connected to a separate four port hybrid power divider in said combining circuit;

- there are (N-1)-way power dividers connected 40 between each said multiplier element and said recombining circuit; and,

- phase delay elements are connected between the outputs of all but one of said (N-1)-way power dividers and said recombining circuit. 45

11. A phased array antenna coupling circuit as claimed in claim 4 wherein:

said frequency multiplier elements each multiply signals to the Nth power;

said multi-output power dividers each have N out- 50 puts; and wherein is further included (N-1)-way power dividers each having N-1 outputs and each being connected between a separate multiplier element and said recombining circuit means.