December 1972 provided by NASA Technical Reports Sen

B72-10729

# **NASA TECH BRIEF**

# Manned Spacecraft Center

NASA Tech Briefs announce new technology derived from the U.S. space program. They are issued to encourage commercial application. Tech Briefs are available on a subscription basis from the National Technical Information Service, Springfield, Virginia 22151. Requests for individual copies or questions relating to the Tech Brief program may be directed to the Technology Utilization Office, NASA, Code KT, Washington, D.C. 20546.

# Frequency-To-Amplitude Converter: A Concept

Frequency-To-Amplitude Converter

## The problem:

The accurate detection of speech frequencies is a major obstacle in achieving accurate speech processing and bandwidth compression. Standard frequency-to-amplitude conversion requires special frequency counters and frequency discriminators with resultant trade-offs between signal bandwidth and signal quality. Conse-

quently, the bandwidth compression is achieved at the expense of voice quality and intelligibility.

### The solution:

A newly designed circuit allows direct frequencyto-amplitude conversion without the need for special counters and discriminators and provides for individual

(continued overleaf)

or simultaneous emphasis of the high or low frequencies. The circuit is simple, small, and light weight, and is versatile in its frequency range and region of conversion.

#### How it's done:

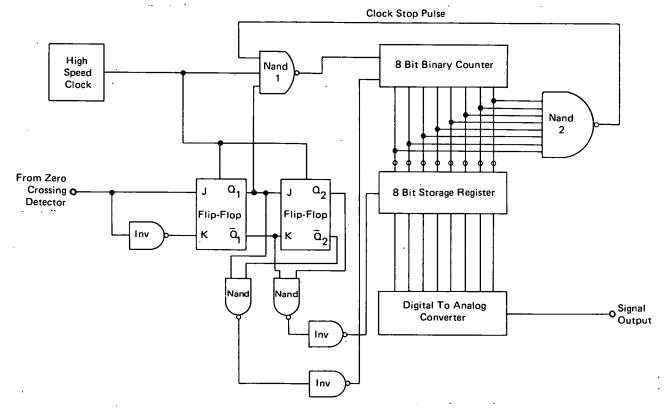

The figure shows the new frequency-to-amplitude converter circuit. It measures the time between zero crossings of a given input signal. In operation, the signal is first sensed through a zero crossing detector (not shown in the figure) and then applied simultaneously into a JK flip-flop and an inverter. When this action occurs, the Q<sub>1</sub> output of a two-stage flip-flop opens a nand gate (No. 1) and allows clock pulses from a high-speed clock to drive an 8-bit binary counter. When the second zero crossing occurs, the Q<sub>1</sub> output of the flip-flop closes the nand gate (No. 1) and stops the clock pulse drive to the counter. At this time the counter stops counting, and its value, via 8 inverters, is dumped into an 8-bit storage register as a result of a storage actuate pulse derived from the Q1 and Q2 outputs of the two-stage flip-flop. Following this storage action a second pulse (called a clear pulse), derived from the  $Q_1$  and  $\bar{Q}_2$  output of the flip-flops, clears the counter and makes the counter ready to repeat the count process when the third input signal zero crossing occurs. In the meantime, the 8-bit storage register output drives an 8-bit digital to analog (D/A) converter. The D/A output is a voltage level which is a function of the time between the first and second zero crossing of the input signal. The process is repeated for the third and subsequent zero crossing.

#### Notes:

- 1. This invention is in the conceptual stage only. At the time of this publication no model or prototype exists.

- 2. Requests for further information may be directed to:

Technology Utilization Officer Manned Spacecraft Center Code JM7 Houston, Texas 77058

Reference: TSP72-10729

### Patent status:

This invention is owned by NASA, and a patent application has been filed. Inquiries concerning non-exclusive or exclusive license for its commercial development should be addressed to:

Patent Counsel Code AM Manned Spacecraft Center Houston, Texas 77058

> Source: Carrington H. Stewart Manned Spacecraft Center (MSC-12395)

B72-10729 Category 01