B72-10347

NASA Tech Briefs announce new technology derived from the U.S. space program. They are issued to encourage commercial application. Tech Briefs are available on a subscription basis from the National Technical Information Service, Springfield, Virginia 22151. Requests for individual copies or questions relating to the Tech Brief program may be directed to the Technology Utilization Office, NASA, Code KT, Washington, D.C. 20546.

# **Overlap Diffusion for Increasing Phototransistor Dynamic Range**

#### The problem:

The present phototransistors operating in the chargestorage mode have very limited dynamic ranges. There are severe limitations on both the maximum voltage at which these devices may be operated and the maximum base-collector capacitance which can be obtained from them.

#### The solution:

The base-collector capacitance in phototransistors is increased by a factor of five by use of one of the two methods of  $n^+$  diffusion.

### How it's done:

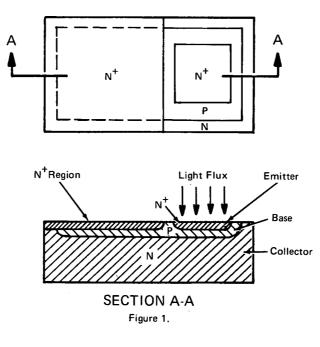

As shown in the Figure 1, one configuration of the improved phototransistor is constructed of a silicon or germanium semiconductor wafer. The lower portion forms the collector region to provide an n-type conductivity for n-p-n type phototransistors (p-type conductivity for p-n-p type). Above the collector region is a base region which is formed by diffusion of impurities into the substrate exhibiting p-type conductivity for an n-p-n device (n-type for a p-n-p device). A third distinct emitter region is formed by diffusion of  $n^+$  impurities into the base region ( $p^+$  impurities for p-n-p device) to create a second junction. This stage completes the formation of conventional phototransistor. To depart from the conventional device, a second base-collector junction is formed by an  $n^+$  ( $p^+$  for p-n-p) conductivity layer, as in the case of an emitter region. This layer is out of the emitter-collector path and does not contribute to the base-collector junction breakdown. At the same time, this layer increases the base-collector capacitance.

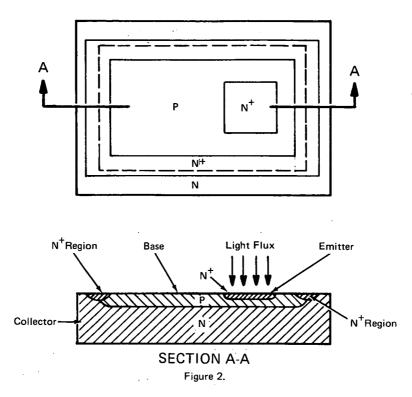

A second type of construction that increases the basecollector capacitance is shown in Figure 2. This photo-

(continued overleaf)

This document was prepared under the sponsorship of the National Aeronautics and Space Administration. Neither the United States Government nor any person acting on behalf of the United States Government assumes any liability resulting from the use of the information contained in this document, or warrants that such use will be free from privately owned rights.

transistor includes an additional base-collector junction which is provided by diffusion of  $n^+$  region into the base periphery ( $p^+$  for p-n-p). This additional region connects to the collector region by a common peripheral boundary. Again, being out of the emitter-collector path, this region provides additional base-collector capacitance without a decrease in the maximum base-collector operating voltage.

## Note:

Requests for further information may be directed to:

Technology Utilization Officer Marshall Space Flight Center Code A&TS-TU Huntsville, Alabama 35812 Reference: B72-10347

#### Patent status:

This invention is owned by NASA, and a patent application has been filed. Inquiries concerning non-exclusive or exclusive license for its commercial development should be addressed to:

> Patent Counsel Marshall Space Flight Center Code A&TS-PAT Huntsville, Alabama 35812

> > Source: D. H. McCann of Westinghouse Electric Corp. under contract to Marshall Space Flight Center (MFS-20407)

B72-10347