June 1971

Brief 71-10204

# NASA TECH BRIEF

## Ames Research Center

NASA Tech Briefs announce new technology derived from the U.S. space program. They are issued to encourage commercial application. Tech Briefs are available on a subscription basis from the National Technical Information Service, Springfield, Virginia 22151. Requests for individual copies or questions relating to the Tech Brief program may be directed to the Technology Utilization Office, NASA, Code KT, Washington, D.C. 20546.

### Coarse Roll-Rate Gain-Control Circuit

A coarse roll-rate gain-control circuit is used in the spin-rate computing unit of the control system for a solar-pointing rocket during its acquisition mode. Direction cosines from magnetometers and coarse sun sensors are used to derive a function that is approximately the roll-rate times the sum of the absolute values of the direction cosines. The roll-rate circuit takes the resulting signal and divides it by the sum of the absolute values of the direction cosines to produce a signal that is proportional to the roll rate.

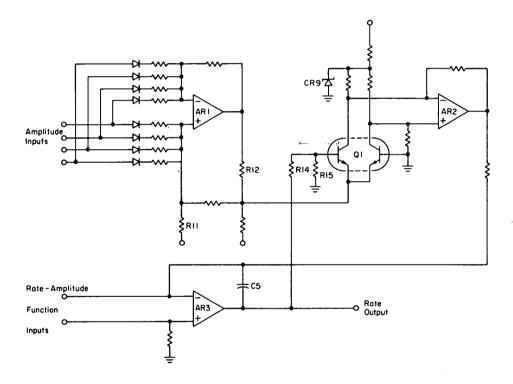

Division in the coarse roll-rate gain-control circuit is accomplished by including a multiplier in the feedback loop of a high gain operational amplifier, AR3 (see diagram). The multiplier circuit includes a signal source (AR1), matched differential transistors (Q1), and a summing amplifier (AR2).

The absolute value of the direction cosines is taken at the input of amplifier AR1; the positive input voltages are sent to the negative amplifier input while the negative inputs are coupled to the positive amplifier

(continued overleaf)

input. Any increase in the absolute value of the sum of the direction cosines causes the AR1 amplifier output voltage to swing in a negative direction which increases the bias current to the multiplier transistors (Q1). Resistor R11 is needed to balance the AR1 input voltage; otherwise, the negative 0.6-volt base emitter drop of Q1 would cause the AR1 amplifier to be offset by the same amount since the drop is fed back on the positive input. Resistor R12 is necessary to prevent the division result from going to infinity (saturation) when the amplitude and rate inputs go to zero; it causes a small bias current to flow in multiplier Q1.

The multiplier supply voltage is reduced to 6.2 volts by CR9 so that it is maintained within the common mode range of AR2. The multiplier input voltage is divided by R14 and R15 to keep the Q1 input voltages very small (approx. 20 mV); this is required so that the small-signal equivalent characteristics of the multiplier are maintained for satisfactory multiplying accuracy.

The AR2 amplifier sums the Q1 differential collector currents and provides a single-end output voltage.

Amplifier AR3 requires a small capacitor (C5) to prevent high-frequency oscillation. The rate inputs come from a rate-switching circuit composed of a capacitor in series with a resistor. With several rate function input signals (not shown) connected to each input terminal (positive and negative), amplifier AR3 sums and divides at the same time.

#### Note:

Requests for further information may be directed to:

Technology Utilization Officer Ames Research Center Moffett Field, California 94035 Reference: B71-10204

#### Patent status:

No patent action is contemplated by NASA

Source: Walter A. Cooke of

Lockheed Missiles & Space Company

under contract to

Ames Research Center

(ARC-10064)