brought to you by & CORE

September 1970

Brief 70-10163

# NASA TECH BRIEF

NASA Tech Briefs announce new technology derived from the U.S. space program. They are issued to encourage commercial application. Tech Briefs are available on a subscription basis from the Clearinghouse for Federal Scientific and Technical Information, Springfield, Virginia 22151. Requests for individual copies or questions relating to the Tech Brief program may be directed to the Technology Utilization Division, NASA, Code UT, Washington, D.C. 20546.

## Communications Link for SDS 900 Series Computers

## The problem:

To design a combined system of two or more computers with a minimum number of connections in order to reduce data errors substantially.

#### The solution:

Develop a high speed, self-clocking single channel control and data link apparatus to interface between the two computers.

## How it's done:

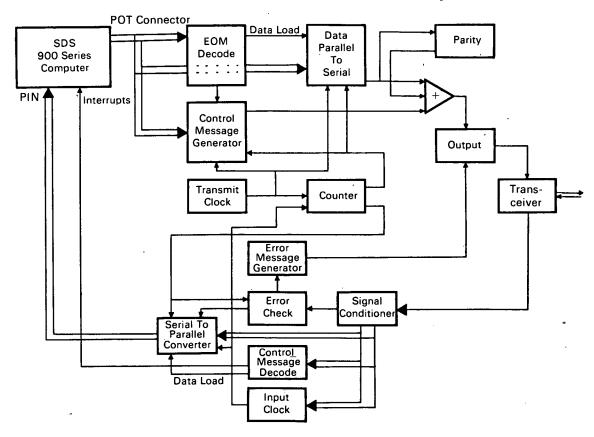

The block diagram above depicts the interfacing circuitry associated with the computer at one end of the communications link. Identical circuitry is associated with the computer at the other end of the link.

The transmitted output from the remote computer is received in serial form by the transceiver shown

(continued overleaf)

at the far right in the diagram. Timing circuits determine if a complete data and control message has been received, and check the composite signal for correct parity and rate. If errors are present, an error control message is sent back to the originating computer. If the signal is normal, it is converted from series to parallel form and input to the local computer (PIN), which then acts on the control and data components to perform the task programmed.

To transmit, the data in parallel output form (POT) is fed through the energize output medium (EOM) decode to the parallel-to-serial converter. The EOM senses the start of a transmission and activates the appropriate equipment to route the data to the transceiver. The serial data, together with control codes and a parity bit, are fed to the output driver which converts the pulses to a three-level form (+5 volts for the 1 state; -5 volts for the 0). Transmission of the data in this form removes the necessity of transmitting a clock signal on a separate channel.

#### Note:

; . . ;

Requests for further information may be directed to:

Technology Utilization Officer NASA Pasadena Office 4800 Oak Grove Drive Pasadena, California 91103 Reference: TSP70-10163

# Patent status:

No patent action is contemplated by NASA.

Source: Arthur I. Zygiebaum, James W. Layland,

and Warren L. Martin of

Caltech/JPL

under contract to

NASA Pasadena Office

(NPO-11161)