View metadata, citation and similar papers at core.ac.uk

brought to you by CORE

September 1970 Brief 70-10009

NASA Tech Briefs announce new technology derived from the U.S. space program. They are issued to encourage commercial application. Tech Briefs are available on a subscription basis from the Clearinghouse for Federal Scientific and Technical Information, Springfield, Virginia 22151. Requests for individual copies or questions relating to the Tech Brief program may be directed to the Technology Utilization Division, NASA, Code UT, Washington, D.C. 20546.

Analog-to-

Digital

Converter

**Timing Logic**

# Digital Data Transition Tracking Loop Improves Data Reception

#### The problem:

Single channel communications and telemetry systems employ symbolic coding techniques to ensure error-free reception of telemetered data when adverse signal-to-noise ratios are encountered. For example, a convolutional code that uses five symbols for each information bit, provides essentially error-free performance with a ratio of symbol energy to noise spectral density of -5 db. A transition tracking loop with a very narrow bandwidth is required to achieve symbol synchronization and filtering which eliminate input signal and receiver generated data errors.

Integrator

Data Channel

## The solution:

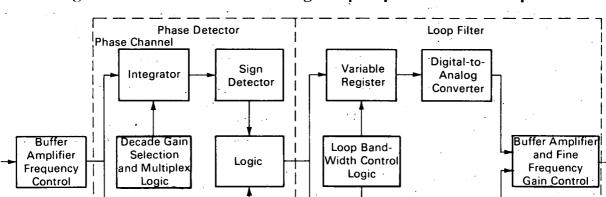

A digital transition tracking loop, motivated by the requirement of extreme stability, eliminates the drifts, leakages, and instabilities inherent in analog filters. The major components of the digital data transition tracking loop shown in the figure are the phase detector, loop filter, voltage-controlled oscillator and timing logic.

Digital-to-

Analog

Converter

#### How it's done:

Variable Gain

Up-Down

Counter

VCO

The input to the integrators in the phase detector is the received signal which consists of a constant amplitude, bipolar video data stream plus white Gaussian noise. In the in-phase channel, the integrations are performed over the assumed data symbol positions, i.e., from (n-1)T to nT, where T is the symbol duration, so that the signs of the integrals represent estimates of the binary data symbols. In the midphase channel, the integration windows are symmetric (continued overleaf)

This document was prepared under the sponsorship of the National, Aeronautics and Space Administration. Neither the United States Government nor any person acting on behalf of the United States Government assumes any liability resulting from the use of the information contained in this document, or warrants that such use will be free from privately owned rights. about times nT. Whenever a transition occurs, the mid-phase channel integral forms an estimate of the timing error between the actual transition time and the assumed transition time, nt. In particular, whenever the actual transition occurs within the mid-phase window, the expected value of the integral is proportional to the absolute value of the timing error. The final estimate of timing error is made by the phase detector logic circuits. For simplicity in design of the loop filter, the phase estimate is quantized to only one bit, which causes a loop signal-to-noise ratio degradation of less than 2 db compared to the perfect digitization case. The timing error estimate is zero if no transition is detected, and +1 or -1 whenever a transition is detected, depending on the sign of the mid-phase integral and the direction of the transition.

The improved phase detector results in a higher signal-to-noise ratio (SNR) at the phase detector output, and hence a higher loop SNR and lower synchronization error. Compared to more conventional transition tracking phase detectors, the improvement in signal-to-noise ratio at the phase detector output is 3 to 9 db. The significance of the improved phase detector is that better synchronization is attained without lowering the loop bandwidth. This is especially important when acquisition times or Doppler rates are important.

The components of the loop filter output are generated separately in the digital domain, and then converted to analog voltages and summed in an operational amplifier; the summation is performed by an up-down counter which acts as a perfect integrator.

The loop bandwidth is controlled by varying the two gains of the digital filter. Initial acquisition of symbol synchronization may be achieved by increasing

D

the gains, thus widening the loop bandwidth, and selecting the VCO center frequency such that the frequency error between the symbol rate and the VCO frequency is less than the loop bandwidth. When symbol lock is achieved, the loop bandwidth is narrowed to give better tracking performance.

## Notes:

- 1. The digital transition tracking loop would be useful in digital communications applications, such as long distance telephone or microwave-linked computer-to-computer or computer-to-input/output data therminal hookups. Information concerning this innovation would be of interest to the designers and manufacturers of computers, peripheral data processing equipment, and communications equipment.

- 2. No additional documentation is available. Specific questions, however, may be directed to:

Technology Utilization Officer NASA Pasadena Office 4800 Oak Grove Drive Pasadena, California 91103 Reference: B70-10009

### Patent status:

This invention is owned by NASA, and a patent application has been filed. Royalty-free, nonexclusive licenses for its commercial use will be granted by NASA. Inquiries concerning license rights should be made to NASA, Code GP, Washington, D.C. 20546.

Source: T. O. Anderson, W. C. Lindsey

and W. J. Hurd of Caltech/JPL under contract to NASA Pasadena Office (NPO-10844)