August 1969

## Brief 69-10271

## NASA TECH BRIEF

NASA Tech Briefs are issued to summarize specific innovations derived from the U.S. space program, to encourage their commercial application. Copies are available to the public at 15 cents each from the Clearinghouse for Federal Scientific and Technical Information, Springfield, Virginia 22151.

Improved Method of Fabricating Planar Gallium Arsenide Diodes

An improved, simple method has been devised for fabricating electroluminescent (light-emitting) planar P-N GaAs (gallium arsenide) diodes. The planar-type GaAs diode emits substantially equal amounts of light from its P and N sides, whereas the light from the P side of a common mesa-type GaAs electroluminescent diode has approximately half the intensity as the light from the N side of a mesa-type diode made by diffusing P-type impurities into the entire surface of the Ntype GaAs wafer to form a P-N junction. The lower intensity of light from the P side of such a mesa-type GaAs diode is due to the fact that the light absorption coefficient of the P-type material is much higher than that of the original N-type GaAs.

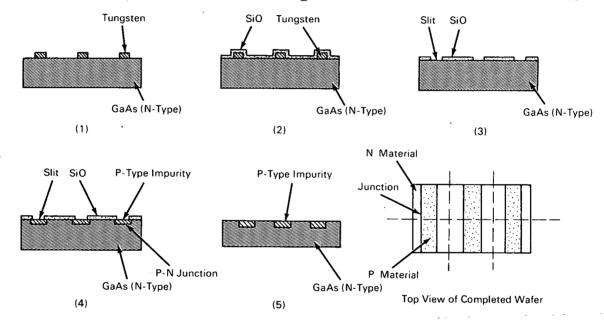

Conventional techniques for fabricating other types of planar diodes cannot be used in fabricating a planar GaAs diode. For example, silicon dioxide, which is extensively used as a maskant in the fabrication of planar silicon diodes and other semiconductive components, cannot be thermally grown on GaAs or evaporated onto it at a temperature low enough (below about 400°C) to prevent the dissociation of the GaAs. In the new method, the GaAs is masked with SiO (silicon monoxide) to allow P-type impurities to be diffused in unmasked portions of the GaAs to form P-N junctions. The deposition of SiO is performed below the dissociation temperature of GaAs. A first step (1) in fabricating the planar GaAs diode is to place on the GaAs wafer a number of strips of material (e.g., tungsten) which do not react with GaAs or SiO. In the second step (2), a layer (5000 to 8000 angstroms) of SiO is vapor-deposited over the tungsten strips and

Government assumes any liability resulting from the use of the information contained in this document, or warrants that such use will be free from privately owned rights.

<sup>(</sup>continued overleaf)

This document was prepared under the sponsorship of the National Aeronautics and Space Administration. Neither the United States Government nor any person acting on behalf of the United States

exposed surface of the GaAs wafer. In step (3), the tungsten strips with the SiO deposit on them are removed, leaving a series of unmasked openings or slits in the SiO deposit on the GaAs wafer. In step (4), Ptype impurity, such as zinc or cadmium, is diffused into the GaAs wafer through the slits, forming P-N junctions. After the diffusion is completed, the SiO mask is etched away, step (5), with an appropriate solution (e.g., a hot concentrated solution of hydrofluoric acid) and washed with water. The resultant wafer may be divided into smaller segments or chips to form a number of individual diodes. For example, the dotted lines in the top view of the completed wafer indicate the division of the wafer into six diodes, each with a channel-like diffusion of P material in the surface of N-type GaAs.

## Note:

Documentation is available from: Clearinghouse for Federal Scientific and Technical Information Springfield, Virginia 22151 Price \$3.00 Reference: TSP69-10271

## Patent status:

No patent action is contemplated by NASA. Source: Tsu-Hsin Yeh and M. M. Roy Jet Propulsion Laboratory (XNP-04235)