December 1967

Brief 67-10624

# NASA TECH BRIEF

NASA Tech Briefs are issued to summarize specific innovations derived from the U.S. space program, to encourage their commercial application. Copies are available to the public at 15 cents each from the Clearinghouse for Federal Scientific and Technical Information, Springfield, Virginia 22151.

### The problem:

To design an ultracompact, low-power astable multivibrator with sure-start characteristics. Slowly applied or steadily increasing supply voltages often fail to trigger a multivibrator by producing "lockup" (both transistors are switched to the ON position). Standard multivibrators also lack frequency/temperature programming flexibility, and thus are not useful in changing thermal environments.

### The solution:

Use of multiple chip custom block, MIC construction to fabricate an ultracompact, low-power astable multivibrator. Careful circuit design and the design flexibility provided by materials used in MIC fabrication provide a multivibrator that (1) free runs, eliminating "lockup," (2) is triggerable, pulling into synchronization with an external signal source, and (3) permits design flexibility for controlling the frequency variations with temperature. The multivibrator (continued overleaf)

This document was prepared under the sponsorship of the National Aeronautics and Space Administration. Neither the United States Government nor any person acting on behalf of the United States Government assumes any liability resulting from the use of the information contained in this document, or warrants that such use will be free from privately owned rights. starts reliably as approximately one-third of the supply voltage is reached.

# How it's done:

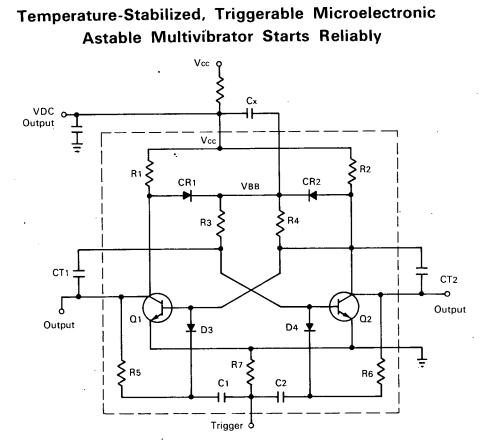

The multivibrator, packaged in a 12-pin, TO-8 MIC block, is shown inside the dashed lines of the figure.

The sure-starting circuitry, which assures that the multivibrator free runs and will not lock up when  $V_{cc}$  is applied slowly, is essentially the CR1(CR2) in series with R3(R4) dc-coupled parallel (shunt) path around CT1(CT2), timing capacitors. The timing capacitors store and apply equal voltages to the transistor bases. The transistor thresholds are reached simultaneously, producing a "lockup" condition. The dc-coupled parallel paths introduce the nonlinearities of R1, R2, R3, R4, CR1, and CR2, providing a slight initial imbalance to the transistor bases and insuring that one transistor will be biased off while the other conducts.

The synchronization feature is provided by R5(R6), C1(C2), and D3(D4) as the hybrid triggering circuit for Q1(Q2). C1 differentiates the incoming squarewave signal, while D3 conducts only during negative cycles to turn off Q1. R6, C2, and D4 serve the differentiating, steering, and blocking function for the Q2 side.

The multivibrator period vs temperature performance can be controlled to yield low thermally-caused variations, or an increase or decrease in period with increased temperature. This feature is controlled with proper selection of the timing resistor and capacitor temperature coefficients (sign and magnitude). For example: diffused resistors have a large (+) T<sub>c</sub>; thin film resistors, a small (-) T<sub>c</sub>; glass dielectric capacitors, a small (+) T<sub>c</sub>; and ceramic disk capacitors, a large (-) T<sub>c</sub>.

Using a discrete circuit as the control, the frequency variations vs temperature were compared for various resistors at -55° and +125°C. The frequency variation for a discrete circuit with mica timing capacitors is +7% at 125°C. In comparison, for boron-diffused resistors in a MIC, together with low or negative temperature coefficient timing capacitors, the variation is from -17% at  $-55^{\circ}$ C to +4% at  $125^{\circ}$ C. A multiple chip circuit version using anodized tantalum thin film resistors gave -15% at  $-55^{\circ}$ C and +33% at 125°C with glass capacitors and -20% and +48% with ceramic dielectric capacitors. With a monolithic diffused resistor circuit using negative-temperaturecoefficient ceramic dielectric capacitors, the minimum variation was obtained, -2% at  $-55^{\circ}C$  and +4% at 125°C.

## Notes:

- 1. All resistors except R3 and R4 can have 20% tolerances; however, R3 and R4 must be matched to within  $\pm 10\%$ .

- 2. Inquiries concerning this invention may be directed to:

- Technology Utilization Officer Manned Spacecraft Center Houston, Texas 77058 Reference: B67-10624

## Patent status:

Inquiries about obtaining rights for the commercial use of this invention may be made to NASA, Code GP, Washington, D.C. 20546.

> Source: W. J. Stebbins of Westinghouse Electric Corporation under contract to Manned Spacecraft Center (MSC-1173)