December 1967

# NASA TECH BRIEF

NASA Tech Briefs are issued to summarize specific innovations derived from the U.S. space program, to encourage their commercial application. Copies are available to the public at 15 cents each from the Clearinghouse for Federal Scientific and Technical Information, Springfield, Virginia 22151.

Multipulse Current Source Offers Low Power Losses and High Reliability

#### The problem:

Magnetic memory cores, frequently used in digital computational equipment, require a source of current pulses for drive power. Since the impedance of the magnetic core is a function of its direction of saturation, (i.e., information state), the current source must present a high impedance to the cores. This is usually accomplished by placing a high resistance in series with the core. This however, results in extensive power loss. In addition, the large number of semiconductor switches required decreases the reliability of the current source.

#### The solution:

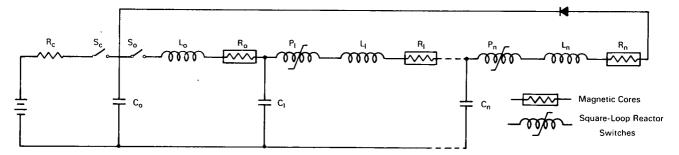

A pulse current source which uses low loss, high Q. LC circuits to provide the necessary high impedance. Square-loop reactors are used to replace the semiconductor switches.

### How it's done:

Each of the identical stages of the pulse current source serves as a high-impedance current source for the next stage. A current pulse is generated in succeeding stages when switch So is closed. Energy remaining at the final stage is returned to the initial energy storage capacitor, Co. Since the only energy dissipated in the circuit is in the switching resistance of the magnetic cores, the system is highly efficient.

The capacitor (C) of each stage will charge through the high Q inductor (L), square loop reactor (P), and magnetic core (R) of the preceding stage. When the square-loop reactor is in one saturated state it presents a high impedance to the charging current. The leakage current through the square-loop reactor will start to change its direction of saturation. The reactor switches into opposite saturation just as the capacitor becomes fully charged. In this state, the reactor presents a low impedance to the charge on the capacitor, which allows the capacitor to discharge, thereby developing a current pulse in the magnetic core. A small amount of current also flows back into the preceding stage, resetting that reactor to its original state. This process will be repeated through all of the stages until the discharge of the last capacitor  $(C_n)$  recharges Co. Due to the losses in the magnetic cores, however,  $C_0$  is not fully charged, and because of diode  $D_1$ , the last reactor  $(P_n)$  has not been reset. Co can be recharged by closing S<sub>c</sub>, and P<sub>n</sub> can be reset by placing a separate reset winding on the reactor which could be activated by the discharge of Co.

## Notes:

1. The switches shown can be replaced by electromechanical (relays) or electronic (transistors) elements. (continued overleaf)

This document was prepared under the sponsorship of the National Aeronautics and Space Administration. Neither the United States Government nor any person acting on behalf of the United States

Government assumes any liability resulting from the use of the information contained in this document, or warrants that such use will be free from privately owned rights.

- 2. This invention should be of interest to manufacturers of computer memory equipment.

- 3. Inquiries concerning this invention may be directed to:

Technology Utilization Officer Langley Research Center Langley Station Hampton, Virginia 23365 Reference: B67-10603

## Patent status:

Title to this invention has been waived under the provisions of the National Aeronautics and Space Act [42 U.S.C. 2457 (f)] to the Stanford Research Institute, Menlo Park, California 94025.

Source: Stanford Research Institute under contract to Langley Research Center

(LaRC-68)