## RICE UNIVERSITY

# Dynamic Assertion-Based Verification for SystemC

by

## **Deian Tabakov**

A THESIS SUBMITTED

IN PARTIAL FULFILLMENT OF THE

REQUIREMENTS FOR THE DEGREE

## **Doctor of Philosophy**

APPROVED, THESIS COMMITTEE:

Moshe Y. Vardi, Chair

Karen Ostrum George Professor in Computational Engineering

Kartik Mohanram Assistant Professor of

Electrical and Computer Engineering

and Computer Science

Luay Nakhleh

Associate Professor of Computer Science and Biochemistry and Cell Biology

Houston, Texas

December, 2010

#### ABSTRACT

Dynamic Assertion-Based Verification for SystemC

by

#### Deian Tabakov

SystemC has emerged as a de facto standard modeling language for hardware and embedded systems. However, the current standard does not provide support for temporal specifications. Specifically, SystemC lacks a mechanism for sampling the state of the model at different types of temporal resolutions, for observing the internal state of modules, and for integrating monitors efficiently into the model's execution. This work presents a novel framework for specifying and efficiently monitoring temporal assertions of SystemC models that removes these restrictions.

This work introduces new specification language primitives that 1) expose the inner state of the SystemC kernel in a principled way, 2) allow for very fine control over the temporal resolution, and 3) allow sampling at arbitrary locations in the user code. An efficient modular monitoring framework presented here allows the integration of monitors into the execution of the model, while at the same time incurring low overhead and allowing for easy adoption. Instrumentation of the user code is automated using Aspect-Oriented Programming techniques, thereby allowing the integration of user-code-level sample points into the monitoring framework.

While most related approaches optimize the size of the monitors, this work focuses on minimizing the runtime overhead of the monitors. Different encoding configurations are identified and evaluated empirically using monitors synthesized from a large benchmark of random and pattern temporal specifications.

The framework and approaches described in this dissertation allow the adoption of assertion-based verification for SystemC models written using various levels of abstraction, from system level to register-transfer level. An advantage of this work is that many existing specification languages can be adopted to use the specification primitives described here, and the framework can easily be integrated into existing implementations of SystemC.

# Acknowledgments

I would like to extend my sincere gratitude to my adviser Professor Moshe Y. Vardi. His guidance and support have been invaluable and his belief in me unfaltering. I cannot ever hope to repay the time and efforts that he devoted to my growth both academically and as a person; I can only hope that I will have the opportunity to pay this debt forward to a colleague or a student.

I would like to thank Dr. Kartik Mohanram and Dr. Luay K. Nakhleh for serving as members of my dissertation committee. Their questions, comments and suggestions have helped me distill the arguments and clarify the exposition. I appreciate the time and efforts that they put in reading and evaluating my dissertation and presentations.

I also thank Eli Singerman and Gila Kamhi for hosting me during my internship with Intel's Design Technology and Solutions Division. Their insightful comments and many discussions about this work have helped me understand the specification needs of the actual practitioners of dynamic verification. I would also like to acknowledge that this work was supported in part by a grant from the Intel Corporation.

I owe thanks to all past and present students in the Verification and Algorithms research groups who helped me find my bearings in the department. I have had many stimulating discussions with Seth Fogarty, Sumit Nain, Guoqiang Pan, Ben McMahan and Kristin Y. Rozier.

I owe special thanks to Ioan Şucan for his help untangling thorny C++ issues and for the countless hours we have spent in discussion and exchange of ideas.

Last but not least, I would like to thank my parents, Evelina and Todor, and my wife Linh, for their support and encouragement.

# Contents

| Abstract                         |              |                        |                                                    | ii |

|----------------------------------|--------------|------------------------|----------------------------------------------------|----|

|                                  | Ackı         | nowledg                | gments                                             | iv |

| 1                                | Introduction |                        |                                                    |    |

|                                  | 1.1          | Design                 | n crisis                                           | 1  |

|                                  | 1.2          | SystemC                |                                                    |    |

|                                  | 1.3          | Design                 | verification                                       | 5  |

|                                  |              | 1.3.1                  | Formal verification                                | 5  |

|                                  |              | 1.3.2                  | Dynamic verification                               | 6  |

|                                  |              | 1.3.3                  | Trade-offs between dynamic and formal verification | 7  |

|                                  |              | 1.3.4                  | Limitations of design verification                 | 8  |

|                                  | 1.4          | Assert                 | ion-based verification                             | 8  |

| 1.5 Contributions of this thesis |              | butions of this thesis | 11                                                 |    |

|                                  |              | 1.5.1                  | Specification primitives for SystemC               | 11 |

|                                  |              | 1.5.2                  | Monitoring framework for SystemC                   | 12 |

|                                  |              | 1.5.3                  | Automatic instrumentation of user code             | 13 |

|                                  |              | 1.5.4                  | Automatic generation of efficient monitors         | 14 |

|                                  | 1.6          | Outlin                 | e of the thesis                                    | 14 |

| 2                                | Fur          | ndam                   | entals of SystemC                                  | 16 |

|                                  | 2.1          | Systen                 | nC as a modeling language                          | 18 |

|                                  |              | 2.1.1                  | Modules                                            | 18 |

|                                  |              | 2.1.2                  | Hierarchical modules                               | 20 |

|                                  |              | 2.1.3                  | Interfaces, ports, and channels                    | 22 |

|   |     | 2.1.4                                  | SystemC events                                     | 29 |

|---|-----|----------------------------------------|----------------------------------------------------|----|

|   |     | 2.1.5                                  | Data types                                         | 31 |

|   | 2.2 | System                                 | nC as a simulation environment                     | 32 |

|   |     | 2.2.1                                  | Parallel execution                                 | 32 |

|   |     | 2.2.2                                  | Signals and channels                               | 33 |

|   |     | 2.2.3                                  | Delta notifications and delta-cycles               | 34 |

|   |     | 2.2.4                                  | Timed notifications and advance of simulation time | 34 |

|   |     | 2.2.5                                  | The start of a simulation                          | 35 |

|   |     | 2.2.6                                  | Simulation semantics of SystemC                    | 35 |

|   | 2.3 | Summ                                   | ary and discussion                                 | 37 |

| 3 | Spe | ecifica                                | ation Primitives for SystemC                       | 38 |

|   | 3.1 | Existin                                | ng languages                                       | 38 |

|   |     | 3.1.1                                  | Brief history of assertion language standards      | 38 |

|   |     | 3.1.2                                  | Overview of PSL                                    | 40 |

|   |     | 3.1.3                                  | Overview of SystemC Verification Standard          | 41 |

|   |     | 3.1.4                                  | Overview of NSCa and TLA                           | 41 |

|   | 3.2 | Related work                           |                                                    |    |

|   | 3.3 | 3.3 Deficiencies in existing languages |                                                    | 43 |

|   |     | 3.3.1                                  | Inflexible abstraction levels                      | 43 |

|   |     | 3.3.2                                  | Lack of mechanisms for user-code specification     | 44 |

|   |     | 3.3.3                                  | Lack of definition of execution trace              | 45 |

|   | 3.4 | Kerne                                  | l-level primitives                                 | 46 |

|   |     | 3.4.1                                  | Kernel phases                                      | 46 |

|   |     | 3.4.2                                  | SystemC events                                     | 49 |

|   | 3.5 | User n                                 | nodel primitives                                   | 50 |

|   |     | 3.5.1                                  | Class data members                                 | 50 |

|   |     | 352                                    | Statement-level primitives                         | 50 |

|                                 |     | 3.5.3 Function calls                                     | 50 |

|---------------------------------|-----|----------------------------------------------------------|----|

|                                 | 3.6 | Library code state                                       | 51 |

|                                 | 3.7 | Execution trace                                          | 52 |

|                                 | 3.8 | New specification primitives                             | 53 |

|                                 |     | 3.8.1 Kernel-level primitives                            | 54 |

|                                 |     | 3.8.2 User-code primitives                               | 56 |

|                                 | 3.9 | Using primitives as clock expressions                    | 60 |

| 3.10 Summary and discussion     |     |                                                          | 62 |

| 4                               | Mo  | nitoring Framework for SystemC                           | 64 |

|                                 | 4.1 | Introduction and motivation                              | 64 |

|                                 |     | 4.1.1 Exposing the simulation semantics                  | 64 |

|                                 |     | 4.1.2 A model implementing squaring via addition         | 65 |

|                                 |     | 4.1.3 A model implementing an airline reservation system | 68 |

|                                 | 4.2 | Related work                                             | 70 |

| 4.3 Modifications of the kernel |     | Modifications of the kernel                              | 72 |

|                                 |     | 4.3.1 Determining when monitors are activated            | 73 |

|                                 |     | 4.3.2 Handling communication with monitors               | 75 |

|                                 | 4.4 | Instrumentation of the MUV                               |    |

|                                 | 4.5 | 5 Experimental results                                   |    |

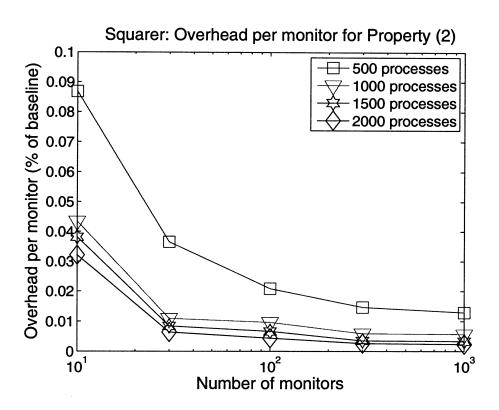

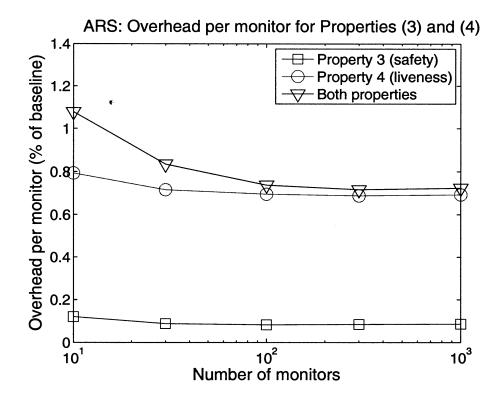

|                                 |     | 4.5.1 Framework overhead                                 | 80 |

|                                 |     | 4.5.2 Monitoring overhead                                | 80 |

|                                 |     | 4.5.3 Airline reservation system                         | 84 |

|                                 | 4.6 | Summary and discussion                                   | 87 |

| 5                               | Ası | pects of Temporal Monitoring of SystemC                  | 88 |

|                                 |     | Introduction and motivation                              | 88 |

|                                 |     | Preliminaries                                            | 90 |

|                                 |     | 5.2.1 Aspect-Oriented Programming                        | 90 |

|   |     | 5.2.2  | Monitoring framework                              |

|---|-----|--------|---------------------------------------------------|

|   | 5.3 | Relate | ed Work                                           |

|   | 5.4 | User-c | ode primitives                                    |

|   |     | 5.4.1  | Exposing function calls                           |

|   |     | 5.4.2  | Exposing function execution                       |

|   |     | 5.4.3  | Exposing function parameters and return values 94 |

|   |     | 5.4.4  | Exposing syntax                                   |

|   |     | 5.4.5  | Exposing private variables                        |

|   | 5.5 | Imple  | mentation                                         |

|   |     | 5.5.1  | Exposing function calls                           |

|   |     | 5.5.2  | Exposing function execution                       |

|   |     | 5.5.3  | Exposing function parameters and return values    |

|   |     | 5.5.4  | Exposing syntax                                   |

|   |     | 5.5.5  | Exposing private variables                        |

|   | 5.6 | Exper  | imental evaluation                                |

|   | 5.7 | Summ   | ary and discussion                                |

| _ | _   |        |                                                   |

| 6 | _   |        | ed Temporal Monitors 107                          |

|   | 6.1 | Introd | uction and motivation                             |

|   | 6.2 | Relate | ed work                                           |

|   | 6.3 | Theor  | etical background                                 |

|   |     | 6.3.1  | Bad prefixes                                      |

|   |     | 6.3.2  | Automata on infinite words                        |

|   |     | 6.3.3  | Automata on finite words                          |

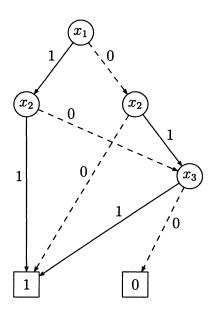

|   |     | 6.3.4  | From NFW to monitors                              |

|   | 6.4 | Monit  | or generation                                     |

|   |     | 6.4.1  | State minimization                                |

|   |     | 6.4.2  | Alphabet representation                           |

|   |                          | 6.4.3                        | Alphabet minimization                         | . 117 |

|---|--------------------------|------------------------------|-----------------------------------------------|-------|

|   |                          | 6.4.4                        | Monitor encoding                              | . 118 |

|   |                          | 6.4.5                        | Configuration space                           | . 127 |

|   | 6.5 Experimental setup   |                              | imental setup                                 | . 127 |

|   |                          | 6.5.1                        | SystemC model                                 | . 127 |

|   |                          | 6.5.2                        | Properties                                    | . 128 |

|   | 6.6 Experimental results |                              | imental results                               | . 130 |

|   |                          | 6.6.1                        | State minimization                            | . 131 |

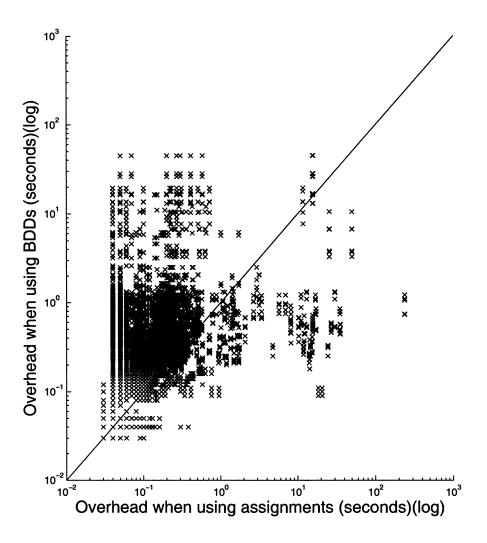

|   |                          | 6.6.2                        | Alphabet representation                       | . 131 |

|   |                          | 6.6.3                        | Alphabet minimization                         | . 131 |

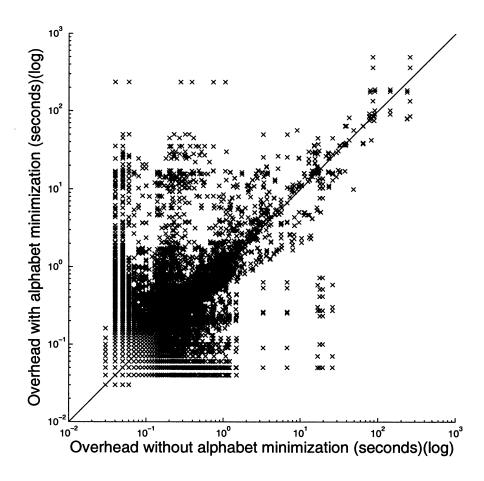

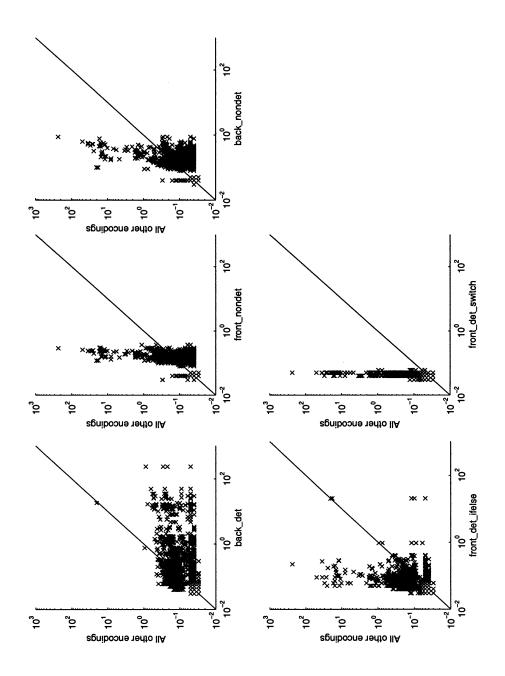

|   |                          | 6.6.4                        | Monitor Encoding                              | . 132 |

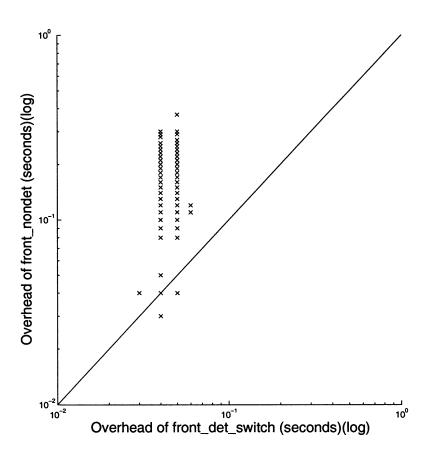

|   |                          | 6.6.5                        | Best configuration                            | . 134 |

|   | 6.7                      | Summ                         | ary and discussion                            | . 136 |

|   |                          |                              |                                               |       |

| 7 | Coı                      | nclusi                       | on and Perspectives                           | 140   |

|   | 7.1                      | 7.1 Summary of contributions |                                               | . 140 |

|   | 7.2                      | 7.2 Adopting the framework   |                                               | . 142 |

|   |                          | 7.2.1                        | Adopting the new specification primitives     | . 142 |

|   |                          | 7.2.2                        | Exposing the operations of the SystemC kernel | . 143 |

|   |                          | 7.2.3                        | Exposing user code primitives                 | . 143 |

|   |                          | 7.2.4                        | Generating efficient monitors from properties | . 143 |

|   | 7.3                      | Future                       | e directions                                  | . 144 |

| A | Sou                      | irce c                       | ode of the Adder model                        | 146   |

|   |                          |                              |                                               |       |

# Chapter 1

## Introduction

## 1.1 Design crisis

One logarithmic graph with 4 data points on a straight line led to the following observation in a 1965 issue of the *Electronics* magazine:

The complexity for minimum component costs has increased at a rate of roughly a factor of two per year [...] Certainly over the short term this rate can be expected to continue, if not to increase. [Moo65]

The author of these now famous words was Gordon Moore, a chemist and a physicist, and co-founder of Intel Corp. 10 years later, Moore updated his prediction, stating that "the new slope might approximate a doubling every two years, rather than every year." [Moo75]

In the decades since, Moore's Law has been widely misunderstood and often misquoted, and has been invoked when discussing capacities of dynamic RAM modules and hard disk drives, the computational power of microchips, and the number of megapixels in consumer digital cameras. In a 1995 speech, Gordon Moore looked back over the 30 years since he first stated his famous "law", and joked:

The definition of "Moore's Law" has come to refer to almost anything related to the semiconductor industry that, when plotted on semi-log paper, approximates a straight line. [Moo95]

Part of the reason for the popularity of Moore's Law is its uncanny accuracy. Indeed, if we plot the number of transistors on commodity processors versus time, starting with the early designs in 1960 and going through the latest microprocessor from the Itanium family<sup>1</sup>, the curve is clearly exponential. However, as our ability to put more transistors on a die has increased, so has the complexity of the designs. Addressing the increasing complexity has led to an increasing level of abstraction in designs.

In the 1960s and 1970s it was possible to design circuits at the transistor level. As the circuits grew bigger, designers started thinking in terms of gates. In the 1990s, tools for automatic synthesis of gate-level designs allowed the practitioners to adopt an even higher level of abstraction: Register Transfer Level (RTL). This move was widely acclaimed as a revolution of the design process [Fos08].

However, in the 2000s a new type of devices started to become more commonplace, for example, cell phones, network routers, and smartcards, collectively called systems-on-chip (SoC). A SoC often consists of more than one processor, and contains on-chip and external memory, analog and digital signal processors, peripheral devices, and complex on-chip buses. Such systems are often capable of running a modern operating system such as GNU Linux or Windows Mobile. The software and the hardware of such systems are tightly connected, with the software both controlling the hardware, and requiring it to run. Designing and debugging software for such systems is a difficult task by itself, usually requiring many months and even years. Shrinking time-to-market made it all but impossible to wait for the hardware to be designed, taped out, and for the first prototypes to roll off the production floor, before starting to design the software. Instead, there is increasing pressure to co-design the hardware and the software together, a task not well suited for RTL.

Another problem with RTL is that a micro-architecture is usually specified by a natural language document, referred to as the *micro-architectural specification* (MAS) [Var07]. It is increasingly difficult to design RTL from such informal and

<sup>&</sup>lt;sup>1</sup>At the time of writing of this thesis, the latest Intel microprocessor was Tukwila, with more than 2 billion transistors on a single die

often underspecified documents. Moreover, if there are errors in the RTL, it is almost impossible to determine whether the error was in the original design, or in the translation of the design from MAS to RTL, as the RTL serves as both the microarchitectural model and its implementation [Var07].

The divergence between what engineers could put on the chip and what the designers could simulate and verify, has been increasing, leading Gadi Singer, one of Intel's Vice Presidents, to issue a call to action for the electronic design automation (EDA) industry:

We have a very good flow generally to go down from RTL to layout. However, RTL was established two decades ago. Since then, complexity has grown severalfold and the EDA industry has not provided a similar level of support for design and refinement at the next level. This is a level that is an absolute requirement to deal with the growing complexity [Goe05].

The need to move beyond the register transfer level motivated academic and industrial research into language for "system-level" design. A new language would ideally support specification and design at various levels of abstraction, incorporation of embedded software, and creation of executable specifications. One of the most popular languages that were intended to answer the needs of the design community is SystemC.

# 1.2 SystemC

SystemC (IEEE Standard 1666-2005) is both a modeling and a simulation language: designs can be created with various levels of details, and then they can be compiled into executables using standard C++ compilers<sup>2</sup>. The core language consists of macros for modeling fundamental components of hardware designs, such as modules and signals. SystemC also provides hardware-oriented data types like 4-valued logic

<sup>&</sup>lt;sup>2</sup>A detailed introduction to SystemC follows in Chapter 2.

and arbitrary-precision integers. The implementation of SystemC distributed by the Open SystemC Initiative (OSCI) also provides a reference simulator that is linked to the user code and drives the simulation. Various vendors supply their own simulators, which provide additional support for debugging and co-simulation with other hardware description languages.

One of the reasons for SystemC's success is that it allows designers to model systems at several abstraction levels, from the most concrete (gate level) through the most abstract (system level) [GLMS02]. Individual components can be replaced freely without affecting the rest of the design, thus allowing the engineers to investigate alternative approaches and new ideas. This also allows the design process to be parallelized, with different teams working on different components simultaneously.

As a simulation framework, SystemC provides an event-driven environment, where important occurrences like writing to a signal, a clock tick, or a token being consumed from a channel are each represented by an event. Synchronization between events and processes is done behind the scenes by SystemC's simulation kernel. The kernel keeps track of events, schedules processes to run, and updates the values of signals and channels in a fashion that mimics concurrent execution, even though in reality the processes are run sequentially. The seamless integration between hardware-like components (modules, signals) and software (processes) makes SystemC a prime choice for prototyping and testing hardware and hybrid systems early in the design process [CA02].

The object-oriented encapsulation of classes in C++ is naturally extended in SystemC to protect each module's internal data members (representing local memory) from other modules and processes, except through explicitly defined interfaces. C++'s inheritance capabilities allow for the creation of modular designs in SystemC, which, in turn, facilitate reuse and make IP transfer possible [BGM04].

Various libraries provide further functionality. For example, a popular library called TLM (short for Transaction-Level Modeling) defines channels, interfaces, and

protocols that streamline and standardize the development of high-level models in which complex communication and protocols are reduced to a single "transaction". These factors have helped propel SystemC as a *de facto* industry-wide standard modeling language, less than a decade after its first release, and with this increase in use came the increasing need to verify the designs written in SystemC.

## 1.3 Design verification

Before we can check if the behavior of a design is correct, we need to have a "yardstick" against which the behavior is compared. Behavior of the design over time is often expressed using temporal formulas [Pnu77]; in his dissertation such temporal formulas are called *properties* of the design. A *specification* is a set of asserted properties, which describe intended behavior of the system. Informally, the goal of design verification is to ensure that the actual behavior of the design is consistent with its specification. If an inconsistency is discovered, the verification tool can usually produce a *witness* of the violation: a trace which corresponds to an execution of the model and which violates the specification. There are two major directions of research in this field: formal verification and dynamic verification.

### 1.3.1 Formal verification

One feature that all formal verification methods share is that they produce a mathematical proof that the design can never violate the specification. If the design is not written in a formalism with formal semantics, it needs to be translated before model checking can be applied. Practical application is limited to small blocks that contain mostly control logic such as state machines, as opposed to blocks that are used to transform data, such as multipliers [CH07].

One common application of formal verification is in *equivalence checking*: showing that two models have the same behavior. Usually it is done after a refinement step or after some optimizations (e.g., clock-tree synthesis) to ensure that the functionality

of the model or the circuit is still correct [Ber03]. In these cases the old model serves as a specification for the new one. Equivalence checking can also be used to verify the correctness of the output of the synthesis tool, for example, when synthesizing netlists from RTL.

### 1.3.2 Dynamic verification

While formal verification checks if all executions of the system conform to the specification, dynamic verification checks if a particular execution of the model conforms to the specification. This approach involves executing the model under verification (MUV) in some environment, while running checkers in parallel with the model. The checkers typically monitor the inputs to the MUV and ensure that the behavior or the output is consistent with the expected behavior or output and, if a violation is detected, return the trace of execution leading to the violation. Dynamic verification is weaker than formal verification because it provides no guarantees that the system can never violate the specification. It is sometimes called "functional verification" (see, e.g., [Ber03, Fos08, Piz07]) and "runtime verification" (see, e.g., [CR07, LS09]). This thesis uses the term "dynamic verification" to highlight the distinction from "formal verification".

There are two major approaches to dynamic verification: *black box* and *white box*. The difference is mainly in the amount of information exposed to the verification framework:

• Black box. When using this paradigm, dynamic verification is performed without any knowledge of the details of implementation of the design. All verification is done through explicitly declared interfaces. A disadvantage of using this approach is that an error may occur inside the design without manifesting itself at the interface. However, an advantage of using black box dynamic verification is that the verification effort does not depend on the specific implementation. Pure black-box dynamic verification is impractical for large designs because

they have too many internal signals and states to effectively verify all of the functionality from the periphery [Ber03]. Black box verification is mostly used to specify the behavior of third-party designs and libraries.

• White box. This method gives the verification framework full access to the internal structure and implementation of the MUV. Verification efforts can focus on specific blocks or individual functions. In case an error is detected, it is reported sooner than when using black box verification, and it is usually easier to identify the incorrect implementation. White box dynamic verification requires detailed knowledge of the implementation of the design, which is often available only to the engineers who are writing the model.

### 1.3.3 Trade-offs between dynamic and formal verification

- Capacity vs. Completeness. Formal verification has capacity limits and is best applied to small blocks with critical importance (for example, arbiters and bus controllers). Even small models can have a large state space, which makes formal verification intractable. Dynamic verification has fewer capacity limitations, however, it cannot provide a complete verification solution. In contrast to formal verification, dynamic verification does not constitute proof that the model conforms to the specification, and corner cases may remain unexercised, resulting in undiscovered bugs.

- Formal semantics. Formal verification requires that the model has well defined formal semantics. In particular, C++ is known to lack formal semantics [Vel05], which means that formal verification methods are restricted to a subset of C++. As a consequence, formal verification of SystemC requires that the model be translated to another language (e.g., abstract state machines [GHT04]) with formal semantics.

## 1.3.4 Limitations of design verification

Although design verification is crucial for uncovering design or implementation bugs, successful application requires good understanding of its limitations. One possible source of frustration comes from specification errors: a specification may misrepresent the design intent, thus triggering a false positive. Software engineers have faced this issue for decades: in 1990 Moser and Melliar-Smith wrote

"Even carefully written formal specifications are prone to error, and experience has shown that unverified specifications are comparable in reliability to untested programs [MMS90]."

Lam goes even further and claims that even "missing specifications" can be considered a type of specification errors [Lam05].

Another issue is that in most applications, specifications do not provide complete functional coverage. This means that even if the specifications have been proven to hold in full, there may still be undetected errors. The correctness of the model is not an absolute measure; it is always with respect to specific specification of its behavior.

## 1.4 Assertion-based verification

Monitors (also called "functional checkers" or just "checkers") are used as aids for dynamic verification. In the late 1990s, manually written monitors were a traditional part of the simulation environment (see, e.g., [GBA+99]). Typically, a monitor observes the execution of the MUV and issues a warning or terminates execution if the observed behavior deviates from the expected behavior. In cases when deviation is observed, the problem and its source are easier to identify and debug. Furthermore, using monitors automates the analysis of the tests results and allows a large number of random test vectors to be executed without the need for immediate attention by a verification engineer. The disadvantage is that writing and maintaining monitors

manually is an expensive and laborious process, and for intricate specifications it is very easy to make mistakes when constructing the monitor by hand.

Automated monitor generation was first proposed by Abarbanel et al. [ABG+00], who used the FoCs tool to generate VHDL monitors from specifications written in a temporal language based on Computation Tree Logic (CTL) and regular expressions [BBL98]. Their overall experience with FoCs was very favorable, particularly because it allowed to "[leverage] the same formal rules for model checking of small design blocks as well as for simulation analysis across all higher simulation levels." [ABG+00].

The advantage of automatic generation of monitors from specifications was acknowledged almost immediately by the industry (see, e.g., US Patent 6591403, "System and method for specifying hardware description language assertions targeting a diverse set of verification tools" [BF03], which was submitted in October 2000). The term "assertion-based verification" (ABV) started to be used in white papers from the electronic design automation (EDA) vendors in 2002 (see, e.g., [Syn02]), in peer-reviewed papers in 2003 (see, e.g., [NdPF $^+$ 03]), and in books in 2003 (e.g., [FKL03]). The industry also recognized the need for temporal languages that can express properties related to ongoing behavior, such as p must hold until q is true [AFF $^+$ 02]. Assertions are most commonly used to facilitate verification, hence the name assertion-based verification. Some authors even prefer using the term assertion-based design to emphasize the idea that assertions should be introduced in the earliest stages of the design process [BZ08, FKL03].

Among the several advantages of using ABV is the modular nature of assertions: each one is a partial specification of the system, and those specifications can be added incrementally, as time permits. Designs with thousands of assertions are not uncommon [BZ08], and the only practical way to build such a set of specifications is to add them to the design and to debug them one at a time.

Another advantage of using ABV is that once the assertions have been added to a particular design, they can be reused across different refinement steps (with possible minor modifications to the sampling rate; see Chapter 3 for a full discussion). Some designs are constructed with reuse in mind and the associated assertions serve both as a formal description of the design, as well as constraints on the inputs that detect and reject incorrect usage.

A further benefit of using ABV in the initial specification of the design is that the assertions allow the verification and the design teams to base their work on a common set of formal properties. This usage of assertions supplements the natural language description of the design, and is an important part of the documentation of the design.

A successful ABV solution requires three components:

- A formal declarative language for expressing assertions and a formal definition of a trace of execution. The semantics of some temporal operators can only be defined with respect to an execution trace.

- 2. A monitoring framework capable of observation of the execution trace. This includes both the ability to decide the truth value of any atomic formula, and the ability to sample the values of atomic formulas at all states on the execution trace.

- 3. A mechanism for automatic generation of monitors from specifications. The monitor must detect all finite executions of the model that violate the property.

This thesis addresses all of these issues and provides a complete framework for applying assertion-based verification to SystemC. Components of the framework are discussed briefly in this chapter, and at length in the subsequent chapters.

## 1.5 Contributions of this thesis

## 1.5.1 Specification primitives for SystemC

There have been a few attempts to adapt temporal specification languages to SystemC (see discussion of related work in Chapter 3), but they suffer from several drawbacks. Previous works do not address the most fundamental issue for temporal specification languages: a precise definition of a trace of execution. Moreover, existing temporal specification languages cannot handle the different levels of abstraction that may coexist in a single SystemC design, and cannot be adapted easily as the model is refined. Another issue is that existing temporal specification languages for SystemC focus on the hardware-oriented nature of SystemC and ignore the fact that SystemC models both hardware and software.

This thesis describes a new approach to defining temporal languages for SystemC. The starting point is a precise definition of a SystemC trace. Intuitively, a trace is a sequence of states in the execution of the model. Defining this notion precisely for SystemC is nontrivial because it requires finding a good abstraction of the simulation semantics of SystemC. It is then argued that modern specification languages fail to identify important Boolean properties relevant to the execution of SystemC models. This thesis proposes enriching the Boolean layer with a new set of atomic propositions, exposing the operations of the SystemC kernel, as well as the control flow and the syntax of the user code, thereby making the temporal specification language more expressive. Finally, this work leverages the fact that the clock-sampling mechanism available in modern temporal specification languages offers a way to express temporal properties at different levels of abstraction. A fine sampling would correspond, for example, to subcycle-level abstraction, while coarser sampling would correspond, for example, to transaction-level abstraction. Since any Boolean expression can be used as a clock expression, the additions to the Boolean layer that is proposed here also provides a much finer control over the temporal resolution.

The new primitives proposed in this dissertation are at the Boolean layer and can be added easily to existing temporal specification languages such as PSL [PSL07]; all that is needed is to adapt the underlying syntax for state assertions. The main feature of the resulting framework is the ease with which properties can be expressed at different levels of abstraction, without having to use different languages. This contribution was published as [TVKS08].

## 1.5.2 Monitoring framework for SystemC

The traditional approaches to dynamic verification involve connecting a separate checker module in parallel with the MUV for each property to be checked. The difficulty of applying this approach to SystemC is that it only allows monitoring the state of the model when control is passed to the checker module. Thus, this approach cannot be applied to monitor properties that refer to finer temporal resolution, e.g., referring to a particular SystemC event. This dissertation argues that the specification primitives discussed earlier require that certain nominal information about the kernel, specifically, kernel phases and event notification, has to be exposed to the monitors.

Once it becomes clear that the SystemC kernel needs to be exposed, the two key questions are how to do it with small changes to an existing implementation, and how to avoid performance penalties. On one hand, optimizing for performance alone would require direct modification of the existing source code to hook the new functionality to the existing data structures. This would require the monitoring framework to be rewritten for each SystemC implementation, limiting portability. On the other hand, optimizing for portability would require adding a layer of indirection that abstracts away the concrete implementation of the SystemC kernel, which would slow down the execution. Since each optimization affects negatively the other, the challenge is to find a good balance between the two. This thesis describes an approach that accomplishes both small change and low performance overhead. The necessary

changes to the SystemC code are modularized to make it easy and fast to modify existing implementations. The framework can easily adapt to changes in the SystemC semantics that may be added in future releases.

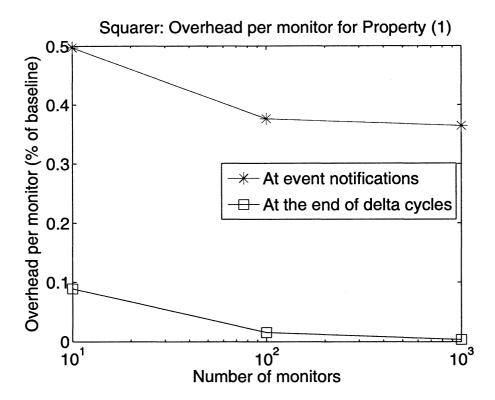

This dissertation shows that monitoring SystemC properties using the framework presented here has reasonable overhead (0.05% – 1% per monitor) and that the marginal cost of additional monitors decreases. As proof of concept, the framework is used to specify and check properties of two SystemC models. Based on the empirical results it is argued that the additional expressive powers and flexibility of the framework does not incur a prohibitive performance hit. This contribution was published as [TV10a].

#### 1.5.3 Automatic instrumentation of user code

The benefits of object-oriented encapsulation and data hiding inherent in SystemC are deterrents for effective monitoring. Access to internal variables is granted only to the objects' own processes and is denied to the monitors, which execute as external processes. A key requirement for monitoring the specification language primitives described earlier is allowing monitoring processes access to all internal variables, even those marked **protected** or **private**. The third contribution of this work is defining a simple yet powerful approach for exposing the execution flow, the syntax, and the state of the user code, without requiring extensive annotation or manual instrumentation from the model designers.

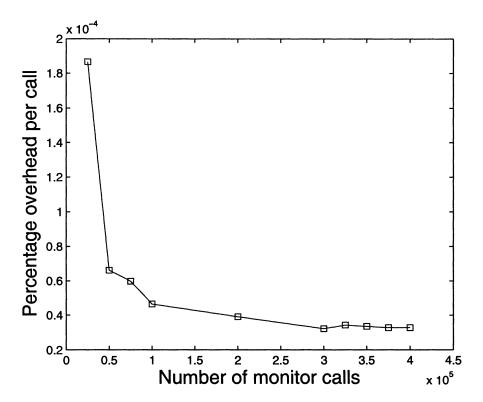

The approach presented here uses Aspect-Oriented Programming (AOP) [KIL+97] techniques to expose function calls and returns, the actual parameters passed to functions, the return values of functions, and the precise instances when the function execution starts and ends. In addition, the approach presented here allows identifying, via regular expressions, any line or a set of lines of code, and exposing them to the monitoring framework as atomic propositions. Empirical results show that the overhead due to automated instrumentation of the user code is very low ( $\sim 0.5 \times$

$10^{-4}\%$  of baseline execution time per monitor call).

## 1.5.4 Automatic generation of efficient monitors

The last component of assertion-based verification for SystemC calls for a method for generating runtime monitors from formal properties. For simple properties it may be feasible to write the monitors manually; however, in most industrial workflows, writing and maintaining monitors manually would be an extremely high-cost, labor-intensive, and error-prone process. This work uses existing approaches to construct a Deterministic Finite Word automaton (DFW) from a temporal property, such that the automaton accepts the finite traces that violate the property. Many works have elaborated on that approach; this thesis follows the algorithm presented in [dR05].

Most of prior work on this subject has focused on the underlying algorithmics or on heuristics to generate smaller monitors or on fast monitor generation. In this thesis the focus is shifted toward optimizing the runtime overhead that monitor execution adds to simulation time. This reflects more accurately the priorities of the industrial applications of monitors. A large SystemC model may be accompanied by dozens and even hundreds of monitors, so lower runtime overhead is a crucial optimization criterion, much more than monitor size or monitor-generation time. This work identifies several algorithmic choices that need to be made when generating temporal monitors for SystemC and presents extensive experimentation to identify the configurations that lead to superior performance. We investigate the effect of individual optimizations on the runtime overhead of monitors, leading to the identification of a combination of optimizations that exhibits the best overall performance. This contribution was published as [TV10b].

## 1.6 Outline of the thesis

Chapter 2 gives introduction to SystemC and discusses its simulation semantics. Chapter 3 presents new specification primitives that allow existing temporal languages to handle a rich set of SystemC properties. The mechanisms for exposing the operations of the SystemC kernel are described in Chapter 4. Chapter 5 presents techniques for automating the instrumentation of the user code, and Chapter 6 shows how to generate efficient monitors. Conclusions and future work are described in Chapter 7.

,

# Chapter 2

# Fundamentals of SystemC

SystemC is a system-level design framework that is capable of handling both hardware and software components. It allowed a designer to combine complex electronic systems and control units in a single model, to simulate and observer the behavior, and to check if it meets the performance objectives. In 2005 the SystemC language reference manual (LRM) was ratified as IEEE 1666-2005 standard.

In the past, the design process for embedded systems has been mostly serial, moving from the architecture designers to the hardware designers to the hardware verification team and finally to the software team, and each team has been using a different language to implement and refine their portion of the design. This approach is known as "waterfall schedule" among project managers [BD05]. Such workflows may work for designs consisting of a few thousands of lines of RTL code, but it quickly becomes inefficient when the designs get bigger and more complex.

Many contemporary systems consist of application-specific hardware and software, and tight production cycles make it impossible to wait for the hardware to be manufactured before starting to design the software. In a typical system-on-chip [CCH+99], for example, a cell phone, there are hardware components that are controlled by software. In addition, many hardware design decisions, for example, numeric precision or the width of communication buses, are determined based on the needs of the software running on them. This has led to a design methodology where hardware and software are co-designed in the same abstract model. The partitioning between what will be implemented in hardware and what will be written as software is intentionally left blurry at the beginning, allowing the designers the ability to consider different

configurations before committing a functional block to silicon or C.

One of the reasons for SystemC's popularity is its ability to parallelize the design process. SystemC allows blocks implemented at different abstraction levels to run together in the same model. Different components can be refined in parallel, using the abstract model as a blueprint showing how the different blocks interact. Communication between modules is specified using well-defined interfaces, which allows two blocks that conform to the same interface to be swapped seamlessly. This gives designers the ability to explore alternative approaches early in the design process, before committing to a particular architecture.

In the strict sense of the word, SystemC is not a new language. In fact, it is a library of C++ classes and macros that model hardware components, like modules and channels; provide hardware-specific data types, like 4-valued logic types; and define both abstract and specific communication interfaces, like Boolean input. SystemC is built entirely on standard C++, which means that every SystemC model can be compiled with a C++ compiler. The compiled model has to be linked with a SystemC simulator (for example, the OSCI-provided reference implementation) to produce an executable program.

Software typically executes sequentially, partly because most computer architectures have a single CPU core, and partly because a single thread of execution is easier to manage by the operating system. However, in a hardware system, many components execute simultaneously. For example, when using a cellphone to make a call, we activate simultaneously a radio subsystem that handles two-way communication with the cell tower, a signal processing unit that converts voice to signal and signal to voice, and a display controller that shows details about the conversation on the screen. Simulating such a system in software requires the ability to simulate a large number of tasks executing simultaneously, and is critical for the early stages of the design.

SystemC addresses this issue by providing mechanisms for simulating (in software)

parallel execution. This is achieved by a layered approach where high-level constructs share an efficient simulation engine [GLMS02]. The base layer of SystemC provides an event-driven simulation kernel that controls the model's processes in an abstract manner. The kernel leverages a concept borrowed from hardware design languages, called *delta cycle*, to give the executing processes the illusion of parallel execution. The details of the simulation semantics of the kernel, the mechanisms for simulating parallel execution, and the way the kernel interacts with the MUV are described in the second half of this chapter.

## 2.1 SystemC as a modeling language

#### 2.1.1 Modules

SystemC modules are the most fundamental building blocks. Similar to C++ objects, modules allow related functionality and data to be incorporated into individual entities and to remain inaccessible by the other components of the system unless exposed explicitly. This allows modules to be developed independently and to be reused or sold in commercial libraries [BGM04]. As an example, the skeleton of a SystemC module is presented in Listing 2.1:

```

1 SC_MODULE(Nand) {

2    // Definitions of processes, internal data, etc

3

4    SC_CTOR(Nand) {

5         // Body of constructor, process registration,

6         // sensitivity lists, etc.

7    }

8 };

```

Listing 2.1: Skeleton code for defining a SystemC module.

In this code fragment, **SC\_MODULE** is one of SystemC's macros, which declares a C++ class named "Nand". Like any other C++ class, a module can declare local variables and functions. **SC\_CTOR** is another predefined macro that simplifies the definition of a constructor for the module. A constructor of a module serves the same

purpose as a constructor of a C++ class (i.e., initializing local variables, executing functions, etc.), but has some additional functionality that is specific to SystemC. For example, the *processes* of the module have to be declared inside the constructor. This is done using pre-defined SystemC macros that specify which class functions should be treated by the SystemC kernel as runnable processes. After declaring each process, the user can optionally specify its *sensitivity list*. The sensitivity list may include a subset of the channels and signals defined in the module, as well as externally defined clock objects or events. Whenever there is a change of value of any of the channels or signals listed in the sensitivity list, the corresponding process is triggered for execution. Listing 2.2 illustrates these concepts.

```

1 SC MODULE(Nand) {

2

// Definitions of ports

3

sc_in <bool> A, B; // Input signal ports

4

// Output signal port

sc out<bool> F;

5

6

// Definitions of processes

7

void some function() {

8

F.write( !(A.read() && B.read()) );

9

10

11

SC CTOR(Nand) {

12

// Process registration, sensitivity lists, etc.

13

SC METHOD (some function); // Indicate that this function

14

// is a ''method process''

15

sensitive << A << B;

16

}

17 };

```

Listing 2.2: A SystemC module of a NAND gate

This code fragment declares two input and one output signals of type **bool** (lines 3-4). The function some\_function() defined on lines 7-9 implements the expected functionality of the NAND gate. Nothing distinguishes this function from any other standard C++ function, until the macro on line 13 declares it to be a process. **SC\_METHOD** indicates that this process is a *method process*. When triggered, a method process executes from start to finish. In particular, a method process cannot

suspend while waiting for some resource to become available. In contrast, a thread process may suspend its execution by calling wait(). The state of the thread process at the moment of suspension is preserved, and upon subsequent resumption (for example, when the waited-for resource becomes available) the execution continues from the point of suspension. Thread processes are declared using the macro SC\_THREAD. Both thread and method processes can define a sensitivity list. Each sensitivity list declaration applies to the process immediately preceding the declaration. Line 15 indicates that the method process some\_function() should be triggered as soon as one of the input signals changes its value.

Any function that is declared as a method process can also be declared as a thread process, at the cost of simulation performance. Nevertheless, certain functionality cannot be expressed easily using method processes, so the extra cost of thread processes is outweighed by their expressiveness. For example, when a process needs to write to a buffer that is currently full, it is very common to suspend execution until the buffer becomes available. An example illustrating such processes is presented later in this chapter.

#### 2.1.2 Hierarchical modules

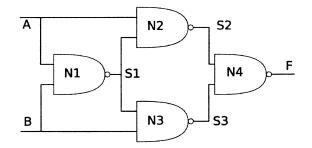

Building modules that include other modules is as easy as using C++ objects inside another C++ class. For example, we can use the model of a NAND in Listing 2.2 to design a module implementing an EXOR gate. Figure 2.1 shows how the gates need to be connected.

We need three "wires" (labeled S1, S2 and S3) to connect the inner gates to each other. The two inputs signal ports (labeled A and B) and the output signal port (F) can be connected directly to the gates, thus we do not require additional wires. Listing 2.3 shows the SystemC implementation.

```

1 SC_MODULE(Exor) {

2  // Definitions of ports

```

Figure 2.1: An EXOR gate implemented using 4 NAND gates.

```

3

sc in <bool> A, B; // Input signal ports

4

sc out<bool> F;

// Output signal port

5

6

// Four instances of the Nand module

7

Nand n1, n2, n3, n4;

8

9

// Three Boolean ''wires''

10

sc_signal<bool> S1, S2, S3;

11

12

// No definitions of processes needed. All functionality

13

// is already implemented in the NAND gates

14

SC CTOR(Exor) : n1(''N1''), n2(''N2''), n3(''N3''), n4(''N4'')

15

16

// Connect the wires

17

18

N1.A(A);

19

N1.B(B);

20

N1.F(S1);

21

22

N2.A(A);

23

N2.B(S1);

24

N2.F(S2);

25

26

N3.A(S1);

27

N3.B(B);

28

N3.F(S3);

29

30

N4.A(S2);

31

N4.B(S3);

32

N4.F(F);

33

} // End of constructor

```

34 };

Listing 2.3: A SystemC module of an EXOR gate using 4 NAND gates.

Just like the Nand module, the Exor module has two Boolean input signal ports and one Boolean output port, defined on lines 3–4. The four instances of the NAND gate are declared on line 7, and the three inner "wires" are represented by Boolean signals declared on line 10. In the constructor the wires are connected to the proper ports of the modules. For example, on lines 18-20 we connect Exor input signal A to the input port of N1 named A. Exor input signal B is connected to input port B of N1, and signal B is connected to the output port of N1, which is named B (see Listing 2.3). We connect similarly the remaining Nand modules.

Notice that there is no ambiguity between the input and output signal ports of the EXOR gate and the NAND gates, even though they all share the names A, B and F. The input ports of the NAND gates are defined inside the modules, and are accessed through the instance names of the modules, e.g., N1.A or N3.F using the C++ operator "()", while the input ports of the Exor module are defined locally and can be accessed directly. Also notice that the Exor module does not define any processes. The processes already defined in the Nand module carry out the necessary functionality. This example illustrates that complicated models can be easily built from existing components with minimal effort.

### 2.1.3 Interfaces, ports, and channels

In traditional hardware models all communication and synchronization between processes is done using signals. SystemC allows the designers to raise the level of abstraction significantly, allowing the processes to exchange arbitrary data. Communication is done using *interfaces*, *ports*, and *channels*, which work together to hold and transmit data.

#### **Interfaces**

SystemC interfaces are sets of "operations", represented by functions. Only the function name, parameter, and return value are specified, without any restrictions how the operation is to be implemented.

A commonly used interface in SystemC is sc\_signal\_in\_if<T>, which provides a virtual function virtual const T& read() const, allowing reading of arbitrary data (represented by the template argument T). Another commonly used interface, sc\_signal\_inout\_if<T>, provides a virtual function virtual void& write(const T&) = 0 that allows writing of arbitrary data of template type T. The particular way of carrying out the operations specified in the interface is determined by each channel implementing the interface.

### **Ports**

Ports in SystemC allow modules to connect to and communicate with their environment. Ports are actual objects that are instantiated inside modules, and pass communication requests from the module to the channel. Having an intermediary object that handles the communication allows the module's processes to remain ignorant about the channel that carry out the communication, as long as the processes use the correct operations as defined in the interface.

Each port declaration specifies the operations that the port is able to perform, i.e., the port's interface. For example, the following statement:

sc\_port< sc\_signal\_in\_if<bool> > p; declares a port p that can access a

channel using the functions declared in the sc\_signal\_in\_if<bool> interface.

As discussed earlier, this interface provides the operation const bool& read().

Thus, we can use the port to read a Boolean value from the channel attached to the

port by calling p.read().

In the two examples presented earlier in Listing 2.2 and Listing 2.3, the code implementing the NAND gate and the EXOR gate contains port declarations that han-

dle the communication of the module with the environment. For example, lines 3-4 in Listing 2.3 declare sc\_in <bool> A, B and sc\_out<bool> F. Here sc\_in <bool> is actually shorthand notation for sc\_port< sc\_signal\_in\_if<bool> >, and similarly, sc\_out<bool> is shorthand for sc\_port< sc\_signal\_inout\_if<bool> >. Calling A.read() and F.write() (lines 7-9 in Listing 2.2) is allowed because the corresponding ports use the sc\_signal\_in\_if and sc\_signal\_inout\_if interfaces.

#### Channels

While interfaces describe what operations are available at the ports, channels define how those operations are implemented. Different channels can implement the same interface, and one channel can implement multiple interfaces. As an example, the implementation of an EXOR gate in Listing 2.3 uses three "wires" of type sc\_signal<br/>bool> to connect the Nand modules; sc\_signal<T> is a pre-defined SystemC channel that implements both sc\_signal\_in\_if<T> and sc signal inout if<T> interfaces.

#### Producer-consumer model

The next example shows communication between modules through a shared channel. The model consists of two modules, Producer and Consumer, and they communicate using a bounded capacity FIFO. We first define the interfaces through which the modules communicate, then show the code implementing the Producer and the Consumer, and finally present the code for the FIFO.

```

1 template <class T>

2 class write_if : virtual public sc_interface {

3

4 public:

5   virtual void write(T& token) = 0;

6   virtual void reset() = 0;

7 };

```

```

8

9 template <class T>

10 class read_if : virtual public sc_interface {

11

12 public:

13  virtual T& read() = 0;

14  virtual int num_available() = 0;

15 };

```

Listing 2.4: Communication interfaces for the producer-consumer model

Listing 2.4 shows a typical SystemC interface definition. It is required that all user-defined interfaces extend **sc\_interface** (line 2, 10). In SystemC the operations allowed on the interfaces must be encoded as pure virtual functions. The implementing channel is required to provide concrete definitions of those functions.

Every second the Producer (Listing 2.5) writes a character to the FIFO with 50% probability, and every second the Consumer (Listing 2.6) reads a character from the FIFO with 50% probability. It is important to point out that the 1-second intervals apply only to simulation time and not to wall-clock time. Wall-clock time is the actual time it takes to run the compiled executable model, and simulation time reflects the apparent time as perceived by the SystemC processes in the model. In the case of the producer-consumer model we can simulate thousands of seconds of simulation time in one wall-clock second.

```

1 SC MODULE(Producer) {

2

// Definitions of ports

3

sc port< write_if<char> > out;

// Output port

4

5

// Definitions of processes

6

void producer process() {

7

const char* str = ''Hello world!'';

8

const char* p = str;

9

10

while (true) {

if (rand() % 2) {

11

12

out.write(*p);

13

p++;

14

if (!*p) {

15

p = str;

```

```

16

}

}

17

18

19

wait(1, SC_SEC);

20

}

21

}

22

23

SC CTOR(Producer) {

// Process registration, sensitivity lists, etc.

24

25

SC_THREAD(producer_process); // thread process

26

27

// No sensitivity list

28

29 };

```

Listing 2.5: A SystemC model of a Producer

The producer has only one port (line 3) that uses the interface write\_if<char> declared earlier, and only one process (lines 6-21). The infinite while-loop writes a character through the output port and then suspends itself explicitly (line 19) using a call to the built-in function wait(). Time in SystemC is defined using a numeric value and a time unit; in this case, SC\_SEC is the pre-defined unit corresponding to seconds. Since producer\_process() contains a wait() statement, it has to be declared a thread process (line 25). Also notice that no sensitivity list is needed. Once triggered, the producer\_process() never terminates, thus it will not need to be triggered again.

The Consumer module is presented next in Listing 2.6.

```

1 SC MODULE (Consumer) {

2

// Definitions of ports

3

sc_port< read_if<char> > in;

// Input port

4

5

// Definitions of processes

6

void consumer_process() {

7

8

while (true) {

9

if (rand() % 2) {

10

std::cout << in.read();</pre>

}

11

12

```

```

13

wait(1, SC SEC);

14

}

}

15

16

17

SC CTOR(Producer) {

18

// Process registration, sensitivity lists, etc.

SC THREAD(consumer_process); // thread process

19

20

21

// No sensitivity list

22

23 };

```

Listing 2.6: A SystemC model of a Consumer

The Consumer model is very similar to the Producer model. An input port is declared on line 3 and the functionality of the module is implemented on lines 6–15. The consumer\_process() uses an infinite while-loop with explicit suspension of execution (line 13), and thus it must be declared a thread process (line 19).

One challenge presented by the Producer and the Consumer modules is that characters are produced and consumed nondeterministically. Since the FIFO has bounded capacity, it may eventually be full when the Producer attempts to store another character, or it may be empty when the Consumer attempts to read another character. The design of the FIFO, presented in Listing 2.7, handles this via *blocking* read() and write() operations.

```

1 template<class T>

2 class fifo : public sc channel,

3

public write if<T>,

4

public read if<T> {

5

6

private:

7

int max = 10; // Capacity of the FIFO

8

T* data[max];

9

int num_elements = 0;

10

int first = 0;

11

sc event write event, read event;

12

13 public:

14

15

// Implementation of the read if

```

```

16

virtual T& read() {

17

if (num elements == 0) {

18

wait(write_event);

19

20

21

T* token = data[first];

22

-- num elements;

23

first = (first + 1) % max;

24

read event.notify();

25

return token;

26

}

27

28

virtual int num_available() {

29

return num elements;

30

}

31

32

33

// Implementation of the write if

34

virtual void write(T& token) {

35

if (num_elements == max) {

36

wait(read event);

37

38

39

data[(first + num_elements) % max] = &token;

40

++num_elements;

41

write_event.notify();

42

43

44

virtual void reset() {

45

num elements = 0;

46

first = 0;

47

}

48

49 };

```

Listing 2.7: A SystemC model of a (blocking) FIFO

Like every user-defined channel, fifo must derive from the pre-defined class sc\_channel. In order to handle the communication between the Producer and the Consumer, the fifo must also implement the interfaces write\_if and read\_if. This is declared explicitly on lines 2-4.

The fifo defines **private** local data to store tokens and to keep track of the total number of tokens, as well as the location in the array where the next token

will be stored (lines 7-11). The rest of the code implements the functions defined in read if (lines 16-30) and write if (lines 34-47).

The implementation of the read() function checks if there is something to read, and if there are no tokens currently in the FIFO, the function suspends execution with a call to wait(write\_event) (line 18). Execution can resume only after write\_event has been notified. The intended behavior of this piece of code is that execution will resume only after there is something to read from the FIFO. Ensuring that this is the case is the responsibility of the designer of the FIFO. In this case write\_event is notified only on line 41 right after a token is placed in the FIFO, thus we can expect correct behavior from the code.

The implementation of write() similarly checks if there is space for one additional token in the FIFO. If this is not the case, execution is suspended until the FIFO is nonempty, by issuing a call to wait(read\_event) on line 36. The expectation of the designer is that read\_event is notified if and only if there is space in the FIFO. The only place where read\_event is notified is on line 24, right after a token has been consumed from the FIFO, thus the designer can expect the code to execute correctly.

### 2.1.4 SystemC events

As seen in Listing 2.7 (line 11), SystemC events are represented by objects of the pre-defined class **sc\_event**. An event determines whether and when a process is triggered or resumed, and usually represents a *condition* that may occur during simulation. The meaning of each event object is determined by the designer, and reporting that the condition represented by the event object has occurred is done by *notifying* the event object.

A very commonly occurring condition in SystemC is the change of value of a signal. Internally, SystemC defines for each **sc\_signal** an associated event, accessible via function call value changed event(), that is notified whenever the value of the

signal is written or modified [IEE06]. For example, the implementation of a NAND gate in Listing 2.2 defines a process that is sensitive to input ports; implicitly, the process is sensitive to the value\_changed\_event() associated with the signals connected to each port.

The effect of the notification of an event e causes all processes that are sensitive to e (or have called **wait**(e)) to be triggered or resumed. There may be, however, some delay from the instance when e.notify() is issued and when its effect takes place, depending on the argument passed to **notify**():

- Calling **notify**() without arguments constitutes *immediate notification*. Any and all processes that are sensitive to the event are triggered before the function call **notify**() returns. Triggering a process is not equivalent to starting it, however. In SystemC there is a pool of processes that are ready to execute in the current simulation cycle. Triggering a process simply adds the process to this pool. This notion will be made more precise in Section 2.2.

- Calling notify() with a zero-valued time unit (e.g., (0, SC\_SEC) or, more commonly, SC\_ZERO\_TIME) delays the effect of the event notification until all currently triggered processes have finished executing. Between the instance when notify() is called and when its effect takes place there may be an arbitrarily long delay (in terms of wall-clock time) during which all other runnable processes take their turn to execute. During that delay, however, the simulation clock does not advance, so the notification of the event and its effect happen in the same instance of time as measured by the simulation clock. This type of event notification is called delta-delayed notification.

- Calling **notify**() with a non-zero argument delays the effect of the notification by the requested number of time units. The argument is added to the current value of the simulation clock, and the event is put in a queue, ordered by the scheduled notification time. This type of event notification is called *time-delayed*

notification.

If the event notification is pending (i.e. it is delta-delayed or time-delayed) it can be *canceled*, which removes any pending effect of the event. It is also allowed to wait for an event for some bounded amount of time, and then resume execution even if the event was not notified. For example, a process issuing a call to wait(2, SC\_SEC, some\_event) resumes execution after 2 seconds of simulation time, unless some event is notified earlier.

### 2.1.5 Data types

A SystemC model can use all C++ data types. This is convenient for the designers of the model's software, but not sufficient for hardware designers. One example why this is the case is given by Grötker et al. [GLMS02]: in software, a loop ranging from 0 to 31 would be indexed by an **int** variable, even though only 6 bits would be sufficient. Implementing this in hardware would require a 6-bit register and a 5-bit adder, and using a 32-bit register and a 32-bit adder would be wasteful. To accommodate the needs of hardware designers, SystemC provides a rich set of hardware-oriented data types.

For example, fixed-precision integral type  $sc_{int}<W>$  and  $sc_{uint}<W>$  encode numbers from  $-2^{W-1}$  to  $(2^{W-1}-1)$  and from 0 to  $(2^W-1)$  accordingly. These types are limited to 64 bits. Arbitrary-precision integral types  $sc_{biguint}<W>$  and  $sc_{biguint}<W>$  can fit and operate on integers bigger than 64 bits, at the cost of worse performance.

The native C++ type **bool** is often implemented as a **short int**, so SystemC provides a replacement **sc\_bv**<W> which can also encode bit-vectors. 4-valued logic values can be encoded using **sc\_logic** and a vector of logic values can be encoded using **sc\_lv**<W>. SystemC also provides a library for fixed-point arithmetic with corresponding data types.

## 2.2 SystemC as a simulation environment

The simulation semantics of SystemC is similar to that of hardware-design languages like VHDL. It is based on the principle that new events are generated as a result of the execution of processes, which were triggered by earlier events. This defines partial order on the executing processes and the notification of SystemC events. This section explores in detail the simulation semantics of SystemC.

## 2.2.1 Parallel execution

In order to simulate parallel execution, SystemC executes processes sequentially, but hides the effect of each process until all "parallel" processes have been executed and each one has reached a synchronization point: either a call to wait() or process termination. For example, values written to signals are not immediately readable by other processes executing "in parallel" with the writing process. Execution of processes is controlled by the SystemC kernel.

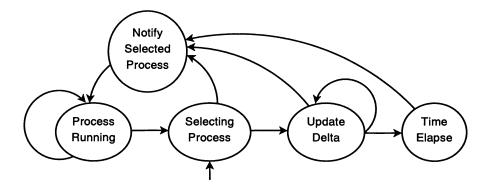

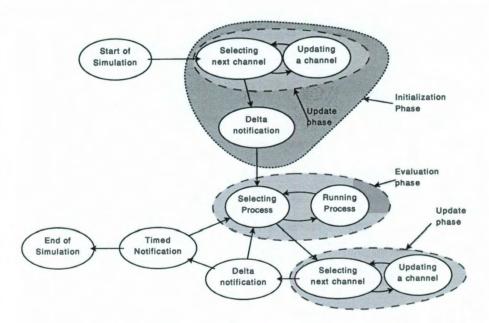

The (sequential) execution of "parallel" processes defines one phase of the overall execution of the model, called evaluation phase. Before the evaluation phase begins, the SystemC kernel creates a list of all processes that it must run. Processes on this list are called runnable processes. Nondeterministically and sequentially, the kernel removes a process from the list and gives it execution control; the process is now running. As soon as the running process suspends itself it becomes waiting. Control is transferred back to the kernel which then removes another process from the list and gives it execution control. The simulation semantics imposes non-preemptive cooperative execution of processes, that is, once the kernel gives a process execution control the kernel cannot take it back. The process must explicitly give back the control by reaching a synchronization point.

During its execution, a running process may request the notification of an event. If the request is for an *immediate notification* (see 2.1.4), all processes waiting on the event become runnable immediately, and are added to the pool of runnable processes.

If the event notification is time-delayed or delta cycle-delayed, it is collected by the kernel but not acted upon during the evaluation phase.

It is also possible to have two or more processes requesting the notification of the same event during the same evaluation phase. In those cases the request with earlier effect survives, and the other one is canceled. For example, if a delta-delayed and a time-delayed notification are requested in the same evaluation phase, the time-delayed notification is canceled while the delta-delayed notification remains. Likewise, an immediate notification cancels any pending time- or delta-delayed notification requests.

## 2.2.2 Signals and channels

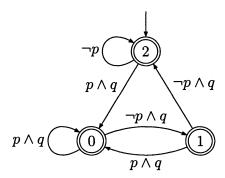

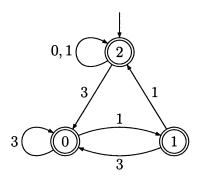

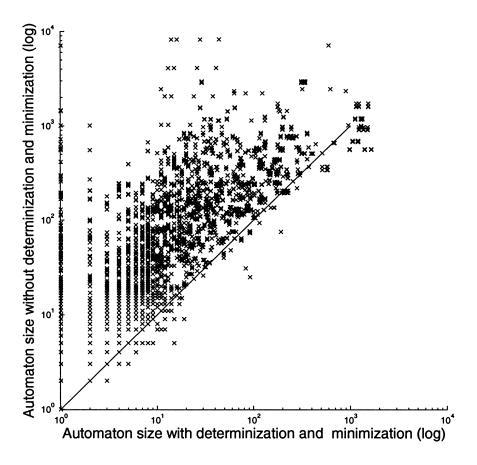

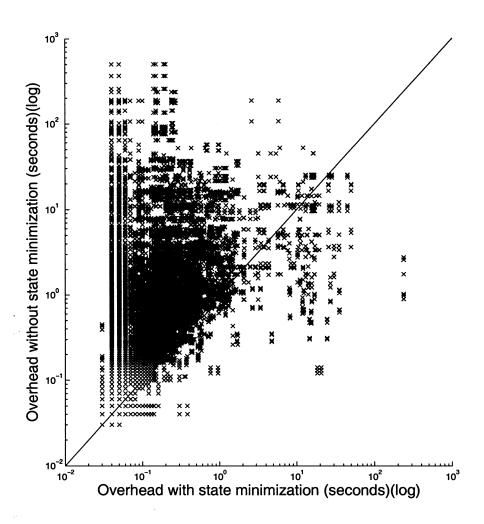

After the end of the evaluation phase the kernel makes visible any changes of values of signals and channels, during the so called *update phase*. If a process wrote a new value to an <code>sc\_signal</code>, the new value becomes the value of the signal. This change of value notifies the signal's <code>value\_changed\_event()</code> using a call to <code>notify(SC\_ZERO\_TIME)</code>. If there are processes that are sensitive to changes of the signal, the effect of event notification is to make those processes runnable. The event notifications are collected by the kernel but are not acted upon in this phase.