#### RICE UNIVERSITY

## Mapping a Dataflow Programming Model onto Heterogeneous Architectures

by

#### Alina Gabriela Sbirlea

A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE

#### **Master of Science**

APPROVED, THESIS COMMITTEE:

Vivek Saakae

Vivek Sarkar, Chair Professor of Computer Science E.D. Butcher Chair in Engineering

Keith D. Cooper L. John and Ann H. Doerr Professor of Computational Engineering

John Mellor Crummer Professor of Computer Science Professor of Electrical and Computer Engineering

Zoran Budimlic Research Scientist Computer Science Department

Houston, Texas November, 2011

#### ABSTRACT

#### Mapping a Dataflow Programming Model onto Heterogeneous Architectures

by

Alina Gabriela Sbirlea

This thesis describes and evaluates how extending Intel's Concurrent Collections (CnC) programming model can address the problem of hybrid programming with high performance and low energy consumption, while retaining the ease of use of data-flow programming.

The CnC model is a declarative, dynamic light-weight task based parallel programming model and is implicitly deterministic by enforcing the single assignment rule. These properties ensure that problems are modelled in an intuitive way. CnC offers a separation of concerns by allowing algorithms to be expressed as a two stage process: first by decomposing a problem into components and specifying how components interact with each other, and second by providing an implementation for each component. By facilitating the separation between a domain expert, who can provide an accurate problem specification at a high level, and a tuning expert, who can tune the individual components for better performance, we ensure that tuning and future development, such as replacement of a subcomponent with a more efficient algorithm, become straightforward.

A recent trend in mainstream desktop systems is the use of graphics processor units (GPUs) to obtain order-of-magnitude performance improvements relative to general-purpose CPUs. In addition, the use of FPGAs has seen a significant increase for applications that can take advantage of such dedicated hardware. We see that computing is evolving from using many core CPUs to "co-processing" on the CPU, GPU and FPGA, however hybrid programming models that support the interaction between multiple heterogeneous components are not widely accessible to mainstream programmers and domain experts who have a real need for such resources.

We propose a C-based implementation of the CnC model for enabling parallelism across heterogeneous processor components in a flexible way, with high resource utilization and high programmability. We use the task-parallel HabaneroC language (HC) as the platform for implementing CnC-HabaneroC (CnC-HC), a language also used to implement the computation steps in CnC-HC, for interaction with GPU or FPGA steps and which offers the desired flexibility and extensibility of interacting with any other C based language.

First, we extend the CnC model with *tag functions* and *ranges* to enable automatic code generation of high level operations for inter-task communication. This improves programmability and also makes the code more analysable, opening the door for future optimizations. Secondly, we introduce a way to specify steps that are data parallel and thus are fit to execute on the GPU, and the notion of task affinity, a tuning annotation in the specification language. Affinity is used by the runtime during scheduling and can be fine-tuned based on application needs to achieve better (faster, lower power, etc.) results. Thirdly, we introduce and develop a novel, data-driven runtime for the CnC model, using HabaneroC (HC) as a base language. In addition, we also create an implementation of the previous runtime approach and conduct a study to compare the performance. Next, we expand the Habanero dynamic work-stealing runtime to allow *cross-device stealing* based on task affinity. Cross-device dynamic work-stealing is used to achieve load balancing across heterogeneous platforms for improved performance. Finally, we implement and use a series of benchmarks for testing the model in different scenarios and show that our proposed approach can yield significant performance benefits and low power usage when using a hybrid execution.

## Acknowledgments

To my advisor, Professor Vivek Sarkar, for his invaluable advise, support and feedback throughout this work. To Professor Keith Cooper for his kind words of encouragements and advice on improving both the work and the exposure of this thesis. To Professor John Mellor-Crummey for evaluating and proving detailed feedback for the improvement of this work and thesis. To Zoran Budimlic for the discussions on the implementation of CnC-HC, his feedback and thoughts.

To the HabaneroC team for the development of the language my work is based on, for their timely response to any language issues that arouse as my work progressed, enabling both HabaneroC and CnC-HC to mature together. For being there to help either with a simple code understanding or complex synchronization issues, (alphabetical order) Zoran Budimlic, Vincent Cave, Vivek Sarkar, Yonghong Yan. To Sagnak Tasirlar for the implementation of Cholesky in CnC-HabaneroJava, used as reference for my CnC-HC implementation and to Aparana Chandramowlishwaran for the Intel-CnC Cholesky implementation. To Max Grossman, undergraduate student at Rice University, for the work done on CnC-CUDA [1] which introduced the GPU extensions in CnC-HabaneroJava. To Yi Zou, PhD. student in Computer Science at UCLA for the implementation of the imaging pipeline on the Convey machine located at UCLA. To the NSF Expeditions Center for Domain Specific Computing for funding and motivating this work.

Last but not least to my family for their support in pursuing this road and a special thanks to my husband for the late long talks, advice, support and care.

# Contents

|          | Abs  | tract                                   | ii  |

|----------|------|-----------------------------------------|-----|

|          | Ack  | nowledgments                            | iv  |

|          | List | of Illustrations                        | vii |

|          | List | of Tables                               | ix  |

| 1        | Int  | roduction                               | 1   |

|          | 1.1  | Motivation                              | 5   |

|          | 1.2  | Contributions                           | 6   |

| <b>2</b> | Ba   | ckground                                | 8   |

|          | 2.1  | Parallel programming models             | 8   |

|          | 2.2  | HabaneroC                               | 11  |

|          | 2.3  | Concurrent Collections                  | 13  |

|          | 2.4  | The CUDA programming model              | 16  |

|          | 2.5  | Related work                            | 17  |

| 3        | Gra  | aph language extensions for CnC-HC      | 22  |

|          | 3.1  | Tag functions                           | 23  |

|          | 3.2  | Ranges                                  | 29  |

| 4        | Co   | mpiler support for CnC-HC               | 31  |

|          | 4.1  | Software lifecycle with $CnC\text{-}HC$ | 31  |

|          | 4.2  | Auto-generated executable code          | 32  |

|          | 4.3  | Auto-generated helper code              | 37  |

| <b>5</b> | Ru                                                      | ntime support for CnC-HC                                         | 40 |  |

|----------|---------------------------------------------------------|------------------------------------------------------------------|----|--|

|          | 5.1                                                     | Previous runtime approaches                                      | 40 |  |

|          | 5.2                                                     | Restart and Replay runtime                                       | 43 |  |

|          |                                                         | 5.2.1 Runtime description                                        | 43 |  |

|          |                                                         | 5.2.2 Theoretical guarantees                                     | 46 |  |

|          | 5.3                                                     | Data Driven runtime                                              | 49 |  |

|          | 5.4                                                     | Domain expert versus tuning expert                               | 51 |  |

| 6        | CnC-HC-Hybrid: A declarative language for heterogeneous |                                                                  |    |  |

|          | arc                                                     | hitectures                                                       | 53 |  |

|          | 6.1                                                     | Overview                                                         | 53 |  |

|          | 6.2                                                     | Language extensions                                              | 54 |  |

|          | 6.3                                                     | Code generation                                                  | 56 |  |

|          | 6.4                                                     | HabaneroC runtime support                                        | 62 |  |

| 7        | Exj                                                     | perimental results                                               | 65 |  |

|          | 7.1                                                     | Performance comparison study between the Restart and Replay and  |    |  |

|          |                                                         | Data Driven runtimes                                             | 67 |  |

|          |                                                         | 7.1.1 When the Data Driven runtime is the better choice          | 67 |  |

|          |                                                         | 7.1.2 When the Restart and Replay runtime is the better choice . | 74 |  |

|          | 7.2                                                     | CPU testing and benchmarks                                       | 77 |  |

|          | 7.3                                                     |                                                                  | 81 |  |

| 8        | Co                                                      | nclusions and future work                                        | 88 |  |

|          | Bib                                                     | oliography                                                       | 91 |  |

vi

# Illustrations

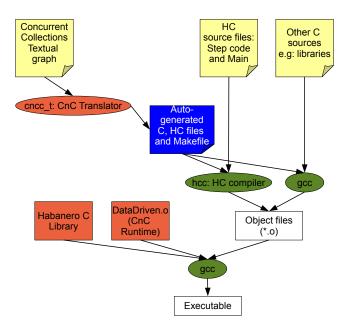

| 4.1 | CnC-HC Build Model                                                        | 32 |

|-----|---------------------------------------------------------------------------|----|

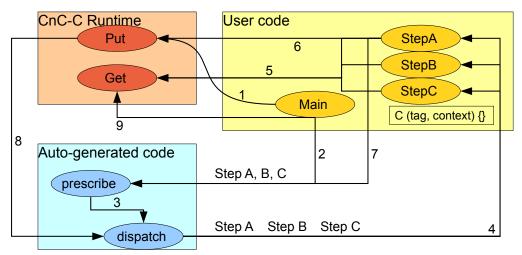

| 5.1 | Hypothetical C implementation of a $CnC$ Runtime, using the Restart       |    |

|     | and Replay policy.                                                        | 42 |

| 5.2 | Control Flow for the Restart and Replay Runtime                           | 43 |

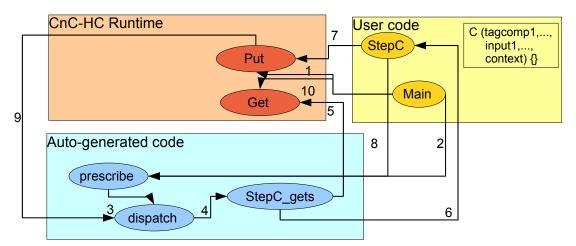

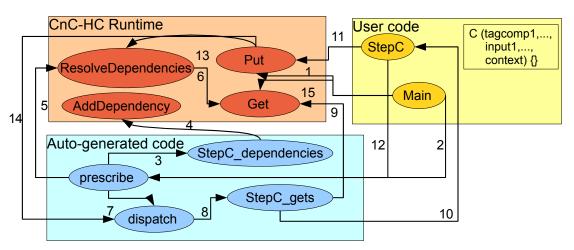

| 5.3 | Control Flow for the Data Driven Runtime                                  | 50 |

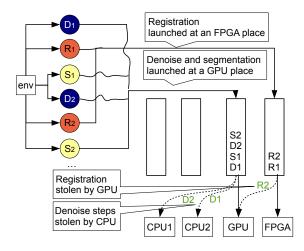

| 6.1 | Dynamic work-stealing between devices for the medical imaging pipeline    | 63 |

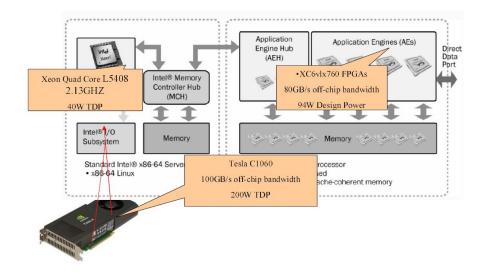

| 7.1 | The Convey HC-1ex architecture. [2]                                       | 66 |

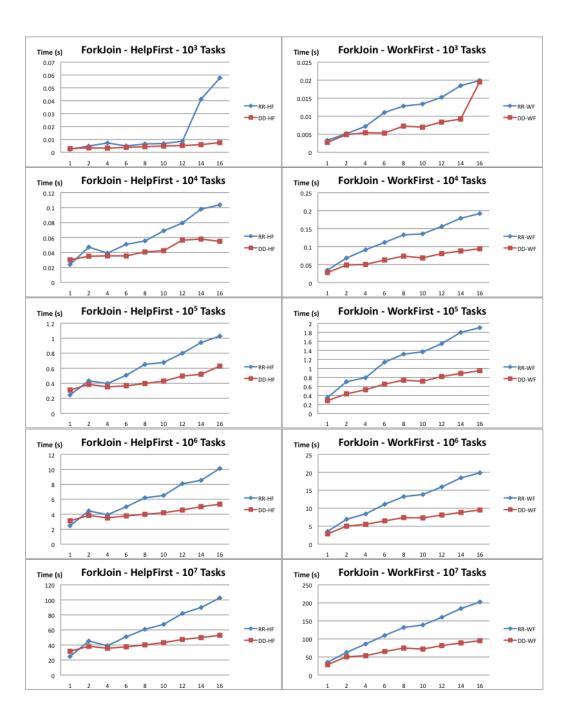

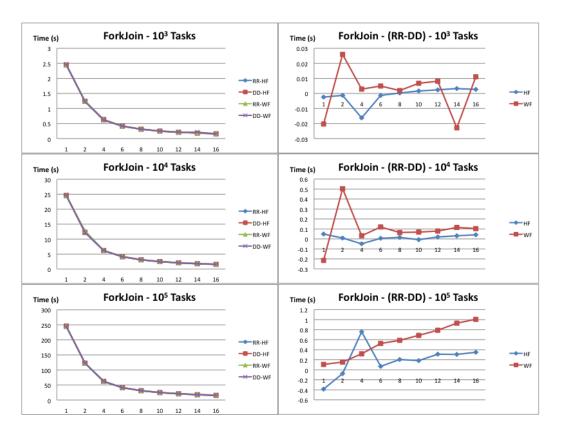

| 7.2 | Performance comparison between the Restart and Replay and Data            |    |

|     | Driven Runtimes for ForkJoin benchmark, with little work, for 1-16        |    |

|     | cores                                                                     | 69 |

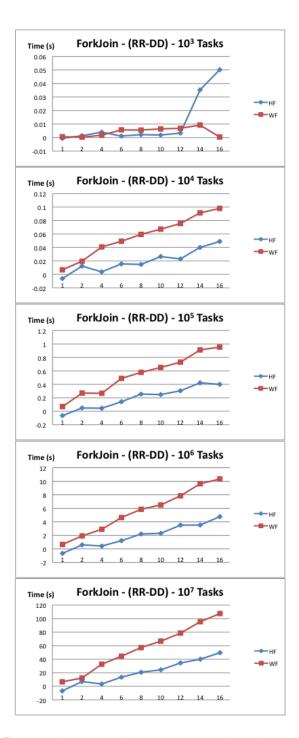

| 7.3 | Time difference between the Restart and Replay and Data Driven            |    |

|     | Runtimes for ForkJoin benchmark, with little work, for 1-16 cores $\ .$ . | 70 |

| 7.4 | Performance comparison between the Restart and Replay and Data            |    |

|     | Driven Runtimes for ForkJoin benchmark, with large work, for 1-16         |    |

|     | cores. For the graphs on the right, a negative value indicates a case     |    |

|     | for which the Restart and Replay runtime performs better than the         |    |

|     | Data Driven runtime                                                       | 71 |

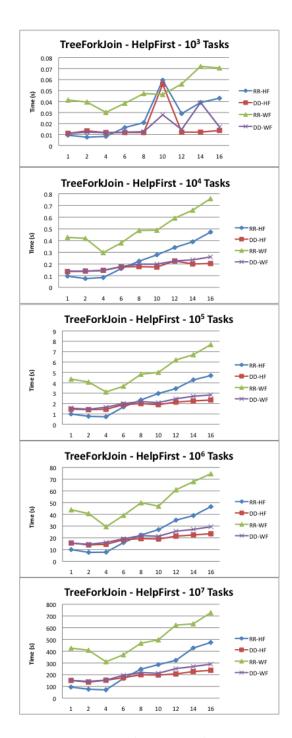

| 7.5  | Performance comparison between the Restart and Replay and Data                |    |

|------|-------------------------------------------------------------------------------|----|

|      | Driven Runtimes for TreeForkJoin benchmark, with little work, 10              |    |

|      | failing Gets, for 1-16 cores                                                  | 73 |

| 7.6  | Performance comparison between the Restart and Replay and Data                |    |

|      | Driven Runtimes for a variant of the ForkJoin benchmark when each             |    |

|      | task needs 100 items that are already available; 1-16 cores. The              |    |

|      | graphs on the right indicate that the Restart and Replay runtime              |    |

|      | performs better than the Data Driven runtime when getting the data            |    |

|      | would be successful on a first attempt.                                       | 76 |

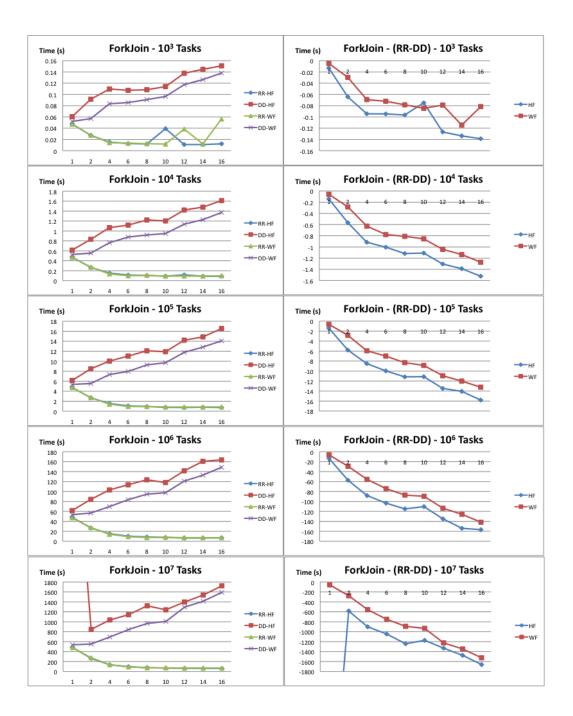

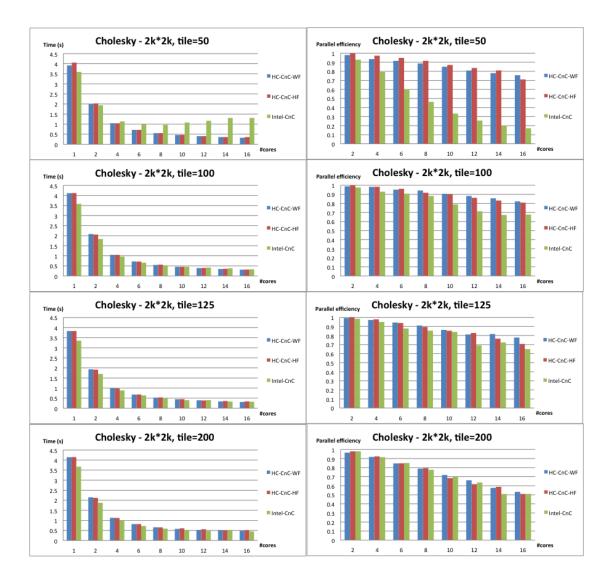

| 7.7  | Performance comparison (time and parallel efficiency) between Intel's         |    |

|      | $CnC$ and $CnC\text{-}HC$ for the Cholesky factorization, on 1-16 cores $\ .$ | 78 |

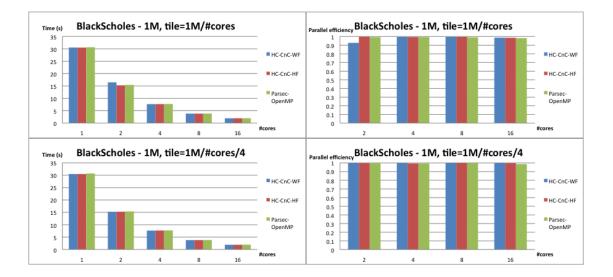

| 7.8  | Performance comparison Parsec's OpenMP and $CnC-HC$ for                       |    |

|      | BlackScholes, on 1-16 cores                                                   | 80 |

| 7.9  | Performance comparison Rodinia's OpenMP and $CnC-HC$ for Heart                |    |

|      | Wall Tracking, on 1-16 cores                                                  | 82 |

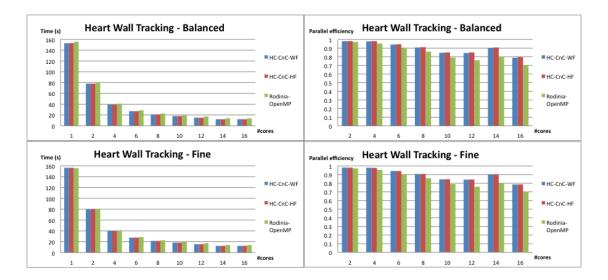

| 7.10 | Performance on two GPU models of the crypt benchmark when a                   |    |

|      | percentage of the work is offloaded to the GPU                                | 83 |

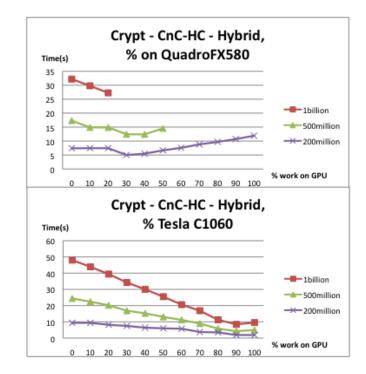

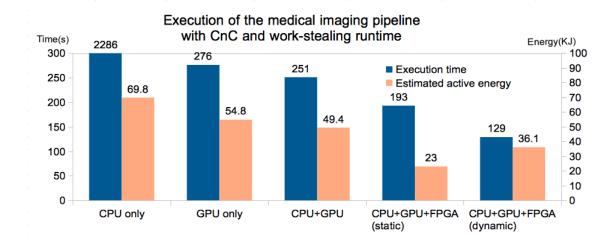

| 7.11 | Evaluating performance for the medical imaging pipeline on a Convey           |    |

|      | HC-1ex with 2 CPU threads, 1 GPU and 1 FPGA                                   | 85 |

| 7.12 | Evaluating performance for the medical imaging pipeline on a Convey           |    |

|      | HC-1ex with 2 CPU threads, 1 GPU and 1 FPGA                                   | 86 |

viii

# Tables

| 2.1 | Comparison between different implementation flavours of the |    |

|-----|-------------------------------------------------------------|----|

|     | Concurrent Collection model                                 | 14 |

## Chapter 1

## Introduction

The computer industry is at a major inflection point in its hardware roadmap due to the end of a decades-long trend of exponentially increasing clock frequencies. Future hardware is expected to be built using homogeneous and heterogeneous many-core processors with order of hundreds of cores per chip and complex architectures designed to target the challenges of concurrency, fault tolerance, energy efficiency and resilience. The current trend is to develop massively multicore architectures that can be specialized to satisfy the energy constraint. These radical changes in hardware architectures have already begun to impact software, as the burden shifts to the programmer to make parallelism explicit. Old views have already begun to change, from finding ways to map software onto complex hardware, to designing hardware based on software needs. These software challenges are further compounded by the need to enable parallelism in mainstream workloads and application domains that have traditionally not had to employ parallelism in the past. Despite over four decades of research, few high-level parallel programming models are available to domain experts who are not at the same time experts in parallelism. Fortunately, this situation is starting to change. Frameworks such as Map-Reduce [3] successfully exploit implicit parallelism on distributed systems and have also been extended to heterogeneous platforms such as GPU [4] and FPGA [5]; however, have a restricted programming model. Other models, such as CUDA [6] and OpenCL [7], provide a restricted programming model to the users of GPU accelerators, but also expose a significant amount of hardware details.

A recent trend in mainstream desktop systems is the use of graphics processor units (GPUs) to obtain order-of-magnitude performance improvements relative to generalpurpose CPUs. In addition, FPGAs have seen increasing use by applications that can take advantage of such dedicated hardware. We see that computing is evolving from using many core CPUs to "co-processing" on the CPU, GPU and FPGA. However, hybrid programming models that support the interaction between the two are not widely accessible to mainstream programmers and domain experts who have a real need for such resources.

At the other end of the spectrum, there are coordination languages such as Intel's Concurrent Collections<sup>\*</sup> (CnC) [9] which are explicitly designed to be implicitly parallel and easy to use by programmers with no knowledge of parallel programming. CnC is a declarative coordination language that can express any dependency graph through combinations of task and data parallelism. CnC computations are built using steps that are related by data and control dependences. These are specified in a straight forward manner in a meta language that can describe a CnC graph. CnC is provably deterministic [9]. While this restricts CnC's scope, it is more general than other deterministic programming models including dataflow and stream-processing, and can incorporate static and dynamic forms of task, data, loop, pipeline, and tree parallelism. All of these properties make the CnC model a very good choice for a domain expert, but what it lacks is the ability to target emerging heterogeneous architectures. To address this problem, we first worked on extending the model for execution on the GPU [1], creating the first such extension. This was developed by extending a variant of Concurrent Collections[9] built on top of HabaneroJava (HJ)

<sup>\*</sup>An earlier version of CnC was called TStreams [8].

[10, 11] programming model with promising results. However, since the model was implemented in a high-level language such as Java, we needed to make the calls to native code through an additional layer (the Java native interface -JNI), which added an additional overhead of copying data and had limited interoperability.

In this work, we show how to extend the CnC programming model to address the problem of hybrid programming while retaining the ease of programming introduced by CnC and enabling host-device interaction. To ensure that we can express parallelism in an easy way and also allow users of the CnC model to express parallelism within a computational step if they so desire, we have chosen a research parallel programming language that is based on C, called HabaneroC (HC). We name this C-based approach Concurrent Collections-HabaneroC (CnC-HC). We have chosen the C language due to past experience with a Java approach, having as a target obtaining the best possible performance, a goal which implied using a language that is low level enough but provide this, but still reasonable to program in. In addition, we wanted to target heterogeneous architectures for which programs are written in languages that can interact easily with the C language. We use HC as the language for implementing the CnC-HC runtime, the CnC computational steps as well as for the interaction with CUDA GPU steps.

The first extension we will present is the introduction of tag functions and ranges in the the CnC graph file specifications. Tag functions specify the relation between the tag that uniquely identifies a step and the tags identifying the data items that the step is either reading or writing, while ranges define contiguous sets of items read or written by a step. These extensions enables the compiler to automatically generate high level operations for inter-task communication, more precisely, the autogeneration of the calls to the functions that read the data items (Get functions) within a computational step. It also enables the generation of the function calls that write data items (Put functions) and that spawn of other steps, yet, as these can be optional depending on each step instance, the generated code will be considered helper code rather than a requirement. C being a low level language, the ability to have much of the interaction code generated automatically, improves programmability and ensures ease of use. This addition of tag functions also makes the code more analysable opening the path for research topics: static analysis of the graph for guarantees such as graph termination, item garbage collection or graph correctness (e.g., there is a path from the steps created by the environment to all steps specified in the graph; all the data read by the environment after the graph execution will be available as it was created during the run).

The second aspect we present is a novel, data-driven runtime for the CnC model, developed in a C framework, using HabaneroC (HC). We also create an implementation of the previous runtime approach and conduct a study between the two runtimes to determine the situations when each performs best. The result can be dependent on the application but also on the scheduling policies defined by HabaneroC, which we shall detail these throughout this thesis.

The third aspect we will tackle is the extension of CnC-HC for heterogeneous architectures. To achieve this, we introduce a way to specify steps that are data parallel and thus are fit to execute on the GPU, and the notion of task *affinity*, a tuning annotation which offers hints on where a computational step should be run. Affinities are used by the runtime during scheduling and can be fine-tuned based on application needs to achieve better (faster, lower power, etc.) results. Further, we expand the HabaneroC dynamic work-stealing runtime to allow cross-device stealing based on task affinity. Cross-device dynamic work-stealing is used to achieve load balancing across heterogeneous platforms for improved performance.

Finally, in our experimental results, we use a series of a series of benchmarks to show that, by using the new CnC-HC, we can match or exceed the performance of Intel's CnC and OpenMP, as well as yield a significant increase in performance and decrease in power consumption when using CnC-HC for a hybrid CPU/GPU/FPGA execution.

#### 1.1 Motivation

Nowadays the roadmaps of hardware and software seem to be on a collision course. The direction of hardware design is to develop a highly customizable hardware whose parameters can be altered based on application needs. For this to be possible, a lot of work is necessary on the application front to abstract the right principles and identify the relevant primitives that characterize a domain.

Our ongoing work in the NSF Expeditions Center for Domain Specific Computing (CDSC) project [12, 13] targets precisely this problem and motivates this thesis. The project aims to determine what hardware features are most useful for a given domain. The high-level idea is that customization is a two-stage process. One involves configuring for the domain and one for a particular application. The configurations that this project is attempting to select for a specific domain involve the instruction window, cache/icache locality, register number, register file organization, allocation of interconnect bus resources. Possible hardware configurations for the customizable platform developed in this project include turning on/off some of the cores for energy efficiency. The work we present here is a first step in achieving our long-term goal of learning from software when developing the appropriate hardware architecture and vice-versa, also known as hardware-software co-design. This first step involves running sample applications for the medical imaging domain in a flexible modelling language and using it to study the computation and communication in these applications.

In this thesis, we propose using CnC for mapping such applications onto heterogeneous architectures, more precisely we propose using CnC as a flexible programming model that can be used by domain experts for such a customizable hardware platform. The Concurrent Collections programming model was chosen for its ease of use for domain experts and the mainstream programmer, who don't have to worry about low level details of parallelism. The extensions we will present keep these properties but target the use of more complex architectures. Work on CnC-HC is further motivated by the fact that, being a C based language, it is very well suited for heterogeneous architectures.

My thesis is that a high level data flow model targeted for domain experts can be and is desirable to be extended for execution on hybrid architectures, with very good performance results, high programmability and low energy consumption.

#### **1.2** Contributions

The main contributions of this thesis are:

- introducing tag functions to the CnC model to relate a step's unique identifier

the tag to the data that it reads, writes and other steps it may start,

- 2. extending a translator for generating appropriate C code, in accordance with the tag functions specified in the CnC graph file. The generated code performs read operations (Get), task creation and launching to increase programmability,

- developing the CnC-HC Restart and Replay runtime, the previous runtime approach for the CnC model,

- 4. developing the CnC-HC Data Driven runtime, our proposed alternative to 3, and comparing the two runtimes,

- 5. adding GPU steps to the CnC-HC model and generating the appropriate C and most of the CUDA interface code with the CnC runtime and user code,

- 6. extending the specification language, translator and runtime for CnC to include an affinity component for GPU and FPGA devices,

- extending the HC work-stealing runtime to perform cross device work-stealing based on the affinity metric in order to achieve load balancing of the work across devices,

- 8. porting a series of benchmarks to CnC-HC and CnC-HC-Hybrid.

The rest of this thesis is organized as follows. Chapter 2 summarizes the background and related work. Chapter 3 introduces a new specification language for CnC-HC. Chapter 4 describes the changes to the tool that interprets the input CnC graph (the translator) needed to support and enable the language extensions proposed in Chapter 3 while Chapter 5 presents the runtime developed for CnC-HC. Further in Chapter 6 we discuss the extensions needs in the graph language and the necessary additions to the translator and runtime for heterogeneous execution. We present and discuss the experimental results in Chapter 7 and finally conclude the thesis and outline possible future work in Chapter 8.

## Chapter 2

## Background

In this chapter we present in more detail aspects which will help understand our work and relate it to other work in the field. First, as this work proposes a parallel programming model, we shall discuss how it fits into the world of parallel programming models. Secondly, we shall detail the HabaneroC programming model, which we have chosen as the basis for this work, because it is a general model which express parallelism in a straight forward manner, because it is a C based language which can interact easily with languages which address accelerators and also because we were able to access and modify the runtime to achieve this work's objectives. Next we describe the Concurrent Collection programming model, a variant of which this thesis brings forward, using as a lower level layer HabaneroC. As our work develops extensions for heterogeneous architectures, which include GPUs, and generates CUDA code for such devices, we next discuss the CUDA programming model. Finally, we shall discuss other work which extends the Concurrent Collection model for various goals and also describe other programming models which address the problem of modelling applications for heterogeneous architectures.

### 2.1 Parallel programming models

A parallel programming model refers to the means of specifying a program such that it can be compiled to run simultaneously on multiple execution units. The primary ways of classifying parallel programming models are based on the approaches taken for process interaction and problem decomposition. These classifications are by no means exhaustive; our aim is not to cover all the models in existence but to highlight those that are most relevant to this thesis.

Considering process interactions, we can distinguish between shared memory and message passing or distributed memory models. In the latter category, we briefly mention MPI [14] and Java RMI [15] as the models most commonly used currently and focus further on the shared memory models which are more relevant to this work. In a shared memory model, parallel tasks share a global address space which is accessed asynchronously when reading and writing data. The model thus requires the use of synchronization primitives to control concurrent accesses to shared variables, to ensure correctness and determinism. We detail a few of the representative shared memory models developed thus far that are most relevant to this work.

At the lowest level, parallelism is expressed by means of threads. For UNIX systems, a standardized C language threads programming interface has been specified by the IEEE POSIX 1003.1c standard. Implementations that adhere to this standard are referred to as POSIX threads, or Pthreads [16]. The routines that are included in these implementations enable the programmer to manage all the low-level details of parallel programming, such as thread management and synchronization. However, not many programmers are trained in all the intricacies of Pthreads, and many models have been designed to hide the thread management details while still offering effective means for exploiting parallelism.

One of the best known shared memory parallel programming models is OpenMP [17, 18]. It is an API (Application Program Interface) implemented for C and Fortran that encompasses a series of runtime library functions and directives for specifying

parallel regions, work sharing, synchronization and environment variables [19].

Considering the problem decomposition classification, we distinguish between data parallelism and task parallelism. Data parallelism is achieved in SIMD, when the same operations are performed on different pieces of the data. This usually refers to vector parallelism, done through vector instructions support from the underlying architecture as well as from the compiler. Examples of data parallel languages include High Performance Fortran [20] and NESL [21]. Another more recent execution model for data parallelism can be found in SIMT models for GPU, such as CUDA (see section 2.4).

Our main interest in this thesis is in task parallel languages, in which different processors may execute different parts of the computation. In general, a whole computation can be viewed as a work flow, where the nodes contain pieces of computation and the edges symbolize data communication and synchronization.

In particular, the dynamic light-weight task-based model defines the basic unit of computation as a task, which may be far smaller than an OS thread, thus enabling fine grained parallelism. The coarsening is performed dynamically at runtime by assigning a set of light-weight tasks to each worker thread, depending on the inherent dependences in the work flow. Some of the better known programming models which adhere to this task-parallel model are Cilk [22], Intel Threading Building Blocks [23], Chapel [24], Fortress [25], OpenMP 3.0 [26], X10 [27], HabaneroJava [10] and our choices for this work, HabaneroC [28] and Concurrent Collections (CnC) [29] [9]. We have chosen HabaneroC, because it is a C-based language thus low level enough to allow us to obtain the best possible performance and easy interaction with languages that address accelerators, while also being a general model which expresses parallelism in a straight forward manner. CnC adds another level of abstraction through the

definition of any problem by means of a dependency graph, offering ease of use for non-expert parallel programmers and enabling the definition of arbitrary task graphs.

#### 2.2 HabaneroC

The HabaneroC (HC) language is a parallel programming model currently being developed at Rice University in the Habanero Research project. Previous work on HabaneroJava motivated this new C-based approach as a means of designing a language well suited for homogeneous and heterogeneous processors, in particular the Customizable Heterogeneous Platform (CHP) being developed in the NSF Expeditions Center for Domain-Specific Computing (CDSC) [13], which includes CPUs, GPUs, and FPGAs.

The two main features of HC we refer to throughout this work, and that we detail further are:

- 1. The *async* and *finish* constructs which define lightweight dynamic task creation and termination [30]

- 2. Hierarchical place trees for locality control [31].

HabaneroC has two basic primitives for the task parallel programming model borrowed from X10 [27]: async and finish.

The async statement ( async  $\langle \text{ stmt } \rangle$  or async { stmt1 .. stmtN } ) causes the parent task to fork a new child task that will execute one or more statements. The parent task continues executing the statements that follow the async statement and does not wait for the child task to finish its execution. The finish statement ( finish  $\langle \text{ stmt } \rangle$  or finish { stmt1 .. stmtN } ) performs a join operation. The task entering a finish scope will execute all the statements in the finish scope which may spawn one or more children. It will then wait for all tasks created in the finish scope to terminate. The language permits arbitrary level of nesting of async and finish scopes.

The HabaneroC runtime uses a work-stealing scheduler that supports work-first and help-first policies [30]. In the work-first policy, the current thread will start to execute a newly spawned task, adding a continuation, representing its parent task, to its work queue from which other threads can steal it. In the help-first policy, the worker will make the child task available for stealing and continue executing the parent task. The work-first policy is good for scenarios when work-stealing is rare, but it performs poorly in situations when the task continuation encompasses high parallelism that is not split into tasks, such as a for loop creating tasks using the async statement. It also has a provable memory bound but can overflow the stack for large irregular computations. The help-first policy performs well when stealing is frequent, it uses little stack but the memory usage can be large. Previous work [30] has shown how the two policies perform in different scenarios and that an adaptive approach that can switch between the two policies can yield good performance improvement and efficient stack and memory usage.

For locality, HabaneroC uses Hierarchical Place Trees (HPTs) [31]. HPTs define hierarchical trees of execution location which are an abstraction for underlying hardware. These places could be cores, groups of cores sharing different levels of cache or devices such as GPUs or FPGAs. The HC language allows the programmer to spawn a task explicitly at such a place and the work-stealing runtime is designed to take advantage of this information and preserve locality.

### 2.3 Concurrent Collections

Concurrent Collections (CnC) [9] is a shared memory, dynamic light-weight task-based parallel programming model. The model can also be described as a macro-dataflow coordination language as it specifies how steps interact with each other or depend on each other, separating these dependences into data and control dependences. A program in the CnC model is defined by a graph describing the dependences between serial pieces of computation called steps.

A graph specification for any program will be built using three components: steps, items and tags. These are grouped into collections:

- 1. a step collection is a group of steps with the same functional behaviour with respect to their inputs. They are declared using parenthesis and are represented graphically using circles.

- 2. an item collection is a group of data items having the same type. They are declared in the textual representation using brackets and in the graphical representation using rectangles.

- 3. a control collection is a group of tags or keys used to uniquely identify items and steps within their respective collections, hence the name tag collection is often used as well. These are declared using angle brackets and are pictured as triangles.

The Concurrent Collection model enforces a dynamic single assignment for items added (*Put*) in an item collection, thus also ensuring that the value that a step will read (*Get*) is the same every time (if the item is empty, the Get operation simply blocks). This property makes the model provably deterministic and race-free [9].

| CnC Flavours               | Intel CnC    | Rice CnC-HJ  | Rice CnC-HC  |

|----------------------------|--------------|--------------|--------------|

| Language                   | C++          | Java         | С            |

| Single Assignment Enforced | -            | $\checkmark$ | $\checkmark$ |

| Gets before Puts           | $\checkmark$ | $\checkmark$ | 1            |

| Data Dependent Gets        | ¥            | ¥            | -            |

| Tag Functions              | -            | -            | ¥            |

| Auto-generated Step Stubs  | V            | ¥            | ¥            |

| Auto-generated Gets        | -            | -            | V            |

| GPU Extensions             | -            | $\checkmark$ | $\checkmark$ |

Table 2.1 : Comparison between different implementation flavours of the ConcurrentCollection model

An implementation dependent property is that of dead-lock freedom. Dead-lock can occur if a step is waiting on an item that is never written, and if the manner this behaviour is implemented in the runtime involves a blocking operation. The CnC-HC implementation we present in this thesis is dead-lock free.

The original definition and implementation of the Concurrent Collections model was done by Intel. The language chosen for the step and runtime implementation in the Intel release is C++ [32]. A second implementation designed and implemented in the Habanero group is CnC-HJ which uses HabaneroJava (HJ) [11] for defining steps, modelling parallelism and ensuring data availability. This thesis presents our work on CnC-HC which uses HabaneroC as the language for implementing CnC steps and for interaction between the CnC-HC runtime, CPU steps and device steps.

We list the differences between these three flavours of CnC in the table 2.1. The

single assignment rule is defined in the specification language of the CnC model, but it is only enforced in the HJ and HC implementations making these more accurate in terms of respecting the language specification.

In all flavours of CnC, a translator is used to interpret the graph specification and generate a series of files that are either used to interact with the runtime or are used as step stubs or suggestion code, all of these offering help to the programmer. The Intel CnC implementation also includes an API which allows more experienced users to bypass the translator.

In all implementations, the calls to the Get functions within a step, that read data, precede the calls to the Put functions, but this restriction is not imposed in Intel's implementation, whereas it is in the Java and C versions. However, this is not in fact a limitation, as any step executing a sequence of Get-Put-Get-Put operations can be split into multiple steps, each adhering to the rule of calling Get before Put. Implementing a source-to-source translator to automate splitting of steps, is a good opportunity for future research.

A feature which we introduced for the first time in the CnC model is a means to auto-generate Get functions by introducing *tag functions* in the graph specification language. We detail this in Chapter 3. Another aspect relating to this is that of data-dependent Gets. This means that information from the one of the items read is used to determine which item is read next. The HC implementation requires that items read be independent of each other due to the addition of tag functions which we believe are a good improvement for usability. This restriction can in fact be relaxed as any step that needs data-dependent Gets can also be split into two or more steps which do not have this requirement. Splitting a step can be fully automated and is a subject for future work, as with splitting steps to ensure the Gets-before-Puts rule. An extension explored in CnC-HJ and CnC-HC is the ability to execute CnC steps on GPU devices, while the model manages the data transfers to and from the device. In addition, we extended the model with a notion of affinity, as a way of specifying multiple types of device steps and having the ability to achieve load balancing between CPUs, GPUs and FPGAs. This is described in Chapter 6.

Another flavour currently under development at Rice University is CnC-Python [33, 34].

#### 2.4 The CUDA programming model

The NVIDIA CUDA programming model is an interface which enables programmers to access the highly parallel hardware of programmable Graphics Processing Units (GPUs). Though initially designed for graphics rendering, these GPUs are now being used for a wide variety of applications, including image and video processing, computational biology and chemistry, fluid dynamics simulation, CT image reconstruction, seismic analysis, ray tracing, and much more [35].

CUDA is an extension of the C programming language, with the CUDA runtime library providing a collection of device memory management, host-device stream synchronization, and execution control functions (among others). The general flow of a CUDA program consists of the following steps [36], where all allocation and copying of device memory is controlled explicitly or implicitly by the host using the CUDA runtime library:

- 1. CPU initiates a data copy from CPU main memory to GPU memory

- 2. CPU instructs GPU to start a kernel

- 3. GPU executes the kernel in parallel and accesses GPU memory

4. CPU initiates a copy that moves results from GPU memory to CPU main memory.

CUDA is a data parallel SIMT architecture, in which the same programmer-defined kernels execute on all launched threads. These threads are launched in batches of blocks and grids, where blocks are collections of threads and grids are collections of blocks [1].

#### 2.5 Related work

Previous work was done for extending different aspects of the Concurrent Collections model. We first worked on developing GPU extensions in the Java flavour of CnC, thus creating CnC-CUDA and obtaining encouraging results [1]. This was a strong motivation for dropping the overhead introduced by making native calls from the Java language and defining steps in a lower level language, more flexible in terms of communication with devices, while keeping the ease of use introduced by CnC. Other extensions include obtaining performance through determining streaming patterns [37].

An active area of research is that of developing programming models to make full use of a set of heterogeneous hardware resources including one or more of CPUs, GPUs, FPGAs or PPUs and SPUs in IBM's Cell processor. Several models have been developed that attempt to abstract the hardware resources for the user, provide an easy to use model while achieving better performance than homogeneous architectures. OpenCL [7] has proposed introducing a standard for heterogeneous programming, so that programs written using the OpenCL API could run on both CPUs and GPUs. The standard was implemented by different graphics card vendors and seems be gaining favour in the community, however, it is a low-level model that relies on the programmer to understand low-level hardware details. Another major drawback that will need to be addressed is the capability of running on different kinds of GPUs within a program.

There has been extensive work on extending existing languages for hybrid execution. Many have proposed using OpenMP-like constructs. StarSs ([38]) is an example which proposes the use of pragmas to split a program into tasks and define data dependence requirements. This does not address the usability problem for domain experts and it restricts parallelism to forall statements rather than the arbitrary graphs that CnC can define.

StarPU [39, 40] is a another runtime system designed for hybrid CPU and GPU execution. It is similar to our work on affinity (Chapter 6) in that a task can be specified to be "fit" for running on the CPU or GPU (".where = CORE|CUDA") and the choice can be made by runtime systems. In CnC-HC we use a HabaneroC runtime call to determine the nature of the current thread to decide which code to run, whereas in StarPU the information is retrieved from a structure making the device-function associations. StarPU also implements a complex memory model in order to manage coherence among CPU and device. This is not needed in CnC as all steps are functional with respect to their inputs and the model is dynamic single assignment, so the data can only be written once. StarPU has extensions for the GPU and Cell but does not address FPGAs. On the opposite side, there are systems that address just CPUs and FPGAs [41], and companies such as Convey [2] which enable the usage of the C language using a shared memory view for accessing FPGAs. Aside from addressing multiple architectures, we also focused on offering high usability by allowing users to specify their algorithm at a high level by means of tasks dependences and automatically generating most of the code necessary to enable parallelism.

A less recent programming model is Merge [42], which distinguishes itself by offering a predicate dispatch-based library system for managing and invoking function variants for different architectures. Merge is a high level language based on mapreduce, having a compiler and runtime responsible for dynamically selecting the best function variant depending on the program and the machine it is run on. Merge is built on top of EXOCHI[43], which allows the available execution units to execute in the same address space, thus making it easy to involve all of them in the computation. This facilitates scheduling (only one global scheduler is needed) and cooperation for Merge. However, in order to use Merge, a new processor/accelerator would need to support the EXOCHI interface, then to be assigned a unique identifier used for predicate dispatch and finally implement function variants for it. What is more, the EXOCHI model has several other drawbacks: it relies on the programmer to ensure cache coherency, it has specific requirements that limit the set of architectures that could use the cache coherence mechanism they provide and it makes strong assumptions about hardware capabilities (e.g., the existence of a TLB on EXO sequencers).

At the other end of the spectrum we find domain specific languages (DSL), which tackle the problem of running on heterogeneous hardware by extending a high-level language like Java. The most recent ones are the DeLite project from Stanford [44, 45] and the Lime language from IBM Research [46]. These approaches are much more complex as they need a source-to-source compiler to convert the conventional code into "native" code (= suited for a particular application) such as C, OpenCL, CUDA or Verilog and a runtime that can interact with the native libraries generated. Work done on previous so called domain specific virtual machines (DSVM) like RapidMind (acquired by Google) or PeakStream (now used in Intel's Array Building Blocks), targeted lower level languages such as C and C++, but in a similar way: the computation would be expressed in a data-parallel manner and compiled for different architectures.

The DSVM's and DSLs approach in general is to enable the same code to be compiled for different processing units, thus missing on many optimizations and lowering performance. They can be more restrictive than what this work proposes (they don't allow an existing algorithm in a different language to be "plugged-in" the application and interact with the rest of the steps, even if that language is supported as a "native" variant). On the other hand, compared to a multi-variant language such as Merge, DSVMs certainly offer a significantly simpler programming model. Quilin [47] is a system which combines the two approaches. It proposes automatic mapping of applications on heterogeneous architectures by using a training run to collect runtime profile information and then use this to divide computations within an application between a CPU and GPU, while also allowing filters to have CPU and GPU hand coded variants. Their approach yields good performance improvements as well as reduction in energy consumption. One assumption Quilin makes for determining the best mapping is that the step's performance varies linearly with its input, which is not true for all applications; also, it only targets CPUs and NVIDIA GPUs, restricting the languages in which a user can hand-code their computation step.

An improvement no other language proposes and that our work brings, is that CnC introduces another level of abstraction where domain experts will simple write "this\_step writes into this\_item\_collection" in a simple format:

(this\_step) -> [ this\_item\_collection ], before moving to such language details as declaring variables, understanding the syntax, etc.. This approach also offers a highly desirable property: easy maintenance, as previous algorithms or computation steps can be reused by knowing their behaviour, not the implementation details, and they can also be replaced with no effort even by algorithms implemented in other languages if the application was initially designed as a dependence graph. In addition, none of the languages presented here can express arbitrary task graphs as CnC, thus offering more generality than other models.

The approach taken in this work is a mix of some of the best parts from the languages presented so far. We introduce ranges in an attempt to describe dataparallel computations, which could map a computation to the GPU transparent to the user by auto-generating the host-device communication. This feature can limit performance as the application would not be tuned for the GPU and also limits the applications that can be written using it to those with data-parallel constructs, yet it would be easy to write by a programmer, with good speedup compared to the CPU only run. On the other hand, we also allow multiple variants of the same step for different architectures and introduce step affinity for different devices in order to dynamically choose where a step is run based on available implementations, hardware availability and knowledge of where the step may run faster.

We conclude that this research builds on and improves past work because the individual tasks in our data-flow programming model can be still expressed in almost any language (including explicitly parallel languages), providing flexibility and reuse of the existing algorithms.

## Chapter 3

## Graph language extensions for CnC-HC

The CnC model was designed to enable the separation between a domain expert, who can provide an accurate problem specification at a high level, and a tuning expert, who can tune the individual components of an application for better performance. However, in the current high-level definition of a program described by a domain expert, the provided information on the data flow is rather vague. The data in a CnC program is grouped in collections, called item collections. The information one can draw from a CnC specification is from what item collection is a step reading and into which item collection it is writing. However, there is no means of knowing from that specification which item it should read so such information wll need to be given also by the domain expert inside the step code. As a result, the domain expert would have to get familiar with an API provided by the CnC runtime in order to make accurate function calls for reading and writing items inside a step.

This work offers an alternative, which removes the need for a domain expert to learn such implementation details, thus increasing programmability.

We introduce *tag functions*, a means of accurately specifying the dependences on specific items belonging to an item collection and between instances of the same or different steps. In this work, a tag function maps a step's unique identifier, the control tag, to the tags (keys) of the items read or written through Get and Put operations respectively, and control items written that enable other steps. We also introduce a way to specify *ranges* of items for item and control collections, by means of two tag

functions representing the start and end of a range.

These additions to the CnC graph specification provide support for automatic code generation of Get functions that retrieve the data required by a step - as well as suggested code for the items written and steps prescribed. What is more, the addition of tag functions makes the program flow more analysable opening new research opportunities, while introducing ranges can be used to extend CnC for other SIMD/SIMT architectures like the GPUs, by allowing parallelism within a step.

The extensions we propose in this work make clearer the separation between the problem definition and its implementation, ensure an easy way of programming through code generation and are further motivated by our goal to design CnC to be mapped onto heterogeneous hardware platforms such as the Customizable Heterogeneous Platform (CHP) being developed in the NSF Expeditions Center for Domain-Specific Computing (CDSC [12] [13]).

#### 3.1 Tag functions

To better understand the notion of tag functions in the context of the CnC graph let us first look at the simple graph specification example shown in listing 3.1, an example used in the CDSC project.

In this example, line 1, using angle brackets, declares a tag of type int. In the classical CnC [9] representation of tag functions, the type can be any user defined type, which can be detailed as being composed of multiple components. For example, the declaration on line 1 could also be written as:  $\langle 1DType \ reg\_tag: \ pos \rangle$ , where the tag would be of type 1DType, having one component called pos. Similarly more complex types can be defined such as:  $\langle 3DType \ position\_in\_3D: \ row, \ col, \ depth \rangle$  which declares a type that will have 3 components.

```

1 < int reg_tag > ;

2 [ float*** input_matrices ] ;

3 [ float*** output_matrices ] ;

4 <reg_tag> :: ( registration );

5 [ input_matrices ] -> ( registration ) -> [ output_matrices ];

6 env -> <reg_tag>, [ input_matrices ];

7 env <- [ output_matrices ];</pre>

```

Listing 3.1: Example 1: CnC graph without tag functions

Lines 2 and 3 declare two item collections, both being 3D matrices of type float. This means that each item found in either of the item collections will be a matrix and each such matrix will be uniquely identified by a tag within the item collection.

Following the item collection declarations is a step prescription (line 4). This is equivalent to saying that when an tag is put in  $\langle reg\_tag \rangle$  tag collection, a step identified by the same tag can start to execute. In the CnC model steps are functional with respect to their inputs and outputs.

The next line (line 5) defines the producer-consumer relations for the step *reg-istration*. We also call these relations "execution relations". Each instance of the registration step can read data from the item collection *input\_matrices* and can write data into the item collection *output\_matrices*. Both relations have full generality, meaning the step can read zero, one or more matrices and can also write a variable number of items as its output.

The last two lines in the graph specification (lines 7 and 8) define the I/O relation with outer environment, which will be responsible for writing into the *input\_matrices* and *reg\_tag* collections and read from the *output\_matrices*.

```

1 < int [1] reg_tag > ;

2 [ float*** input_matrices ] ;

3 [ float*** output_matrices ] ;

4 <reg_tag> :: ( registration );

5 [ input_matrices : k-1 ] -> ( registration : k ) -> [

output_matrices : k-1 ];

6 env -> <reg_tag>, [ input_matrices ];

7 env <- [ output_matrices ];</pre>

```

Listing 3.2: Example 2: CnC graph with tag functions

Let us now look at the same example with some of the extensions added in this thesis (listing 3.2).

An addition to the classical definition of a CnC graph [9] is the introductions of tag sizes in the declaration of a tag, which defines how many components a tag has. For the code to be accurately generated, we need to know the type of each tag. Currently, both the translator and the code generator support any tag type, but the current method of creating a tag from multiple components is defined to accept just a subset of tag types: integer. The format of the tag may be extended to support tuples of different types, for example: (int, char, double, char\*). Offering something transparent for the user for general tag types, in the current format, where tags are strings, requires additional compiler support (e.g., a call to "createTag(int, char, double)" being transformed into "initTag;addInt(int);addChar(char);addDouble(double)"). A more general and efficient alternative is to change the CnC runtime implementation such that tags become arrays of unions. We reserve this for future work, though the programmer can obtain that functionality by marshalling and unmarshalling any tuple into a tuple of ints or creating his own tag creation method.

Item collections are expected to be declared with the correct element type, either a primitive or a user defined type. All items in an item collection are stored internally as pointers but they can be declared both as pointers and non-pointer types (a primitive value will be "boxed" using a pointer).

Instances of computation steps are uniquely identified by tags, which are tuples of symbolic names chosen by the one writing the CnC specification. In a prescription relation, such as the one on line 4 in listing 3.2, the control collection (reg\_tag) will contain a set of tags t which enable the execution of steps identified by t. Consequently, the format of such a tag does not need to be explicit in a prescription relation. This is synonymous with saying that the tag function of a tag t in a control collection is the identity: f(t)=t. Thus, is our implementation of the CnC model, step prescription are kept in the same format as in the classical CnC graph, which also preserves the previous behaviour that a tag can prescribe multiple steps and a step can only be prescribed by one tag. If the user chooses to add tag functions to step prescription as well, the translator will issue a warning, keep the implicit identity function relation and it will ignore the unnecessary tag functions.

In contrast, in an execution relation, a step can read and write multiple inputs and outputs respectively and these can vary greatly depending on the application. To provide flexibility in defining dependences, the items to be read and/or written by a step are defined as functions of the tag's components, thus the name tag function. In the above example, on line 5, the *registration* step is identified by a tag with one element, by means of variable k. The step is defined to get an item from item collection *input\_matrices* and the function to find that element is k - 1. This allows easy code generation without the need of computing the inverse of a function in step executions. Consider if in the above example, the step was identified by  $k^{*2}$  rather than k. This would mean that the correct item to read for any step with tag T is (T-1)/2 obtained by applying the function defined for input *input\_matrices* (f(x) = x-1) to the inverse function of the step identifier (f(x) = x/2). Our approach is the most intuitive way a user would define the task graph, by relating both the inputs and the outputs of a step to what uniquely identifies a step (its tag components).

In the general case of a tag declared to have N dimensions, a get will be performed on a collection: [collection\_name : tagfunction1, tagfunction2, ..., tagfunctionN], where the functions accept the 4 basic operators (+,-,\*,/) and any variable name, yet the variable names should relate to the variables found in the steps list for the generated code to be correct. All items read and written by the step, as well as the tags put to prescribe other steps, can be defined with functions relative to the step's control tag and constants. In addition, the step's outputs (both data and control items) can be declared as relative to the input data, with the indexing operator (e.g.: input[tag component]]). In the above example, the step registration has only one output. It will write an element in collection output\_matrices and this element will be uniquely identified by the key k - 1, representing a tag function. Extensions for more complex functions and user-defined functions are a subject for future work.

For a better understanding of how tag functions can be used, we present a second example, one simulating the execution of a loop with a variable stride.

The example in listing 3.3 contains only one type of computation steps called "loop" (the only key word in a CnC graph is *env* symbolizing the environment), which will in fact execute the body of a while loop, translating the condition to continue to the next iteration into a prescription of another instance of the step "loop"; the tag thus becomes the iteration number. The loop's exit condition is dependent on

Listing 3.3: Example 3: CnC graph simulating a loop

the value of size[0], where size is a collection with only one item. Each step with tag = k, will do some computation on the input matrix obtained from the item collection *input\_matrix* and may enable the execution of the next loop iteration which is computed using the data read from the *jump* item collection. We notice that the item in which the step writes the output (*output\_matrices*) is identified by a tag relating to the step's unique identifier (k) and to the input item jump[k].

This example shows clearly that a step can choose whether to write or not in the outputs (item or tag collections) declared in the graph specification. This loop will eventually terminate when some condition regarding k and size[0] is met (e.g. k>=size[0]) which is synonymous with concluding that we cannot generate *Put* functions or *Prescribe* functions with the same certainty we can generate the *Gets*. For program completeness we require the user to write the tag functions both for inputs and outputs, however the code generated for outputs will be considered as a suggestion rather than a requirement. We believe this design choice will help the user since he would only have to reason about dependences rather than writing code (the suggested code will need very little modifications, if any).

We must mention that we kept backward compatibility to the classic CnC model, such that if tag sizes or tag functions are omitted, the translator will generate suggested code in comment detailing how the Gets should be performed. Writing the proper code remains the users responsibility in this case, as in the original CnC specification.

### 3.2 Ranges

Another addition to the CnC graph specifications is the concept of ranges. Several applications require that several pieces of data in a continuous range be either read or written or both. For a fix number of items known at compile time, this could have been represented by scalar tag functions. For example:

$(some\_step:k) \rightarrow \langle step\_tag:k \rangle, \langle step\_tag:k+1 \rangle, \langle step\_tag:k+2 \rangle \ .$

However, if the number of items read or written is determined at runtime, we need a new way of way of allowing the user to provide this information. Ranges are declared in the CnC graph file using braces and two dots to separate the beginning and end of the range: { *start\_range .. end\_range* }.

Let us consider the example in listing 3.2 once again. In essence, the graph in the example models the execution of multiple instances of fluid registration [48] with no dependences among each other. One will imagine that after defining this graph, the user would have to write the Main function to Put a set of tags, each of which will start an independent step. Considering this, let us create another example that

```

1 < int [1] singleton_tag > ;

2 < int [1] reg_tag > ;

3 [ int size ] ;

4 [ float *** input_matrices ] ;

5 [ float *** output_matrices ] ;

6 <singleton_tag> :: ( singleton_step );

7 <reg_tag> :: ( registration );

8 [ size : 0 ] -> ( singleton_step : t ) -> <reg_tag : { 1 ... size

[0]+1 }>, [ input_matrices : { 0 ... size[0] } ];

9 [ input_matrices : k-1 ] -> ( registration : k ) -> [

output_matrices : k-1 ];

10 env -> [ size ], <singleton_tag>;

```

Listing 3.4: Example 4: CnC graph with ranges

would make the Main call simpler for the user, by using ranges.

In the example from listing 3.4, the user main function would just have to just prescribe a single step, the *singleton\_step* and write the code of initializing the inputs and starting all the registration steps within it. We have shown a possible use case of ranges, but in practice there are several others such as split join operations and reducers. In addition, specifying that a step reads a range of items may be extended to mean that the computation performed is data parallel and thus fit for SIMT execution.

In this chapter, we presented how tag and item collections allow and need the ability to specify tag functions for automatic generation of high level operations for inter-task communication. We will go into more detail of how the code is generated from these specifications in chapter 4.

# Chapter 4

# Compiler support for CnC-HC

In this chapter we present the CnC-HC translator, a tool that generates the necessary code to link the user step code to the CnC runtime as well as suggested step code regarding the items to be put or steps to be prescribed, all these based on the CnC graph specifications.

# 4.1 Software lifecycle with CnC-HC

Let us first discuss what are the steps that a user has to make in order to write a program using CnC-HC. Figure 4.1 presents the implementation flow for a CnC-HC program.

The user will first decompose his algorithm into steps and write a graph specification as described in the previous chapter. The translator is a tool which will generate a series of "glue-code" to enable transparent parallelism for the user based on the guidelines he provided in the graph file. What is more, it will offer step stubs as suggested step code to handle the items a step puts or the steps it may enable. In order to ensure an easy build, the translator will also generate a makefile.

The user can then proceed to writing the code for each of the computation steps and run the makefile to build his application. This will use the HC compiler and gcc compiler and generate an executable. If additional libraries are required, they can be easily added in the provided Makefile.

Figure 4.1 : CnC-HC Build Model

A common scenario in developing a program is making changes to the initial specification. In our case, if the user were to make changes to the graph file and rerun the translator, only the code linking his steps with the runtime will be overwritten to match the new dependences. Thus, if the computation had been written by a programmer prior to running the translator, his code will not be overwritten, but preserved intact.

#### 4.2 Auto-generated executable code

The need for generation of "glue code" is due to application dependent components like item collections and steps but also to the usage of the C language. Some of the artifacts that we need to generate include: an unique identifier for each step, methods that initialize or delete a CnC graph, methods that launch the execution of other steps 1 #define Step\_registration 0

```

2 struct Context{

```

```

3 ItemCollectionEntry ** input_matrices;

```

```

4 ItemCollectionEntry ** output_matrices;

```

5 };

```

6 typedef struct Context Context;

```

Listing 4.1: Auto-generated code defining a unique step id and the context structure for the example in Listing 3.2.

and methods that link the user code to the CnC runtime.

For the example in Listing 3.2 the auto-generated code declaring the step identifier and the item collections is presented in Listing 4.1.

The generated methods can be divided into two parts: the methods available to the user as APIs and the methods generated to transparently enforce constraints as specified by the CnC graph. Let us describe these below using code samples for the example in Listing 3.2.

The auto-generated methods included in the user API are: initGraph, delete-Graph, prescribeStep.

The pair of methods initGraph and deleteGraph are called to instantiate and clear the allocated space respectively, for a CnC graph. The initGraph method will reserve the space for all item collections used in the graph and perform other initialization steps if required, while its complement method will free this allocated space. Each item collection is implemented as a hashtable with a fixed number of buckets (TABLE\_SIZE) defined by the runtime. Here is some sample auto-generated code

```

1 Context* initGraph() {

int i;

2

Context* CnCGraph = (Context*) cnc_malloc (1 * sizeof(Context

3

));

CnCGraph->output_matrices = (ItemCollectionEntry **)

4

cnc_malloc(TABLE_SIZE * sizeof(ItemCollectionEntry*));

for (i=0; i < TABLE_SIZE; i++)

\mathbf{5}

CnCGraph \rightarrow output_matrices[i] = NULL;

6

}

7

return CnCGraph;

8

9 }

10 void deleteGraph(Context* CnCGraph){

cnc_free(CnCGraph->output_matrices, TABLE_SIZE * sizeof(

11

ItemCollectionEntry*));

cnc_free(CnCGraph, 1 * sizeof(Context));

12

13 }

```

Listing 4.2: Auto-generated code initializing and disposing of a graph.

declaring one item collection: Listing 4.2 (we extracted only the initialization for one of the collections for brevity).

The method prescribeStep instantiates a new step, with the corresponding tag and, depending on the chosen runtime, prepares for step execution accordingly (either begins to check dependency satisfaction or sends the step straight for execution taking the chance of the step to fail if data is unavailable; the runtimes are details in chapter 5). An extract of the code generated for this method can be seen in listing 4.3.

). The cherace of the code generated for this motion can be been in houng no.

As the generated files are independently compiled, we use a HabaneroC pragma

```

1 #pragma hc suspendable

2 void prescribeStep(char* stepName, char* stepTag, Context*

context){

Step * step = cnc_malloc(sizeof(Step));

3

step \rightarrow tag = stepTag;

4

// ... step initialization

\mathbf{5}

if (! \operatorname{strncmp}(\operatorname{stepName}, "\operatorname{registration} \setminus 0", 12)) \{

6

step \rightarrow stepID = Step_registration;

7

#ifndef _Data_Driven_Runtime

8

dispatchStep(step);

9

#else

10

registration_dependencies(step->tag, (Context*)step->

11

context , step);

int status = resolveDependencies(step);

12

if (status == CNC_SUCCESS)

13

dispatchStep(step);

14

#endif

15

return;

16

}

17

printf("Step %s not defined \n", stepName);

18

assert(0);

19

20 }

```

Listing 4.3: Auto-generated code for prescribing a new step.

```

1 #pragma hc suspendable

2 void* registration_gets (char * tag, Context * context, Step* step

){

int k = getTag(tag, 0);

3

float *** input_matrices0;

Δ

char* taginput_matrices 0 = createTag(1, k);

5

CNC_GET((void **) & (input_matrices0), taginput_matrices0,

6

context->input_matrices, step);

registration( k, input_matrices0, context );

7

return 0;

8

9 }

```

Listing 4.4: Auto-generated code for getting the input data for a step.

(line 1 in listing 4.3) to mark as interruptible, methods that can spawn tasks and therefore need to be treated differently by the source to source compiler (the details are beyond the scope of this work). We also note on lines 9, 11, 14 calls to autogenerated methods and on line 12 a call to the CnC runtime.

The auto-generated methods that are needed to link the user code to the runtime are: stepName\_dependencies, stepName\_gets, dispatch. For each step we will generate a pair of functions called stepName\_dependencies and stepName\_gets. The former will make runtime calls to store the list of all dependences needed to be satisfied for a step to execute and is only used in the Data Driven runtime. For the graph in Listing 3.2, the method performing the Get calls is presented in listing 4.4. Here, we highlight three runtime calls on line 3, 5 and 6 and a call to the user-written step code on line 7. void dispatchStep(Step\* step){

```

2 switch(step->stepID){

3 case Step_registration: async IN(step){ registration_gets(

step->tag, (Context*)step->context, step); }; break;

4 default: CNC_ASSERT(0, "Attempt at executing an unknown step

!");

5 }

6 }

```

Listing 4.5: Auto-generated code for asynchronously spawning a task.

Calling the dispatch method (listing 4.5) is equivalent to asynchronously executing a step. The generated code for this implies using the async construct provided by HabaneroC to asynchronously launch the execution of a step. This means running the auto-generated code for getting the data needed by a step and then doing the actual user code call. The runtime chosen will determine whether the creation of an asynchronous launch will be equivalent to a successful step execution or a possible failed attempt that will need to be retried. For the scheduling of the tasks launched using the async keyword, CnC will be using HabaneroC's work stealing mechanism. The policy (work first or help first) can be chosen through a command line argument to the executable.

### 4.3 Auto-generated helper code

The translator will use the information provided by the user in the graph file to also generate helper code for the steps. For example if a step was defined to possibly create a control item (tag), the step code will include a comment of how this would translate into code. More precisely, the generated code will call prescribeStep on all steps prescribed by that tag. The user can use this code as he/she sees fit, though in most cases simply uncommenting the suggested code and making minor changes will give the desired user code. In listing 4.6) we present some sample suggested code for a more complex example (the graph from listing 3.4). The step stub for the singleton step contains two comment blocks. The first one refers to data items written, while the second contains the prescription code. The graph specification defined the step to write a range of items, consequently, the generated code will have a for loop with the number of iterations equal to the elements in the range, and it will make the runtime call that writes an item on each iteration. If the specification was accurate, the user would simply have to uncomment this code block and read from an external source, initialize or compute the items to be written. Similarly, the suggested code prescribing the registration steps would be uncommented and, in this case, no additional changes would be needed.

As mentioned before, running the translator on a graph file will also generate a Makefile for building the application using the generated files. This can be altered by the user to meet the application needs, such as adding other source files or libraries.

```

void singleton_step( int k, int size0, Context* context){

/* This is suggested code

\mathbf{2}

int _index1_0;

3

float *** input_matrices 1 [size 0 - 0];

4

for (\_index1_0 = 0; \_index1_0 < size0 - 0; \_index1_0++){

\mathbf{5}

// allocate memory if necessary and fill in values to put

6

here

char* taginput_matrices 1 = \text{createTag}(1, \_\text{index}1_0 + 0);

\overline{7}

Put(input_matrices1[_index1_0], taginput_matrices1,

8

context->input_matrices);

}

9

*/

10

/* This is suggested code

11

int _index2_0;

12

for (\_index2_0 = 0; \_index2_0 < size0; \_index2_0++){

13

char* tagreg_tag2 = createTag(1, \_index2_0);

14

prescribeStep("registration", tagreg_tag2, context);

15

}

16

*/

17

18 }

```

Listing 4.6: Auto-generated suggested step code for handling data and control output edges.

# Chapter 5

# Runtime support for CnC-HC