# ULTRA LOW POWER SUBTHRESHOLD DEVICE DESIGN USING NEW ION

# IMPLANTATION PROFILE

A DISSERTATION IN Electrical and Computer Engineering and Physics

Presented to the Faculty of the University of Missouri - Kansas City in partial fulfillment of the requirements for the degree

# DOCTOR OF PHILOSOPHY

by

# MUNEM HOSSAIN

M.Sc., South Dakota State University, Brookings, SD, USA, 2012 B.Sc., Khulna University of Engineering and Technology, Khulna, Bangladesh, 2009

> Kansas City, Missouri 2016

ALL RIGHTS RESERVED

MUNEM HOSSAIN

© 2016

# ULTRA-LOW POWER SUB-THRESHOLD DEVICE DESIGN USING NEW ION IMPLANTATION PROFILE

Munem Hossain, Candidate for the Doctor of Philosophy Degree

University of Missouri-Kansas City, 2016

# ABSTRACT

One of the important aspects of integrated circuit design is doping profile of a transistor along its length, width and depth. Devices for super-threshold circuit usually employ halo and retrograde doping profiles in the channel to eliminate many unwanted effects like DIBL, short channel effect, threshold variation etc. These effects are always become a serious issue whenever circuit operates at higher supply voltage. Subthreshold circuit operates at lower supply voltage and these kind of effects will not be a serious issue. Since subthreshold circuit will operate at much lower supply voltage then devices for subthreshold circuit does not require halo and retrograde doping profiles. This will reduce the number of steps in the fabrication process, the parasitic capacitance and the substrate noise dramatically.

This dissertation introduces four new doping profiles for devices to be used in the ultralow-power subthreshold circuits. The proposed scheme addresses doping variations along all the dimensions (length, width and depth) of the device. Therefore, the approaches are three dimensional (3D) in nature. This new doping scheme proposes to employ Gaussian distribution of doping concentration along the length of the channel with highest concentration at the middle of the channel. The doping concentration across the depth of the device from the channel region towards the bulk of the device can follow one of the following four distributions: (a) exponentially decreasing, (b) Gaussian, (c) low to high, and (d) uniform doping. The proposed doping scheme keeps the doping concentration along the width of the device uniform. Therefore, under this scheme we achieve four sets of new 3D doping profiles. This dissertation also introduces a new comprehensive doping scheme for the transistors in subthreshold circuits. The proposed doping scheme would bring doping changes in the source and drain areas along with the substrate and channel region of the transistors. The proposed doping scheme is characterized by the absence of halos at the source and drain end. We propose a Gaussian doping distribution inside the source, drain region and a low-high-low distribution across the depth of the transistor from the channel surface towards the body region. It also has a low-high-low doping distribution along the length of the transistor below the channel region.

Results show that a device optimized with proposed doping profiles would offer higher ON current in the subthreshold region than a device with the conventional halo and retrograde doping profiles. Among the four 3D doping profiles for subthreshold device some has better ON current than others. Based on specific requirements one of these four doping profiles can be adopted for different ultra-low-power applications. Our analysis shows better subthreshold swing can be achieved using new doping profile based subthreshold design. Results also show that the optimized

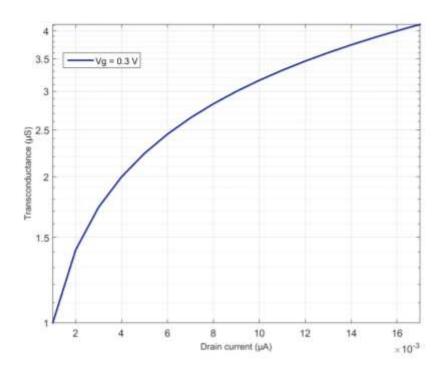

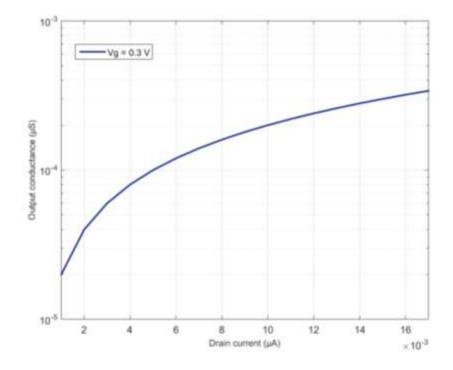

device with the proposed comprehensive doping profile would provide higher ON current ( $I_{on}$ ) at smaller body bias condition. The analysis is performed by changing the doping profile, body bias and ( $V_{gs}$ ) to observe the off-state current ( $I_{off}$ ), threshold voltage variation, magnitude of  $I_{on}/I_{off}$  ratio, transconductance and the output conductance with the proposed doping profiles.

#### APPROVAL PAGE

The faculty listed below, appointed by the Dean of the School of School of Graduate Studies have examined a dissertation titled "Ultra Low Power Sub-Threshold Device Design Using New Ion Implantation Profile," presented by Munem Hossain, candidate for the Doctor of Philosophy degree, and certify that in their opinion it is worthy of acceptance.

# Supervisory Committee

Masud H. Chowdhury, Ph.D., Committee Chair Department of Electrical and Computer Engineering

Ghulam M. Chaudhry, Ph.D. Department of Electrical and Computer Engineering

Deb Chatterjee, Ph.D. Department of Electrical and Computer Engineering

Cory Beard, Ph.D. Department of Telecommunications and Computer Networking

> Paul Rulis, Ph.D. Department of Physics

# CONTENTS

| AE  | BSTRACTiii                                 |

|-----|--------------------------------------------|

| LI  | ST OF ILLUSTRATIONSix                      |

| LI  | ST OF TABLESxiii                           |

| LIS | ST OF ABBREVIATIONSxiv                     |

| AC  | CKNOWLEDGEMENTS                            |

| Ch  | apter                                      |

| 1.  | INTRODUCTION                               |

|     | 1.1. Motivation1                           |

|     | 1.2. Background                            |

|     | 1.3. Problem Statement                     |

|     | 1.4. Contribution of the Dissertation      |

|     | 1.5. Organization of the Dissertation      |

| 2.  | SUBTHRESHOLD BACKGROUND                    |

|     | 2.1. MOSFET Basic                          |

|     | 2.2. Origin of Subthreshold Circuit Design |

|     | 2.3. Subthreshold Current                  |

|     | 2.4. Power, Energy and Frequency           |

|    | 2.5. Minimum Energy Operation                       | 14 |

|----|-----------------------------------------------------|----|

|    | 2.6. Leakage Mechanism                              | 16 |

|    | 2.7. Conclusion.                                    | 21 |

| 3. | IMPLANTATION PROFILES                               | 22 |

|    | 3.1. Introduction                                   | 23 |

|    | 3.2. Proposed Doping Scheme for Subthreshold Device | 26 |

|    | 3.3. Mathematical Modelling and Analysis            | 28 |

|    | 3.4. Conclusion                                     | 47 |

| 4. | THRESHOLD VOLTAGE CALCULATION.                      | 50 |

|    | 4.1. Introduction                                   | 51 |

|    | 4.2. Subthreshold Doping Scheme                     | 53 |

|    | 4.3. Threshold Voltage Modelling                    | 58 |

|    | 4.4. Analysis of Subthreshold Swing Characteristics | 63 |

|    | 4.5. Prospects and Challenges                       | 64 |

|    | 4.6. Conclusion and Future Work                     | 67 |

| 5. | COMPREHENSIVE IMPLANTATION PROFILE                  | 69 |

|    | 5.1. Introduction                                   | 70 |

|    | 5.2. Proposed Comprehensive Doping Scheme           | 72 |

|    | 5.3. Results and Analysis                           | 74 |

|    | 5.4. Conclusion.                                    | 87 |

| 6. | CONCLUSION AND FUTURE WORK                          | 89 |

| RE | EFERENCE LIST                                       | 92 |

| VI | ТА                                                  | 98 |

# LIST OF ILLUSTRATIONS

| Figure |                                                                                                                                                                                                                                                                                                               | Page |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| [1]    | Device structure of an n-channel MOSFET                                                                                                                                                                                                                                                                       | 8    |

| [2]    | Transistor current characteristics                                                                                                                                                                                                                                                                            | 12   |

| [3]    | Energy per cycle for an 8-bit ripple carry adder through HSPICE simulation in PTM                                                                                                                                                                                                                             | 16   |

| [4]    | Short-channel transistor mechanisms: $(I_1)$ , reverse biased p-n junction; $(I_2)$ , subthreshold or weak inversion; $(I_3)$ , drain-induced barrier lowering; $(I_4)$ , punch-through; $(I_5)$ , gate-induced drain leakage; $(I_6)$ , gate oxide tunneling; and $(I_7)$ , hot-carrier injection.           | 17   |

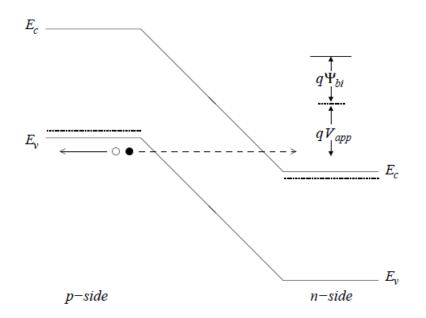

| [5]    | Band-to-band tunneling in an nMOS: valence band electron tunneling from the valence band of the p-side to the conduction band of the n-side; the total voltage drop across the junction, the reverse bias voltage and the built-in voltage is greater than the energy-band gap, $(V_{app} + \psi_{bi} > E_g)$ | 18   |

| [6]    | Tunneling of electrons: direct tunneling occurs when the potential drop across the gate oxide is lower than the barrier height of the tunneling electron ( $V_{ox} < \phi_{ox}$ )                                                                                                                             | 20   |

| [7]    | Injection of hot electrons from the substrate to the oxide                                                                                                                                                                                                                                                    | 20   |

| [8]    | (a) Subthreshold logic region of operation and (b) average power consumption of different technology nodes                                                                                                                                                                                                    | 25   |

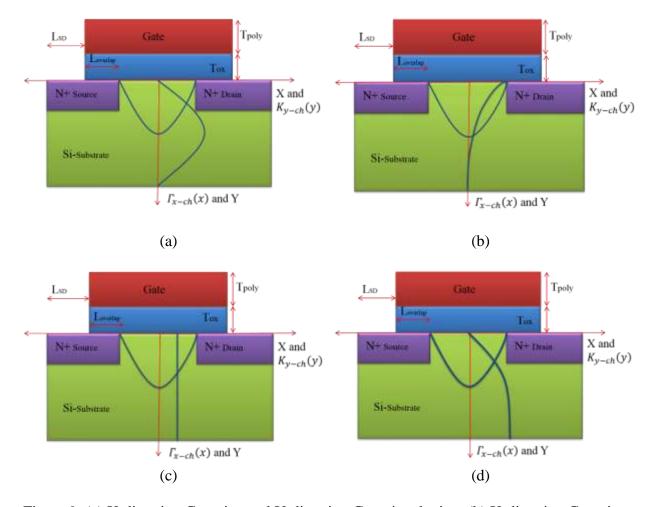

| [9]    | (a) X-direction Gaussian and Y-direction Gaussian doping, (b) X-direction<br>Gaussian and Y-direction Exponentially decreasing doping (c) X-direction<br>Gaussian and Y-direction uniform doping, and (d) X-direction Gaussian and Y-<br>direction low-to-high doping                                         | 26   |

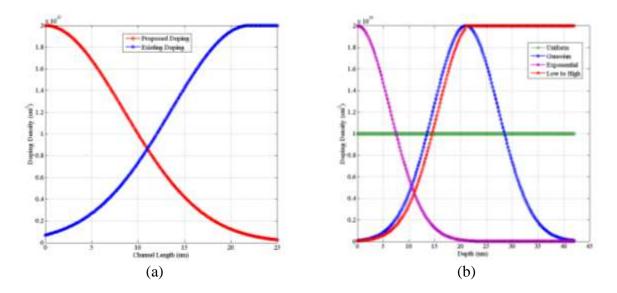

| [10] | (a) Doping distribution along X-dimension – from the middle of the channel to drain (source) end and (b) all four doping distribution along Y-direction from the top surface of the channel towards the bottom surface of the substrate. In (a) red is for the proposed doping profile for subthreshold device and blue is of conventional device.                                                                                                                                                                                                                      | 28 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

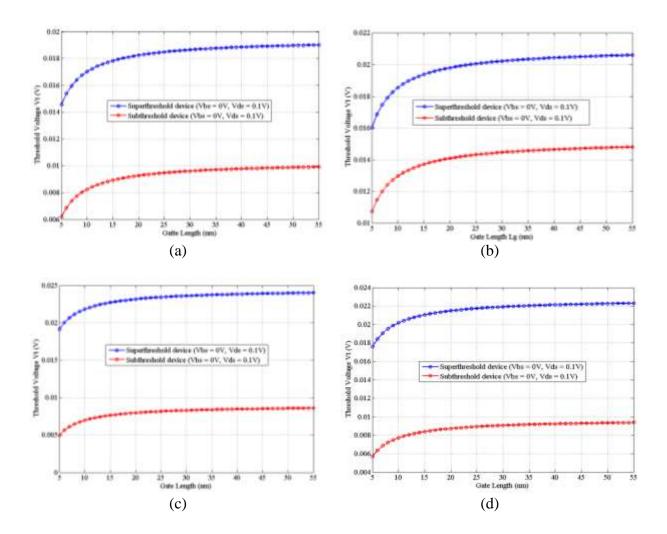

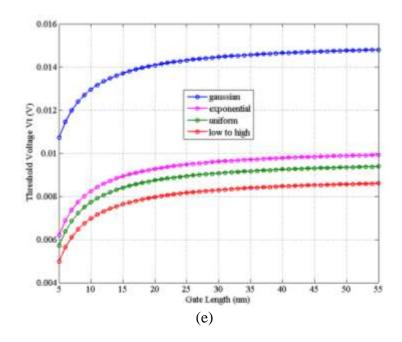

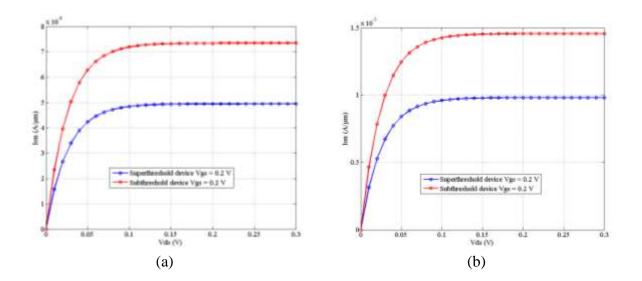

| [11] | Threshold voltage variation with gate length: (a) exponentially decreasing doping profile, (b) Gaussian doping profile, (c) low to high doping profile (d) uniform doping profile and (e) combined threshold voltage versus gate length for subthreshold device. Where $N_{SD} = 1.7 \times 10^{19}$ and $N_{sub} = 1.0 \times 10^{15}$                                                                                                                                                                                                                                 | 35 |

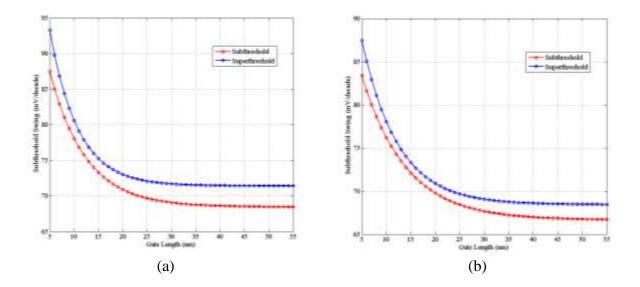

| [12] | SS variation with gate length for subthreshold and super-threshold device: (a) exponentially decreasing doping profile, (b) Gaussian doping profile, (c) low to high doping profile (d) uniform doping profile and (e) combined SS versus gate length for subthreshold device at constant $I_{off} = InA/\mu m$ . Where $L_{eff} = 50 nm$ , $W_{eff} = I\mu m$ , doping density at source and drain region $N_{SD} = 1.7 \times 10^{19}$ , $t_{ox} = Inm$ , $T = 300 K$ , $\sigma 1_{y-ch} = 21 nm \sigma 1_{x-ch} = 10 nm$ and $V_{dd} = 0.2 V$                        | 36 |

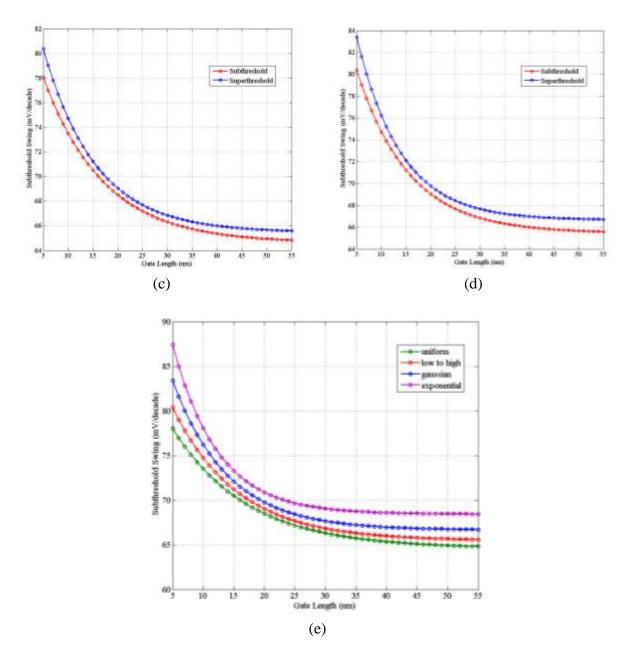

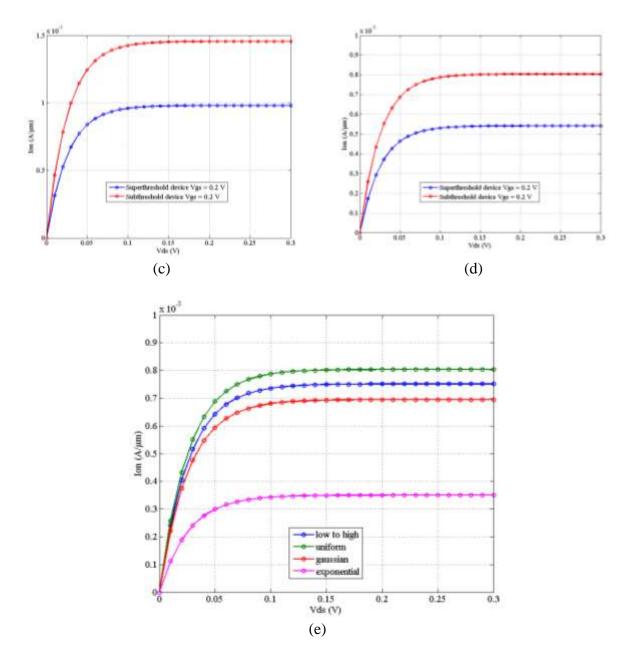

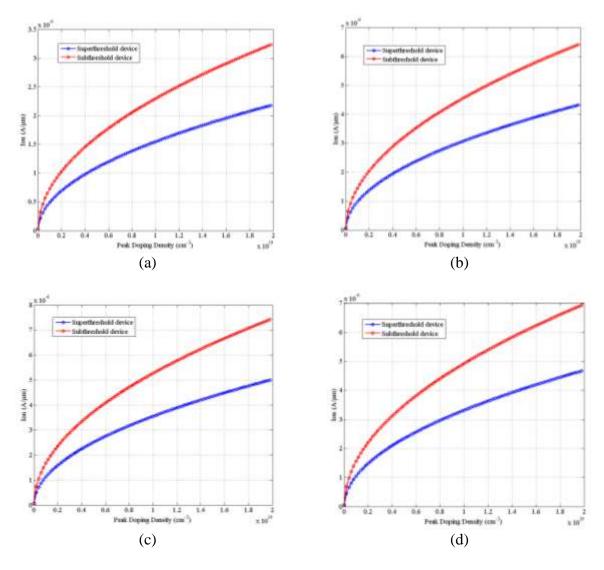

| [13] | $I_{on}$ variation with $V_{ds}$ for subthreshold and super-threshold device: (a) exponentially decreasing doping profile, (b) Gaussian doping profile, (c) low to high doping profile (d) uniform doping profile and (e) combined $I_{on}$ variation with $V_{ds}$ for subthreshold device at constant $I_{off} = InA/\mu m$ . Where $L_{eff} = 50 nm$ , $W_{eff} = I\mu m$ , doping density at source and drain region $N_{SD} = 1.7 \times 10^{19}$ , $t_{ox} = Inm$ , $T = 300 \text{ K}$ , $\sigma 1_{y-ch} = 21 nm \sigma 1_{x-ch} = 10 nm$ and $V_{dd} = 0.2$ V. | 41 |

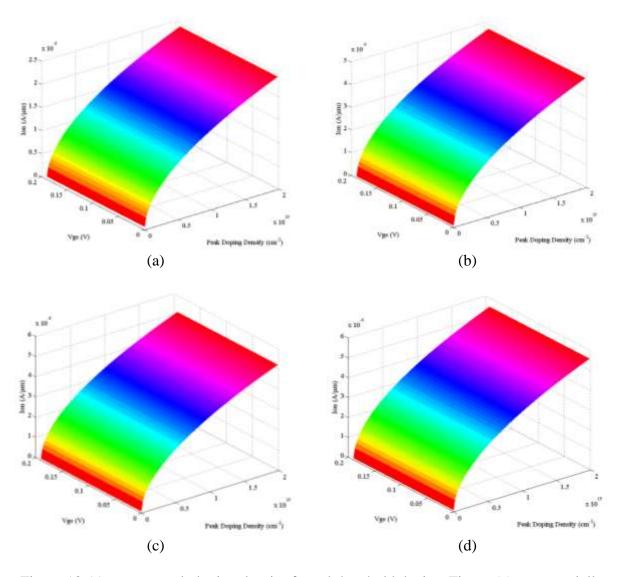

| [14] | $I_{on}$ -Peak doping density for super- and sub-threshold device: (a) exponentially decreasing doping profile, (b) Gaussian doping profile, (c) low to high doping profile and (d) uniform doping profile at constant $I_{off} = InA/\mu m$ . Where $L_{eff} = 50$ nm, $W_{eff} = I\mu m$ , doping density at source and drain region $N_{SD} = 1.7 \times 10^{19}$ , $t_{ox} = Inm$ , $T = 300$ K, $\sigma 1_{y-ch} = 21$ nm $\sigma 1_{x-ch} = 10$ nm and $V_{dd} = 0.2$ V.                                                                                          | 42 |

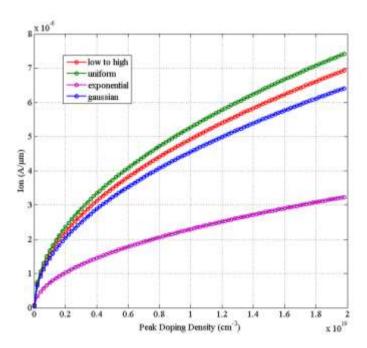

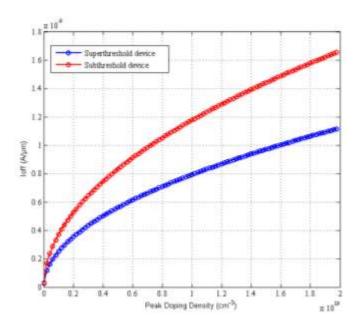

| [15] | Combined Ion-peak doping density comparison for among four different doping profiles for subthreshold operation at constant $I_{off} = lnA/\mu m$                                                                                                                                                                                                                                                                                                                                                                                                                       | 44 |

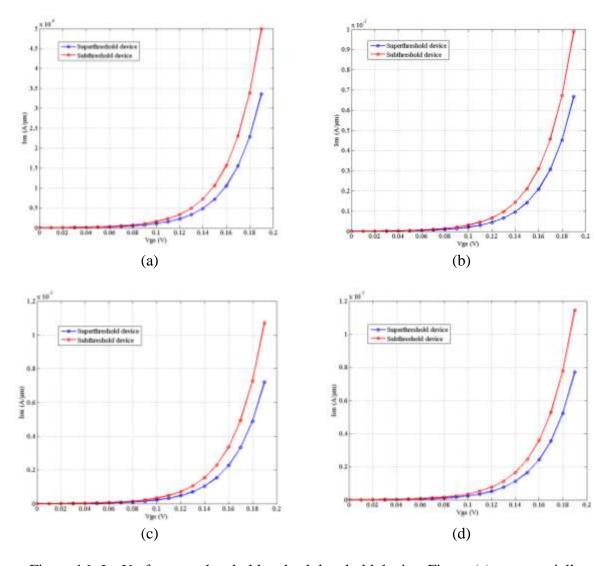

| [16] | $I_{on}$ - $V_{gs}$ for super-threshold and subthreshold device. Figure (a) exponentially decreasing doping profile, (b) Gaussian doping profile, (c) low to high doping profile and (d) uniform doping profile at constant $I_{off} = InA/\mu m$ . Where $L_{eff} = 50$ nm, $W_{eff} = I\mu m$ , doping density at source and drain region $N_{SD} = 1.7 \times 10^{19}$ , $t_{ox} = Inm$ , $T = 300$ K, $\sigma 1_{y-ch} = 21$ nm $\sigma 1_{x-ch} = 10$ nm and $V_{dd} = 0.2$ V.                                                                                     | 45 |

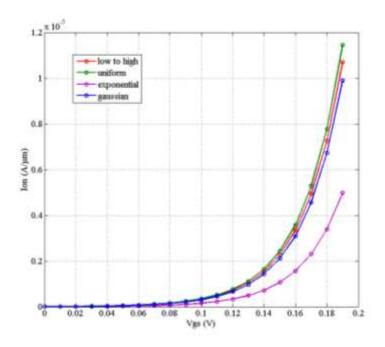

| [17] | $I_{on}$ - $V_{gs}$ comparison among four different doping profile for subthreshold operation<br>at constant $I_{off} = InA/\mu m$                                                                                                                                                                                                                                                                                                                                                                                                                                      | 46 |

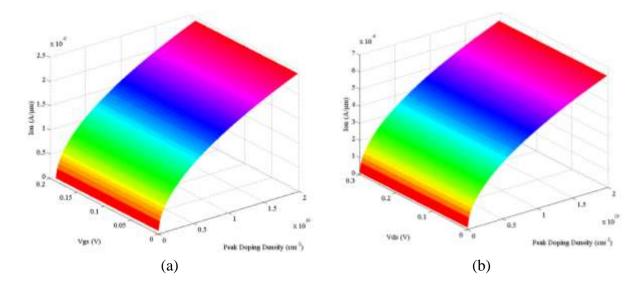

| [18] | $I_{on}$ - $V_{gs}$ -peak doping density for subthreshold device. Figure (a) exponentially decreasing doping profile, (b) Gaussian doping profile, (c) low to high doping profile and (d) uniform doping profile                                                                                                                                                                                          |    |  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|

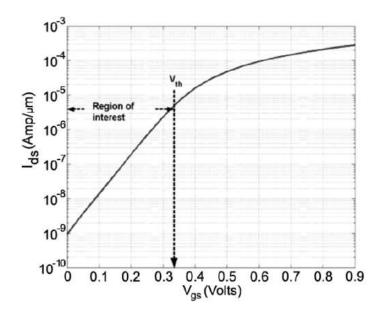

| [19] | Subthreshold logic region of operation                                                                                                                                                                                                                                                                                                                                                                    |    |  |

| [20] | X-direction Gaussian and Y-direction Exponentially decreasing doping. Where, $L_{eff} = 50$ nm, $W_{eff} = 1\mu m$ and $t_{ox} = 1nm$ .                                                                                                                                                                                                                                                                   |    |  |

| [21] | (a) Doping distribution along X-dimension – from the middle of the channel to drain (source) end and (b) Doping distribution along Y-direction from the top surface of the channel towards the bottom surface of the substrate. Red is for the proposed doping profile for subthreshold device and blue is of conventional device.                                                                        | 55 |  |

| [22] | $I_{on}$ - $V_{gs}$ -peak doping density for subthreshold device and $I_{on}$ - $V_{ds}$ -peak doping density for subthreshold device                                                                                                                                                                                                                                                                     | 56 |  |

| [23] | <i>I</i> <sub>off</sub> -Peak doping density for super-threshold and subthreshold device                                                                                                                                                                                                                                                                                                                  | 57 |  |

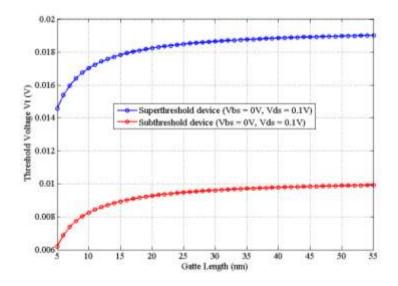

| [24] | Threshold voltage variation with gate length                                                                                                                                                                                                                                                                                                                                                              |    |  |

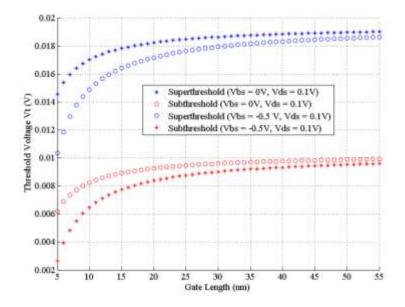

| [25] | Threshold voltage variation with change of gate length at $V_{ds} = 0.1V$ and $V_{bs} = 0$ ,<br>-0.5V. Where $L_{eff} = 50 \text{ nm}$ , $W_{eff} = 1\mu m$ , doping density at source and drain region<br>$N_{SD} = 1.7 \times 10^{19}$ , $t_{ox} = 1nm$ , $T = 300 \text{ K}$                                                                                                                           | 61 |  |

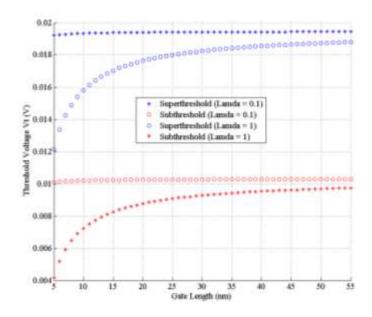

| [26] | Threshold voltage variation with change of gate length at fitting parameter $\lambda = 0.1$ and 1. Where $L_{eff} = 50$ nm, $W_{eff} = 1\mu m$ , doping density at source and drain region $N_{SD} = 1.7 \times 10^{19}$ , $t_{ox} = 1$ nm, $T = 300$ K, $V_{bs} = 0V$ , and $V_{ds} = 0.1V$ .                                                                                                            | 61 |  |

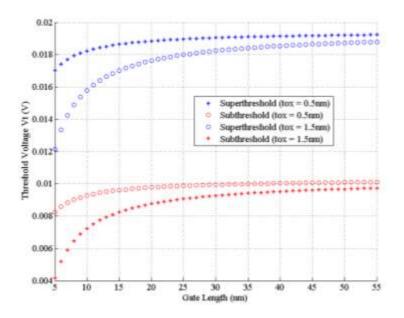

| [27] | Threshold voltage variation with change of gate length at oxide thickness $t_{ox} = 0.5nm$ and $1.5 nm$ . Where $L_{eff} = 50 nm$ , $W_{eff} = 1\mu m$ , doping density at source and drain region $N_{SD} = 1.7 \times 10^{19}$ , $t_{ox} = 1nm$ , $T = 300 K$ , $V_{bs} = 0V$ , and $V_{ds} = 0.1V$ .                                                                                                   | 62 |  |

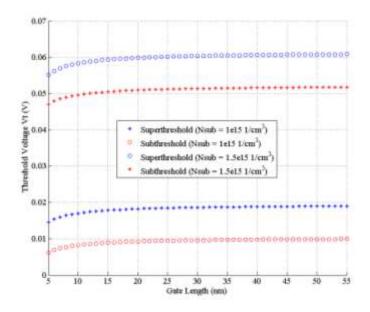

| [28] | Threshold voltage variation with change of gate length at uniform substrate doping $N_{sub} = 1.0 \times 10^{15} \text{ cm}^{-3}$ and $1.5 \times 10^{15} \text{ cm}^{-3}$ . Where $L_{eff} = 50 \text{ nm}$ , $W_{eff} = 1 \mu m$ , doping density at source and drain region $N_{SD} = 1.7 \times 10^{19}$ , $t_{ox} = 0.5 nm$ , $1.5 nm$ , $T = 300 \text{ K}$ , $V_{bs} = 0V$ , and $V_{ds} = 0.1V$ . | 62 |  |

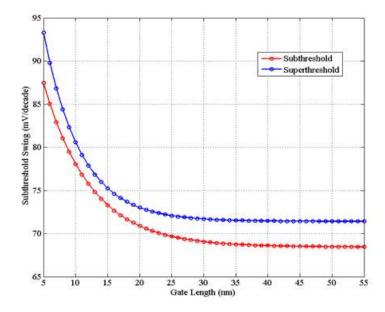

| [29] | Subthreshold swing versus gate length for super-threshold and subthreshold device.                                                                                                                                                                                                                                                                                                                        | 64 |  |

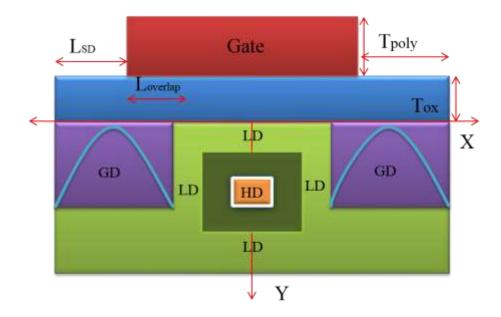

| [30] | Proposed doping scheme: Gaussian distribution (GD) in the source/drain region, low-high-low doing along the depth of the device, and low-high-low doping                                                                                                                                                                                                                                                  |    |  |

|      | along the length of the device under the channel region. Channel length of 15 nm, channel width $1 \ \mu m$ and oxide thickness is $1 \ nm$                                                                                                       | 72 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

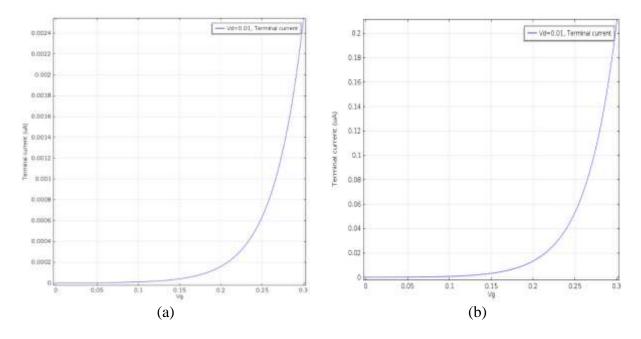

| [31] | (a) Gate voltage vs drain current at $V_d = 0.01 V$ and $V_{bs} = 0 V$ . The threshold voltage is approximately 0.17 V. (b) Gate voltage vs drain current at $V_d = 0.01 V$ and $V_{bs} = -0.1 V$ . The threshold voltage is approximately 0.20 V | 76 |

| [32] | Drain voltage versus drain current for different gate voltage and (a) $V_{bs} = 0 V$ , (b) $V_{bs} = -0.1 V$ .                                                                                                                                    | 78 |

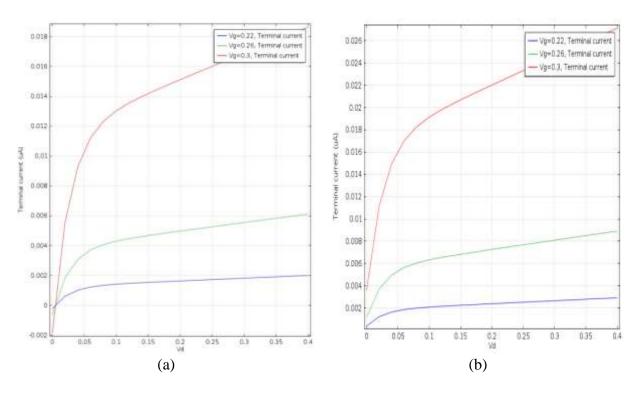

| [33] | Off current for body bias (a) $V_{bs} = 0 V$ , (b) $V_{bs} = -0.1 V$                                                                                                                                                                              | 79 |

| [34] | Transconductance as a function of the drain current under a gate voltage of $10 \text{ mV}$                                                                                                                                                       | 82 |

| [35] | Output conductance as a function of the drain current under a gate voltage of $10  mV$                                                                                                                                                            | 82 |

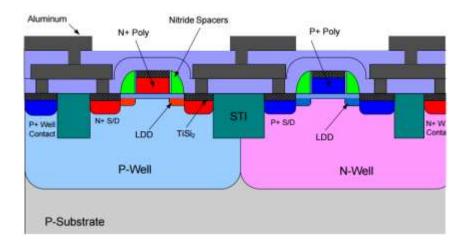

| [36] | CMOS cross section showing NMOS (left) and PMOS (right) transistor                                                                                                                                                                                | 83 |

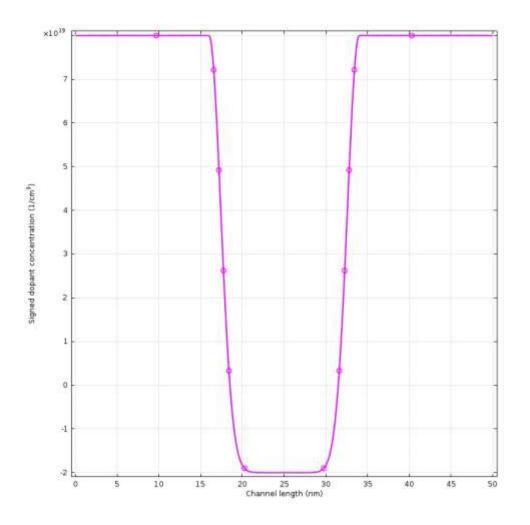

| [37] | Dopant distribution along the channel length                                                                                                                                                                                                      | 84 |

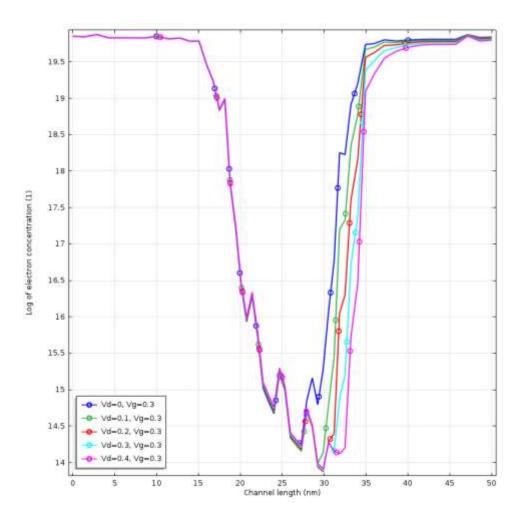

| [38] | Electron concentration along the channel length                                                                                                                                                                                                   | 85 |

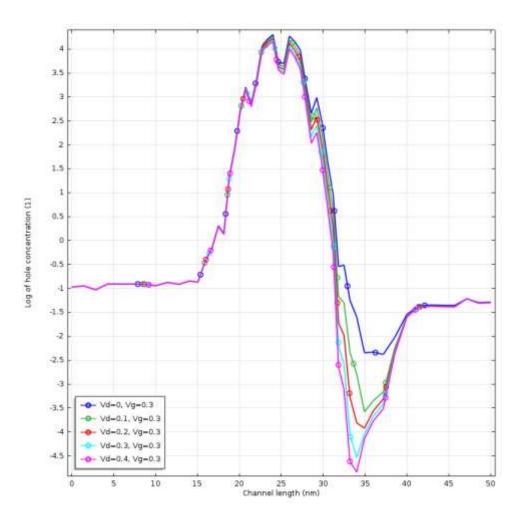

| [39] | Hole concentration along the channel length                                                                                                                                                                                                       | 86 |

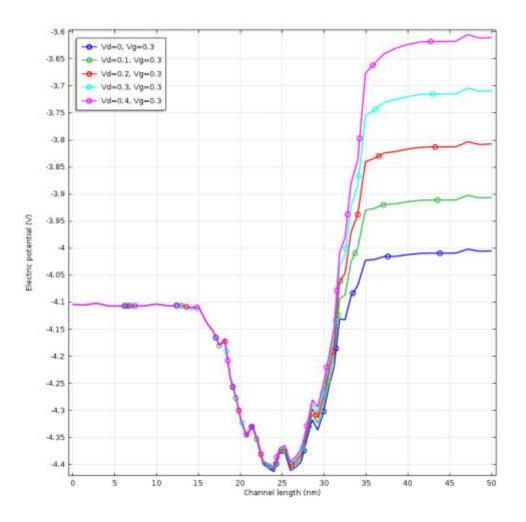

| [40] | Variation of electric potential with channel length                                                                                                                                                                                               | 87 |

# LIST OF TABLES

| Table |                                                                                                                                                                                               | Page |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1.    | Intrinsic delay of gate length 50 nm                                                                                                                                                          | 37   |

| 2.    | $R_{eff}$ and $C_{eff}$ sub components of delay value                                                                                                                                         | 38   |

| 3.    | Tabulated $I_{on}$ at constant $I_{off} = lnA/\mu m$                                                                                                                                          | 38   |

| 4.    | Summaries of transistor behavior                                                                                                                                                              | 79   |

| 5.    | Data table for the list of device (*** this work) with varying gate length ( $L_G$ ), threshold voltage ( $V_{th}$ ), $I_{on}$ , $I_{off}$ , $I_{onf}$ , MOSFET technology and doping profile | 81   |

# LIST OF ABBREVIATIONS

| LAC    | Lateral Asymmetric Channel                        |

|--------|---------------------------------------------------|

| DSM    | Deep Sub Micron                                   |

| HD     | Halo Doping                                       |

| DH     | Double Halo Doping                                |

| UD     | Uniform Doping                                    |

| RCP    | Retrograde Channel Profile                        |

| SSR    | Super Steep Retrograde                            |

| SSRW   | Super Steep Retrograde Well                       |

| LDD    | Lightly Doped Drain                               |

| DG     | Double Gate                                       |

| MOS    | Metal Oxide Semiconductor                         |

| CMOS   | Complementary Metal Oxide Semiconductor           |

| MOSFET | Metal Oxide Semiconductor Field Effect Transistor |

| TFET   | Tunneling Field Effect Transistor                 |

| BTBT   | Band to Band Tunneling                            |

| SOC    | System on Chip                                    |

| SOI    | Silicon on Insulator                              |

| ULP    | Ultra Low Power                                   |

| DIBL   | Drain Induced Barrier Lowering                    |

| GIDL   | Gate Induced Drain Leakage               |

|--------|------------------------------------------|

| SCE    | Short Channel Effect                     |

| GD     | Gaussian Distribution                    |

| PUN    | Pull Up Network                          |

| PDN    | Pill Down Network                        |

| TCAD   | Technology Computer Aided Design         |

| GCDMDG | Graded Channel Dual Material Double Gate |

| RFID   | Radio Frequency Identification           |

| ΙΟΤ    | Internet of Things                       |

#### ACKNOWLEDGEMENTS

I would like to dedicate my dissertation to my family members who constantly inspired me to pursue higher studies. I would like to thank them all who stood behind all these years during my degree.

I would like to express my gratitude and appreciation for my academic advisor Dr. Masud Chowdhury for his encouragement, guidance and leadership. Without his tireless effort and advice, this personal achievement wouldn't be possible.

I would also like to thank my committee members Dr. Ghulam M. Chaudhry, Dr. Masud Chowdhury, Dr. Deb Chatterjee, Dr. Cory Beard and Dr. Paul Rulis for their advice, support and guidance throughout my degree.

I would also like to thank my colleagues and friends, Dr. Mahabube Khoda Siddiki, Emeshaw Ashenafi, Nahid Hossain, Azzedin Es-Sakhi, Muhammad Sana Ullah, Abdul Hamid Bin Yousuf, Maruf Khan, Abdullah Alharbi, and Moqbull Hossen for their constant support during my degree.

Finally I would like to thank all of my teachers, educational administrators, present and past and all who helped me achieve this academic goal.

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 Motivation

One of the important aspects of integrated circuit design is the doping profile of a transistor along its length, width and depth. Devices for super-threshold circuit usually employ halo and retrograde doping profiles in the channel to eliminate many unwanted effects. Devices for subthreshold circuits do not require halo and retrograde doping profiles like conventional superthreshold devices. This will reduce the number of steps in the fabrication process, the parasitic capacitance, and the substrate noise dramatically in the subthreshold devices. The proposed doping scheme would bring changes in doping properties along the length (X direction) and depth (Y direction) of the device and keep the doping concentration along the width constant. The doping profile in X direction is kept somewhat constant in most of the previous designs and only the Y direction doping profiles have been varied. We propose a three-dimensional doping scheme, where doping profiles would be varied in both directions. We propose to adopt Gaussian distribution of doping density in the X direction and four different doping profiles in the Y directions for subthreshold devices. Based on the proposal we would get four possible combinations of twodimensional doping profiles. Superposition of two 2D doping profiles in X and Y directions would lead to a 3D doping profile for the device under each combination. In this dissertation we will focus on the following four combinations of 3D doping profiles: (i) Gaussian distribution of doping profiles

in both X and Y direction, (ii) Gaussian distribution in X and exponentially decreasing in Y direction, (iii) Gaussian distribution in X and low-to-high distribution in Y direction, and (iv) Gaussian distribution in X and uniform distribution in Y direction. For all four combinations we assume the doping density along the width of the device is uniform. It is anticipated that each combination will have certain prospects and constrains for different applications of subthreshold circuits. In this dissertation, we plan to show that for a particular technology generation, lower power and higher performance can be achieved in the subthreshold region by redesigning the devices specifically for subthreshold operation.

## 1.2 Background

Device, circuit, architecture, and system level requirements for ultra-low-power subthreshold circuits (that would be operated below the threshold voltage) are often different from the conventional super-threshold circuits (that are operated above the threshold voltage). Also, the requirements would be different for digital, analog, and mixed signal applications [1], [2]. One of the important aspects of the design is the doping profile along the length, width, and depth of a transistor. Deeply scaled analog CMOS device design for system-on-chip (SOC) applications is very challenging because of the conflicting requirements of the analog and digital circuits [3], [4]. Also, aggressive scaling of power supply is preferred in digital logic circuits, but this leads to degraded signal range and lower design margins for analog circuits [5]. It is observed that with lateral asymmetric channel (LAC) doping the total gate capacitance of a transistor is reduced by almost 10% in the saturation region at 100nm technology node compared to the conventional MOSFETS [6], [7]. Transistor capacitances have significant influences on its RF performance. Furthermore, in the subthreshold region, the transistor input capacitance is less than that of strong inversion operation. The transistor input capacitance in subthreshold is a combination of intrinsic

capacitance, depletion capacitance, parasitic capacitance and fringing capacitances of a transistor. In contrast, the input capacitance in strong inversion operation is dominated by the oxide capacitance. Due to the smaller capacitance and lower supply voltage (maximum limit is the threshold voltage of the transistor) digital subthreshold circuits consume significantly less power than their strong inversion counterpart at a particular frequency of operation. In [8], the electron velocity overshoot phenomenon in the inversion layer is experimentally investigated for a novel thin film silicon-on-insulator (SOI) test device with channel lengths down to 0.08µm. The test SOI structure used LAC doping profile [9]. The high field drift velocity of the inversion carriers is measured. Simulation results show that very uniform carrier density and drift velocity can be achieved with LAC profile in SOI device.

Short-channel devices are usually optimized for super-threshold circuits to ensure higher mobility, lower drain-induced barrier lowering (DIBL), reduced leakage, and minimal threshold voltage roll-off. However, a transistor optimized for super-threshold circuit may not be optimal for the subthreshold region where effects like DIBL, threshold voltage roll-off, and electron/hole tunneling are much less significant [10]. As a consequence, high doping, traditionally used in the super-threshold device to overcome the short-channel effect (SCE) will not be critical for subthreshold operation [11]. In super-threshold device, the main functions of halo and retrograde doping [12], [13] are to reduce DIBL, prevent body punch through, and control the threshold voltage of the device independent of its subthreshold slope. Since DIBL, body punch through and threshold voltage variation are not severe in the subthreshold device due to lower supply voltage, the halo and retrograde doping is not required for such design. High to low doping profile has been proposed for subthreshold operation in [10]. For subthreshold circuit operation lower subthreshold swing and internal device capacitances are critical. However, existing doping profiles do not offer any means to address these critical needs. Also the operating current of subthreshold device is the subthreshold leakage current of the conventional device. Because of the low voltage and leakage current based operation subthreshold circuits will not operate at very high frequency.

#### 1.3 Problem Statement

This dissertation introduces four new doping profiles for devices to be used in the ultralow-power subthreshold circuits. The proposed scheme addresses doping variations along all the dimensions (length, width and depth) of the device. Therefore, the approaches are three dimensional (3D) in nature. This new doping scheme proposes to employ Gaussian distribution of doping concentration along the length of the channel with highest concentration at the middle of the channel. The doping concentration across the depth of the device from the channel region towards the bulk of the device can follow one of the following four distributions: (a) exponentially decreasing, (b) Gaussian, (c) low to high, and (d) uniform doping. The proposed doping scheme keeps the doping concentration along the width of the device uniform. Therefore, under this scheme we achieve four sets of new 3D doping profiles. The doping concentration across the depth of the device is exponentially decreasing means channel surface has highest concentration of dopant distribution and bulk is contained with less dopant distribution. The Gaussian distribution across the depth of the device turn the device into low dopant distribution at the top and bottom surface whereas middle surface is filled with more dopant distribution. Similarly, low to high distribution is somewhat opposites of exponentially decreasing distribution with very small distribution of dopant at the top surface and high distribution underneath the bulk. Finally, uniform distribution specify the equally distributed dopant inside the device from top surface to the bottom surface.

This dissertation also introduces a new comprehensive doping scheme for the transistors in subthreshold circuits. The proposed doping scheme would bring doping changes in the source and drain areas along with the substrate and channel regions of the transistors. The proposed doping scheme is characterized by the absence of halos at the source and drain ends. We propose a Gaussian doping distribution inside the source and drain regions, and a low-high-low distribution across the depth of the transistor from the channel surface towards the body region. It also has a low-high-low doping distribution along the length of the transistor below the channel region.

# 1.4 Contribution of the Dissertation

In this dissertation four different subthreshold doping profile and one comprehensive doping profile has been proposed and mathematically solved for subthreshold application. The main four subthreshold doping profiles are composed of X dimension and Y dimension varying dopant distribution. This new doping scheme proposes to employ Gaussian distribution of doping concentration along the X dimension (length of the channel) with highest concentration at the middle of the channel. The doping concentration across the Y dimension (depth of the device) from the channel region towards the bulk of the device can follow one of the following four distributions: (a) exponentially decreasing, (b) Gaussian, (c) low to high, and (d) uniform doping. Results show that a device optimized with any of the four proposed doping profiles would offer higher ON current in the subthreshold region than a device with the conventional halo and retrograde doping profiles. Among the four 3D doping profiles for the subthreshold device some has better ON current than the others. Based on specific requirements one of these four doping profiles can be adopted for different ultra-low-power applications. Threshold voltage modelling has been performed and a comparative analysis is presented between super-threshold and subthreshold devices threshold voltages. We have also analyzed the subthreshold swing characteristics

of the device with the proposed doping profiles. Our analysis shows that better subthreshold swing can be achieved using our new doping profile based subthreshold design.

In comprehensive doping scheme a Gaussian doping distribution inside the source and drain regions, and a low-high-low distribution across the depth of the transistor from the channel surface towards the body region. It also has a low-high-low doping distribution along the length of the transistor below the channel region. We simulated this comprehensive doping scheme using COMSOL Multiphysics simulation tools. Results show that the optimized device with the proposed doping profiles would provide higher ON current ( $I_{on}$ ) at smaller body bias condition. The analysis is performed by changing the doping profile, the body bias, and the gate-source voltage ( $V_{gs}$ ) to observe the off-state current ( $I_{off}$ ), threshold voltage variation, magnitude of  $I_{on}/I_{off}$  ratio, transconductance, and the output conductance with the proposed doping profiles.

## 1.5 Organization of the Dissertation

In chapter 1 we have discussed the background of the proposed doing profile. We explained our proposed doping profile and summarizes the contribution of whole work. In chapter 2 we have explained the theory behind the MOS subthreshold device, different power issue, different leakage currents and other details. In chapter 3 we have shown our detail analysis of four different doping profile by solving all the proposed doping profile equations. In chapter 4 we shown threshold voltage and subthreshold swing modelling of the one of the proposed doping profile. In chapter 5 we simulated comprehensive doping profile using COMSOL Multiphysics simulation tools and analyzed and compared our results with existing work published recently. Finally, chapter 6 we have concluded our all work and analysis with some future work for further continuation of this research.

#### CHAPTER 2

#### SUBTHRESHOLD BACKGROUND

This chapter begins with an introduction to subthreshold circuits. It then explains the behavior of a transistor in the subthreshold region of operation. The difference between power, energy and frequency of operation in subthreshold and super-threshold circuits is explained. In this chapter, we provide the fundamental aspects of subthreshold design for ultra-low power circuits [36]. A description of subthreshold circuit properties as given here will be helpful to illustrate our proposed methods in this dissertation. This chapter introduces the problem of power consumption in modern deep sub-micron devices. Subsequently, a description of a transistor's leakage mechanisms is given, and the obstacle to technology scaling, by exponential leakage power increases, is exposed. Later, the paradigms of subthreshold design at several levels of hierarchy are presented. First, the characteristics and behavior of MOS transistors in the subthreshold region are described to comprehend subthreshold logic. In addition, the properties and evolution of subthreshold designs, including the state-of-the-art are presented. Then, the challenges of process variations and its impact on circuit behavior are addressed with an emphasis on research in the subthreshold regime. Lastly, considerations for construct a subthreshold optimized transistor are discussed.

#### 2.1 MOSFET Basic

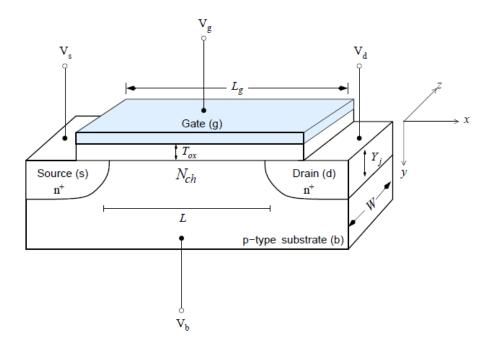

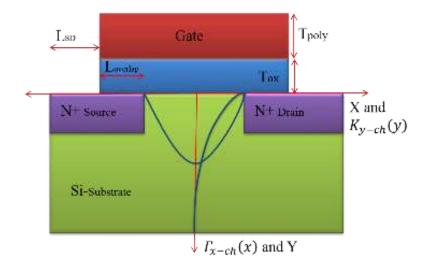

In this dissertation, the object of discussion, analysis, and optimization is the Metal-Oxide-Semiconductor Field-Effect (MOSFET) transistor. Such a transistor is the dominant device in integrated circuits such as processors and memories. The transistor's current is transported by electrons in n-channel devices (nMOS) or by holes in p-channel devices (pMOS). A basic nMOS channel structure is depicted in Figure 1, the substrate (bulk or body) is composed of p-type silicon in which two heavily doped n-type silicon regions, the drain and the source, are formed. Typically, the gate consists of heavily doped or silicide polysilicon, and is separated from the substrate by a thin silicon dioxide film, the gate oxide. The main device parameters are gate oxide insulator thickness ( $T_{ox}$ ), physical gate length ( $L_g$ ), channel doping concentration ( $N_{ch}$ ), source/drain junction depth ( $Y_j$ ), and transistor width (W).

Figure 1: Device structure of an n-channel MOSFET [37]

With shrinking technology sizes, energy efficiency has become a critical aspect of designing digital circuits. Traditionally, voltage scaling, a mechanism in which the supply voltage is varying and the threshold voltage is constant, has been an effective solution in meeting stringent energy requirements. However, voltage scaling does come at a cost of reduction in performance. The limits of voltage scaling, and therefore energy minimization, can be explored by operating a circuit at subthreshold [38]. In subthreshold circuits, the supply voltage is reduced well below the threshold voltage of a transistor. Due to the quadratic reduction in power with respect to the supply voltage, subthreshold circuits are classified as ultra-low power circuits. Specifically in application areas where performance can be sacrificed for low power, subthreshold circuits are an ideal fit. Some of the applications include devices such as hearing aids [39], wrist watches [40], radio frequency identification (RFID), sensor nodes and battery operated devices such as cellular phones. One of the major areas where subthreshold design can be used.

Subthreshold logic operates completely in the subthreshold region. The drain on and off currents are composed entirely of subthreshold leakage. Therefore, the logic assumes a power supply voltage that is less than the threshold voltage,  $V_{dd} < V_{th}$ . Since the leakage current is orders of magnitude lower than the drain strong inversion current and since the power supply is reduced, subthreshold logic dissipates ultra-low-power. Due to the small drive leakage current, the subthreshold logic only fits in designs, where the performance is considerably poor, and not the main concern.

Subthreshold logic shares important properties with traditional strong inversion CMOS logic.

a) High Noise Margins: The output swing goes from  $V_{dd}$  to ground (GND).

b) Low Output Impedance: In the steady state, a low impedance path to either  $V_{dd}$  or GND exists.

In addition, subthreshold logic has a number of advantages over its strong inversion counterpart.

- a) Lower Power Consumption: At the same frequency, subthreshold circuits consume orders of magnitude less power than strong inversion circuits [41].

- b) Higher Gain: The exponential relationship between Isub and Vgs leads to a high transconductance [42].

- c) Better Noise Margins:  $I_{sub}$  readily becomes independent of  $V_{ds}$ . This near ideal current source characteristic improves the noise margin of the logic gates [43].

A notable difference between strong inversion CMOS logic and subthreshold circuits is their robustness. Strong inversion logic will always work, given that the appropriate complementary Pull-Up Network (PUN) and Pull-Down Network (PDN) are implemented, even if the transistors are erroneously sized. In subthreshold circuits, transistor sizing impacts the functionality of CMOS circuits due to low supply voltages [44]. For example, consider a simple inverter, operating in the subthreshold region. Subthreshold  $I_{off}$  leakage always flow through a large pMOS device (which forms the PUN) to a certain extent where, a smaller nMOS (which forms the PDN) cannot pull down the voltage at the output to a full logic 0 level, and vice versa. This problem is augmented by the effect of the process variations.

# 2.2 Origin of Subthreshold Circuit Design

The MOS (Metal Oxide Semiconductor) transistor conducts current, majority carriers, through an inverted channel between the source and drain caused by a nominal voltage applied to

the gate. When a low voltage is applied to the gate, majority carriers in the substrate are repelled from the surface directly below the gate. Then, a depletion charge of immobile atoms forms a depletion region beneath the gate. The minority carriers in the depletion layer are made to move by diffusion and induce a drain current by applying a voltage between the drain and source in the MOS device. This weak inversion current was considered to be insignificantly small and ignored in digital circuit design until the recent decade. The early exploration of subthreshold design was focused on analog circuits such as amplitude detector, quartz ring oscillator, bandpass amplifier, and transconductance amplifier [45]. In the past years, subthreshold digital CMOS designs have been implemented for biomedical devices, FFT processors, and SRAMs [46-51]. This unintended discovery provides an opportunity for meeting the demands of extreme energy efficient systems.

# 2.3 Subthreshold Current

The region of operation of a transistor depends on the supply voltage at which it operates. As the supply voltage is reduced, the region of operation shifts from strong inversion to moderate inversion and finally to weak inversion. The strong inversion region, also known as the super-threshold regime, is characterized by large current drives and a supply voltage substantially above  $V_{th}$ , the threshold voltage of the transistor. The moderate inversion has lower current drives as compared to the super-threshold regime and an operating voltage near to the  $V_{th}$ . The weak inversion region, also known as the subthreshold regime, is characterized by small current drives and a supply voltage below  $V_{th}$ . The behavior of the transistor in the subthreshold and super-threshold regions is shown in equations (2.1) and (2.2) [38]

$$I_{on-sub} = \frac{W}{L_{eff}} \mu_{eff} C_{ox}(m-1) V_T^2 \exp\left(\frac{V_{gs} - V_{th}}{mV_T}\right) \left(1 - \exp\left(\frac{-V_{ds}}{V_T}\right)\right)$$

(2.1)

where *W* is the width of the transistor,  $L_{eff}$  is the effective length,  $\mu_{eff}$  is the effective mobility,  $C_{ox}$  is the oxide capacitance, *m* is the subthreshold slope factor and  $V_T = (KT/q)$ .

$$I_{on-super} = \frac{g_{msat}}{1 + R_s g_{msat}} (V_{dd} - V_{th} - V_{PO})$$

(2.2)

where  $g_{msat}$  is the saturation transconductance,  $R_s$  is the source resistance and  $V_{PO}$  is the pinch off voltage.

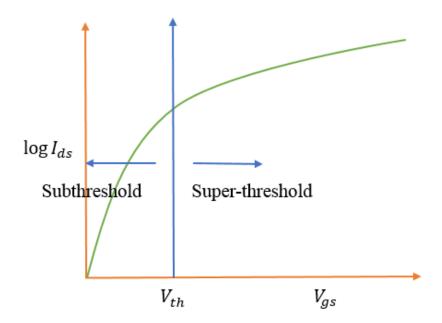

Figure 2: Transistor current characteristics.

The subthreshold and super-threshold regions of operation are highlighted in Figure 2. In the super-threshold region, the current is fairly linear in nature. The transistor current  $I_{on}$  in the subthreshold regime is exponentially dependent on  $V_{th}$  and supply voltage due to which power, delay and current matching between two transistors is also exponentially dependent on  $V_{th}$  and  $V_{dd}$ . This exponential dependence is a key challenge in designing circuits in subthreshold. Some of the parameters that are affected by this challenge are process variations, noise margins, soft errors and output voltage swings. Therefore, when designing energy optimal subthreshold circuits, these parameters play an important role. The current in the subthreshold region, also known as leakage current, is considered to be undesirable when operating the transistor in the super-threshold region. However, this current is quintessential as far as subthreshold operation is concerned. Leakage current is utilized by subthreshold circuits as their conduction current.

## 2.4 Power, Energy and Frequency

The total power in a CMOS circuit is given by equation (2.3)

$$P_{Total} = P_{dynamic} + P_{static} = \frac{1}{2} C_L V_{dd}^2 \alpha f + I_{sc} V_{dd} + I_{static} V_{dd}$$

(2.3)

where  $C_L$  is the load capacitance, f is the frequency of operation,  $I_{SC}$  is the short circuit current and  $\alpha$  is the activity factor. As can be seen from Equation (2.3) the total power consists of two major components: dynamic power and leakage power. Both these components reduce in magnitude as the supply voltage reduces.

The dynamic power consumption is due to the charging and discharging of the load capacitance and the short circuit current. A short circuit current flows when the pull up and pull down networks in a CMOS circuit are simultaneously on and a direct path exists between the supply line and ground. Dynamic power is directly proportional to the square of the supply voltage. Therefore, dynamic power reduces in a quadratic manner when the supply voltage is reduced. Leakage power is dependent on the leakage current flowing in the CMOS circuit.

At super-threshold, the charging (or discharging) current is greater than the leakage current. Hence, dynamic power dominates over leakage power in super-threshold. At subthreshold, supply voltage is lower than the threshold voltage of the transistor. Due to its quadratic relation with supply voltage, dynamic power reduces drastically in subthreshold. Also, leakage current is regarded as the conduction current in subthreshold. Therefore, leakage power dominates than dynamic power in the subthreshold region of operation.

Energy is one of the important design metrics in digital circuits. The energy estimation in these circuits is given by Equation (2.4)

$$E_{Total} = E_{dynamic} + E_{static} = \frac{1}{2} C_L V_{dd}^2 \alpha + I_{static} V_{dd} t_p$$

(2.4)

where  $C_L$  is the load capacitance,  $t_p$  is the circuit delay and  $\alpha$  is the activity factor. The important observation in Equation (2.4) is the dependence of leakage energy on delay  $t_p$ . Since  $t_p$  is high in subthreshold, the leakage energy is greater than the dynamic energy. As the supply voltage is increased, the delay and hence the leakage energy, reduces. Therefore, at super-threshold the dynamic energy is the more dominant of the two. Short circuit energy is negligible at subthreshold and can be ignored [38].

#### 2.5 Minimum Energy Operation

Since energy minimization is the enabling factor for subthreshold design, identifying the operating voltage range for the optimal energy forms the design basis. Two commonly used terms in subthreshold design are  $V_{min}$ , the voltage at which the energy of the circuit is minimum and  $V_{dd,limit}$ , the lowest supply voltage at which the circuit can be operated. In most cases the  $V_{min}$  is greater than  $V_{dd,limit}$ .  $V_{min}$  denotes the ideal supply voltage at which the circuit should be operated. Stacking of transistors raises the  $V_{dd,limit}$  of a circuit well above that of a simple inverter. The location of the energy minimum of any circuit is a compromise between the dynamic and leakage energies. The point of intersection of the dynamic and leakage energy curves is defined as the

minimum energy point of the circuit. The activity factor,  $\alpha$ ,  $V_{th}$ ,  $L_{eff}$ , sub- $V_{th}$  slope and  $I_{on}$  are interdependent and should be considered for determining the minimum energy point of any design.

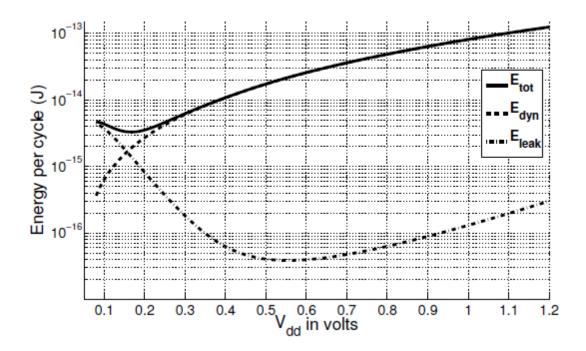

The minimum energy operation point  $(E_{min})$  for a digital circuit means that the circuit consumes less Energy per cycle than any other point in the parameter space. Among the different parameters, power supply voltage  $(V_{dd})$  and device threshold voltage  $(V_{th})$  are mainly considered for the minimum energy point. The energy and delay contours for a ring oscillator circuit with varying  $V_{dd}$  and  $V_{th}$  show that  $E_{min}$  occurs in the subthreshold region [52]. For given  $V_{dd}$  and  $V_{th}$ , the minimum energy point for a circuit is determined by the relationship between energy and latency. As  $V_{dd}$  scales down, dynamic energy is quadratically reduced, while the delay of a circuit exponentially increases at supply voltages below  $V_{th}$ . The increased delay induces an exponential increase of leakage energy. The minimum energy point occurs where the magnitudes of dynamic energy and leakage energy are equal. The switching activity of a circuit affects its minimum energy point. When the dynamic energy is decreased by reducing switching events, the leakage energy remains constant with switching activity. Thus, the leakage energy contributes substantially more to the total energy of a circuit. In that case, the minimum energy point occurs at higher supply voltages compared to higher activity circuits. Adversely, higher switching circuits move the minimum energy point to lower supply voltages to suppress the dynamic energy. There are two representative minimum energy models in the literature. First, when the operating frequency and technology of a subthreshold circuit are given, the minimum energy model is derived to obtain the closed forms for optimal  $V_{dd}$  and  $V_{th}$ , respectively [53]. This model uses fitting parameters normalized to a characteristic inverter for the given technology, where the minimum sized inverter, for simplicity, is a good choice. All other gates are normalized with respect to the inverter.

Figure 3: Energy per cycle for an 8-bit ripple carry adder through HSPICE [54] simulation in PTM 90 nm CMOS,  $E_{min} = 3.29 \, fJ$  at  $V_{dd} = 0.17 \, V (V_{th,pmos} = -0.21 \, V \text{ and } V_{th,nmos} = 0.29 \, V)$ .

2.6 Leakage Mechanism

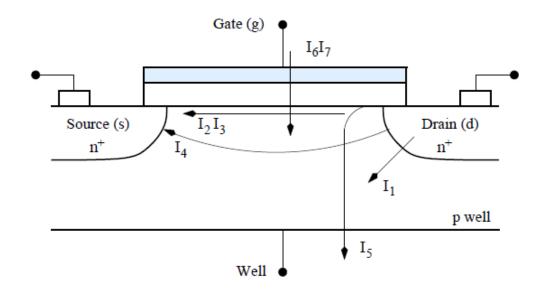

Static power is dissipated during the idle time, that is, when no transition or switching activity occurs. As the transistor threshold voltage, channel length, and gate oxide thickness are reduced in deep submicron (DSM) regimes, the static power dissipation becomes a challenging obstacle for the development of modern ICs. Consequently, the identification of the different leakage components is pivotal for the analysis and design of low-power applications. Figure 4 [55] denotes the seven transistor intrinsic leakage mechanisms in short channel devices.

Figure 4: Short-channel transistor mechanisms:  $(I_1)$ , reverse biased p-n junction;  $(I_2)$ , subthreshold or weak inversion;  $(I_3)$ , drain-induced barrier lowering;  $(I_4)$ , punch-through;  $(I_5)$ , gate-induced drain leakage;  $(I_6)$ , gate oxide tunneling; and  $(I_7)$ , hot-carrier injection.

$I_1$  is the reverse bias p-n junction leakage. Drain-to-substrate and source-to- substrate junctions are normally reverse biased, occasioning a p-n junction leakage current. It has two components: i) the minority carrier diffusion/drift near the edge of the depletion region, and ii) the electron-hole pair generation in the depletion region of the reverse biased junction. If both the n-and p-regions are heavily doped, which is the case of an advanced MOS, to mitigate short-channel effects, Band-to- Band Tunneling (BTBT) can also be present. The effect dominates the p-n junction leakage component. IBTBT occurs when a high electric field (>  $10^6$ V/cm), across the reverse biased junction, leads to electrons from the valence band of the p-side to migrate to the conduction band of the n-side, as denoted in Figure 5 [56].

$I_2$  is the weak inversion or subthreshold conduction current between the source and drain. It occurs when the gate voltage is below the threshold voltage ( $V_g < V_{th}$ ). Recently, this current dominates device off-state leakage mechanisms due to the low  $V_{th}$  values of transistors [57]. This weak inversion current is the drive current in the subthreshold regime. Consequently, this leakage component is looked at the next section.

Figure 5: Band-to-band tunneling in an nMOS: valence band electron tunneling from the valence band of the p-side to the conduction band of the n-side; the total voltage drop across the junction, the reverse bias voltage and the built-in voltage is greater than the energy-band gap,  $(V_{app} + \psi_{bi})$

# $E_g$ ).

$I_3$  is the Drain-Induced Barrier Lowering (DIBL). It occurs when a high drain voltage is applied to a short-channel device, and thus, the potential (voltage) barrier (to the electrons for an nMOS) at the surface between the source and drain is lowered. For example, consider the potential energy barrier at the surface between the drain and source, depicted in Figure 6 [58]. At the off condition, this potential prevents the flow of electrons between the terminals. However, as the drain voltage is increased, the potential barrier is reduced in short-channel devices. In this way, the higher the drain voltage applied to a short channel device, the lower the barrier height is, and thus, the source injects carriers into the channel surface without the control gate voltage playing a role [58].

$I_4$  is the channel punch-through. At even higher drain voltages and channel length reductions, the drain and source depletion regions approach each other and eventually merge in the deep substrate. As a result, the gate totally loses control over the channel, and the flow of the drain current becomes independent of the control voltage [58].

$I_5$  represents the Gate-Induced Drain Leakage (GIDL). It is the result of the influence of high electric fields on the gate-drain overlap region. Consequently, the depletion width of the drain to substrate p-n junction is thinned out [58]. Carriers are generated in the substrate and drain from the direct band-to-band tunneling, trap-assisted tunneling, or a combination of thermal emission and tunneling [57]. Oxide thickness ( $T_{ox}$ ) reductions and higher supply voltages lead to a higher potential between the gate and the drain, which in turn, enhances the electric field dependent GIDL.

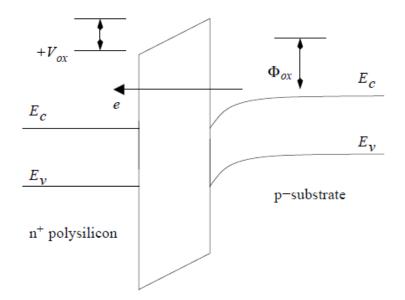

$I_6$  refers to oxide leakage tunneling. The continuous reduction of the oxide thickness leads to an increase in the field across Tox. The high electric field results in the tunneling of electrons from the inverted substrate-to-gate and also from the gate-to-substrate through  $T_{ox}$ . This current flow is known as oxide leakage tunneling. The direct tunneling of electrons is signified in Figure 7.

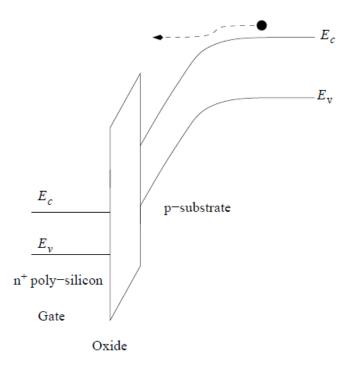

$I_7$  is the gate current due to hot carrier injection. If a region with a high electric field is located near the Si-SiO2 interface (as it occurs in the pinch-off condition), some of the electrons or holes can gain sufficient energy from the field to cross the interface potential barrier and enter the oxide layer. This phenomenon, called a hot-carrier injection, is represented in Figure 7 [58].

Figure 6: Tunneling of electrons: direct tunneling occurs when the potential drop across the gate oxide is lower than the barrier height of the tunneling electron ( $V_{ox} < \phi_{ox}$ ).

Figure 7: Injection of hot electrons from the substrate to the oxide.

#### 2.7 Conclusion

This chapter describes some issues in reducing power consumption in scaled devices. A MOS's intrinsic leakage mechanisms are explained. The three more contributive leakage components in DSM technologies are subthreshold, oxide tunneling, and reverse bias p-n junction BTBT. Subthreshold leakage is the drive current in the subthreshold regime. In addition, the characteristics of MOS transistors in the subthreshold region are examined with respect to the strong inversion regime, including current flow mechanism, intrinsic capacitances, and the exponential relation between the gate voltage and drain current. Then, the paradigms of subthreshold logic are outlined. Subthreshold logic and strong inversion CMOS logic share several properties such as high noise margins, and low output impedance with improved features in power consumption and gain. Beginning with the analog field, it was not until the late 1990s that subthreshold circuits attracted attention in the digital domain; since then, several subthreshold systems have been implemented with standard DSM technologies. Later, process variations and their impact on circuit behavior are presented. The three essential parameters to account for variations are: oxide thickness, channel length, and channel doping concentration. Variability is one of the most challenging obstacles in recent technologies, and is accentuated in subthreshold designs. Finally, an optimized transistor structure for subthreshold operation is discussed, as a promising construction block in terms of simplified fabrication processes, faster operation, and lower power consumption.

#### CHAPTER 3

# IMPLANTATION PROFILES

Devices for super-threshold circuit usually employ halo and retrograde doping profiles in the channel to eliminate many unwanted effects. Devices for subthreshold circuits do not require halo and retrograde doping profiles. This will reduce the number of steps in the fabrication process, the parasitic capacitance, and the substrate noise dramatically. This chapter introduces four new doping profiles for devices to be used in the ultra-low-power subthreshold circuits. The proposed scheme addresses doping variations along all the dimensions (length, width and depth) of the device. Therefore, the approaches are three dimensional (3D) in nature. This new doping scheme proposes to employ Gaussian distribution of doping concentration along the length of the channel with highest concentration at the middle of the channel. The doping concentration across the depth of the device from the channel region towards the bulk of the device can follow one of the following four distributions: (a) exponentially decreasing, (b) Gaussian, (c) low to high, and (d) uniform doping. The proposed doping scheme keeps the doping concentration along the width of the device uniform. Therefore, under this scheme we achieve four sets of new 3D doping profiles. Results show that a device optimized with any of the four proposed doping profiles would offer higher ON current in the subthreshold region than a device with the conventional halo and retrograde doping profiles. Among the four 3D doping profiles for the subthreshold device some

has better ON current than the others. Based on specific requirements one of these four doping profiles can be adopted for different ultra-low-power applications.

3.1 Introduction

Device, circuit, architecture, and system level requirements for ultra-low-power subthreshold circuits (that would be operated below the threshold voltage) are often different from the conventional super-threshold circuits (that are operated above the threshold voltage). Also, the requirements would be different for digital, analog, and mixed signal applications [1], [2]. One of the important aspects of the design is the doping profile along the length, width, and depth of a transistor. Deeply scaled analog CMOS device design for system-on-chip (SOC) applications is very challenging because of the conflicting requirements of the analog and digital circuits [3], [4]. Also, aggressive scaling of power supply is preferred in digital logic circuits, but this leads to degraded signal range and lower design margins for analog circuits [5]. It is observed that with lateral asymmetric channel (LAC) doping the total gate capacitance of a transistor is reduced by almost 10% in the saturation region at 100nm technology node compared to the conventional MOSFETS [6], [7]. Transistor capacitances have significant influences on its RF performance. Furthermore, in the subthreshold region, the transistor input capacitance is less than that of strong inversion operation. The transistor input capacitance in subthreshold is a combination of intrinsic capacitance, depletion capacitance, parasitic capacitance and fringing capacitances of a transistor. In contrast, the input capacitance in strong inversion operation is dominated by the oxide capacitance. Due to the smaller capacitance and lower supply voltage (maximum limit is the threshold voltage of the transistor) digital subthreshold circuits consume significantly less power than their strong inversion counterpart at a particular frequency of operation. In [8], the electron velocity overshoot phenomenon in the inversion layer is experimentally investigated for a novel

thin film silicon-on-insulator (SOI) test device with channel lengths down to 0.08µm. The test SOI structure used LAC doping profile [9]. The high field drift velocity of the inversion carriers is measured. Simulation results show that very uniform carrier density and drift velocity can be achieved with LAC profile in SOI device.

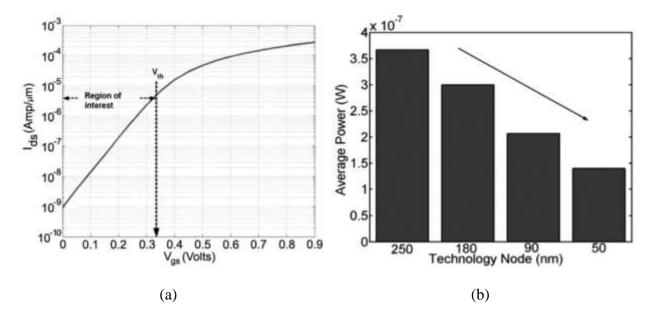

Short-channel devices are usually optimized for super-threshold circuits to ensure higher mobility, lower drain-induced barrier lowering (DIBL), reduced leakage, and minimal threshold voltage roll-off. However, a transistor optimized for super-threshold circuit may not be optimal for the subthreshold region where effects like DIBL, threshold voltage roll-off, and electron/hole tunneling are much less significant [10]. As a consequence, high doping, traditionally used in the super-threshold device to overcome the short-channel effect (SCE) will not be critical for subthreshold operation [11]. In super-threshold device, the main functions of halo and retrograde doping [12], [13] are to reduce DIBL, prevent body punch through, and control the threshold voltage of the device independent of its subthreshold slope. Since DIBL, body punch through and threshold voltage variation are not severe in the subthreshold device due to lower supply voltage, the halo and retrograde doping is not required for such design. High to low doping profile has been proposed for subthreshold operation in [10]. For subthreshold circuit operation lower subthreshold swing and internal device capacitances are critical. However, existing doping profiles do not offer any means to address these critical needs. Also the operating current of subthreshold device is the subthreshold leakage current of the conventional device. Because of the low voltage and leakage current based operation subthreshold circuits will not operate at very high frequency. Figure 8(a) shows the region of operation of the subthreshold logic circuits. Power consumption is becoming a critical issue in super-threshold device. Technology scaling results in reduction of the total power consumption in super-threshold domain. Figure 8(b) shows how technology scaling can reduce the

total average power consumption of an inverter (driving an identical inverter), all operating at the same frequency [10]. Dramatic reduction of average power consumption is also possible in the subthreshold circuits with technology scaling.

Figure 8: (a) Subthreshold logic region of operation and (b) average power consumption of different technology nodes [10].

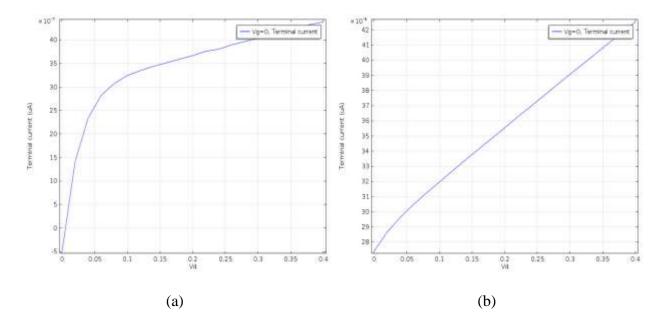

We are currently exploring a set of new doping profiles for devices to be used in the subthreshold circuits. Here, we have outlined the general principle of this new doping scheme. We have presented the outline of four possible combinations of doping profiles along the three dimensions of the device for the subthreshold circuits. This four new doping profile is characterized by Gaussian distribution along the X-direction (along the channel length) and exponentially decreasing, Gaussian, low-to-high or uniform doping concentration along the Y-direction (towards the depth) of the device.

Figure 9: (a) X-direction Gaussian and Y-direction Gaussian doping, (b) X-direction Gaussian and Y-direction Exponentially decreasing doping (c) X-direction Gaussian and Y-direction uniform doping, and (d) X-direction Gaussian and Y-direction low-to-high doping.

## 3.2 Proposed Doping Scheme for Subthreshold Device

The proposed doping scheme would bring changes in doping properties along the length (X direction) and depth (Y direction) of the device and keep the doping concentration along the width constant. The doping profile in X direction is kept somewhat constant in most of the previous designs and only the Y direction doping profiles have been varied. We propose a three-dimensional doping scheme, where doping profiles would be varied in both directions. We propose to adopt Gaussian distribution of doping density in the X direction and one of the four different doping

profiles in the Y directions for subthreshold devices. Based on the proposal we would get four possible combinations of two-dimensional doping profiles illustrated in Figure 9. Superposition of two 2D doping profiles in X and Y directions would lead to a 3D doping profile for the device under each combination. In this chapter we will focus on the following four combinations of 3D doping profiles: (i) Gaussian distribution of doping profiles in both X and Y direction, (ii) Gaussian distribution in X and exponentially decreasing in Y direction, (iii) Gaussian distribution in X and low-to-high distribution in Y direction, and (iv) Gaussian distribution in X and uniform distribution in Y direction. For all four combinations we assume the doping density along the width of the device is uniform. It is anticipated that each combination will have certain prospects and constrains for different applications of subthreshold circuits. In this project, we plan to show that for a particular technology generation, lower power and higher performance can be achieved in the subthreshold region by redesigning the devices specifically for subthreshold operation.

Conventional super-threshold devices use combination of halo or retrograde doping along the channel and uniform or high-to-low doping along the depth of the channel. In this dissertation we have applied the proposed four doping profiles in the super-threshold device as well to perform a comparative analysis of the performance both in the super- and sub-threshold devices with the proposed doping scheme. Each of these four doping combinations opens the door for a new class of subthreshold devices optimized for specific set of ultra-low-power applications in analog, digital and mixed signal domains. Our future work will present detail comparative analysis of various performance parameters of the doping profiles of Figure 9a to Figure 9d in a more comprehensive form along with the validation using device level simulation tools like TCAD and test data if possible. Here we concentrate on the analytical proof and qualitative analysis of proposed doping.

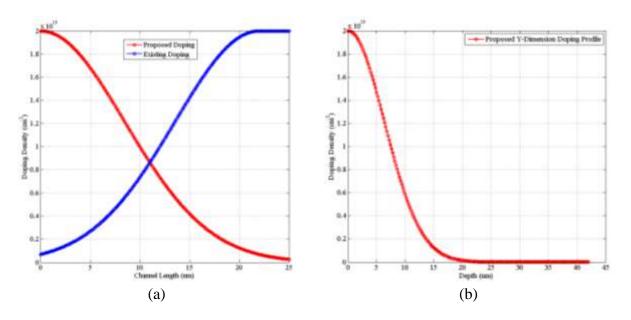

Figure 10: (a) Doping distribution along X-dimension – from the middle of the channel to drain (source) end and (b) all four doping distribution along Y-direction from the top surface of the channel towards the bottom surface of the substrate. In (a) red is for the proposed doping profile for subthreshold device and blue is of conventional device.

#### 3.3 Mathematical Modelling and Analysis

A technique based on the subthreshold current–voltage (I-V) characteristics to extract 2-D doping profiles is proposed in [14]. Here we propose a new doping profile for subthreshold device operation using similar approach. We modeled MOSFET subthreshold current based on the proposed doping profile. The formulation of the model is shown for NMOS transistor and can be easily applied to PMOS transistor. Device structure with Gaussian shaped channel doping along the X dimension (length of the channel) has been considered as shown in Figure 10a. In conventional super-threshold device the doping concentration at the middle of the device is the lowest and at the source (drain) ends it is the highest (blue line) and it will lead to form an inverse Gaussian shape dopant distribution. In our proposed scheme for subthreshold device (red line), the middle of the channel has highest doping concentration and the drain (source) end has the lowest.

The variation of doping concentration from the middle towards the both ends is of Gaussian shape under our proposed scheme. And the proposed doping profile (red line) is exactly the inverse of the existing doping profile (blue line). The reason behind selecting the inverse model of X dimension doping profile has been discussed earlier. Across the vertical middle line of the device the doping is symmetrical. In this dissertation, for the Y direction (along the depth of the device) we consider the variation of doping concentration as depicted in Figure 10b, where the four different Y dimension doping density from the channel surface towards the body of the device are shown. The 2D Gaussian doping profile in the channel can be represented as in (3.1) [14].

$$N_{cheff}(x, y) = A_p \Gamma_{x-ch}(x) K_{y-ch}(y) + N_{sub}$$

(3.1)

$$\Gamma_{x-ch}(x) = exp^{\left(\frac{-(x)^2}{\sigma l_{x-ch}^2}\right)}, \qquad -\frac{L_{eff}}{2} \le x \le +\frac{L_{eff}}{2}$$

(3.2)

$$\Gamma_{x-ch}(x) = exp^{\left(\frac{-(x-\beta_{ch})^2}{\sigma 1_{x-ch}^2}\right)}, \qquad 0 \le x \le \beta_{ch}$$

(3.3)

Equations (3.2) and (3.3) represents X dimension doping distribution for subthreshold and super-threshold device operation. For subthreshold device, the X dimension has high doping at the center of the channel and falls off towards the source or drain junction as in (3.2). For super-threshold the X dimension has low doping at the center of the channel and increase towards the source or drain junction as depicted in (3.3).  $L_{eff}$  is the effective length of the channel and  $\beta_{ch}$  controls the position of the effective doping along the channel. Here (3.4) illustrates the Gaussian Y dimension (from the channel surface towards the body) doping profile for the subthreshold device. Gaussian doping profile along Y-dimension is realized by lower doping in the channel area followed by exponentially increase towards the bulk and reaches to a peak value at  $y = \alpha_{ch}$ . After peak the doping will exponentially decrease and reaches to steady state at  $y \leq 2\alpha_{ch}$ . Parameter

$\alpha_{ch}$  controls the position and  $\sigma 1_{y-ch}$  controls the variance of gaussian doping profile along ydimension. Since the doping distribution is getting low inside lower end of the bulk that will lead to reduce the capacitance of the bottom junction and reduces substrate noise effects and parasitic latch-up problems. And strong doping between channel area and lower end of the bulk will help to form the channel very fast at lower threshold voltage.

$$K_{y-ch}(y) = exp^{\left(\frac{-(y-\alpha_{ch})^2}{\sigma 1_{y-ch}^2}\right)}, \quad 0 \le y \le 2\alpha_{ch}$$

(3.4)

Equation (3.5) illustrates the exponentially decreasing Y dimension (from the channel surface towards the body) doping profile for the subthreshold device.

$$K_{y-ch}(y) = exp^{\left(\frac{-(y-\alpha_{ch})^2}{\sigma 1_{y-ch}^2}\right)}, \alpha_{ch} = 0, 0 \le y \le d$$

(3.5)

Here *d* is the depth of the device (measured from the channel surface to the bottom surface of the substrate). The parameter  $\alpha_{ch}$  controls the position and  $\sigma 1_{y-ch}$  controls the variance of exponentially decreasing doping profile along Y-direction. Here  $\alpha_{ch} = 0$  means that the variation of doping concentration starts from the surface of the channel. Since the doping at lower end is low this will also lead to the reduced capacitance at the bottom junction, lower substrate noise and lower parasitic latch-up problems.

$$K_{y-ch}(y) = exp^{\left(\frac{-(y-\alpha_{ch})^2}{\sigma 1_{y-ch}^2}\right)}, \sigma 1_{y-ch} = c, 0 \le y \le d_1$$

3.6(a)

$$= exp^{\left(\frac{-(y-\alpha_{ch})^{2}}{\sigma 1_{y-ch}^{2}}\right)}, \ \sigma 1_{y-ch} = \infty, \ d_{1} \le y \le d_{2}$$

3.6(b)