Intelligent Scheduling and Memory Management Techniques

for Modern GPU Architectures

by

Shin-Ying Lee

A Dissertation Presented in Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy

Approved July 2017 by the Graduate Supervisory Committee:

Carole-Jean Wu, Chair Chaitali Chakrabarti Fengbo Ren Aviral Shrivastava

ARIZONA STATE UNIVERSITY

August 2017

02017Shin-Ying Lee

All Rights Reserved

#### ABSTRACT

With the massive multithreading execution feature, graphics processing units (GPUs) have been widely deployed to accelerate general-purpose parallel workloads (GPGPUs). However, using GPUs to accelerate computation does not always gain good performance improvement. This is mainly due to three inefficiencies in modern GPU and system architectures.

First, not all parallel threads have a uniform amount of workload to fully utilize GPU's computation ability, leading to a sub-optimal performance problem, called warp criticality. To mitigate the degree of warp criticality, I propose a Criticality-Aware Warp Acceleration mechanism, called CAWA. CAWA predicts and accelerates the critical warp execution by allocating larger execution time slices and additional cache resources to the critical warp. The evaluation result shows that with CAWA, GPUs can achieve an average of 1.23x speedup.

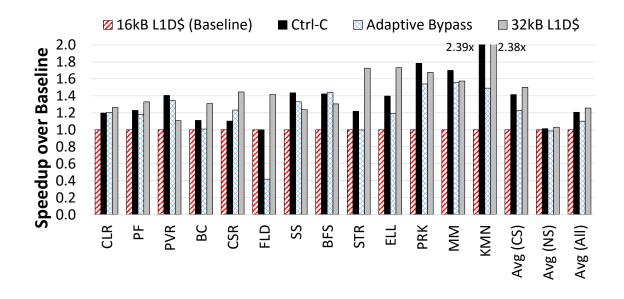

Second, the shared cache storage in GPUs is often insufficient to accommodate demands of the large number of concurrent threads. As a result, cache thrashing is commonly experienced in GPU's cache memories, particularly in the L1 data caches. To alleviate the cache contention and thrashing problem, I develop an instructionaware Control Loop Based Adaptive Bypassing algorithm, called Ctrl-C. Ctrl-C learns the cache reuse behavior and bypasses a portion of memory requests with the help of feedback control loops. The evaluation result shows that Ctrl-C can effectively improve cache utilization in GPUs and achieve an average of 1.42x speedup for cache sensitive GPGPU workloads.

Finally, GPU workloads and the co-located processes running on the host chip multiprocessor (CMP) in a heterogeneous system setup can contend for memory resources in multiple levels, resulting in significant performance degradation. To maximize the system throughput and balance the performance degradation of all co-located applications, I design a scalable performance degradation predictor specifically for heterogeneous systems, called HeteroPDP. HeteroPDP predicts the application execution time and schedules OpenCL workloads to run on different devices based on the optimization goal. The evaluation result shows HeteroPDP can improve the system fairness from 24% to 65% when an OpenCL application is co-located with other processes, and gain an additional 50% speedup compared with always offloading the OpenCL workload to GPUs.

In summary, this dissertation aims to provide insights for the future microarchitecture and system architecture designs by identifying, analyzing, and addressing three critical performance problems in modern GPUs.

#### ACKNOWLEDGMENTS

Exploring the darkest world to discover new opportunities, doing research is one of the toughest adventures. It is a lonely, challenging, stumbling, and endless journey. Yet, it is also the most exciting and joyful achievement when we see a beam of light in the deep darkness. I am truly glad I have had a chance to enjoy this great moment, watching a warm ray of light shining the ground.

I am grateful to my research advisor, Dr. Carole-Jean Wu. With her passion in research, Carole opened a door for me to this amazing research space. With her patience in teaching, Carole guided me overcoming all the challenges I had experienced. This thesis would not have been possible without her enthusiasm for mentoring students.

I would like to thank Dr. Chaitali Chakrabarti, Dr. Fengbo Ren, and Dr. Aviral Shrivastava for serving on my dissertation committee and helping me improve my research work.

I would like to thank my writing instructor, Gregory Fields, and all tutors from the ASU writing center for reviewing and polishing my research papers as well as my PhD dissertation.

I would like to thank my colleagues at AMD and Apple, Cyril de Chanterac, Dr. Jin Chen, Dr. Ying Chen, Michael Christman, Michael Chung, Dr. Anas Lasram, Dr. Timour Paltashev, Dhruv Saksena, Dr. Dana Schaa, Dr. Churayev Sergey, Dr. Stephen Somogyi, and Charles Tan, for broadening my vision in industry and inspiring me to find out new research ideas.

I would like to thank all my labmates and classmates in ASU, Akhil, Amrit, Benjamin, Chia-Wen, Davesh, Dhinakaran, Digant, Duo, Hsing-Min, Jhe-Yu, Jian, Jeevan, Ke, Moslem, Nishant, Shail, Vignesh, and Yooseong for assisting me in setting up my experiment infrastructure and reviewing my code. I would like to thank Yen-Shao and Chung-Ying for preparing a geat apartment for me before I arrived in Arizona.

I would like to thank Chi-Han and Yu-Ying for generously providing me a cozy home in a foreign country.

Most importantly, I would like to thank for my parents and my old brother, Yu-Rey, for supporting, encouraging, and motivating me finishing this adventure.

Without all your kindly encouragement, unlimited support, valuable suggestions, as well as rigorous criticisms, I would never be able to arrive at a destination of such a long journey. After four and a half years, now, it is the time to share this wonderful moment with all of you in my life to sincerely express my best gratitude.

|      |      | Pa                                                              | ıge |

|------|------|-----------------------------------------------------------------|-----|

| LIST | OF T | ABLES                                                           | ix  |

| LIST | OF F | IGURES                                                          | х   |

| CHAI | PTER |                                                                 |     |

| 1    | INT  | RODUCTION                                                       | 1   |

|      | 1.1  | GPGPU Architecture and Computation                              | 2   |

|      | 1.2  | The Inefficiencies of Current GPGPU and Accelerator-rich System |     |

|      |      | Designs                                                         | 4   |

|      |      | 1.2.1 Execution Time Disparity and Warp Criticality             | 5   |

|      |      | 1.2.2 Resource Contention and Cache Thrashing                   | 6   |

|      |      | 1.2.3 Data Movement Overheads and Memory Interference           | 7   |

|      | 1.3  | Contributions                                                   | 9   |

| 2    | REL  | ATED WORK                                                       | 11  |

|      | 2.1  | Warp Criticality                                                | 11  |

|      | 2.2  | Cache Thrashing Problem and Cache Management                    | 14  |

|      | 2.3  | Memory Interference in Heterogeneous Systems                    | 18  |

| 3    | WAI  | RP CRITICALITY AND CRITICALITY-AWARE WARP SCHEDUL-              |     |

|      | ING  |                                                                 | 23  |

|      | 3.1  | The Baseline GPGPU Architecture and its Computation Model       | 23  |

|      | 3.2  | GPU Latency Hiding Ability                                      | 25  |

|      |      | 3.2.1 Factors Stalling Warp Execution                           | 25  |

|      |      | 3.2.2 Latency Attribution Algorithm                             | 27  |

|      |      | 3.2.3 Characterization Methodology                              | 31  |

|      |      | 3.2.4 Latency Characterization                                  | 33  |

|      | 3.3  | Warp Criticality                                                | 35  |

# TABLE OF CONTENTS

|   | 3.4 | Warp   | Scheduler Design Exploration for Critical Warp Acceleration .  | 39 |

|---|-----|--------|----------------------------------------------------------------|----|

|   |     | 3.4.1  | CAWS Algorithms                                                | 39 |

|   |     | 3.4.2  | CAWS Implementation                                            | 40 |

|   | 3.5 | Evalu  | ation and Analysis                                             | 42 |

|   | 3.6 | Chapt  | er Summary                                                     | 44 |

| 4 | CO  | ORDIN  | ATED CRITICALITY-AWARE WARP ACCELERATION                       | 48 |

|   | 4.1 | Source | e of Execution Time Disparity                                  | 48 |

|   |     | 4.1.1  | Workload Imbalance                                             | 49 |

|   |     | 4.1.2  | Diverging Branch Behavior                                      | 51 |

|   |     | 4.1.3  | Contention in the Memory Subsystem                             | 52 |

|   |     | 4.1.4  | Latency Introduced by the Warp Scheduler                       | 54 |

|   | 4.2 | Coord  | linated Criticality-Aware Warp Acceleration Design             | 55 |

|   |     | 4.2.1  | Critical Warp Identification with Criticality Prediction Logic | 56 |

|   |     | 4.2.2  | greedy Criticality-Aware Warp Scheduler                        | 59 |

|   |     | 4.2.3  | Criticality-Aware Cache Prioritization                         | 60 |

|   | 4.3 | Evalu  | ation and Analysis                                             | 65 |

|   |     | 4.3.1  | Experimental Environment and Methodology                       | 65 |

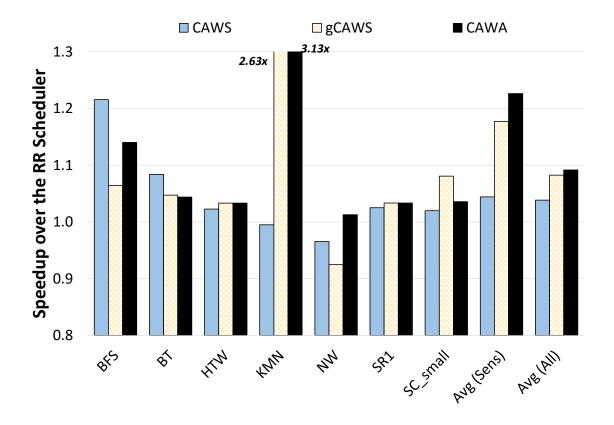

|   |     | 4.3.2  | Performance Overview                                           | 66 |

|   |     | 4.3.3  | Performance Analysis for CPL                                   | 69 |

|   |     | 4.3.4  | Performance Analysis for gCAWS                                 | 70 |

|   |     | 4.3.5  | Performance Analysis for CACP                                  | 72 |

|   | 4.4 | Chapt  | er Summary                                                     | 75 |

| 5 | INS | TRUC   | ΓΙΟΝ-AWARE CONTROL LOOP BASED ADAPTIVE CACHE                   | ē  |

|   | BYI | PASSIN | IG                                                             | 76 |

Page

|   | 5.1 | GPU (           | Cache Access Behavior Characterization                        | 76  |

|---|-----|-----------------|---------------------------------------------------------------|-----|

|   | 5.2 | Contro          | ol-Loop Based Adaptive Cache Bypassing                        | 83  |

|   |     | 5.2.1           | Design Overview of Ctrl-C                                     | 83  |

|   |     | 5.2.2           | Cache Line Reuse Prediction and iReuse Table                  | 84  |

|   |     | 5.2.3           | Feedback Control Loop                                         | 85  |

|   |     | 5.2.4           | The Ctrl-C Cache Bypassing Algorithm                          | 87  |

|   | 5.3 | Evalua          | ation and Analysis                                            | 88  |

|   |     | 5.3.1           | Experimental Environment and Methodology                      | 88  |

|   |     | 5.3.2           | Performance Improvement                                       | 90  |

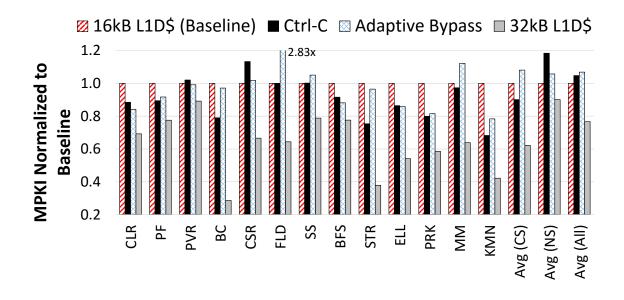

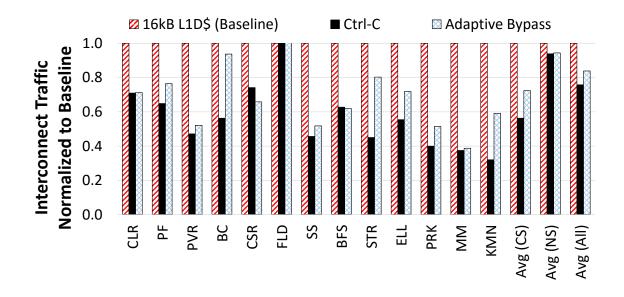

|   |     | 5.3.3           | MPKI and Interconnect Traffic Reduction                       | 91  |

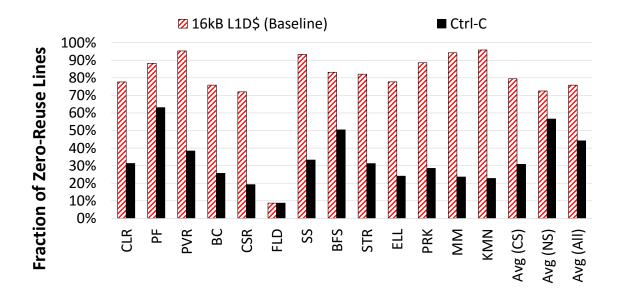

|   |     | 5.3.4           | Fraction of Zero-reuse Lines                                  | 92  |

|   |     | 5.3.5           | Hardware Implementation Overhead                              | 93  |

|   | 5.4 | Chapter Summary |                                                               |     |

| 6 | PER | FORM            | ANCE CHARACTERIZATION AND PREDICTION FOR                      |     |

|   | НЕТ | TEROG           | ENEOUS COMPUTER SYSTEMS WITH GPUS                             | 97  |

|   | 6.1 | Hetero          | ogeneous Systems and the OpenCL Framework                     | 97  |

|   | 6.2 | Metho           | dology1                                                       | .00 |

|   |     | 6.2.1           | Experiment Infrastructure and Configurations                  | .00 |

|   |     | 6.2.2           | Workload Construction1                                        | .01 |

|   | 6.3 | Motiva          | ation for an Intelligent Execution Target Scheduler1          | .01 |

|   |     | 6.3.1           | Performance Characterization1                                 | .02 |

|   |     | 6.3.2           | Optimal Execution Target in the Presence of Memory In-        |     |

|   |     |                 | terference1                                                   | .03 |

|   |     | 6.3.3           | Performance Degradation with Different Co-location Scenarios1 | .05 |

|          |      | 6.3.4   | Performance Degradation with Different Scheduling Priorities106   |

|----------|------|---------|-------------------------------------------------------------------|

|          | 6.4  | Perform | mance Degradation Predictor for Heterogeneous Systems108          |

|          |      | 6.4.1   | The HeteroPDP Prediction Scheme Overview                          |

|          |      | 6.4.2   | OpenCL Kernel Execution Time Prediction for <i>alone</i> 110      |

|          |      | 6.4.3   | OpenCL Kernel Execution Time Prediction for <i>co-located</i> 111 |

|          |      | 6.4.4   | Performance Model Training for OpenCL Kernels111                  |

|          |      | 6.4.5   | Performance Degradation Prediction for Native CPU Ap-             |

|          |      |         | plications                                                        |

|          | 6.5  | Evalua  | tion and Analysis113                                              |

|          |      | 6.5.1   | Execution Time and Execution Target Prediction Accuracy . 113     |

|          |      | 6.5.2   | Evaluation for System Performance                                 |

|          |      | 6.5.3   | HeteroPDP with Varying Scheduling Priorities                      |

|          |      | 6.5.4   | HeteroPDP Scalability Analysis                                    |

|          | 6.6  | Chapte  | er Summary                                                        |

| 7        | CON  | ICLUSI  | ONS                                                               |

| REFE     | EREN | CES     |                                                                   |

| APPENDIX |      |         |                                                                   |

|          |      |         |                                                                   |

A REGRESSION MODELS AND COEFFICIENTS FOR HETEROPDP  $\ldots 142$

# LIST OF TABLES

| Table | Page                                                                      |

|-------|---------------------------------------------------------------------------|

| 3.1   | GPGPU-sim Configurations for Latency Characterization 31                  |

| 3.2   | Benchmarks for GPGPU Latency Hiding Ability Characterization 46           |

| 3.3   | The Speedup and Frequency of Criticality Inversion within a Thread-       |

|       | block for BFS                                                             |

| 4.1   | GPGPU-sim Simulation Configurations for CAWA                              |

| 4.2   | Benchmarks for CAWA Evaluation                                            |

| 5.1   | GPGPU-sim Simulation Configurations for Ctrl-C 89                         |

| 5.2   | Default Configurations for the Ctrl-C Control Loop Design                 |

| 5.3   | Benchmarks for Ctrl-C Performance Evaluation                              |

| 6.1   | Memory Interference Infrastructure Setup and Configurations               |

| 6.2   | CPU Workloads for the Characterization Studies and Design evaluation 123  |

| 6.3   | OpenCL Workloads for the Characterization Studies and Design Eval-        |

|       | uation                                                                    |

| 6.4   | The OpenCL Kernel Features Used for Execution Time Prediction $\dots 125$ |

| A.1   | Coefficients for Predicting OpenCL Kernel Execution Time $alone$ on       |

|       | the Intel Core i7-3770 CMP143                                             |

| A.2   | Coefficients for Predicting OpenCL Kernel Execution Time $alone$ on       |

|       | the AMD FirePro S9150 GPU144                                              |

| A.3   | Coefficients for Predicting OpenCL Kernel Execution Time $co$ -located    |

|       | on Intel Core i7-3770 CMP145                                              |

| A.4   | Coefficients for Predicting OpenCL Kernel Execution Time $co$ -located    |

|       | on the AMD FirePro S9150 GPU146                                           |

# LIST OF FIGURES

| Figure | Pa                                                                           | age |

|--------|------------------------------------------------------------------------------|-----|

| 1.1    | An Example of an Accelerator-rich Heterogeneous Computer System              | 2   |

| 1.2    | An Overview of the Modern GPGPU Microarchitecture                            | 3   |

| 3.1    | The Execution Order with the Baseline RR Scheduler                           | 24  |

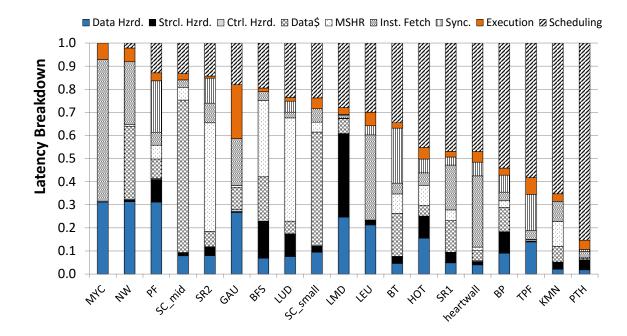

| 3.2    | Latency Breakdown for GPGPU Applications                                     | 32  |

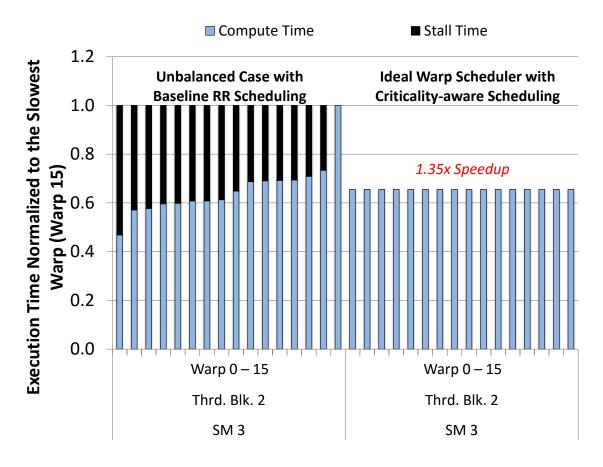

| 3.3    | An Example of Warp Criticality from the GPGPU Application ${\tt BFS}\ldots$  | 37  |

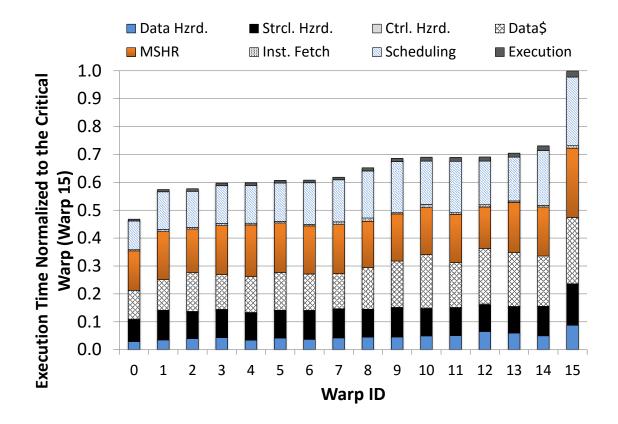

| 3.4    | Latency Breakdown for the BFS Application                                    | 38  |

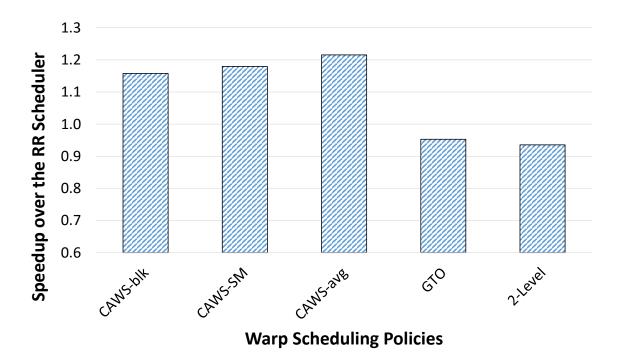

| 3.5    | The Speedup Comparison for Different Warp Scheduling Policies on ${\tt BFS}$ | 42  |

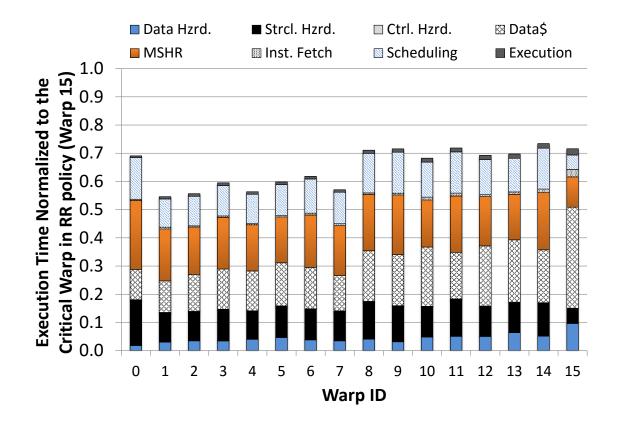

| 3.6    | Latency Breakdown for the ${\tt BFS}$ Application under the Oracle CAWS-     |     |

|        | avg Scheduling Policy                                                        | 44  |

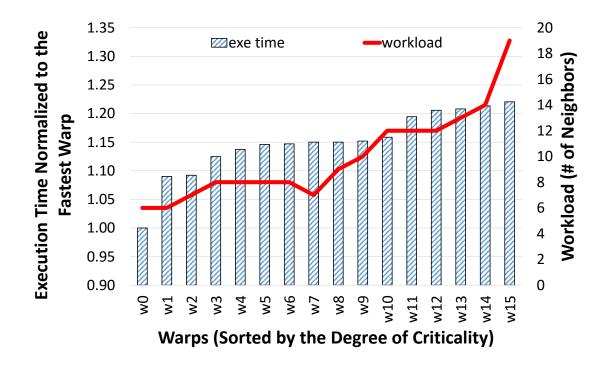

| 4.1    | Warp Execution Time Disparity Caused by Workload Imbalance for ${\tt BFS}$   | 50  |

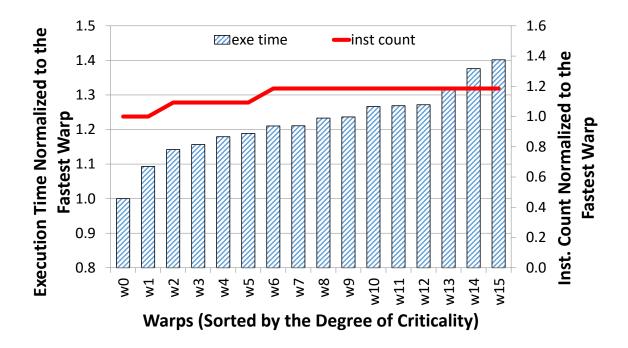

| 4.2    | Warp Execution Time Disparity Caused by Diverging Branch Behavior            |     |

|        | for BFS                                                                      | 52  |

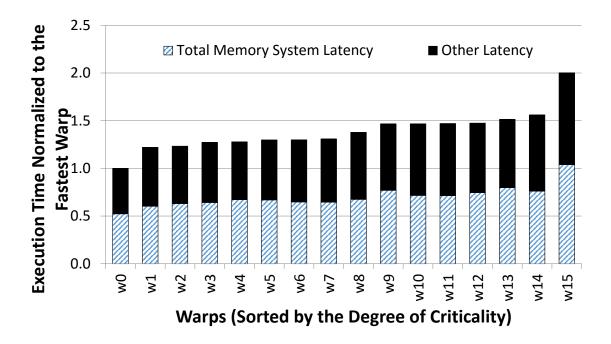

| 4.3    | Warp Execution Time Disparity Caused by Memory Subsystem Delay               |     |

|        | for BFS                                                                      | 53  |

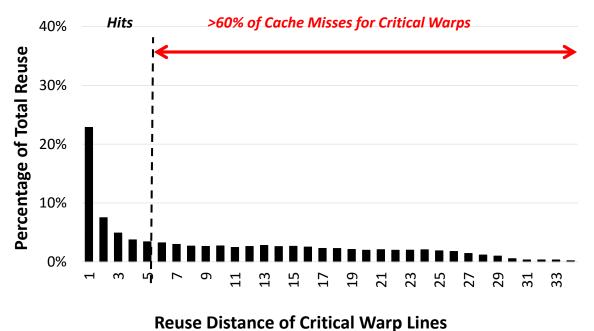

| 4.4    | L1 Data Cache Reuse Distance for the Critical Warps in $\mathtt{BFS}$        | 54  |

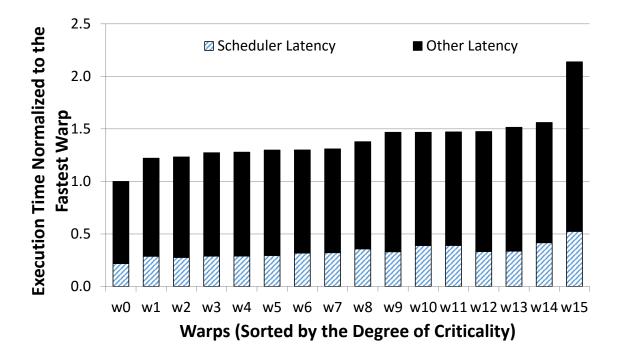

| 4.5    | Warp Execution Time Disparity Caused by Warp Scheduling Delay for            |     |

|        | BFS                                                                          | 55  |

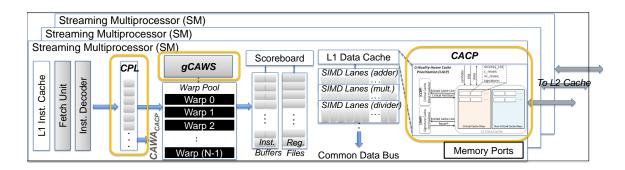

| 4.6    | The CAWA Architecture                                                        | 56  |

| 4.7    | The Instruction Count Disparity Caused by Branches                           | 57  |

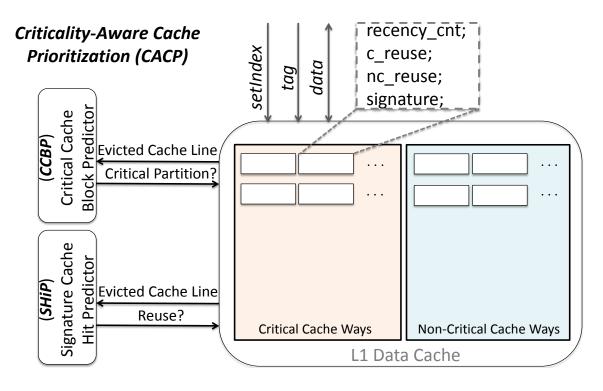

| 4.8    | The Criticality-aware Cache Prioritization Scheme                            | 60  |

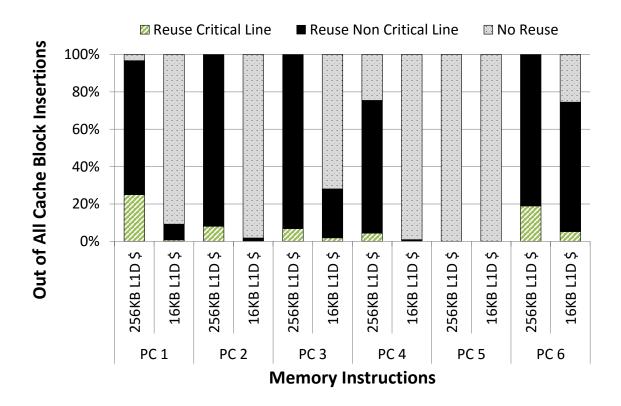

| 4.9    | Reuse Behavior of Different PCs for BFS                                      | 61  |

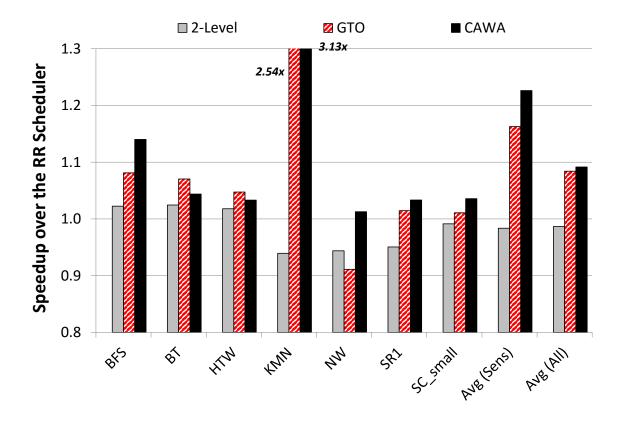

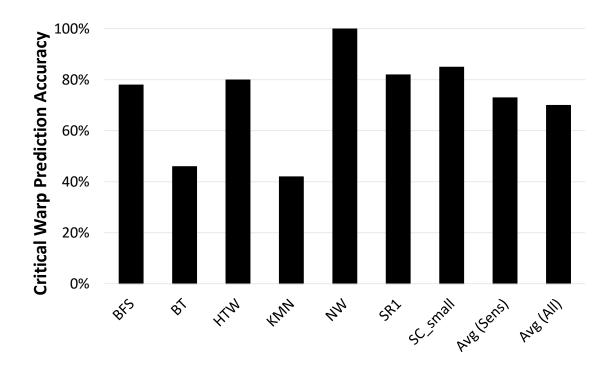

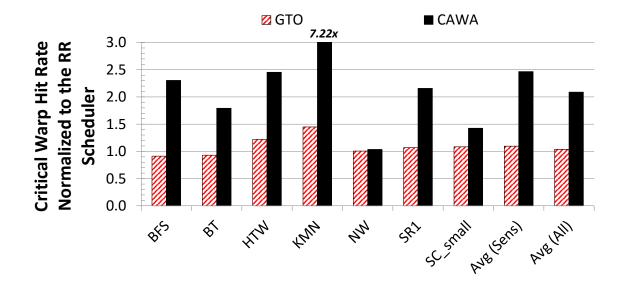

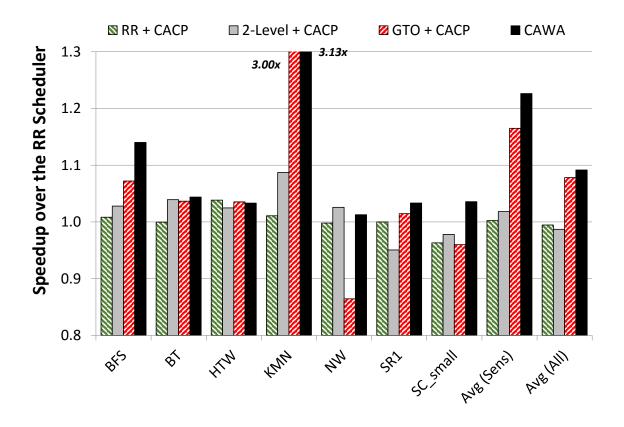

| 4.10   | Performance Improvement of CAWA                                              | 68  |

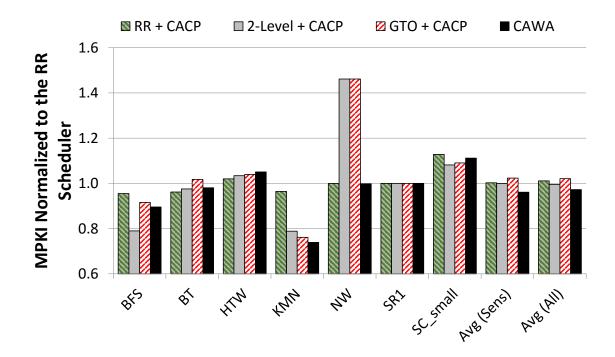

| 4.11   | L1 Data Cache MPKI Reduction of CAWA                                         | 69  |

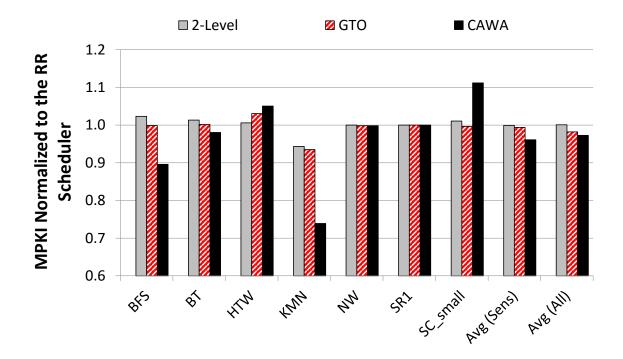

| 4.12   | The Prediction Accuracy of CPL                                               | 70  |

| 4.13 | The Performance Improvement of gCAWS                                           | 71 |

|------|--------------------------------------------------------------------------------|----|

| 4.14 | L1 Data Cache Critical Warp Hit Rate of CAWA                                   | 72 |

| 4.15 | L1 Data Cache MPKI Reduction of CACP with Different Warp Schedul-              |    |

|      | ing Policies                                                                   | 73 |

| 4.16 | L1 Data Cache Performance Improvement of CACP with Different                   |    |

|      | Warp Scheduling Policies                                                       | 74 |

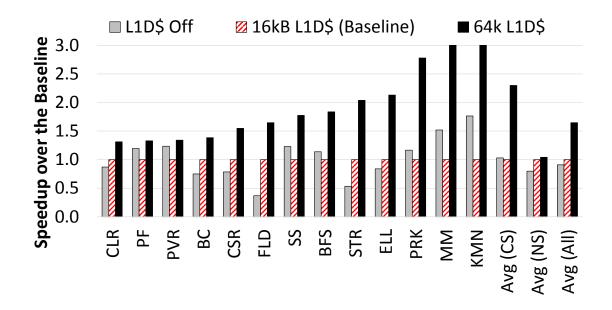

| 5.1  | Speedup of Different L1 Data Cache Configurations                              | 77 |

| 5.2  | An Example of Thrashing in GPU Caches                                          | 79 |

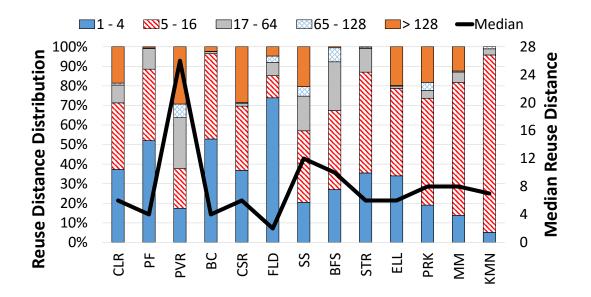

| 5.3  | The Distribution of L1 Data Cache Reuse Distance                               | 80 |

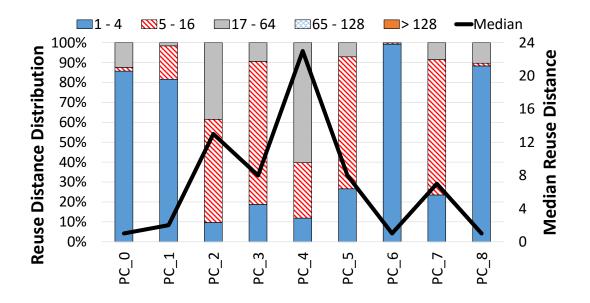

| 5.4  | The Distribution of L1 Data Cache Reuse Distance per Insertion PC              |    |

|      | of BFS                                                                         | 81 |

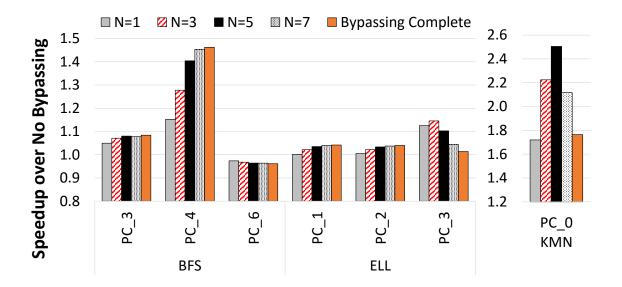

| 5.5  | Speedup with Varying an Instruction's Insertion/Bypassing Ratio $\ldots\ldots$ | 82 |

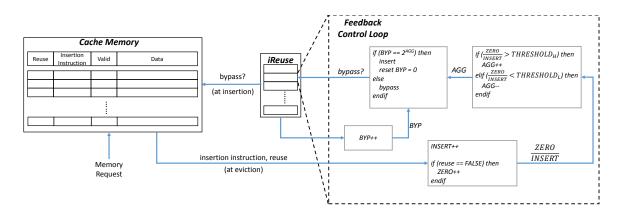

| 5.6  | The System Diagram of Ctrl-C Design                                            | 87 |

| 5.7  | The Performance Improvement of Ctrl-C                                          | 91 |

| 5.8  | The L1 Data Cache MPKI Reduction of Ctrl-C                                     | 92 |

| 5.9  | The L1 to L2 Caches Interconnect Traffic Reduction of Ctrl-C                   | 93 |

| 5.10 | The Fraction of Zero-reuse Cache Lines with Ctrl-C                             | 94 |

| 6.1  | An Example of a Heterogeneous Computer System with Multiple OpenCL             |    |

|      | Enabled Devices                                                                | 99 |

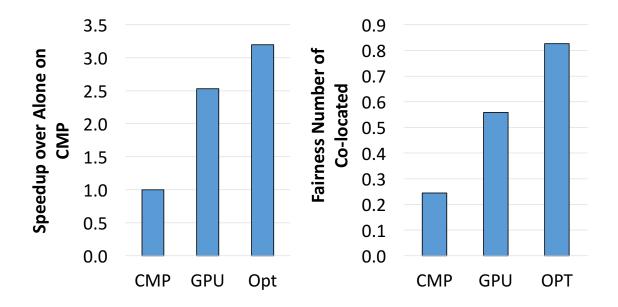

| 6.2  | The Average Execution Time Speedup and Slowdown Fairness of Run-               |    |

|      | ning OpenCL Applications1                                                      | 04 |

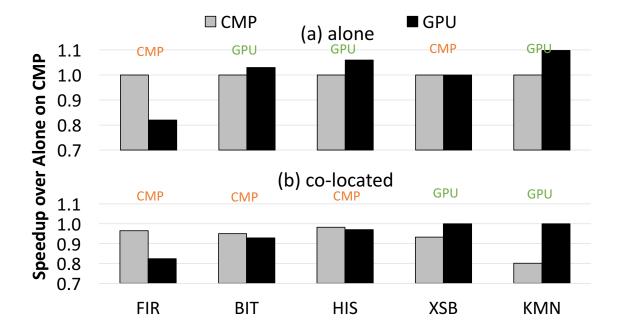

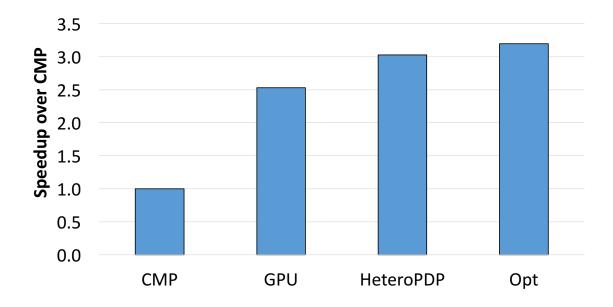

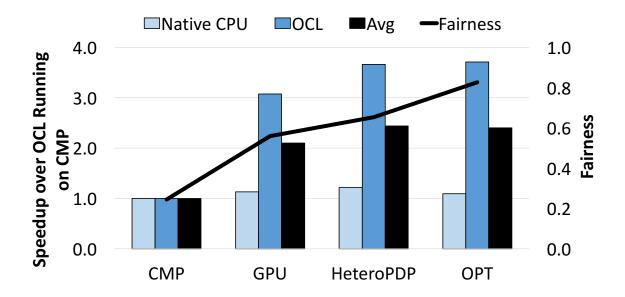

| 6.3  | The Execution Time Speedup of an OpenCL Application                            | 05 |

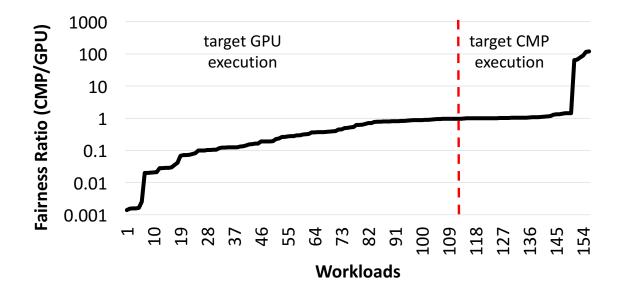

| 6.4  | The Fairness Ratio between Running an OpneCL Kernel on the CMP                 |    |

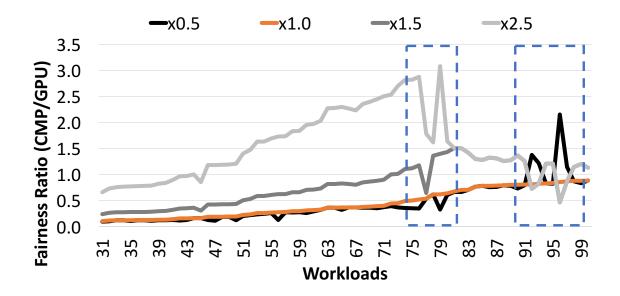

|      | versus on the GPU 1                                                            | 07 |

#### Figure

6.5

6.6

| The Fairness Ratio of Running an OpneCL Kernel on the CMP versus  |

|-------------------------------------------------------------------|

| on the GPU with Varying Scheduling Priorities                     |

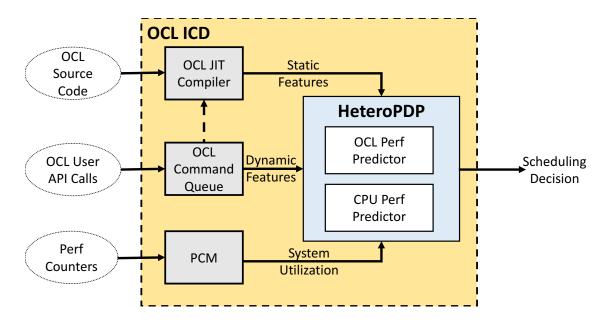

| System Diagram of the HeteroPDP Prediction Scheme109              |

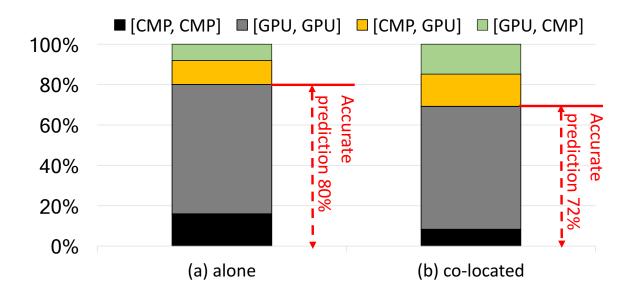

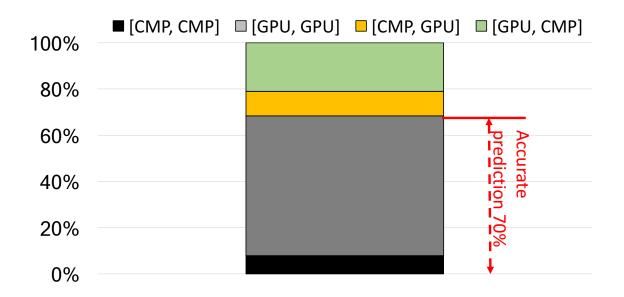

| The Prediction Accuracy of Selecting the Optimal Execution Target |

6.7

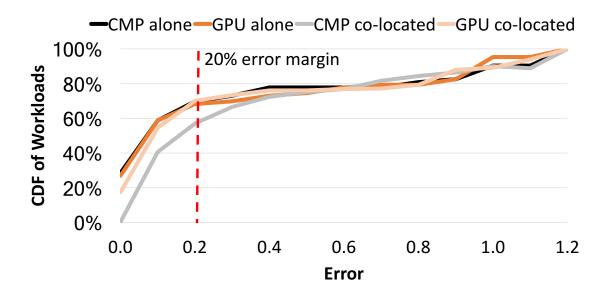

- 6.8The CDF of Prediction Errors for Predicting OpenCL Kernel Execu-

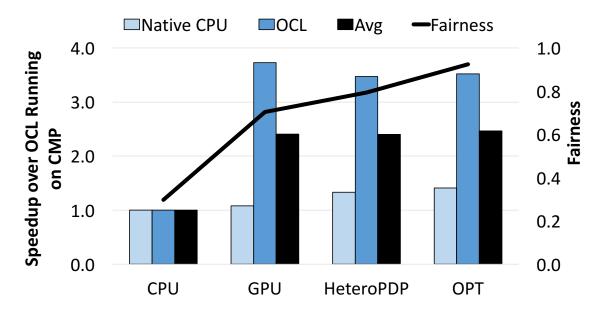

- 6.9The System Speedup of HeteroPDP when Running an OpenCL Appli-

- 6.10 The Speedup and Fairness of HeteroPDP when an OpenCL Application

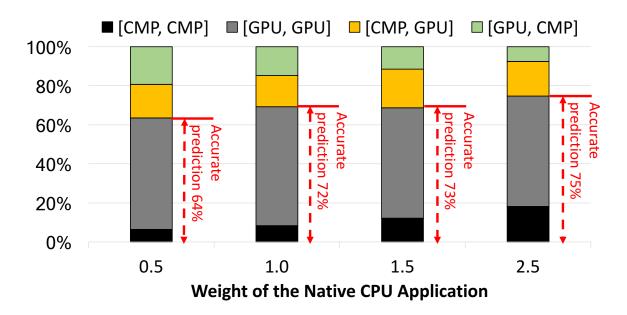

- 6.11 The Prediction Accuracy of Selecting the Optimal Target to Run an OpneCL Kernel Co-located with a Native CPU Application Having

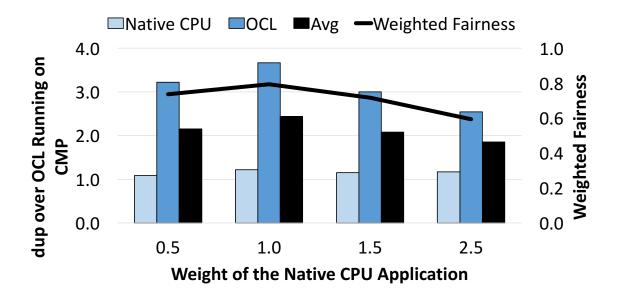

- 6.12 The Speedup of HeteroPDP when Running Workloads Consisting of an OpenCL Application and a Native CPU Application with Varying

- 6.13 The Prediction Accuracy of Selecting the Optimal Target Device to Run an OpneCL Kernel *co-located* with Two Native CPU Applications . 120

- 6.14 The Speedup and Fairness of HeteroPDP when Running Workloads Consisting of Two Native CPU Applications and One OpenCL Appli-

### Chapter 1

# INTRODUCTION

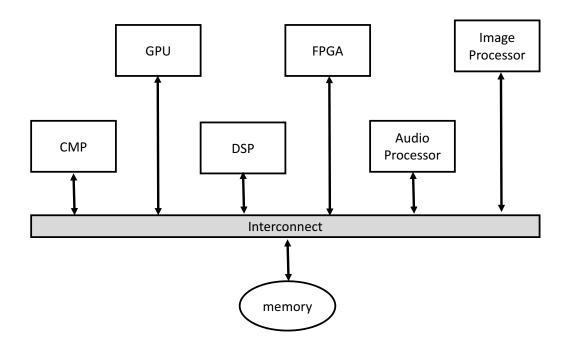

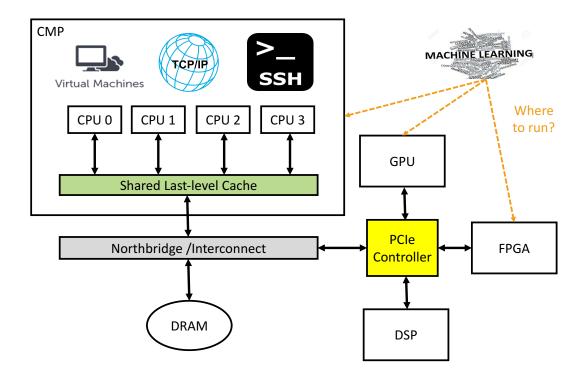

Modern computer systems are accelerator-rich, equipped with many types of hardware accelerators or sensors, e.g., graphics processing units (GPUs), tensor processing units (TPUs) [56], digital signal processors (DSPs), image processors, audio processors, and field-programmable gate arrays (FPGAs) to speed up computation and/or reduce energy consumption [25, 47, 105, 123]. Figure 1.1 exhibits an example of an accelerator-rich heterogeneous system architecture which integrates a variety of execution devices in a single computer machine. The advantage of having such kinds of heterogeneous systems is that workloads can be dynamically distributed to run on different devices based on their characteristics to maximize the overall system throughput.

GPUs are a type of hardware accelerators in modern computer systems. They are pervasively deployed to high performance computing clusters (HPCs). GPUs were initially devised to perform graphics related computations, specifically frame rendering, 3D modeling, video codec, and digital image processing. Nevertheless, the capability of performing massive multithreading and fast context-switching has been the forte of modern GPU architectures, which enables GPUs to accelerate generalpurpose parallel workloads such as scientific computation, weather forecasting, as well as machine learning workloads. Therefore, it is getting more and more notice today to offload and execute general-purpose GPU (GPGPU) workloads on the highly-parallel, throughput-oriented architecture.

Figure 1.1: An example of an accelerator-rich heterogeneous computer system.

# 1.1 GPGPU Architecture and Computation

GPUs are based on the single instruction multiple thread (SIMT) computation paradigm where multiple threads are grouped together to form a warp or wavefront. Threads in a warp are mapped to a single instruction multiple data (SIMD) execution unit such that all threads execute the same instructions, but with different data.

The benefit of the large number of warps and fast context-switching is latencyhiding—whenever the execution of a warp stalls, e.g., facing a cache miss and waiting for the data to be ready, it can be swapped out and another warp can be swapped in for immediate execution to maximize resource utilization without paying much context-switching overhead.

A modern GPU consists of multiple streaming-multiprocessors (SMs) or computation units (CUs). Each SM is similar to a SIMD processor, which has vector

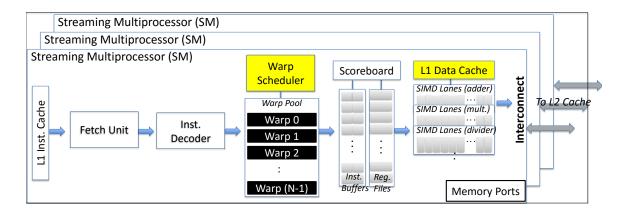

Figure 1.2: An overview of the modern GPGPU microarchitecture.

functional units, register file, cache memories, and instruction fetch/decode units as what Figure 1.2 illustrates [79]. Additionally, an SM also has a warp pool to record the context of all running threads for performing fast-context switching. To order the execution of the large number of parallel warps, an SM employs a hardware warp scheduler to dispatch and allocate computation resources for warp execution. Note that, the components highlighted in yellow in Figure 1.2 are the main components in the GPU microarchitecture which this thesis work focuses on.

At runtime, a GPGPU application first copies data from the host machine to a GPU's memory space. The application then spawns a massive number of threads that execute the same piece of code in a kernel to process the data. Multiple threads are grouped into a small batch, called a thread-block (TB) or a cooperative thread array (CTA). Threads from a thread-block have the same life-cycle and are dispatched to an SM for concurrent execution. For the threads to be executed by the vector functional units in an SM, the threads in a thread-block are split into several warps. All threads within a warp are executed simultaneously by the vector functional units. At every cycle, the warp scheduler selects a ready warp for execution. When a warp stalls, GPUs can perform fast context-switching to process another ready warp without introducing any additional latency. By interleaving the execution with a

large number of parallel warps, GPUs can hide execution latency to maximize the pipeline utilization and achieve a considerable throughput.

1.2 The Inefficiencies of Current GPGPU and Accelerator-rich System Designs

Although modern GPUs can process a large number of threads in parallel, it has been shown that directly employing GPUs to accelerate parallel workloads does not always gain good performance improvements. This is mainly due to three reasons:

- 1. Not all warps have the same amount of workload. Warps have different number of instructions for execution, and thereby there is an execution time disparity between parallel warps. This execution time disparity can raise a sub-optimal performance problem, called warp criticality.

- 2. The shared hardware resources are limited, in particular the cache storage and memory bandwidth. It is difficult to fairly accommodate the demands of all running threads. Concurrent running threads compete the shared computation resources that may introduce additional stall cycles, lowering the pipeline utilization.

- 3. To perform computation on a GPU often requires to copy a large amount of data between the host CMP and the GPU back and forth for communication and synchronization. Because of the limited bandwidth capacity of the system bus and the host main memory, these data transfer operations can incur significant execution time overhead and memory interference, resulting in lower average throughput than always using the host CMP to process the same workload.

#### 1.2.1 Execution Time Disparity and Warp Criticality

In the GPGPU computation paradigm, a thread-block is the basic computation unit dispatched onto an SM. A thread-block contains a number of warps that have the same life-cycle and are bounded to the same synchronization barrier. In other words, warps from the same thread-block start execution at the same time, and are blocked at the same synchronization barrier until all warps finish the associated computation workloads.

However, not all warps have the same amount of workload, and therefore warps do not always finish at the same time. A significant execution time disparity is observed between warps in a thread-block for GPGPU workloads. As a result, fast running warps have to wait at a synchronization barrier or kernel exit point until the slowest running warp, or the so-called critical warp, finishes. This raises two problems that significantly degrade the performance of GPUs. First, the execution time of a thread-block is determined by the execution time of the critical warp. Although faster running warps finish the assigned workloads, they are suspended at a synchronization barrier without performing any meaningful computation. Consequently, it occupies and wastes precious shared hardware resources such as the register file. Second, when faster running warps finish execution and are idle, the number of active warps decreases. In such a scenario, the GPU may not have enough ready warps to hide latency stalls. When a warp, especially the critical warp, stalls, its execution latency will be exposed and thereby the GPU pipeline is not fully utilized. This performance problem is called the *warp criticality* problem.

To address the warp criticality problem, in Chapter 3, I discuss the important factors that contribute to GPU pipeline stall and present the results that quantify the severity of the warp criticality problem for GPGPU applications [68, 69]. I identify the sources of warp execution time disparity in Chapter 4 [72]. While the average execution time disparity between the warps that share a synchronization point in a thread-block can result in reduced pipeline utilization and lower throughput, the performance of GPGPUs is also significantly constrained by the memory subsystem. I propose a coordinated warp scheduler and cache prioritization scheme, called Criticality-Aware Warp Acceleration (CAWA), to effectively reduce the degree of warp criticality [72].

# 1.2.2 Resource Contention and Cache Thrashing

Modern GPUs are often equipped with cache memories to filter out the interconnect bandwidth demands as well as to reduce the average memory access latency. However, because of the massive multithreading computation paradigm, cache capacities, especially the L1 data caches, of GPUs are relatively small. For instance, an SM of the NVIDIA Maxwell GPU can process up to 2048 concurrent threads and has a 24kB L1 data cache shared across all running threads [92]. Namely, on average, each thread can only obtain a few bytes of the data cache storage. Threads contend for the cache storage with each other, resulting in a severe cache thrashing problem, namely, cache lines are frequently swapped in/out without receiving any reuse. Consequently, GPGPU applications do not utilize cache memories efficiently.

The cache inefficiency in GPUs incurs two critical problems which often limit the performance of GPUs. First, due to the cache thrashing problem, many GPGPU applications have high data cache miss rates. GPU caches are not able to effectively reduce the average memory access latency, leading to additional pipeline stalls. Second, a large amount of adjacent data elements brought into the cache with the demanded data is never referenced before being evicted. This injects additional data traffic to the interconnect and can increase the queuing latency in the interconnect. Due to the unnecessary data traffic, applying caches to preserve spatial localities significantly degrades the performance in some GPGPU workloads instead [51].

Many prior works proposed to apply cache bypassing techniques to alleviate the degree of cache thrashing in GPUs. A widely used approach to bypass memory requests from caches is to employ compilers to perform off-line analysis and identify data that are unlikely to receive any reuse in the near future [51, 76, 77, 121]. However, the compiler-based approaches are not flexible for input dependent applications. In addition to the static compiler based schemes, a number of prior works proposed to use additional hardware components to count and predict the reuse distances of cache lines at runtime [74, 109]. However, the reuse distances of GPGPU cache lines can be extremely long and exhibit a disperse distribution. It is challenging to accurately predict reuse characteristics of GPGPU cache lines with low storage requirement. These dynamic prediction algorithms, therefore, require a large number of hardware counters and incur significant implementation overhead.

To tackle the cache inefficiency problem in GPUs, Chapter 5 of this thesis explores the cache access behavior of GPGPU applications. I propose a low hardware implementation overhead cache bypassing algorithm—Control-Loop Based Adaptive Cache Bypassing (Ctrl-C)—for GPGPUs to accurately predict the cache reuse behavior without the need of off-line analysis and dynamically bypass memory requests to prevent cache lines from early eviction [70]. Ctrl-C significantly improves the overall performance of GPGPUs and outperforms other state-of-the-art GPU cache bypassing schemes.

#### 1.2.3 Data Movement Overheads and Memory Interference

In a heterogeneous system, GPUs are usually attached to the host machine via the PCIe or AGP bus interface. When offloading computation onto a GPU card, the system has to frequently copy data between the host main memory and the GPU internal memory via the bus to synchronize the data. Since the system bus and main memory bandwidth is a limited resource, the data movement operations frequently become a critical performance bottleneck of GPUs and dominate the total execution time [13, 37, 81, 93, 108]. As a result, exploiting GPUs to accelerate computation does not always exhibit better overall throughput than processing on CMPs directly.

In order to eliminate the performance impacts of data movement operations, numbers of prior works, such as [6, 114, 115, 120], developed performance prediction schemes to dynamically make offloading decisions. These works focused on adopting machine learning or compiler techniques to profile and analyze the characteristics of a GPGPU application to understand whether offloading the computation is able to receive performance or energy benefits.

However, apart from the GPU application itself, in a realistic computer system, there are many concurrent processes co-located on the same machine, sharing the system bus and main memory bandwidth. For example, in an on-demand cloud computing environment such as Amazon Web Service (AWS) [3], Google Cloud [36], and Microsoft Azure [24], compute nodes are simultaneously servicing multiple applications or hosting multiple virtual machines with native CPU applications as well as GPU acceleratable applications. In such execution environment, co-located applications contend for shared resources in the memory subsystem. Consequently, existing task scheduling schemes that only consider the characteristics of an application itself but do not take into account memory interference from co-located workloads are not robust and provide sub-optimal performance gain.

To understand the need for an intelligent scheduler that can make an accurate decision for which optimal execution target an application should be executed on in the presence of memory interference, Chapter 6 of this thesis provides a detailed performance characterization study for accelerate-rich heterogeneous systems. Based on the observations, I design a scalable **Hetero**geneous **P**erformance **D**egradation **P**rediction (**HeteroPDP**) scheme to accurately predict the system performance degradation when an application is running on different execution targets with memory interference [71]. With the prediction outcomes of HeteroPDP, a workload can be dynamically to be dispatched to run on the optimal execution target device based on the optimal goal.

# 1.3 Contributions

The goal of this thesis is to design architectural- as well as system-level solutions to address the inefficiencies of GPGPU microarchitectures and system architectures of accelerator-rich computers equipped with GPUs. Specifically, the thesis focuses on discussing the warp criticality, cache contention, and memory interference problems in GPGPUs. Besides, this thesis also provides detailed characterization studies and new insights of GPGPU architecture designs from different aspects, including warp scheduling algorithms, memory management techniques, and performance predictions. Overall, this work makes the following key contributions:

- 1. Providing a detailed characterization of the latency hiding ability of GPGPUs.

- Identifying the warp criticality problem and providing an in-depth study of the warp execution time disparity in the massive multithreading computation of GPGPUs.

- 3. Designing a coordinated warp scheduling and cache prioritization solution to efficiently eliminate the warp criticality problem in GPGPUs.

- 4. Developing a control loop based cache bypassing algorithm to intelligently mitigate the cache contention problem in GPGPUs.

- 5. Analyzing the system performance degradation in the presence of memory interference in a CPU-GPU multiprogrammed computing environment.

- 6. Proposing a performance degradation mechanism to balance the execution time slowdown and maximize the overall system throughput for accelerator-rich computer systems.

The following chapters of this thesis present my research accomplishments in detail. The rest of this thesis is organized as follows:

- 1. Chapter 2 discusses prior studies related to this thesis work.

- 2. Chapter 3 describes the warp criticality problem and shows the characterization results for its impact on the performance of GPGPU workloads.

- 3. Chapter 4 presents a solution that accelerates the execution of critical warps, called Criticality-Aware Warp Acceleration (CAWA).

- 4. Chapter 5 demonstrates a control loop based adaptive cache bypassing (Ctrl-C) algorithm to effectively mitigate cache contention in GPGPUs.

- 5. Chapter 6 presents a performance degradation prediction (HeteroPDP) scheme to accurately predict and balance the system performance degradation in the presence of memory interference in a heterogeneous system setup.

- 6. Chapter 7 summarizes this thesis work and makes the conclusions.

#### Chapter 2

# RELATED WORK

To better understand the context and novelty of my thesis work, this chapter focuses on reviewing and discussing prior studies in the related areas.

While the goal of this thesis work is to solve three inefficiencies in modern GPGPU microarchitectures and accelerator-rich heterogeneous systems (i.e., the warp criticality, the cache contention, and the system memory interference problems), I will first review the prior studies relevant to warp criticality. I will then present the works regarding cache management in CPUs and GPUs. Finally, I will introduce the designs related to the shared system resource management as well as the task scheduling in heterogeneous computer systems.

### 2.1 Warp Criticality

Thread Criticality in CMPs. The concept of thread criticality in CMPs is similar to the warp criticality problem in GPUs. A multithreading application often applies barriers to synchronize between threads. However, not all threads arrive at a barrier at the same time. Fast running threads are idle at a barrier to wait for the slowest running thread. The execution time of a parallel application is dominated by the execution time of the critical thread on CMPs. In order to improve the system performance, it is important to identify the critical thread in advance and accelerate the critical thread execution.

Li et al. pointed out that some threads in CMPs are often idle to wait for slower running threads, resulting in energy waste [75]. In order to save energy, Liu et al. presented a probability model to estimate the thread running time and guide the dynamic voltage and frequency scaling (DVFS) of CMPs [80]. Cai et al. proposed using compilers to insert check points in the parallel regions that all threads execute to evaluate the execution speed of each thread [17]. By monitoring the time a thread reaches the check points, the critical thread can be detected. Bhattacharjee and Martonosi observed that the critical threads often encounter more cache misses and have longer average memory access latency [14]. Bhattacharjee and Martonosi designed a thread criticality predictor (TCP) by monitoring the per-thread cache access behavior. TCP is then used to guide the task stealing as well as DVFS of CMPs. Ebrahimi et al. exploited the degree of resource contention at a spin lock as the metric to predict the critical thread [30]. If a lock is frequently held by a particular thread, this thread has likelihood to be the critical thread. Bois et al. proposed a stack based approach to measure thread criticality by monitoring the number of waiting threads in a certain time interval [15]. A thread has a higher degree of criticality if there are more threads waiting at a spin lock when this particular thread performs computation. Turakhia et al. observed that the number of instructions in a code section (i.e., the code between two consecutive barrier instructions) has locality [111]. In other words, two consecutive code sections often have similar number of instruction counts. Based on this observation, Turakhia designed a thread progress equalization (TPEq) scheme to predict the degree of thread criticality by predicting and calculating the distance to reach a barrier.

Although the concept of thread criticality in CMPs is similar to warp criticality in GPUs, due to the distinct difference between CPU and GPU architectures and computation paradigms, the effects introduced by the critical threads and critical warps vary as well. Because GPU has a large number of parallel warps and frequently switches the execution between the parallel warps, there are more factors that can lead to warp criticality as I will present in Chapter 4. It is still difficult to accurately predict the critical warp with these thread criticality prediction algorithms for CMPs.

**GPGPU warp scheduling.** While the warp criticality problem can substantially limit the performance of GPGPU workloads, this thesis work proposes using a criticality-aware warp scheduling algorithm to eliminate the warp execution time disparity. Next, I present the state-of-the-art warp scheduling algorithms to better understand the design of warp schedulers.

Many prior works focused on improving the performance of GPUs by modifying warp scheduling algorithms to prevent warps from stalling. Gebhart et al. and Narasiman et al. designed a 2-Level scheduler to split warps into different subgroups and keep only one group of warps active at a time [35, 87]. The warp scheduler is only able to issue instructions from the active subgroup of warps, so that the resource contention problem can be alleviated. Jog et al. further improved the 2-Level scheduler by assigning warps with continuous IDs to different subgroups [54, 55. Because memory requests from continuous warps have higher probability to fall into the same L2 cache or DRAM bank, resulting in bank conflicts and longer memory access latency. With this warp grouping algorithm, the GPU performance can be improved by avoiding bank conflicts at the L2 cache and DRAM. Rogers et proposed a cache conscious mechanism to monitor and measure the degree of al. memory contention by a loose locality score (LLS) [101, 102]. The warp scheduler then dynamically modulates the number of active warps based on the degree of LLS value. If the cache controller detects cache lines in the L1 data cache are frequently evicted due to the interference from inter-warp accesses (LLS value is high), the warp scheduler will decrease the number of active warps. While applications might have different preferences of warp scheduling policies, Awatramani et al. proposed a phaseaware warp scheduling algorithm which applies compilers to analyze the GPGPU kernel source code and select the optimal warp scheduling policy, whereas Lee et al. designed an adaptive algorithm to dynamically select the optimal scheduling algorithm based on the instruction issue pattern at runtime [10, 67].

These proposed warp scheduling algorithms aim to prevent all warps from stalling at the same time due to long latency memory operations to improve the pipeline utilization. These scheduling policies allow the warp scheduler to tolerate memory latency better by reducing the idle time of GPU pipeline. However, these warp scheduler designs do not take the impact of warp criticality into account. The warp criticality problem can still limit the performance of GPGPU workloads. In contrast, my proposed criticality-ware scheduling design (Chapter 3 and 4) in this thesis aims to resolve resource contention by ordering the warp execution based on warp criticality and allowing critical warps to execute with larger time slices. Therefore, the performance of GPGPU workloads can be significantly improved.

### 2.2 Cache Thrashing Problem and Cache Management

In addition to the warp criticality problem, memory contention and cache thrashing is another main problem limiting GPU's performance. To design a new cache management policy to improve the cache efficiency in GPGPUs, I intend to review prior studies that focused on lessening the degree of cache thrashing in CPUs and GPUs next.

**CPU cache management.** Many cache management policies have been proposed to mitigate cache thrashing in CPUs. Jiménez designed a tree-based pseudo LRU (pLRU) cache replacement policy, which exploits machine learning techniques to find out the optimal promotion and insertion position for cache lines on an LRU stack [53]. Qureshi et al. proposed the BIP cache insertion policy and set dueling mechanism to insert new cache lines at the LRU position to achieve the optimal hit rate when cache thrashing occurs [97, 98]. Jaleel et al. designed an RRIP algorithm which predicts the reuse distance of a cache line by giving each cache line a re-reference prediction value (RRPV) and updating RRPV when a set is accessed [49]. Wu et al. proposed a signature based framework, SHiP, to predict the reuse distance of an incoming cache line based on the particular signature of a memory request, e.g., the insertion program counter value and memory address [119]. Arunkumar and Wu designed a reuse-and-cost aware memory access (ReMAP) scheme that takes the DRAM access latency into account to select the best cache eviction candidate [8]. Lai et al. and Khan et al. proposed dead block sampling algorithms to predict if a cache line will not be reused in the near future [61, 63]. The dead block then can be bypassed or evicted from the cache. However, all these reuse distance prediction works were built on top of CPU's last level caches, which usually have higher associativity with the capacity in MB scale. For instance, the Intel Core i7-2600 CPU is equipped with a 8MB L3 cache [44]. While the L1 data caches in GPUs are much smaller and have lower way-associative, the cache trashing problem is severer. These CPU cache management algorithms are not able to accurately predict the data reuse patterns in GPUs.

In order to prevent cache lines from early eviction, Dung et al. proposed a PDP protect algorithm to bypass part of memory requests [29]. In PDP, each cache line has a protection counter which is decremented by one when the corresponding set is accessed. A cache line can be evicted only when its protection counter reaches zero. If no line has a zero protection value, then the new incoming memory request will be bypassed. PDP guarantees a cache line will not be evicted within a short time period. However, the reuse distances for GPGPU workloads can be extremely long and often have a disperse pattern. It is difficult to predict and set up an optimal protection distance.

**GPU memory and cache management.** Stratton et al. conducted a detailed characterization study and suggested that resource contention in the memory subsystem is a critical performance problem limiting GPGPU performance [106, 107]. In order to alleviate the memory contention in GPUs, Lee et al. designed a compiler-based scheme to predict the per-thread working set size [66]. According to the prediction outcome, GPUs can then limit the number of active threads to regulate the degree of memory contention. Chatterjee et al. proposed a sub-channel architecture specifically for GPU DRAMs to mitigate the degree of contention in DRAM row buffers [18]. Choo et al. observed that using unified L1 data caches shared across multiple SMs can improve inter-warp locality and mitigate cache contention [23]. Sethia and Mahlke designed an Equalizer scheme that can dynamically monitor the demand of different shared resources in GPUs [104]. If Equalizer detects the warp execution time is dominated by memory access time, it throttles the warp execution by stopping creating new thread-blocks on an SM.

Cache bypassing is an approach for balancing cache capacity scaling and its utilization [85]. To effectively improve GPU cache utilization and mitigate the degree of cache contention, many cache bypassing algorithms have been proposed. Jia et al. designed a FIFO queue (MRPB) to reorder requests to reduce inter-warp contention [52]. Additionally, MRPB bypasses requests if intra-warp memory contention is detected. Chen et al. designed an adaptive resource management scheme that monitors cache contention and interconnect congestion [22]. If the degree of cache contention or bandwidth demand is too high, memory requests will be bypassed. Mahmoud et al. proposed using cache miss rate as a metrics to evaluate if an application is a streaming workload and make cache bypassing decision accordingly [60]. However, these prior designs do not distinguish reuse patterns among memory requests. Cache lines with near reuse distances may be bypassed, losing an opportunity to improve the cache hit rate.

Xie et al. and Liang et al. modified compilers to analyze GPGPU applications source code and guide GPUs to bypass data which are unlikely to receive any reuse [76, 77, 121]. Li et al. proposed a valley model to guide compilers analyzing if a GPU application can benefit from cache bypassing [73] for varying number of spawned threads. However, these compiler-based schemes are not able to predict the reuse behavior of input dependent applications, e.g., applications with pointer chasing execution behavior.

Tian et al. proposed the PC-based Adaptive Bypassing that uses confidence counters to predict zero-reuse lines and bypasses all requests if detecting cache lines will not receive any reuse [109]. Lee et al. designed a region-aware caching mechanism (GREEN) [65]. GREEN dynamically tracks the degree of locality and selectively bypasses data that are located in the memory regions with poor locality. Li et al. suggested adding additional tag array entries to track the data reuse patterns [74]. Nevertheless, the reuse distance can be extremely long for GPUs. It is challenging to accurately predict the data reuse patterns with a limited number of confidence counters or tag array entries.

Zheng et al. designed an adaptive cache and concurrency allocation (CCA) scheme to dynamically trace the per-warp memory access footprint [125]. CCA then prevents cache lines from early eviction by limiting the number of warp allowed to access to the cache memory. Dai et al. developed a model-driven approach that dynamically estimates the cache hit rate as well as execution time speedup improvement if reducing the number of warps that can allocate the data cache storage [27]. The model-driven approach then intends to bypass memory requests issued by a set of designated warps to maximize the cache hit rate. However, with the imbalanced memory access time created by these works, the model-driven approach may increase the degree of warp criticality, degrading GPU pipeline utilization.

Koo et al. developed an access pattern-aware cache management policy (APCM) that dynamically identify the locality type (inter-warp locality, intra-warp locality, and streaming) of each memory instruction [62]. If a memory instruction is predicted to have streaming access behavior, APCM will then bypass requests issued by this particular instruction. However, APCM bypasses all the memory requests if it predicts the memory access pattern is streaming. In such case, the hardware tracker loses the information to examine the cache access pattern. It is difficult to identify whether a bypassing decision is correct or not.

In contrast, in this work, I propose a low circuit implementation overhead design— Ctrl-C (Chapter 5)—to dynamically learn the cache line reuse behavior and perform selectively cache bypassing to alleviate the cache thrashing problem in GPGPUs without a need of off-line analysis.

#### 2.3 Memory Interference in Heterogeneous Systems

Memory Interference and Management The shared resource contention in the CMP domain has been studied by an extensive amount of prior works. These works mainly focused on discussing managing the capacity and bandwidth of the shared memory subsystem. Mutlu and Moscibroda proposed a stall-time fair DRAM scheduling algorithm to reduce the performance degradation and improve system slowdown fairness caused by shared resource contention in the DRAM modules by dynamically assigning different DRAM access priorities to the co-scheduled threads [86].

In order to understand the effects of cache interference in a CMP system, Hsu et al. conducted a detailed characterization study to analyze the performance impacts with different shared cache partition strategies. To mitigate the shared last-level cache

contention, Jaleel et al. proposed a thread-aware dynamic insertion policy (TADIP) to monitor and select the insertion policy for co-located applications that share the last-level cache [48]. Qureshi and Patt designed a utility-based cache partitioning (UCP) algorithm to eliminate the shared cache interference in a multiprocessor system by allocating different size of cache storage to each co-located application based on the cache utilization [96]. In order to solve the underutilization problem and reduce the implementation overhead of UCP, Xie and Loh proposed a pseudo partitioning (PIPP) scheme that simulate the cache partitioning algorithm by inserting a new cache line at different positions [122]. Wang and Chen proposed a futility scaling (FS) mechanism that targets at partition the cache storage for co-located processes without losing the cache associativity [113]. Intra-application cache interference stemmed from operating system activities and hardware prefetching can occur and degrade an application's performance as well. Wu and Martonosi studied the intra-application cache interference problem and proposed an OS-aware cache insertion policy to eliminate the intra-application interference by prioritizing the memory requests asserted by kernel- and user- space processes [118]. In order to accommodate the shared cache resources for processes with different OS scheduling priorities, Wu and Martonosi developed a adaptive timekeeping replacement (ATR) policy to dynamically adjust the cache decay intervals based on the optimization target [117].

In addition to using the architectural-level solutions to alleviate the shared resource contention problem, many works targeted at designing software scheduling algorithms to allocate the shared resources. Mars et al. designed a low overhead algorithm, called Bubble-up, to predict the degree of shared resource contention and to schedule services to run on different computation nodes in data center execution environments [82]. The Bubble-up algorithm aimed to maximize the per-node loading without violation the real-time deadline or quality-of-service (QoS) constraints. On the other hand, Jaleel et al. proposed a cache replacement and utility-aware scheduling (CRUISE) targeting at coordinating the OS scheduling and cache replacement policy to maximize the system throughput on a single CMP machine [50]. To schedule workloads running on a single-ISA heterogeneous multiprocessor system (e.g., the big-little core architecture [7]), Craeynest et al. proposed a performance impact estimation (PIE) algorithm to predict the performance when a program runs on the other core [26].

Nevertheless, all of these existing solutions looked at the homogeneous architecture domain only. In contrast, in my thesis, the proposed HeteroPDP scheme (Chapter 6) targets at predicting and mitigating the degree of shared resource contention specifically in heterogeneous computer systems.

Shared Resource Management for Heterogeneous Systems Since many commercial products have integrated CPU and GPU cores into one single die, how to efficiently manage the shared resources between the different types of processors is a significant research problem, especially for the shared last-level cache [41, 42]. Lee and Kim proposed a thread-level parallelism aware policy (TAP) to partition the shared cache storage for co-located CPU and GPU workloads [64]. Mekkat et al. developed an algorithm, called HeLM, to dynamically determine the priority of CPU and GPU cache accesses [83]. Kayıran et al. designed a concurrency management scheme that mitigates the memory bandwidth contention in a heterogeneous system by regulating the number of concurrent running on the GPU cores [57]. García et al. quantified the impact of shared virtual memory space between the CPU and GPU cores and suggested that developers have to redesign OpenCL programs to leverage the utilization between CPU and GPU cores to optimize the system throughput [34]. Ausavarungnirun et al. developed a staged DRAM controller that aims to improve the fairness of CPU-GPU shared DRAM by using dedicated CPU and GPU request queues in the memory controller and treat the CPU/GPU requests with different priorities [9]. Seo et al. designed a memory-aware load balance algorithm (MLB) [103]. MLB aims to balance the performance degradation by allocating more DRAM bandwidth for data movement between the host CPU and the hardware accelerators. None of these works, however, addressed the shared resource contention problem from the aspect of task scheduling by taking into account the degree of memory interference from multiple levels of the memory hierarchy.

**OpenCL Kernel Scheduling** Many prior works have pointed out that employing GPUs to accelerate OpenCL kernels does not always lead to performance improvement, due to the data movement and synchronization overhead [13, 37, 42, 81, 93, 108, 124]. In order to identify the optimal execution target device to run an OpenCL kernel, many works proposed applying a variety of machine learning techniques to dynamically analyze and predict the behavior of an OpenCL kernel. Wu et al., designed a performance and power predictor for GPUs by adopting the K-means algorithm [120]. Wen et al., proposed using support vector machine (SVM) to model the performance gain of GPUs [115]. Ardalani et al. employed regression models to project the GPU kernel execution time by running the same kernel on CMPs [6]. Wen and O'Boyle designed a decision tree based algorithm to analyze the performance benefits that offloading an OpenCL to run on an accelerator [114]. Aji et al. designed a set of OpenCL API extensions enabling compilers to guide the OpenCL scheduler select the optimal target device at runtime [1, 2].

Instead of predicting the performance gain, a number of studies focused on minimizing the data transfer overhead. Lustig and Martonosi developed a fine-grained synchronization mechanism to early start the GPU kernel execution and hide the data transfer latency [81]. Ham et al. proposed a supply-compute framework (DeSc) which decouples the communication and compute engines to hide the data transfer overhead by out-of-order executing data fetching and computation [38]. Belviranli exploited just-in-time (JIT) compilers to hide the communication overhead by automatically reordering the GPU application programming interface (API) calls to overlap the data transfer operations [13].

However, none of the prior works takes the shared resource interference introduced by the co-located applications into account in making a scheduling decision. They simply took an individual GPU kernel's characteristics to do performance prediction and optimization. While a realistic machine can service several processes or applications simultaneously, these designs are not robust. Instead, in this work the proposed HeteroPDP in Chapter 6 aims to optimize the performance for the entire system.

## Chapter 3

# WARP CRITICALITY AND CRITICALITY-AWARE WARP SCHEDULING

Modern GPUs achieve a high throughput by applying massive multithreading and fast context-switching to hide the execution latency. When the execution of a warp stalls, the warp can be swapped out and another ready warp can be swapped in for execution. These stalls could be caused by cache misses or pipeline hazards, e.g., data or structural hazards.

## 3.1 The Baseline GPGPU Architecture and its Computation Model

A GPGPU application is a highly multithreading program. Massive number of parallel threads execute the same program code, called a *kernel*, with different data. At runtime, a GPGPU application creates multiple thread-blocks to perform parallel computations, where a thread-block is an array of concurrent threads that are dispatched to run on a GPU shader core together. Threads from the same thread-block share global data and synchronize at barriers. A programmer can invoke barrier instructions (the API calls of *\_\_\_\_syncthread()* in CUDA [91] or *barrier()* in OpenCL [16] semantics) explicitly to block the thread execution and make threads synchronize. In addition to the explicit synchronization barriers, threads are automatically blocked to synchronize when they finish their own workloads as well, i.e., an implicit synchronization barrier can be observed at the end of kernel code. When reaching a barrier point, either explicit or implicit, a thread has to stop execution until all threads from the same thread-block reach the same barrier.

Figure 3.1: The execution order with the baseline RR scheduler.

A modern GPU is a cluster of multiple shader cores, called streaming multiprocessors (SMs) or computation units (CUs), where each SM is a unified graphics and computing processor that can execute graphics rendering or general-purpose computations as shown in Figure 1.2 [79]. An SM is a *single instruction multiple data* (*SIMT*) processor, which processes massive number of parallel threads from the same GPGPU program with vector functional units. In order to fit into the width of the vector functional unit, multiple parallel threads from the same thread-block are further grouped into a small batch, called a *warp*. A warp is the basic unit to be scheduled and executed in the GPU pipeline.

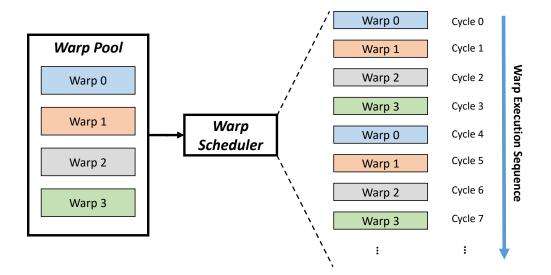

In order to efficiently execute the large number of parallel warps, an SM applies a warp pool and warp scheduler to manage the warp execution as highlighted in Figure 1.2. The warp pool records the context of all running warps. At each cycle, the warp scheduler selects a ready warp from the warp pool to be issued and executed. The warp scheduler orders the warp execution based on its warp scheduling algorithm. For example, with the baseline round robin (RR) scheduling policy, the warp scheduler iteratively selects a warp from the warp pool to executed as illustrated in Figure 3.1. While the warp execution is interleaved, the warp execution latency can be hidden. For example, in Figure 3.1, a warp is selected to be execute every four cycles. Any operation with a latency fewer than 4 cycles will be hidden well and not affect the pipeline throughput.

## 3.2 GPU Latency Hiding Ability

At every cycle, GPU's warp scheduler selects an available warp from the warp pool for execution as discussed in Chapter 3.1. If there is a ready instruction in the selected warp's instruction buffer without any pipeline hazards, the warp is ready for execution; otherwise, the selected warp stalls. By interleaving the execution of warps, GPU can hide the warp stall cycles and maximize the computation throughput. However, GPUs are not always able to achieve a high throughput. To understand this sub-optimal performance problem, I delve deep to investigate GPU's latency hiding ability.

## 3.2.1 Factors Stalling Warp Execution

In order to evaluate the effectiveness of the modern GPU's latency hiding ability, I first need to identify the sources of warp execution time delays. In the following, I explain each of the potential factors that can delay a warp's instruction from getting executed:

1. Warp Scheduling Delay. At every cycle, the warp scheduler selects a warp for execution based on the warp scheduling policy. In the baseline GPU architecture, a fair round robin (RR) scheduler is employed to select warps in the warp pool. For instance, if there are 48 active warps in the warp pool, the RR warp scheduler will iterate over the 48 warps cycle-by-cycle to issue one instruction per warp. A warp is selected for instruction issue and execution every 48 cycles and will have up to 47 cycles delay from the RR scheduling policy to hide any stall cycle from itself.

- 2. Instruction Buffer and Instruction Cache Miss. In order to store instructions fetched from the instruction cache, each warp has an instruction buffer. When a warp selected for execution has no valid instruction in its instruction buffer, additional latency penalty is paid due to the empty instruction buffer caused by instruction cache misses.

- 3. Structural Hazard. If there is an available instruction in the selected warp's instruction buffer, the instruction will be placed in the scoreboard while also accessing the source operands in the register file. This is when structural hazards caused by contentions in the register file banks and at the various functional units are examined. If the decoded instruction cannot proceed for execution due to the unavailability of the register file bank or due to the unavailability of the register file bank or due to the unavailability of the register file bank or due to the unavailability of the register file bank or due to the unavailability of the register file bank or due to the unavailability of the register file bank or due to the unavailability of the register file bank or due to the unavailability of the register file bank or due to the unavailability of the register file bank or due to the unavailability of the register file bank or due to the unavailability of the register file bank or due to the unavailability of the register file bank or due to the unavailability of the register file bank or due to the unavailability of the register file bank or due to the unavailability of the register file bank or due to the unavailability of the register file bank or due to the unavailability of the register file bank or due to the unavailability of the register file bank or due to the unavailability of the register file bank or due to the unavailability of the register file bank or due to the unavailability of the register file bank or due to the unavailability of the register file bank or due to the unavailability of the register file bank or due to the unavailability of the register file bank or due to the unavailability of the register file bank or due to the unavailability of the register file bank or due to the unavailability of the register file bank or due to the unavailability of the register file bank or due to the unavailability of the register file bank or due to the unavailability of the register file ban

- 4. Control Hazard. Unlike CMPs that are often equipped with advanced branch predictors, modern GPUs do not currently implement branch prediction logics and rely on the massive multithreading feature to overlap the latency caused by control hazards. However, it is possible for a warp to experience additional control hazard stalls. For example, if a branch or function call instruction falls onto the *taken* path for a particular warp, and there is no other active warp in the pool at this time instance to help hide the branch address resolution latency, the particular warp then has to spend additional cycle(s) until its target address is calculated.

- 5. Data Hazard. In addition to the stalls coming from structural and control hazards, data dependency can introduce additional penalty to an active warp. Currently, there is no data forwarding logics implemented in GPUs. Therefore, warps have to wait until data dependency is resolved before it can proceed execution. If an instruction is dependent on an older load instruction experiencing a cache miss, this particular dependent instruction will spend a significant amount of stall cycles until the data hazard is cleared.

- 6. MSHR and Data Cache Miss. Memory load and store instructions can experience additional stall cycles if the miss status holding registers (MSHRs) for the data cache are highly contended or if a data cache miss is encountered. Depending on the availability of the MSHRs and where the requested data resides, the amount of latency can vary.

- 7. Synchronization Primitives In addition to pipeline hazards, cache miss, and scheduling latencies, implicit and explicit synchronization primitives in GPU programs can make warp execution stall as well. This delay mainly comes from how the communication between the parallel warps is structured.

# 3.2.2 Latency Attribution Algorithm

In order to understand how the different stall factors can contribute to a warp's execution time, I develop a latency attribution algorithm to count and reason about where stall cycles come from for warps. Because latencies caused by the various stall factors can be significantly overlapped in GPUs, it is a challenging task to accurately and faithfully attribute stall cycles to the corresponding cause.

At every cycle, the warp scheduler looks for a ready warp by iterating over the active warps in the instruction issue stage at the GPU pipeline as illustrated in Al-

## Algorithm 1 The warp scheduler in GPUs.

| 1:  | 1: function WARPSCHEDULER                                             |  |  |  |

|-----|-----------------------------------------------------------------------|--|--|--|

| 2:  | while $NoReadyWarp$ AND $NotVisitedAllWarps$ do                       |  |  |  |

| 3:  | $\triangleright$ visiting the next warp based on the scheduling order |  |  |  |

| 4:  | $w \leftarrow nextWarp()$                                             |  |  |  |

| 5:  | probe(w)                                                              |  |  |  |

| 6:  | if $w$ is ready then                                                  |  |  |  |

| 7:  | $\triangleright$ executing the instruction from w $issue(w)$          |  |  |  |

| 8:  | end if                                                                |  |  |  |

| 9:  | end while                                                             |  |  |  |

| 10: | end function                                                          |  |  |  |

gorithm 1. For each of the visited warps, whether they are ready or not, I record the execution status of the warp by instrumenting the baseline warp scheduler's implementation with a monitoring function, called *probe()* (Line 5 in Algorithm 1). If the visited warp is not ready, the monitoring function will investigate the sources of stalls and update the corresponding latency counting logics; otherwise, the visited warp is ready for execution.

Next, I delve deeper into the monitoring function probe() and present the latency attribution algorithm. First, I calculate the time during which a warp does not execute any new instruction because of the scheduling policy (Line 3 – 5 in Algorithm 2). This is determined to be the difference between the time when a warp is checked and the time when this particular warp was last checked. The time difference signifies how long the selected warp needs to wait until it can potentially issue the next instruction, i.e., the scheduling delay.

After the scheduling latency is determined, the monitoring function next examines whether the selected warp is ready or not. If ready, the *w.Exec* counter is incremented

# Algorithm 2 The warp latency attribution function.

| 1: <b>f</b> | 1: function PROBE(w) $\triangleright$ w: context of the input warp |  |  |  |

|-------------|--------------------------------------------------------------------|--|--|--|

| 2:          | $\triangleright$ calculating the scheduling delay                  |  |  |  |

| 3:          | $t \leftarrow CurrTime - w.PrevTime$                               |  |  |  |

| 4:          | $w.Scheduling \leftarrow w.Scheduling + t$                         |  |  |  |

| 5:          | $w.PrevTime \leftarrow CurrTime$                                   |  |  |  |

| 6:          | $\mathbf{if}\ waiting at a synchronization barrier\ \mathbf{then}$ |  |  |  |

| 7:          | $w.Sync \leftarrow w.Sync + 1$                                     |  |  |  |

| 8:          | else if instruction buffer is empty then                           |  |  |  |

| 9:          | $w.Fetch \leftarrow w.Fetch + 1$                                   |  |  |  |

| 10:         | else if branchtaken then                                           |  |  |  |

| 11:         | $w.CtrlHazard \leftarrow w.CtrlHazard + 1$                         |  |  |  |

| 12:         | else if datadependencydetected then                                |  |  |  |

| 13:         | ${f if}\ caused by a data cachemiss\ {f then}$                     |  |  |  |

| 14:         | if $w.CurrPendingAddr \neq w.PrevPendingAddr$ then                 |  |  |  |

| 15:         | $w.DataHazard \leftarrow w.DataHazard + 1$                         |  |  |  |

| 16:         | $w. PrevPendingAddr \leftarrow w. CurrPendingAddr$                 |  |  |  |

| 17:         | else                                                               |  |  |  |

| 18:         | $w.DataCacheMiss \leftarrow w.DataCacheMiss + 1$                   |  |  |  |

| 19:         | end if                                                             |  |  |  |

| 20:         | else                                                               |  |  |  |

| 21:         | $w.DataHazard \leftarrow w.DataHazard + 1$                         |  |  |  |

| 22:         | end if                                                             |  |  |  |

23: else if functional unit una bailable then 24:  $w.StrlHazard \leftarrow w.StrlHazard + 1$ 25: else 26:  $w.Exec \leftarrow w.Exec + 1$ 27: end if 28: end function

(Line 26 in Algorithm 2). Otherwise, the monitoring function investigates the stall factors sequentially – synchronization primitives, no available instructions in the instruction buffer or instruction cache misses, control hazard, data hazard, data cache misses, and structural hazard. Because a warp can be stalled due to multiple stall factors at the same time (the latency hiding feature by the massive multithreading GPUs), I want to be cautious about not double-counting latencies overlapped by several stall factors. For example, if a warp stalls due to data dependency on an older, load instruction that misses in the data cache, I attribute only the first stall cycle to the data hazard factor and any additional, subsequent stall cycle(s) to the data cache miss factor. This is because the underlying reason for the warp stall is the data cache miss encountered by the previous cache miss. If there is no following dependent instruction on a previous load cache miss (while the cache miss is being serviced), this latency attribution algorithm does not attribute any stall cycle for this data cache miss. Therefore, it is important to note that the latency shown under the data cache miss category represents only the latency penalties that stall pipeline execution.

I also want to highlight that since GPUs rely on the fast context-switching between the massive number of available warps to improve pipeline utilization, even if a warp encounters no delay from pipeline hazards, memory accesses, or synchronization overhead, it still suffers from delays caused by the scheduling policy. For

| Architecture              | NVIDIA Fermi GTX480             |

|---------------------------|---------------------------------|

| Num. of SMs               | 15                              |

| Max. # of Warps per SM    | 48                              |

| Max. # of Blocks per SM   | 8                               |

| Num. of Schedulers per SM | 2                               |

| Num. of Registers per SM  | 32768                           |

| Shared Memory             | 48KB                            |

| L1 Data Cache             | 16KB per SM (32-sets/4-ways)    |

| L1 Inst Cache             | 2KB per SM (4-sets/4-ways)      |

| L2 Cache                  | 768KB (64-sets/16-ways/6-banks) |