# Radiation Hardened by Design Methodologies for Soft-Error Mitigated

Digital Architectures

by

Chandarasekaran Ramamurthy

A Dissertation Presented in Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy

Approved July 2017 by the Graduate Supervisory Committee:

Lawrence Clark, Chair David Allee Bertan Bakkaloglu Keith Holbert

ARIZONA STATE UNIVERSITY

August 2017

#### **ABSTRACT**

Digital architectures for data encryption, processing, clock synthesis, data transfer, etc. are susceptible to radiation induced soft errors due to charge collection in complementary metal oxide semiconductor (CMOS) integrated circuits (ICs). Radiation hardening by design (RHBD) techniques such as double modular redundancy (DMR) and triple modular redundancy (TMR) are used for error detection and correction respectively in such architectures. Multiple node charge collection (MNCC) causes domain crossing errors (DCE) which can render the redundancy ineffectual. This dissertation describes techniques to ensure DCE mitigation with statistical confidence for various designs. Both sequential and combinatorial logic are separated using these custom and computer aided design (CAD) methodologies.

Radiation vulnerability and design overhead are studied on VLSI sub-systems including an advanced encryption standard (AES) which is DCE mitigated using module level coarse separation on a 90-nm process with 99.999% DCE mitigation. A radiation hardened microprocessor (HERMES2) is implemented in both 90-nm and 55-nm technologies with an interleaved separation methodology with 99.99% DCE mitigation while achieving 4.9% increased cell density, 28.5 % reduced routing and 5.6% reduced power dissipation over the module fences implementation. A DMR register-file (RF) is implemented in 55 nm process and used in the HERMES2 microprocessor. The RF array custom design and the decoders APR designed are explored with a focus on design cycle time. Quality of results (QOR) is studied from power, performance, area and reliability (PPAR) perspective to ascertain the improvement over other design techniques.

A radiation hardened all-digital multiplying pulsed digital delay line (DDL) is designed for double data rate (DDR2/3) applications for data eye centering during high

speed off-chip data transfer. The effect of noise, radiation particle strikes and statistical variation on the designed DDL are studied in detail. The design achieves the best in class 22.4 ps peak-to-peak jitter, 100-850 MHz range at 14 pJ/cycle energy consumption. Vulnerability of the non-hardened design is characterized and portions of the redundant DDL are separated in custom and auto-place and route (APR). Thus, a range of designs for mission critical applications are implemented using methodologies proposed in this work and their potential PPAR benefits explored in detail.

# DEDICATION

To my parents Vijayalakshmi and T.R. Ramamurthy

#### ACKNOWLEDGMENTS

I would like to express my gratitude to the various individuals who helped and supported me throughout the duration of my doctorate.

Firstly, I would like to thank my mother Vijayalakshmi Ramamurthy, for inculcating patience and curiosity, and my father T.R. Ramamurthy for inculcating creativity and steadfastness in me. Their support has been instrumental during the course of my studies as I manoeuvred various challenges.

The Indian tradition of "guru-shishya parampara" or student-teacher lineage states that 'the genuineness of the guru (teacher), and the respect, commitment, devotion and obedience of the shishya (student), is the best way for subtle or advanced knowledge to be conveyed'. In the same vein I would like to thank Professor Lawrence T. Clark for being my mentor during this PhD. I would also like to thank Professors David Allee, Bertan Bakkaloglu and Keith Holbert for being part of my committee and providing valuable feedback.

I want to thank my colleagues Srivatsan Chellappa, Sandeep Shambhulingiah, Vinay Vashishtha, Sushil Kumar, Aditya Gujja, Lovish Masand, Ankita Dosi, Parshant Rana, Chris Lieb, Dan Patterson, Nathan Hindman, Satendra Maurya and Jerin Xavier for the discussions, brainstorming sessions and contributions which helped me achieve my doctoral degree goals. I would like to thank the administrative staff at the electrical engineering department, Toni, Lynn, Jenna, Esther and Donna for their support and help. I would also like to thank Angelica Campos for her emotional support and encouragement.

Finally I would like to thank the 'higher power' that makes our 'pale blue dot' tick because it's the recognition of our insignificance that gives our lives purpose and focus.

# TABLE OF CONTENTS

|                                                                 | Page |

|-----------------------------------------------------------------|------|

| LIST OF TABLES                                                  | ix   |

| LIST OF FIGURES                                                 | X    |

| CHAPTER                                                         |      |

| 1. INTRODUCTION                                                 | 1    |

| 1.1. Introduction                                               | 1    |

| 1.2. Space Weather and Radiation Environment                    | 2    |

| 1.3. Radiation Effects on CMOS devices                          | 5    |

| 1.4. Single Event Effects                                       | 7    |

| 1.5. Scaling and SER                                            | 14   |

| 1.6. Radiation Hardening                                        | 21   |

| 1.7. Multiple Node Charge Collection (MNCC) and Domain Crossing |      |

| Errors (DCE)                                                    | 25   |

| 1.8. MNCC Separation in CAD Flows                               | 27   |

| 1.9. Summary                                                    | 31   |

| 2. MODULE LEVEL SEPARATION: AES                                 | 33   |

| 2.1. Introduction                                               | 33   |

| 2.2. AES Encryption Background.                                 | 33   |

| 2.3. TMR Pulse-clocked Latch for RHBD                           | 40   |

| CHAPTER                                         | Page |

|-------------------------------------------------|------|

| 2.4. Pulsed Latch Operation                     | 45   |

| 2.5. Module Level Separation CAD Flow           | 47   |

| 2.6. Spatial Separation Analysis                | 55   |

| 2.7. Test Chip Implementation                   | 57   |

| 2.8. Error Injection Simulation Validation      | 59   |

| 2.9. Experimental Setup and Silicon Validation  | 60   |

| 2.10. Design Comparison                         | 63   |

| 2.11. Summary                                   | 64   |

| 3. INTERLEAVED SEPARATION: HERMES               | 66   |

| 3.1. Introduction                               | 66   |

| 3.2. HERMES Background                          | 67   |

| 3.3. Improved Interleaved Separation            | 70   |

| 3.4. ReAPR Co-design methodology                | 76   |

| 3.5. Implementation                             | 86   |

| 3.6. Reliability Analysis and Radiation Testing | 88   |

| 3.7. Summary                                    | 93   |

| 4. RADIATION HARDENED PULSED MULTIPLYING DLL    | 95   |

| 4.1. Introduction                               | 95   |

| 4.2. Delay Locked Loop Background               | 95   |

| 4.3. Radiation Hardened Pulsed Multiplying DLL  | 99   |

| 4.4. Decoding Logic                             | 111  |

| CHAPTER                                              | Page |

|------------------------------------------------------|------|

| 4.5. Control (Acquisition and Tracking) Logic Design | 117  |

| 4.6. Functional Logic Simulations                    | 131  |

| 4.7. Process Variability                             | 134  |

| 4.8. Circuit Simulations and Critical Timing         | 139  |

| 4.9. Performance Overview                            | 144  |

| 4.10. Soft-Error vulnerability                       | 148  |

| 4.11. TC 25 55-nm Test-chip Structures and Results   | 151  |

| 4.12. TC23 90 nm Test Results                        | 154  |

| 4.13. Performance summary and comparison.            | 159  |

| 4.14. Summary                                        | 160  |

| 5. DMR SEMI-CUSTOM DESIGN FLOW: REGISTER-FILE        | 161  |

| 5.1. Introduction                                    | 161  |

| 5.2. DMR Registerfile Background                     | 161  |

| 5.3. DMR RF Circuit Design                           | 164  |

| 5.4. Well-bias for Body Control                      | 169  |

| 5.5. RF Column Design                                | 170  |

| 5.6. Decoder Synthesis APR design                    | 172  |

| 5.7. Checker Circuits                                | 177  |

| 5.8. Performance Overview                            | 179  |

| 5.9. Implementation Summary                          | 182  |

| 5.10. Summary                                        | 183  |

| CHAPTER       | Page |

|---------------|------|

| 6. CONCLUSION | 184  |

| REFERENCES    | 187  |

# LIST OF TABLES

| Table                                                                                       |

|---------------------------------------------------------------------------------------------|

| 2.i Design Metric Comparison of the Proposed Implementation to Standard Flip-Flop And       |

| Temporal 4CE FF Based Designs. 63                                                           |

| 3.i: Dumbell (Large Fences), Interleaved Fences and Unhardened AES Design Metric            |

| Summary 72                                                                                  |

| 3.ii. Radiation Testing Results and Nodal Separation Summary                                |

| 3.iii HERMES2 (90 nm) [Farn16] Proton Beam Testing Results with the Errors                  |

| Summarized by Unit/Operation, Error Cross-Section with Statistical Bounds are 93            |

| 4.i. Specification Comparison of DDR, DDR2 and DDR3 Memories                                |

| 4.ii (a) DDR Clock Specifications and the Length of the Delay Line Required (B) Number      |

| Of Delay Lines and the Distance Between Individual Pulses Based on DDR2 And DDR3            |

| Mode across Corners                                                                         |

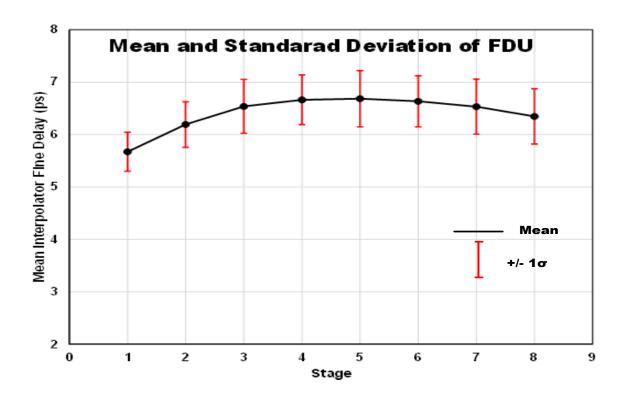

| 4.iii Fine Delay Unit Delay Statistics for an Interpolate By 8. Mean and Standard Deviation |

| are Shown Extracted from Monte Carlo Simulations                                            |

| 4.iv. ADPMDLL Performance Summary and Comparison with Previous Radiation                    |

| Hardened DLLs. 159                                                                          |

| 5.i Comparison of Characterized and Simulated Delays for the Register File                  |

# LIST OF FIGURES

| Figure                                                                                   |

|------------------------------------------------------------------------------------------|

| 1.1. Cartoon Showing the Space Radiation Environment (Courtesy of NASA,                  |

| www.meted.Ucar.Edu)                                                                      |

| 1.2 Galactic Cosmic Radiation Dose Rate Variance with Latitude and Solar Cycle           |

| (Courtesy of NASA, www.meted.Ucar.Edu)                                                   |

| 1.3. (a) Ion Strike at the Output of a CMOS (Metal and Gate Connectivity not Shown). (b) |

| Funnel Formation and Charge Collections Mechanisms in the Semiconductor Following        |

| an Ion Strike.                                                                           |

| 1.4. A Single Event Transient Manifesting on a Combinational Portion of a CMOS Circuit.  |

| Collection of Charge and the Change in the State of the Node Capacitance Cl and the      |

| Current Steering Mechanism as a Function of the Restoring PMOS after [Koba09] 10         |

| 1.5. A Single Event Upset Due to Radiation Strike on the Storage Node in a Latch, the    |

| Storage Feedback is Upset as the Two Node Reach the Stable Erroneous (10) State from     |

| the (01) State                                                                           |

| 1.6. SET Cross Section with Scaling on Planar Technologies [Bene06], SET Pulse Width     |

| Increases as We Scale Due to the Reduction in the Nodal Capacitance and Operating        |

| Voltages.                                                                                |

| 1.7. Critical Charge Reduction Trend with Different Technology Nodes for the Intel       |

| Foundry Technology, after [Seif15].                                                      |

| 1.8. (a)[Seif15], (b)[Fang16], (c)[Oldi15] and (d)[Lee15] Planar and Finfet SER/SEUCross |

| Section/Failure in Time Measurement from Different Technology Foundries with             |

| Enhanced SER Reduction over Planar Technologies                                          |

| Figure                                                                                     |

|--------------------------------------------------------------------------------------------|

| 1.9. Drain Depletion in a Finfet Technology Which is at a Distance of the Height of Subfin |

| away from the Substrate, Reducing Charge Collection Efficiency                             |

| 1.10. SER Increase with Number of Fins, 0-1, 1-0 Transition with Low and High Parasitic    |

| Bipolar Transistor Gain (B) are Shown, after [Seif15]                                      |

| 1.11. Onset of Charge Collection Amplification under Laser Irradiation with Increased      |

| Bipolar Gain Thereby Increase in SER at Lower Laser Energies is Shown, after [Seif15].     |

|                                                                                            |

| 1.12. (a) Cross Section and (b) Soft Error Rate as a Function of Clock Frequencies         |

| Measured in [Reed96] and [Seif12] Respectively. Increased Vulnerability with Increased     |

| Clock Frequency is Consistently Observed over Multiple Generations                         |

| 1.13. Triple Modular Redundancy (TMR) with Complete Triplication of Combinationa and       |

| Sequential Elements Ensuring Complete Mitigation with Minimal Timing Penalty, (b)          |

| Dual Modular Redundancy (DMR) Which Detects a Mismatch in the Copies to Set an Error       |

| Flag to Be Used by the Error Handler Ensuring Inhibition of Erroneous Signals and (c)      |

| Temporal Hardening Delaying Signals in Time to Ensure That the Set Gets Masked by          |

| Majority Voting. 22                                                                        |

| 1.14. (a) Multi-node Charge Collection Mitigation Cross Section Due to Nodal Separation    |

| by N-well, (b) MBU in FPGAS as Demonstrated in [Quin07] Leading to Dces and (c) CAD        |

| Methodology Based Separation of Multi-bit TMR Cells with Spacer Between Each Groups        |

| to Ensure That Even Non-equivalent Flops in Multiple Domains Cannot Be Upset with a        |

| Single Strike 24                                                                           |

| Figure                                                                                   |

|------------------------------------------------------------------------------------------|

| 1.15. Effective Cross Section Seen by an Ionizing Particle That Simultaneously Strikes   |

| Two Nodes a and B Causing Upset. Only a Limited Solid Angle Can Pass Through the         |

| Collection Region of Both Nodes, Providing a Straightforward Estimate of the Upset       |

| Probability, after [Sham14]26                                                            |

| 1.16. A Method of CAD Based Critical Component Separation of CMOS Gates by Using         |

| Critical Spacing Rules (E.G. 5 Mm) Recursively, after [Klei10]                           |

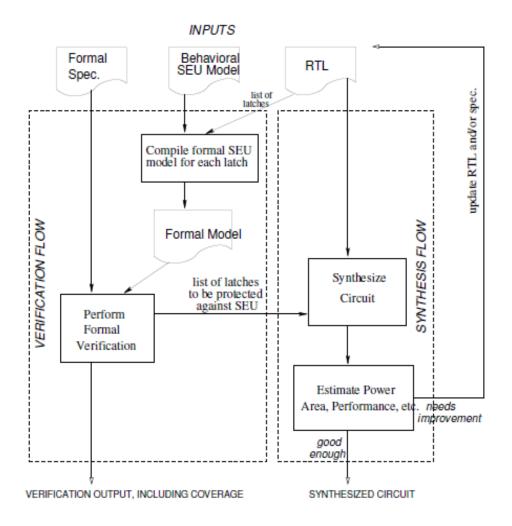

| 1.17. Verification Based SEUEstimation and Selective Hardening in Synthesis Step, after  |

| [Sesh06]                                                                                 |

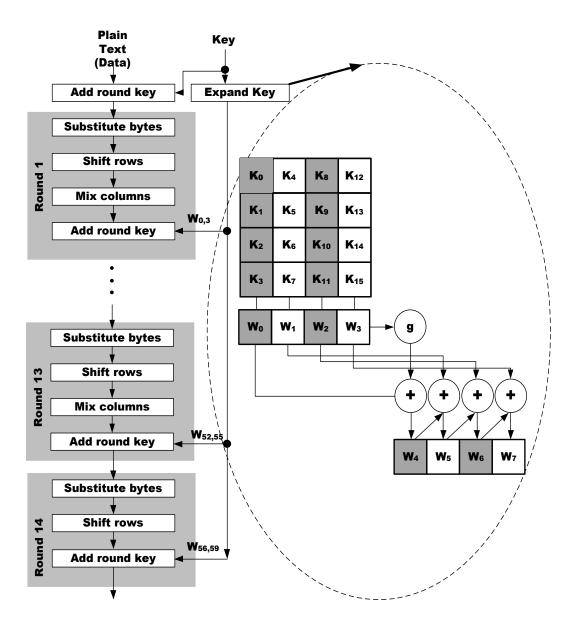

| 2.1. AES Engine Algorithm Showing 14 Rounds for a 256 Bit Key Design, Expand Key         |

| Stage Which Creates the Key for Each round to Be Added in Add round Key Step is Shown    |

| in the Dotted Circle.                                                                    |

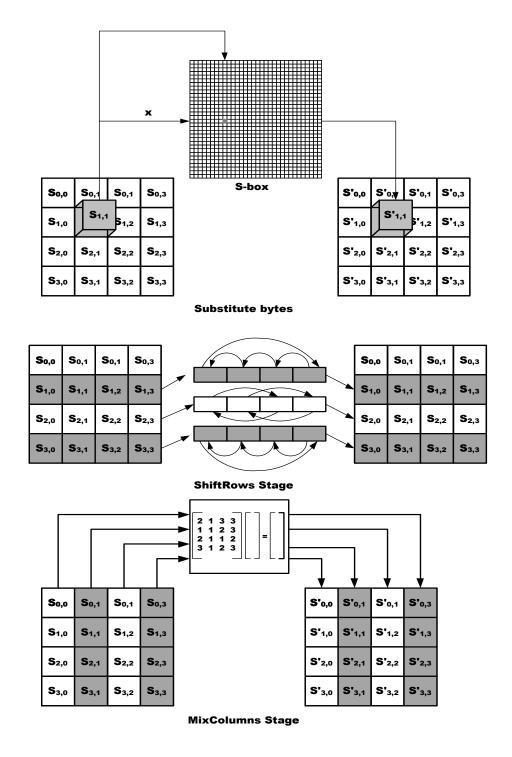

| 2.2. AES Transformations, Substitute Bytes, Shift Rows and Mix Column Stages are Done    |

| on the Input Stage Matrix. Sbox is Shown in the Substitute Bytes Transformation 37       |

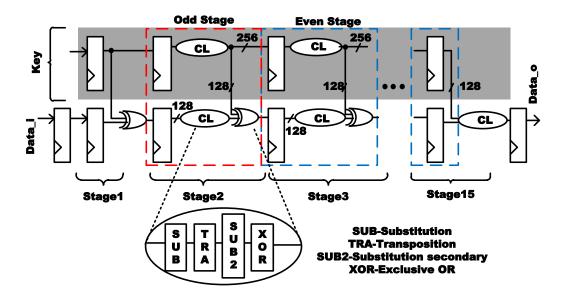

| 2.3. Advanced Encryption Standard Architecture as Implemented. It is Pipelined over 15   |

| Stages for High-speed Operation. Transformations by the Combinational Logic (Cl) are     |

| Shown in Boxes. 39                                                                       |

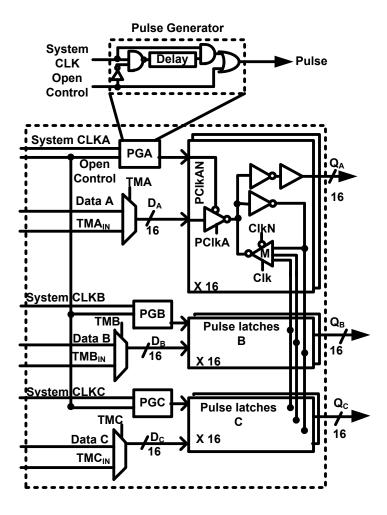

| 2.4 Schematic of Self-correcting Pulse-clocked Latches and Pulse Generators.             |

| Multiplexers Select Between Data and Test Mode Input, Majority Voting Internal Nodes     |

| (Maj_a, Maj_b and Maj_c) are Also Marked                                                 |

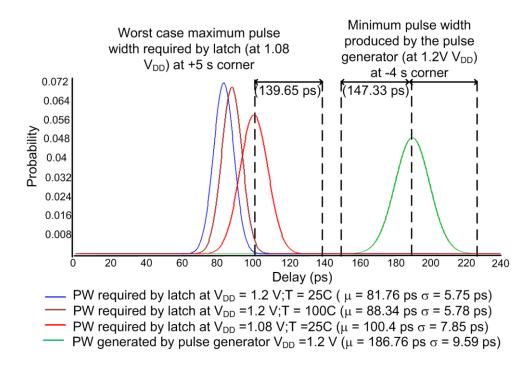

| 2.5 Statistical Analysis of the Pulse Latch and Pulse Generator Showing Worst-case Pulse |

| Width for Proper Data Capture Mean and Sigma as Well as Pulse Generator Variation as     |

| Determined by Mc Simulation                                                              |

| Figure                                                                                  |

|-----------------------------------------------------------------------------------------|

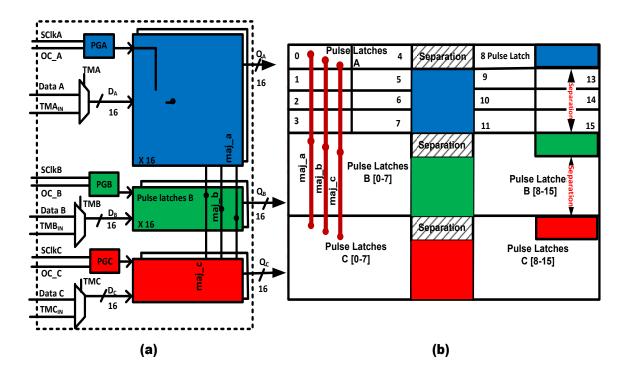

| 2.6 Color Coded Schematic (a) and Layout (b) of the 16-bit, TMR Pulse Latch Design with |

| 3 Domains (A-blue, B-green and C-red) Highlighted. Latches and the Shared Pulse         |

| Generator are Shown. The Spatial Separation Incorporated Which Makes the Layout Dce     |

| Immune                                                                                  |

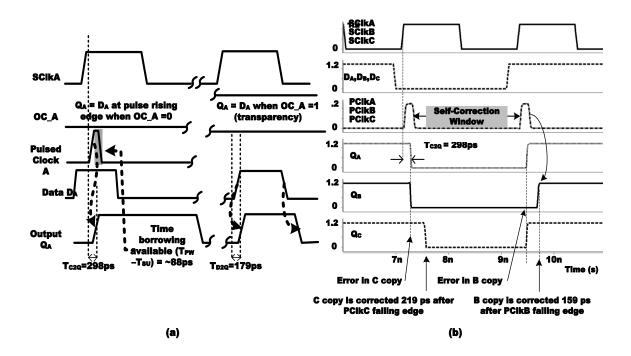

| 2.7 (a) Pulse-latch Operation with Nominal Pulse Width and Decision Window Timings      |

| (Tc2q and Td2q). Nominal Time Borrowing of 88 Ps is Afforded by the Design. (b) Self-   |

| correction in the TMR Latch is Shown with an Error in the C Copy, the Onset of the      |

| Negative Edge of the Clock Pulse Initiates Correction. Correction Window is a Function  |

| of the Slack Afforded in Path is Question and Varies Accordingly                        |

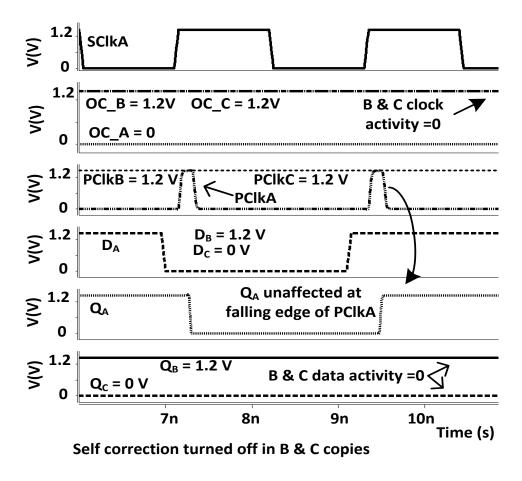

| 2.8 Non-redundant Mode Operation with Data Db and Dc Held at 1 and 0 Respectively       |

| with Open-control Set to Transparent. 46                                                |

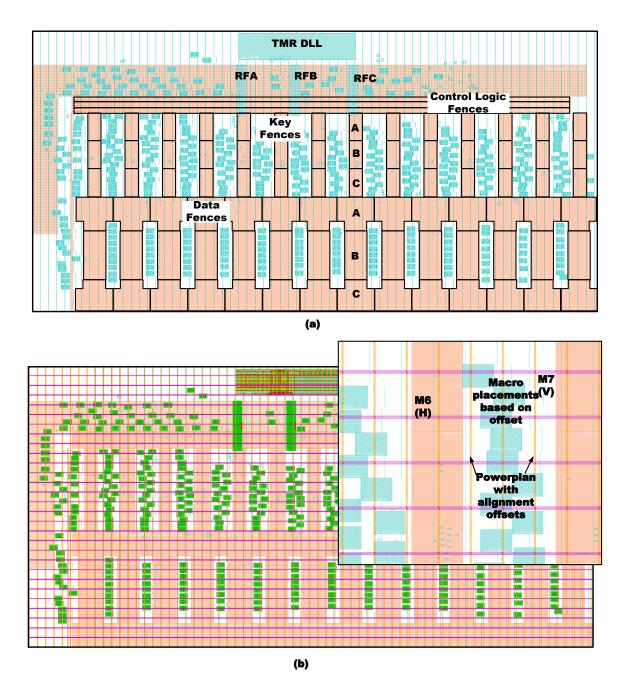

| 2.9 RHBD CAD Module Level Separation Using Large Fences, Complete Separation of         |

| Custom, APR (Combinational and Clock) Portions is Achieved to Create a Dce Immune       |

| Design                                                                                  |

| 2.10 RHBD CAD Module Level Separation Using Large Fences, Complete Separation of        |

| Custom, APR (Combinational and Clock) Portions is Achieved to Create a Dce Immune       |

| Design                                                                                  |

| 2.11 Timing Waveforms of Self-correction in the Pulse-latch. C Copy is Corrected to 0   |

| after 340.1 Ps. B Copy is Corrected to 1 after 202.8 Ps                                 |

| 2.12 Timing Waveforms of Self-correction in the Pulse-latch. C Copy is Corrected to C   |

| after 340.1 Ps. B Copy is Corrected to 1 after 202.8 Ps                                 |

| Figure                                                                                        |

|-----------------------------------------------------------------------------------------------|

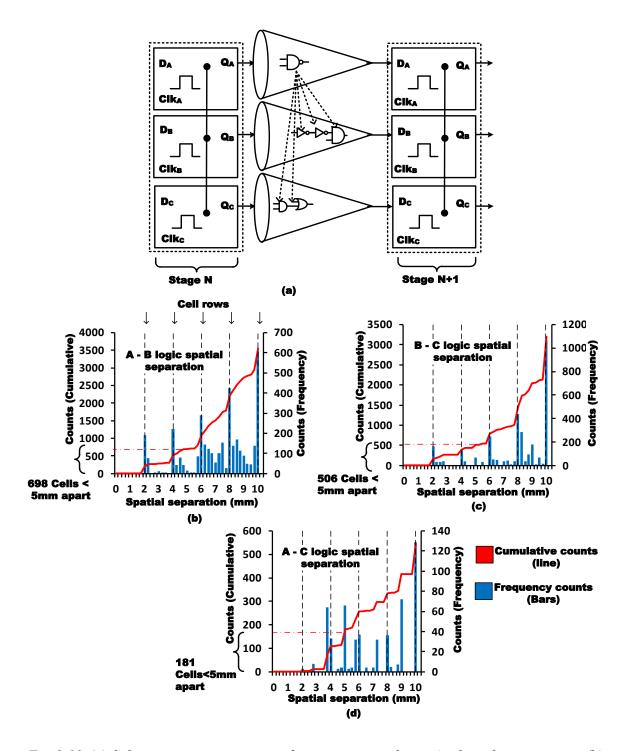

| 2.13 (a) Schematic Representation of Separation Analysis, Analysis Histograms in (b) Ab.      |

| (c) Bc and (d) Ac of Cell Separation Comparison for the Design Pipeline Shows Very Few        |

| Pairs Placed Without Adequate Separation. 54                                                  |

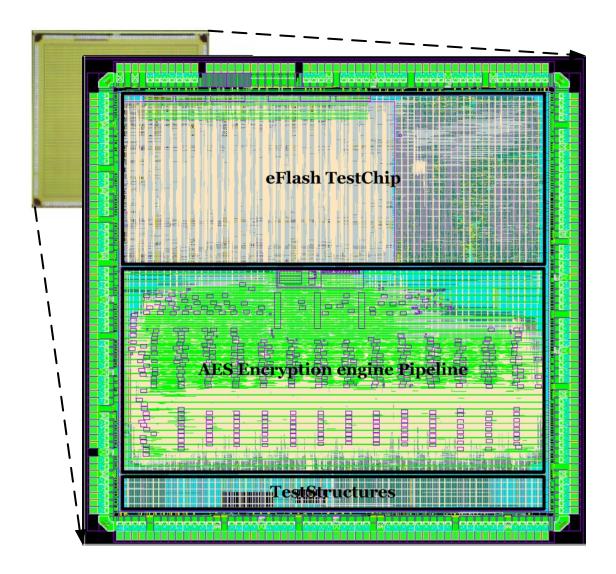

| 2.14 AES Implementation on a 4 by 4 Mm Die on a 90 Nm Process, the AES Design is              |

| Marked along with Other Structures in the Test Chip. Wire Bond I/O Pad Ring Consists of       |

| 211 I/O's                                                                                     |

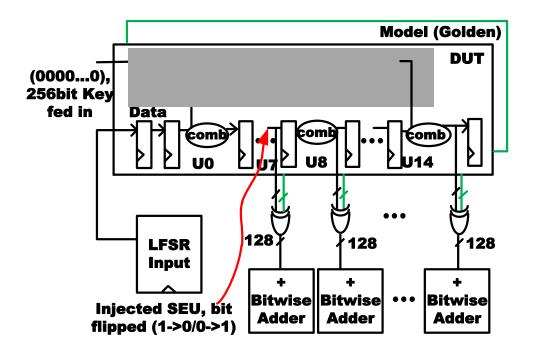

| 2.15 Error Injection Simulation Test Setup. Model and Device under Test are Shown. Error      |

| is Injected at the 8th Stage and Subsequent Stages are Observed for Error Propagation. Lfsr   |

| Generates the Inputs Data Bits and the Key is Constant                                        |

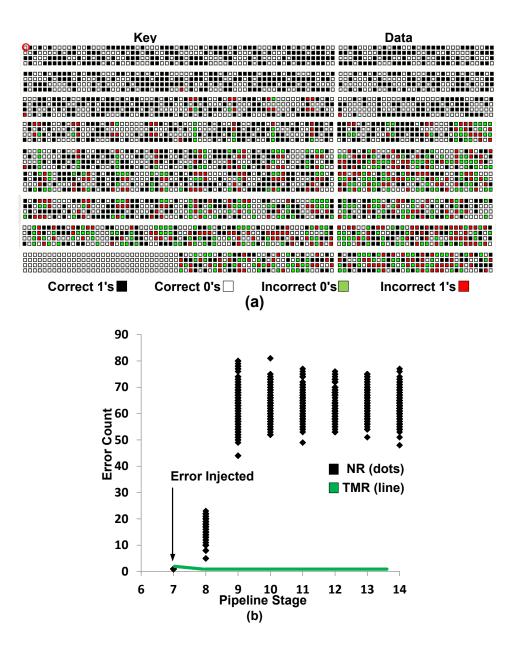

| 2.16 (a) Non-redundant AES Error Injection Graphical Representation Using Perl. Reds          |

| are Incorrect 1's and Green are Incorrect 0's, Correct 1's are in Black and 0's in White. (b) |

| Error Count per Pipeline Stage Plot Showing Correction Capability of TMR (Light Blue)         |

| Version and the Error Diffusion in Non-redundant Version (Black)                              |

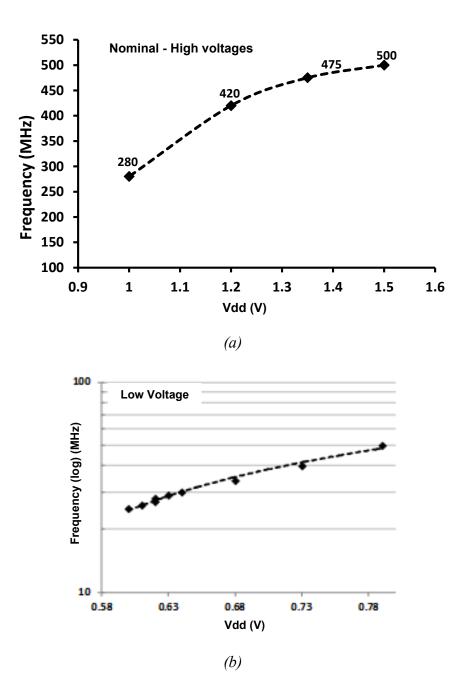

| 2.17 (a) Measured Test Chip Fmax Vs. Vdd at High Operating Voltages. The Upper Values         |

| are Measured Using the Psu Mode, (b) Measured Test Chip Fmax Vs. Vdd at Low                   |

| Operating Voltages. 60                                                                        |

| 2.18. Broad Beam Testing Setup at Uc Davis. The Cob Dut is Shown at the Top. The              |

| Controlling Fpga is at the Bottom, away from the Beam Track                                   |

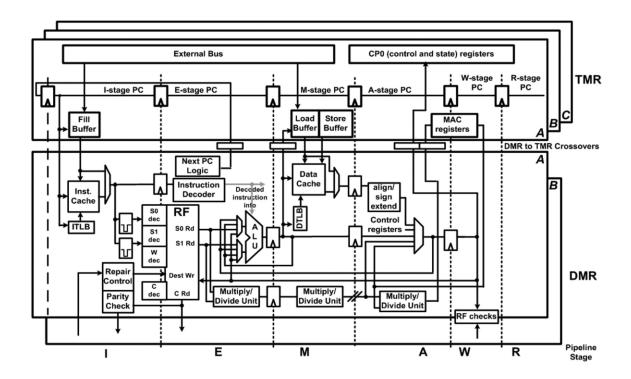

| 3.1. Hermes2 Architecture Block Diagram of a 6-stage with the Speculative DMR Pipeline        |

| and the Architectural TMR Architectural States. DMR to TMR Crossovers Logic is Also           |

| Shown (Also Implemented in TMR)                                                               |

| Figure                                                                                     |

|--------------------------------------------------------------------------------------------|

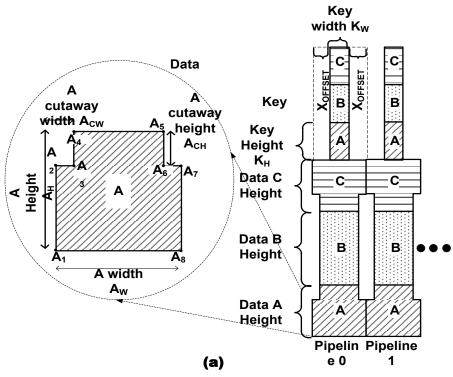

| 3.2. (a) Large Fence Module Separation Diagram Representation (b) Interleaved Fence        |

| Diagram Representation with a, B and C Fences (c) Sequential and Combinational Domain      |

| Mismatch If the Fence and the TMR Site Definitions are not Aligned in the Interleaved      |

| Fences Creating Potential SE Vulnerabilities. 69                                           |

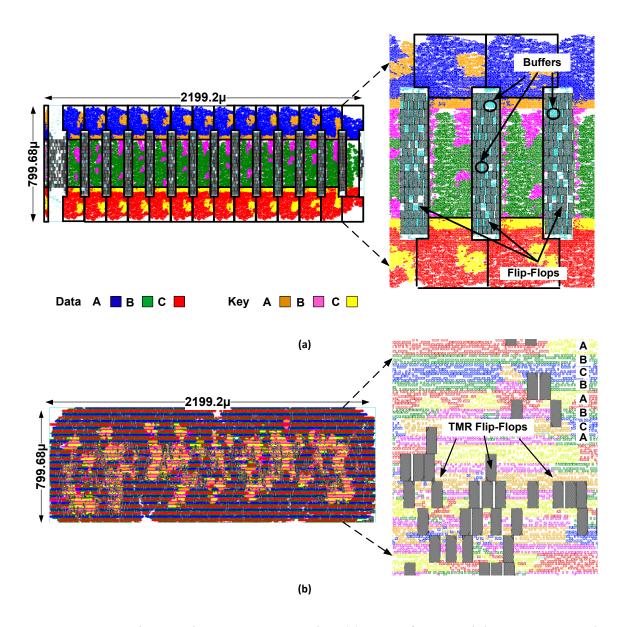

| 3.3. AES Implemented at 250 Mhz Speed in (a) Large Fence Module Separation with Key        |

| and Data Fence (b) Interleaved Fence Encounter Representation with Key and Data Mixed      |

| in the a, B and C TMR Domain Fences. Color Coding Pertaining to Key and Data a, B and      |

| C Domains is Shown. Both Designs are Implemented in the Same Area with the Same Flip-      |

| flops to Ensure Proper Apples to Apples Comparison                                         |

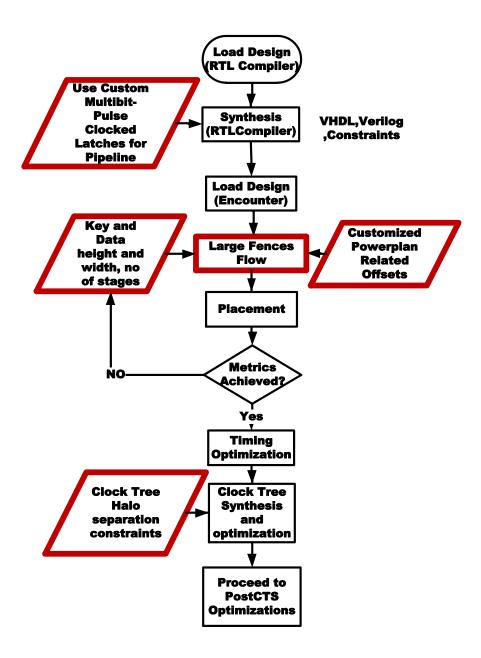

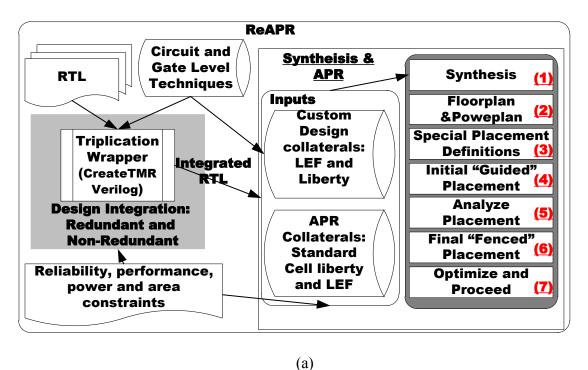

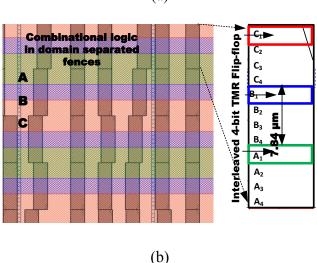

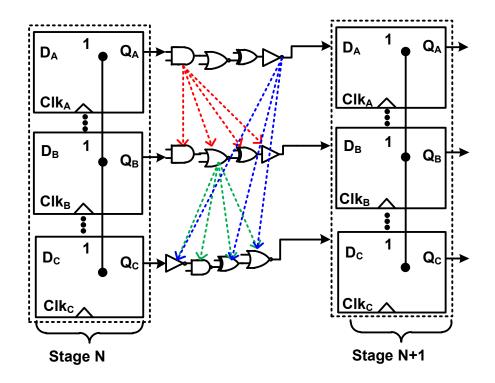

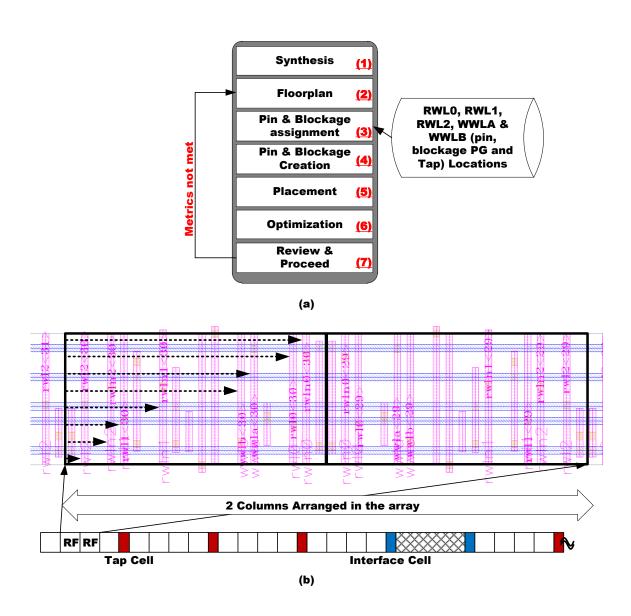

| 3.4. (a) ReAPR Flowchart with Steps to Create Domain Separated MNCC Mitigated Logic        |

| Required Inputs and APR Steps (1-7) are Elucidated. Domain Separated RTL is Created        |

| by the Triplication Wrapper and Synthesized Verilog is the Output from Synthesis (b)       |

| Domains Provide MNCC Induced SE Mitigation. The Multi-bit FFs Straddle Domains so          |

| the Associated Storage is in the Same Domain as Combinational Logic                        |

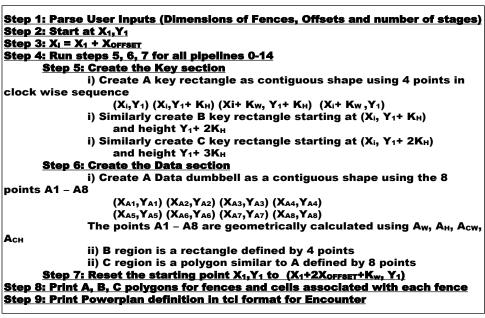

| 3.5. ReAPR Flow Place and Route Steps Described in a Pseudo Code, with the Specific        |

| Domain Separation Related Steps and Subroutines Post RTL Integration and Synthesis.77      |

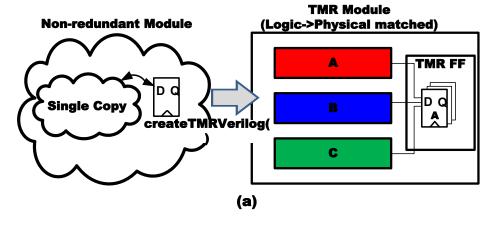

| 3.6. (a) Diagrammatic Representation of the TMR Verilog Creation with Physical Domain      |

| Matched to Logical Hierarchies (b) Pseudo Code for Creation of TMR Verilog by              |

| Triplication of Non-redundant Verilog. Output Verilog is Instantiated to Create Integrated |

| RTL/Verilog Design. 78                                                                     |

| Figure                                                                                  |

|-----------------------------------------------------------------------------------------|

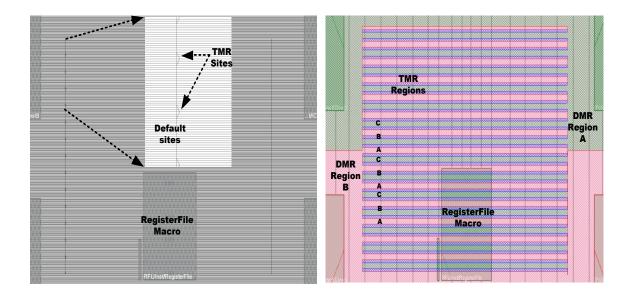

| 3.7. (a) 4 (a) Site Definitions for Multi-height TMR Cells and Default Cells. (b).Guide |

| Generation in the APR Environment, TMR and DMR Guides Can Be Seen Colored in Red        |

| (a), Blue (b) and Green (c).                                                            |

| 3.8. (a) Guided Initial Placement, TMR Flip-flops are Placed in the Correct TMR Sites.  |

| TMR and DMR Combinational Logic is Placed Based on Data Flow and Timing, but Not        |

| Domain Separated, (b) TMR Flip-flops are Fixed and the Guides are Converted to Fences   |

| Before the Fenced Placement Run Step (6).                                               |

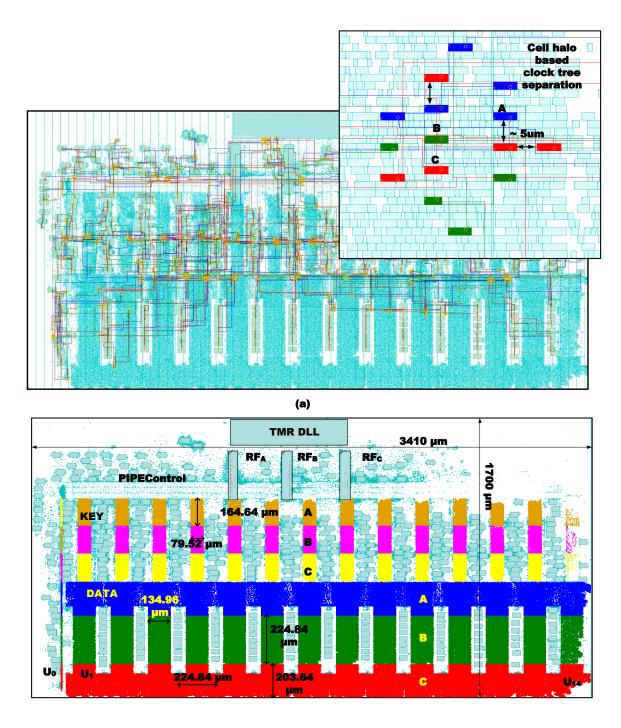

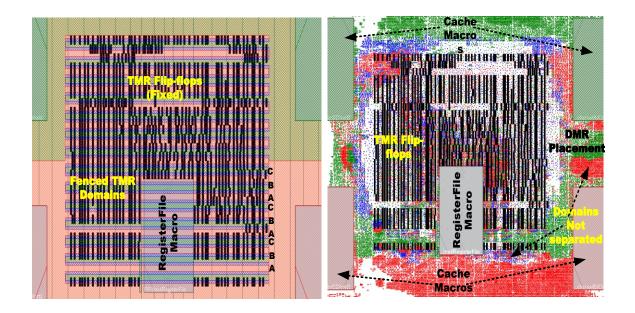

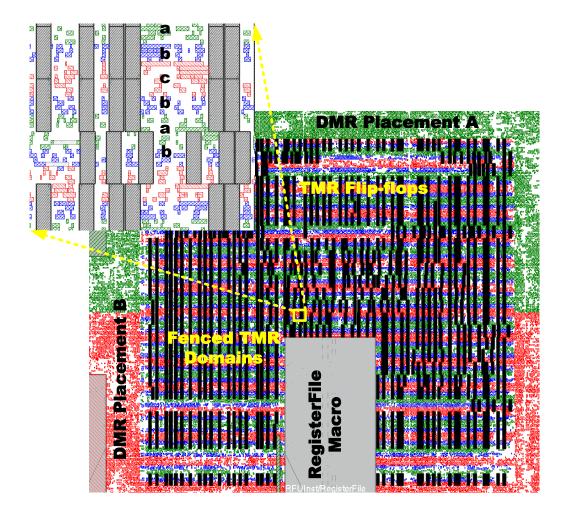

| 3.9. Complete Domain Separated Physical Placement Snapshot. The Zoomed Image Has        |

| the Color Coded a B and C Domains Placed Within 4 Cell Heights Tall Fenced Regions.     |

| DMR Placement Surround the TMR Placement in Fences Akin to the Large Fences of          |

| Chapter 2. Integrated Fences Thus Allows Placement of Redundant Logic with the Best     |

| Possible Ppa. 83                                                                        |

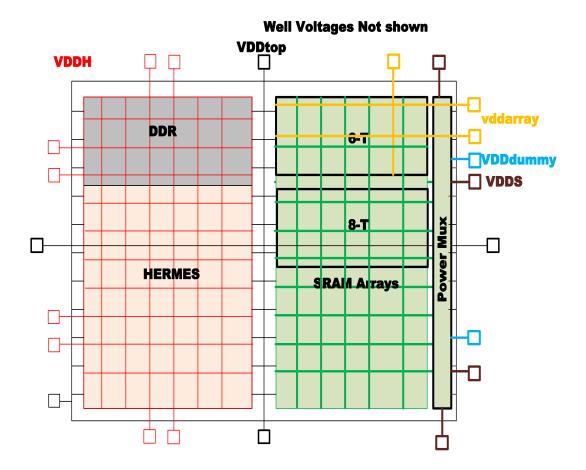

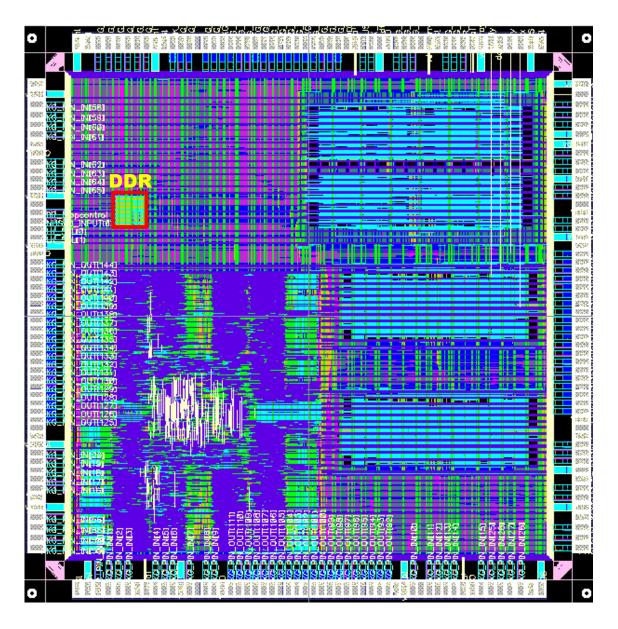

| 3.10. Tc25 Top Level Floorplan Diagram with Different Power Domains That Exist in the   |

| Chip. The Design Constituents with Their Approximate Placement Location with Respect    |

| to the Chip Origin is Shown. Other Design Constituents in the Chip are Sram Arrays for  |

| Process Variation Study. 85                                                             |

| 3.11. (a) Large Fence Module Separation Diagram Representation (b) Interleaved Fence    |

| Diagram Representation with a, B and C Fences (c) Sequential and Combinational Domain   |

| Mismatch If the Fence and the TMR Site Definitions are not Aligned in the Interleaved   |

| Fences Creating Potential SE Vulnerabilities                                            |

| Figure                                                                                    |

|-------------------------------------------------------------------------------------------|

| 3.12. Spatial Separation Analysis Schematic View, a, B and C Paths to the Redundant Flip- |

| flops are Queried and Their Separation is Analyzed for Cells Spacing Less than 4 Standard |

| Cell Heights (6.48 Um). This is Repeated for All of the Design Flip-flops                 |

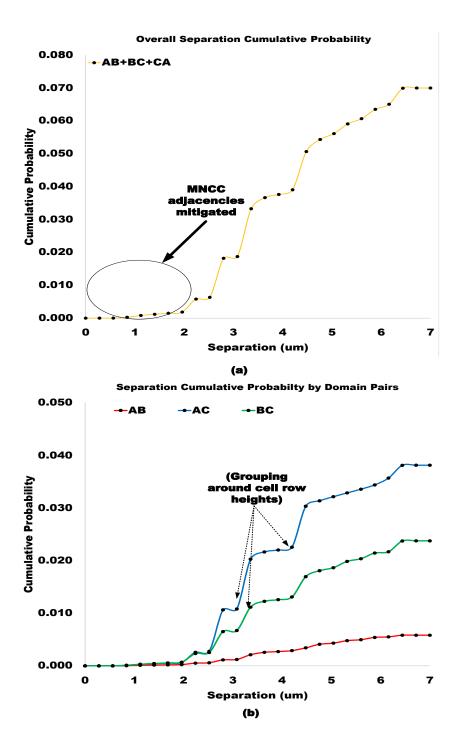

| 3.13. (a) Cumulative Probability of the Spatial Separation Analysis Showing 99.86 % Cells |

| Protected from MNCC Upsets up to a Span of ~ 3um. (b) Ab, Bc and Ac Comparison            |

| Cumulative Probabilities with the Ac and Bc Cell Adjacencies Higher than the Ab           |

| Adjacencies Due to the Size and the Form-factors of the Designed Fences                   |

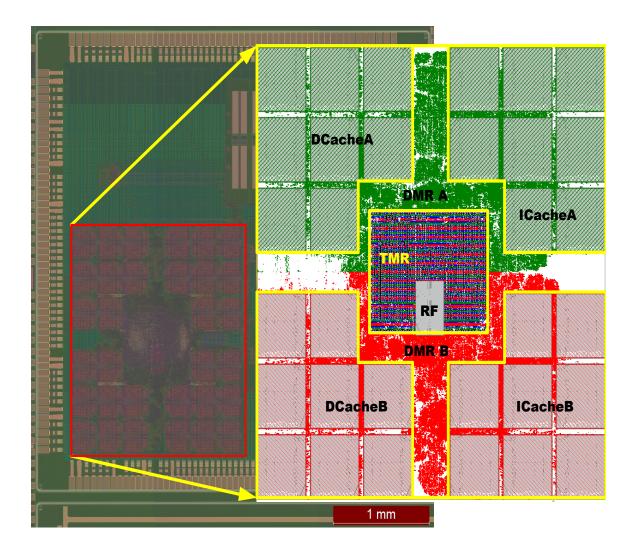

| 3.14. 90 Nm Implementation of Hermes2 [Farn16], TMR and DMR Regions are                   |

| Highlighted, the Base Version of the Interleaved Serpentine Flow is Used to Implement     |

| the Design. The Design Was Tested Using Proton Radiation at Uc Davis 63 Mev Cyclotron     |

| Beam. 92                                                                                  |

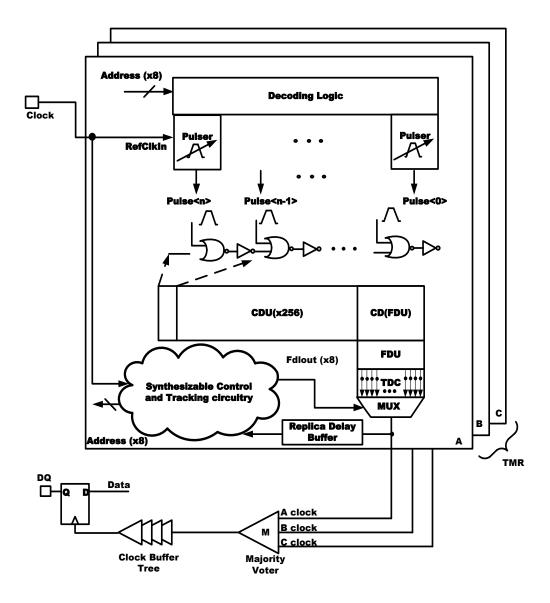

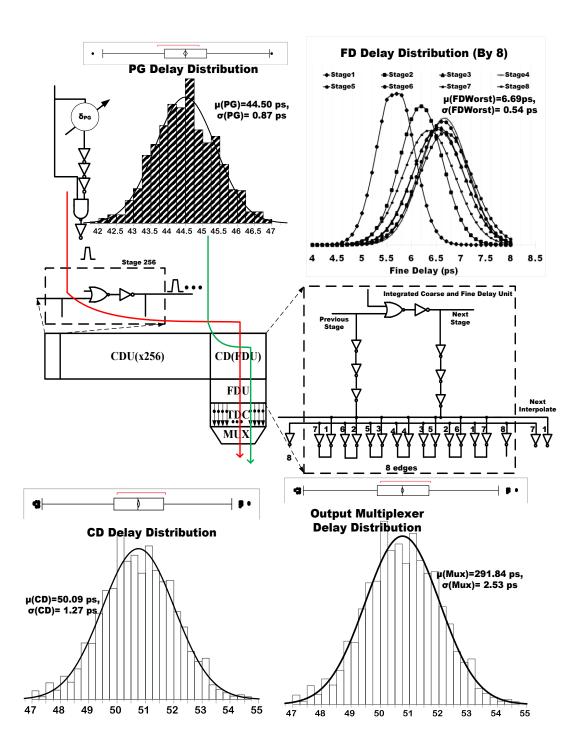

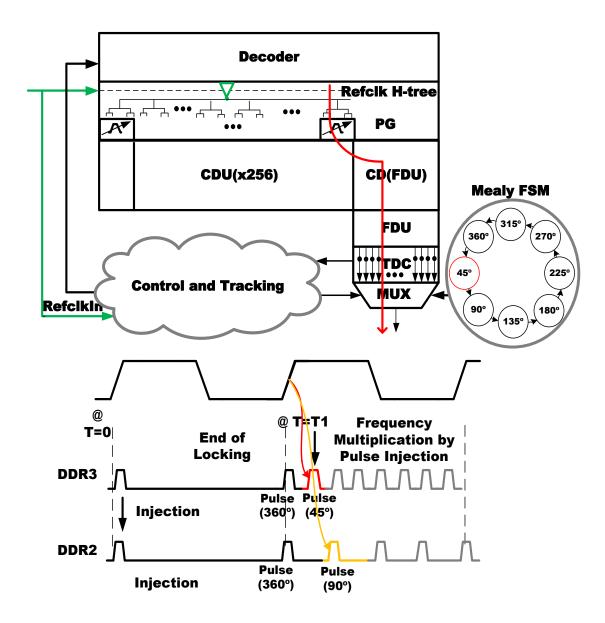

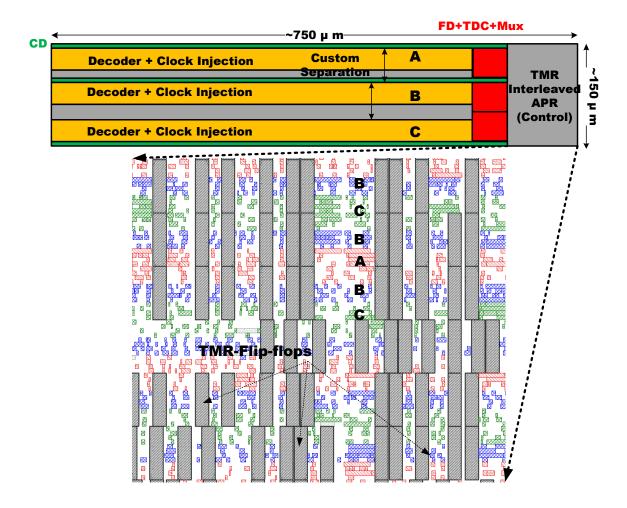

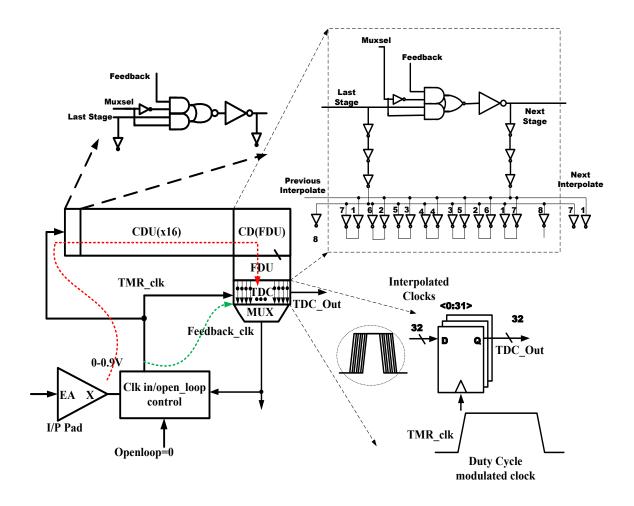

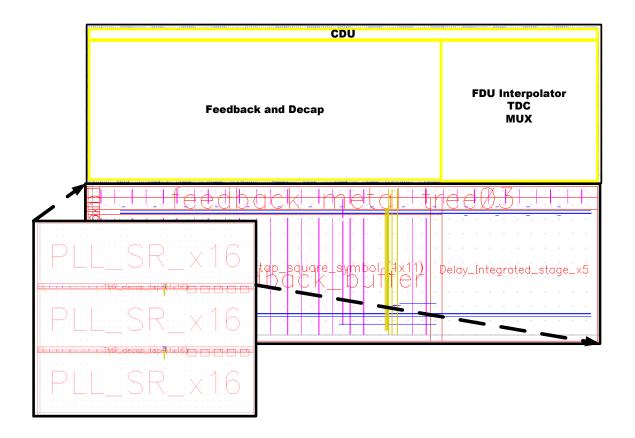

| 4.1. Top Level Architecture of the Radiation Hardened All-digital Dll Implementation      |

| Three Clocks are Generated and Voted out to Create the Soft-error Free Clock Which        |

| Clocks the Data in the Dram Capture Path (Dq)                                             |

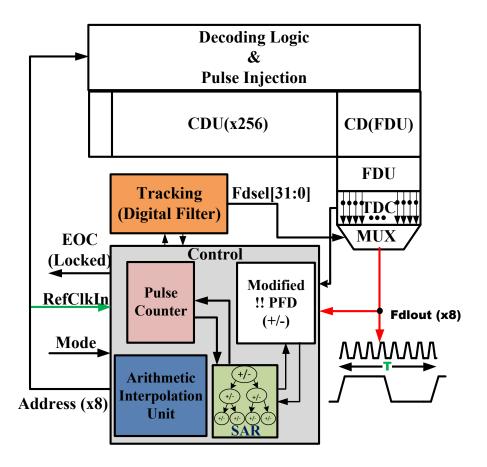

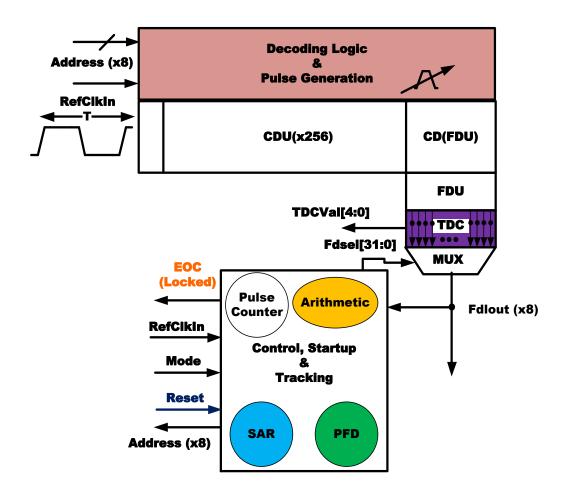

| 4.2. ADPMDLL Architecture Showing the Digital Delay Line Consisting of Coarse and         |

| Fine Delay Units (Cdu and Fdu). A Bang-bang Phase Detector and Tdc are Used to            |

| Calculate Phase Difference in Locking and Tracking Mode, Respectively. Control Unit       |

| Constituents are Also Shown. 101                                                          |

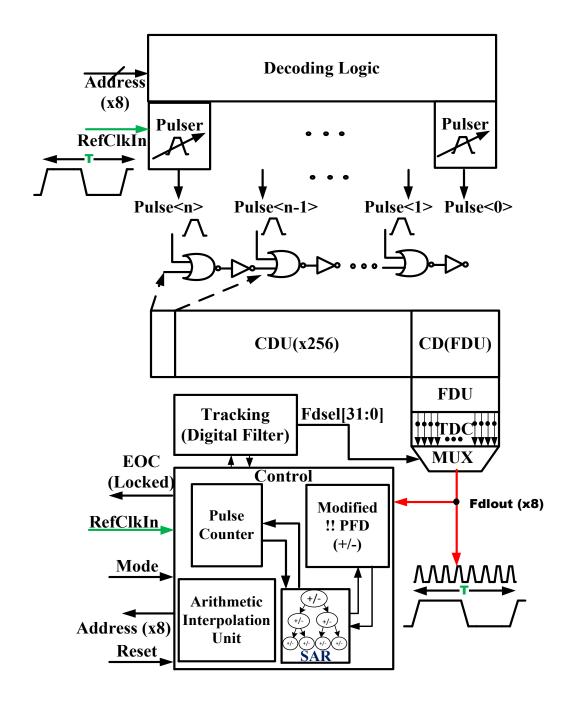

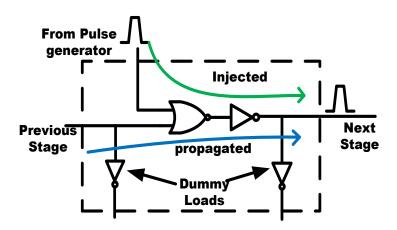

| 4.3. ADPMDLL Coarse Delay Unit is Shown, Propagating and Injecting Path are               |

| Highlighted in Blue and Green, Respectively. Dummy Loads Ensure Matched Slews             |

| Across the Coarse Delay and Fine Delay Chain                                              |

| Figure                                                                                   |

|------------------------------------------------------------------------------------------|

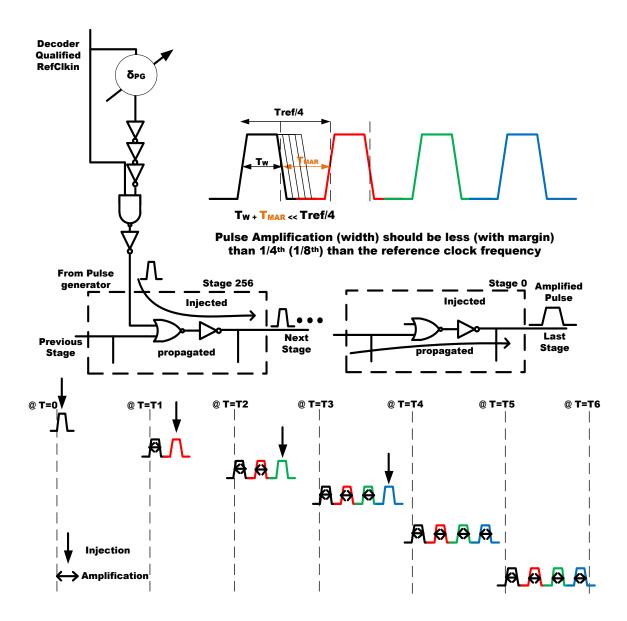

| 4.4. Pulse Width Sizing Requirements and Critical Timing Relationships for Ensuring Tha  |

| Fidelity of the Multiplied Clock is Maintained. Pulse Injection and Amplification are    |

| Shown at Different Time Stamps. 104                                                      |

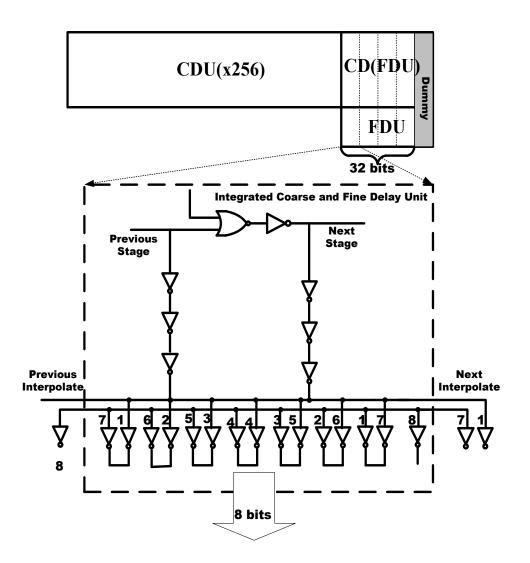

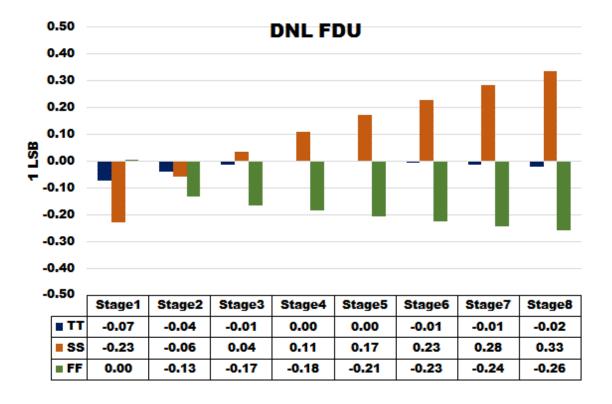

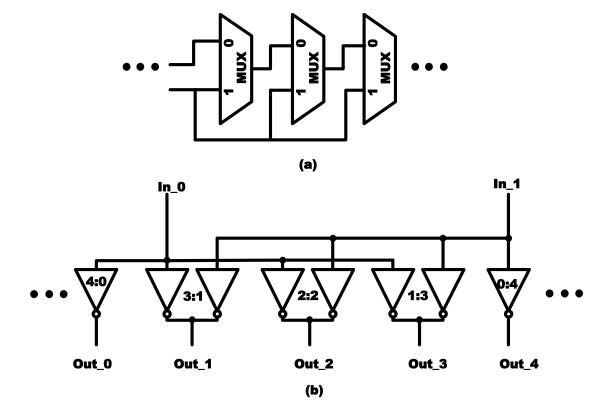

| 4.5. Inverter Phase Interpolator by 8 Design. Interpolation of Edges Derived from Coarse |

| Delay Unit. Four Such Units are Stacked to Create a 32 Bit Fine Delay Unit               |

| 4.6 Inverter Phase Interpolator by 8 Design. Interpolation of Edges Derived from Coarse  |

| Delay Unit. Four Such Units are Stacked to Create a 32 Bit Fine Delay Unit               |

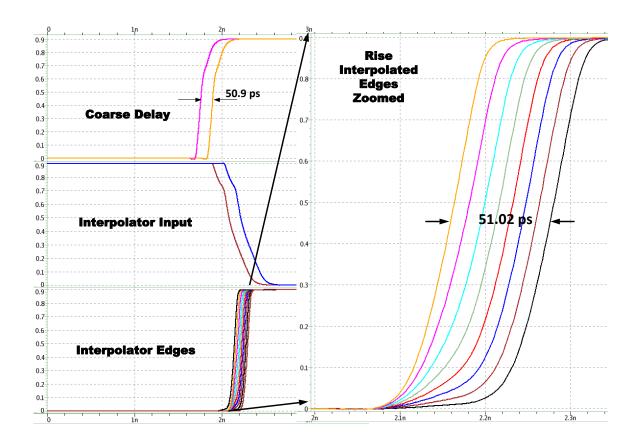

| 4.7 Fine Delay Unit Simulation Waveforms, Interpolated Fine Edges are Zoomed and         |

| Shown on the Right, the Values are Derived from the Coarse Delay Unit Delay 111          |

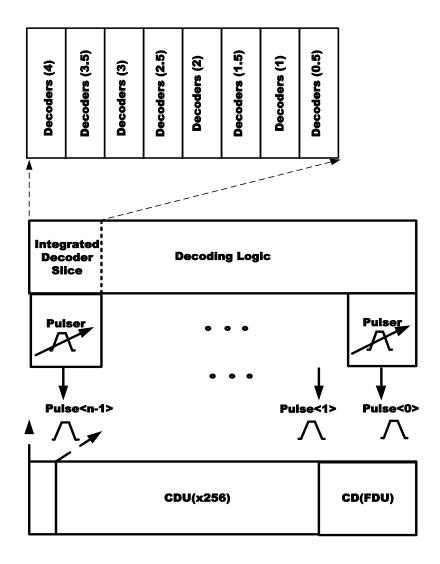

| 4.8 ADPMDLL Top Level Decoding Architecture Shows the Minimized Area Footprin            |

| Decoders (8 in Number) That are Implemented for Controlling the Delay Line Width. 112    |

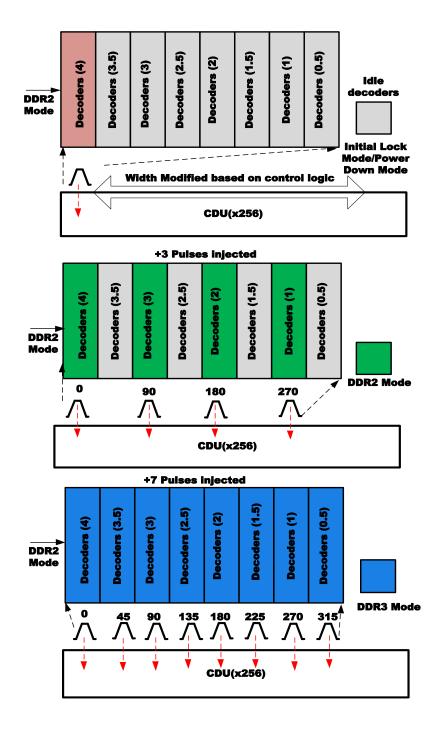

| 4.9 DDR Modes of Operation and the Decoder Activity, DDR2, DDR3 and Locking Mode         |

| Shown, Idle Decoders in Low Power Mode Shown in Grey                                     |

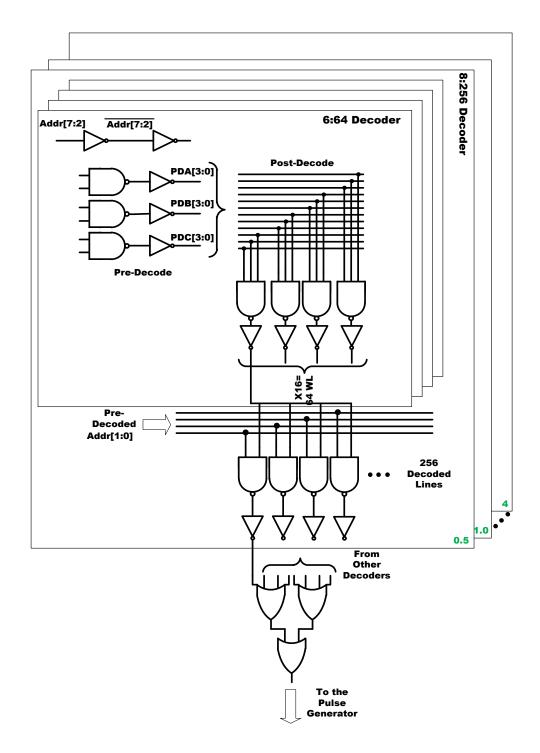

| 4.10 Decoding Logic Schematic Overview, Individual Decoders and the or Logic Which       |

| Enables Selection Between Decoders is Shown                                              |

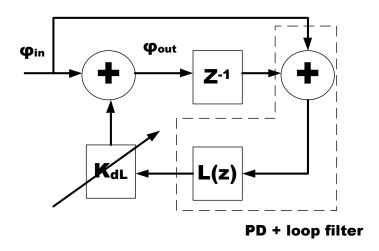

| 4.11 General 0th Order Type 1 Dll Which Only Has Feed-forward Clock Path Z-domain        |

| Block Diagram. 115                                                                       |

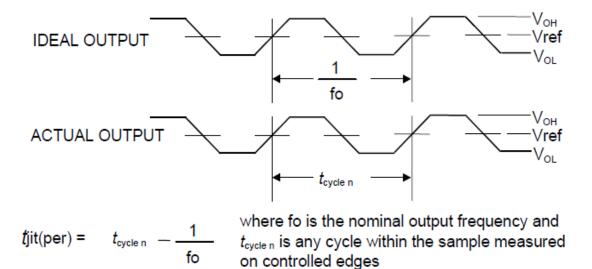

| 4.12 Waveform and Definitions of Cycle-to-cycle Jitter (a) and Period Jitter (b) after   |

| [Jede03]116                                                                              |

| 4.13 Control Logic Overview, Constituents of the Control Logic are Shown Here, Colored   |

| Portions Indicate APRed Logic and White Background Indicates the Custom Logic 117        |

| Figure                                                                                     |

|--------------------------------------------------------------------------------------------|

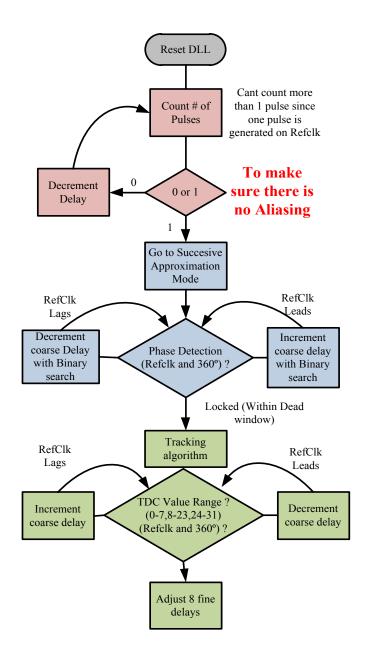

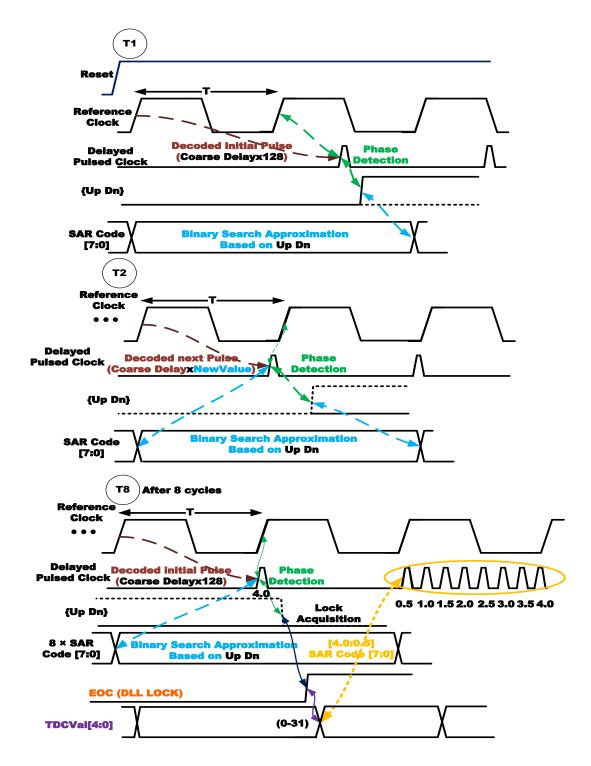

| 4.14 ADPMDLL Acquisition and Tracking Algorithm Flowchart, Algorithm Shows the             |

| Binary Search Acquisition and Step Tracking Using Fine Delay and Arithmetic                |

| Approximation. 119                                                                         |

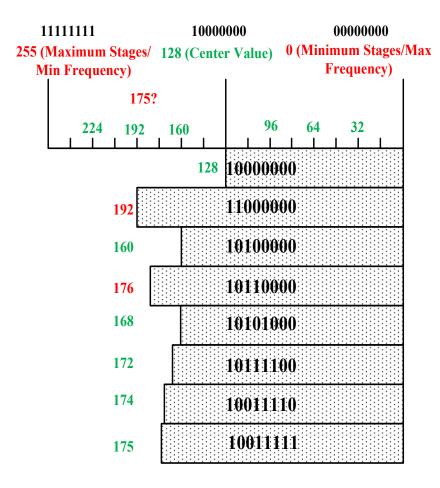

| 4.15 Successive Approximation Algorithm Tracking a Value of 175 with Initial Seed of       |

| 128. Binary Values Used in the Control Logic Sar is Shown in the Shaded Regions. Red       |

| and Green Coloring Signifies Phase Frequency Detection Output                              |

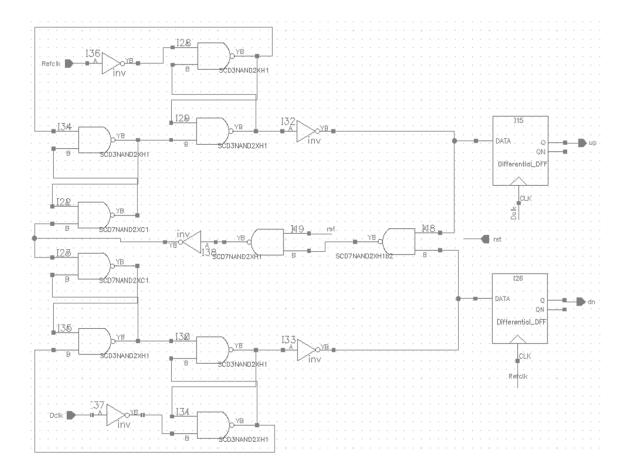

| 4.16 Modified Bang-bang Phase Detector Design Schematic, It Measures the Difference        |

| Between the Reference Clock and the Pulsed Clock and Creates a 2 Bit {up,Dn} Signal        |

| Processed by Sar Unit. An Asynchronous (Active Low) Reset is Used to Ensure Known          |

| State Before the Comparison Begins. 122                                                    |

| 4.17 Bang-bang Phase Detector Design Schematic, It Measures the Difference Between         |

| the Reference Clock and the Pulsed Clock and Creates a 2 Bit {up,Dn} Signal Processed      |

| by Sar Unit. An Asynchronous (Active Low) Reset is Used to Ensure Known State Before       |

| the Comparison Begins. Table Inset Shows the Minimum Resolvable Phase Difference.          |

|                                                                                            |

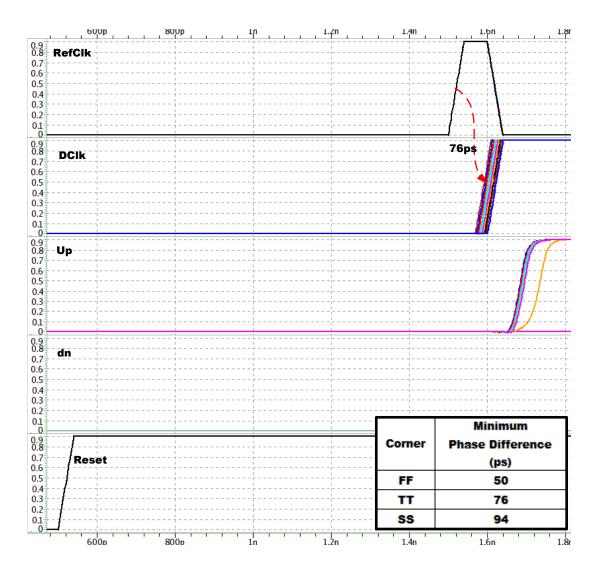

| 4.18 Time to Digital Converter Design Which Processes 32 Bit Edge Data and Produces a      |

| 5 Bit Code That Represents the Phase Error with a Granularity of 6ps. Values Representing  |

| Lad and Lead are Shown with the Associated Waveforms. The Centering Delay Ensures          |

| That Center Value (16) Corresponds to 0 Ps Phase Error. 124                                |

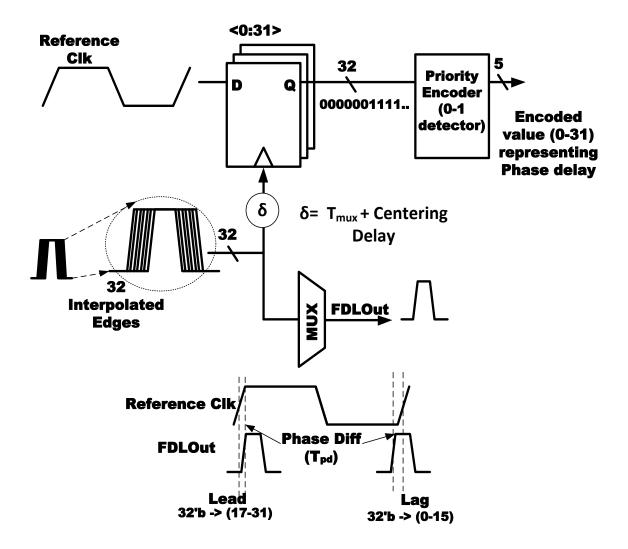

| 4.19 Differential Non-linearity for the Fdu Across Corners, Even at the Worst Case the Dnl |

| is Less Than 35lsh                                                                         |

| Figure                                                                                 |

|----------------------------------------------------------------------------------------|

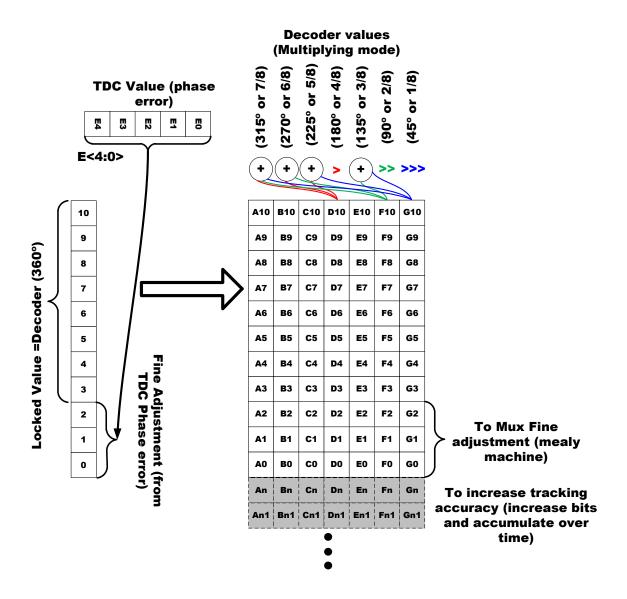

| 4.20 Arithmetic Multiplied Code Creation for High Frequency Clock Injection, 1/8-7/8th |

| of the Locked Values with the 2-1, 2-2 and 2-3bit Position Values Calculated and       |

| Maintained with Shift and Add Arithmetic to Allow Locking Resolution of ~6.25 Ps, Car  |

| Be Further Improved with Increasing Bit Positions and Accumulating the Values for      |

| Increased Power. 127                                                                   |

| 4.21 Color Coded ADPMDLL Top Level Diagram Which is the Reference for Waveform         |

| Definition of Working of the ADPMDLL in Fig. 21                                        |

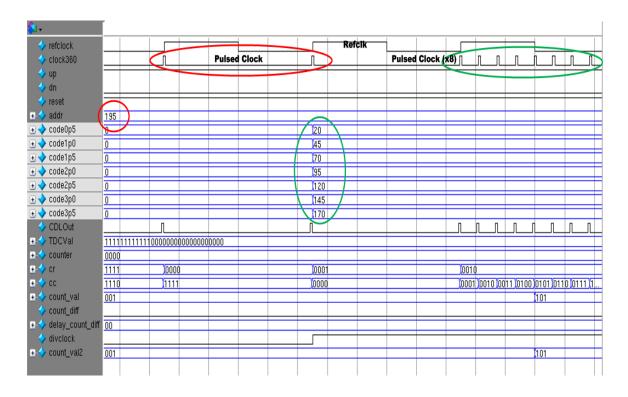

| 4.22 Color Coded ADPMDLL Top Level Functional Waveforms, Color Corresponds to          |

| the Unit Which is Causal to the Signal.                                                |

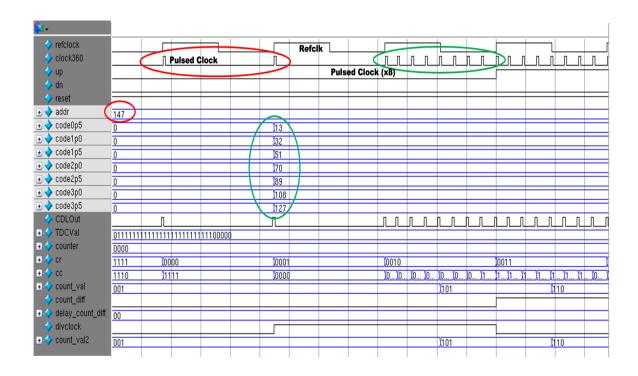

| 4.23 100 Mhz Clock Locked with Initial Single Pulses and with 8 Pulses Post Locking    |

| The Locked Code Value (Addr) is 195 and the Divided Values are Shown for Pulse         |

| Injection. 131                                                                         |

| 4.24 133 Mhz Clock with Single Injected Locked Pulse and Post Locking 8 Pulses Locked  |

| by Linear Interpolation with the Code Values and Interpolated Values Circled in Red. 8 |

| Pulses Locked per Reference Clock. Locked Value is 147                                 |

| 4.25 266 Mhz Clock Locked with 8 Pulses, Single Pulse Injected and Locked Circled in   |

| Red and the 8 Pulses Injected and Locked Circled in Green. The Locked Value is 71, Res |

| of the Interpolated Values are Circled in Red                                          |

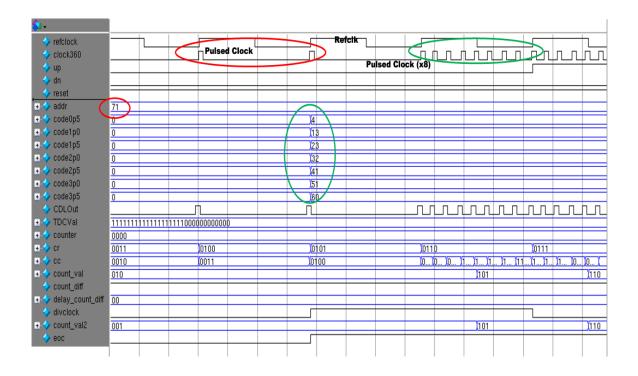

| 4.26 Coarse Delay 1 Sigma Variation Bound for One Coarse Delay Unit. A Maximum         |

| Variation of 19.68 Ps Can Be Accumulated Due to Coarse Delay Random Variation 135      |

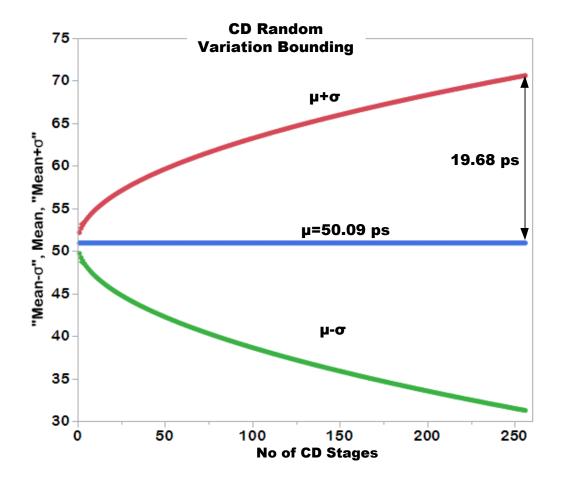

| 4.27 Gaussian Noise Mismatch Analysis Summary for the ADPMDLL, Mean and Sigma          |

| of the Corresponding Units are Shown, Only Units Which are in Critical Path and Hence  |

| Figure                                                                                       |

|----------------------------------------------------------------------------------------------|

| Contributing to Phase Error/Jitter Specifications are Shown. Green and Red Arrows            |

| Indicate the Fast and Slow Paths Contributing to the Variation Leading to Phase Error in     |

| the High Frequency Clock. 136                                                                |

| 4.28 ADPMDLL Critical Path and Critical Path Timing Diagram Highlighted in Red, the          |

| Fastest Pulse Injection (or the Smallest Delay) That Can Meet Timing is the Requirement      |

| for the Successful Frequency Multiplication or Pulse Injection in the DDR3 Mode. The         |

| Equivalent Path in DDR2 Mode is Shown in Orange and is Less Timing Critical than the         |

| DDR3 Path as Explained in Previous Sections. 139                                             |

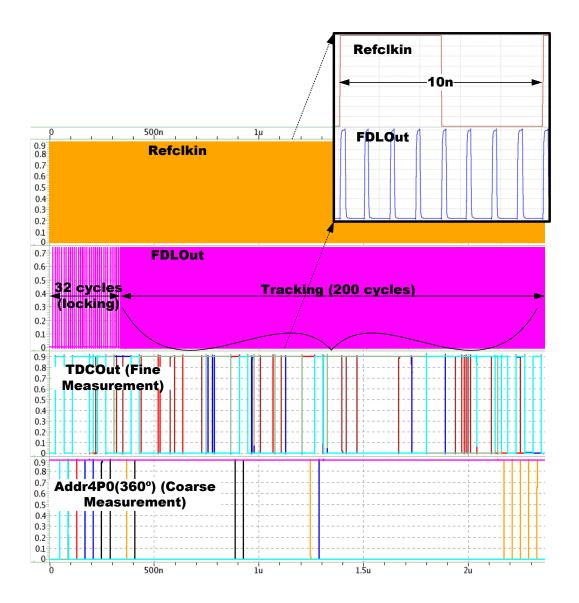

| 4.29 Spice (Ultrasim) Simulation Timing Waveforms for a 10ns Input Reference Clock           |

| Cycle. Locking is Completed in 32 Clock Cycles and the Pulses are Injected into the Loop     |

| Subsequently After. Tracking is Observed for 200 Cycles. Tdc Output Tracks the Phase         |

| Error and Eliminates Jitter It with Digital Correction as Described in the Earlier Sections. |

|                                                                                              |

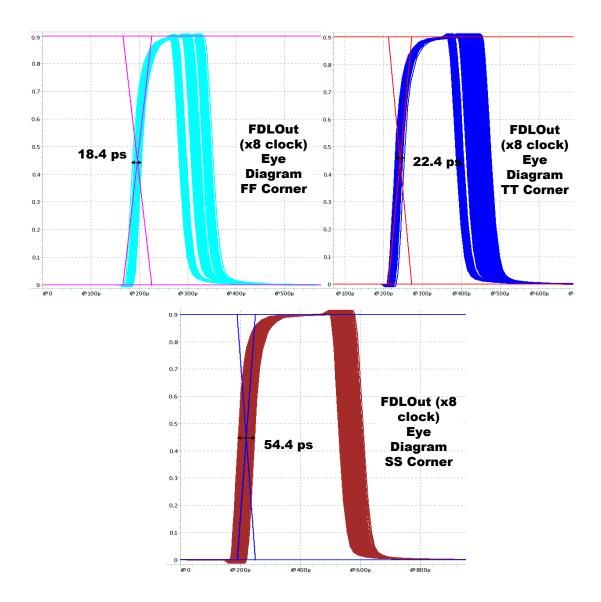

| 4.30 Eye Diagrams Showing Peak-to-peak Jitter for TT, FF and SS (Clockwise) Corner           |

| Simulations. P2p Jitter is below the Required Limit for DDR2 Transfer as per the Jedec       |

| Specs. The Black Line Indicates the Ideal Reference Clock Eye Diagram. The Falling           |

| Waveforms with Disparate Waveform Indicates the Across Corner Pulse                          |

| Amplification/Attenuation Behavior Where the Pulse Width Constraint is Still Met 142         |

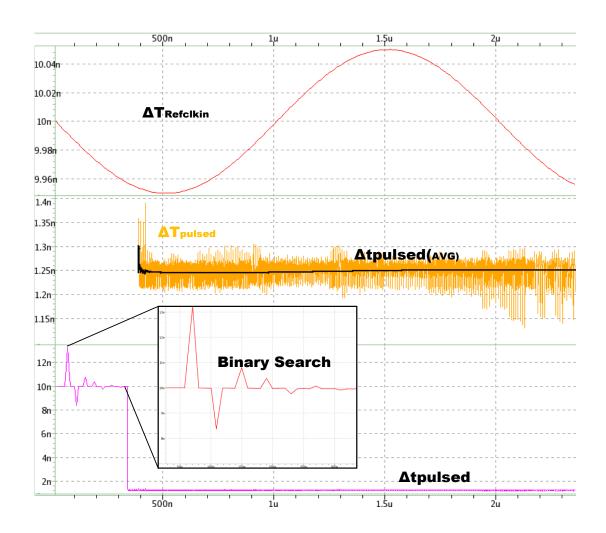

| 4.31 Noise PeRFormance of the Apdmdll in Presence of a 500k 100ps P2p Noise Variation        |

| of Input Reference Clock. The Pulsed Clock and its Average is Shown in the Yellow and        |

| Black Respectively. Binary Search Algorithm for ADPMDLL Locking in Presence of               |

| Input Jitter is Also Shown                                                                   |

| Figure                                                                                    |

|-------------------------------------------------------------------------------------------|

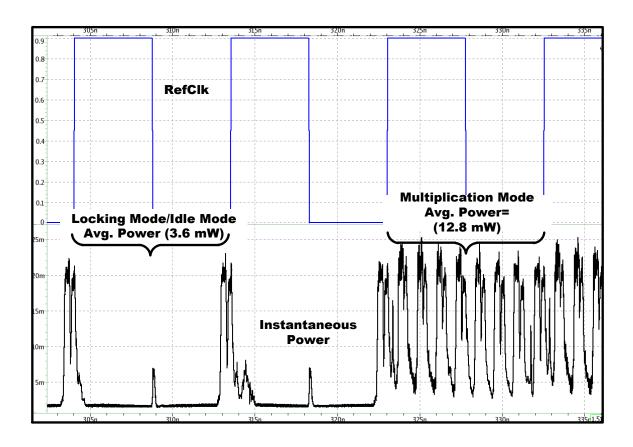

| 4.32 Power Measurement Waveforms of the Apdmdll, Locking/Idle Mode Power and              |

| Multiplication Mode are Both Shown, as Expected Much Higher Activity is Observed          |

| While Producing DDR3 Standard Multiplied Clock                                            |

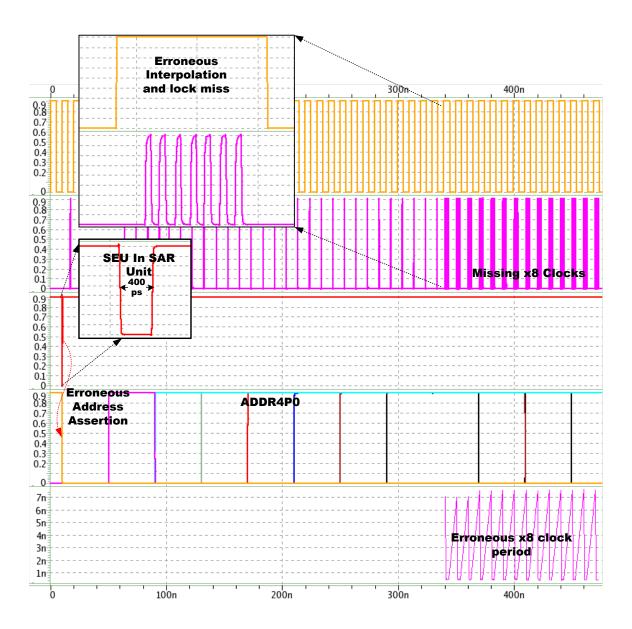

| 4.33 Simulation Waveforms of Soft Error Vulnerability in the Proposed ADPMDLI             |

| Design. Sar Unit is Upset with a 400 Ps Set Which is Captured by the Sequential Units and |

| Results in Missed Acquisition and Merged Pulses. 147                                      |

| 4.34 Block Level Schematic of the Test Structure Taped-out for the Purpose of Delay       |

| Variability and Fine-delay Non-linearity. The Delay Unit is Different from the Unit       |

| Described in This Work, the Implemented Design in Test-chip (Tc25) Was not a Pulsed       |

| Design, the Components However Were Shared                                                |

| 4.35 Block Level Schematic of the Test Structure Taped-out for the Purpose of Delay       |

| Variability and Fine-delay Non-linearity. The Delay Unit is Different from the Unit       |

| Described in This Work, the Implemented Design in Test-chip (Tc25) Was not a Pulsed       |

| Design, the Fine Delay Unit Components However Were Identical                             |

| 4.36 Tc25 Test-chip Snapshot Showing the Ddl Test-structure in Red. The Test-structure    |

| is Fabricated Inside a 4 by 4 mm Die with Wire-bond Packaging                             |

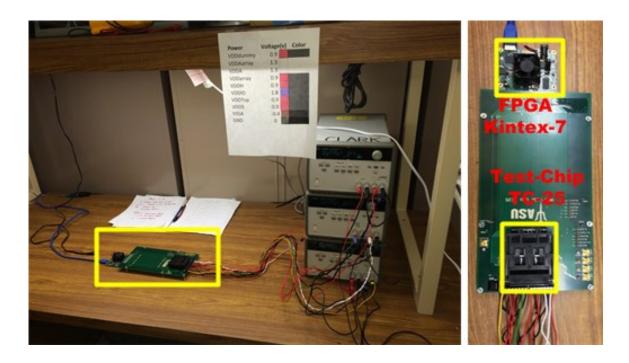

| 4.37 Tc 25 Dll Test Structure for Coarse and Fine Delay Unit for Delay and Non-linearity  |

| Testing. The Single Slice Which are Triplicated are Shown in the Zoomed Figure 152        |

| 4.38 Tc 25 Test-setup. The Fpga Board and the Custom Test-board are Shown. The Test-      |

| chip Tc25 is Plugged in the Socket and the Power Supplies are Connected to the Test-chip  |

| as Shown 153                                                                              |

| Figure                                                                                    |

|-------------------------------------------------------------------------------------------|

| 4.39 Tc 23 Implemented Coarse and Fine Delay Structures, the Fine Delay Was               |

| Implemented as by 4 Interpolate Instead of by 8 Interpolation as in This Chapter 154      |

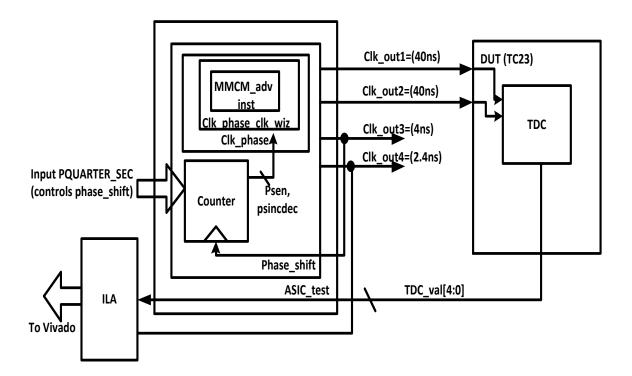

| 4.40 Tc 23 Fpga Testing Verilog Hierarchy Block Diagram to Capture Tdc Data out as a      |

| Result of Phase Shifts Applied Through Clock Manager Module Mmcm                          |

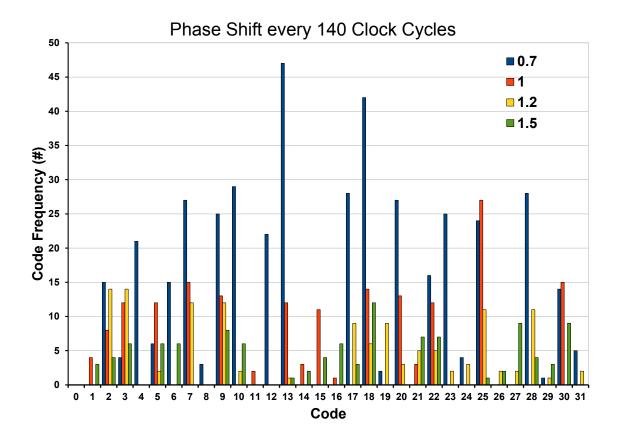

| 4.41 Code Distribution with Phase Shifts of 14.2 Ps Applied Every 140 Cycles 156          |

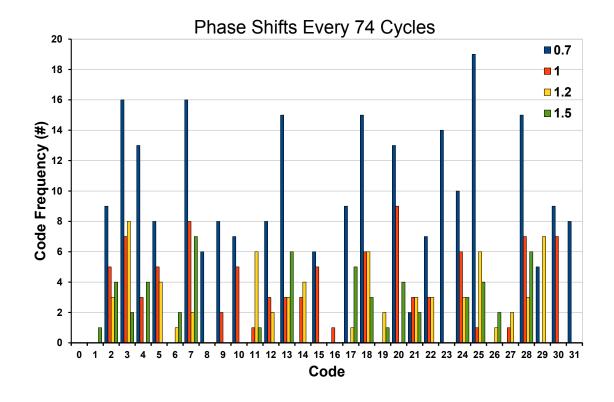

| 4.42 Code Distribution with Phase Shifts of 14.2 Ps Applied Every 74 Cycles               |

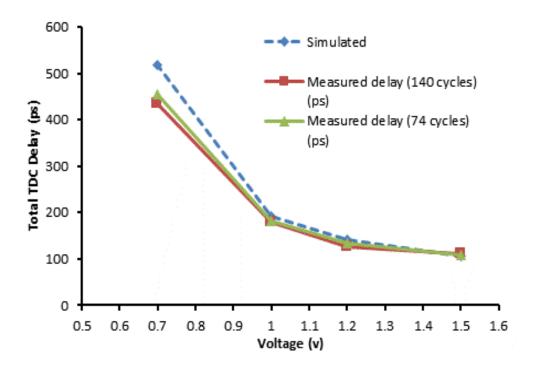

| 4.43 Measured Vs Simulated Delay of the Total Tdc Delay for the Two Experiments           |

| Shown in Fig4.41 and Fig. 4.42. Measured and Simulated Values Agree Closely and Only      |

| Vary at Low Voltages. 158                                                                 |

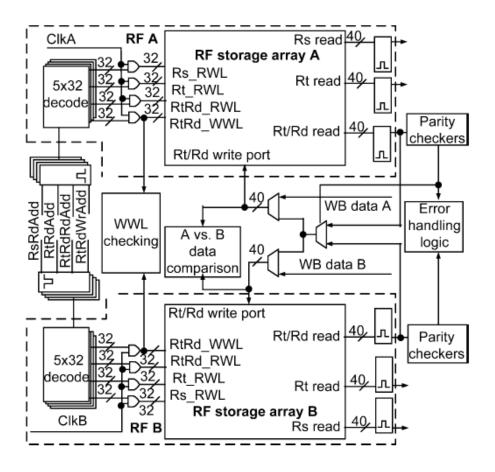

| 5.1. DMR RF Architectural Diagram with the a and B Copies and the Checking (WWL           |

| Parity and Comparison) Logic to Detect the Erroneous Pipeline Before Commitment to        |

| Architectural State, after [Clar11]                                                       |

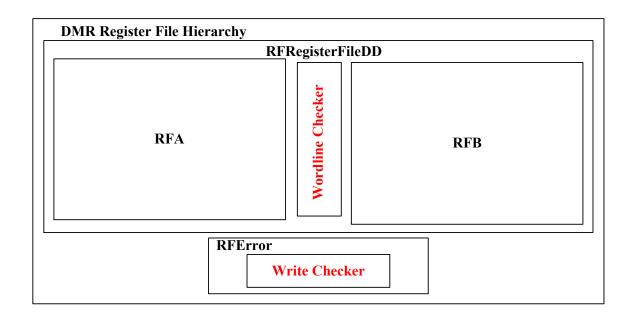

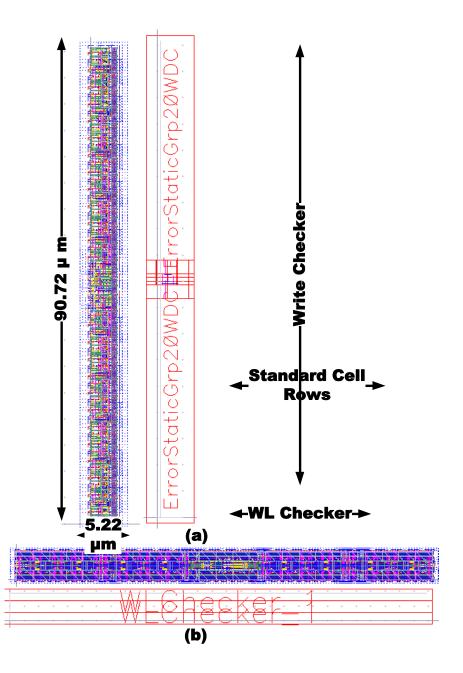

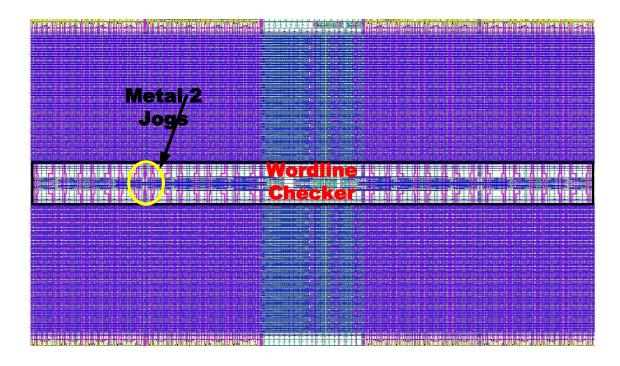

| 5.2. DMR RF Implementation Hierarchy, Wordline Checker is Implemented in the              |

| Registerfile Hierarchy Rfregisterfiledd and the Write Checker Circuits are Implemented in |

| the Rferror Hierarchy to Be Implemented in a Separate Physical Block                      |

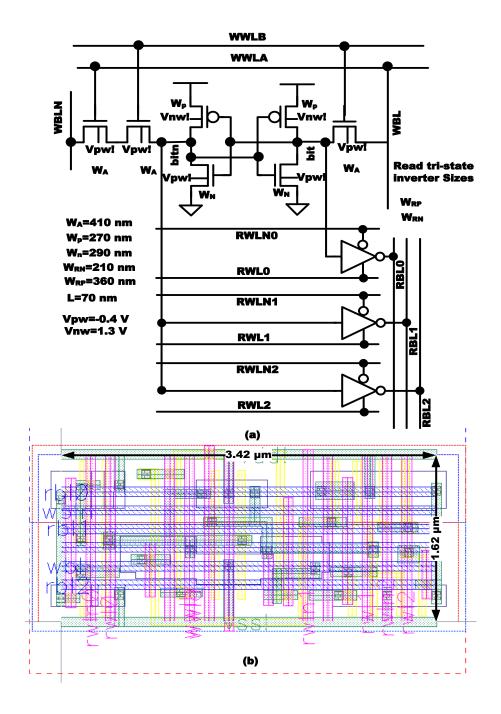

| 5.3. (a)Register File Cell Design, Single Copy of the DMR Cell with 2 Redundan            |

| Transistors for Dual Word-line Access, Multiple Ports are Shown, (b) Layout of the Cel    |

| in a 3,42 by 1.62 Um Area                                                                 |

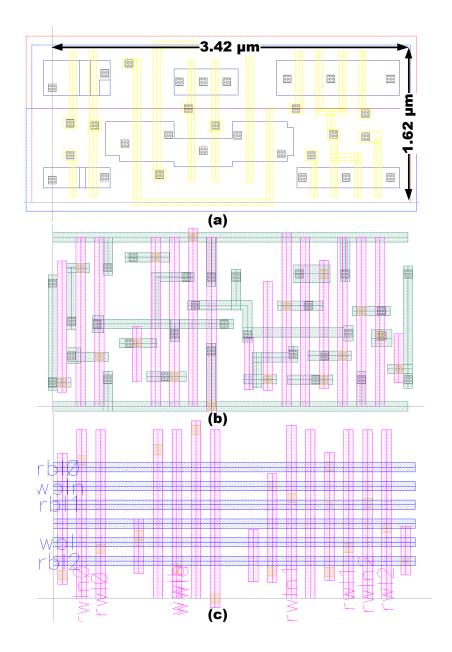

| 5.4. (a)Register File Bit-cell Design, Metal and Active Layer Usage and Layout are Shown  |

| by Layer in (a) Poly and Diffusion, (b) M1 and M2 (c) M2 and M3. High Density Layou       |

| for the Multi-ports Incorporated in the Cell are Shown                                    |

| Figure                                                                                     |

|--------------------------------------------------------------------------------------------|

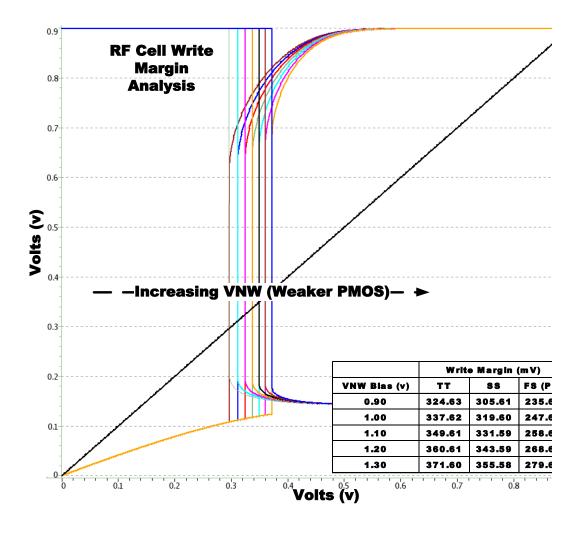

| 5.5. Register-file Write Stability Analysis, the N-well Voltage is Varied to Make the PMOS |

| Weaker Increasing the Write Margin. The Table Inset Shows the Simulated Values             |

| Summary Across Corners. 167                                                                |

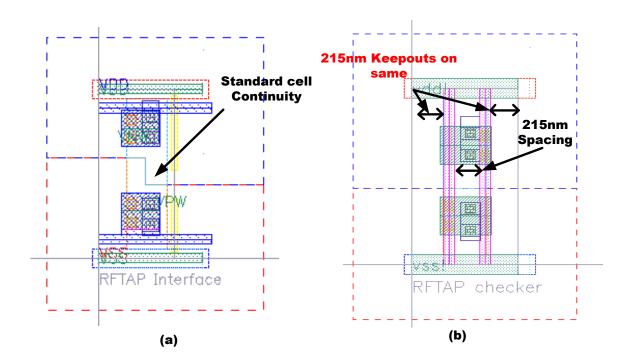

| 5.6. (a) Standard Cell Rail and Well (P and N) Continuity Shown in the Interface Cell (b)  |

| RF Tap Cell Spacing and Special Keep-out to Alleviate High Voltage Spacing Drc to the      |

| Secondary Power Rails for P and N Well Biasing. 168                                        |

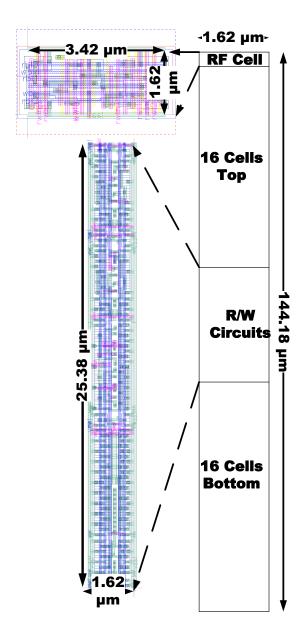

| 5.7. RF Columns with the Rw Circuit Size and Physical Arrangement. All Dimensions are      |

| Shown in Micrometers. 169                                                                  |

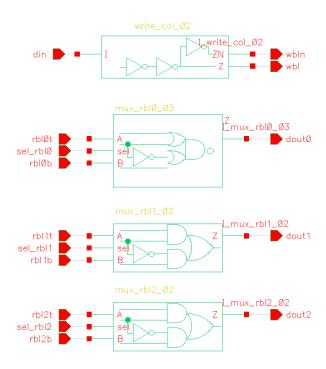

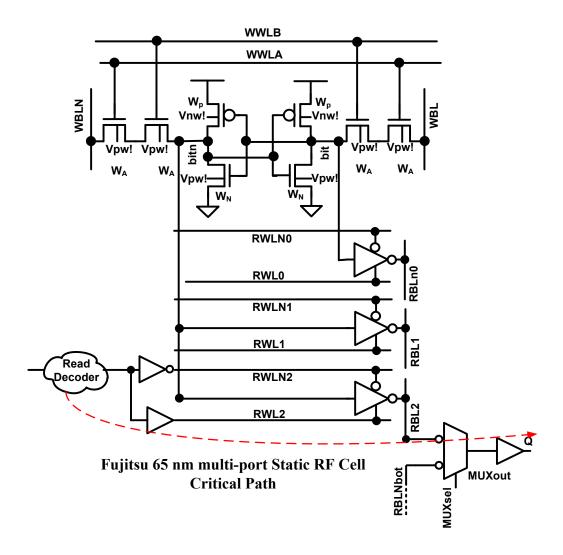

| 5.8. Write and Read Circuits for the RF Columns, Rbl0, Rbl1 and Rbl2 are Read ou           |

| Statically, with CMOS Gates as Shown in the Schematics, with Rbl0 Connected to the Bi      |

| Storage Value of the Cell While the Rbl1 and Rbl2 are Connected to Bitn Storage Value      |

| Resulting in Different Readout Value (1 and 0) Respectively                                |

| 5.9 (a). DMR RF Decoder APR Flow, Pin and Blockage Assignment is Done in the Per           |

| Module Which Inputs the Locations of the Specific Pins for the Decoder That Drives the     |

| Specific Port and Creates Blockages for the Rest of the Pass-through (b) RF Decoder        |

| Arrangement That is Used to Create the Automatic Pin, Blockage, Power, and Secondary       |

| Pg (Well Biases) for the APRed Decoders (Tap and Interface Cells are Shown) 173            |

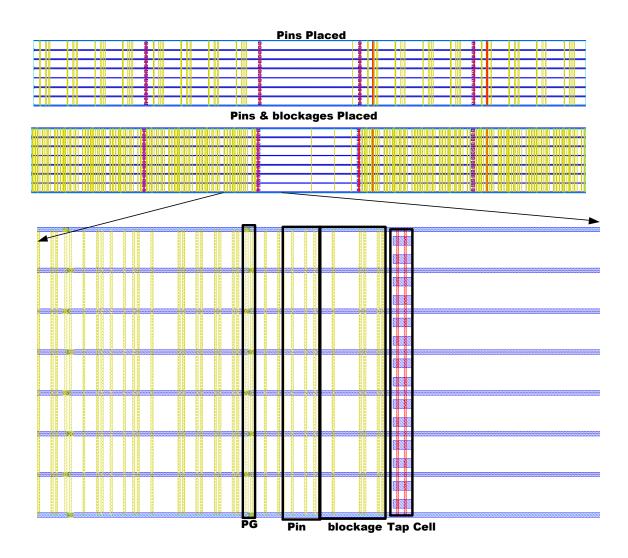

| 5.10 APRed Rwl0, Rwl1, Rwl2, WWLa or WWLb Decoder Automatic Pin, Blockage                  |

| Power (M4), and Secondary Pg (Well Biases on M2) Assignment. Pins and Blockages are        |

| Both Created on M4 Based on the Inputs Provided to the Perl Module Which Creates a Des     |

| File for Use in Defin Flow 174                                                             |

| Figure                                                                                   |

|------------------------------------------------------------------------------------------|

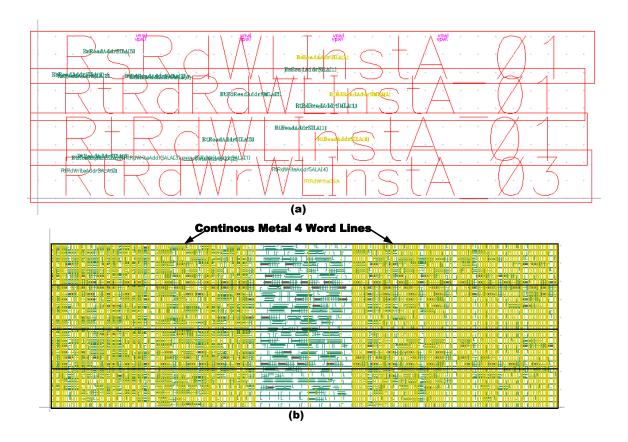

| 5.11 Decoder Arrangement (a) and Metal 4 Continuity (b) for Abutment with Columns,       |

| Decoder a Has the WWLa Version of the Write Decoder and Decoder B (Rfb) Has the          |

| WWLb Version of the Write Decoder, the Read Decoders are Identical                       |

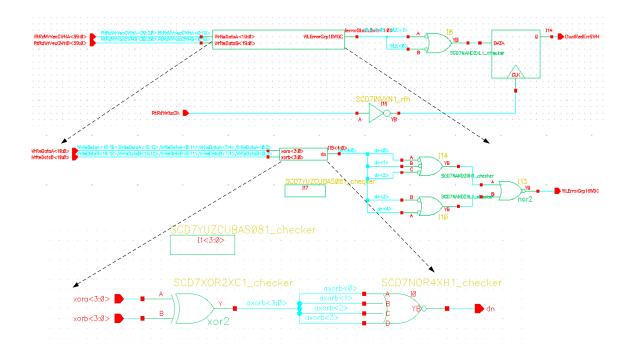

| 5.12 Checker Circuit Hierarchy in Schematic for Write and Wl Checkers. Wl and Write      |

| Checkers are 32 and 40 Bit Each. 176                                                     |

| 5.13 Checker Circuits Physical Layout, Wl Checker (b) is Horizontal and Write Chercker   |

| (a) is Vertical with Respect to the Standard Cell Row Placement (Standard Cells Rows are |

| Horizontal). 177                                                                         |

| 5.14 Checker Circuits Physical Layout, Wl Checker (b) is Horizontal and Write Chercker   |

| (a) is Vertical with Respect to the Standard Cell Row Placement (Standard Cells Rows are |

| Horizontal). 179                                                                         |

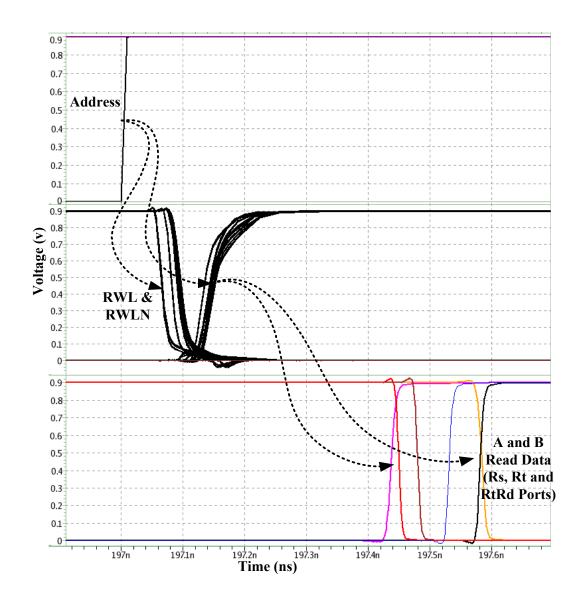

| 5.15 RF Critical Path Timing Path, Showing Address in to Data out Timing in Red 180      |

| 5.16 RF Critical Path Timing Path, Showing Address in to Data out Timing in Red 181      |

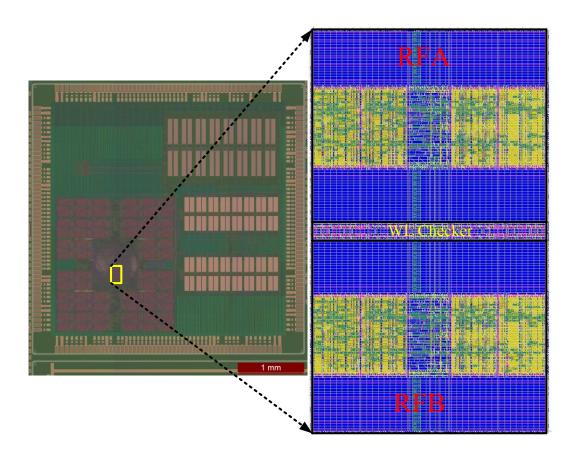

| 5.17 Physical Arrangement of the Dual Redundant Arrays and Word Line Checkers in the     |

| 55 nm Implemented Test Chip Tc 25.                                                       |

#### CHAPTER 1. INTRODUCTION

#### 1.1. Introduction

Integrated circuits (ICs) have increased the processing capacity and speed of electronics in the past few decades, based on Moore's law [Moor65]. Application specific ICs (ASIC) on silicon substrates allow millions of logic gates to be integrated for varying applications such as data processing, data encryption, off–chip data transfer, etc. These ICs can be susceptible to radiation particle induced malfunctions or errors. Historically, lead based isotopes in solder bumps of flip-chip packaging, lead frame alloys and interconnect metallization were initial sources of alpha particles which caused memory transient failures in terrestrial environments [May79]. Such errors could be corrected by rebooting the memory element and therefore are characterized as soft-errors, as opposed to hard errors which manifest due to physical irregularities in the circuit fabrication leading to permanent defects.

While packaging induced soft errors have largely been eliminated in modern ICs, electronic systems operating in radiation environments (e.g. space, nuclear reactors, particle accelerators) are exposed to a host of particles such as heavy ions, protons and neutrons. These particles cause electron hole pair generation in sensitive diffusion regions in complementary metal oxide semiconductor (CMOS) ICs resulting in radiation particle strikes, categorized as single event effects (SEE). SEEs have been identified as the primary failure mechanism in spacecraft malfunctions [Koga93, Ecof94, Sore00, Prit02]. The study, analysis and mitigation of these effects is broadly classified as radiation hardening. Even biomedical, automotive and banking applications [Nara06], which require highly

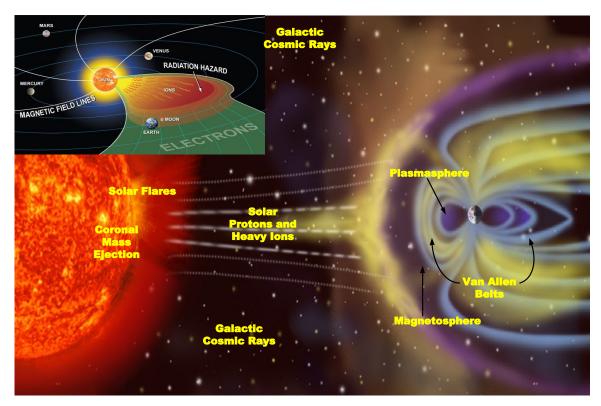

Fig 1.1. Cartoon showing the space radiation environment (courtesy of NASA, www.meted.ucar.edu).

reliable systems also rely on radiation hardening for critical applications. This chapter describes the radiation sources, the resulting effects on CMOS devices and mitigation strategies that are employed to counter radiation induced soft-errors. Following these definitions the motivation for this dissertation is explained.

## 1.2. Space Weather and Radiation Environment

Space weather, as described by the space weather prediction center, is the "variable condition in the sun and the neighboring space environment". This weather creates the radiation profile that Earth experiences. Figure 1.1 shows the interplanetary space environment with the Van Allen belts and the solar weather that is encountered by the planet Earth.

The typical astrophysical phenomena and resulting radiation particle spectra experienced are:

- 1. Protons and heavy nuclei ions associated with solar flares and coronal mass ejections (CME)

- 2. Galactic cosmic rays originating as a result of astrophysical phenomena such as supernova explosions

- 3. Trapped radiation due to Earth's Val Allen belts

- 4. Neutrons (Comic-ray albedo neutrons or CRAN particles)

- 5. Photons (γ-rays, X-rays, ultraviolet, extreme ultraviolet, optical, infra-red and radio waves)

The solar contributions to the space weather consist of solar winds, solar flares and coronal mass ejections. Solar winds are made up of ionized particles and can be visualized as a gas continuously flowing from the sun at 300 to 600 km/s (Fig. 1.1). Generally, solar winds do not cause major impact on Earth, but the particle stream can be enhanced and accelerated when more violent emission events such as flares and CMEs occur. The solar cycle is an approximate 11 year cycle marked by an increase and decrease in the number of sunspots, which are dark, cooler areas where a strong magnetic field consequently inhibits plasma from the sun's interior from interacting with the hotter surface plasma. The activity level of the sun varies from a quiet state with few sunspots, called solar minimum, to a more active state with many sunspots, called solar maximum. The likelihood of violent solar events becomes more significant closer to the solar maximum. Solar flares are the primary cause of sudden variation in brightness across the electromagnetic spectrum. These events accelerate electrons and protons traveling to Earth.

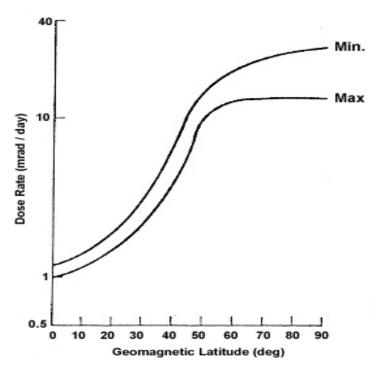

Fig 1.2 Galactic cosmic radiation dose rate variance with latitude and solar cycle (courtesy of NASA, www.meted.ucar.edu).

Radiation effects in low and medium Earth orbits that pass through the Van Allen belts consist of 93% protons, 6% alpha particles, and about 1% heavy nuclei [Stass88]. The Van Allen belts can be described as a toroid of particles trapped by the Earth's magnetic field and consist of a low altitude "inner belt" from 100~6000 km with high energy (tens of MeV/nucleon) protons and electrons; and a high altitude "outer belt" of up to 60,000 km with mostly high energy (1-10MeV/nucleon) electrons [Guss96].

Coronal Mass Ejection is a large burst of coronal material or magnetized plasma ejected away from the sun. The plasma can travel at speeds up to 2000 km/s under extreme circumstances. The material can travel in the direction of Earth where it will interact with Earth's atmosphere and magnetic field.

Earth and its atmosphere are also subjected to galactic cosmic rays (GCRs). This "background" radiation contains mainly protons, electrons, and atomic particles (from all elements of the periodic table) that originate far away in the galaxy. In the absence of significant solar events, cosmic ray intensities increase across the Earth's atmosphere. GCR intensity is modulated by the 11-year solar cycle [Barth03]. GCRs are comprised of 87% protons, 12% helium, with the remainder composed of heavy ions through actinides [Fred96]. Figure 1.2 plots the GCR dosage variation with geometric latitude and solar cycles. Minimum solar activity and greater latitude results in maximum GCR dose.

CRAN particles are secondary cosmic ray neutrons produced by the interaction of GCR with the Earth's atmosphere at about 55km above the planet surface. These particles have a half-life of ~11.7 minutes beyond which they decay into an electron, a proton and an anti-neutrino. Secondary neutrons are the most important contributor to radiation effects on CMOS at altitudes below 60,000 feet [Hazu00].

#### 1.3. Radiation Effects on CMOS devices

Radiation can cause degradation [Denn69], malfunction or damage of CMOS devices and consequently electronic systems [Kern88]. The exact mechanism of such a malfunction is dependent on the type, mass, kinetic energy, charge of the impinging particle, mass, atomic number and density of the target material. When an ion strikes a CMOS device, it loses energy as it passes through the device due to the columbic interaction with the electrons of the silicon lattice, leading to ionization in the particle's track. The particle can also directly strike the nucleus of a silicon atom and lead to direct ionization, however, the probability of such an interaction is very low.

The distance the particle travels inside the silicon lattice is dependent on the "stopping capacity" of the material. This distance is a function of the impinging particle's mass, energy and the density of silicon. Linear energy transfer (LET) refers to the energy loss of the particle per unit length in silicon. LET has units of MeV-cm<sup>2</sup>/mg and is given by the equation (1),

$$LET = \frac{1}{\rho} \frac{de}{dx} \left( MeV - \frac{cm^2}{mg} \right) \tag{1}$$

Here  $\frac{de}{dx}$  is the energy loss per unit length and  $\rho$  is the density of the material in mg/cm<sup>3</sup>.

The maximum LET value is usually referred to as the Bragg peak and signifies the maximum energy transferred right before the particle comes to rest [Hseih81].

Radiation particle strikes result in two charge deposition mechanisms in materials: direct and indirect ionization. In direct ionization, the electrons of the silicon nucleus are struck by the impinging particle and freed from the silicon bonds, thereby creating a dense track of charge. Indirect ionization results from the impinging particle dislocating the nucleus from its lattice structure. The charged nucleus then creates a track of charge, creating electron-hole pairs along its trajectory.

The two major radiation effects on CMOS devices and systems are single event effects (SEEs) [Mavis02] and total ionizing dose (TID) effects [Barn06]. TID is a non-destructive phenomenon of radiation induced variations in the threshold voltage under sustained ionizing exposure. This variation changes the performance of the CMOS device due to increased leakage and lower noise performance. This work is focused on mitigating errors arising out of single events and hence TID will not be discussed further.

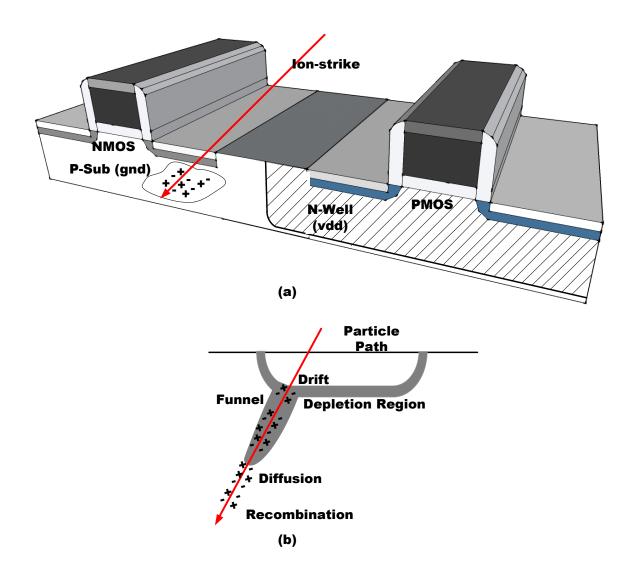

### 1.4. Single Event Effects

Single event effects as the name suggests is the response of the CMOS circuit to a single radiation particle strike. As a result of charge deposition in the sensitive area of the circuit as shown in Fig. 1.3(a), electron-hole pairs can be collected by the diffusion node to change nodal voltage temporarily (SET) or permanently (an SEU in a memory element). As defined previously, the three main particles that cause single event upsets are heavy ions, protons and neutrons. Heavy ions primarily cause upsets through direct ionization whereas proton based upset mechanism is dominated by indirect ionization through proton-nuclei collision. Upsets due to neutrons are completely as a result of indirect ionization owing to their charge neutrality [Sagg05].

There are three stages of SEE formation: charge generation, charge collection and circuit response. Charge generation is decided by the particle's mass and energy and properties of the material it passes through. Charge is generated due to ionization (direct or indirect) generally within a few microns of the junction. In silicon, one electron-hole pair is produced for every 3.6 eV of energy lost by the incident radiation. Silicon has a density of 2328 mg/cm<sup>3</sup>, therefore it is easy to calculate from equation (1) that an LET of 97 MeV-cm<sup>2</sup>/mg corresponds to a charge deposition of 1 pC/um. Hence the amount of collected charge in silicon can be given by the formula

$$Q = 0.01036 * LET (pC / \mu m)$$

(2)

Fig 1.3. (a) Ion strike at the output of a CMOS (metal and gate connectivity not shown). (b) Funnel formation and charge collections mechanisms in the semiconductor following an ion strike.

Thus the collected charge Q for silicon substrate is in the range of 1-100 fC depending on the type of particle, its trajectory, and its energy over the path through or near the p-n junction. The most sensitive semiconductor device structure is the reverse-biased p-n junction. In a worst-case scenario, a p-n junction that is unbiased or floating is extremely sensitive to any charge collected from a radiation event. Circuits likely to have

this scenario include dynamic random access memories (DRAM), dynamic logic circuits, and analog designs like charge pumps. Since gate capacitance in ultra-deep submicron technologies is less than 2 fC/µm, nominally deposited charge can upset technologies with supply voltages less than 1 V. The charge deposited by impinging particles remains constant as gate capacitances are reduced due to scaling in modern technologies.

Three mechanisms that act on the charge created by an energetic particle strike are:

1) carriers can move by drift in response to applied or built-in fields in the device, 2) carriers can move by diffusion due to carrier concentration gradients or 3) carriers can be consumed by recombination through direct or indirect processes. These three mechanisms are not unique to radiation particle strikes and are in fact the governing processes of charge transport in semiconductors under normal operating conditions [Dodd03]. The most sensitive regions in CMOS devices are the reverse biased p-n junctions. A radiation particle strike on the reverse biased junction is illustrated in 1.3(b). Drift, diffusion and recombination processes governing charge collection and propagation are shown. A funneling mechanism results in the ion track distorting electric field lines, allowing collection by drift beyond depletion regions [Hsie81]. Compared to drift, diffusion is a less critical collection process since it is a slower process and spreads charge over multiple collection nodes over time. Nonetheless diffusion does cause upsets in certain scenarios [Sex91].

The characteristic that determines single event upset sensitivity of a device is its critical charge ( $Q_{crit}$ ). This is the amount of charge that must be collected at the critical nodes of the device to cause the single event upset or soft error [Dod95].

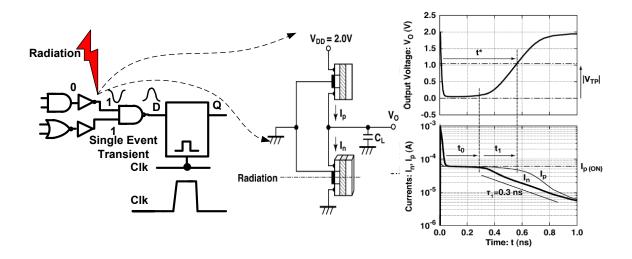

Fig 1.4. A single event transient manifesting on a combinational portion of a CMOS circuit. Collection of charge and the change in the state of the node capacitance CL and the current steering mechanism as a function of the restoring PMOS after [Koba09].

## 1.4.1. Single Event Transient (SET)

When ionizing radiation particles deposit charge on combinational logic rather than sequential or memory logic, the gate output diffusion node voltage may flip. The collected charge may charge or discharge the output node depending upon the charge polarity and location of the particle strike. Since the charge deposition happens in a period of picoseconds the circuit response takes much longer to remove the charge deposited, a momentary voltage spike is created [Heil89, Bene04, Gadl04].

An SET is a transient disturbance in the voltage and logic value of the node in question. The amplitude and width of such a transient is a function of the driving strength of the transistor which restores the circuit node voltage to the correct state and nodal capacitance of disturbed nodes. The transient may increase the voltage on the node beyond the switching point of a gate (typically VDD/2) thereby switching the gate output in response to erroneous transition as shown in Fig. 1.4. Propagation of the erroneous pulse

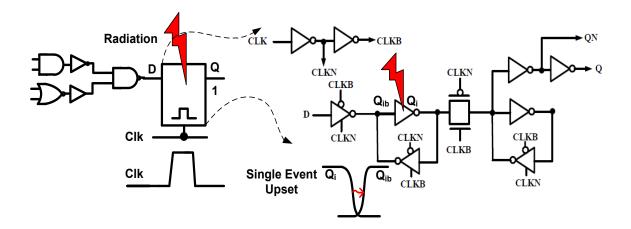

Fig 1.5. A single event upset due to radiation strike on the storage node in a latch, the storage feedback is upset as the two node reach the stable erroneous (10) state from the (01) state.

is based on sizing of gates downstream and in general the low pass nature of CMOS circuits tends to reduce the pulse widths and can in certain cases attenuate the pulse over multiple stages.

# 1.4.2. Single Event Upsets (SEU) or Soft-Errors

Single event upsets or soft-errors were observed in the late 70's in terrestrial DRAM's [May79] which were caused by alpha particles emitted by the IC packages. Since DRAMs have floating capacitive nodes which are highly susceptible to drift and diffusion mechanisms the charge state and hence node voltage and causes an upset or a soft-error. In static random access memories (SRAM) and other sequential elements (latches and flip-flops) the upset is caused primarily by aforementioned drift mechanisms and diffusion is less critical due to charge restoring paths which can neutralize the diffusion induced charge.

Fig. 1.5 shows a radiation particle strike on a flip-flop internal storage node leading to the flipping of the storage element (a back to back inverter). Voltage of storage nodes Qi and Qib are reversed since the transient on Qi results in a stable Qi=0 and Qib=1 due to

feedback action. This represents the upset due to the radiation event or an SEU [Sagg05]. SEUs can also be caused by travelling SETs that get latched by sequential elements during their sampling window. Once the machine state has been changed, it is impossible to distinguish an SEU from a particle strike on the sequential element and the one from an SET on combinational logic in the fan-in cone of the sequential element.

Single radiation particles can lead to single or multiple bit upsets (MBU) [Muss96] in CMOS circuits. MBU's are studied exhaustively in memory elements due to their highly dense arrayed structure. Multiple bits are placed in close proximity and based on the angle of incidence and the LET imparted by the particle 2, 3 and 4 bit upsets have been observed. MBUs are particularly significant in modern technologies as device dimensions and node capacitances decrease.

#### 1.4.3. Soft-Error Cross Section Measurement

The metric used to calculate the soft-error vulnerability of IC's to proton, neutron and heavy ion radiation particle strikes is called *cross section*. This is the probability of a radiation particle to hit a given target and is given by

$$\sigma = \frac{Errors (\#)}{Fluence \left(\frac{particles}{cm^2}\right)},$$

(3)

where cross section is expressed in units of cm<sup>2</sup>. This area therefore represents the apparent size of the target. Weibull distribution statistics can be used to analyze cross section data. The Weibull distribution has a threshold LET which signifies the onset of errors with increasing LET. The rate at which soft errors occur is called soft error rate (SER). The unit of measure commonly used with SER and other hard reliability mechanisms is failure in

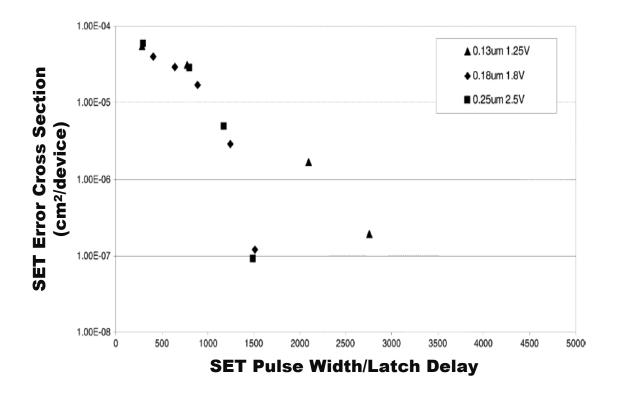

Fig 1.6. SET cross section with scaling on planar technologies [Bene06], SET pulse width increases as we scale due to the reduction in the nodal capacitance and operating voltages. time (FIT). One FIT is equivalent to one failure in 10<sup>9</sup> device hours. Here, failure rate per

hour is defined as the

$$\lambda = \frac{r}{EDH} = \frac{r}{D \times H \times Af}, \tag{4}$$

where EDH is equivalent device hours, D is the number of devices test and Af is the acceleration factor derived from Arrhenius equation [Elle12].

### 1.4.4. Other Single Event Effects

Another type of soft error occurs when the critical system control register bit is flipped, such as in field programmable gate arrays (FPGAs) or DRAM control circuitry, so that the error causes the product to malfunction. This type of soft error is called a single

event functional interrupt (SEFI) [Koga97]. SEFI leads to a direct product malfunction as opposed to typical memory soft errors that may or may not affect the final product operation depending on the algorithm, data sensitivity, etc.

Single event latch-up (SEL) is a steady high current state that results when a parasitic silicon controlled rectifier (SCR) (p-n-p-n) structure is triggered into a regenerative forward bias [Dodd03]. A circuit in latch-up will continue to malfunction until the IC is reset. If the latch-up current is large enough this can be a destructive in nature.

Other failure modes related to single events are the single event gate rupture (SEGR) and single event breakdown (SEB) [Dodd03]. Both mechanisms are destructive and lead to hard unrecoverable failures. Hard errors (as opposed to soft errors) are beyond the scope of this work and will not be discussed further.

# 1.5. Scaling and SER

With increase in clock speeds due to scaling, the probability of an SET being sampled to cause an upset in the machine state has also increased. This is due to typical transient pulse widths, which become comparable to clock frequencies. Fig. 1.6 shows experimentally collected SET Pulse width and cross section data on three generations of CMOS technologies. As the planar CMOS technology scaled, the current drive increased steadily and the width of the transistor reduced steadily by a factor of 0.7x. Reduced

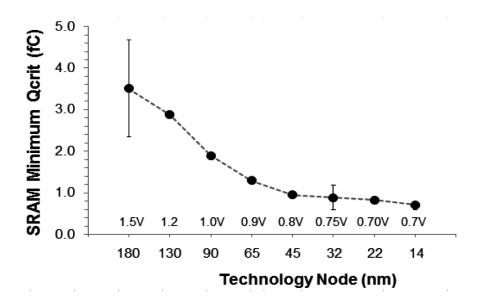

Fig 1.7. Critical charge reduction trend with different technology nodes for the Intel foundry technology, after [Seif15].

physical dimensions have a threefold effect: (1) A reduction in dimension leads to the reduced nodal capacitances, (2) a smaller physical area and (3) lower operating voltage which will reduce amount of circuit nodal charge. Critical charge Q<sub>crit</sub> is reduced due to these effects and even though the charge injected from radiation on silicon remains invariant, soft errors are steadily declining due to the reduced collection efficiency in scaled planar technologies.

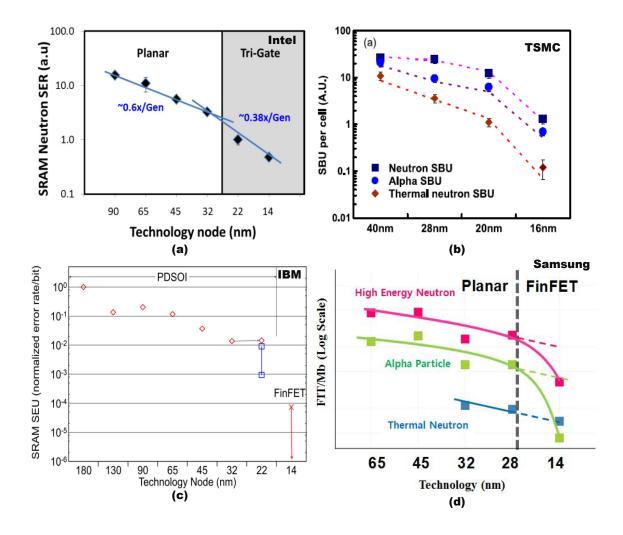

While planar transistors show a steady nominal reduction in the SER rate, finfet or trigate technology has shown a substantial reduction in the soft-error vulnerability trend. Fig. 1.7 shows the crucial SRAM charge Q<sub>crit</sub> trend for Intel transistors across technology generations [Seif15]. Experimental data published from four major IC foundries (Intel,

Fig 1.8. (a)[Seif15], (b)[Fang16], (c)[Oldi15] and (d)[Lee15] Planar and finfet SER/SEU cross section/Failure in time measurement from different technology foundries with enhanced SER reduction over planar technologies.

TSMC, Samsung and IBM) validate that the finfet as a structure is generally more robust for SER than the planar technologies.

The soft error rates are also improved in case of IBM's fully and partially depleted silicon on insulator (SOI) transistors. This is due to the increase threshold LET and reduced

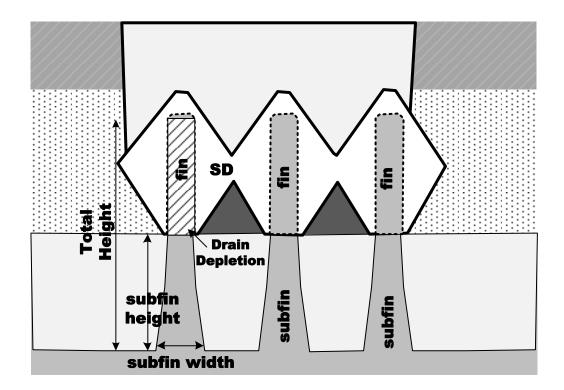

Fig 1.9. Drain depletion in a finfet technology which is at a distance of the height of subfin away from the substrate, reducing charge collection efficiency.

collection efficiency in finfet structures [Mamo11, Fang11, Noh15]. Figure 1.8 shows finfet soft-error vulnerabilities of the four major foundries mentioned above based on respective research publications which proves the reduction of SER beyond the range predicted by scalar bulk transistors. A simplified insight into the factors effecting soft-error rates is given by equation 4:

$$SER \sim A_{diff} \times exp\left(-\frac{Q_{crit}}{Q_{coll}}\right)$$

(4)

The critical charge ( $Q_{crit}$ ) trend for Intel technology over the past few generations is shown in Fig. 1.7. Older technologies had a 30 % reduction over prior generations in the critical charge, while the newer finfet technologies have a 15 % reduction.  $Q_{coll}$  is the charge collection due to the radiation event and can only be estimated using TCAD

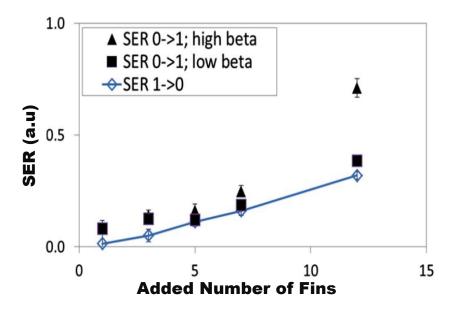

Fig 1.10. SER increase with number of fins, 0-1, 1-0 transition with low and high parasitic bipolar transistor gain  $(\beta)$  are shown, after [Seif15].

simulations and by analyzing measured data.  $Q_{coll}$  is a strong function of the doping profiles and the architecture of the MOSFET (planar, SOI, or finfet).

Based on results published by major foundries, the collection efficiency is reduced in finfet devices since it is a function of a) fin footprint, which equals the product of subfin width and the fin length, b) subfin height and c) subfin doping. The dependency of efficiency on fin footprint is almost linear and exponential to the distance of the drain depletion edge to the substrate (Fig. 1.9).

It is important to remember that the scaling beyond 90 nm was not based on classical dimensional scaling (Dennard scaling) but rather due to technology improvements like high-k gates, strained silicon, metal gate and finfet architectures. These improvements

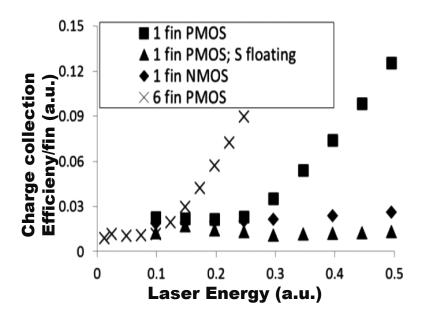

Fig 1.11. Onset of charge collection amplification under laser irradiation with increased bipolar gain thereby increase in SER at lower laser energies is shown, after [Seif15]. have increased the current drive while arresting the reduction of Q<sub>crit</sub>, hence reducing the SER.

Another effect that has appeared in scaled finfet technologies is the charge amplification due to parasitic bipolar P-N-P device formation in off-state PMOS connected to storage nodes as demonstrated in [Seif15]. This effect is a dependent on the  $\beta$  of the said parasitic device and increases linearly with the number of fins that form the storage nodes. This increase is shown in Fig. 1.10, where the increase in the SER in different latches with storage nodes made up of increasing number of fins is plotted. At higher  $\beta$  values and higher LETs, the charge collection efficiency also increases non-linearly for devices with high number of fins as illustrated in Fig. 1.11.

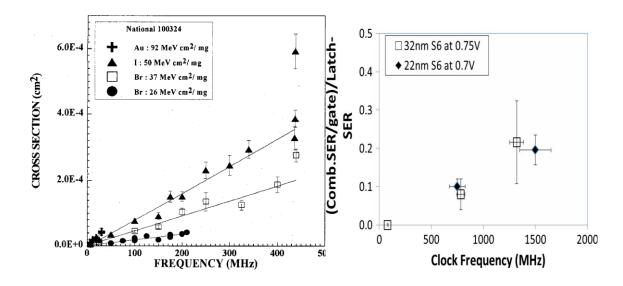

With increased scaling, clock frequencies continue to scale and hence the probability of capture and sample of single event effects also increases irrespective of the

Fig 1.12. (a) Cross section and (b) soft error rate as a function of clock frequencies measured in [Reed96] and [Seif12] respectively. Increased vulnerability with increased clock frequency is consistently observed over multiple generations.

type of technology. Fig. 1.12(a) and (b) show the effect of clock frequencies on the cross section and soft error rates for irradiated test structures across generations and technologies. While finfets are generally less susceptible compared to their planar counterparts of similar dimensions, the increased clock frequency has a similar impact on SER as on the planar transistors. Fig. 1.12(b) specifically shows 22 nm finfet data for increased clock rates and it follows the same trend as a 32 nm planar bulk transistor.

In conclusion, scaled technologies are still susceptible to soft-errors and upsets in the presence of radiation events, though the SER trends are somewhat encouraging due to reduced collection efficiency and newer fin dependent effects. Trends have also shown a negative impact on the SER rates in scaled technologies. Ever increasing clock frequencies further compound these problems. Depending upon the intensity and type of radiation

exposure, this susceptibility of the CMOS devices calls for specific mitigation strategies, which are described in the subsequent sections.

# 1.6. Radiation Hardening

Having discussed in detail the radiation sources and effects on CMOS devices, methods for mitigating soft errors or single events is studied in this section. Techniques for creating radiation tolerant and radiation immune circuits is referred to as "radiation hardening". Radiation hardening could involve either circuit and system level design techniques, fabrication process techniques or a combination of both.

When integrated circuit fabrication processing is used to harden circuits by increasing the critical charge on sensitive nodes, the hardening is called radiation hardening by process (RHBP) [Lacoe00]. RHBP is cost intensive as a separate fabrication process, needs to be maintained and also limits the maximum speed of the design since intentional RC is introduced on design nodes.

### 1.6.1. Radiation Hardening by Design

Since IC technology is mature and ubiquitous, a general hardening technique irrespective of the process is more practical since the same circuit or system level design techniques can be applied across a range of commercial processes.

This radiation hardening methodology is referred to as radiation hardening by design (RHBD). The focus of this work is on RHBD. Common RHBD techniques involve adding redundancy to the design either in the spatial domain or temporal domain to mitigate or mask radiation induced soft-errors.

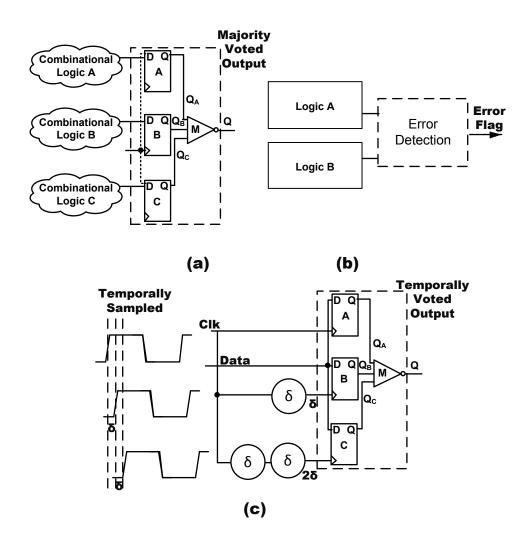

Fig 1.13. Triple modular redundancy (TMR) with complete triplication of combinationa and sequential elements ensuring complete mitigation with minimal timing penalty, (b) Dual Modular Redundancy (DMR) which detects a mismatch in the copies to set an error flag to be used by the error handler ensuring inhibition of erroneous signals and (c) Temporal hardening delaying signals in time to ensure that the SET gets masked by majority voting.

## 1.6.1.1. Hardening by Spatial Hardware Redundancy

Hardening by design can be accomplished by spatial hardware redundancy techniques such as triple modular redundancy (TMR) [Lyon62] [Hind09] [Hind11] and/or double modular redundancy (DMR) [Clar11] [Teif08] [Furu10]. Triple and double modular redundancy can correct and detect soft errors respectively, as shown in Fig.

1.13(a) and 1.13(b). Fig. 1.13(a) shows the triple mode redundancy with voting circuits that correct a single bit error on one of the copies of the circuitry.

Variants with either the sequential and/or combinational logic triplicated are designed for varying requirements of hardening and area overhead. Fig. 1.13(b) shows dual mode redundancy where the checker logic can detect the onset of errors because of mismatch. Based on the type of auxiliary schemes such as, parity bit and error correcting codes (ECC), the right values can be recovered in DMR hardening. The probability of upsetting two bits of the TMR or DMR logic could be significant if not designed carefully. Mitigating multi-node upsets will be studied in detail in subsequent sections and other chapters in this report.

Error correcting codes (ECC) for detection and correction of bit upsets are used as in [Fuji90]. In error detection and correction (EDAC) schemes, redundant bits are added to a data word to enable the system to detect and correct errors in the data (caused by SEU or SEFI) using enhanced ECC schemes such as Hamming codes [Chen84]. There is generally a trade-off associated with the area overhead (number of ECC bits) and the number of bit upsets that can be corrected.

# 1.6.1.2. Hardening by Temporal Redundancy

Single event upsets can also be mitigated by sampling data at different time stamps to ensure that any upsets can be filtered and recovered in the time allowed between sampling. Fig. 1.13(c) shows such a sampling system with a  $\delta$  delay between each sample points. Three copies of sequential elements are created and they are sampled by clocks with

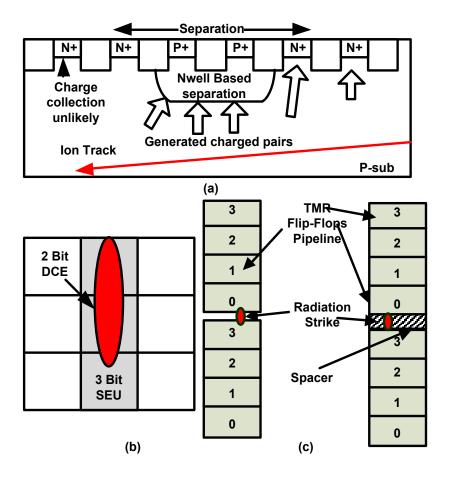

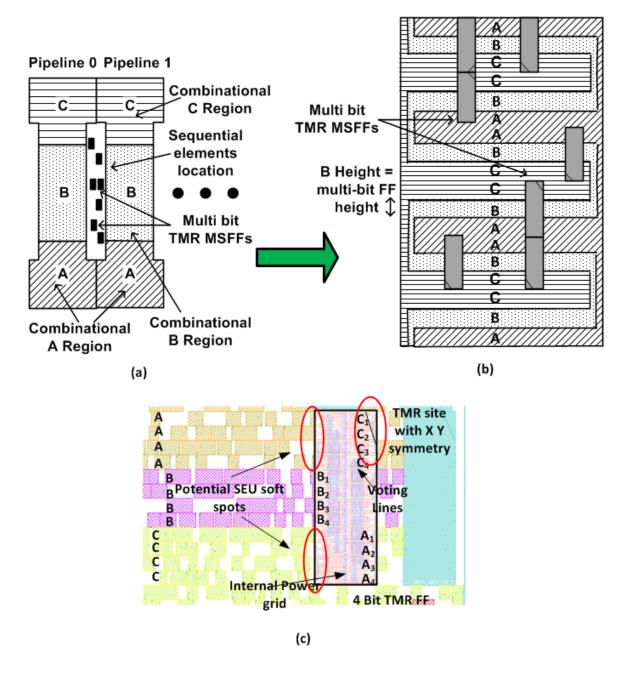

Fig 1.14. (a) Multi-node charge collection mitigation cross section due to nodal separation by n-well, (b) MBU in FPGAs as demonstrated in [Quin07] leading to DCEs and (c) CAD methodology based separation of multi-bit TMR cells with spacer between each groups to ensure that even non-equivalent flops in multiple domains cannot be upset with a single strike.

$\delta$  delay between them. In case of an SET the incorrect value will only be sampled by one of the copies, as long as  $\delta$ >TSET (SET width). This method of hardening is called temporal hardening [Mavi02] [Matu10] [Clar14] [Nase06] .

A dual interlocked cell (DICE) latch [Cali96] is the most common redundant structure, doubling the storage nodes in a configuration that requires two (critical) nodes to be upset to change the state. DICE latch based flip-flops have been shown to be

susceptible to SET induced upsets arising from particle strikes spanning multiple nodes [Black08, Warren09].

## 1.7. Multiple Node Charge Collection (MNCC) and Domain Crossing Errors (DCE)

Multiple node charge collection (MNCC) occurs when multiple nodes collect charge deposited by the same ionizing radiation particle track. MNCC can span several microns, greatly complicating the design and layout of hardened architectures. Particle strikes that span multiple nodes may affect multiple redundant copies of bits that can thwart such schemes [Koga93] [Black08]. Redundant latches have long been known to be sensitive to such upsets [Hazu04].

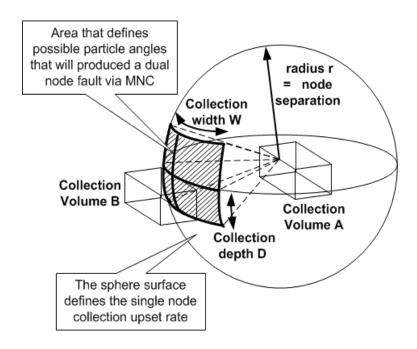

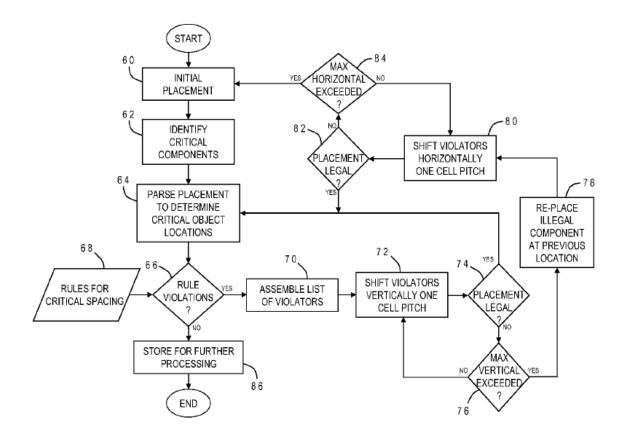

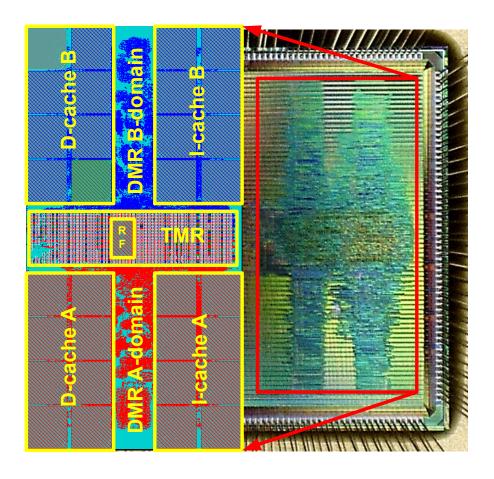

In rad-hard FPGAs, these multiple node upsets cause non-recoverable errors [Quin07]. Quinn, et al., termed multiple node charge collection that resulted in upsets despite TMR due to upset of multiple hardened domains as domain crossing errors (DCEs). They quantified the SEU span to be directly proportional to the number of DCEs in FPGAs. Consequently, as the relative physical size of the charge collection area increases, the DCE probability increases. Fig. 1.14(b) shows the representation of a 3 bit upset on a FPGA which can lead to a 2 bit DCE [Quin07].