### A Thesis Submitted for the Degree of PhD at the University of Warwick

#### **Permanent WRAP URL:**

http://wrap.warwick.ac.uk/92000

### **Copyright and reuse:**

This thesis is made available online and is protected by original copyright.

Please scroll down to view the document itself.

Please refer to the repository record for this item for information to help you to cite it.

Our policy information is available from the repository home page.

For more information, please contact the WRAP Team at: wrap@warwick.ac.uk

# Developing Graph-based Co-scheduling Algorithms with GPU Acceleration

by

## Huanzhou Zhu

A thesis submitted to The University of Warwick in partial fulfilment of the requirements  $\qquad \qquad \text{for admission to the degree of}$

PhD

## Department of Computer Science

The University of Warwick

May 2016

## Abstract

On-chip cache is often shared between processes that run concurrently on different cores of the same processor. Resource contention of this type causes the performance degradation to the co-running processes. Contention-aware co-scheduling refers to the class of scheduling techniques to reduce the performance degradation. Most existing contention-aware co-schedulers only consider serial jobs. However, there often exist both parallel and serial jobs in computing systems. This thesis aims to tackle these issues. We start with modeling the problem of co-scheduling the mix of serial and parallel jobs as an Integer Programming (IP) problem. Then we construct a co-scheduling graph to model the problem, and a set of algorithms are developed to find both optimal and near-optimal solutions. The results show that the proposed algorithms can find the optimal co-scheduling solution and that the proposed approximation technique is able to find the near optimal solutions. In order to improve the scalability of the algorithms, we use GPU to accelerate the solving process. A graph processing framework, called WolfPath, is proposed in this thesis. By taking advantage of the co-scheduling graph, WolfPath achieves significant performance improvement. Due to the long preprocessing time of WolfPath, we developed WolfGraph, a GPU-based graph processing framework that features minimal preprocessing time and uses the hard disk as a memory extension to solve large-scale graphs on a single machine equipped with a GPU device. Comparing with existing GPU-based graph processing frameworks, WolfGraph can achieve similar execution time but with minimal preprocessing time.

# Acknowledgements

First, I would like to express my sincere gratitude to my supervisor Dr. Ligang He, whose guidance, encouragement and support have been invaluable to me during my time at the Department of Computer Science at the University of Warwick. I would like to thank you for encouraging my research and for allowing me to grow as a research scientist. Your advice on my research have been priceless.

It is my great pleasure to work with all my lab-mates, particularly Bo Gao Chao Chen, Zhuoer Gu, Peng Jiang, Shenyuan Ren, Xufeng Lin, Chen Gu, Matthew Bradbury, Stephen Roberts and Nentawe Gurumdimma, for their stimulating discussions in science and technology and for all the fun we have had in the last four years.

I would like to thank all my friends, especially Wolfy Wang, Zihao Chen, Qiwei Jin, Yuxuan Zhan, Ye Kuang, Hui Xu, Dake Xu, Yibing Chen.

I would also like to say a heartfelt thank you to my parents for always believing in me and supporting me and encouraging me in all my pursuits.

In the end, I would like to give my special thanks to Momofuku Ando, the inventor of instant noodles. This invention saves me uncountable amount of time and liberates me from thinking one of the biggest problem in my life: what to eat. Without instant noodles, I am very likely died of the starvation long before I complete my PhD.

## **Declarations**

Parts of this thesis have been previously published by the author in the following:

- Huanzhou Zhu, Ligang He, Stephen. A. Jarvis Optimizing job scheduling on multicore computers IEEE International Symposium on Modeling, Analysis and Simulation of Computer and Telecommunication Systems 2014 (MASCOTS'2014) [149]

- Huanzhou Zhu, Ligang He, Bo Gao, Kenli Li, Jianhua Sun, Hao Chen, Keqin Li Modelling and Developing Co-scheduling Strategies on Multicore Processors 2015 International Conference on Parallel Processing (ICPP'2015). [150]

- Ligang He, Huanzhou Zhu, Stephen Jarvis Developing graph-based coscheduling algorithms on multicore computers *IEEE Transactions on Par*allel and Distributed Systems (TPDS). [52]

In addition, the following works are in progress of being submitted:

- "WolfPath: Accelerating iterative graph searching algorithms on GPUs"

- "WolfGraph: Wolf Graph: Edge-Centric graph processing on GPUs"

# Abbreviations

**BFS** Breadth First Search BSPBulk Synchronous Parallel CPICycles Per Instruction  $\mathbf{CMR}$ Cache Miss Rate  $\mathbf{C}\mathbf{W}$ Concatenated Window  $\mathbf{CEL}$ Concatenated Edge List CSRCompressed Sparse Row CDFCumulative Distribution Function  $\mathbf{DI}$ Distributed Intensity  $\mathbf{EVM}$ Edge Vertex Message  $\mathbf{GAS}$ Gather Apply Scatter  $\mathbf{IP}$ Integer Programming LLC Last Level Cache LPDLeast Performance Degradation MRC Miss Rate Curves MPPMulti Process Parallel MTPMulti Thread Parallel **MER** Maximum Effective Rank O-SVP Optimised Shortest Valid Path PSWParallel Sliding Window  $\mathbf{PE}$ Embarrassingly Parallel PCProcess Communication

RDDResilient Distributed Dataset Resilient Distributed Graph RDGSSSPSingle Source Shortest Path SDPStack Distance Profile  $\mathbf{SVP}$ Shortest Valid Path  $\mathbf{SVPPE}$ Shortest Valid Path for Embarrassingly Parallel **SVPPC** Shortest Valid Path for Process Communication  $\mathbf{SM}$ Streaming Multiprocessor  $\overline{\mathbf{VWC}}$ Virtual Warp Centric

# Contents

| A            | bstra | act                                      |  |   | iii |

|--------------|-------|------------------------------------------|--|---|-----|

| $\mathbf{A}$ | ckno  | owledgements                             |  |   | v   |

| D            | eclar | rations                                  |  |   | vi  |

| $\mathbf{A}$ | bbre  | eviations                                |  | , | vii |

| Li           | st of | f Figures                                |  | x | vii |

| Li           | st of | f Tables                                 |  | х | ix  |

| 1            | Intr  | roduction                                |  |   | 1   |

|              | 1.1   | Contention aware co-scheduling           |  |   | 2   |

|              | 1.2   | Parallel Graph Processing                |  |   | 5   |

|              | 1.3   | Research Contributions                   |  |   | 6   |

|              | 1.4   | Thesis Organisation                      |  |   | 8   |

| 2            | Lite  | erature Review                           |  |   | 9   |

|              | 2.1   | Introduction                             |  |   | 9   |

|              | 2.2   | Job Co-scheduling                        |  |   | 11  |

|              |       | 2.2.1 Overview of Co-Scheduling Problems |  |   | 11  |

|              |       | 2.2.2 Performance Prediction             |  |   | 12  |

|              |       | 2.2.3 Co-scheduling strategies           |  |   | 14  |

|              | 2.3   | Graph processing systems                 |  |   | 18  |

|   |      | 2.3.1  | Challenges in Graph Processing                                    | 18 |

|---|------|--------|-------------------------------------------------------------------|----|

|   |      | 2.3.2  | Distributed Graph Processing System                               | 20 |

|   |      | 2.3.3  | Graph Processing Systems on a single machine $\ \ldots \ \ldots$  | 24 |

|   | 2.4  | Graph  | Processing Systems Accelerated by the GPU $\ \ldots \ \ldots$     | 28 |

|   | 2.5  | Summ   | ary                                                               | 33 |

| 3 | Co-S | Schedu | lling of Serial and Parallel Jobs                                 | 34 |

|   | 3.1  | Introd | uction                                                            | 34 |

|   | 3.2  | Forma  | lizing the job co-scheduling problem                              | 36 |

|   |      | 3.2.1  | Formalizing the co-scheduling of serial jobs                      | 37 |

|   |      | 3.2.2  | Formalizing the co-scheduling of serial and parallel jobs $$ .    | 38 |

|   | 3.3  | The gr | raph model for co-scheduling                                      | 42 |

|   |      | 3.3.1  | The graph model                                                   | 43 |

|   |      | 3.3.2  | Intuitive strategies to solve the graph model                     | 44 |

|   | 3.4  | Shorte | st valid path for serial jobs                                     | 46 |

|   |      | 3.4.1  | The SVP algorithm                                                 | 46 |

|   |      | 3.4.2  | Further optimization of SVP $\ \ldots \ \ldots \ \ldots \ \ldots$ | 51 |

|   | 3.5  | Shorte | st valid path for parallel jobs                                   | 51 |

|   |      | 3.5.1  | Co-scheduling PE jobs                                             | 52 |

|   |      | 3.5.2  | Co-scheduling PC jobs                                             | 55 |

|   | 3.6  | Co-sch | eduling jobs on multi-processor computers                         | 58 |

|   | 3.7  | Co-sch | eduling multi-thread jobs                                         | 60 |

|   | 3.8  | The A  | *-search-based algorithm                                          | 61 |

|   |      | 3.8.1  | Traditional A*-search algorithm                                   | 62 |

|   |      | 3.8.2  | SVPPC-A*                                                          | 63 |

|   |      | 3.8.3  | Case studies for the A*-search based algorithm                    | 65 |

|   | 3.9  | Heuris | tic A*-search Algorithm                                           | 65 |

|   | 3.10 | Cluste | ring approximation for finding the shortest valid path            | 68 |

|   | 3.11 | Evalua | tion                                                              | 70 |

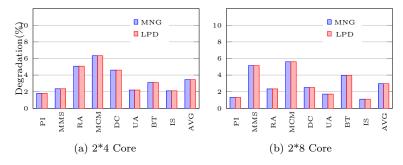

|   |      | 3.11.1 | Evaluating the O-SVP algorithm                                    | 72 |

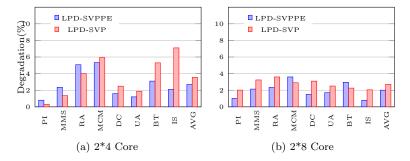

|   |               | 3.11.2                 | The O-SVPPE algorithm                                                                                                                        |

|---|---------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

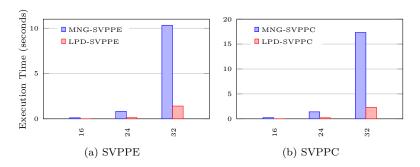

|   |               | 3.11.3                 | The O-SVPPC algorithm                                                                                                                        |

|   |               | 3.11.4                 | Scheduling in Multi-processor Computers                                                                                                      |

|   |               | 3.11.5                 | Scheduling Multi-threading Jobs 80                                                                                                           |

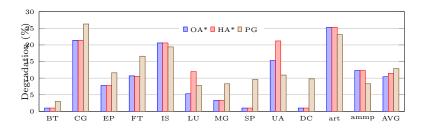

|   |               | 3.11.6                 | The A*-search-based algorithms 82                                                                                                            |

|   |               | 3.11.7                 | Heuristic A*-search algorithm                                                                                                                |

|   |               | 3.11.8                 | Efficiency of OA* and IP $\dots \dots \dots$ |

|   |               | 3.11.9                 | The optimization techniques 89                                                                                                               |

|   | 3.12          | Summ                   | ary                                                                                                                                          |

| 4 | Wo            | lfPath:                | Accelerating Iterative Graph Searching Algorithm                                                                                             |

|   | on (          | $\mathbf{GPU}$         | 93                                                                                                                                           |

|   | 4.1           | Introd                 | luction                                                                                                                                      |

|   | 4.2           | Repre                  | senting Co-Scheduling Graph in GPU 95                                                                                                        |

|   | 4.3           | WolfP                  | ath Framework                                                                                                                                |

|   |               | 4.3.1                  | Motivation: the limitation of current approach 98                                                                                            |

|   |               | 4.3.2                  | Computation model of WolfPath                                                                                                                |

|   |               | 4.3.3                  | Finding Optimal Co-scheduling solution with WolfPath $$ . $104$                                                                              |

|   | 4.4           | Gener                  | al Graph representation in WolfPath                                                                                                          |

|   |               | 4.4.1                  | Preprocessing                                                                                                                                |

|   |               | 4.4.2                  | Edge List Combination                                                                                                                        |

|   |               | 4.4.3                  | Out of GPU memory processing                                                                                                                 |

|   | 4.5           | Exper                  | imental Evaluation                                                                                                                           |

|   |               | 4.5.1                  | Performance comparison with CPU based $\mathbf{A}^*$ algorithm $$ . 112                                                                      |

|   |               | 4.5.2                  | Performance evaluation with general graphs 113                                                                                               |

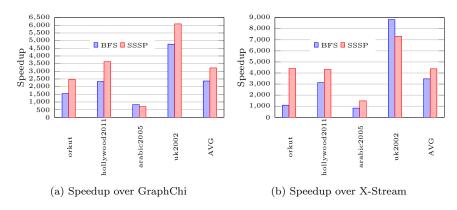

|   |               | 4.5.3                  | Memory occupied by different graph representation 117                                                                                        |

|   |               | 4.5.4                  | Pre-processing time                                                                                                                          |

|   | 4.6           | Summ                   | nary                                                                                                                                         |

| 5 | Wo            | lfGrap                 | h: an Edge-Centric graph processing framework on                                                                                             |

|   | $\mathbf{GP}$ | $\mathbf{U}\mathbf{s}$ | 120                                                                                                                                          |

|   | 5.1 | Introd | luction                                                                        |

|---|-----|--------|--------------------------------------------------------------------------------|

|   | 5.2 | An O   | verview of Edge Centric Processing on GPU 122                                  |

|   |     | 5.2.1  | Edge centric Graph data structure                                              |

|   |     | 5.2.2  | Computation model                                                              |

|   | 5.3 | In-me  | mory processing Engine in WolfGraph                                            |

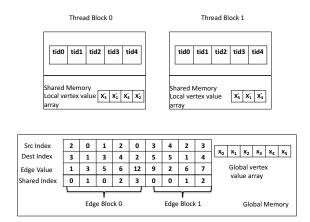

|   |     | 5.3.1  | Parallel processing in WolfGraph                                               |

|   |     | 5.3.2  | Two-level GPU processing and memory access pattern $132$                       |

|   |     | 5.3.3  | ${\bf Implementing\ GPU-based\ graph\ processing\ algorithms\ us-}$            |

|   |     |        | ing WolfGraph                                                                  |

|   | 5.4 | Out o  | f GPU memory processing                                                        |

|   |     | 5.4.1  | Graph Partition and Computation                                                |

|   |     | 5.4.2  | Concatenate Edge List representation                                           |

|   | 5.5 | Out-o  | f-Core Graph processing                                                        |

|   |     | 5.5.1  | Out-of-Core graph partitioning                                                 |

|   |     | 5.5.2  | Out-of-Core processing                                                         |

|   | 5.6 | Imple  | mentation of WolfGraph                                                         |

|   |     | 5.6.1  | Loading Engine                                                                 |

|   |     | 5.6.2  | Data Transfer Engine                                                           |

|   |     | 5.6.3  | Computation Engine                                                             |

|   | 5.7 | Evalua | ation                                                                          |

|   |     | 5.7.1  | Performance Evaluation                                                         |

|   |     | 5.7.2  | Global Memory efficiency                                                       |

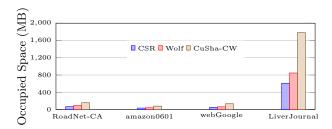

|   |     | 5.7.3  | Memory occupied by different graph representation $159$                        |

|   |     | 5.7.4  | Sensitivity Analysis of WolfGraph                                              |

|   | 5.8 | Summ   | nary                                                                           |

| e | Con | alusia | ns and Further Work 164                                                        |

| 6 | 6.1 |        | ns and Further Work  pping Graph-based Methods to Find Optimal or Near-optimal |

|   | 0.1 |        | heduling solutions                                                             |

|   | 6.2 |        |                                                                                |

|   | 6.2 | vvoiiP | ath: Accelerating the graphs with layered structure by GPU166                  |

| 6.3     | WolfGraph: A General Purpose GPU-based Large-Scale Graph |     |

|---------|----------------------------------------------------------|-----|

|         | Processing Framework                                     | 166 |

| 6.4     | Discussion                                               | 167 |

| 6.5     | Further Work                                             | 170 |

| Bibliog | graphy                                                   | 172 |

# List of Figures

| 1.1 | An illustration example for the difference between serial and par-  |    |

|-----|---------------------------------------------------------------------|----|

|     | allel jobs in calculating the performance degradation               | 4  |

| 2.1 | The Vertex State Machine in Pregel                                  | 21 |

| 2.2 | The execution model of Graphlab                                     | 23 |

| 2.3 | Shard Representation of the Graph                                   | 25 |

| 2.4 | GraphChi Execution model                                            | 26 |

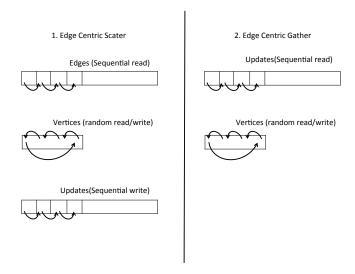

| 2.5 | Edge Centric Execution model                                        | 27 |

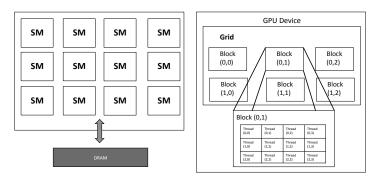

| 2.6 | GPGPU architecture and thread execution model in Cuda               | 29 |

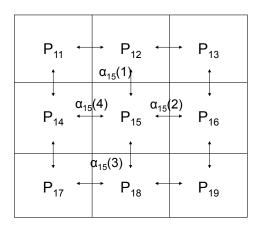

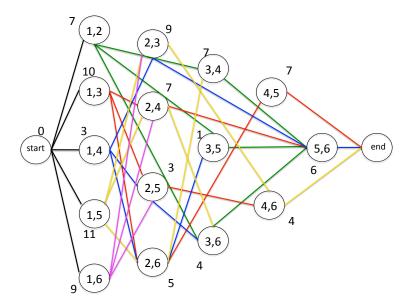

| 3.1 | An illustrative example for modelling the communication time $$ .   | 42 |

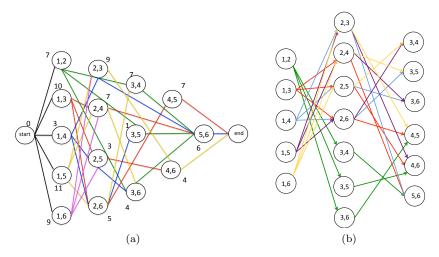

| 3.2 | The exemplar co-scheduling graph for co-scheduling 6 jobs on        |    |

|     | Dual-core machines; the list of numbers in each node is the node    |    |

|     | ID; A number in a node ID is a job ID; The edges of the same        |    |

|     | color form the possible co-scheduling solutions; The number next    |    |

|     | to the node is the node weight, i.e., total degradation of the jobs |    |

|     | in the node                                                         | 44 |

| 3.3 | The graph model for a mix of serial and parallel jobs               | 54 |

| 3.4 | The example of communication-aware process condensation $\ . \ .$   | 57 |

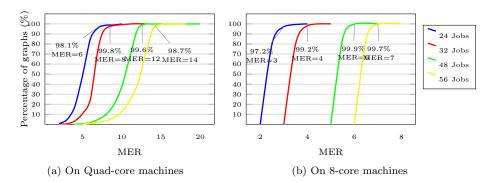

| 3.5 | Cumulative Distribution Function (CDF) of MER $\dots$               | 67 |

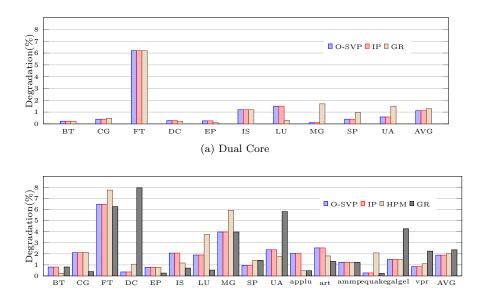

| 3.6 | Comparing the degradation of serial jobs under O-SVP, IP, HPM       |    |

|     | and GR                                                              | 73 |

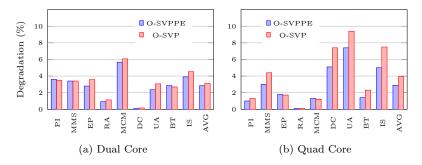

| 3.7  | Comparing the degradation under SVPPE and O-SVP for a mix                     |     |

|------|-------------------------------------------------------------------------------|-----|

|      | of PE and serial benchmark programs                                           | 75  |

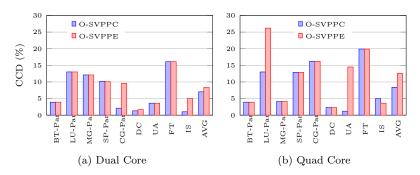

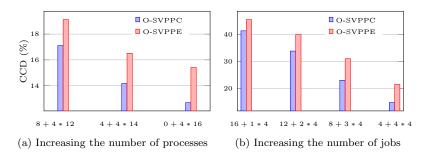

| 3.8  | Comparing the Communication-Combined Degradation (CCD)                        |     |

|      | obtained by SVPPC and SVPPE                                                   | 77  |

| 3.9  | Impact of the number of parallel jobs and parallel processes $\ . \ . \ .$    | 77  |

| 3.10 | Comparing the degradation caused by the straightforward method                |     |

|      | and the LPD method                                                            | 80  |

| 3.11 | Comparing the degradation under LPD-SVP and LPD-SVPPE                         |     |

|      | for a mix of PE and serial benchmark programs                                 | 80  |

| 3.12 | Comparing the Communication-Combined Degradation (CCD)                        |     |

|      | obtained by LPD-SVPPC and LPD-SVPPE                                           | 81  |

| 3.13 | Comparing the solving times of the LPD and the MNG method,                    |     |

|      | coupled with SVPPE and SVPPC $\ \ldots \ \ldots \ \ldots \ \ldots$            | 81  |

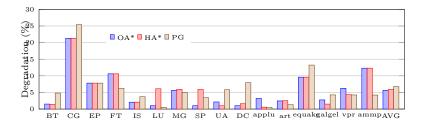

| 3.14 | Comparing performance degradations of benchmarking applica-                   |     |

|      | tions on Quad-core machines under OA*, HA* and PG                             | 86  |

| 3.15 | Comparing performance degradations of benchmarking applica-                   |     |

|      | tions on 8-core machines under OA*, HA* and PG $\ \ldots \ \ldots$ .          | 87  |

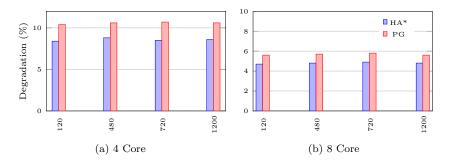

| 3.16 | Comparing the degradation under ${\rm HA}^*$ and PG algorithms $$             | 87  |

| 3.17 | Scalability of HA* on Quad-core and 8-core machines $\dots$                   | 88  |

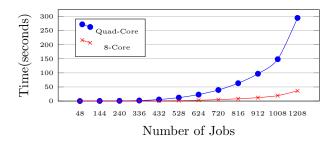

| 3.18 | Scalability of OA*                                                            | 90  |

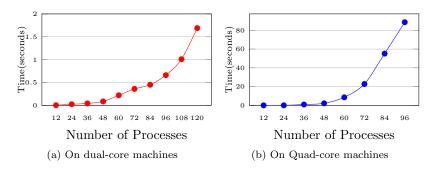

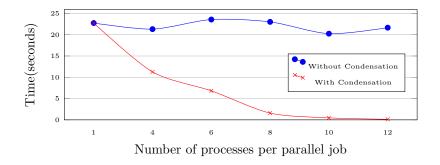

| 3.19 | Solving time with and without process condensation as the num-                |     |

|      | ber of processes per parallel job increases. The total number of              |     |

|      | parallel processes and serial jobs is 72                                      | 90  |

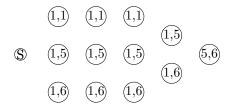

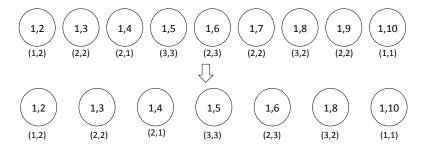

| 4.1  | The example co-scheduling graph from Chapter 3 and after reor-                |     |

|      | ganisation                                                                    | 96  |

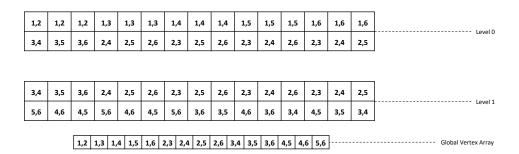

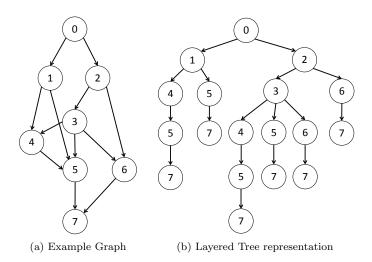

| 4.2  | An Example of layered edge list structure for graph in Figure $4.3\mathrm{a}$ | 97  |

| 4.3  | An Example graph and its Layered tree representation                          | 107 |

| 4.4  | Execution time comparison between WolfPath and A*-Search $$                   | 113 |

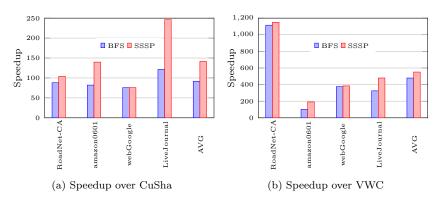

| 4.5  | Speedup of WolfPath over CuSha and VWC                                        | 114 |

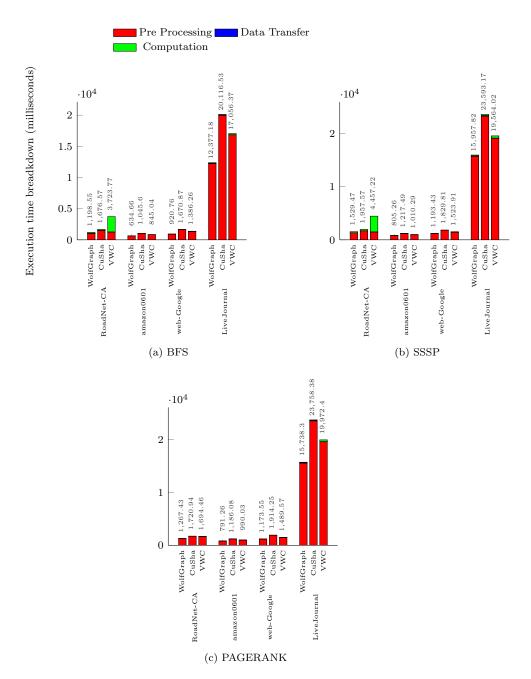

| 4.6  | Execution time breakdown of WolfPath, CuSha and VWC on                     |

|------|----------------------------------------------------------------------------|

|      | different algorithms and graphs. Reported times are in milliseconds. $115$ |

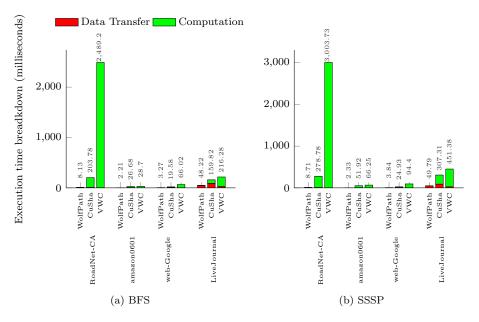

| 4.7  | Speedup of WolfPath over GraphChi and X-Stream                             |

| 4.8  | Memory occupied by each graph using CSR, CuSha-CW, WolfPath118             |

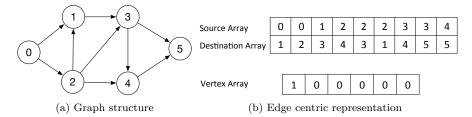

| 5.1  | An exemplar graph and its edge centric representation 123                  |

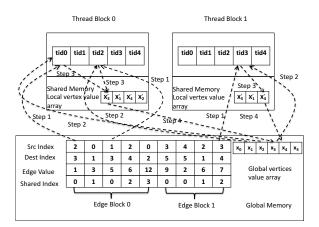

| 5.2  | The Edge block representation of graph in Figure 5.1a 128                  |

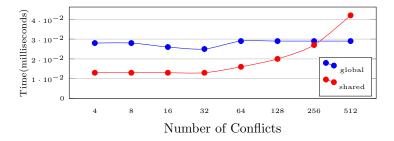

| 5.3  | The run-time of the benchmark program with different synchro-              |

|      | nization degree in shared memory and global memory $\dots \dots 130$       |

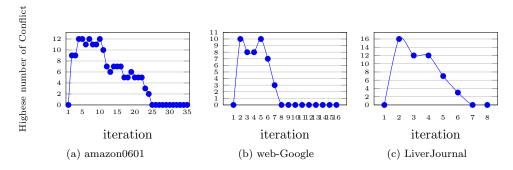

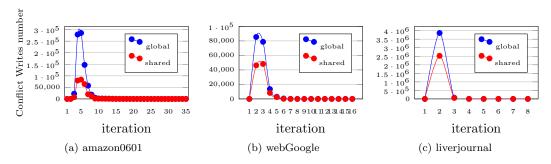

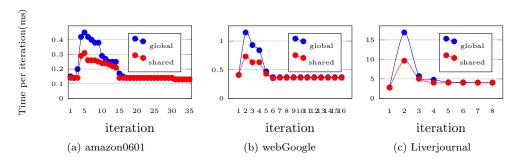

| 5.4  | Maximum conflict among all thread blocks                                   |

| 5.5  | Conflict writes to global memory with and without using shared             |

|      | memory                                                                     |

| 5.6  | Execution time per iteration. (ms)                                         |

| 5.7  | The process procedure inside edge blocks of graph shown in Figure          |

|      | 5.2                                                                        |

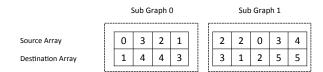

| 5.8  | An example of partitioning graph in Figure 5.1a into 2 sub-graphs $140$    |

| 5.9  | An example of building the concatenate edge list from 2 sub-               |

|      | graphs. The gray area represent the edges used to build the                |

|      | concatenate edge list in each iteration                                    |

| 5.10 | Architecture of WolfPath framework                                         |

| 5.11 | The speedup of WolfGraph over GraphChi and X-stream $\dots$ 153            |

| 5.12 | Execution time breakdown of WolfGraph, GraphChi and X-Stream               |

|      | on out-of-GPU-memory graphs. Reported times are in seconds $154$           |

| 5.13 | Execution time breakdown of WolfGraph, CuSha and VWC on                    |

|      | in-GPU-memory graphs. Reported times are in milliseconds. $$ $157$         |

| 5.14 | Average profiled efficiencies of WolfGraph with CuSha and VWC              |

|      | on liveJournal graph                                                       |

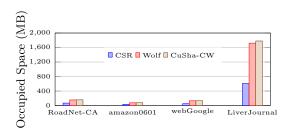

| 5.15 | Memory occupied by each graph using CSR, CuSha-CW, Wolf-                   |

|      | Graph Edge list representations over all benchmarks 160                    |

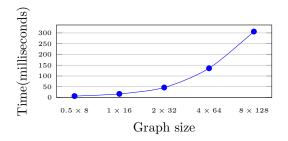

| 5.16 | Execution time of WolfGraph when Changing graph size with           |

|------|---------------------------------------------------------------------|

|      | graph degree equal to 16. A $x \times y$ graph has around x million |

|      | vertices and y million edges                                        |

|      |                                                                     |

# List of Tables

| 3.1  | The summary of all symbols used in this Chapter                               |

|------|-------------------------------------------------------------------------------|

| 3.2  | Comparison of IP and O-SVPpe for serial and parallel jobs $$ $$ 74            |

| 3.3  | Comparison of IP and O-SVPPC for serial and parallel jobs $76$                |

| 3.4  | Schedule result for Multi-threading program                                   |

| 3.5  | Comparing the solving time between MTP and SVPPE $\dots$ 82                   |

| 3.6  | The optimality of SVP-A*                                                      |

| 3.7  | The optimality of SVPPC-A*                                                    |

| 3.8  | Comparison of the strategies for setting $h(v)$ with serial jobs 85           |

| 3.9  | Comparison of the strategies for setting $h(v)$ with parallel jobs $$ . $$ 85 |

| 3.10 | Efficiency of different methods on Quad-core machines 89                      |

| 3.11 | Comparing the clustering method with O-SVP 91                                 |

| 4.1  | Real world graphs used in the experiments                                     |

| 4.2  | The computation time comparison of Original CuSha and Modi-                   |

|      | fied CuSha                                                                    |

| 4.3  | Memory to Computation                                                         |

| 4.4  | Co-scheduling graphs used in the experiments                                  |

| 4.5  | Real world graphs used in the experiments                                     |

| 4.6  | Execution time WolfPath, GraphChi and X-Stream on different                   |

|      | algorithms and graphs. Reported times are in seconds 117                      |

| 17   | Droppe cogging Time (Seconds)                                                 |

| 5.1 | Real world graphs used in the experiments                                   | 152 |

|-----|-----------------------------------------------------------------------------|-----|

| 5.2 | Execution time of WolfGraph, GraphChi and X-Stream on out-                  |     |

|     | of-core graphs. Reported times are in seconds. $\ \ldots \ \ldots \ \ldots$ | 156 |

| 5.3 | The execution time of out-of-GPU memory WolfGraph and in-                   |     |

|     | GPU memory VWC on different algorithms and graphs                           | 160 |

| 5.4 | The break down processing time with different thread block size             |     |

|     | on a<br>mazon0601 measured in miliseconds                                   | 162 |

| 5.5 | The break down processing time with different thread block size             |     |

|     | on Hollywood-2011 measured in seconds                                       | 162 |

|     |                                                                             |     |

## Chapter 1

## Introduction

Multicore processors have now become a mainstream product in CPU industry. In a multicore processor, multiple cores reside and share the resources on the same chip. However, running multiple applications on different cores could cause resource contention, which leads to performance degradation. Many studies have shown that it is possible to isolate some resources, such as disk bandwidth [142] [103], network bandwidth [47] [24] for the co-running jobs. However, it is very difficult to isolate the on-chip last level cache (LLC). This problem is known as the shared cache contention and has been studied extensively in the literature [71], [61], [152], [21]. The existing approaches to addressing on-chip shared cache contention fall into three categories: 1) Architecture-level solutions to improve hardware and provide isolation among threads[102] [121] [68], 2) System-level solutions to partition the cache for each application [143] [79] [69] [20], and 3) Software-level solutions to develop schedulers to reduce the contention [35] [38] [92] [60]. In these three categories, the architecture-level solution is still under active development by the processor vendors. The cache partitioning solution requires many changes in the existing system-level software (such as operating system) and therefore incurs high implementation cost. The third approach, developing contention-aware schedulers, is a fairly lightweight approach, and therefore attracts many researchers' attention, which is also the focus of this work.

## 1.1 Contention aware co-scheduling

Existing studies of the co-scheduling problem can be classified into two categories. Research in the first category aims at developing practical job scheduling systems that produce solutions on a best effort basis [127] [132], [153], [12], [51] [137]. Algorithms developed in this category are often heuristics-based in order to reduce computation cost. The work in the second category aims to develop the algorithms to either compute or approximate the optimal co-scheduling strategy (referred to as the *optimal co-scheduling problem* in the rest of this thesis) [28] [128] [59]. Due to the NP-hard nature [61] of this class of problems, obtaining an optimal solution is often a computation-expensive process and is typically performed offline. Although an optimal solution is not suitable for direct uses in online job scheduling systems, its solution provides the engineer with a unique insight into how much performance can be extracted if the system were best tuned. Additionally, knowing the gap between current and optimal performance can help the scheduler designers to weight the trade-off between efficiency and quality.

There are some research studies in contention-aware co-scheduling [11][38]. To the best of our knowledge, the existing methods that aim to find the optimal co-scheduling only consider the serial jobs [61]. The work in [61] modelled the optimal co-scheduling problem for serial jobs as an integer programming problem. However, there typically exists both serial and parallel jobs in the computing systems, such as clusters and clouds [139], [32], [114].

Some conventional systems disallow co-scheduling of parallel jobs and serial jobs in the same multicore machine. Take PBS [123] as an example. Although all jobs can share the same node in PBS (that is, parallel and serial jobs will share nodes without any configuration to the batch system), some sites decide to configure the PBS in the way that this does not happen. The main purpose

for this is to avoid the performance interference between different types of jobs since the performance degradation caused by interference is either unknown or its prediction is inaccurate.

This also happens in some data centers (clouds). When a task is submitted to a data center, a configuration file for the task is created to specify the rules for the cluster manager to run the task. By default, data centers do not restrict the sharing of the same node between different jobs. But the users can disallow co-locate this task with other tasks in the task configuration file[95]. However, disallowing job co-locations through either configuration or resource reservation is a major contributor to low machine utilization. For example, in the production clusters at Twitter with thousands of servers, managed by Mesos [55], the CPU utilization is consistently below 20%, and a 12,000-server Google cluster managed by Borg consistently achieves CPU utilization of 25-35% [32].

In order to improve resource utilization, it is necessary to consider both parallel jobs and serial jobs when designing co-scheduling systems. However, the existing methods of finding the optimal co-scheduling cannot be applied to the system that contains both parallel and serial jobs.

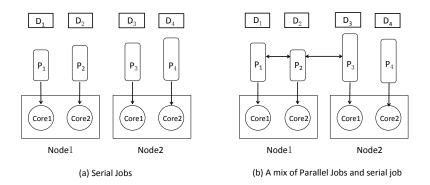

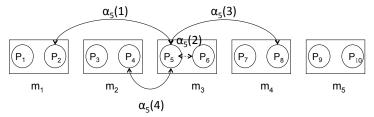

We use Figure 1.1 to illustrate why different considerations should be taken when co-scheduling parallel jobs. The figure considers two co-scheduling scenarios. In Figure 1a, 4 serial jobs (i.e., 4 processes  $p_1$ , ...,  $p_4$ ) are co-scheduled on two dual-core nodes, while in Figure 1b a serial job ( $p_4$ ) and a parallel job with 3 processes (i.e.,  $p_1$ ,  $p_2$  and  $p_3$ ) are co-scheduled.  $D_i$  drawn above  $p_i$  is the degradation of  $p_i$  in the co-scheduling solution. The arrows between  $p_1$  and  $p_2$  as well as between  $p_2$  and  $p_3$  represent the interactions between the parallel processes. In Figure 1a, the objective is to minimize the sum of the performance degradation suffered by each process (i.e.,  $D_1 + D_2 + D_3 + D_4$ ). In Figure 1b, the performance degradation (i.e., increased execution time) of the parallel job is dependent on the processes that has been affected the most and therefore completing the execution last. Therefore, the performance degradation of the parallel job should be computed by  $max(D_1, D_2, D_3)$ . The objective in Figure

1b is to find the co-scheduling solution that minimizes  $max(D_1, D_2, D_3) + D_4$ .

Figure 1.1: An illustration example for the difference between serial and parallel jobs in calculating the performance degradation

In order to address this problem, this thesis proposes a graph-based method to find the optimal co-scheduling solution for a mix of serial and parallel jobs. Two types of parallel job are considered in this thesis: Multi-Process Parallel (MPP) jobs, such as the jobs written in MPI (Message Passing Interface), and Multi-Thread Parallel (MTP) jobs, such as the jobs written in OpenMP.

The graph model presented in this thesis aims to provide theoretical insights into co-scheduling problems. That is, the optimal result founded by our model is used to compare with the scheduling results generated from other scheduling systems. However, due to the high complexity of finding the optimal scheduling solution, this process is timing consuming. Thus, the solving process of the graph model is performed offline. We argue that accelerating the solving process can relieve the model user from the long waiting time. Therefore, in this thesis, we also explore the possibility of accelerating the solving process by using GPU, this is because compare to other parallel processing platforms, GPU has the following advantages: first, GPU can bring high parallelism degree and performance to a single machine. Second, it is more energy-efficient than distributed systems.

## 1.2 Parallel Graph Processing

Many studies have shown that the graph theory can be used to solve scheduling problems [74], [130] [75] [28] [126] [25]. However, as shown in [150] [52] [149], when modelling optimal scheduling problem into graph problem, the graph size increases exponentially. For example, when using the method presented in [52] to schedule 64 jobs to 16 quad-core machines, the graph size is 16,777,216 nodes and 3,450,553,937 edges. It is challenging to process graphs of such a scale.

The demand for processing large-scale graphs efficiently has been growing recently. This is because graphs can be used to describe a wide range of objects, and computations on graph-based data structures are the core of many applications. Motivated by the need to process very large graphs, many frameworks have been developed for processing large graphs on distributed systems. Such frameworks include GPS [113] MocGraph [147] Trinity [116] Chaos [110] Chronos [48] Gram [138]. However, since developing distributed graph algorithms is challenging, some research studies aim to design the graph processing systems that can handle large graphs (with billions of edges) on a single PC. The results of these studies are FlashGraph [145], PathGraph [140], GraphQ[133], LLAMA [90], Ligra [118][119], Ringo [105]. However, these systems suffer from the limited degree of parallelism provided by conventional processors. To overcome this problem, a lot of research employs GPU to accelerate graph processing due to its massively parallel architecture, such as Medusa[146], Gunrock [135], CuSha [65] and MapGraph [40] [66] [117].

However, using GPU for efficient graph processing remains a challenging and open problem due to the following reasons. First, although GPU provides a massive degree of parallelism compared to CPU, its hardware architecture requires regular data access pattern to achieve the peak performance. However, most graphs are of highly irregular structure, which leads to the problems of irregular memory accesses and underutilization of GPU and consequently limits the performance of graph algorithms on GPU. For example, most existing graph

processing techniques [50] [29] [15] [82] employ the vertex-centric processing and rely on the CSR (Compressed Sparse Row) representation of graphs. Due to the poor locality in the CSR representation, however, visiting a node's neighbours usually leads to random memory accesses, which is known as non-coalesced accesses. Second, because GPU has the limited global memory space compared with CPU, it requires frequent data copying between device memory and host memory, which also results in poor performance. Third, as pointed out by Guo et al. [46], in the state-of-the-art GPU-based graph processing systems, the time spent in reading the graph from hard disk to memory and in constructing the data structure in memory constitute a big proportion of the total processing time for a large graph. Reducing this pre-processing time will significantly improve the overall performance of graph processing frameworks. Finally, Existing work of GPU-based graph processing assumes the entire graph can fit into the global memory of GPU. However, there are large-scale graphs that are even bigger than the GPU memory, which makes these works infeasible to solve massive scale graph problems. Lack of support for large-scale graphs beyond the capacity of device memory is pointed out as one of the most critical problems of the existing graph processing methods using GPUs.

#### 1.3 Research Contributions

In this thesis, the problem of finding the optimal co-scheduling for a mix of serial and parallel jobs is modelled as an Integer Programming (IP) problem first. Then the existing IP solvers can be used to find the optimal co-scheduling solution that minimizes the performance degradation. However, the IP-based method suffers from long processing time and poor scalability. Therefore, a graph-based method is further proposed in this thesis. A layered graph is constructed to model the co-scheduling problem on single processor machines. The problem of finding the optimal co-scheduling solutions is then modelled as finding the shortest VALID path in the graph. Moreover, this thesis develops a

set of algorithms to find the shortest valid path for both serial and parallel jobs. A number of optimization measures are also developed to increase the efficiency of these proposed algorithms (i.e., accelerate the solving process of finding the optimal co-scheduling solution). After these, the graph model and proposed algorithms are extended to co-schedule a mix of serial and parallel jobs on multi-processor machines.

Moreover, it has been shown that the A\*-search algorithm can effectively avoid the unnecessary searches when finding the optimal solution. In this thesis, an A\*-search-based algorithm is developed to combine the ability of the A\*-search algorithm and the proposed optimization measures in terms of accelerating the solving process. Further, a heuristic method, called heuristic A\*-search, is developed to find the near-optimal solutions efficiently. Finally, a flexible approximation technique is proposed so that we can control the scheduling efficiency by setting the requirement for the solution quality.

In order to accelerate the processing speed of our co-scheduling algorithms, a GPU-based graph processing framework called WolfPath is designed to accelerate the processing of the co-scheduling graph, by exploiting the special structure of the co-scheduling graph. WolfPath can also be used to process general graphs by adding the pre-processing steps to convert a general graph into a graph with similar graph structure as in the co-scheduling graph. The design of WolfPath concentrates on addressing the non-coalesced memory access to graph edges and frequent data exchange between GPU and CPU memories. In addition, by taking advantage of the graph structure, WolfPath is also able to process large graphs that cannot fit in the GPU memory.

Due to the long pre-processing time of WolfPath, WolfGraph is finally proposed in this thesis. By using the iterative graph computation model and carefully designed data structure, WolfGraph requires the minimum graph pre-processing. With carefully designed graph structure, WolfGraph requires less pre-processing time than other systems. A two-level thread synchronisation scheme, first in shared memory and then in global memory, is designed in Wolf-

Graph, which proves to be faster than the synchronisation in global memory only. WolfGraph can work as a general purpose graph processing framework that can accelerate any graph algorithms. In addition, by adding the support for the secondary storage, WolfGraph can handle the graphs that are even larger than the host memory.

## 1.4 Thesis Organisation

In Chapter 1, we discuss the motivations of the research presented in this thesis and outline the main research contributions. In Chapter 2.2, we describe two important components in designing co-scheduling systems: performance prediction and scheduling strategy. In Chapter 2.3, we discuss the challenges of processing large scale graphs and review some state-of-the-art techniques developed in graph process systems.

In Chapter 3, we extend the existing work from co-scheduling serial jobs to co-scheduling a mix of serial and parallel jobs. In Chapter 4, we use GPU to parallelise the algorithms proposed in Chapter 3, and extend the algorithms to a GPU-based graph processing framework, WolfPath. Chapter 5 presents WolfGraph, a general purpose GPU-based graph proposing framework that aims to reduce the graph pre-processing and support both GPU acceleration and secondary storage device. Finally, Chapter 6 concludes the thesis and discusses the future work.

## Chapter 2

# Literature Review

#### 2.1 Introduction

In multicore processor architectures, multiple cores reside on a chip are not fully independent but share resources such as caches and memory controllers with neighbouring cores. These shared resources are managed exclusively in hardware and are job-unaware. They treat the requests from different jobs running on different cores as if they were all requests from one single source. This means that they do not enforce any fairness or partitioning when different jobs use the resources. This is resulting in performance degradation due to competition for shared resources. Some researchers observed that an application could slow down by multiple folds if it shares resources with processes running on neighbouring cores, comparing with it running alone.

There has been significant interest in the research community in addressing shared resource contention on multicore processors. The majority of work required modifications to hardware and falls into one of two classes: performance aware cache modification [107] [58] [122] [120] [83] or performance-aware DRAM controller memory scheduling [84] [125] [57] [101]. These proposed solutions require changes to the hardware, major changes to the operating system, or both. As such, the majority of these techniques have only been evaluated in simula-

tion and, as of this writing; none of these promising solutions have yet been implemented in commercial systems.

Another research trend tends to deal with shared resource contention on the level of job scheduling [59] [134] [36] [11]. In this context job scheduling refers to mapping jobs to the cores of the multicore processors. Different mappings result in different combinations of jobs competing for shared resources. Some job combinations compete less aggressively for shared resources than others. Contention mitigation via job scheduling aims to find the job mappings that lead to the best possible performance.

The most common objective optimized by contention-aware schedulers is overall throughput. These schedulers typically aim to reduce the contention of jobs with high resource usage and thus lower the overall performance degradation for the workload. In designing such schedulers, there are two very important aspects that need to be considered: performance prediction and co-scheduling strategies. The performance prediction is used to estimate the performance when multiple jobs co-run together. The co-scheduling strategy makes the co-scheduling decision based on the information acquired by the prediction. Existing co-scheduling strategies can be classified into two categories. Researches in the first category aims at developing practical job scheduling systems that produce solutions based on heuristics algorithms [127] [132], [153], [12], [51] [137]. The work in the second category aims to develop the algorithms to either compute or approximate the optimal co-scheduling strategy [28] [128] [59].

As discussed in the last chapter, in this thesis, the GPU has been used to accelerate the solving process of the algorithms we proposed. Hence, in this chapter, we also reviewed the existing work in the literature on the graph processing techniques.

Most existing graph processing techniques can be classified into the following three categories: the first category is distributed systems. Such frameworks include Pregel[93], GraphLab[85], PowerGraph[43], GraphX [44]. However, developing distributed graph algorithms is challenging, some research studies aim to

design the graph processing systems that can handle large graphs (with billions of edges) on a single PC. The results of these studies lead to the second category, which is single machine shared memory graph processing systems, such as PathGraph [140], GraphQ [133], LLAMA [90] and GridGraph [151]. The third category graph processing technique is heterogeneous processing systems. In these systems, the accelerators (e.g., GPU, FPGA) are used to overcome the limited degree of parallelism provided by conventional processors. The results of these studies are Medusa[146], Gunrock [135], CuSha [65] and MapGraph [40].

This chapter contains two parts: the first part concentrates on reviewing the co-scheduling technologies, and the second part focuses on reviewing the graph processing systems. In the first part, we first discuss the existing performance prediction technologies in Section 2.2.2. Then we review the current co-scheduling strategies in Section 2.2.3. In the second part, we first discuss the challenges faced by graph processing systems designer in Section . We review the existing distributed graph systems in Section 2.3.2. We discuss the single machine graph processing systems in Section 2.3.3. In Section 2.4, we discuss the state-of-art GPU accelerated graph processing systems. We summarise and conclude this chapter in Section 2.5.

### 2.2 Job Co-scheduling

#### 2.2.1 Overview of Co-Scheduling Problems

Job co-scheduling has been used to address the contention problem in multicore systems. Its strategy is to assign jobs to cores in a way that the overall degradation is minimized. Normally, the input to the co-scheduling system is the performance of a job when it co-runs with other jobs. The output is the suitable schedules decision determined by the co-scheduling strategy.

The scheduling decision produced by the co-scheduling strategy has a huge impact on the performance of running jobs. The experiments conducted by Jiang in [61] can be used to demonstrate the effect of different scheduling strate-

gies.

The experiments conducted in [61] compare four different scheduling strategies, the optimal strategy; two well designed hierarchical strategies (hierarchical perfect matching and greedy algorithms) and a random strategy. The experiment results show that the optimal strategy degrades the overall average performance by 5.14%. The hierarchical perfect matching algorithm reduces the average degradation to 5.21%, whereas the greedy algorithm reduces it to 4.51%. The schedules produced by the random strategy causes more than 20% average performance degradation, which is about 300% worse than the optimal strategy. On the other hand, the schedules produced by the two approximation algorithms have 1.4% and 0.7% more degradations than the optimal strategy on average.

The above example demonstrates the importance of co-scheduling strategy and how it can affect the performance of co-running jobs. It also shows the needs for developing the optimal strategy. As used in the above example, the result produced by the optimal co-scheduling can be used to benchmark other scheduling algorithms.

#### 2.2.2 Performance Prediction

In order to make co-scheduling decisions, it is important to know the performance when multiple jobs co-run together. However, the search space is too big to benchmark all job combinations beforehand. Consider a system with two quad core CPUs, where the last level cache (LLC) is shared among all four cores on each CPU. There are 8! = 40,320 ways to map 8 jobs onto the 8 available cores. Many of these mappings are redundant. For example, if cores 0,1,2 and 3 share a LLC, then in all the mappings of four jobs, A, B, C and D, to 4 cores, the mappings  $\{(A, 0), (B, 1), (C, 2), (D, 3)\}$  and  $\{(A, 1), (B, 3), (C, 2), (D, 0)\}$  are equivalent in terms of performance. Nevertheless, there are still  $\binom{8}{4} = 70$  performance-unique mappings. For a cluster with thousands of nodes, the huge number of mappings makes it infeasible to benchmark them all to find optimised co-scheduling decisions. As such, it is very helpful to predict the

performance of different mappings without actually benchmarking all possible mapping combinations.

Many different techniques have been proposed for modelling performance degradation when the applications share resources on multicore systems [136], [16] [34] [148], [68], [36], [144], [19] [30] [129] [111]. The majority of the work focuses on sharing the LLC, which many researchers believed was the primary source of contention. The best known technique uses Stack Distance Profiles (SDP) and Miss Rate Curves (MRC) to predict the performance of multiple processes sharing the LLC. SDPs were first proposed by Mattson [96] and first used for the prediction purposes by [19]. The two techniques are a concise description of the memory reuse patterns of an application and a measure of the benefit derived from additional cache space.

In Chandra's method, SDP is used to record the hits and misses of each cache line when each process is running alone. The SDC model tries to construct a new SDP that merges the separate SDPs of individual processes that are to be co-running together. This model relies on the intuition that a process that reuses its cache lines more frequently will occupy more cache space than other processes. Based on this, the SDC model examines the cache hit count of each process' stack distance position. For each position, the process with the highest cache hit count is selected and copied into the merged profile. After the last position, the effective cache space for each process is computed based on the number of stack distance counters in the merged profile.

While SDPs were shown to be an effective tool for modelling performance degradation in the LLC, the main limitation of this method is that it is difficult to obtain the SDP information online on current systems. One approach to get around the need of using SDP is to approximate the cache occupancy of competing processes by using LLC misses and access rate, which can be easily collected by using the hardware performance counter available in most modern processors. In [7], they predict the performance of a process in a mapping by calculating the cache occupancy ratio first, which is the ratio of the LLC access

rate of this process to the LLC access rate of all the processes that share the same LLC cache. Then, they calculate the LLC miss rate that this process should experience under the measured LLC miss rate and the calculated cache occupancy ratio. A linear regression model is then used to predict the CPI (Cycles Per Instruction) from the predicted LLC miss rate and the measured L1 miss rate.

However, this method is rather complex. The recently proposed co-schedulers are trying to mitigate the problem. The schedulers proposed by [70], [37] [152] approximate performance degradation with the LLC miss rate only. Based on the observation and experiments, they showed that the applications that suffer from high LLC cache miss rate would suffer from high performance degradation. In addition, they also found that the jobs with high LLC cache miss would stress the entire memory hierarchy, and therefore these applications should not be scheduled together.

#### 2.2.3 Co-scheduling strategies

Many co-scheduling schemes have been proposed to reduce the shared cache contention in a multi-core processor. Different metrics can be used to indicate the resource contention, such as Cache Miss Rate (CMR), overuse of memory bandwidth, and performance degradation of co-running jobs. These schemes fall into the following two classes.

The first class of co-scheduling schemes aims at improving the runtime schedulers and providing online scheduling solutions. The work in in [11, 37, 152] proposed a decision mechanism called distributed intensity (DI). The mechanism first sorts all jobs to be scheduled based on their miss rates. It then begins pairing applications from both ends of the list. The application with a higher miss rate is paired with one with a lower rate. This process is conducted every time when a new job enters the queue, a job terminates or in every predefined time period.

The work in [70] proposes the decision mechanisms called OBS-L, OBS-X

and OBS-C. OBS-L attempts to reduce cache interference by spreading the total misses across all cache groups (a cache group consists of the shared LLC and the cores attached to it). Whenever a core becomes available, it selects a job whose miss rate is most complementary to other jobs that are sharing the cache. The OBS-X works by adding new jobs to the cache-group that has the smallest total miss rate. In addition, by monitoring the system workload at real time, it moves the jobs with the highest miss rate from the cache-group with the highest total miss rate to the cache-group with the lowest miss rate, so that the miss rate can be spread more evenly. Finally, OBS-C is based on the observation when pairing cache-heavy and cache-light jobs together, and the cache-light jobs tend to suffer less due to such pairing. Based on this observation, OBS-C extends the time slices of cache-light jobs, similar to the idea proposed by [36].

Based on the activity vectors [97], the scheduler presented in [98] makes the decision in the following way: A job's activity vector records its usage of system resources during the previous time slice, such as memory-bus, the LLC and the rest of the core. This usage is normalized to the theoretical maximum usage. The proposed scheduler performs the thread migrations, so that the jobs with complementary activity vectors can be co-scheduled together. They formalize this concept by measuring the variability of the activity vectors of jobs within the run queue. Higher variability indicates that the current jobs will yield high performance if being co-scheduled together. Another decision mechanism they proposed is called sorted co-scheduling. It works by grouping cores into pairs and attempts to schedule only complementary jobs on each core within the pair.

The work in [134] demonstrated that rearranging the scheduling order of input jobs can reduce the cache contention. In their work, by monitoring the cache miss of running jobs on each core and the jobs in the run queue, they rearrange the order of the jobs in run queue periodically. The purpose of their scheduler is to co-scheduler jobs with complementary cache miss rate together, therefore, if the job current running has a high cache miss, the job with low cache miss rate will be move to the front of the run queue and verse vice. Hence, the

complementary jobs will be co-scheduled together.

The work discussed above only considers the co-scheduling of serial jobs. In some cluster systems managed by conventional cluster management software such as PBS, the systems are configured in the way that parallel and serial jobs cannot share different cores on the same chip. This happens too in some data centres, where when a user submits a job, s/he can specify in the job's configuration file the rule of disallowing the co-scheduling of this job with other jobs on different cores of the same chip [95]. The main purpose of doing these is to avoid the performance interference between different types of jobs. However, disallowing the co-scheduling of parallel and serial jobs causes very poor resource utilization, especially as the number of cores in multicore machines increases.

Coupling with the support of accurate performance predictions, some popular cluster management systems [55] [95] [32] have been developed to co-schedule different types of jobs, including parallel jobs and serial jobs, to improve resource utilization. For example, The work in [95] presents a characterization methodology called Bubble-Up to enable the accurate prediction of performance degradation due to interference in data centres. The work has conducted the experiments with the real-world large-scale applications in Googles production data centres. The results demonstrated that the proposed prediction methodology can predict the performance interference between co-locating applications with an accuracy within 1% to 2% of the actual performance degradation.

The work in [32] applies the classification techniques to accurately determine the impact of interference on performance for each job. A cluster management system called Quasar is then developed to increase resource utilization in data centres through co-scheduling. Quasar can make better resource allocation (i.e., allocating the right amount of resources for each job) and resource assignment (i.e., selecting the specific servers and cores that will satisfy a given resource allocation) decisions to mitigate the interference between co-located workloads. The applications managed by Quasar include multi-server parallel jobs, such as Hadoop, Storm and Spark, and single-server jobs such as PARSEC, SPLASH-2,

BioParallel. A single-server job can be run on a single core or multiple cores using multi-threading. Quasar co-schedules parallel jobs and single-server jobs and uses the single-server jobs to fill any cluster capacity unused by parallel jobs.

Mesos [55] is a platform for sharing commodity clusters between multiple diverse cluster management frameworks, such as Hadoop [10], Torque [123], Spark [141] and etc, aiming to improve cluster utilization. Mesos has been used in production clusters such as at Twitter. In Mesos, the tasks from different cluster management frameworks (e.g., MPI jobs or serial jobs submitted to Torque and MapReduce jobs submitted to Hadoop) can be co-located in the same multicore server unless esoteric interdependencies between frameworks explicitly require that certain tasks from two frameworks cannot be co-located. The authors also pointed out that the situation of esoteric interdependencies is rare in practice.

The second class of co-scheduling schemes focuses on providing the basis for conducting performance analysis. It mainly aims to find the optimal coscheduling performance offline, in order to provide a performance target for other co-scheduling systems. The extensive research is conducted in [61] to find the co-scheduling solutions. The work models the co-scheduling problem for serial jobs as an Integer Programming (IP) problem, and then uses the existing IP solver to find the optimal co-scheduling solution. It also applies the perfect matching algorithm to find the optimal co-scheduling solution on 2-core processors. When the processor has more than 2-core (e.g., 4-core), a hierarchical perfect matching is proposed to first use perfect matching to schedule the jobs on two groups of cores. Then each group is further partitioned into two equal-sized subgroups of virtual cores and the perfect matching is applied again on these two subgroups. This procedure repeats until each subgroup contains only one physical core. They also proposes a greedy algorithm, which takes the following steps to find a good co-scheduling solution: 1) obtaining the set of all possible u-cardinality sets, 2) computing the politeness of a job, which is defined as the reciprocal of the sum of the degradations of all u-cardinality sets that contains that job, 3) in each round of scheduling, adding into the final co-scheduling solution the u-cardinality that satisfies these two conditions: i) it contains the job whose politeness is the smallest in the unallocated jobs; ii) its total degradation is smallest.

The co-scheduling studies in the [61] only consider the serial jobs and mainly apply the heuristic approach to find the solutions. Although it can obtain the optimal co-scheduling solution, it is only for serial jobs.

The work presented in this thesis falls into the second class. In this thesis, a new graph based method is developed to find the optimal co-scheduling solution offline for both serial and parallel jobs. Moreover, this thesis develops a set of approximation methods to find the near-optimal co-scheduling solution with lower time complexity. In this work, we choose SDC model to predicate the performance degradation of the co-running jobs. This is because although LLC cache miss rate can be easily obtained using the hardware counter and this value can be used to guide the scheduling, it is unable to show how much degradation a job will suffer when it is co-running with other jobs. On the other hand, as discussed above, the SDC model can predicate the performance degradation value. In addition, our scheduling method works offline. Therefore, obtaining SDP offline is not an issue in our work.

## 2.3 Graph processing systems

In this section, we first summarise the challenge in parallel graph processing, and then review the state-of-the-art graph processing systems proposed in the literature.

#### 2.3.1 Challenges in Graph Processing

The problems that are abstracted as graphs have some characteristics that make efficient parallelisation nontrivial. As stated in [88] [53], processing graph in parallel suffers from data-driven computation, irregular and unstructured data

structure, poor locality and high data access to computation ratio. We discuss these characteristics in detail in the following.

- Data Driven computation Graph computation is completely driven by the graph data. That being said, when executing a graph algorithm, the computation is dictated by the vertex and edge structure of the graph rather than being directly expressed by the code. As stated in [87] and [45], the performance of graph processing algorithms/frameworks are highly dependent on the graph structure. Hence how to design a graph processing system that can produce the same performance on different graph structures remains an open question. In addition, another problem caused by the data driven computation is that it is difficult to parallelise the graph algorithm according to its computational structure. This is because the structure of computation in the algorithm is not known beforehand.

- Irregular and Unstructured data structure The data in graph problems are typically highly irregular and unstructured. When processing graph in parallel, the graph data need to be partitioned first. Then, depending on the platform, the partitioned workload will be assigned to each compute node, process or thread. However, the irregular graph structure makes it difficult to evenly partition the data. The workload balance between different computation units cannot be achieved with unevenly partitioned data, which limits the scalability of the target system.

- Poor locality Graphs are used to represent the relationships between objects. However, the relationship between these objects may be irregular and unstructured. Therefore, the locality of computations and data access patterns is poor. On the modern processors, locality is the key to achieve high performance [94] [67] [33]. Thus, it is hard to achieve high performance for graph algorithms, especially for the graph computation requiring to access secondary storage devices, because random access to the hard disk is very slow compared to other components in computers.

Therefore, how to organise the graph data and design the corresponding computation model to improve the data locality is the key to improve the graph processing performance.

• High data access to computation ratio Most graph computation algorithms are based on the iterative computation model. In each iteration, the algorithms need to traverse the graph structure to fetch the data required by the computation. Most graph algorithms are computation light [64] and their memory access to computation ratio is high. As discussed before, the locality of the graph data is poor. Hence, the runtime is dominated by the wait for the memory access.

In next three sections, we review some well known graph processing algorithms and frameworks on different architectures, and discuss how these solutions tackle the challenges mentioned in this section.

#### 2.3.2 Distributed Graph Processing System

The most widespread class of parallel machines are distributed systems. A distributed system consists of multiple processing units where each unit has its own private memory. Data is partitioned over the separate nodes and explicit communication (e.g. message passing) is required to synchronize computation. Scaling out refers to adding more processing units to the system [100]. With cloud computing this type of scaling is available through Infrastructure as a Service (IaaS) [4].

Recently, many MapReduce [31] based general purpose data processing framework such as [17] [10] [141], and graph processing frameworks such as Pegasus [62] and GPS [113], started exploiting efficient parallel processing of large volumes of data on the distributed systems. In this section, we review some well known distributed graph processing systems proposed in the literature.

Pregel [93] is a distributed graph processing system developed by Google. The design of its vertex centric model is based on BSP (bulk synchronous

Figure 2.1: The Vertex State Machine in Pregel

parallel)[131]. Pregel partitions a graph based on vertices. Each graph partition contains a set of vertices and the edges associated with these vertices. Each partition is processed by one compute node in the system. In Pregel, the user defines the computation function. And this computation function will be invoked iteratively until the final result is found.

The iterative process in Pregel is performed as follows: in each iteration (or a superstep in Pregel's term), each active vertex (the vertex that needs to be computed) invokes the computation function. In the computation function, the vertex first reads the message sent from by its neighbours in the last iteration, computes the updated value based on the message received, and then sends the updated value to its neighbours through its outgoing edges. Its neighbours will receive this value as a message in the next iteration. Once a vertex sends the message, its state will change to inactive. An inactive vertex will become active when it receives a new message. The whole process terminates when there is no active vertex in the system. This process is called Vertex State Machine in Pregel and is illustrated in Figure 2.1.

Pregel uses message passing to communicate between different compute nodes. In each iteration, the number of messages send from one vertex to its neighbours is unlimited. The corresponding receiver will read these messages in the next iteration. In the distributed environment, in order to reduce the communication cost between compute nodes, the user can define a combination function to group multiple messages into one message and send it to another machine.

Giraph [5] is an open source implementation of Pregel. It is used by Facebook

to process the graphs with the scale of trillions of edges [23]. Facebook added the multi-threading support to the Giraph. So the performance of graph loading, writing and computation have been improved compare to Giraph and Pregel.

GraphLab [86] [85] is an asynchronous distributed shared-memory system. Unlike the synchronous communication in the BSP model, the GraphLab develops an asynchronous model called GAS (gather, apply, scatter) to implement its parallel computation in the distribute environment. A program in GraphLab implements a user-defined GAS function for each vertex. To avoid the imbalanced workload caused by high-degree vertices in graphs, a recent version of GraphLab, called PowerGraph [43], introduces a new graph partition scheme to handle this challenge. PowerGraph uses an algorithm called Vertex-cut partitioning, which partitions an input graph by cutting the vertex set, so that the edges of a high-degree vertex will be handled by multiple compute units. As a trade-off, vertices are replicated across compute units, and communication among compute units are required to guarantee that the vertex value on each replica remains consistent.

The GAS model works in the following way: in the Gather phase, each active vertex collects information from its neighbours' vertices and edges. In the Apply phase, each active vertex can update its value based on the information gathered and its old value. Finally, in the Scatter phase, each active vertex can activate the adjacent vertices. However, unlike Pregels message passing paradigm, GraphLab can only gather information from adjacent edges and scatter information to them, which limits the functionality of the GAS model.

GraphLab maintains a global scheduler. The compute units fetch vertices from the scheduler for processing, and add the neighbours of these vertices into the scheduler if needed. The GraphLab engine executes the user-defined GAS function on each active vertex until no vertex remains in the scheduler. The GraphLab scheduler determines the order to activate vertices, which enables GraphLab to provide both synchronous and asynchronous scheduling.

Unlike the synchronous model, in the asynchronous execution, change made

Figure 2.2: The execution model of Graphlab

to each vertex and edge during the Apply phase is committed immediately and visible to subsequent computation. Asynchronous execution can accelerate the convergence of some algorithms. For example, the PageRank algorithm can converge much faster with the asynchronous execution. However, asynchronous execution may incur the extra cost due to locking/unlocking.

GraphLab also provides synchronous execution model. In each iteration, it executes the GAS phases in order. The GAS function of each active vertex runs synchronously with a barrier at the end of each iteration. Changes made to the vertex value are committed at the end of each iteration. Vertices activated in an iteration are executed in the subsequent iteration. The whole process is shown in Figure 2.2.

GraphX [44] is a parallel graph processing system. It supports GraphLab and Pregel abstractions. GraphX is built on top of the more general data processing system Spark [141]. It introduces RDG (resilient distributed graph), which is an extension to the RDD (resilient distributed dataset) in Spark. With such extension, many graph algorithms can be implemented easily with the Spark's build in operations, such as join, map and group - by. In order to use Spark's

build in operation, GraphX also redesigned the vertex-cut algorithm.

Chaos [110] is a graph processing system designed for analytics on big graphs using clusters. Chaos builds on the X-Stream (discussed in detail in next section) [109] single-machine graph processing system, but scales out to multiple machines. Chaos adopts an edge-centric and GAS (Gather-Apply-Scatter) programming model. Due to the use of the edge-centric model, Chaos partitions the graph for sequential storage access, rather than for locality and load balance, resulting in much lower pre-processing times. In Chaos, the graph data is distributed uniformly and randomly across the cluster and does not attempt to achieve locality, based on the observation that in a small cluster network bandwidth far outstrips storage bandwidth. In addition, Chaos uses work stealing to allow multiple machines to work on a single partition, thereby achieving load balance at runtime. With all these features, Chaos is limited only by the aggregate bandwidth and capacity of all storage devices in the entire cluster.

#### 2.3.3 Graph Processing Systems on a single machine

Nowadays, with the ever increasing processing power of CPUs and large storage capacity, it is possible to process large-scale graph on a single machine. Compared to distribute systems, processing a graph on a single machine has the following advantages. First, the communication overhead is low. On a single machine with multiple cores/processors, the communication between these computing units is achieved by the shared memory, which is much faster compared to the network connection used in distributed systems. Second, from a user's perspective, managing, programming, debugging and optimising codes on a single machine is much easier than on distributed systems. Third, hardware and energy cost is relatively low.

Comparing with the fast growth rate of real-world problems, such as analysis on social networks or the web graph, the increasing rate of memory size is much slower. Therefore, processing large graphs from the persistent storage becomes the mainstream in the graph processing design based on single machines. Since

Figure 2.3: Shard Representation of the Graph

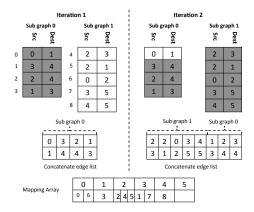

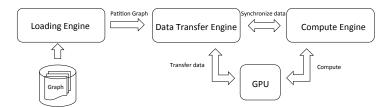

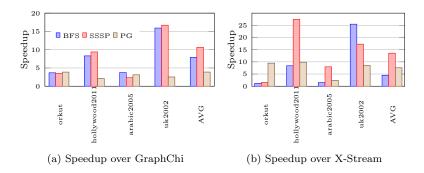

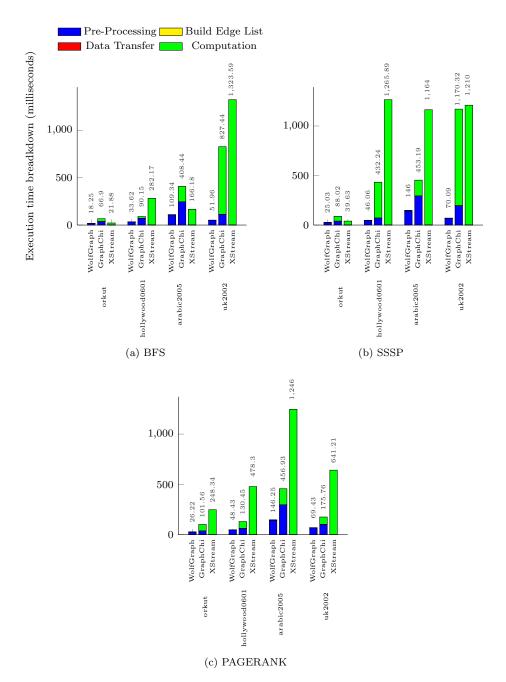

most single machine frameworks use the hard disk as the memory extension, how to read from and write to the hard disk efficiently becomes the primary challenge in designing the efficient graph processing framework on these systems. In this section, we discuss the techniques used by some representative single machine graph processing frameworks.