# All-GaN Integrated Cascode Heterojunction Field Effect Transistors

Sheng Jiang, Kean Boon Lee, Ivor Guiney, Pablo F. Miaja, Zaffar H. Zaidi, Hongtu Qian, David J.

Wallis, Andrew J. Forsyth, Senior Member, IEEE, Colin J. Humphreys, and Peter A. Houston

Abstract—All-GaN integrated cascode heterojunction field effect transistors were designed and fabricated for power switching applications. A threshold voltage of +2 V was achieved using a fluorine treatment and a metal-insulator-semiconductor gate structure on the enhancement mode part. The cascode device exhibited an output current of 300 mA/mm by matching the current drivability of both enhancement and depletion mode parts. The optimisation was achieved by shifting the threshold voltage of the depletion mode section to a more negative value with the addition of a dielectric layer under the gate. The switching performance of the cascode was compared the equivalent GaN enhancement-mode-only device by measuring the hard switching speed at 200 V under an inductive load in a double pulse tester. For the first time, we demonstrate the switching speed advantage of the cascode over equivalent GaN enhancement-mode-only devices, due to the reduced Miller-effect and the unique switching mechanisms. These observations suggest that practical power switches at high power and high switching frequency will benefit as part of an integrated cascode configuration.

*Index Terms*—Power electronics, Semiconductor devices, Semiconductor switches, SPICE, Semiconductor heterojunctions.<sup>1</sup>

# I. INTRODUCTION

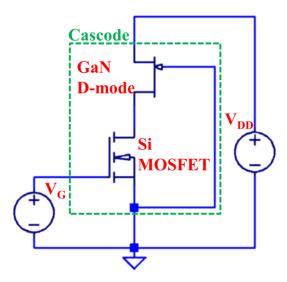

Cascode devices of GaN heterojunction field effect transistors (HFETs) plus Si MOSFETs have recently attracted much attention and are now commercially available [1-8]. The typical layout consists of a series connection of a high voltage depletion-mode (D-mode) GaN device and a low voltage enhancement-mode (E-mode) Si device as

Manuscript submitted December 20, 2016. This work was funded by the Engineering and Physical Sciences Research Council (EPSRC), United Kingdom, under EP/K014471/1 (Silicon Compatible GaN Power Electronics).

S. Jiang, K. B. Lee, Z. H. Zaidi, H. Qian and P. A. Houston are with the Department of Electronic and Electrical Engineering, University of Sheffield, Mappin Street, S1 3JD Sheffield, United Kingdom (e-mail: sjiang5@sheffield.ac.uk; kboon.lee@sheffield.ac.uk; hqian2@sheffield.ac.uk; p.a.houston@sheffield.ac.uk).

I. Guiney, D. J. Wallis and C. J. Humphreys are with the Department of Materials Science and Metallurgy, University of Cambridge, 27 Charles Babbage Road, CB3 0FS Cambridge, United Kingdom (e-mail: ig306@cam.ac.uk; djw24@cam.ac.uk; colin.humphreys@msm.cam.ac.uk).

P. F. Miaja and A. J. Forsyth are with the School of Electrical and Electronic Engineering, University of Manchester, M13 9PL, Manchester, United Kingdom (e-mail: pfmiaja@gmail.com; Andrew.Forsyth@manchester.ac.uk).

shown in Fig. 1. The GaN plus Si hybrid cascode device not only enables normally-off operation, but the cascode structure also offers the advantage of mitigation of the Miller effect, leading to an improved switching speed and reduced switching losses [8-9]. This makes cascode devices strong candidates for high power and high frequency switching applications. However, a few issues have been reported that may negate the speed advantage in the GaN plus Si hybrid cascode devices [10-13]. Firstly, the connections between the Si MOSFET and GaN devices result in increased parasitic inductance, which can cause excessive 'ringing' effects at fast switching speed thus limiting high frequency operation [12-13]. This brings challenges to the packaging design as reported by several studies on the effect of improved packages for the hybrid cascode devices [12-15]. In addition, due to the mismatch in intrinsic capacitances between the Si and GaN devices and the body diode in the Si MOSFET, the Si device can be driven into avalanche mode causing additional switching energy loss [10]. Moreover, the mismatched capacitances together with the parasitic inductance may cause large oscillations during turn-off under high current operation [11]. Adding an external capacitor between the drain and gate of the Si device was proposed in [10] and [11] to match the capacitance in the hybrid cascode device and prevent avalanche in the Si device, at the expense of additional parasitic inductance and careful designs in the device packaging are required.

In this study, we proposed an all-GaN integrated cascode device by replacing the Si MOSFET with a low voltage GaN E-mode device, so that the issues above can be addressed and the switching speed can be improved. The avalanche in the low voltage device during turn-off can be avoided due to the lack of body diode in the GaN E-mode device. In additional, the parasitic inductance can be minimized by monolithic integration, reducing the oscillation during turn-off operation [11] as well as leading to improved parallel operation [16]. Only a few studies on the integrated cascode structure have been reported and are limited to RF applications [17] and [18]. Additionally, there has been no analysis of the interrelationships between the E and D-mode devices, which is required to enable full optimization of the cascode design for switching applications. In this paper, we describe the design and fabrication of all-GaN integrated cascode devices for switching applications and present an analysis of the optimization requirements.

Fig. 1. Circuit diagram of GaN + Si MOSFET cascode configuration.

### II. DC CHARACTERISTICS

### A. Device fabrication

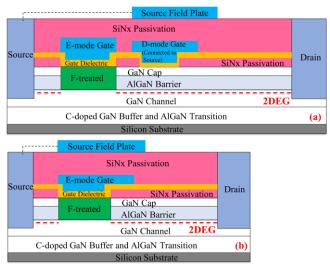

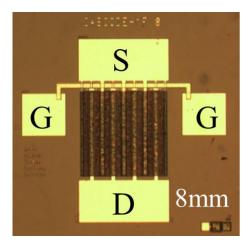

Fig. 2 shows the structures of an all-GaN integrated cascode device and a GaN E-mode-only device. The GaN/AlGaN/GaN heterojunction structure was grown on a 6-inch Si substrate using metal-organic chemical vapour deposition. All-GaN monolithically integrated cascode devices were fabricated using a standard GaN HFET fabrication process. Firstly, mesa isolation was performed by inductively coupled plasma etching to define the device area. An ohmic metal stack (Ti/Al/Ni/Au) was deposited and annealed at 830 °C to form the source and drain contacts. A typical contact resistance of 0.7  $\Omega$ ·mm was obtained from transmission line model measurements. Devices were passivated with 70 nm SiN<sub>x</sub> using plasma enhanced chemical vapour deposition (PECVD) and a 1.5 µm gate window was opened by etching through the SiN<sub>x</sub> layer using reactive ion etching (RIE) for both the E-mode and D-mode gate. A CHF<sub>3</sub> plasma-treatment in an RIE system was performed on the E-mode gate window to implant fluorine and shift the threshold voltage,  $V_{th}$ , from negative to positive [19]. A nominally 20 nm thick SiN<sub>x</sub> layer was deposited using PECVD prior to the T-shaped Ni/Au gate metal formation step to form a metal-insulator-semiconductor (MIS) gate structure in the E-mode section. Both a Schottky gate and an MIS gate for the D-mode part of the cascode structure were studied and will be discussed further in Section II-C. A gate-connect field plate (GFP) was formed on the gate of the D-mode part in the cascode configuration. Finally, devices were passivated with 300 nm of PECVD SiN<sub>x</sub> before the formation of the source-connected field plate (SFP), and Ti/Au bond pads were deposited after via opening in this  $SiN_x$ . Devices with gate widths,  $W_g$ , of 100 µm and 8 mm were fabricated. Fig. 3 shows the optical image of a 8 mm integrated cascode device. For comparision, D-mode-only and E-mode-only devices were also fabricated at the same time. All devices have a gate length of 1.5 µm, GFP extension ( $L_{GFP}$ ) of 1 µm and SFP ( $L_{SFP}$ ) extension of 2  $\mu$ m. The source-drain separation ( $L_{SD}$ ) of the E-mode-only and the cascode devices are 16 µm and 22.5 µm (additional 1.5  $\mu m$  D-mode gate length and 5  $\mu m$  gap between D-mode and E-mode gates), respectively.

Fig. 2. Device structure of (a) an all-GaN integrated cascode device and (b) an E-mode-only device with source field plate.

Fig. 3. Monolithically integrated AlGaN/GaN HFET cascode configuration with gate width of 8 mm.

# B. DC characteristics

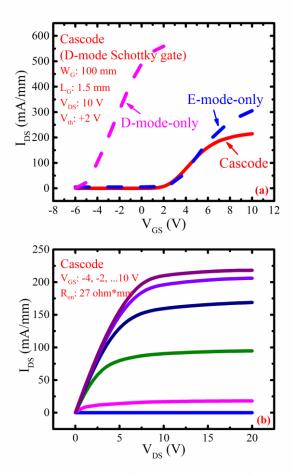

Fig. 4(a) shows the gate transfer characteristics of 100  $\mu$ m gate width E-mode-only and cascode devices. Both E-mode-only and cascode devices have a positive  $V_{th}$  of +2 V. It is noted that these devices may suffer from switching issues [20] due to relatively low  $V_{th}$  under high dv/dt operations and reliability issues due to the instability of the fluorine treatment [21-22] and MIS gate [23-25] techniques. Other E-mode technologies such as MOSFETs [26] and p-AlGaN gate [27] or other E-mode technologies which address these concerns can be applied to realize the integrated cascode configuration.

Fig. 4(b) shows the I-V characteristic of the cascode device. An on-resistance  $(R_{on})$  of 27  $\Omega$ ·mm (6 m  $\Omega$ ·cm<sup>2</sup> normalized to the active area between source and drain contacts and gate width) is measured from the cascode device, which is higher than other reported lateral single [26 and 28] and vertical devices [29-32]. The higher  $R_{on}$  is a

result of larger device area to accommodate both D-mode and E-mode parts. An output current of 200 mA/mm at  $V_{DS} = 10$ V and  $V_{GS} = +10$  V was measured from the cascode device. The D-mode-only device with a Schottky gate as shown in Fig. 4(a) has a  $V_{th}$  of -5.5 V and an output current around 575 mA/mm at  $V_{DS} = 10$  V and  $V_{GS} = +2$  V, while the E-mode-only device has the same  $V_{th}$  as the cascode but a higher output current close to 300 mA/mm. Since both the E-mode and D-mode parts have the same  $W_{\varrho}$ , the output current of the cascode structure is limited by the section with the lower current drivability, which is the E-mode part in this case. However, a lower output current in the cascode device compared to its equivalent E-mode-only device is observed and this indicates that some optimization of the design is required to achieve the maximum output current in the cascode device.

Fig. 4. (a) Gate transfer characteristics of an all-GaN integrated cascode device together with an equivalent E-mode-only device and a D-mode-only device (b) I-V characteristic of a 100 µm gate width cascode device.

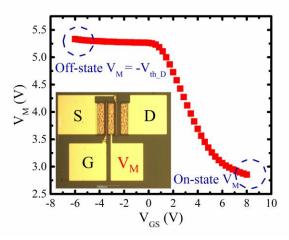

To facilitate the full understanding of how the cascode configuration works, particularly the voltage transients from off-state to on-state between the E-mode and D-mode, a cascode device with an additional ohmic pad between the D-mode gate and the E-mode gate was fabricated, as shown in the inset of Fig. 5. This layout does not change the I-V characteristics and allows the potential between the D-mode gate and the E-mode drain  $(V_{M_DC})$  to be monitored. Fig. 5 illustrates the measured  $V_{M_DC}$  as a function of the E-mode

gate bias,  $V_{GS}$ . During the off-state ( $V_{GS} < V_{th\_cascode}$ ),  $V_{M\_DC(off)}$  is equal to 5.3 V, which is the magnitude of the D-mode threshold voltage ( $V_{th\_D}$ ), and the channel under the D-mode gate metal is fully depleted. When  $V_{GS}$  increases to the on-state ( $V_{GS} > V_{th\_cascode}$ ),  $V_{M\_DC}$  drops and the channel under both D-mode and E-mode gates begin to conduct. At the on-state ( $V_{GS} = +8$  V),  $V_{M\_DC(on)}$  or  $V_{DS\_E.mode(on)}$  is equal to 2.8 V, which is below the 'knee' voltage of the E-mode part. As a result, the output current of the cascode device is limited by the drain-source voltage  $V_{DS\_E.mode(on)}$  of the E-mode part to guarantee the maximum current drivability of the cascode configuration.

Fig. 5. The middle point voltage  $(V_M)$  measured as a function of gate bias using a cascode device with an extra pad between the E-mode gate and the D-mode gate. The on-state value of  $V_M$  determines the conducting state of both D-mode and E-mode parts in the cascode device.

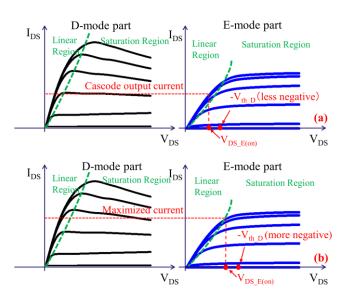

To optimize the output current of the cascode device, we equate the current through the D-mode and E-mode parts by engineering  $V_{th\_D}$  and hence control  $V_{M\_DC(on)}$  to ensure both parts are biased at the desired  $V_{DS}$  during the on-state. From Fig. 6,  $V_{M\_DC(on)}$  depends on the D-mode  $V_{th}$  and how much  $V_{M\_DC}$  drops when the gate bias increases. Therefore, by increasing the D-mode  $V_{th}$  (to be more negative),  $V_{M\_DC(on)}$  or  $V_{DS\_E-mode(on)}$  will also increase until it reaches the E-mode 'knee' voltage. However, a more negative  $V_{th\_D}$  also increases  $V_{M\_DC(off)}$  and hence increases the total energy stored at the middle node of the cascode during switching, which may increase the switching loss and limit the switching frequency. Therefore, it is vital to optimize the D-mode  $V_{th}$  to match the output current of both E-mode and D-mode sections for maximum overall current.

Fig. 6. (a) A less negative  $V_{th_D}$  yields a smaller  $V_{DS\_E(on)}$  and cascode output current (b) A more negative  $V_{th_D}$  pushes  $V_{DS\_E(on)}$  to the  $V_{knee\_E}$  and improve the cascode output current to its maximum value.

## C. Output current optimization

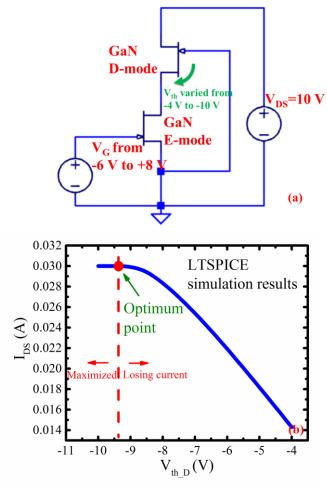

An LTSPICE simulation of the all-GaN cascode based on a Si JFET model was conducted to obtain the optimum D-mode  $V_{th}$  for the maximum overall current. Fig. 7(a) shows the schematic diagram of the simulation circuit. The device parameters used in the simulation were extracted experimentally as shown in Table I. Capacitive elements were not considered for the DC simulations.

Fig. 7. (a) Simulation circuit used to study the influence of the D-mode  $V_{th}$  on the output current of the cascode device. (b) Simulation results of drain current indicating an optimum D-mode  $V_{th}$  that leads to the maximum output current.

TABLE I Summary of Device parameters used in LTSPICE for  $V_{\mbox{\tiny TH}}$  engineering

|                              | D-mode part   | E-mode part            |

|------------------------------|---------------|------------------------|

| Gate width $(W_g)$           | 100 μm        | 100 μm                 |

| $Trans$ - $conductance(g_m)$ | 150 mS/mm     | 75 mS/mm               |

| On-resistance $(R_{on})$     | 13 Ω mm       | $14 \Omega \text{ mm}$ |

| Threshold voltage $(V_{th})$ | -4 V to -10 V | +2 V                   |

Fig. 7(b) shows the simulated output current of a cascode device with varying  $V_{th}$  of the D-mode part. The output current increases with increasing (negative) D-mode  $V_{th}$  as a result of increasing  $V_{DS\_E-mode(on)}$  as discussed above. The simulated current reaches its maximum value at a  $V_{th}$  of -9.2 V. At this point,  $V_{DS\_E-mode(on)}$  reaches the 'knee' voltage of the E-mode part (5.9 V) and hence no further improvement in the drain current is observed up to -10 V.

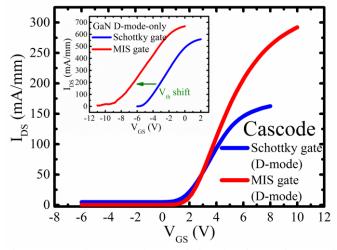

In order to verify the simulated results, two cascode structures were fabricated: one with a Schottky gate structure for the D-mode part and the other one with a nominally 10 nm PECVD  $SiN_x$  MIS gate to shift  $V_{th}$  more negative. Fig. 8 compares  $V_{th}$  of GaN D-mode-only devices with a MIS gate and Schottky gate.  $V_{th}$  of the D-mode devices is shifted from -5.5 V to -8.5 V with the MIS gate. The output current of the cascode configuration, as shown in the gate transfer characteristics, has been successfully improved from 150 to 300 mA/mm for the device with a D-mode MIS gate which is at similar level as the GaN E-mode-only device at  $V_{GS}$  =10 V.

This shows an excellent agreement with the simulated results and highlights the importance of matching both D-mode and E-mode to provide the maximum output current in the cascode devices.

Fig. 8. Cascode output characteristics showing an improved current from the optimised cascode structure resulting from an increase in the threshold voltage of the D-mode section (inset).

### III. SWITCHING PERFORMANCE

### A. Experimental

The hard switching performance was compared between an 8 mm gate width multi-finger gate all-GaN integrated cascode device and an 8 mm gate width GaN E-mode-only device using a double pulse tester (DPT). Fig. 9 shows the circuit diagram of the measurement setup of the DPT for the devices. A 0.5 mH inductive load was used to deliver a 0.4 A load current. A commercial gate driver supplying a voltage from -4 V to +6 V was used to switch on the device. A high gate resistor (100  $\Omega$ ) was used for both  $R_{G \ on}$  and  $R_{G \ off}$  to limit the gate drive current and hence slow the switching speed to better enable the switching comparisons. The load current to peak gate current ratio was around 10:1. Schottky diodes were used in both gate and load loops to minimise the reverse recovery time. The devices were wire bonded to a printed circuit board for the measurement and is shown highlighted in the box in Fig. 10. In total two pulses were applied to the gate of both devices. The first pulse was to build up the load current and the turn-off time was measured at the end of the first pulse. The turn-on transient was recorded at the beginning to the second pulse. The drain current was sensed by a 400 MHz bandwidth current viewing resistor T&M SDN-414-01. The gate voltage, drain current and drain voltage were monitored and recorded by a LeCroy WaveSurfer oscilloscope.

Fig. 9. Circuit diagram of Double Pulse Tester for switching speed measurement.

Fig. 10. An optical image of the DPT measurement setup.

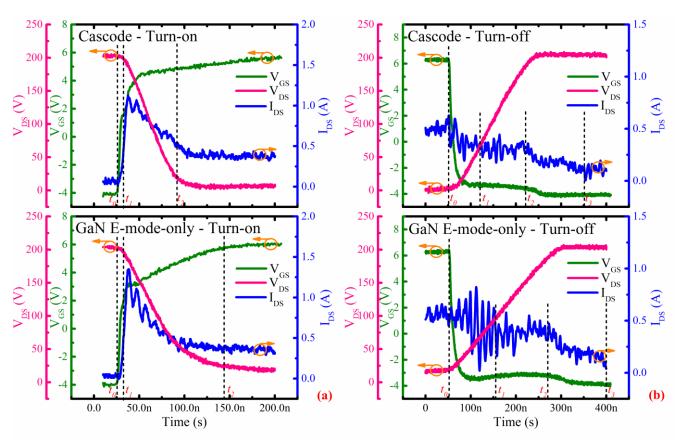

The switching speed of both cascode and GaN E-mode-only devices were measured at 200 V drain bias. Typical switching sequences of the cascode configuration has been detailed in [9], therefore, in this study, we will simplify the explanation of the switching waveforms and extract the voltage and current rise (fall) time for comparison. During turn-on from  $t_0 - t_1$ , as shown in Fig. 11 (a), the current in the cascode  $(I_{DS})$  rises up to the load current value after  $V_{GS}$  of both the E-mode and D-mode parts reach the value that can provide the load current. After that, the voltage of cascode  $(V_{DS})$  drops to the on-state voltage during  $t_1 - t_2$ . The overshoot of the current during the interval of  $t_1 - t_2$  is due to the discharge of the parallel capacitance in the load loop. During the turn-off from  $t_0 - t_2$ , as shown in Fig. 11 (b),  $V_{DS}$ rises up first to 200 V after the  $V_{GS}$  falls below  $V_{th}$ . In the interval of  $t_0 - t_I$ ,  $I_{DS}$  steps down from the load current due to the charging of the parasitic parallel capacitance in the load loop [8-9]. The ringing effect during  $t_0 - t_2$  is caused by the parasitic inductance in the circuit. The E-mode-only device shows an increased ringing amplitude compared to the cascode which could be caused by differences in the wire bonding geometry detail. However, this should have little influence on the comparison.  $V_{DS}$  reaches 200 V at  $t_2$ , where  $I_{DS}$  starts to drop and the turn-off transition ends at  $t_3$ .

Results of switching speed and energy loss for both

devices are summarized in Table II. The rise/fall times of  $V_{DS}$  and  $I_{DS}$  are extracted from 10% of their peak values to 90%. The energy loss is calculated by the integration of the IV product during the switching transition period. The all GaN integrated cascode device exhibits a faster switching speed compared to the E-mode-only device, resulting in approximately 35% and 21% less in the turn-off and turn-on switching energy losses, respectively.

gate is located on (for Schottky gate) or close to the semiconductor (for MIS gate) in the cascode, the channel under the D-mode gate will be fully depleted before the region between the D-mode and E-mode gates as the off-state drain bias increases. Once the channel under the D-mode gate is depleted ( $V_{th}$  for the Schottky and the MIS gate is 5 V and 9 V, respectively), the region between the D-mode and E-mode gates is effectively shielded from the drain bias and the

Fig. 11. 200V (a) turn-on and (b) turn-off switching waveforms for 8 mm cascode and 8 mm GaN E-mode-only devices.

TABLE II

SUMMARY OF SWITCHING RESULTS AT 200 V FOR THE ALL GAN INTEGRATED CASCODE CONFIGURATION AND GAN E-MODE-ONLY DEVICE

|          |                                   | Cascode | GaN<br>E-mode-only |

|----------|-----------------------------------|---------|--------------------|

| Turn-on  | Current rise time $(t_{r_{\_I}})$ | 5 ns    | 5 ns               |

|          | Voltage fall time $(t_{f_{-}V})$  | 51 ns   | 104 ns             |

|          | Turn-on energy loss $(E_{on})$    | 5.55 µJ | 7.02 µJ            |

| Turn-off | Current fall time $(t_{f_{-}}I)$  | 110 ns  | 110 ns             |

|          | Voltage rise time $(t_{r_{-}V})$  | 134 ns  | 200 ns             |

|          | Turn-off energy loss $(E_{off})$  | 9.39 µJ | 14.41 μ <b>J</b>   |

# B. Discussion

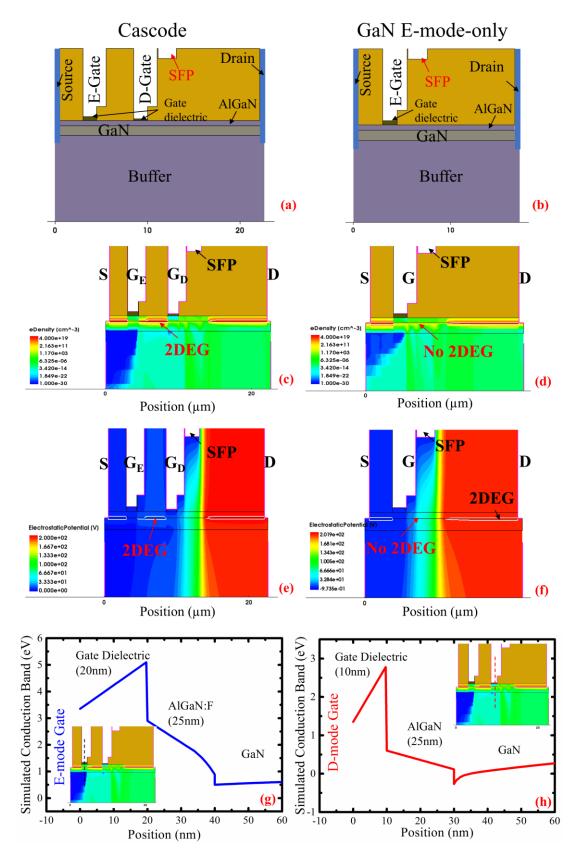

Inspection of Fig. 2(b) reveals the possibility of the SFP acting as a gate to form a D-mode device in a cascode-like configuration. However, the fundamental operational difference between the integrated cascode configuration and the E-mode-only device is the presence of 2DEG in the region between D-mode and E-mode gates during the off-state in the cascode. A TCAD simulation based on the structures of our cascode and E-mode-only devices was carried out, as shown in Fig. 12 (a) and (b). As the D-mode

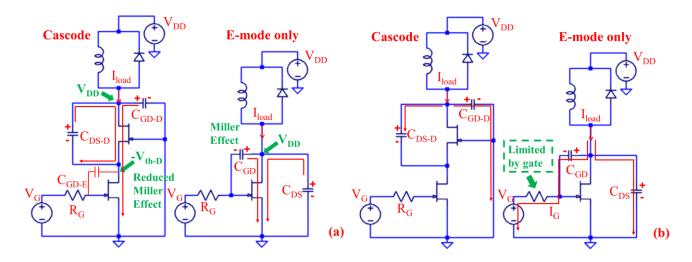

2DEG is retained as observed in the TCAD simulation in Fig. 12(c) and (e). This leads to reduction in the Miller effect as the Miller capacitance becomes the gate-drain capacitance of the E-mode part ( $C_{GD-E}$ ) and is only subject to a relatively low voltage (which is equal to the D-mode gate  $V_{th}$ ) and not the full drain bias during switching. On the other hand, the GaN E-mode-only device does not exhibit such behaviour as the depletion region extends continuously from the gate towards the drain as shown in Fig. 12(d) and (f) at high drain voltage. As a result,  $C_{GD}$  is subject to the high drain voltage during the switching processes. The SFP, on the other hand, will result in a reduction in the effective  $C_{GD}$  as it enhances the depletion region extension toward the drain compared to the device without SFP. Note that the value of the intrinsic capacitance  $(C_{GD})$  in the E-mode-only device can be several times smaller than  $C_{GD-E}$  in the cascode device due to a smaller E-mode gate to E-mode drain spacing in the latter. However, because the voltage at the drain of the E-mode part is much lower compared to the drain voltage, especially for high voltage applications, the cascode device still retains a benefit in the switching speed. The conduction band diagram under the E-mode and D-mode gate in the cascode device can be found in Fig. 12 (g) and (h), respectively.

Fig. 12. Device structures of (a) cascode and (b) E-mode-only used in TCAD simulation. TCAD simulation of electron density for (a) integrated cascode device and (b) single GaN E-mode device during off-state at  $V_{DS} = 200 \text{ V}$  and  $V_{GS E-mode} = 0$ V. TCAD simulation of electrostatic potential for (c) integrated cascode device and (d) single GaN E-mode device during off-state at  $V_{DS} = 200 \text{ V}$  and  $V_{GS\_E-mode} = 0 \text{ V}$ . The integrated cascode device is with  $L_{SD} = 22.5 \mu m$ ,  $L_{GD} = 12 \mu m$ ,  $L_{GFP} = 1 \mu m$ and  $L_{SFP}$  =2  $\mu$ m. The single GaN E-mode device is with  $L_{SD}$  =16  $\mu$ m,  $L_{GFP}$  =1  $\mu$ m and  $L_{SFP}$  =2  $\mu$ m. Conduction band diagram under (e) E-mode and (f) D-mode gate in the cascode device at  $V_{DS} = 0$  V and  $V_{GS\_E-mode} = 0$  V. A uniform fluorine concentration with sheet density of  $1.2 \times 10^{13}$  cm<sup>-2</sup> in the AlGaN barrier under E-mode MIS gate was used in the simulation.

Fig. 13. The charging and discharging paths of the output capacitance in the cascode device and GaN E-mode-only device with SFP during (a) turn-on process and (b) turn-off process.

Up to this point we have discussed the differences between the cascode and E-mode-only devices in terms of how they function. We will now consider the fundamental charging mechanisms of each, leading to the observed differences in the switching speeds. During turn-on, because the effective Miller capacitance is shifted to  $C_{GD-E}$  at the middle point, the majority of the energy stored in the output capacitance of the cascode device is dissipated with no Miller-effect. In addition, the energy stored in  $C_{DS-D}$  is discharged through the D-mode channel only, as shown in Fig. 13(a). Therefore, the fact that our D-mode device has a higher trans-conductance  $(g_m)$  and current drivability, which enables a larger discharging current within the D-mode channel, also contributes to the faster turn-on speed for the cascode device. During turn-off, the output capacitance of the cascode device is charged up to the high voltage by the full load current which is normally higher than the current in the gate loop, while the charging process of the output capacitance is limited by the current at the gate node in the E-mode-only device as illustrated in Fig. 13(b). This larger charging current is the main reason for the cascode device to be more advantageous in turn-off compared to turn-on, as observed in our experimental and [1], [4] and [8]. The turn-off advantage strongly depends on the load current to peak gate current ratio [8]. With a good gate driver and small gate resistor to provide sufficient gate current, the switching performance of the E-mode-only device is expected to be comparable to that of cascode device [8]. However, in this case the cascode device would still benefit from a lower di/dt in the gate loop to achieve the same switching speed. In addition, the availability of gate drivers with current capability close to the load current is limited in high current applications.

These observations show that, for practical high frequency and high power switches, the cascode device will have lower switching losses compared to the equivalent E-mode-only device. The price to pay for this advantage is a slightly more complex structure and a higher specific on-resistance.

# IV. CONCLUSION

The all-GaN integrated cascode configuration is an excellent candidate for high frequency high power applications due to the reduced Miller effect and reduced

parasitics. Devices were fabricated with a positive  $V_{th}$  of +2 V and output current of 300 mA/mm. Careful optimization of the D-mode device threshold voltage is required to achieve maximum cascode current drivability, which equals the output current of its E-mode part. The fundamental operational difference between an integrated cascode device and GaN E-mode-only device is discussed using TCAD simulation. This shows that the presence of the 2DEG in the region between D-mode and E-mode gates during the off-state is the key to enable the device cascode switching behaviour. All-GaN integrated cascode devices show relatively faster switching speed and 35% (21%) less in turn-off (turn-on) switching energy loss under 200 V hard switching measurement compared with GaN E-mode-only device with SFP. The advantage originates from the reduced effective Miller-capacitance and the unique switching mechanisms in the cascode device. Compared with the GaN E-mode-only device, the cascode can achieve a given switching frequency but with less current requirement in the gate driving circuit. As power increases, a greater benefit will accrue from switches incorporating a cascode structure.

### V. ACKNOWLEDGEMENT

The authors acknowledge financial support from the UK Engineering and Physics Sciences Research Council (EPSRC) under EP/K014471/1 (Silicon Compatible GaN Power Electronics).

### REFERENCES

- [1] X. Huang, Z. Liu, Q. Li, and F C. Lee, "Evaluation and application of 600 V GaN HEMT in cascode structure," *IEEE Trans. on Power Electronics*, vol. 29, no. 5, pp.2453-2461, May 2014.

- [2] T. Hirose, M. Imai, K. Joshin, K. Watanabe, T. Ogino, Y. Miyazaki, K. Shono, T. Hosoda and Y. Asai, "Dynamic performances of GaN-HEMT on Si in cascode configuration," in *Proc. APEC*, 2014, pp. 174-181.

- [3] X. Huang, F. C. Lee and Q. Li, "Characterization and Enhancement of High-Voltage Cascode GaN Devices,"

- IEEE Trans. Electron Devices, vol. 62, no. 2, pp. 270-277, Feb. 2015.

- [4] X. Huang, Q. Li, Z. Liu and F. C. Lee, "Analytical loss model of high voltage GaN HEMT in cascode configuration," IEEE Trans. Power Electronics, vol. 29, no. 5, pp. 2208-2219, May. 2014.

- [5] J. Roig, F. Bauwens, A. Banerjee, W. Jeon, A. Young, J. McDonald, B. Padmanabhan and C. Liu, "Unified theory of reverse blocking dynamics in high-voltage cascode devices," in *Proc. APEC*, 2015, pp. 1256-1261.

- [6] T. Kikkawa, T. Hosoda, K. Shono, K. Imanishi, Y. Asai, Y. F. Wu, L. Shen, K. Smith, D. Dunn, S. Chowdhury, P. Smith, J. Gritters, L. McCarthy, R. Barr, R. Lal, U. Mishra and P. Parikh, "Commercialization and reliability of 600 V GaN power switches," 2015 IEEE International Reliability Physics Symposium, Monterey, CA, 2015, pp. 6C.1.1-6C.1.6.

- [7] S. She, W. Zhang, X. Huang, W. Du, Z. Liu, F.C. Lee, and Q. Li, "Thermal analysis and improvement of cascode GaN HEMT in stack-die structure," in proc. IEEE ECCE, pp.5709-5715, 2014.

- [8] X. Huang, T. Liu, B. Li, F. C. Lee and Q. Li, "Evaluation and applications of 600V/650V enhancement-mode GaN devices," Wide Bandgap Power Devices and Applications (WiPDA), 2015 IEEE 3rd Workshop on, Blacksburg, VA, 2015, pp. 113-118.

- [9] A. R. Alonso, M. F. Diaz, D. G. Lamar, M. A. P. Azpeitia, M. M. Hernando and J. Sebastian, "Switching performance comparison of the SiC JFET and SiC JFET/Si MOSFET cascode configuration," IEEE Trans. Power Electronics, vol. 29, no. 5, pp. 2428-2440, May. 2014.

- [10] X. Huang, W. Du, F. C. Lee, Q. Li, and Z. Liu, "Avoiding Si MOSFET avalanche and achieving zero-voltage switching for cascode GaN devices," IEEE Trans. Power Electronics, vol. 31, no. 2, pp. 593-600, Jan. 2016.

- [11] W. Du, X. Huang, F. C. Lee, Q. Li and W. Zhang, "Avoiding divergent oscillation of cascode GaN device under high current turn-off condition," in *Proc. APEC*, 2016, pp. 1002-1009.

- [12] Z. Liu, X. Huang, F.C. Lee, and Q. Li, "Package parasitic inductance extraction and simulation model development for the high-voltage cascode GaN HEMT,"IEEE Trans. on Power Electron., vol.29, no.4, pp.1977-1985, Apr. 2014.

- [13] Z. Liu, X. Huang, F. C. Lee and Q. Li, "Simulation model development and verification for high voltage GaN HEMT in cascode structure," in *Proc. ECCE*, 2013, pp. 3579-3586.

- [14] Z. Liu, X. Huang, W. Zhang, F. C. Lee and Q. Li, "Evaluation of high-voltage cascode GaN HEMT in different packages," in Proc. APEC, 2014, pp. 168-173.

- [15] W. Zhang, X. Huang, Z. Liu, F. C. Lee, S. She, W. Du and Q. Li, "A New Package of High-Voltage Cascode Gallium Nitride Device for Megahertz Operation," IEEE Transactions on Power Electronics, vol. 31, no. 2, pp. 1344-1353, Feb. 2016.

- [16] H. Li, X. Zhang, L. Wen, J. Brothers, C. Yao, C. Han, L. Liu, J. Xu, J. Puukko and J. Wang, "Paralleled Operation of High-Voltage Cascode GaN HEMTs," IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 4, no. 3, pp. 815-823, Sept. 2016.

- [17] R. Wang, Y. Wu and K. J. Chen, "Gain improvement of enhancement-mode AlGaN/GaN high-electron-mobility transistors using dual-gate architecture," Jpn. J. Appl. Phys., vol. 47, no. 4, pp. 2820, Apr. 2008.

- [18] B. M. Green, K. K. Chu, J. A. Smart, V. Tilak, H. Kim, J. R. Shealy and L. F. Eastman, "Cascode connected AlGaN/GaN HEMTs on SiC substrates," IEEE Microwave Guided Wave Lett., vol. 10, no. 8, pp. 316-318, Aug. 2000.

- [19] Y. Cai, Y. Zhou, K. M. Lau and K. J. Chen, "Control of threshold voltage of AlGaN/GaN HEMTs by fluoride-based plasma treatment: From depletion mode to enhancement mode," IEEE Trans. Electron Devices, vol. 53, no. 9, pp. 2207-2215, Sept. 2006.

- [20] Q. Zhao and G. Stojcic, "Characterization of Cdv/dt Induced Power Loss in Synchronous Buck DC-DC Converters," IEEE Transactions on Power Electronics, vol. 22, no. 4, pp. 1508-1513, July 2007.

- [21] M. J. Wang, L. Yuan, K. J. Chen, F. J. Xu, and B. Shen, "Diffusion mechanism and the thermal stability of fluorine ions in GaN after ion implantation," Journal of applied physics, vol. 105, no. 8, pp. 083519, 2009.

- [22] F. Medjdoub, M. Alomari, J. F. Carlin, M. Gonschorek, E. Feltin, M. A. Py, C. Gaquie're, N. Grandjean and E. Kohn, "Effect of fluoride plasma treatment on InAlN/GaN HEMTs," Electronics Letters, vol. 44, no. 11, pp. 696-698, May 2008.

- [23] D. Bisi, M. Meneghini, F. A. Marino, D. Marcon, S. Stoffels, M. V. Hove, S. Decoutere, G. Meneghesso and E. Zanoni, "Kinetics of Buffer-Related R<sub>ON</sub>-Increase in GaN-on-Silicon MIS-HEMTs," IEEE Electron Device Letters, vol. 35, no. 10, pp. 1004-1006, Oct. 2014.

- [24] M. Meneghini, I. Rossetto, D. Bisi, M. Ruzzarin, M. V. Hove, S. Stoffels, T. Wu, D. Marcon, S. Decoutere, G. Meneghesso and E. Zanoni, "Negative Bias-Induced Threshold Voltage Instability in GaN-on-Si Power HEMTs," IEEE Electron Device Letters, vol. 37, no. 4, pp. 474-477, April 2016.

- [25] F. Sang, M. J. Wang, C. Zhang, M. Tao, B. Xie, C. P. Wen, J. Wang, Y. Hao, W. Wu and B. Shen, "Investigation of the threshold voltage drift in enhancement mode GaN MOSFET under negative gate bias stress," Japanese Journal of Applied Physics, vol. 54, no. 4, pp. 044101, 2015.

- [26] M. Wang, Y. Wang, C. Zhang, B. Xie, C. P. Wen, J. Wang, Y. Hao, W. Wu, K. J. Chen, and B. Shen, "900 V/1.6 m $\Omega$ ·cm<sup>2</sup> Normally Off Al<sub>2</sub>O<sub>3</sub>/GaN MOSFET on Silicon Substrate," IEEE Transactions on Electron Devices, vol. 61, no. 6, pp. 2035-2040, June 2014.

- [27] T. Sugiyama, D. Iida, M. Iwaya, S. Kamiyama, H. Amano, and I. Akasaki, "Threshold voltage control using SiNx in normally off AlGaN/GaN HFET with p-GaN gate," physica status solidi (c), vol. 7, no. 7-8 pp. 1980-1982, 2010.

- [28] S. Kaneko, M. Kuroda, M. Yanagihara, A. Ikoshi, H. Okita, T. Morita, K. Tanaka, M. Hikita, Y. Uemoto, S. Takahashi and T. Ueda, "Current-collapse-free operations up to 850 V by GaN-GIT utilizing hole injection from drain," 2015 IEEE 27th International Symposium on Power Semiconductor Devices & IC's (ISPSD), Hong Kong, 2015, pp. 41-44.

- [29] T. Oka, T. Ina, Y. Ueno and J. Nishii, "Over 10 A operation with switching characteristics of 1.2 kV-class vertical GaN trench MOSFETs on a bulk GaN

substrate," 2016 28th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Prague, 2016, pp. 459-462.

- [30] H. Nie, Q. Diduck, B. Alvarez, A. P. Edwards, B. M. Kayes, M. Zhang, G. Ye, T. Prunty, D. Bour and I. C. Kizilyalli, "1.5-kV and 2.2-  $m\Omega \cdot cm^2$  Vertical GaN Transistors on Bulk-GaN Substrates," IEEE Electron Device Letters, vol. 35, no. 9, pp. 939-941, Sept. 2014.

- [31] T. Oka, T. Ina, Y. Ueno and J. Nishii, "1.8 mΩ·cm<sup>2</sup> vertical GaN-based trench metal-oxide-semiconductor field-effect transistors on a free-standing GaN substrate for 1.2-kV-class operation." Applied Physics Express, vol. 8, no. 5, pp. 054101, 2015.

- [32] T. Oka, Y. Ueno, T. Ina and K. Hasegawa, "Vertical GaN-based trench metal oxide semiconductor field-effect transistors on a free-standing GaN substrate with blocking voltage of 1.6 kV," Applied Physics Express, vol. 7, no. 2, pp. 021002, 2014.

**Sheng Jiang** received his B.Sc.(Eng) degree from East China University of Science and Technology (ECUST), Shanghai, China, in 2011 and MSc(Eng) degree from the University of Sheffield, Sheffield, U.K., in 2013. He is currently a PhD student in the department of

Electronic and Electrical Engineering, the University of Sheffield. His research interest includes design, fabrication and characterisation of GaN based HFETs for high frequency high power applications.

**Kean Boon Lee** received the Ph.D. degree in electronic engineering from The University of Sheffield, Sheffield, U.K., in 2010. He is currently a Lecturer with The University of Sheffield, Sheffield, U.K. His current research interests include wide bandgap semiconductors and high-voltage/high-speed GaN HEMT

technologies.

**Ivor Guiney** is currently with the Department of Materials Science and Metallurgy, University of Cambridge.

Pablo F. Miaja (S'07 M'13) was born in Oviedo, Spain, in 1984. He received the M.S. degree in telecommunication engineering from the University of Oviedo (Spain) in 2007 and in 2012 the PhD. degree from the same university. Between December 2007 and November 2014 he worked as a researcher at the

Electronic Power Supply Systems Group of the University of Oviedo. Between November 2014 and May 2016 he was a Research Associate at the Power conversion Group of the University of Manchester (U.K). His research interests include dc/dc conversion, digital control of switched converters and power-supply systems for communication equipments.

Zaffar Zaidi completed his PhD in Electronic Engineering from The University of Sheffield, United Kingdom in 2015. Presently, he is working in The University of Sheffield as a

research associate. His area of interest includes GaN based high power and high speed devices

Hongtu Qian received his first class honours degree in Electronic Engineering from the University of Sheffield, Sheffield, U.K., in 2013. He is currently a PhD student in the department of Electronic and Electrical Engineering, the University

of Sheffield. His current research interest includes development of novel energy efficient vertical field effect devices in GaN-related materials for power switching applications.

Dr David Wallis has a first class honours degree in Physics and Computing and a PhD in Microstructural Physics from the University of Cambridge. He has more than 25 years experience in the characterisation and growth of III-V semiconductor materials

and has been involved in the growth of GaN by MOCVD since 2002. He was the technical lead for GaN characterisation and growth at QinetiQ (formerly RSRE and DERA) until 2011. Between 2012 and 2016 Dr Wallis worked for Plessey Semiconductors Leading the technical development of GaN based LEDs on large area Si substrates for commercial applications. In March 2016 he took up an EPSRC Manufacturing fellowship based at the University of Cambridge and is currently leading the development of GaN based device structures for a variety of optical and electronics applications.

Andrew J. Forsyth (M'98) received the B.Sc.(Eng) degree from Imperial College, London, U.K., in 1981 and the Ph.D. degree from the University of Cambridge, Cambridge, U.K., in 1987. He was a Design Engineer with GEC Electrical Projects Ltd from 1981 to 1983, a Lecturer at the University of Bath from 1986-1990, and a Lecturer / Senior Lecturer at Birmingham

University from 1991 to 2004. Since 2004 he has been Professor of Power Electronics at the University of Manchester, Manchester U.K. His research interests include high-frequency converters and magnetic components, wide-band-gap device applications, more-electric aircraft and electric vehicle systems.

**Colin Humphrevs** is Professor of Materials Science and Director of Research in the Department of Materials Science and Metallurgy, University of Cambridge, and a Fellow of Selwyn College, Cambridge. He is a Fellow of the Royal Society and a Fellow of the Royal Academy of Engineering. He

founded and directs the Cambridge Centre for Gallium Nitride (GaN). He founded two spin-off companies to exploit the research of his group on low-cost LEDs for home and office lighting. The companies were acquired in February 2012 by Plessey, which is now manufacturing LEDs based on

# > REPLACE THIS LINE WITH YOUR PAPER IDENTIFICATION NUMBER (DOUBLE-CLICK HERE TO EDIT) < 11

this technology at their factory in Plymouth, UK. He founded and directs the Cambridge/Rolls-Royce Centre for Advanced Materials for Aerospace. His h-index is 56 and his publications receive over 1000 citations per year.

**Peter A. Houston** received the B.Sc. degree (Hons.) in physics and the Ph.D. degree from Strathclyde University, Glasgow, U.K., in 1972 and 1975, respectively. He is currently Professor of electronic devices with a specific research interest in the design and fabrication of GaN – based HEMTs for power switching applications.