# **Durham E-Theses**

# Multi-microprocessor power system simulation

Flaxman, J. W.

#### How to cite:

Flaxman, J. W. (1987) *Multi-microprocessor power system simulation*, Durham theses, Durham University. Available at Durham E-Theses Online: http://etheses.dur.ac.uk/6762/

#### Use policy

The full-text may be used and/or reproduced, and given to third parties in any format or medium, without prior permission or charge, for personal research or study, educational, or not-for-profit purposes provided that:

- a full bibliographic reference is made to the original source

- a link is made to the metadata record in Durham E-Theses

- the full-text is not changed in any way

The full-text must not be sold in any format or medium without the formal permission of the copyright holders.

Please consult the full Durham E-Theses policy for further details.

# NULTI-MICROPROCESSOR POWER

# SYSTEN SIMULATION

A Ph.D. THESIS

by

# J.W. FLAXMAN

UNIVERSITY OF DURHAM

SCHOOL OF ENGINEERING

# AND APPLIED SCIENCE

1987

The copyright of this thesis rests with the author. No quotation from it should be published without his prior written consent and information derived from it should be acknowledged.

#### MULTI-MICROPROCESSOR POWER SYSTEM SIMULATION

## A Ph.D. THESIS by J.W. FLAXMAN 1987

## ABSTRACT

This thesis presents the results of research performed into the simulation of electrical power systems using a set of microprocessors operating in parallel. The uses and methods of simulation on analog and single processor computers are discussed as well as on multiple processor machines. It then considers various methods already used in the field of simulation for both the dynamic and network sets of equations in detail and the problems of using them on parallel processors. Several possible methods of parallel simulation are proposed and the best of these developed into a detailed algorithm for simulating both the dynamic and network portions of the power system .

to

The different types of multiprocessor system are looked at , both in terms of physical configuration and the type of hardware used to implement the different types of system . The problems inherent in parallel computing are discussed and a form of multiprocessor, suitable for the simulation algorithm, is then developed taking these problems into account . The hardware is developed using widely available hardware and the algorithm is then implemented upon this hardware .

The results obtained using the simulator show that the proposed system provides a more economical solution, both in terms of the time taken in producing results and in the cost of the system, when compared with a conventional single processor computing system such as a mini computer.

# ACKNOWLEDGEMENTS

I would like to express my thanks to those people, without whom my research and this thesis would have been impossible; Professor M.J.H. Sterling for his help and guidance . Dr. M.R Irving and the O.C.E.P.S. research group at Durham for their assistance . Heather, my wife, for her encouragement, support and endless supply of coffee . My parents for the hours of proof reading and constructive comments and finally my grandparents for helping to finance the purchase of my word processor .

# LIST OF CONTENTS

# CHAPTER

2.

36

| 1.    | Introduction:                             | 11 |

|-------|-------------------------------------------|----|

| 1.1   | Simulator uses                            | 13 |

| 1.1.1 | Energy management system development      | 14 |

| 1.1.2 | Transient studies                         | 16 |

| 1.1.3 | Operator training                         | 17 |

| 1.1.4 | Teaching                                  | 19 |

| 1.2   | Methods of simulation                     | 20 |

| 1.2.1 | Analog and hybrid simulators              | 20 |

| 1.2.2 | Load flow type simulators                 | 22 |

| 1.2.3 | Combined dynamic/algebraic simulators     | 23 |

| 1.3   | Simulator hardware                        | 24 |

| 1.3.1 | Mainframe and supercomputers              | 25 |

| 1.3.2 | Midi and minicomputers                    | 26 |

| 1.3.3 | Array processors                          | 27 |

| 1.3.4 | Microprocessors and multi microprocessors | 28 |

| 1.4   | Multiprocessor simulation                 | 30 |

| 1.4.1 | Hardware support                          | 31 |

| 1.4.2 | Software support                          | 32 |

| 1.5   | Research objectives                       | 33 |

| 1.6   | Thesis layout                             | 34 |

|       |                                           |    |

Generation and load modelling 37 Generating equipment models 2.1

| 2.1.1    | Supply system                 | 38 |

|----------|-------------------------------|----|

| 2.1.2    | Prime mover modelling         | 40 |

| 2.1.3    | Shaft modelling               | 43 |

| 2.1.4    | Synchronous machine modelling | 43 |

| 2.1.5    | Excitation system modelling   | 47 |

| 2.2      | Load modelling                | 48 |

| 2.2.1    | General load model            | 48 |

| 2.2.2    | Dynamic load model            | 49 |

|          |                               |    |

| 3. Netwo | ork solution                  | 50 |

| 3.1      | Gauss method                  | 50 |

| 3.2      | Newton-Raphson method         | 55 |

| 3.3      | Diakoptics                    | 61 |

| 3.4      | Direct method                 | 68 |

|          |                               |    |

| 4. Simu  | lator theory                  | 70 |

| 4.1      | Generator representation      | 71 |

| 4.2      | Load representation           | 76 |

| 4.2.1    | Synchronous load model        | 76 |

| 4.2.2    | General load model            | 77 |

| 4.3      | Network representation        | 80 |

| 4.4      | Matrix alteration algorithm   | 87 |

|          |                               |    |

| 5. Nult  | iprocessor software design    | 91 |

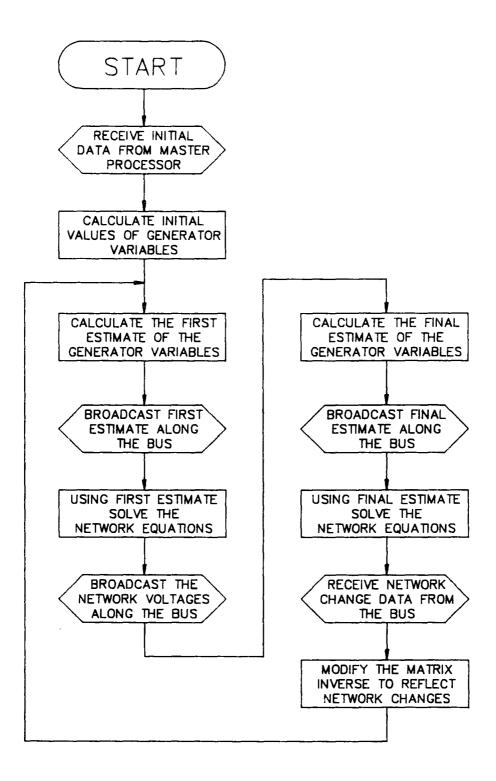

| 5.1 .    | Master processor software     | 91 |

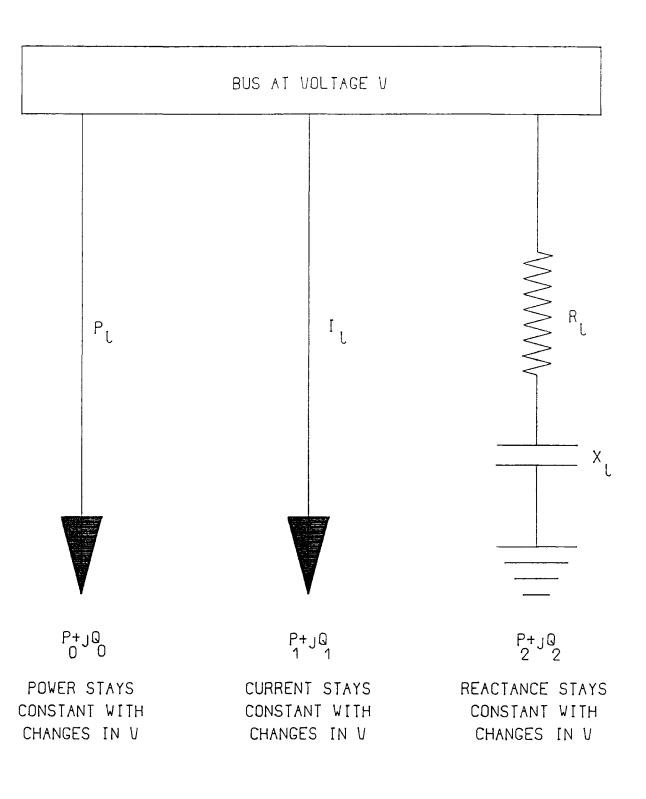

| 5.1.1    | Simulator initialisation      | 93 |

| 5.1.2    | Broadcast control             | 94 |

| 5.1.3 | Result corruption and transfer | 95         |

|-------|--------------------------------|------------|

| 5.1.4 | Simulator control              | 97         |

| 5.2   | Slave processor software       | 98         |

| 5.2.1 | Slave initialisation           | 9 <b>9</b> |

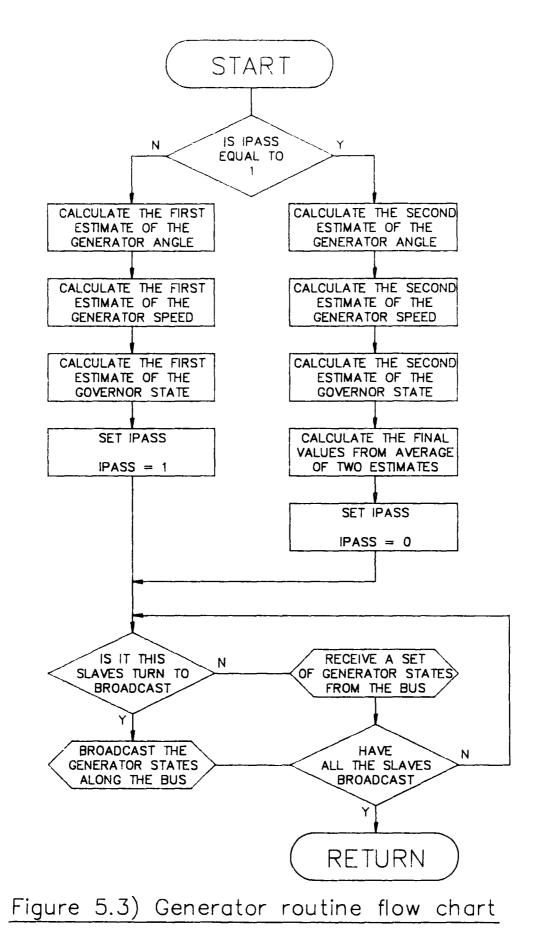

| 5.2.2 | Generator routine              | 101        |

| 5.2.3 | Load routine                   | 103        |

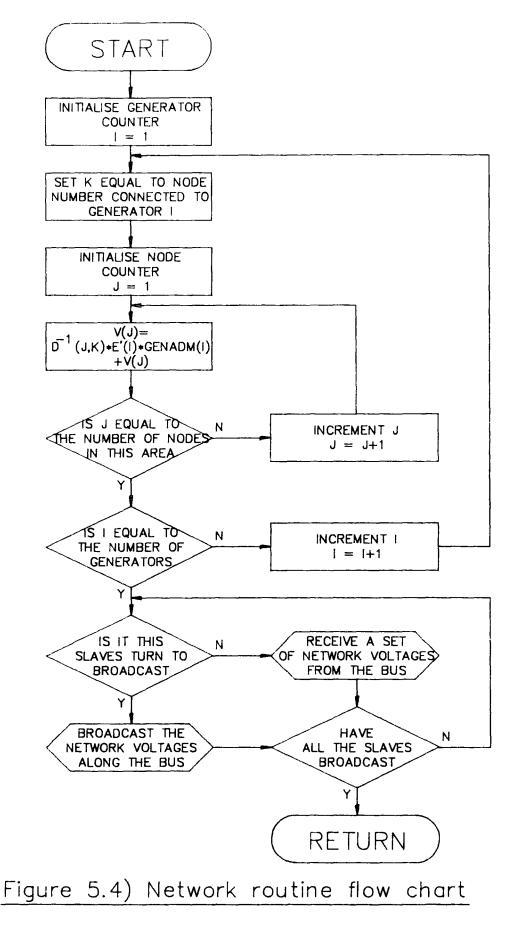

| 5.2.4 | Network routine                | 104        |

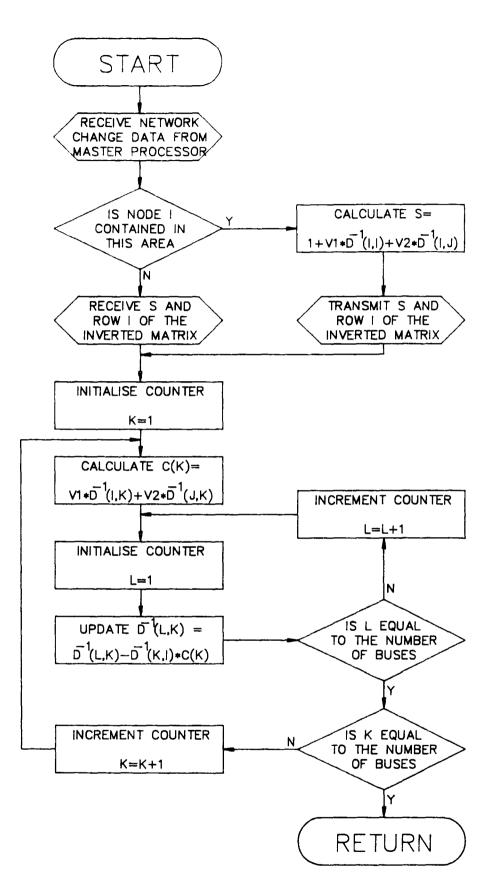

| 5.2.5 | Householder routine            | 107        |

| 5.3   | Software functions             | 110        |

| 5.3.1 | Sine and cosine                | 110        |

| 5.3.2 | Arctangent                     | 112        |

| 5.3.3 | Square root                    | 112        |

| 5.4   | Host software                  | 113        |

|       |                                |            |

| 6. Multiproc | essor hardware design             | 116 |

|--------------|-----------------------------------|-----|

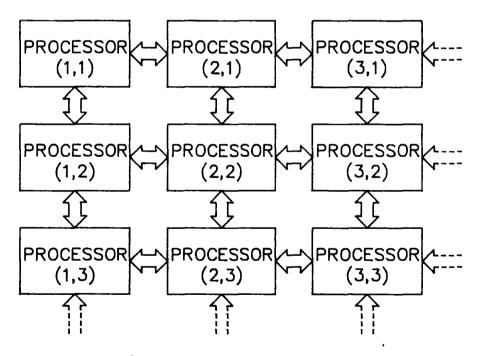

| 6.1 Mult     | tiprocessor components            | 116 |

| 6.1.1        | Multiprocessor Emulation          | 117 |

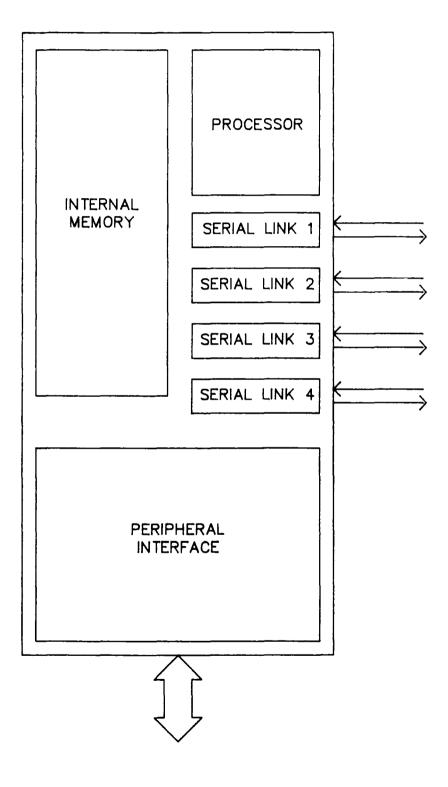

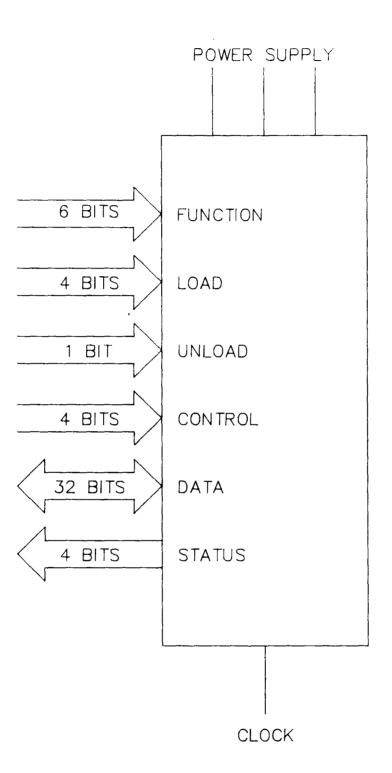

| 6.1.2        | Transputers                       | 120 |

| 6.1.3        | M68000 and M68020 microprocessors | 123 |

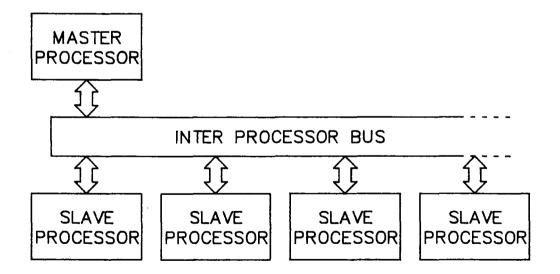

| 6.2 Mult     | tiprocessor configurations        | 125 |

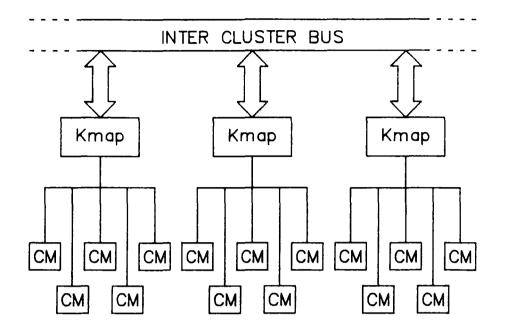

| 6.2.1        | CM* multiprocessor structure      | 126 |

| 6.2.2        | Linear multiprocessor structure   | 128 |

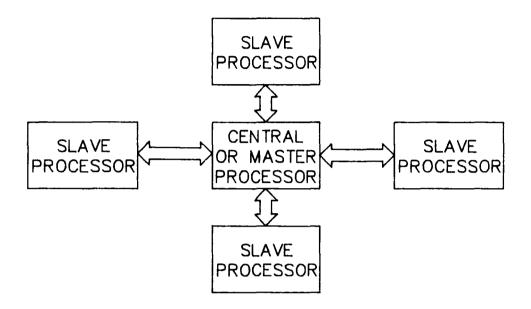

| 6.2.3        | Radial multiprocessor structure   | 129 |

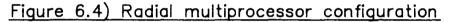

| 6.2.4        | Grid multiprocessor structure     | 131 |

| 6.3 Pro      | cessor communication              | 132 |

| 6.3.1        | Common memory systems             | 133 |

| 6.3.2        | Bus connected systems             | 133 |

|              |                                   |     |

| 6.4   | Development hardware                       | 13 <b>4</b> |

|-------|--------------------------------------------|-------------|

| 6.4.1 | M68000 system with IEEE bus                | 135         |

| 6.4.2 | M68020 system with floating point hardware | 137         |

| 7. Results |                                        | 144 |

|------------|----------------------------------------|-----|

| 7.1 Numer  | ical results                           | 146 |

| 7.1.1      | Load outage test                       | 148 |

| 7.1.2      | Line outage test                       | 155 |

| 7.1.3      | Generator outage test                  | 161 |

| 7.1.4      | Multiple event test                    | 166 |

| 7.2 Timin  | g results                              | 173 |

| 7.2.1      | Generator and load routine timing      | 173 |

| 7.2.2      | Network routine timing                 | 174 |

| 7.2.3      | Householder routine timing             | 179 |

| 7.2.4      | Communications timing                  | 181 |

| 7.3 Overa  | ll timing                              | 182 |

| 7.3.1      | Steady state solution time             | 184 |

| 7.3.2      | Network change time                    | 185 |

| 7.4 Simul  | ation timing estimates                 | 187 |

| 7.4.1      | Load model comparison timings          | 187 |

| 7.4.2      | Multiprocessor size comparison timings | 188 |

| 7.5 Simul  | lator hardware requirements            | 190 |

|            |                                        |     |

# 8. Conclusions

.

9. References and bibliography 199

| 9.1 | References | 19 | 99 |

|-----|------------|----|----|

|-----|------------|----|----|

192

•

| 10. | Appendices                             | 208 |

|-----|----------------------------------------|-----|

|     | Appendix 1 - Diakoptic cut line matrix | 208 |

|     | Appendix 2 - Test system parameters    | 210 |

|     | Appendix 3 - Timing results            | 213 |

|     | Appendix 4 - Code examples             | 215 |

# LIST OF ILLUSTRATIONS

# FIG. ILLUSTRATION

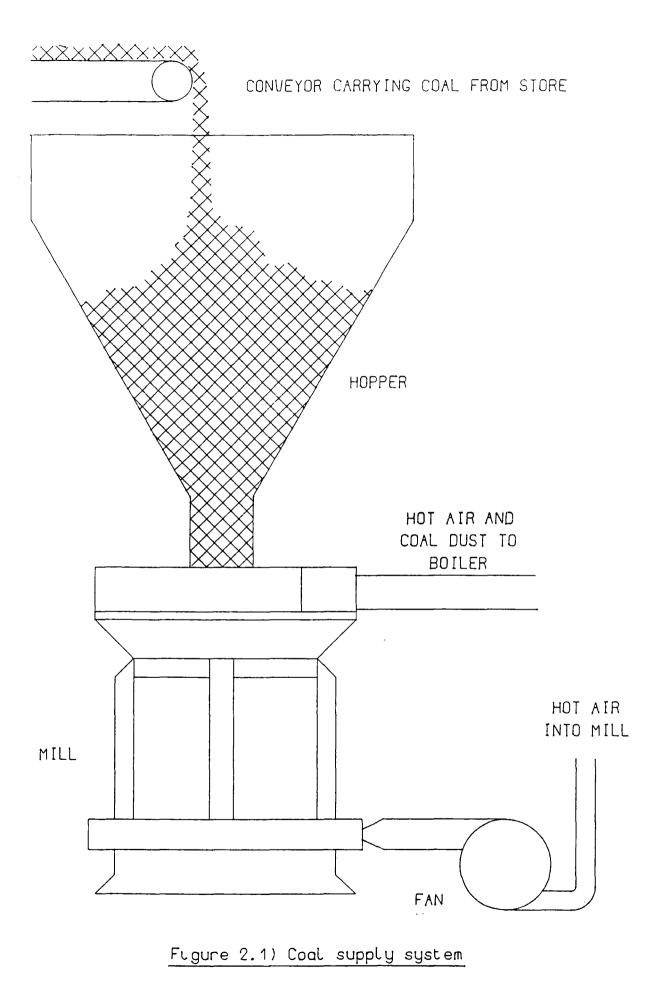

| 2.1 | Coal supply system                       | 39  |

|-----|------------------------------------------|-----|

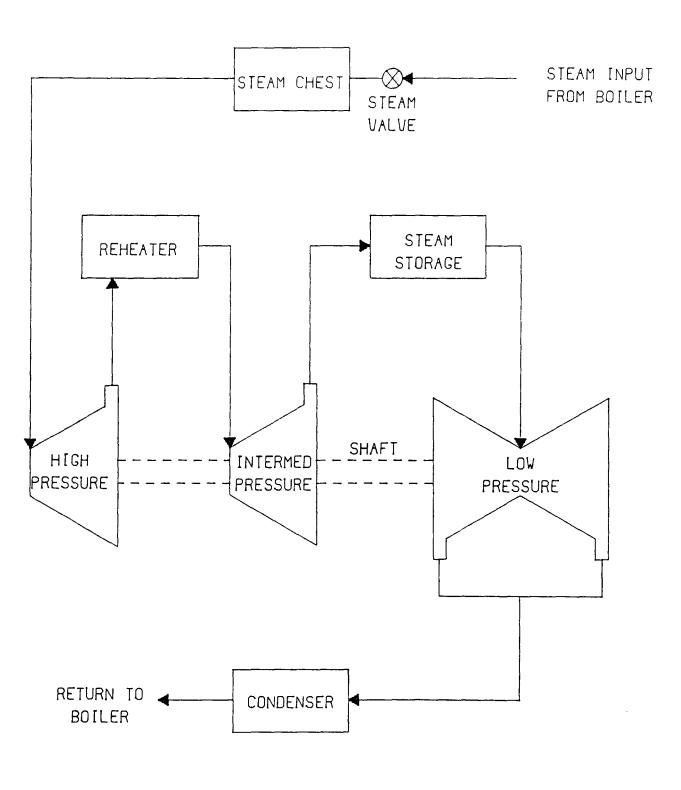

| 2.2 | Prime mover string                       | 42  |

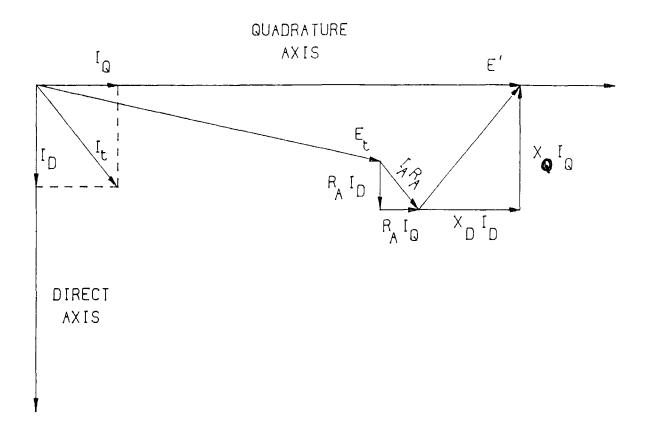

| 2.3 | Approximate generator vector diagram     | 45  |

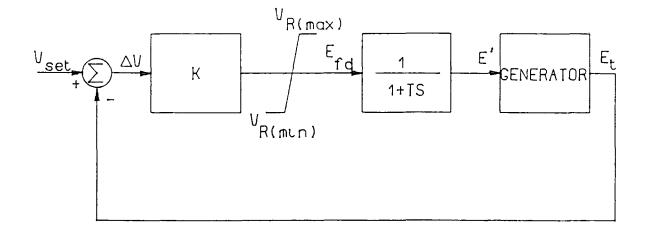

| 2.4 | Excitation system block diagram          | 45  |

|     |                                          |     |

| 3.1 | Example network divided into areas       | 57  |

| 3.2 | Connecting lines replaced by loads       | 57  |

| 3.3 | Network divided through buses            | 60  |

| 3.4 | Network representation for direct method | 60  |

|     |                                          |     |

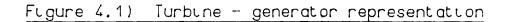

| 4.1 | Turbine-generator representation         | 72  |

| 4.2 | Governor model block diagram             | 72  |

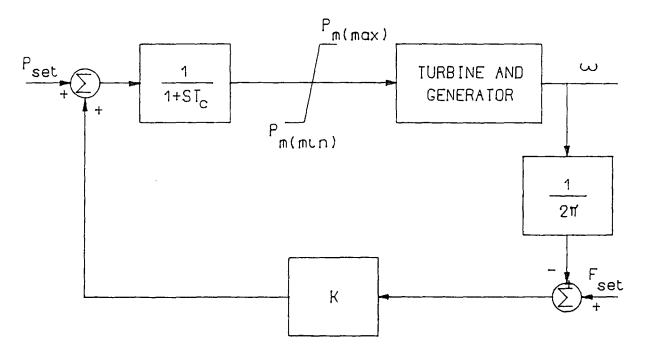

| 4.3 | General load representation              | 79  |

|     |                                          |     |

| 5.1 | Master routine flow chart                | 92  |

| 5.2 | Slave routine flow chart                 | 100 |

| 5.3 | Generator routine flow chart             | 102 |

| 5.4 | Network routine flow chart               | 105 |

| 5.5 | Householder routine flow chart           | 108 |

| ·   |                                          |     |

| 6.1 | Transputer architecture                  | 121 |

| 6.2 | Structure of a CM* multiprocessor        | 127 |

- 7 -

| 6.3 | Linear multiprocessor configuration   | 127 |

|-----|---------------------------------------|-----|

| 6.4 | Radial multiprocessor configuration   | 130 |

| 6.5 | Multiprocessor grid configuration     | 130 |

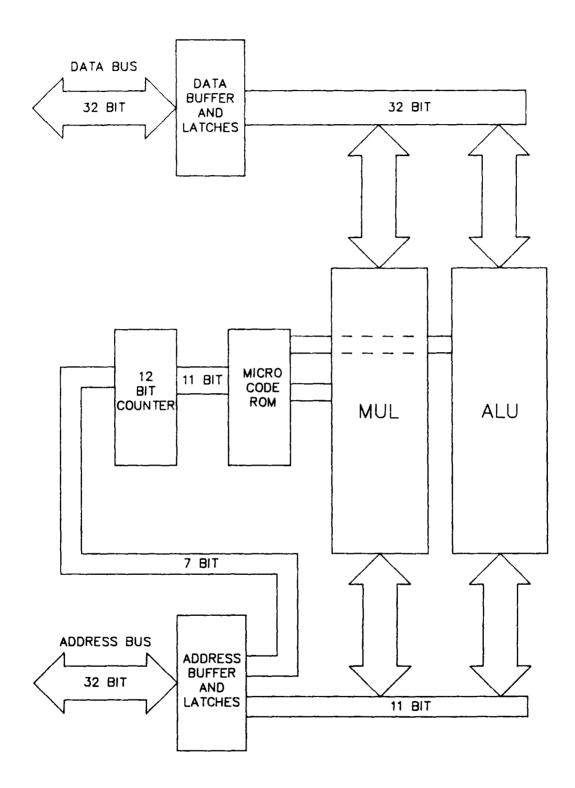

| 6.6 | Weitek floating point architecture    | 139 |

| 6.7 | Block diagram of floating point board | 141 |

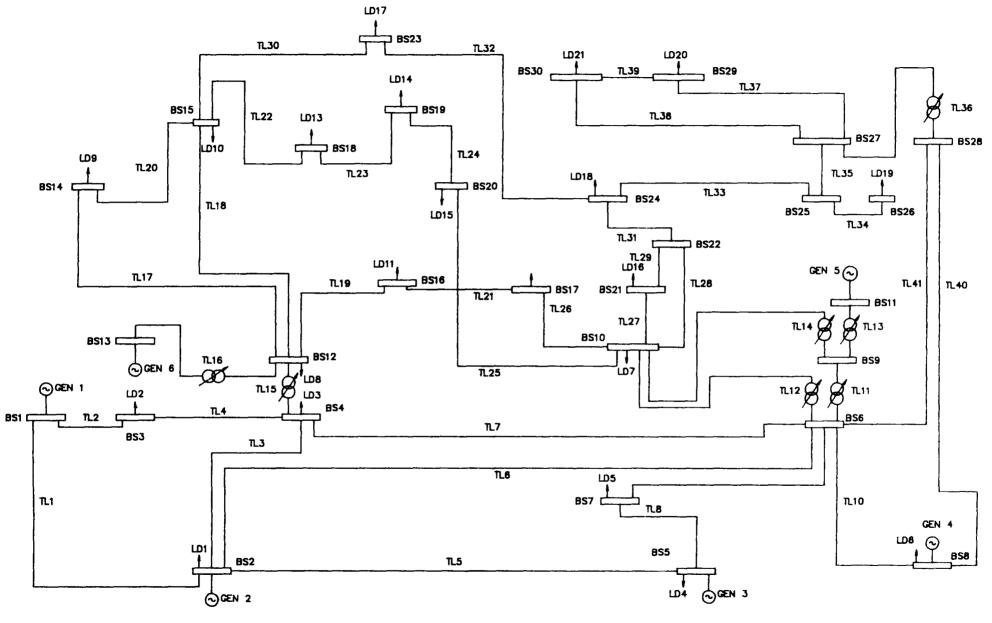

| 7.1  | IEEE 30 bus test network                     | 147 |

|------|----------------------------------------------|-----|

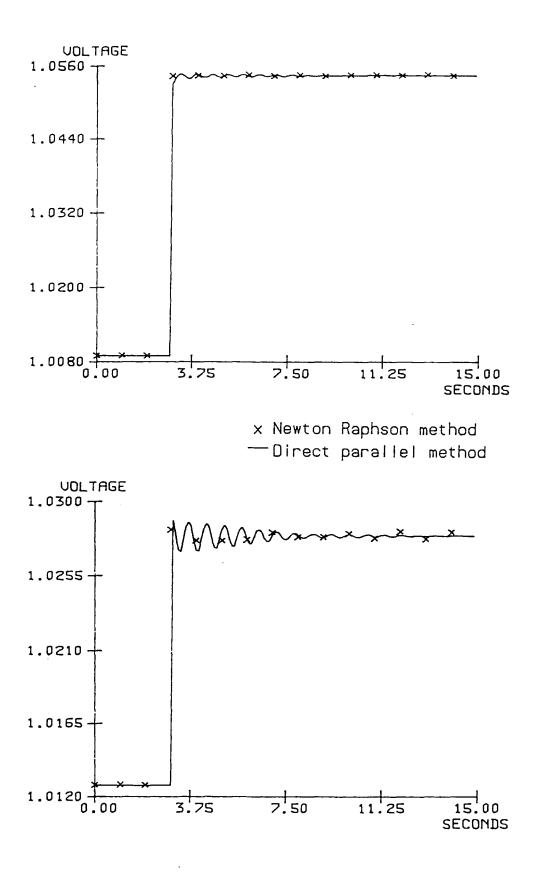

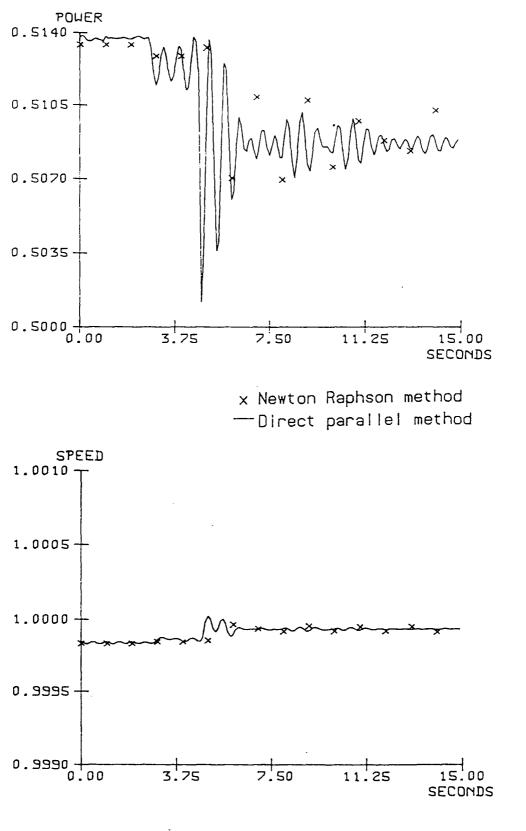

| 7.2  | Voltages at bus 5 and 28 during test 1       | 149 |

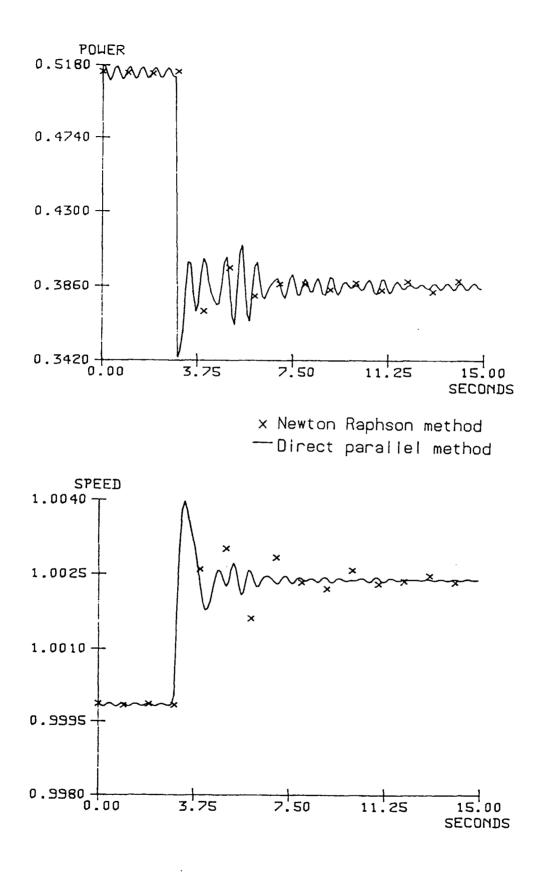

| 7.3  | Power and speed of generator 1 during test 1 | 152 |

| 7.4  | Power and speed of generator 3 during test 1 | 153 |

| 7.5  | Power and speed of generator 5 during test 1 | 154 |

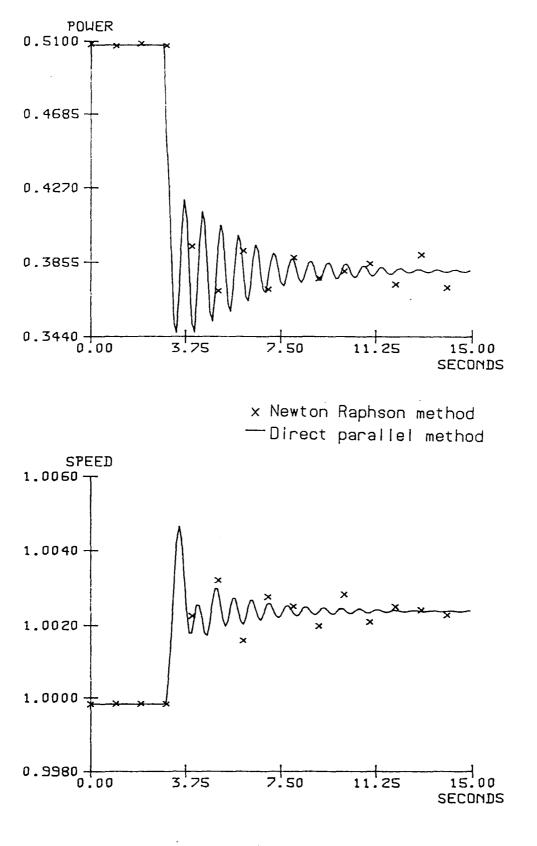

| 7.6  | Voltages at bus 5 and 28 during test 2       | 156 |

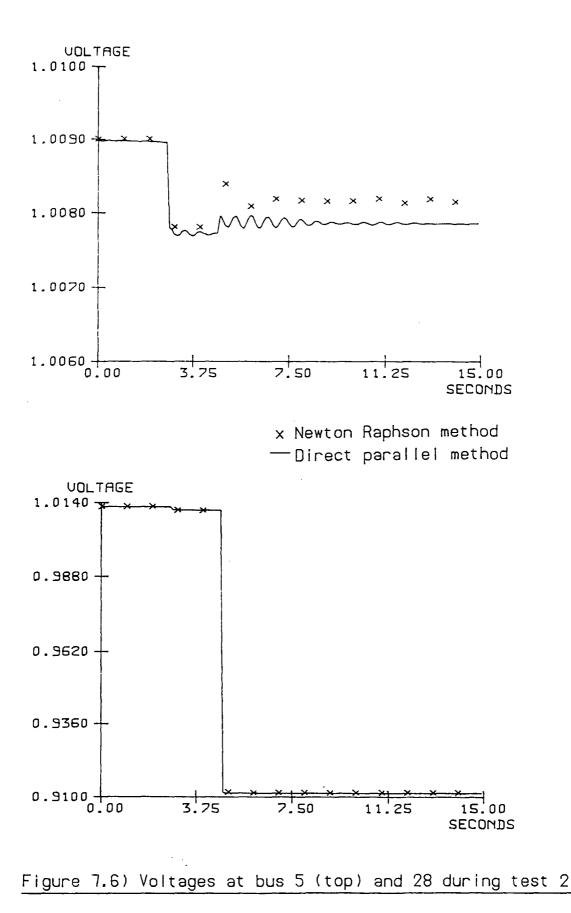

| 7.7  | Power and speed of generator 1 during test 2 | 158 |

| 7.8  | Power and speed of generator 3 during test 2 | 159 |

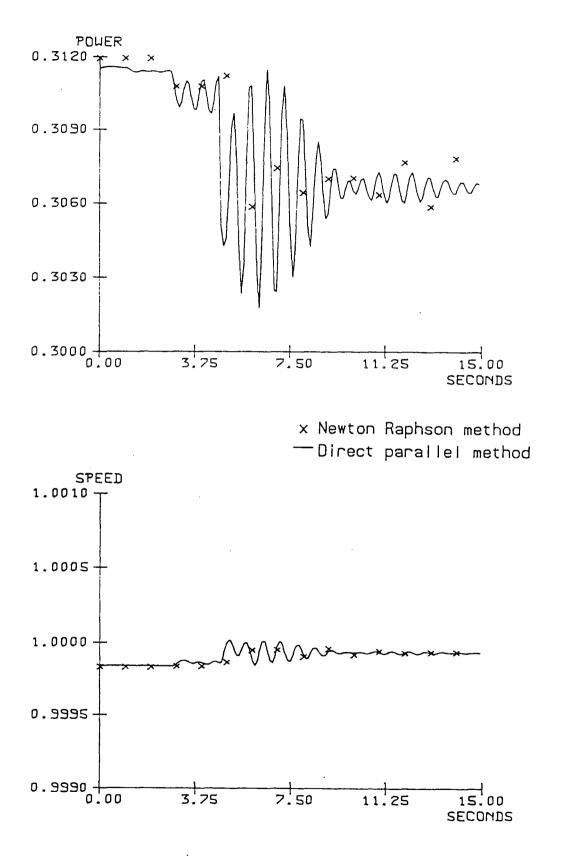

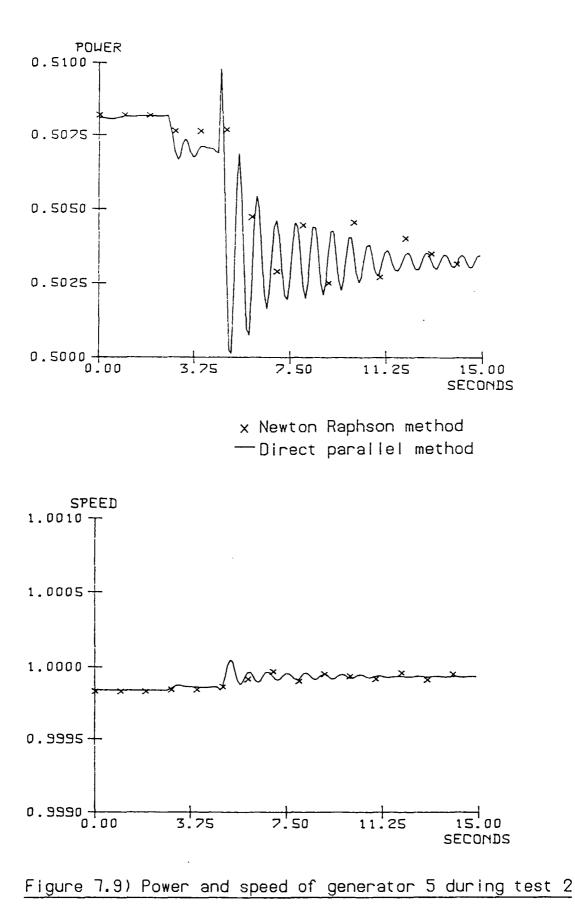

| 7.9  | Power and speed of generator 5 during test 2 | 160 |

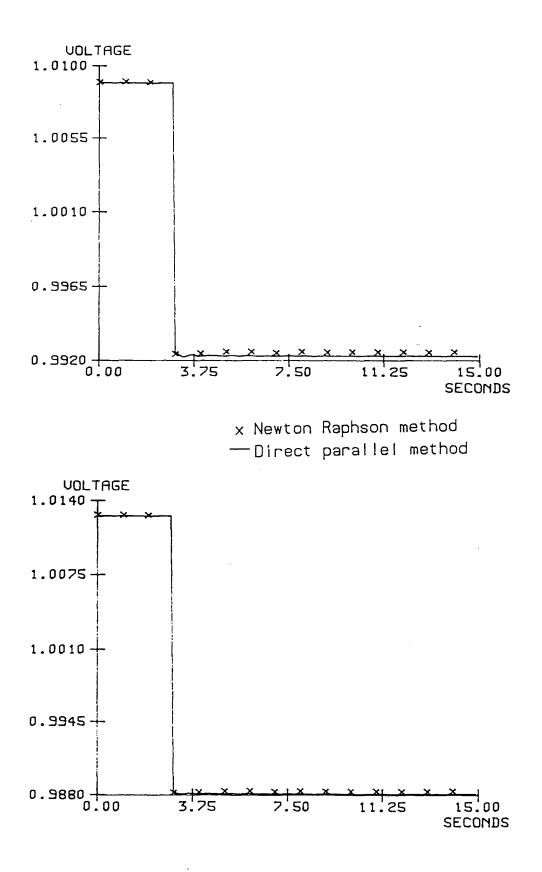

| 7.10 | Voltages at bus 5 and 28 during test 3       | 162 |

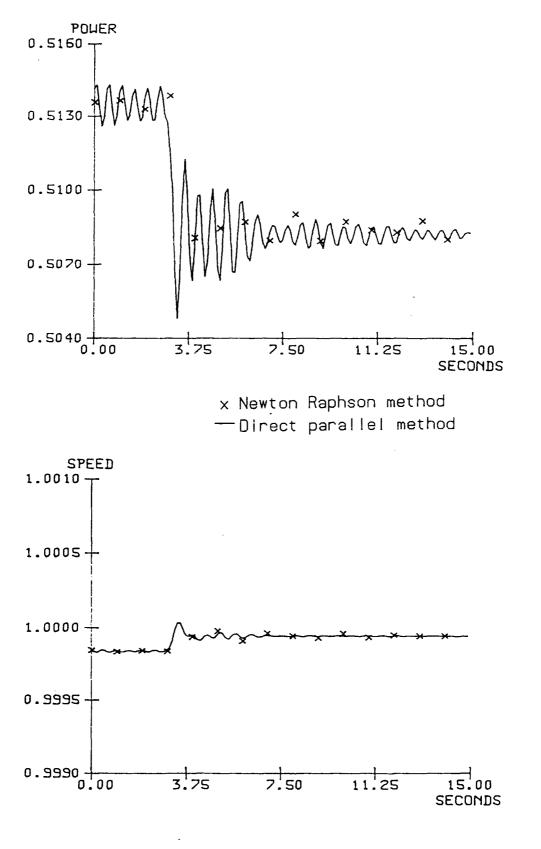

| 7.11 | Power and speed of generator 1 during test 3 | 163 |

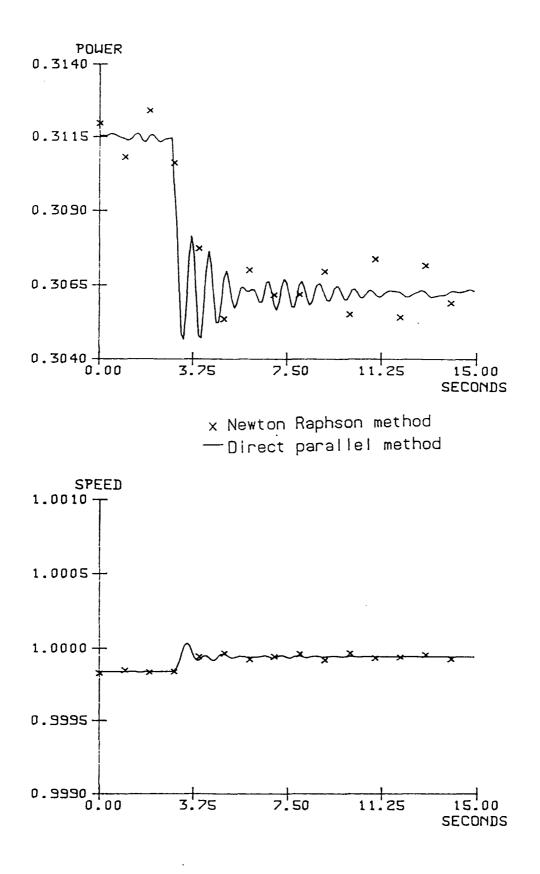

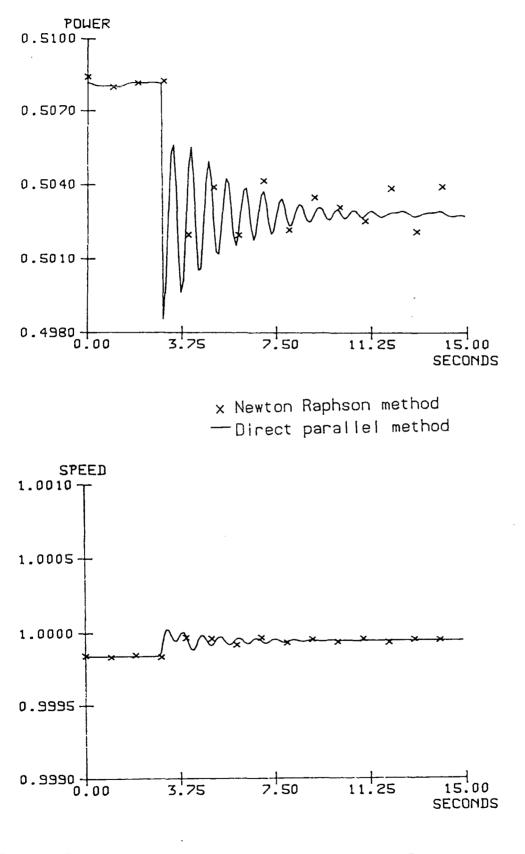

| 7.12 | Power and speed of generator 3 during test 3 | 164 |

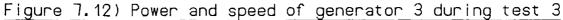

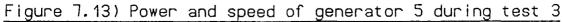

| 7.13 | Power and speed of generator 5 during test 3 | 165 |

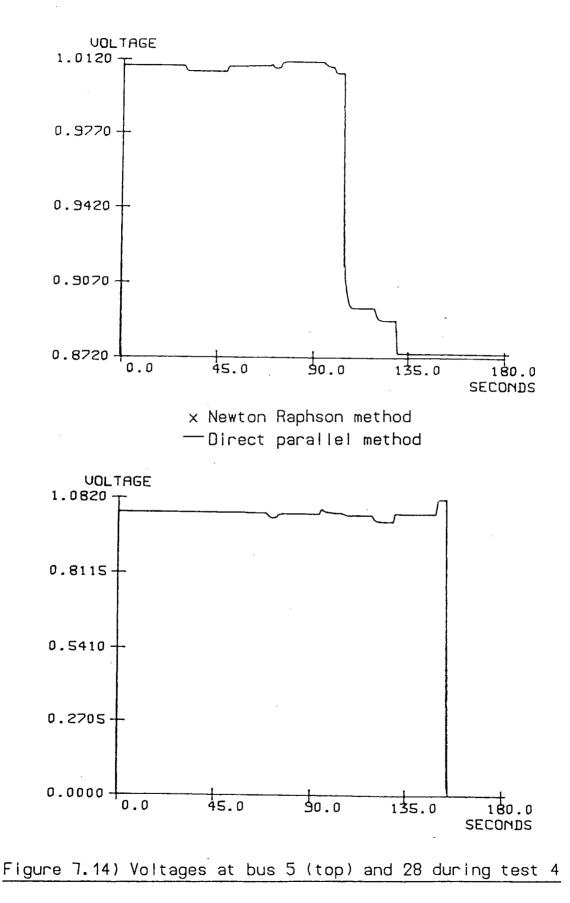

| 7.14 | Voltages at bus 5 and 28 during test 4       | 168 |

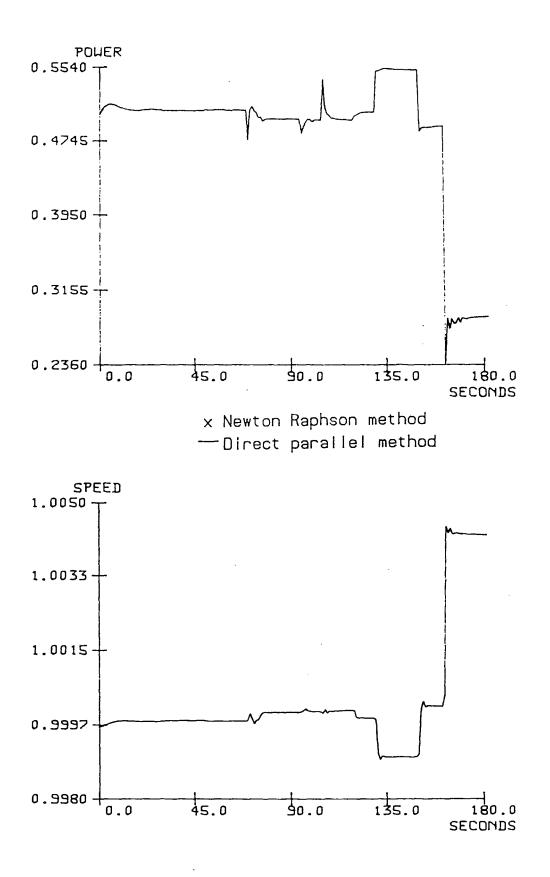

| 7.15 | Power and speed of generator 2 during test 4 | 169 |

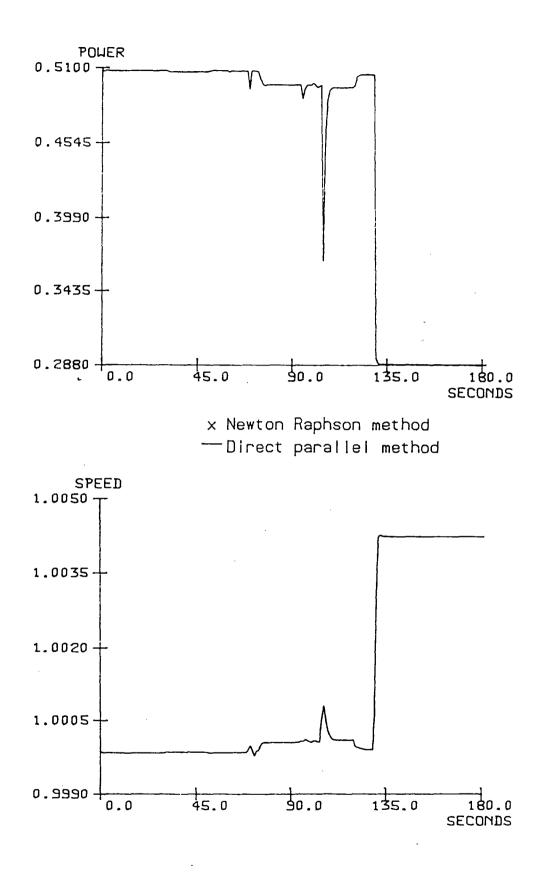

| 7.16 | Power and speed of generator 4 during test 4 | 170 |

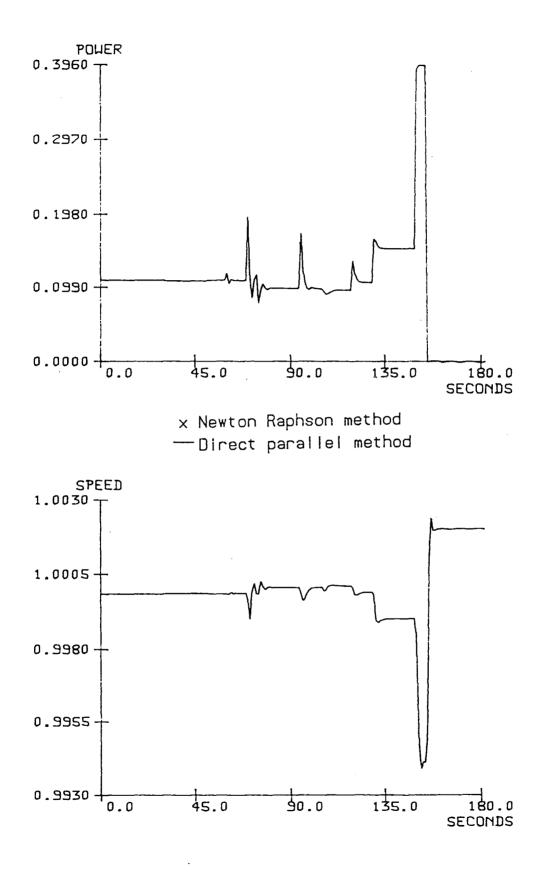

| 7.17 | Power and speed of generator 6 during test 4 | 171 |

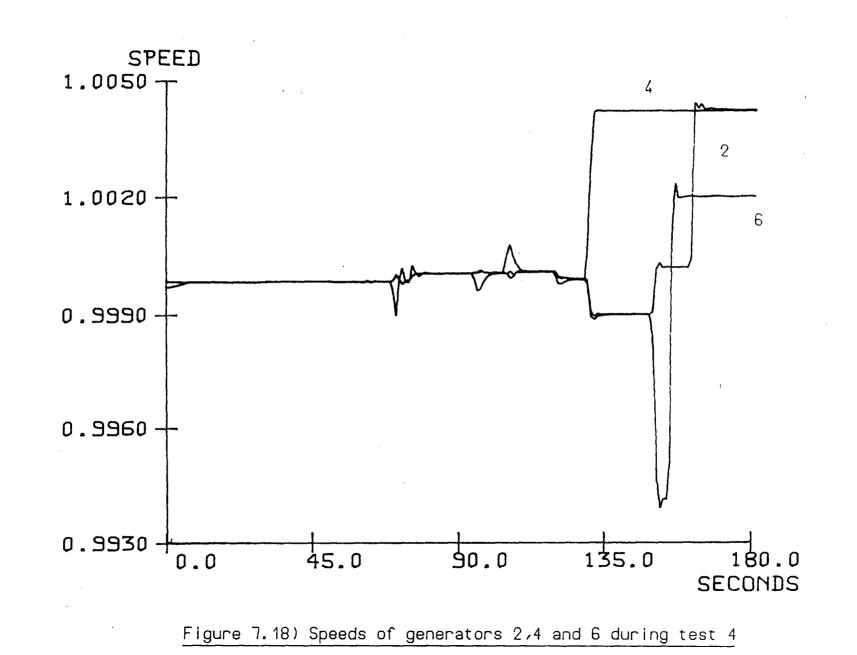

| 7.18 | Speeds of generators 2,4 and 6 during test 4 | 172 |

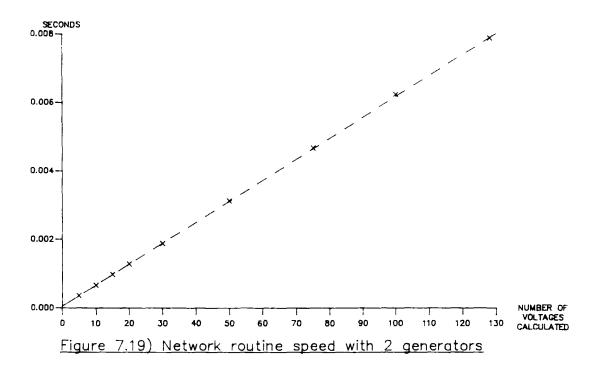

| 7.19 | Network routine speed with 2 generators      | 175 |

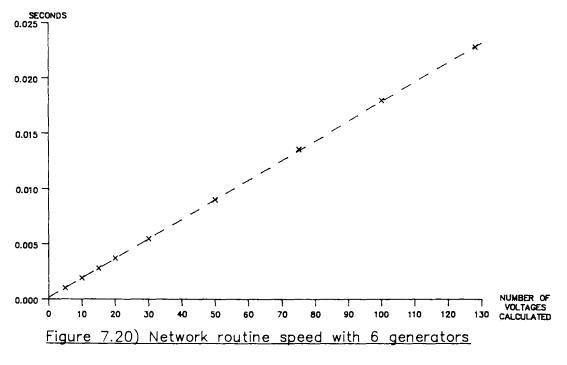

| 7.20 | Network routine speed with 6 generators      | 175 |

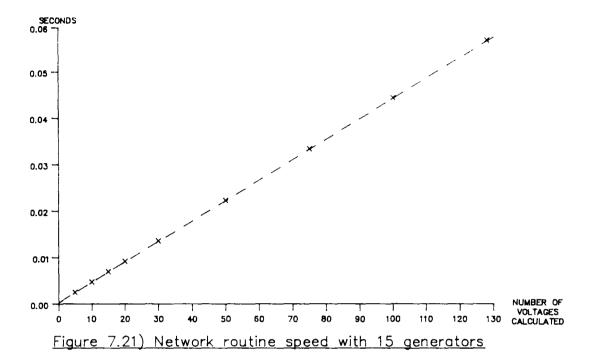

| 7.21 | Network routine speed with 15 generators     | 176 |

|      |                                              |     |

- 8 -

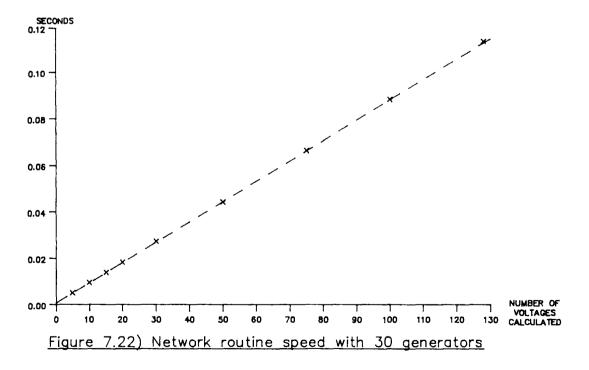

| 7.22 | Network routine speed with 30 generators            | 176 |

|------|-----------------------------------------------------|-----|

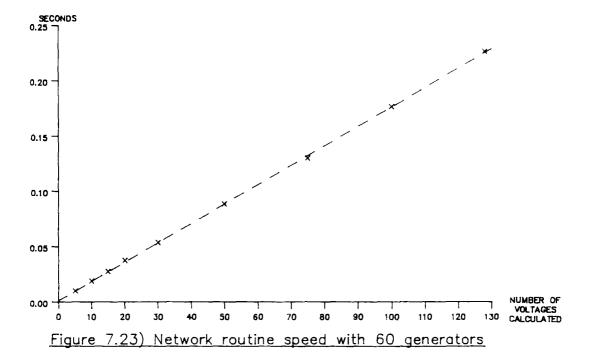

| 7.23 | Network routine speed with 60 generators            | 177 |

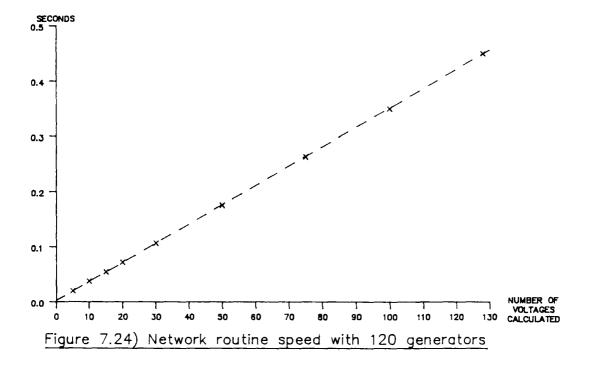

| 7.24 | Network routine speed with 120 generators           | 177 |

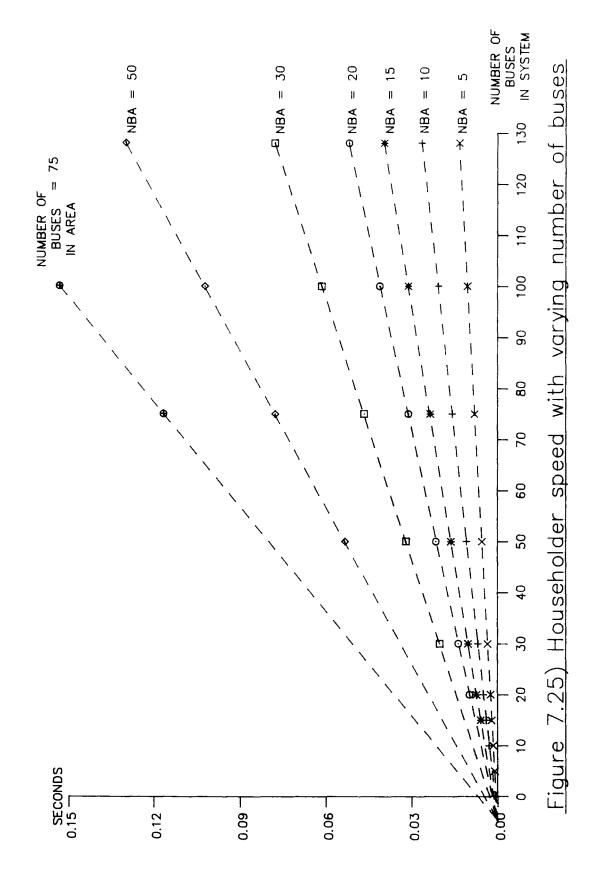

| 7.25 | Householder speed with varying number of buses      | 180 |

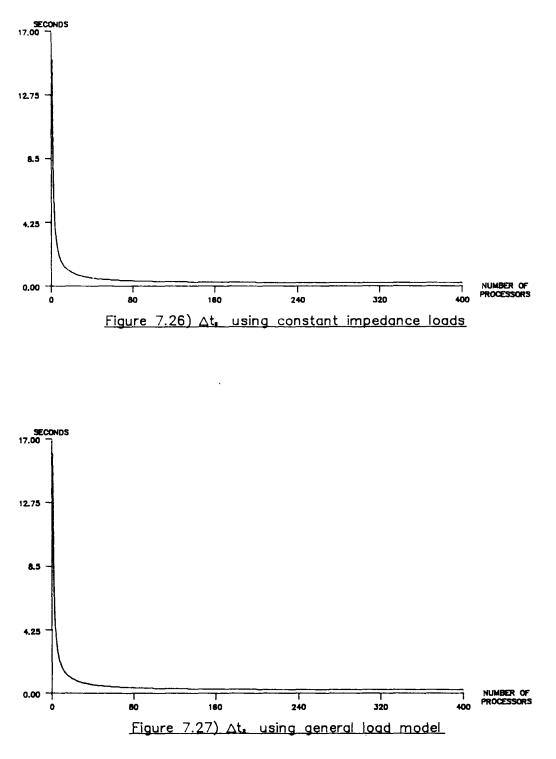

| 7.26 | $\Delta t_{\approx}$ using constant impedance loads | 189 |

| 7.27 | $\Delta t_{2}$ using general load model             | 189 |

•

# LIST OF SYMBOLS

# SYMBOL

# MEAN ING

| δ                  | Generator rotor angle                        |

|--------------------|----------------------------------------------|

| Δt                 | Iteration time step                          |

| E'                 | Voltage behind generator transient reactance |

| E <sub>t.</sub>    | Voltage at generator terminals               |

| Fo                 | System frequency ( 50 Hz )                   |

| Fset               | Generator frequency set point                |

| Н                  | Generator inertia                            |

| I <sub>t.</sub>    | Generator current                            |

| Iinj               | Current injection into network               |

| К                  | Generator governor gain                      |

| P_                 | Generator electrical power produced          |

| Pg                 | Generator output power                       |

| P <sub>m</sub>     | Generator input mechanical power             |

| Pset               | Generator power set point                    |

| (P + jQ)           | Complex power                                |

| $(R_{A} + jX_{D})$ | Generator transient reactance                |

| T <sub>c</sub>     | Turbine time constant                        |

| ω                  | Generator speed                              |

| V <sub>E</sub>     | Voltage at node p                            |

| İp                 | Injected current at node p                   |

| Ура                | admittance between nodes p and q             |

## 1 INTRODUCTION

Simulators are pieces of equipment which accurately model the behaviour of some form of physical system. They have been used in several engineering fields to allow control systems to be developed or for operators to learn about them : most often in cases where a mistake in the handling of the physical system would prove dangerous or costly . A prime example is the use of flight simulators in the training of commercial pilots : such simulators provide a realistic model of the cockpit of the aircraft in which the pilots sits . The view of the external terrain, which is modelled by computers, is projected onto screens outside the windows of the cockpit . The simulator relates the manipulation of the controls inside the cockpit to the effects on the view outside and allows the pilot to be subjected to emergency conditions, such as engine failure, without endangering lives or expensive equipment .

The physical system to be modelled for a power system simulator is made up of various items of equipment, linked together to supply power over a particular area. Electrical generators, driven by some form of prime mover such as a turbine, produce power which is transmitted to the consumers via lines and transformers. There are two distinct types of control on the system, operating on different time scales:

First the control which takes place locally and acts very quickly . For example, the mechanical governors and voltage regulators on generator sets . These attempt to regulate respectively

. - 11 -

the speed and voltage produced by the generator to some set points. They begin to act as soon as the generator deviates from its set point. The set points themselves may come from some portion of the second type of control provided in the system.

The second type of control is the global operating scheme . This is the control of the system as a whole at regional or national level, rather than each individual item of equipment . The sorts of function performed centrally are the prediction of the amount of load in the near future and the scheduling of generators to produce the power required for the predicted load . The regional control must also reduce the likelihood of equipment failures, which can drastically affect the performance of the entire system, and cope with the effects of such failures if and when they occur .

In the U.K. the regional control system gathers its data from the network through a SCADA (Supervisory Control And Data Acquisition) computer system which is connected to many measuring devices and transducers throughout the system. The SCADA computer collects the measurements and presents them to the operators and to the control computers. Because of the amount of data that has to be collected it takes some time for the control centre to receive the data and act upon it: this means that the global control cannot act as quickly as the local control.

The OCEPS (Operational Control of Electric Power Systems) research group at Durham has been developing computer software to perform many of

- 12 -

the control functions performed in the control centres, both at regional and at national level . To test the algorithms produced a simulator is required which models the power system as accurately as possible .

Simulators have been produced in various forms for power system analysis for several years now . The basic problem is to model the dynamic components of the power system, such as the power station generators and the consumer loads, and compute the flow of power along the transmission lines connecting them. The simulator must be as controllable as the real system and respond to the controls in as similar a way as possible .

The uses and methods of simulation are varied and the accuracy and speed of the simulator depend on its intended purpose. The presentation of the calculated results and the input of changes to the system (referred to as the man-machine interface) also vary according to the use for which the simulator is designed. In general they are used much as flight simulators are used; to allow things to be done to the model which could prove costly and hazardous on the real system and to monitor the effects of those actions in detail.

# 1.1 SINULATOR USES

Power system simulators can be used for a variety of different tasks, each task requiring the same end result - an accurate dynamic model of the power system . The presentation and time scale of the model vary, depending upon the type of task . Four main areas of importance can be

- 13 -

distinguished : energy management system development, transient studies, operator training and teaching . Each of these is described and discussed in turn below .

#### 1.1.1 ENERGY MANAGEMENT SYSTEM DEVELOPMENT

The development of efficient power system control strategies is a field where large amounts of money can be saved by a small percentage decrease in operating costs . For instance the annual fuel cost of the C.E.G.B. is some  $\pounds4000$  million, so even a %% reduction would amount to a saving of  $\pounds20$  million per year. Of course, the power system cannot be run safely on an economic least cost basis but account also has to be taken of the service to the consumer . Any control strategy must therefore balance the costs of running the system with the reliability and tolerance of the system to faults such as partial loss of generation, voltage reductions and so on .

A simulator is an essential tool for the development of a computerised control strategy - or energy management system (EMS) . It enables the computer programs to be tested under both normal running and emergency conditions without affecting the actual power system or the consumers it supplies. It is essential that the EMS should be thoroughly tested before it is used on the real system because mistakes and accidents can be costly to both the generating board and the consumer if the power supply fails. For this reason the simulator must model as accurately as possible the response of the actual system to the controls applied by the EMS .

Several types of simulator have been produced as test beds using both digital (M. Rafian et al. (11) and analog (R. Joetten et al. (2]) technology. To test the latest computer control algorithms the simulator should be as realistic a model of the system as possible, providing real time simulation and also representing the short term transients . However, the data produced by the simulator should correspond to the rates achieved by conventional SCADA systems so that the algorithms are not provided with more information than would normally be available . The possibility of incorrect measurements due to noise or failure of transducers should also be incorporated so that data validation and state estimation routines can be thoroughly tested .

The simulator for this type of use is accessed almost entirely by other programs and the need for any man-machine interface is minimal: all actions by operators would normally come through a SCADA program with its own interface . The only actions which need to go directly to the simulator are for debugging, which requires no more than a simple monitor with access to variables and the ability to run the programs step by step . All other instructions involve the passing of commands from the SCADA to the simulator and the returning of the simulated values . If the SCADA and the simulator are running in the same machine this can be done via a global memory area; if they are in separate machines a simple serial or parallel data line is all that is needed.

## 1.1.2 TRANSIENT STUDIES

The next area in which dynamic simulation is useful is that of examining the effects of transients in a system . Most SCADA systems on power systems present new data to the operator at relatively long time intervals ( up to 30 seconds ) and any short term effects are not seen at all . This does not matter to the operator because the effects are short term and he cannot do anything on so short a time scale . However it is useful to know what transients occur in a system when, for example, a circuit breaker is opened . For this type of information to be gathered, tests can be made on the real system or on a simulator . The simulator must have extremely accurate models of all the power system components and have a short enough time step to catch the transients which are being studied . However there is normally no need for the simulator to run in real time because there is no human interaction required.

Transient studies are useful in the design and tuning of the short time scale control which is applied locally to elements of the power system. The governor on a turbine can be altered to make the generator less likely to go unstable when equipment failures occur, but the tests on different governor parameters must be carried out with the generator connected to the rest of the system. This is because the response of the other generators and loads in the system may alter the response of the machine under test.

The man-machine interface for transient stability analysis consists of the ability to define the set of events to take place and

- 16 -

then, once the simulator has run, to view all the resulting data in a convenient form such as trend graphs. It is important that the tests should be repeatable so that the effects of altering of certain elements in the system can be seen clearly.

#### 1.1.3 OPERATOR TRAINING

With the high reliability of modern power system components the occurrence of major faults such as islanding (the power system dividing into discrete parts) and large generation failures is rare. However it is precisely at these times that a well-trained operator may be able to play a crucial part in preventing or reducing the catastrophic effects such failures can have. Some post-fault studies have shown that the response of operators to serious system faults was not ideal, and there is accordingly a need for improved facilities for training operators to deal with major faults. Since the mid 1970's there has been an increase in the interest in and amount of work on operator ( or dispatcher ) training simulators [3-9]. This is due to three main factors:

a) Rising fuel costs have increased the amount of money to be saved by running the system closer to its operational limits and, in the case of regions with more than one generating authority, the exchange of power between authorities has become higher, pushing line flows close to limits and making unexpected outages of lines more important .

- 17 -

- b) Environmental issues have forced new generation plant to be sited away from urban centres and hence away from the load. This again adds to the problem of high power flows along transmission lines.

- c) The introduction of new types of equipment, such as pumped storage facilities, require the operator to be trained in the abilities and limitations of such equipment.

An operator training simulator must provide the trainee with an exact replica of the environment in which he is going to work. This can be achieved by building a control room and driving all the instrumentation and displays from the simulator instead of from the system itself . In this case the simulator has to have the same characteristics as the EMS development simulator so that the operator is given exactly the same amount of data as in a real control room in real time . As an alternative the dispatcher training simulator is run on the back-up computers in a real control room to provide the correct environment . This solution also saves the expense of building a replica control room and utilises the computing power available more fully . However, care has to be taken in such a system to ensure that a trainee cannot accidentally influence the real power system and that the back-up computer is always available for instant use should the primary control computer fail .

The operator also needs access to all the tools he would normally have at his disposal in the energy management system, such

- 18 -

as security analysis and generator rescheduling. Using such a system the operator can be trained in the use of the system and the software, starting with the normal operation of the plant, and then in dealing with major faults which can be introduced as frequently as the trainer wishes, giving the operator an amount of experience almost impossible to achieve without a simulator.

# 1.1.4 TEACHING

Using a simulator for teaching purposes is really an extension of the operator training problem . In teaching institutions such as polytechnics and universities where elements of power system theory are taught, practical work to back up the teaching is difficult because of the diversity of problems to be looked at and the expense of providing a small-scale low-voltage power system to be used as a model. However a simulator with a suitable man-machine interface can be used to give students a feel for the dynamics of the system and how changes in topology ( network configuration ) and system parameters can affect the running of the system. The simulator should give as much relevant information to the student as possible, even if this means that it no longer runs in real time, so that maximum benefit is gained from the time spent on it.

The man-machine interface for this type of use must allow the students to display all parameters of the system in an easily interpreted form, and to repeat the same scenario many times so that

- 19 -

all the effects of specific actions may be viewed . There should also be provision for the teaching staff to interact with the simulator at the same time so that parameters may be changed and the results viewed without having to restart the simulator with a new scenario of events to occur .

## 1.2 METHODS OF SINULATION

There are three main types of simulator available . Each has its advantages and can be used for different types of problem:

# 1.2.1 ANALOG AND HYBRID SIMULATORS

The first power system simulators were analog machines using electrical components to model the various parts of the system . These simulators could run in real time because the models operated in parallel . However, with the advent of digital computers it became easier to model parts of the system and perform some of the control and data collection using digital hardware . These digital/analog machines are called hybrid simulators and are still used because of their faster than real time capabilities .

The digital part of the simulator is normally interfaced to the analog via a series of digital/analog and analog/digital converters which allow the computer to vary certain parameters and collect the

- 20 -

data as a normal SCADA system would . There are two main problems with both analog and hybrid simulators:

- a) Even when the simulator is constructed out of modules, each module representing one type of component in the power system, the system topology is very inflexible. The hybrid simulator is slightly better than the analog, but if a new generator needs to be added to the system then another module has to be inserted by hand. If a completely different power system has to be simulated the simulator must be rewired in its entirety.

- b) The cost of producing the components is high and they can be quite large . As a result the simulator for a large system can be bulky and also extremely expensive . For example the simulator developed by R. Joetten et al. [2] has modules on circuit boards 100 mm by 160 mm and it requires 12 such boards to represent a bank of three single phase, two winding transformers.

However for power authorities with small systems, hybrid simulators can be useful because the system to be modelled is reasonably static and, by using a base frequency higher than the system frequency, faster than real time simulation is possible for the study of long term dynamics of the system (G.E. Ott et al. [10]).

- 21 -

#### 1.2.2 LOAD FLOW TYPE SIMULATORS

The most common type of digital simulator first uses a load flow approach to solve the network equations and then solves the dynamic equations such as the generator and load models using the initial nodal voltages and powers produced by the load flow (A. Keyhani [11]). This technique is widely used for three main reasons:

- a) First, because load flow calculations have been an important analysis tool for a long time. There are many well developed methods for calculating the load flow which are both fast and accurate. Methods such as the fast decoupled load flow (B. Stott and O. Alsac [12]) and the Newton load flow (W.F. Tinney and C.E. Hart [13]) can easily be adapted to work as the network solution part of a simulator.

- b) Secondly, because the generator and load models are separate from the network equations they can be varied in complexity and accuracy depending on the type of work for which the simulator is to be used .

- c) Thirdly, the load flow method gives fast computation of results, especially when the system is in a steady state condition, and it is thus easier to develop a simulator to run in real time.

- 22 -

Another time-saving feature of this technique is the fact that the load flow element need only be run once every few seconds while the dynamic model elements run far more frequently to give a more accurate simulation of the transient state of the system .

# 1.2.3 COMBINED DYNAMIC/ALGEBRAIC SIMULATORS

Combining the dynamic and algebraic equations of the network into a single algorithm and solving them simultaneously also provides a good method of simulation (M. Rafian et al. [1], L. Elder and M.J. Metcalfe [14]) . It can take longer than the previous method but has several advantages:

- a) The method is highly accurate and stable: even if the system is split into islands by a line outage the simulator keeps going and automatically calculates the results for as many islands as are formed.

- b) The load flow method always has the results of the dynamic and algebraic equations out of step by one integration whereas the combined method is tightly coupled and there is nothing out of step .

- c) Although the combined method takes longer than the load flow method the correct choice of models for the system

- 23 -

components can still allow the simulator to produce results in real time .

The combined set of equations can also be split into those which require frequent calculation and those concerned with longer term dynamics . By removing the long term equations from the fast iteration the simulation can be speeded up .

## **1.3 SINULATOR HARDWARE**

Many forms of hardware are used for power system simulation, ranging from the circuit board modules used in the hybrid and analog simulators to the various forms of digital hardware grouped under the heading 'vector processors'. H.H. Happ et al. [15] examined the possibilities of the future technology while more recently D.M. Detig [16] and M. Takatoo et al. [17] have looked at the effects of vector processors on power system applications . Processors are often classified into groups according to their capabilities as follows:

- a) SISD Single Instruction Single Data:- Machines which execute

one instruction at a time on one piece of data .

- b) SIMD Single Instruction Multiple Data:- Machines which execute one instruction at a time on a set of pieces of data.

MIMD - Multiple Instruction Multiple Data:- Machines which execute a set of instructions on a set of pieces of data simultaneously.

All the forms of hardware have their pros and cons . Those of the analog and hybrid hardware have already been mentioned: those of the digital machines available are as follows:

#### 1.3.1 MAINFRAME AND SUPERCOMPUTERS

Mainframes such as the IBM 370 and supercomputers like the CRAY-1 are digital computers with large memory areas and extremely high computation speeds, ideal for large 'number crunching' operations like simulation problems . Unfortunately they are also extremely expensive and can be afforded only by large organisations and computer bureaux . Access to such machines is often possible but, for economic reasons, only in a time-sharing environment where a large number of users have the computer time divided between them . So a simulation task might run in real time if no one else was using the system but, under normal usage, the timing of the task would be much slower and entirely dependent on the load put upon the machine by other users .

Supercomputers often 'pipeline' instructions, that is they split each instruction into its component parts; fetch from memory, arithmetic operation and then store in memory; and can fetch the next

- 25 -

piece of data while the last one is in the arithmetic stages, which means that a far higher processing speed is obtained . Several pipelines often run together in step performing the same instructions on many pieces of data (SIMD).

## 1.3.2 MIDI AND MINICOMPUTERS

Coming down the price scale in digital computing hardware are the midi and mini computers . These are more in the price range of large research groups . Naturally the power of these machines cannot compare to that of the supercomputers and the size of the memory available is smaller, but they do give a viable way of simulating power systems in real time, even if the systems that can be simulated in real time are restricted in size due to the lower computing power . These machines normally only operate as SISD machines and although some degree of pipelining may be possible there is normally only one pipeline in the machine .

One advantage the larger computers do have is that the development and operation of software can all be performed on one machine . Support for minicomputers in terms of software and hardware tools available is good and, with high level languages as standard, software written for one machine can easily be transferred onto a different machine .

#### 1.3.3 ARRAY PROCESSORS

To improve the performance of minicomputers, without the expense of moving to a mainframe, array processors have been developed to provide execution rates far higher than available on minicomputers for certain types of operation. These machines require a minicomputer as a host and are used for performing arithmetic on vectors and arrays. The host computer normally loads the array processor by direct memory access (DMA) and lets the processor calculate the required result, for example a matrix multiplication, and then obtains the answer by DMA again.

The array processor is similar to the processing element in a mainframe, using a parallel, pipelined structure to give high computation rates for certain types of mathematical operations. An array processor is a form of MIMD machine but in a very restricted way; having for example two pipelines, one for addition/subtraction and the other for multiplication/division, and a processor dedicated to integer and indexing problems . D.M. Detig [16] suggests that array processors will not realise large improvements for power system applications . However recent developments such as cross compilers for FORTRAN allow array processors to be programmed in high level languages . This means that the effort required to put algorithms on array processors has been reduced and programmers do not need to know about the structure of the hardware or how to program it directly .

- 27 -

Using a cross compiler, the simulator currently used at Durham has been transferred onto a FPS 5205 array processor giving a speedup of 3-4 times and, with further tailoring of the algorithm to suit array processor architecture, it is hoped to improve this .

# 1.3.4 MICROPROCESSORS AND MULTI MICROPROCESSORS

The growth in power and reduction in cost of microprocessors and their peripherals has led to a great deal of interest in using them for power system applications . The development of affordable microprocessors with high execution rates and 16 or 32 bit word lengths has meant that they can provide performance nearing that of minicomputers at a fraction of the cost . In addition, the software support for them (including compilers for many high level languages) means that code already developed can often be transferred onto microprocessors with a minimum of effort . To give one example of the high execution speeds possible, a benchmark run on a Motorolla microprocessor with floating point maths hardware took 1.5 times as long as a VAX 8600 which cost at least 30 times as much . While the structure of this benchmark certainly favoured the microprocessor it shows that for some types of application their value for money is excellent .

A natural step forward with such cheap processing power is to try to run several processors simultaneously on a problem . This configuration enables different operations to be carried out on

- 28 -

various pieces of data at any one time (MIMD). Several studies have been made on the use of these multi microprocessor systems in power system analysis. H.H. Happ [18], J. Fong et al. [19] and F.M. Brasch et al. [20] looked at their application to power system studies in general, while W.L. Hatcher et al. [21], R. Lopez-Lopez [22], S.N. Talukdur et al. [23] and L. Dale et al. [24] looked at transient stability studies and simulation. Many other researchers have studied the general use of multi microprocessors, including H. Mukai [25], S.H. Fuller et al. [26] and A.K. Jones et al. [27]. Work on modelling their effects was undertaken by J. Grosser and S.N. Talukdur [28] who produced models to estimate the run time of algorithms when put onto a MIMD machine.

The main difficulty with the use of multiprocessor systems is that the problem has to be split into parts which can be solved simultaneously . With most computing being a sequential set of instructions this is not always easy . Some problems break down into parts quite readily while others simply cannot be computed in parallel and so no gain can be made by using more than one processor.

Several systems have been built, or designed, to utilise this type of architecture, the most widely known being the  $CM^*$  at Carnegie-Mellon University on which several of the above papers are based . However any system developed as a general purpose system will not give optimum performance for a specific task and, with the low price and relative ease of construction, it may well prove

- 29 -

advantageous to design the hardware around the software if it is just to be used for one specific task.

#### 1.4 MULTIPROCESSOR SIMULATION

The research group at Durham has been involved in the field of power system research for over 18 years and recently some third year undergraduates looked into the possibility of producing a power system simulator using a multi microprocessor system .First A. Perry [29] in 1982 and then J. Thomson [30] in 1983 carried out work which showed that it should be possible to produce a simulator which would run on hardware far cheaper than a minicomputer .

For any problem to be solved efficiently using a multiprocessor there are three requirements which have to be met by the software :

- a) First, the problem must be split into parts which can be computed in parallel on the separate processors. Some problems are so non linear that this is impossible but for many problems at least part of the solution can be split up and performed in parallel.

- b) Secondly, the amount of processing that has to be done centrally by a single processor must be minimised. The main advantage of a parallel processor is the speed of computation and any computing carried out centrally does not take advantage of this .

c) Thirdly, the time spent in communicating between the processors must be minimised . There is a finite limit on the speed of data transfer and this can be one of the major bottlenecks in any multiprocessor system . Not only is the amount of data to be transferred important but the time spent on setting up each transfer can be significant . It is, therefore, preferable to have a few transfers with large amounts of data than to have many small transfers .

Both Perry and Thomson used the TMS 9995 microprocessor for their studies. However with the advent of chips with 32 bit data structures it was decided to change to a more powerful processor. The main requirements for the processor for the multiprocessor simulator were those of processing power and support, both in hardware and software.

Two types of processor were looked at in detail, the Motorolla M68000 family and the Inmos Transputer . The processor that was finally decided upon was the M68000 for the following reasons:

#### 1.4.1 HARDWARE SUPPORT

Hardware support is available in two forms . First the availability of a development system on which programs can be tested and debugged before implementing them on the actual hardware . Secondly the availability of hardware compatible with the microprocessor out of which a workable system to run the software can be built .

- 31 -

The M68000 had both these, a UNIX based development system being available within the university while boards using the processor could be designed and manufactured by the university. Also the M68000 was the first of a family of processors and more powerful versions would be available as the project went on . The Transputer was still under development and systems which emulated it were only just becoming available . It was, however, specifically designed for use as a multi processor system and in the future may well become an extremely powerful tool in parallel systems for all types of applications .

Finally, in terms of hardware support, the processor had to have specialised hardware available to perform the mathematical operations for floating point numbers because realising them in software is far too time consuming. Motorolla were due to bring out their maths coprocessor for use with the M68000 family .However, other floating point hardware is available which can be used with the Motorolla microprocessor, some of which give far better performance than the Motorolla co-processor .

## 1.4.2 SOFTWARE SUPPORT

The availability of high level languages such as FORTRAN and C greatly helps the development of programs and makes them easier both to read and to change . Also any programming done in a high level language can be transferred onto other machines with a minimum of effort so that the software does not become obsolete when the hardware is out of date . However when developing hardware as well as software it is quite often necessary to program in assembler as well as the high level languages and the availability of development software to facilitate this again saves time .

The Transputer was designed to be programmed using OCCAM, a concurrent programming language for use with multiple microprocessors. The M68000, using the UNIX development system had access to some powerful development and debugging tools and a number of different languages, some of which were also available on the university's mini computers as well. Thus algorithms could be tested on either the development system or a mini computer before they were tried on the multiprocessor system itself.

### 1.5 RESEARCH OBJECTIVES

The main objective of this research was to develop a real time power system simulator for use by the research team at Durham in the development of an energy management system. This objective can be split into a number of separate tasks :

a) First, to design efficient software for the power system simulation, capable of being used on its own as a research simulator and, in conjunction with an EMS, as a dispatcher training and teaching simulator. Also the simulator should, with the use of short time steps, be able to simulate the transients in the system for transient studies .

- b) Secondly, to develop microprocessor hardware to best utilise the parallelism of the software developed and produce a working simulator which was easily expandable to model different sizes of power systems.

- c) Thirdly, to examine the limitations of the simulator developed. Both in terms of the size of system that could be modelled using the hardware and the time step that could be achieved by using different numbers of processors in the hardware.

#### 1.6 THESIS LAYOUT

The original work put forward in this thesis, which can be found discussed in detail in the conclusions, is twofold . First the production of power system simulator software for use on parallel processors, in particular a parallel algorithm for the solution of the set of algebraic network equations, which minimises both the data transfer between processors and the amount of computing to be done centrally . Secondly, the implementation of the software on hardware suitable for exploiting the parallelism of the algorithms and the timing of the resulting simulator for various sizes of network .

The thesis itself can be split into four discrete parts :

- 34 -

- a) Chapters 2,3 and 4 deal with the methods of modelling the various power system components, Chapters 2 and 3 covering the generator, load and network models suitable for parallel computation while Chapter 4 looks at the theory finally used on the parallel processors .

- b) Chapters 5 and 6 deal in detail with the simulator that has been developed, Chapter 5 containing the software details while Chapter 6 describes the simulator hardware.

- c) Chapters 7 and 8 present the results obtained, both the timings of the algorithms and the results of certain test runs carried out, and the conclusions drawn from the research .

- d) The final part contains the references used in the thesis and the appendices . Each appendix contains some material to expand on a certain part of the body of the thesis .

#### 2 GENERATION AND LOAD MODELLING

The simulation problem can be split into two parts . Firstly, the solution of the equations relating to the dynamic parts of the system, such as the generators and loads . Secondly the use of the results obtained for the generation and load values to produce a set of values for the voltages and power flows around the network . This split between the dynamic and network equations means that different generator and load models and solution techniques can be used without affecting the network solution . The only connection between the network and the dynamic solutions are the parameters produced by one part for the other part to use . Thus the only restriction placed upon the dynamic models is that they utilise and produce the correct parameters to interface correctly with the network model .

This possibility of changing the dynamic models used by the simulator means that different uses to which the simulator may be put can be accommodated . For instance for transient studies the dynamic models have to be extremely accurate and the time step very short in order to show the full dynamic response of the system to any changes made . The simulator may not run in real time with this sort of model, but this is not as important as the production of highly accurate results . However for training purposes the transients, over which the operator has no real control, need not be as accurately simulated but the results must be produced in real time so that the operator is given the right amount of time in which to respond . This separation of the dynamic and network equations means that any dynamic model and solution technique can be used . By producing the software in a modular fashion the interchange of dynamic models can be made extremely easy . Several papers have been written on the affects of various load and generator models on the results produced in simulators [31-37]. These can help to give a guide in the choice of what complexity of dynamic model to use for each of the different uses of the multiprocessor simulator .

#### 2.1 GENERATING EQUIPMENT MODELS

The models for the generating equipment in the system can be split into five separate parts . These are:

1) The supply, such as the boiler or reactor in thermal power stations and the reservoir in hydro stations . The thermal stations supply section must include elements such as the fuel supply to the boiler .

2) The prime movers, either gas turbines, steam turbines or hydro turbines and the mechanical governors controlling their rotational speed.

3) The shaft which transmits the mechanical power between the turbines and the synchronous machine. This has torsional elasticity,

- 37 -

inertia and damping due to friction in the bearings etc. which affect the dynamics of the system .

4) The synchronous machine itself, which converts the mechanical power produced by the turbine into electrical power for transmission across the grid .

5) Finally the excitation system which alters the field winding voltage in the synchronous machine to control the voltage produced at the machine terminals .

The most complex and important section of the model is the synchronous machine itself . This is because of the speed at which electrical transients can occur and the complexity of the interaction of the electric fields within the machine . The turbine and mechanical governor systems have slower time constants while the supply system reacts very slowly to any changes in the system . The time constants in the supply are of the order of minutes rather than seconds and those in the turbine range between about 10 seconds to 200 milliseconds .

#### 2.1.1 SUPPLY SYSTEM

The supply system for a typical coal fired station is shown in figure 2.1 . The coal is fed via conveyers to pulverisers, the coal dust is mixed with air and blown through fans into the boiler furnace, the boiler then produces the steam to drive the turbines .

- 38 -

There are several time constants involved in this sort of system: The amount of fuel processed by the pulverisers takes time to increase or decrease. The boiler heat output is slow to react to changes in the amount of fuel injected and there is often a large volume of steam reserve in the supply system so that changes in steam pressure occur slowly.

In a hydro station the simplicity of the supply system means that it has far fewer time constants and the power station can react far faster to changes in the demand . This means that large hydro stations such as the Dinorwig pump storage scheme in North Wales can be used to control the system frequency by going from standby to produce up to 1800 Meggawatts in only eleven seconds .

For thermal stations there are several different boiler models available, these often model the control on the boiler as several feedback loops using the boiler pressure, turbine steam flow and turbine speed. These, when modelled using the various time constants involved, give the boiler response to changes in turbine load. For the hydro supply the only time constant to be taken into account is that of the water supply to the turbine so the modelling is simplified greatly.

### 2.1.2 PRIME MOVER MODELLING

The prime movers are the machines which produce the rotation for the generators, this might be a series of steam turbines in a

- 40 -

thermal station as shown in figure 2.2 or a water turbine in a hydro station . For the thermal turbines there is a time constant before each of the turbines in the set corresponding to the steam chest, reheater or storage time . For example any change in boiler pressure first has to be passed through the steam chest before reaching the high pressure turbine, then to reach the intermediate pressure turbine the pressure change has to be relayed through the high pressure turbine and the reheater . A similar process occurs for the change to reach the low pressure turbines . Thus part of the pressure change affects the low pressure turbine a significant amount of time after affecting the high pressure turbine . These time lags should all be represented in the turbine model if highly accurate results are required from the simulator .

The other part of the generating equipment which is modelled with the turbine is the mechanical governor controlling the power input to the turbine in the form of steam input in thermal stations or water in hydro stations . This can be simply represented by a feedback loop with a single time constant representing the speed of response of the governor, a governor gain representing the sensitivity of the governor and upper and lower limits set on the amount of power input to the turbine . The rate of change of the input power can also be limited to model the speed of opening or closing of the steam valve controlled by the governor .

- 41 -

# Figure 2.2) Prime mover string

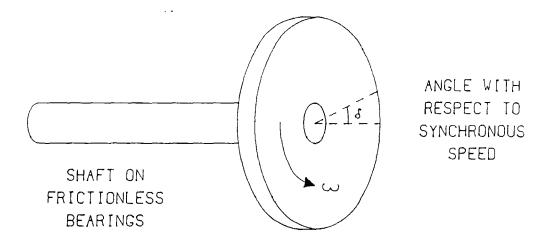

#### 2.1.3 SHAFT MODELLING

The shaft which connects the various turbines to the synchronous machines is usually an extremely large and heavy piece of equipment rotating at quite high speeds. The shaft has elastic properties inherent in its manufacture and damping due to the friction in the bearings and the drag due to the rotation of the shaft in the surrounding fluids. Thus the dynamics of the shaft itself can be extremely complex and can cause certain harmonic effects in the generating equipment.

For simulations in which the high speed oscillations of the shaft are not important the shaft can be modelled as a single lumped inertia with a damping term . For detailed transient studies the elasticity of the shaft has to be included to show the effects of resonance .

#### 2.1.4 SYNCHRONOUS MACHINE MODELLING

For a balanced, three phase power system the equations governing the synchronous machine can be split into the direct and quadrature axis. This is done by using Parks equations. From these equations an approximate set of equations to represent the machine can be derived. The assumptions used to create this set of equations vary depending upon the use to which the simulator is to be put. For use in EMS development, operator training or teaching environments the long term system dynamics are more important than the short term transients . Taking this into account a set of simplifying assumptions can be made to the synchronous machine model . These can give a representation as shown in figure 2.3 where:

- E' voltage behind generator impedance

- E. voltage at generator terminals

- $X_{o}, X_{q}$  direct and quadrature axes reactances

- R<sub>A</sub> generator resistance

- It generator current

- $I_{\omega}, I_{\alpha}$  direct and quadrature components of generator current

The assumptions made to simplify the generator equations to this level are:

- a) Neglect the modelling of all the harmonics of greater then second order. The amount of high order harmonics in a modern generating equipment is small so this is a reasonable simplification to the model.

- b) Assume that the magnetic circuit in the synchronous machine performs in a totally linear way. For the modelling of slow transients this is a reasonable assumption. However, for transient studies needing high speed transient representation the saturation of the magnetic paths should be taken into account.

Figure 2.3) Approximate generator vector diagram

# Figure 2.4) Excitation system block diagram

c) The independence of the generator's parameters from any frequency changes . Frequency dependence can be modelled if required but any increase in the model complexity will cause the simulation time to increase .

This model gives the following equations to govern the electrical characteristics of the synchronous machine.

$$\mathbf{E}_{t} = \mathbf{E}' - \mathbf{j} \mathbf{X}_{D} \mathbf{I}_{D} - \mathbf{j} \mathbf{X}_{Q} \mathbf{I}_{Q} - \mathbf{R}_{A} \mathbf{I}_{A}$$

(2.1.1)

$$I_{A} = I_{D} + jI_{Q} \qquad (2.1.2)$$

If the further assumption that the direct and quadrature axes reactances are the same is made  $(X_D = X_Q)$  then equation (2.1.1) reduces to:

$$\mathbf{E}_{t} = \mathbf{E}^{t} - \mathbf{j} \mathbf{X}_{D} \mathbf{I}_{D} - \mathbf{j} \mathbf{X}_{D} \mathbf{I}_{Q} - \mathbf{R}_{A} \mathbf{I}_{A}$$

(2.1.3)

which, by incorporating equation (2.1.2), then reduces to:

$$E_t = E' - I_{\rho} * (R_{\rho} + jX_{D})$$

(2.1.4)

There are many assumptions that can be used to develop ways of obtaining the value for E', the voltage behind the machine impedance . The following equation couples the voltage with the field current :

$$E' = \omega * M * I_{r}$$

(2.1.5)

where M is the mutual inductance between the field winding and the armature winding and  $\omega$  is the rotor speed. This can be assumed to be constant the voltage becomes a simple function of rotor speed and

field current . For a far more simple model the value of E' can be fixed at a particular value governed by the initial conditions of the model . If any relation to the field current is used then a model of the excitation system used by the synchronous machine must be present to provide values of  $I_{\rm f}$  .

#### 2.1.5 EXCITATION SYSTEM MODELLING

On any synchronous machine there must be some form of excitation system to provide the voltage to the field winding. This voltage produces the magnetic flux in the generator which induces the electrical currents in the rotor windings.

The field voltage is often controlled by an Automatic Voltage Regulator (AVR). This piece of equipment monitors the terminal voltage of the synchronous machine and varies the field voltage accordingly. This is, therefore, a simple feedback control system and has various time constants associated with it. Typically these time constants are short enough to be ignored for uses which do not require high speed transients to be modelled. A single time constant is included to model the time lag between the altering of the field voltage and the resultant change in the voltage behind the transient reactance. Also there are upper and lower limits placed upon the field voltage, this produces a model which can be represented by the block diagram shown in figure 2.4. Where T is the time constant and K the gain in the feedback system .

#### 2.2 LOAD MODELLING

The loads in the system also need to be modelled accurately to enable the simulator to produce satisfactory results. There are various types of load present in any network, from the simple lighting loads to the complex dynamic loads such as industrial motors. Several papers have been written on the effects of load modelling [34 - 37] and there are a series of models available for the different types of loads or for modelling a more general mixture of load.

#### 2.2.1 GENERAL LOAD MODEL

One of the most commonly used load modelling techniques is to represent the way in which the magnitude of the load varies with changes in the supply voltage :

$$P + jQ = P_0 * |V|^{M} + jQ_0 * |V|^{N}$$

(2.2.1)

where  $P_{\odot} + jQ_{\odot}$  is the load power at per unit voltage and M and N are constants for the particular combination of loads being modelled . This model can be expanded further to include variations of the load due to fluctuations in the supply frequency :

$$P + jQ = P_{o} * (|V|^{N} + A(F - F_{o})) + jQ_{o} * (|V|^{N} + B(F - F_{o})) \quad (2.2.2)$$

with A and B again being constants for the particular type of load, F is the system frequency and  $F_{\rm o}$  the standard system frequency .

- 48 -

Three special cases of equation (2.2.1) are often used for simplifying the load model, these are: M=N=0 which gives a load with constant power characteristics, M=N=1 which gives constant current and M=N=2 representing constant impedance loads .

#### 2.2.2 DYNAMIC LOAD MODEL

Another way of representing those loads in the system which are dynamic, such as industrial motors, is to use a similar model as that used for the synchronous machine in the generating station model. This is normally done by representing a group of motors as a single dynamic load with inertia and damping due to friction . The model acts in exactly the same way as in synchronous machine model but the input power from the turbine is replaced by a load on the motor ( this load may vary with speed ) . Also instead of producing electrical power and injecting it into the network the motor removes power from the system to satisfy the load .

#### 3 NETWORK SOLUTION

The second part of the simulation problem is the solution of the network equations to determine the voltages at the nodes and the power flows along the lines . The network routine has to be performed twice for each time step: this is because the generator routine needs an intermediate network solution before it can calculate the final generator solution . The actual network values are then calculated by the network routine using the final generator solutions . The time taken for each network solution is, therefore, critical because there have to be two network solutions performed: thus the algorithm must minimise, as far as possible, both the amounts of data transfer needed and computing time taken .

There are several ways of solving the set of algebraic equations which govern the network characteristics and several assumptions which can be made to simplify the calculations. Some of these methods can readily be used on parallel processors while others are too non linear or involve too much data transfer to be split for parallel computation. Several methods were tried before one was developed which fully utilised the parallel processor architecture.

#### 3.1. GAUSS METHOD

The Gauss method is a basic iterative method for solving a set of equations and it has several variations, such as the Gauss-Seidel method .

The standard method is simple to divide between a set of processors for parallel computation and the Gauss iteration also has the advantage of being very simple, both in mathematical technique and in programming required .

The equations representing the system can be represented in matrix form thus:

$$\mathbf{Y} \qquad \mathbf{*} \qquad \begin{bmatrix} \mathbf{V}_{1} & & \mathbf{I}_{1} \\ \vdots \\ \vdots \\ \mathbf{V}_{n} & & \mathbf{I}_{n} \end{bmatrix} \qquad (3.1.1)$$

The exact formulation of this equation is covered in detail in the theory section, Chapter 4, of this thesis . It is simply a matrix version of Kirchhoff's current law which states that the sum of all currents entering a bus must be zero . The equation (3.1.1) is constructed using complex numbers,  $V_{\rm p}$  is the voltage at node p while  $I_{\rm p}$  is the injected current at that node . The Y matrix consists of elements representing the admittance and line charging of the lines connecting the nodes . Looking at a single row of equation (3.1.1) we obtain :

$$I_{p} = \sum_{q=1}^{q=n} (Y_{pq} * V_{q})$$

$$(3.1.2)$$

$I_{\rm p}$  is the current injected at node p due to any load or generation . If the total generation minus the total load at node p is  $(P_{\rm p}$  +  $jQ_{\rm p})$  then  $I_{\rm p}$  can be written as :

$$I_{p} = \frac{(P_{p} + jQ_{p})}{(V_{p})^{*}}$$

(3.1.3)

- 51 -

the \* indicating the complex conjugate of a quantity . Combining equations (3.1.2) and (3.1.3) gives :

$$\frac{(\mathbf{P}_{p} + \mathbf{j}\mathbf{Q}_{p})}{(\mathbf{V}_{p})^{**}} = \sum_{\mathbf{Q}=1}^{\mathbf{Q}=\mathbf{n}} (\mathbf{Y}_{p}, \mathbf{v} + \mathbf{V}_{p})$$

(3.1.4)

This can be rewritten in a form suitable for Gaussian iteration by taking the value  $V_{\rm p}$  out of the summation on the right hand side (3.1.5). This equation is then executed iteratively for all nodes . The initial guesses for V are put into the right hand side and a new estimate calculated: the new estimate is then used on the right hand side until two consecutive sets of answers agree within a given tolerance. If  $V_{\rm p}$  is the k<sup>tr</sup> estimate of the voltage at node p then the next estimate is calculated by :

$$V_{P^{k+1}} = \frac{(P_{P^{+}} + jQ_{P})}{Y_{PP^{+}} * (V_{P^{k}}) *} - \frac{q^{=n}}{\sum} \frac{(Y_{Pq^{-}} + V_{q^{k}})}{q \neq p}$$

(3.1.5)

$$q \neq p$$

$$q = 1$$

The calculations can be speeded up further by using an acceleration factor on the calculated voltages . This simply involves increasing the size of the change in voltage at each iteration :

$$\Psi^{\mathbf{k}+1} = \Psi^{\mathbf{k}} + \alpha(\Psi^{\mathbf{k}+1} - \Psi^{\mathbf{k}}) \qquad (3.1,6)$$

where  $\alpha$  is the acceleration factor . For load flow type calculations a value of around 1.2 or 1.3 has proved to give the best results . This whole algorithm can easily be divided into sections for parallel processing . Each processor is given a set of nodal voltages to calculate together with

a copy of the required parts of the Y matrix at the start of the simulation . The values of  $(P_{rp} + jQ_{pp})$  have to be updated each time step for those nodes with generators to incorporate the generated power calculated by the generator algorithm . Then at each iteration the latest values of V are passed to all processors and a new set calculated . This method has several advantages:

- a) The Y matrix has relatively few elements and this sparsity helps to reduce both the memory requirements for the algorithm and the amount of non zero terms in the summation portion of equation (3.1.5).

- b) Any changes in the network such as the outage of a line require very little computation and the altering of only four of the elements in the Y matrix. Load changes affect only the  $(P_{\rm p} + jQ_{\rm p})$  value for a node, which is easily updated.

- c) The computing can also be reduced by calculating the values of  $Y_{_{\rm FP}}/Y_{_{\rm FP}}$  at the start of the simulation as they remain constant throughout until affected by network changes .

- d) The time for a single iteration is small and only one iteration is required when the system is in a steady state .

- e) Although all the voltages have to be updated in each of the processors for each iteration the data transfer occurs in a single

- 53 -

block at the end of each iteration . This means that the time spent setting up the communication is small .

f) Finally, all the computing can be done in parallel . There is no need for any central calculation which would slow the algorithm down: only the communication with the host computer need be done by a central processor .

The Gauss method is well proven in its normal sequential form and the parallel form gives the same results . However, with some network configurations it fails to converge and simulation of the system becomes impossible by this method . The amount of data transferred between processors is quite large: all the nodal voltages have to be updated for each iteration . Also, when transients were introduced into the system, the number of iterations before convergence was achieved became large and the time taken by the algorithm, both in communication and computation, was far larger than the time step . This meant that real time simulation was not feasible .

As has been mentioned, there are several variations on the Gauss method . The most straight forward of these being the Gauss-Seidel in which, instead of waiting for a full set of voltages to be calculated before substituting them back in, the most recent voltage calculated is always used . For example when a new value of V, has been obtained it is used to help calculate  $V_2$  and then both are used in  $V_3$  and so on until  $V_m$  is calculated . From equation (3.1.5) this gives :

- 54 -

$$V_{r_{1}}^{h+1} = \frac{(P_{r_{1}} + jQ_{r_{2}})}{Y_{r_{1}r_{2}} * (V_{r_{1}}^{h}) *} - \frac{\sum_{q=1}^{q=p-1} (Y_{r_{2}} * V_{q}^{h+1})}{Y_{r_{2}r_{2}}} - \frac{\sum_{q=n}^{q=n} (Y_{r_{2}} * V_{q}^{h})}{Y_{r_{2}r_{2}}}$$

(3,1,7)

When this is implemented in a parallel form the data transfers between processors become spread throughout the algorithm instead of one block at the end of each iteration. This increases the overheads on the data transfers but reduces the number of iterations needed.

A compromise can be obtained by each processor using the latest values it has computed but ignoring those calculated by other processors until the start of the next iteration . This reduces the number of iterations without altering the data transfer, but does not have a large enough effect to enable real time simulation .

One possible solution to the problem of the time taken by the network solution would be to have a variable time step depending on the conditions . When the simulator needed several iterations to converge the time step could be lengthened to allow real time simulation to continue . However, this would loose one of the main attractions of having a short, fixed time step for the simulation ; that of modelling the transient response of the system .

#### 3.2 NEWTON-RAPHSON METHOD

Another method of modelling the network is to use the Newton-Raphson load flow method . This method relates the active and reactive power mismatches in the system to the voltage angle and magnitude :

$$\Delta \mathbf{P} = \begin{array}{ccc} J_{1} & J_{2} \\ = \end{array} \qquad \mathbf{*} \\ \Delta \mathbf{Q} \\ \end{array} \qquad \begin{array}{c} J_{3} & J_{4} \\ \end{array} \qquad \Delta \mathbf{V} \end{array} \qquad (3.2.1)$$

The square matrix containing  $J_1, J_2, J_3$  and  $J_4$  is the Jacobian matrix of the system (W.F.Tinney and C.E. Hart [13]) .  $\Delta P$  and  $\Delta Q$  are the power mismatches in the system with the present estimates of voltage while  $\Delta \theta$ and  $\Delta V$  are the changes in voltage angle and magnitude to be made for the next estimate . This procedure is iterated until both  $\Delta \theta$  and  $\Delta V$  are smaller than a particular convergence value.

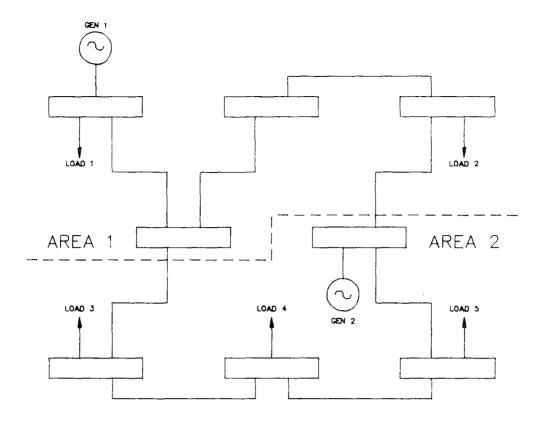

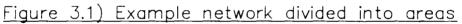

To divide the algorithm so it could be split into parts for parallel computation the power system was divided into areas. The solution of each area was then performed by a separate processor. The flow of power between the areas was represented by calculating the power flowing along the lines connecting the areas and including this power as an injection or drain on the relevant buses as shown in figures 3.1 and 3.2. Thus a processor only needs to know the voltage of the bus at the far end of each of its inter area lines before the start of each iteration. The solution procedure is as follows :

1) Form the four submatrices  $J_1, J_2, J_3$  and  $J_4$  from the parameters of the system and combine these to give the complete Jacobian matrix as given in equation (3.2.1).

Figure 3.2) Connecting lines replaced by loads

- 2) Calculate the power mismatches  $\Delta Q$  and  $\Delta P$  at all buses including the dummy loads which represent the lines cut when the network is divided into areas .

- 3) Solve the equation (3.2.1) using Zollenkopf bi-factorisation [38] to produce  $\Delta\theta$  and  $\Delta V$ . Update the old values of V and  $\theta$  using the calculated changes .

- 4) Repeat steps 2-3 until the values of  $\Delta Q$  and  $\Delta P$  are smaller than a given tolerance .

When a line outage occurs the Jacobian matrix changes . However, the Jacobian is only altered between time steps, never part way through a set of iterations . To make the calculation of the Jacobian easier the right hand column matrix is altered to contain  $\Delta V/V$  instead of  $\Delta V$ . This change does not affect the convergence or accuracy of the algorithm . This method has several advantages over the Gaussian method;

The data transfer between areas for each iteration is limited to the voltages of the buses at the ends of connecting lines . By choosing the areas to minimise the number of tie lines the data transfer is reduced . The transfers also all happen at once so both the data transferred and the overheads on setting up the communication are small .

The number of iterations for convergence during transient conditions is small and even though the calculation of the matrix

- 58 -

factors is quite lengthy this is only performed once per network solution .

The method does not have the convergence problems of the Gauss routine: therefore it is far more robust for use in simulation .

The major drawback with this method is the calculation of the relative phase angles between areas . Each processor calculates the voltages in its area with reference to some reference voltage . To calculate the power flow along the connecting lines the relative angles must be known . The use of a generator routine which produces voltages with respect to a constant 50 Hz all the areas effectively use the same reference voltage . However, if an area is left without generation because of an outage, problems can arise in the calculation and convergence .

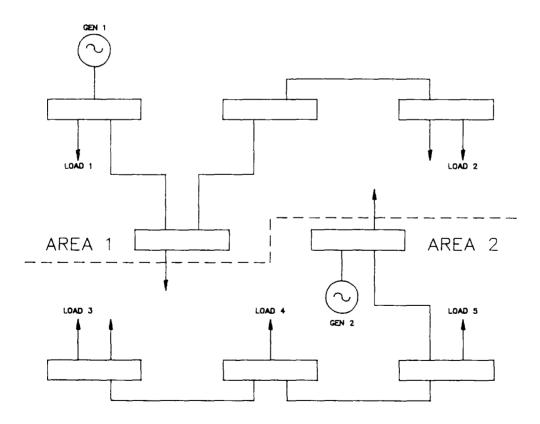

One way of avoiding this situation is to split the system through the buses instead of the lines ( figure 3.3). This solves the angle problem because any one bus must have the same voltage and angle in all the areas in which it appears. The power flow in the lines between the areas is again represented as loads on the split buses. Unfortunately, the convergence of this method was found to be far worse than the initial method because the power transfer between areas became problematical.

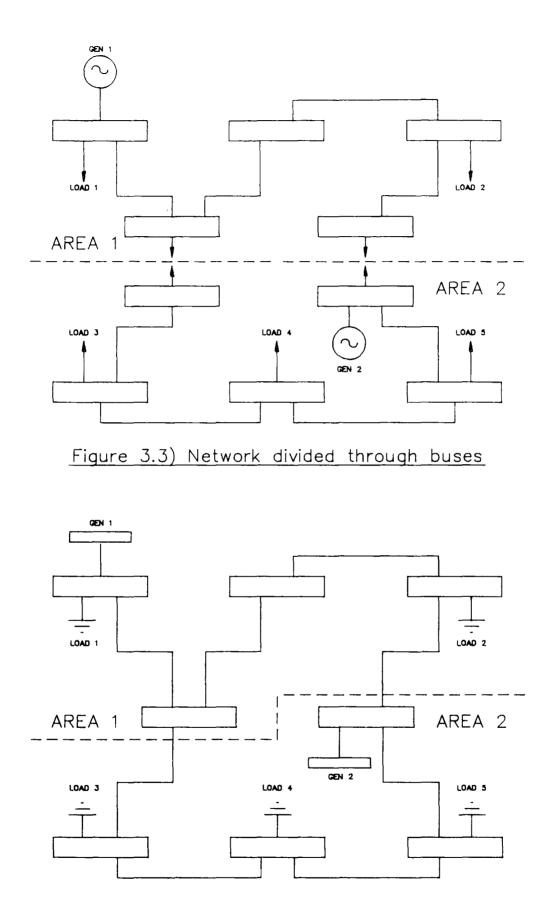

Figure 3.4) Network representation for direct method

#### 3.3 DIAKOPTICS

Diakoptics is a method of solving parts of a problem as separate entities and then combining the partial solutions to help provide an overall solution. The name derives from the Greek *kopto* meaning to tear and so these methods are sometimes known simply as tearing or piecewise methods. The method was first put forward by G. Kron and has been applied to many fields of engineering including the solution of power system network equations.

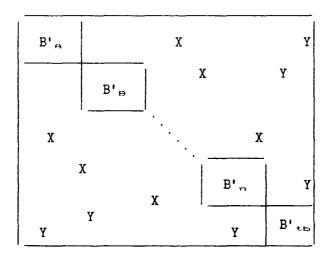

This technique is obviously a candidate for parallel processing since it inherently divides the network into parts for separate solution . Several methods have been developed for solving load flow problems using diakoptics (H.H. Happ [39]) . The piecewise method looked at for the simulator was based upon the diakoptic version of the fast decoupled load flow (M. El-Marsafawi et al. [40]) .

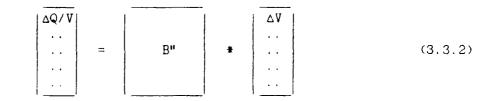

Starting with the equation (3.2.1) this method neglects the small cross coupling between the real power and voltage magnitude ( $J_2$  in the Jacobian ) and between the reactive power and the voltage angle ( $J_3$ ). Further simplifications are then made (B. Stott and O. Alsac [12]) to obtain the following equations which have to be solved :