# **Durham E-Theses**

# Characterisation of silicon mis negative resistance devices

Clifton, Paul Alan

#### How to cite:

Clifton, Paul Alan (1989) Characterisation of silicon mis negative resistance devices, Durham theses, Durham University. Available at Durham E-Theses Online: http://etheses.dur.ac.uk/6434/

#### Use policy

The full-text may be used and/or reproduced, and given to third parties in any format or medium, without prior permission or charge, for personal research or study, educational, or not-for-profit purposes provided that:

- a full bibliographic reference is made to the original source

- a link is made to the metadata record in Durham E-Theses

- the full-text is not changed in any way

The full-text must not be sold in any format or medium without the formal permission of the copyright holders.

Please consult the full Durham E-Theses policy for further details.

# CHARACTERISATION OF SILICON MIS NEGATIVE RESISTANCE DEVICES

by Paul Alan Clifton BSc (L'pool)

A thesis submitted for the Degree of Doctor of Philosophy in the University of Durham June 1989

The copyright of this thesis rests with the author. No quotation from it should be published without his prior written consent and information derived from it should be acknowledged.

# Declaration of Originality

I hereby declare that the work presented in this thesis has not previously been nor is currently submitted for any other degree.

The work reported in this thesis was carried out by the candidate, except where indicated by reference to other authors.

# DEDICATION

To my parents.

.

# ABSTRACT

Metal-insulator-semiconductor switches (MISS), in which the 'I' denotes some form of thin semi-insulating layer and the semiconductor part consists of a pn junction, are part of the general class of regenerative switching devices which includes the thyristor. The switching behaviour of the MISS derives from the ability of the MIS junction to exhibit current gain and to exist in two modes, deep depletion and inversion. In this thesis, a general model for the regenerative switching is proposed after investigating the properties of the MIS junction both theoretically and experimentally. Results from MIS diodes with tunnelling-thickness oxide I-layers indicate that interface states play a dominant role in their electrical behaviour and that the uniformity of the oxide is poor, giving rise to a large spread in the current-voltage characteristics. Subsequently, the epitaxial form of the MISS device is investigated and in particular the importance of isolation of the pn junction. It is concluded that spreading effects set a practical lower limit to the device dimensions, making the epitaxial form unsuitable for microelectronic applications. An alternative semi-insulator, 'silicon-rich oxide' (SRO) is introduced as an optional I-layer with possibly greater integrity than tunnel oxide. MIS diodes formed with SRO are shown to have very similar properties to tunnelling diodes. Large area devices fabricated using this material are surprisingly discovered to exhibit stable negative differential resistance (NDR). Although this discovery at first appears to be contrary to normal circuit stability criteria and to the regenerative feedback model itself, both of these points are resolved. It is shown that the frequency of oscillation of an unstable device is controlled by the external circuit. Then it is proposed that if this frequency is greater than the maximum frequency of operation of the regenerative mechanism, stable NDR is observed. In the final chapter, alternative lateral MISS structures which should overcome the geometrical limitations of epitaxial devices are discussed.

# ACKNOWLEDGEMENTS

Thanks are due to my supervisor Dr M.J.Morant for obtaining the SERC quota award which allowed me to undertake these studies. Special thanks go to Steve Lavelle with whom I enjoyed many fruitful theoretical discussions and whose rigorous approach to device modelling has raised the level of our understanding of the MISS device. The clean room technician, Mr.J.Gibson is also acknowledged for his very capable management of the fabrication facilities and for assistance in device processing. Closer to home, I thank my partner Sue for her great patience during the period of writing this thesis and for giving me the personal stability to see it through. Finally I thank all my family and friends who gave me much needed encouragement.

# CONTENTS

# 1. Introduction

Page

18

| 1.1 | Regenerative Switching Devices             | 1 |

|-----|--------------------------------------------|---|

| 1.2 | The MISS                                   | 2 |

| 1.3 | Thesis Outline                             | 4 |

|     |                                            |   |

|     | 2. Theory of the Non-Equilibrium MIS Diode |   |

| 2.1 | Introduction                               | 6 |

| 2.2 | Equilibrium MIS Diodes                     | 6 |

|     | 2.2.1 The MIS Diode Under Zero Bias.      | 7  |

|-----|-------------------------------------------|----|

|     | 2.2.2 MIS Diodes Under Reverse Bias.      | 7  |

|     | 2.2.3 Inversion in MIS Diodes.            | 9  |

| 2.3 | The Non-Equilibrium MIS Diode             | 10 |

|     | 2.3.1 Disequilibrium In Reverse Bias.     | 10 |

| 2.4 | Generation in the Surface Depletion Layer | 12 |

| 2.5 | Tunnelling Currents Through Thin Oxides.  | 13 |

|     | 2.5.1 Introduction.                       | 13 |

|     | 2.5.2. Electron Tunnel Current.           | 14 |

|     | 2.5.3.Hole Tunnel Current.                | 15 |

|     | 2.5.4. Tunnelling Via Surface States.     | 16 |

.

2.6 Conclusions

# 3. Fabrication and Characterisation of Tunnel Oxide MIS Diodes

| 3.1 | Introduction                                               | 21 |

|-----|------------------------------------------------------------|----|

| 3.2 | MIS Diodes with Tunnelling Thickness SiO <sub>2</sub>      | 22 |

|     | 3.2.1. Aluminium Top Contact                               | 22 |

|     | 3.2.2. The Aluminium-Oxide Interface                       | 22 |

|     | 3.2.3. Stoichiometric SiO <sub>2</sub>                     | 23 |

|     | 3.2.4. The Oxide-Silicon Interface                         | 23 |

|     | 3.2.5. The Silicon Surface                                 | 24 |

| 3.3 | Theory of Thin Oxide Growth                                | 25 |

| 3.4 | Fabrication of Tunnel Oxide MIS Diodes.                    | 27 |

|     | 3.4.1. Cleaning of Substrates                              | 27 |

|     | 3.4.2 Growth of Field Oxide                                | 28 |

|     | 3.4.3. Patterning of the MIS Windows                       | 28 |

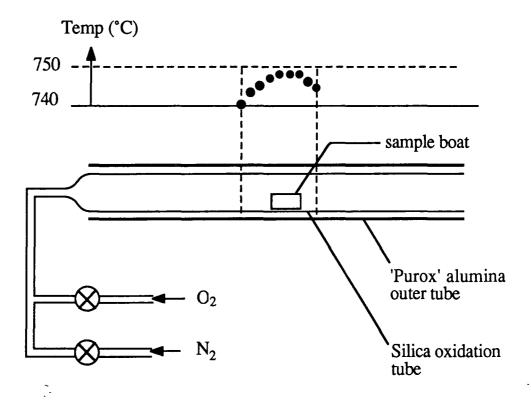

|     | 3.4.4. Growth of Tunnel Oxides                             | 29 |

|     | 3.4.5 Evaporation and Patterning of the Aluminium Contacts | 30 |

|     | 3.4.6 Back Contact Metallisation                           | 31 |

| 3.5 | Determination of Tunnel Oxide Thickness                    | 31 |

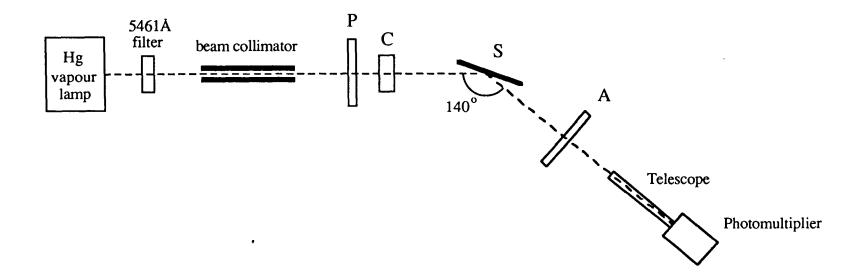

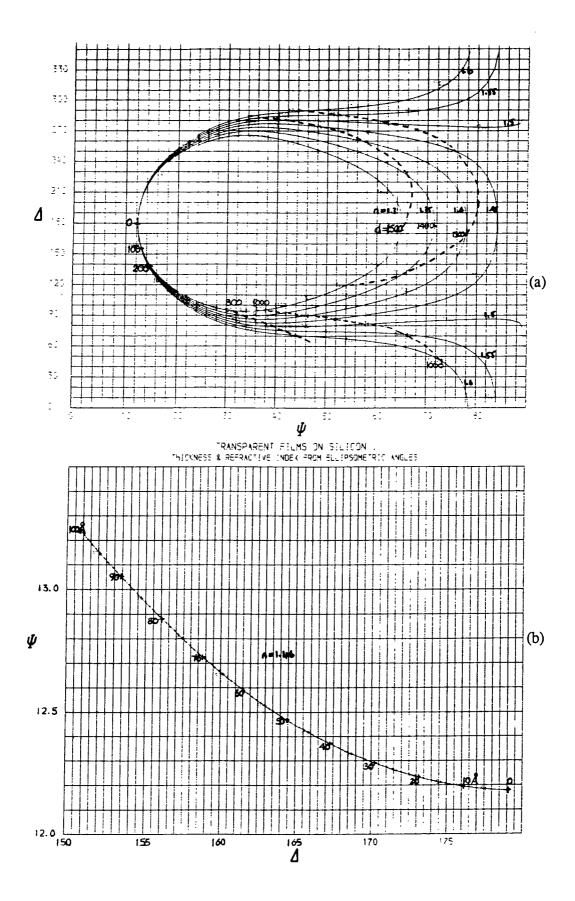

|     | 3.5.1 Measurement of Ultra-Thin Oxides by Ellipsometry     | 31 |

|     | 3.5.2 Measurement of Accumulated Capacitance               | 32 |

| 3.6 | Electrical Characterisation of MIS Diodes                  | 33 |

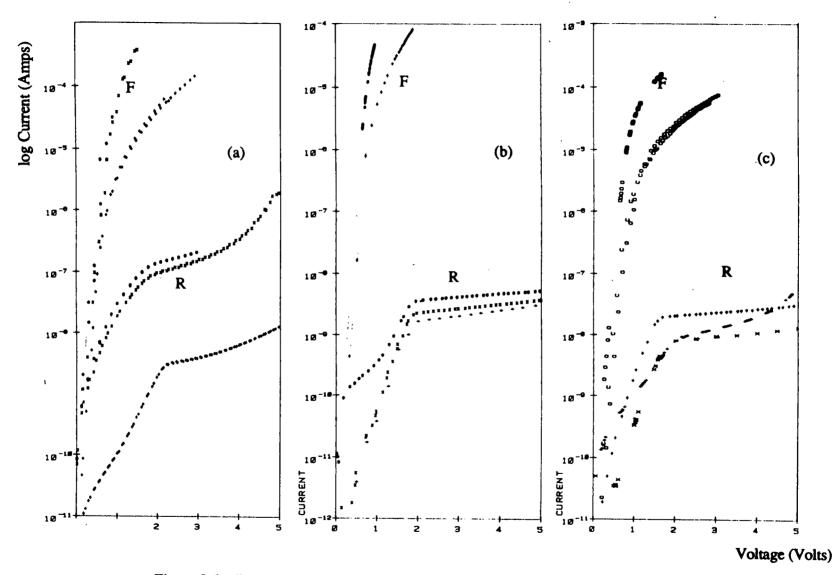

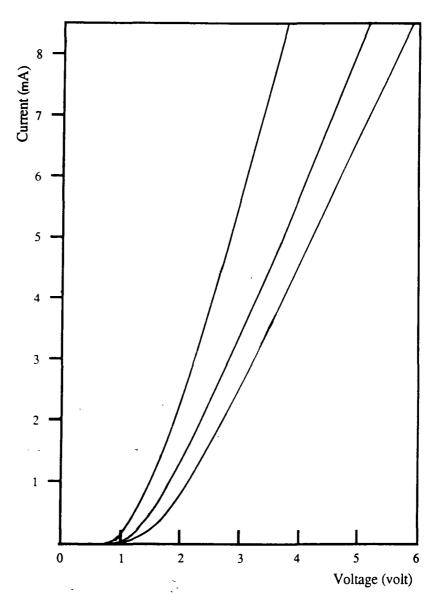

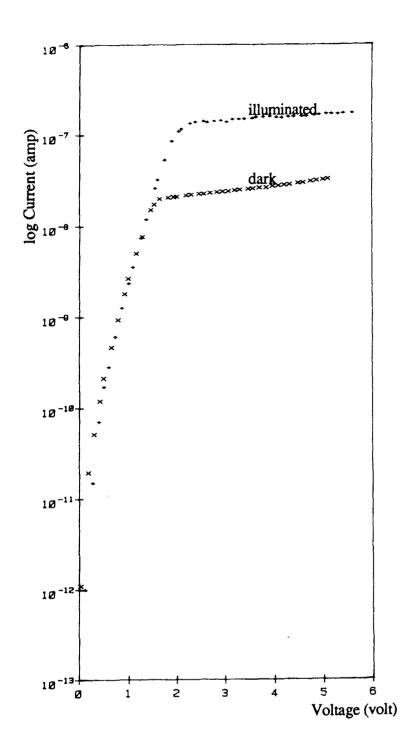

| 3.7 | Current-Voltage Characteristics                            | 33 |

|     | 3.7.1 Forward Bias                                         | 34 |

|     | 3.7.2 Reverse Bias                                         | 38 |

|     | 3.7.3 The Reverse Saturation Current                       | 38 |

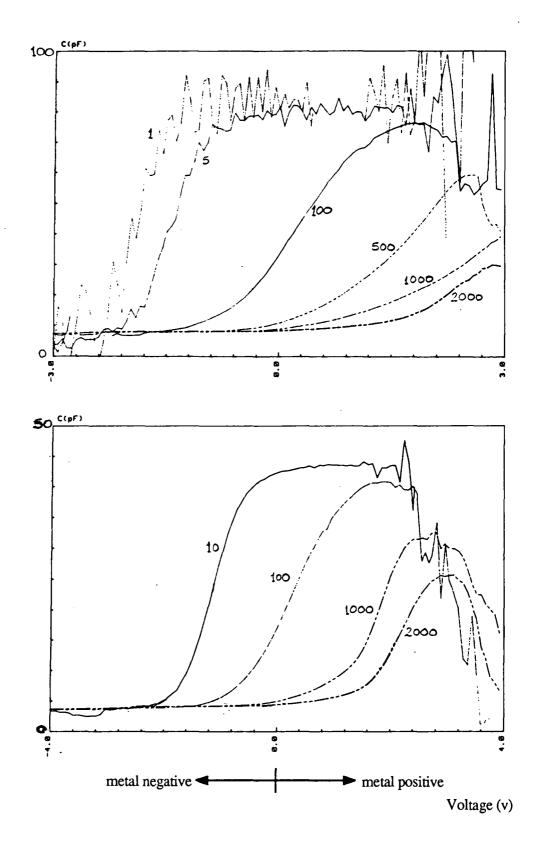

| 3.8 | Capacitance-Voltage Characterisation of MIS Diodes         | 41 |

| 4. A Theoretical Basis for the Study of MISS Devices |    |

|------------------------------------------------------|----|

| 4.1 Introduction                                     | 47 |

| 4.2 A Steady State Model of the MISS                 | 48 |

| 4.3 The pn Junction                                  | 49 |

| 4.3.1 Recombination in the pn Junction               | 50 |

| 4.3.2 Hole Diffusion Current.                        | 50 |

| 4.3.3 Electron Diffusion Current.                    | 52 |

| 4.4 The MIS Junction                                 | 53 |

| 4.4.1 Direct Tunnel Currents.                        | 53 |

| 4.4.2 Generation in the Surface Depletion Region.    | 54 |

| 4.5 Formulation of the Steady State Model            | 54 |

| 4.6 A General outline of the Switching Mechanism.    | 55 |

| 4.6.1 The Off State.                                 | 56 |

| 4.6.2 The Switching Point.                           | 56 |

| 4.6.3 The NDR Region.                                | 57 |

| 4.6.4 The Holding Point.                             | 58 |

| 4.6.5 The On State.                                  | 58 |

| 4.7 The Modes of Operation of the MISS Device        | 58 |

| 4.7.1 The 'Avalanche' Mode.                          | 58 |

| 4.7.2 The 'Punch-Through' Mode.                      | 59 |

| 4.7.3 The Generation-Controlled Mode.                | 59 |

| 4.7.4 The 'High Current' Mode.                       | 60 |

| 4.7.5 A Synopsis of the pn-MIS Junction Interaction. | 60 |

| 4.8        | Regenerative Switching in the MISS.                                                                                                                                                                                                                                                                                            | 61                               |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

|            | 4.8.1 Introduction.                                                                                                                                                                                                                                                                                                            | 61                               |

|            | 4.8.1 The Regenerative Feedback Model of the MISS.                                                                                                                                                                                                                                                                             | 61                               |

| 4.9        | A Proposed Model of the MISS Consistent with Thyristor Theory.                                                                                                                                                                                                                                                                 | 63                               |

|            | 4.9.1 The MIS as an 'Inversion Base Bipolar Transistor'.                                                                                                                                                                                                                                                                       | 64                               |

|            | 4.9.2 The Small-Signal Gain of a Tunnel Oxide IBT                                                                                                                                                                                                                                                                              | 66                               |

|            | 4.9.3 The Regenerative Feedback Loop Gain.                                                                                                                                                                                                                                                                                     | 67                               |

|            | 4.9.4 Limitations of the Regenerative Feedback Model.                                                                                                                                                                                                                                                                          | 68                               |

| 4.1(       | ) Conclusions                                                                                                                                                                                                                                                                                                                  | 69                               |

|            | 5. Epitaxial Tunnel Oxide MISS Devices                                                                                                                                                                                                                                                                                         |                                  |

|            | 5. Epitaxiai Tuiniei Oxide MISS Devices                                                                                                                                                                                                                                                                                        |                                  |

| 5.1        | Introduction                                                                                                                                                                                                                                                                                                                   | 71                               |

| 5.1<br>5.2 | -                                                                                                                                                                                                                                                                                                                              | 71<br>72                         |

|            | Introduction                                                                                                                                                                                                                                                                                                                   |                                  |

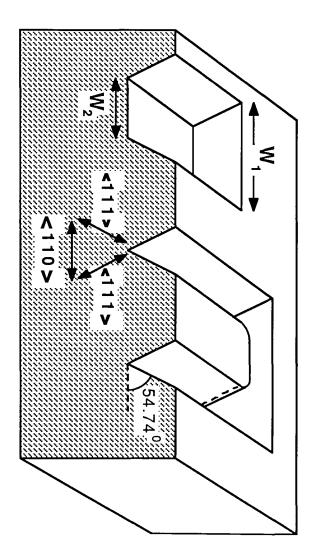

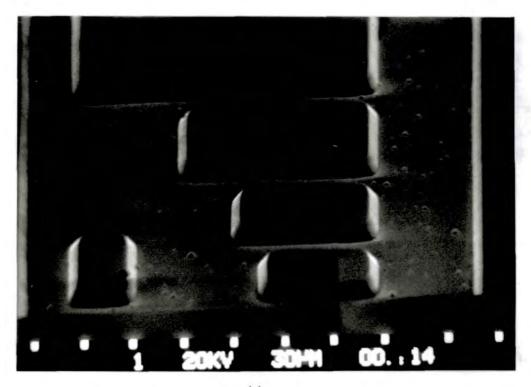

|            | Introduction<br>Etching of V-grooves in {100} Silicon                                                                                                                                                                                                                                                                          | 72                               |

|            | Introduction<br>Etching of V-grooves in {100} Silicon<br>5.2.1 Characterisation of the V-groove Etching Process                                                                                                                                                                                                                | 72<br>74                         |

|            | Introduction<br>Etching of V-grooves in {100} Silicon<br>5.2.1 Characterisation of the V-groove Etching Process<br>5.2.2 Measurement of Groove Depth                                                                                                                                                                           | 72<br>74<br>75                   |

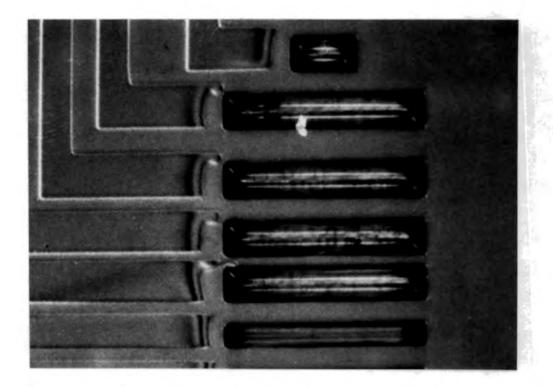

|            | Introduction<br>Etching of V-grooves in {100} Silicon<br>5.2.1 Characterisation of the V-groove Etching Process<br>5.2.2 Measurement of Groove Depth<br>5.2.3 Photolithography on a Grooved Topology.                                                                                                                          | 72<br>74<br>75<br>75             |

| 5.2        | Introduction<br>Etching of V-grooves in {100} Silicon<br>5.2.1 Characterisation of the V-groove Etching Process<br>5.2.2 Measurement of Groove Depth<br>5.2.3 Photolithography on a Grooved Topology.<br>5.2.4 Fabrication of Isolated Epitaxial MISS Devices                                                                  | 72<br>74<br>75<br>75<br>76       |

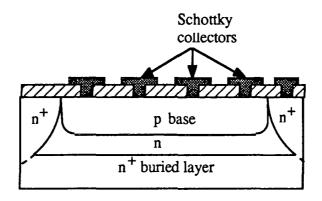

| 5.2        | Introduction<br>Etching of V-grooves in {100} Silicon<br>5.2.1 Characterisation of the V-groove Etching Process<br>5.2.2 Measurement of Groove Depth<br>5.2.3 Photolithography on a Grooved Topology.<br>5.2.4 Fabrication of Isolated Epitaxial MISS Devices<br>Switching Characteristics of Isolated Epitaxial MISS Devices. | 72<br>74<br>75<br>75<br>76<br>77 |

| 5.4 | Initial Forming of MISS Switching Characteristics.         | 80 |

|-----|------------------------------------------------------------|----|

|     | 5.4.1 Possible Causes of Forming                           | 81 |

|     | 5.4.2 Generation of Interface States in MIS Diodes         | 82 |

| 5.5 | Area Effects in the Isolated MISS.                         | 83 |

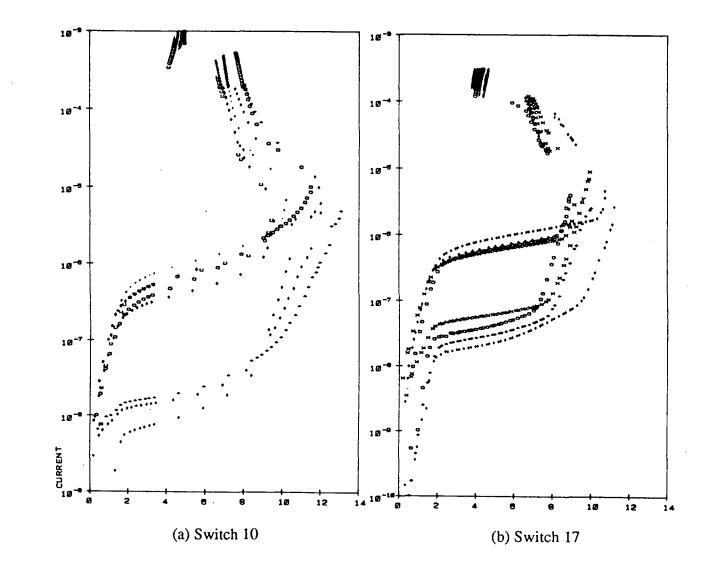

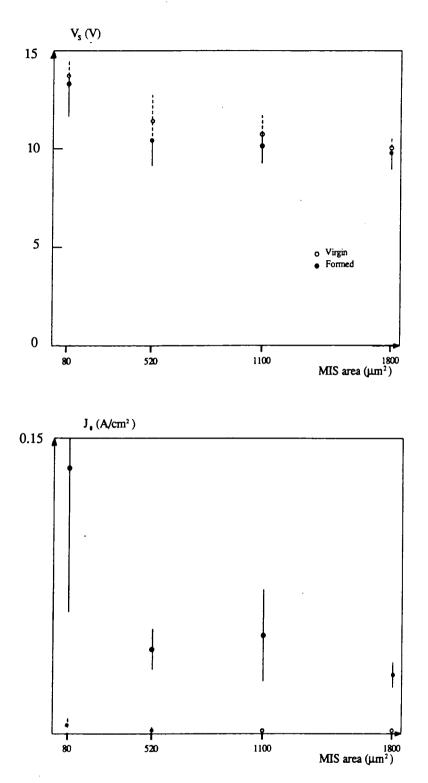

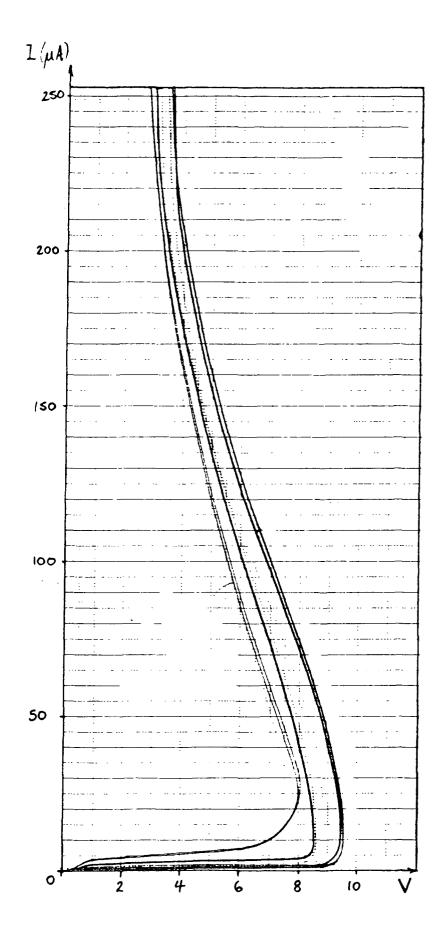

|     | 5.5.1 Measured Effects on Device Characteristics           | 83 |

|     | 5.5.2 Effects of Area on the Feedback Gain                 | 85 |

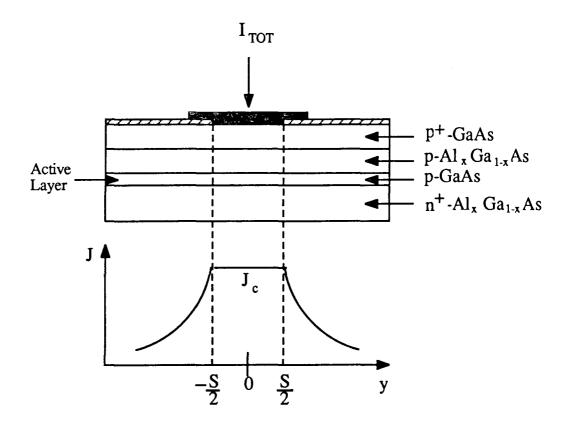

|     | 5.5.3 Current Spreading in the Stripe-Contact Laser        | 87 |

|     | 5.5.4 Current Spreading in Epitaxial MISS Devices          | 88 |

|     | 5.5.5 Evaluation of the Current Spreading in MISS Devices. | 89 |

|     | 5.5.6 The Spreading Length in 'Punch-Through' Mode Devices | 91 |

|     | 5.5.7 The MIS Aspect Ratio and Depletion Layer Spreading   | 93 |

| 5.6 | Conclusions                                                | 94 |

|     | 6. Deposition and Characterisation of Silicon Rich Oxide   |    |

| 6.1 | Introduction                                   | 97  |

|-----|------------------------------------------------|-----|

| 6.2 | Application of SRO in MISS Devices             | 97  |

| 6.3 | The Structure of $SiO_x$                       | 98  |

| 6.4 | Deposition of SRO                              | 99  |

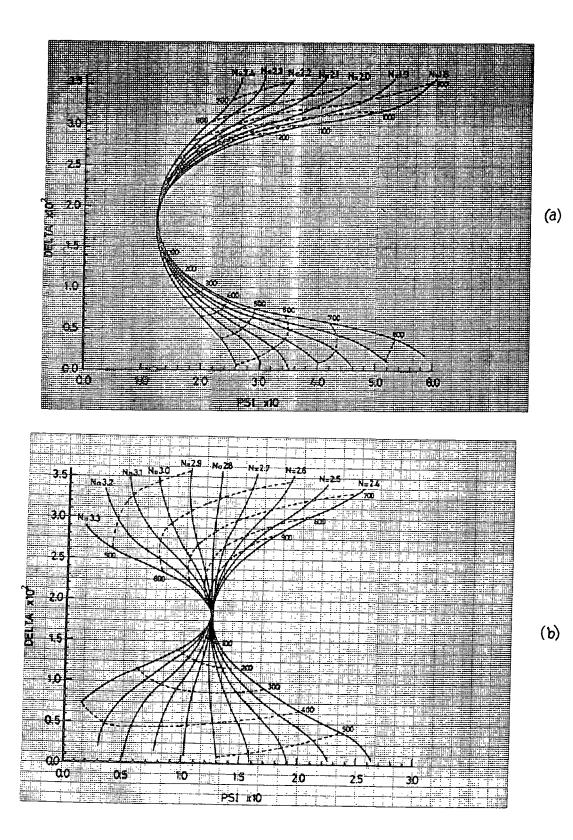

| 6.5 | Determination of SRO Thickness and Composition | 100 |

| 6.6 | Annealing of SRO films                         | 102 |

| 6.7 | Electrical Characterisation of SRO MIS Diodes  | 102 |

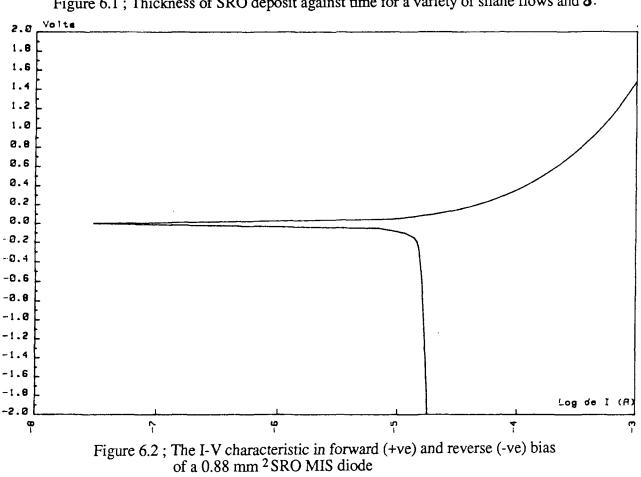

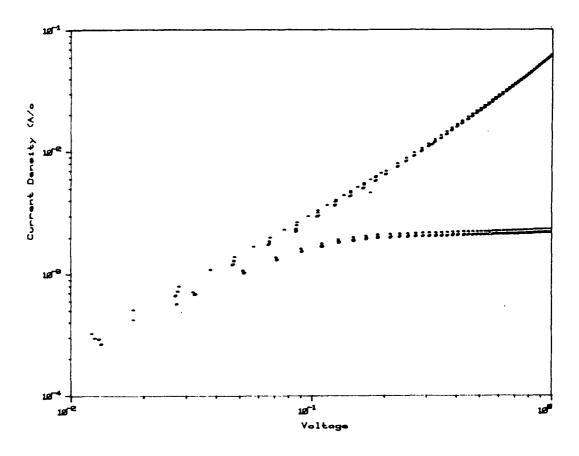

|     | 6.7.1 Current-Voltage Characteristics          | 102 |

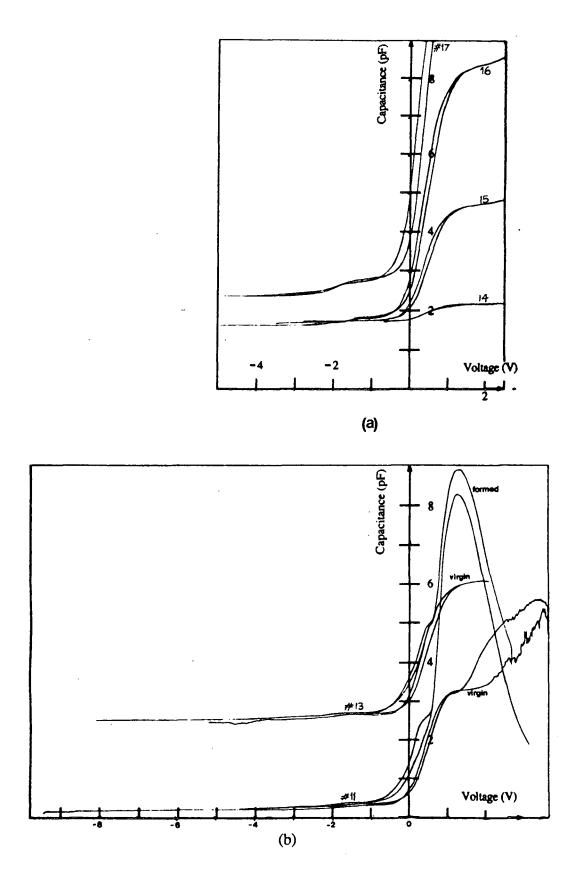

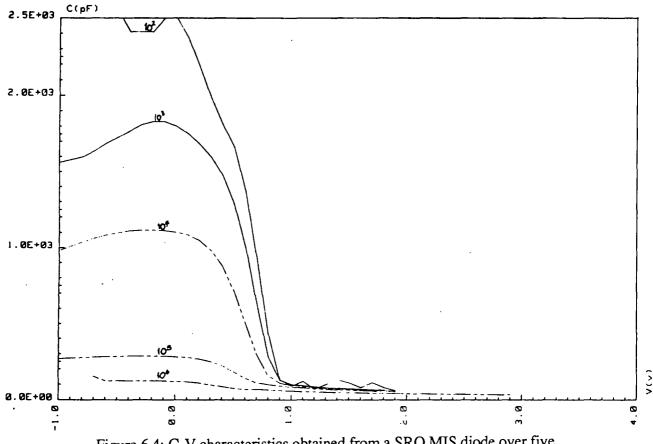

|     | 6.7.2 Capacitance-Voltage Characteristics      | 103 |

|     | 6.7.3 SRO MISS Devices                         | 103 |

# 7. Stable Negative Differential Resistance

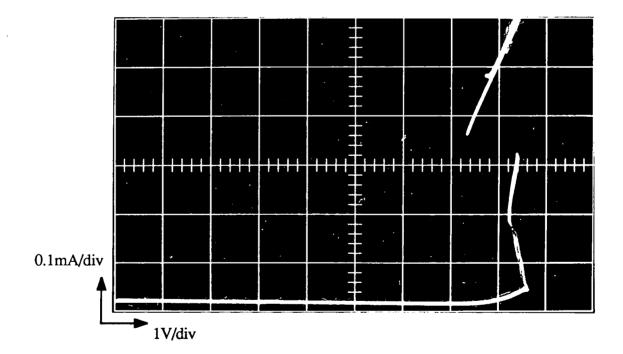

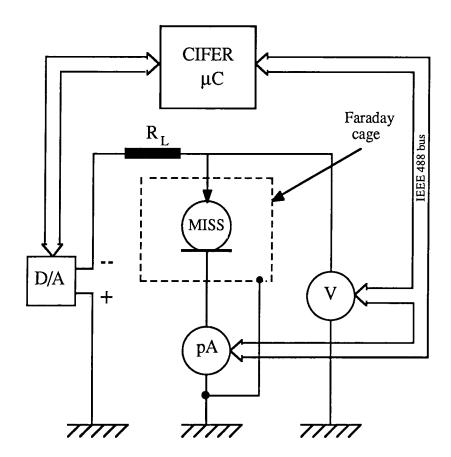

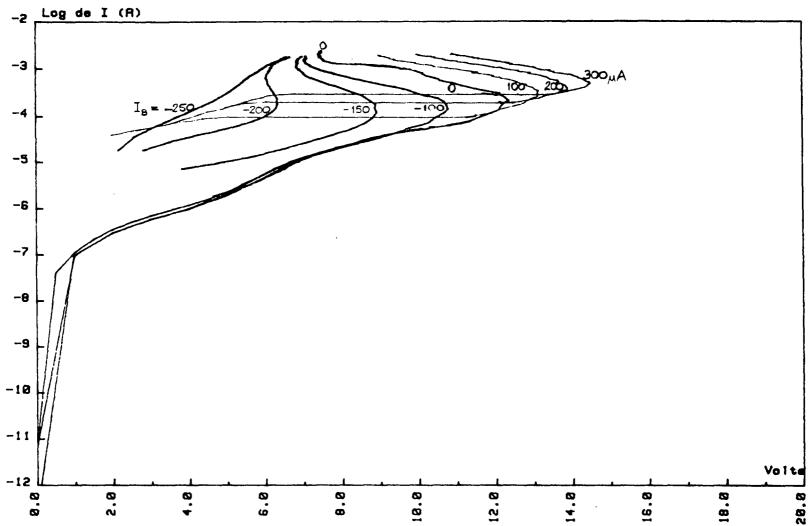

| 7.1 | Introduction; Large Area MISS Devices                          | 105       |

|-----|----------------------------------------------------------------|-----------|

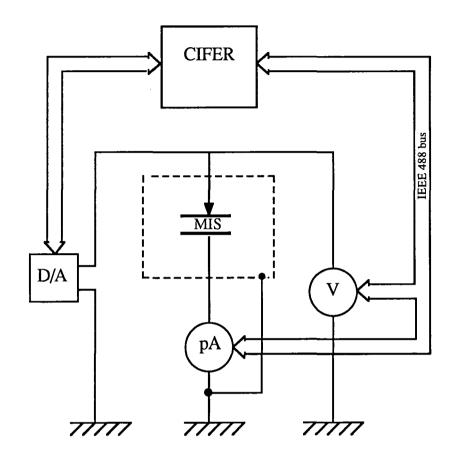

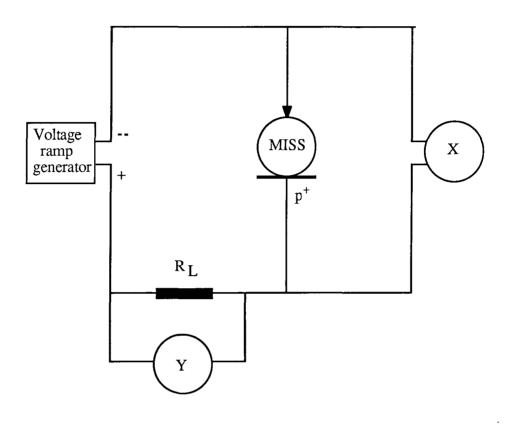

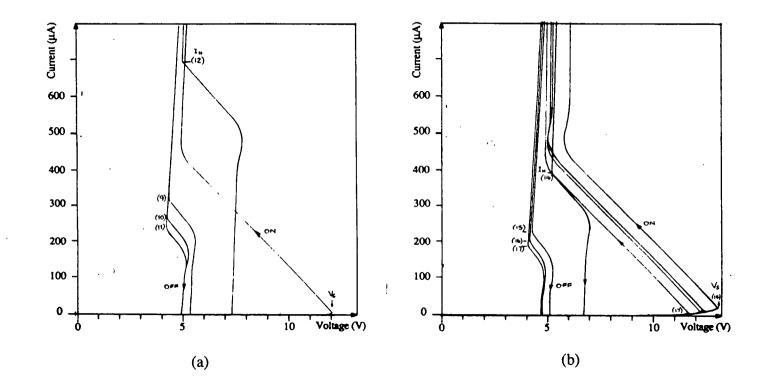

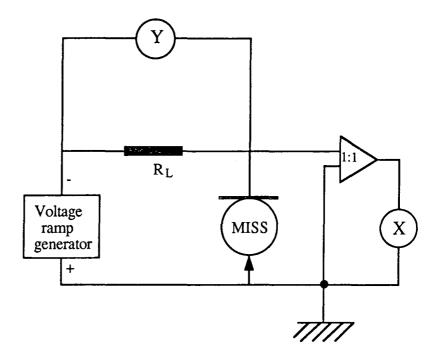

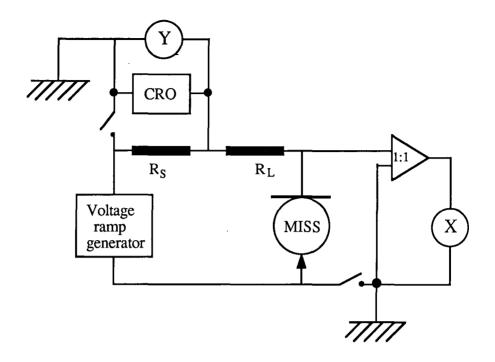

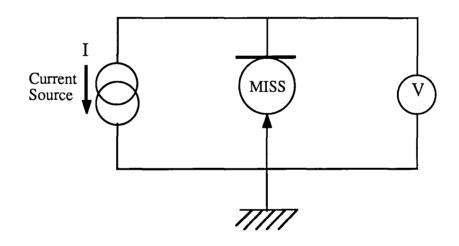

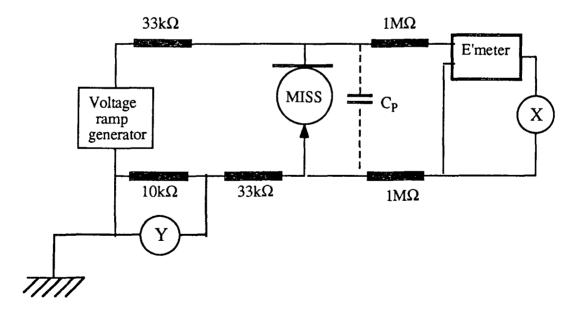

| 7.2 | Measurement of MISS Characteristics                            | 106       |

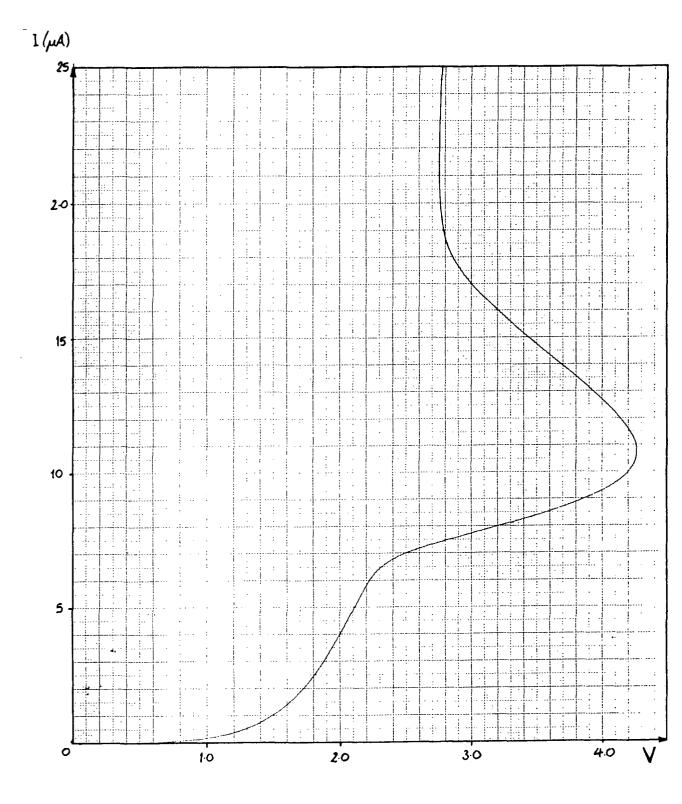

|     | 7.2.1 The First Observation of Stable Negative Differential Re | esistance |

|     |                                                                | 107       |

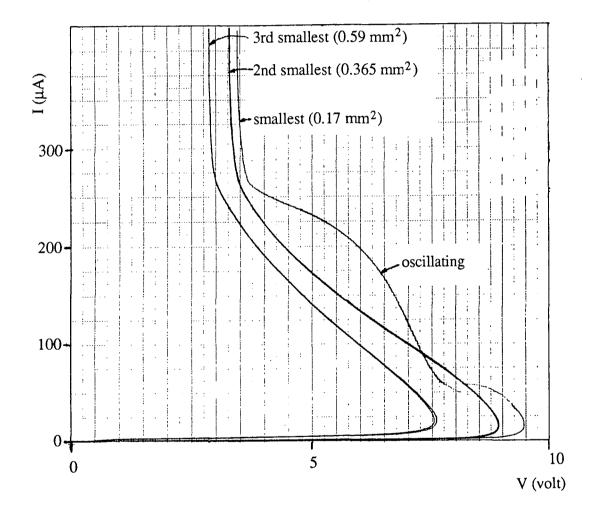

|     | 7.2.2 Stability and Device Dimensions                          | 108       |

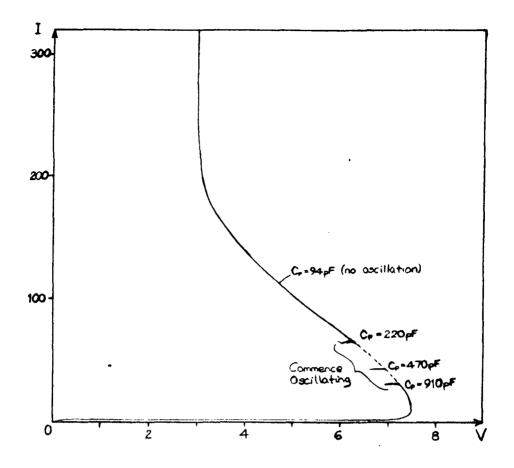

|     | 7.2.3 Detection of Oscillations using an Oscilloscope.         | 109       |

|     | 7.2.4 Use of a Constant Current Source                         | 109       |

|     | 7.2.5 The Effect of Capacitive Loading on NDR Stability        | 110       |

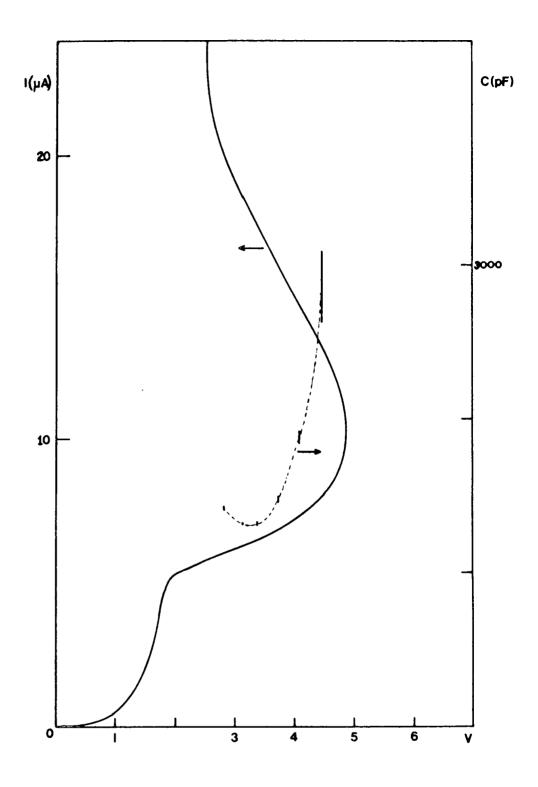

| 7.3 | Circuit Stability and the Concept of Negative Differential Cap | pacitance |

|     |                                                                | 111       |

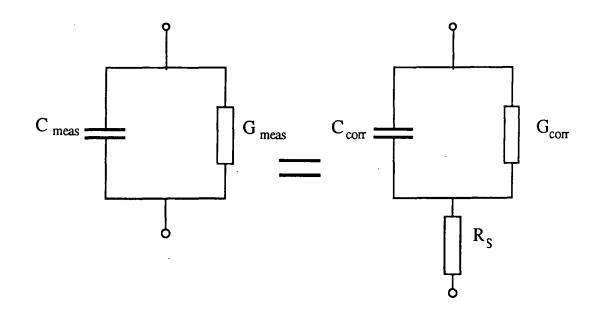

|     | 7.3.1 Measurement of Negative Differential Capacitance         | 114       |

| 7.4 | The Unstable State                                             | 115       |

|     | 7.4.1 Frequency of Oscillation                                 | 115       |

|     | 7.4.2 Oscillations in Small Area Devices                       | 116       |

|     | 7.4.3 Very Low Frequency Oscillations                          | 117       |

|     | 7.4.4 The Amplitude of Oscillation                             | 120       |

| 7.5 | Stable NDR and the Regenerative Feedback Mechanism             | 123       |

| 7.6 | The Condition for Stable NDR                                   | 124       |

| 7.7 | Conclusions                                                    | 125       |

# 8. Conclusions

| 8.1 | Negative Differential Capacitance                            | 128 |

|-----|--------------------------------------------------------------|-----|

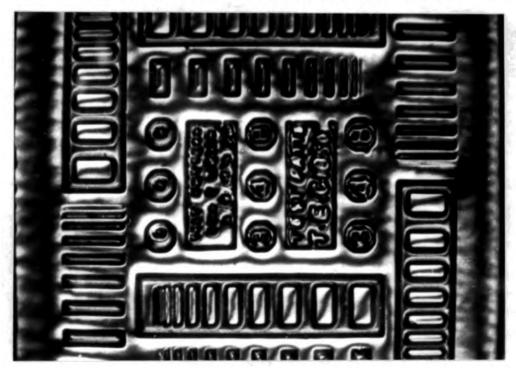

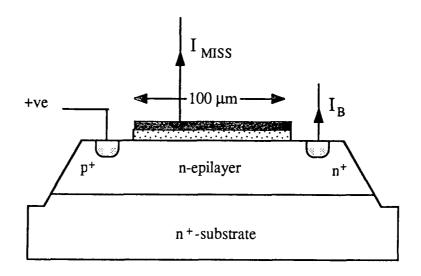

| 8.2 | Applications of the MISS in Microelectronics                 | 129 |

| 8.3 | Limitations of the Epitaxial MISS                            | 129 |

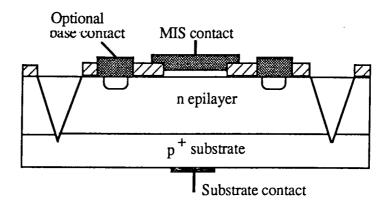

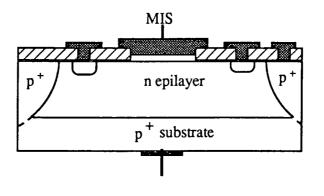

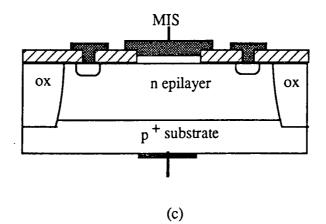

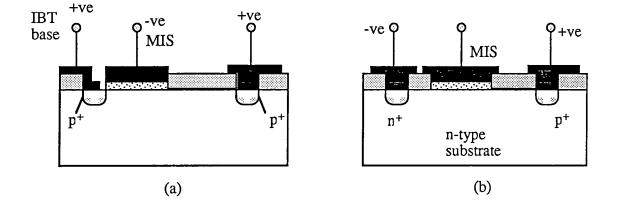

| 8.4 | Lateral Forms of the MISS Device                             | 130 |

|     | 8.4.1 <b>MISIM</b>                                           | 130 |

|     | 8.4.2 The Three-Terminal Lateral M-I-n-p <sup>+</sup> Switch | 131 |

| 8.5 | Future Trends in MISS Switches                               | 132 |

| Appendix A | 134 |

|------------|-----|

| Appendix B | 139 |

| Appendix C | 142 |

| Appendix D | 144 |

•

# CHAPTER ONE

# Introduction

## 1.1 Regenerative Switching Devices

The appearance of the first alloyed junction transistor in 1950 marked the beginning of the modern era of solid state electronics. For the first time, the function of amplification, which is fundamental to most electronic systems, could be achieved using a completely solid device. Transistors consequently superseded the bulky, unreliable and power-hungry vacuum tubes which had served for the previous 40 years. The new devices relied for their operation on the simultaneous transport of particles of both polarities (electrons and holes) through semiconducting material and were consequently termed 'bipolar'.

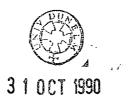

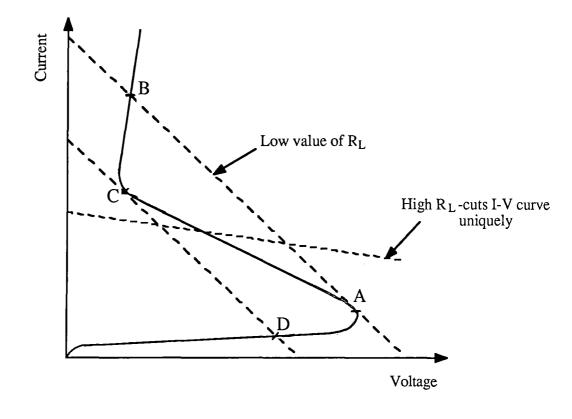

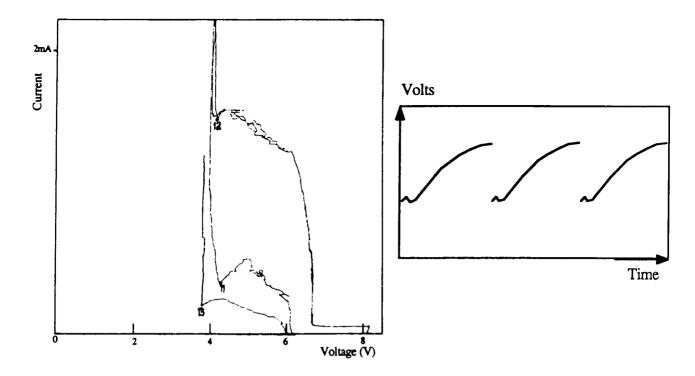

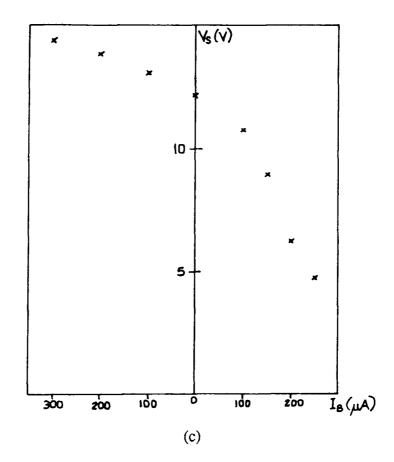

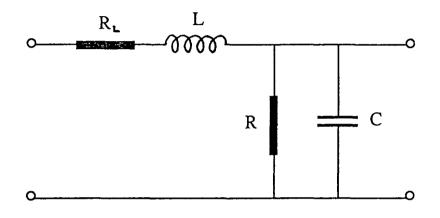

The arrival of the bipolar junction transistor (BJT) was followed very soon after, in 1952, by the Shockley diode (silicon controlled rectifier or thyristor). This four layer p-n-p-n structure brought the possibility of regenerative switching in the solid state and thus replaced the vacuum thyratron. Regenerative switching devices (RSDs) exhibit two stable states in their current-voltage characteristics due to the interaction of two amplifying mechanisms in the form of a feedback loop. A high impedance 'off'-state is separated from a low impedance 'on'-state by a zone of negative differential resistance (NDR) as shown in figure 1.1. The thyristor is therefore a solid state switch with memory; once switched on, the device remains in that state until its current supply is reduced below the holding current  $(I_H)$  indicated in the figure. Furthermore, the voltage at which the device switches  $(V_S)$  may be controlled by the application of a small 'gating' current through one of the intermediate layers in its p-n-p-n structure. The obvious application of such an effect is the control of the transmission of electrical power to a load such as a motor or light source and the principle market for thyristors is indeed power electronics. Although control of power has become very much the domain of the thyristor, its possible use as a digital memory device has not gone unnoticed. Any device with two stable conductive states is inherently capable of Boolean data retention. Moreover, the memory effect in an RSD is of a static nature. Once the

Figure 1.1; The 'S-type' or 'current-controlled' switching characteristic of a Regenerative Switching Device.

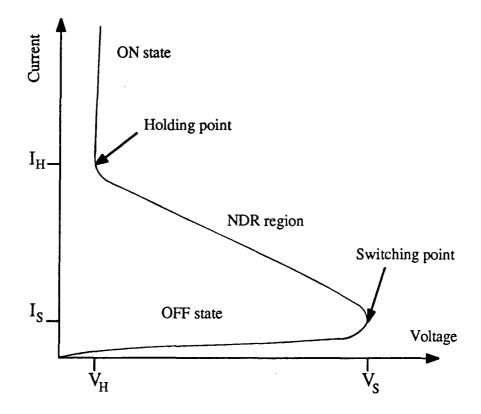

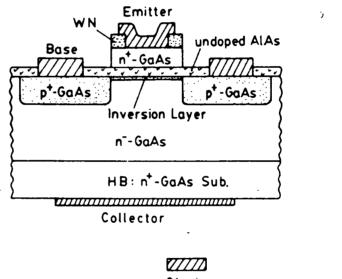

Figure 1.2; The basic structure of a conventional Metal-Insulator-Semiconductor Switch (MISS)

device is established in one or other of its conductive states, it remains in that state (assuming its electrical supply is maintained) without the need to be 'refreshed'. The lack of success of the thyristor as a memory device is in part due to its slow switching speed but perhaps of greater significance is the incompatibility of its four-layer structure with established integrated circuit fabrication techniques.

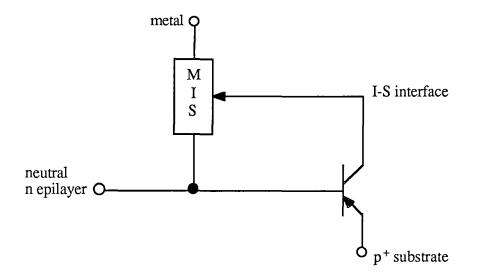

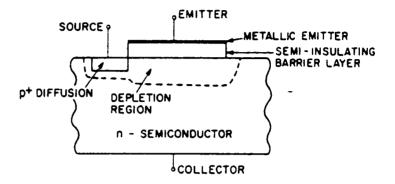

## 1.2 The MISS

Twenty years after the development of the thyristor, a new semiconductor device, of much simpler construction, was found to exhibit two states of conduction in the same manner as RSDs. Yamamoto and Morimoto<sup>[1]</sup>, found, quite by accident, that an epitaxial p-n junction on which they were working displayed a switching characteristic when under forward bias. They attributed this effect to the presence of a thin insulating layer between the top metal contact and the n-type layer. Subsequently the device became known as a 'Metal-Insulator-Semiconductor Switch' or MISS. The structure of a conventional MISS of this type is shown schematically in figure 1.2. At about that time, the discovery that a MIS junction might be capable of current amplification was also creating some interest.<sup>[2]</sup> However, it was not until four years later that it was suggested that the switching mechanism in the MISS was regenerative.<sup>[3]</sup>

The MISS was experimentally found to be much faster than the thyristor with turnon times of a few nS reported<sup>[3] [4]</sup>. In addition, the simplicity of its construction made it ideally suited to microelectronic applications. For instance, in semiconductor memory, a single MISS (with two MOS transistors for loading and addressing) could replace the six MOS transistors required to form a static random access memory (SRAM) cell<sup>[5]</sup> Operated in its 'unstable' NDR region by a simple biasing circuit, the MISS may behave as a relaxation oscillator<sup>[5]</sup> with potentially large dynamic range and very small geometry.<sup>[6]</sup> Also, being highly sensitive to illumination, it can be turned on by an optical pulse and thus shows promise as an optoelectronic switching device.<sup>[7]</sup>

Why then, it must be asked, does the MISS remain little more than the subject of scientific curiosity 17 years after its discovery?

In part it might be said that the reason is historical. The BJT and subsequently the Schockley diode were **developed** at Bell Labs between 1945-50 on the basis of sound semiconductor theory by a team who had as a specific goal the realisation of a solidstate amplifier. In contrast, the MISS was **discovered**, with the result that experiment preceded theory and has continued to do so ever since. Looking back to the late 70's it may be seen that theoretical progress was thwarted by the assertion of El-Badry and Simmons<sup>[8]</sup> that the interaction between the MIS and pn junctions was based on either punch through of their depletion regions or avalanching in the reverse biased MIS junction, both of which were well known first breakdown phenomena in BJTs. This tended to divert attention from the regenerative switching theories advanced the previous year.

Meanwhile, experimental development continued apace but without the guidance of a sound theoretical understanding. Kroger and Wegener<sup>[9]</sup>. reported successful use of a variety of semi-insulating layers;  $SiO_xN_y$  (15-60Å), amorphous Si (200-2000Å) polycrystalline Si (10<sup>3</sup>-10<sup>4</sup>Å) and amorphous Ge (40-400Å) as well as tunnelling thickness oxide,  $SiO_2$  (20-45Å) and of several MIS contact metals including chromium, aluminium and molybdenum. In addition, they found no basic assymetry in the I-V characteristics of the complimentary M-I-n-p and M-I-p-n structures nor did it appear to matter whether the pn junction was epitaxial or diffused. Thus, by 1978 the **generality** of the switching phenomenon had been established.

Since then, a large amount of experimental data, often conflicting, has accumulated but without a sound theory to explain it. More recently, concepts of gain and regenerative feedback have enjoyed something of a revival in a series of review papers<sup>[10-12]</sup>. Meanwhile, however, silicon MOS technology has continued to advance at a remarkable pace. The single transistor RAM cell was developed in 1976<sup>[13]</sup> and 1 Megabit memory chips are now feasible, obviating any benefits the MISS might have brought in 1972. Most other proposed functions of the MISS, such as in oscillators and charge-transfer type devices, may also now be performed with speed and efficiency by MOS transistor circuitry.

It is against this historical background that this work was embarked upon in 1983. Although by no means all the questions have been answered, it is hoped that this thesis, by means of informed theoretical and experimental enquiry, goes some way towards resolving the remaining confusion which surrounds the MISS and points the way to future developments.

## 1.3 Thesis Outline

In view of the stated generality of the switching phenomenon in MISS devices, it is intended to keep the discussion as general as possible. However, the use of tunnel oxide I-layers has been predominant in this, as in past studies. Tunnelling is perhaps the best understood of the possible mechanisms of conduction through insulating films and hence much of the theoretical discussion will concentrate on this MIS system. Despite this, it should hopefully remain apparent that the switching processes described do not depend on any particular conduction regime.

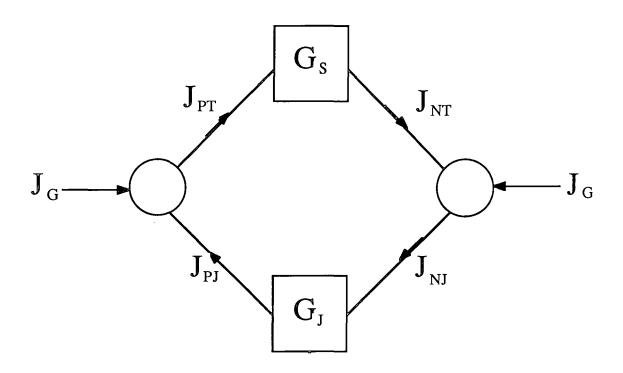

A first-order theoretical treatment of the MIS diode is given in chapter 2 followed by an experimental study of the tunnel oxide MIS. Chapter 4 then deals with the theoretical models of the MISS. Starting from a well established steady state description of the device, a more complete regenerative feedback model is proposed in which it is suggested that the MIS diode itself behaves as a bipolar transistor when switching occurs. This new approach conceptually brings the MISS into the fold of RSDs, alongside the thyristor and hopefully removes any remaining doubts about the nature of the switching mechanism.

In chapter 5, an experimental study of the epitaxial MISS is reported with a view to assessing the potential for scaling down the device for microelectronic applications. It is concluded that the epitaxial MISS is fundamentally unsuited to implementation in very large-scale integrated circuits and that tunnel oxide is unlikely to offer either reproducibility or stability in manufactured devices. An alternative semi-insulating material, silicon-rich oxide (SRO) is introduced in chapter 6. This material has already found widespread use in integrated circuits both as a passivation layer for high voltage bipolar I.C.s<sup>[14]</sup> and as a charge injection layer for electrically-alterable memories<sup>[15]</sup> but at the time of these studies, its application to MISS devices was novel.

Some remarkable experimental observations made in the course of assessing SRO layers for MISS devices are presented in chapter 7. Although these discoveries seem at first to conflict with the regenerative switching model previously espoused, the introduction of a new concept, negative differential capacitance, together with a consideration of frequency limitations of MISS devices lead to a successful resolution.

Finally, by way of a conclusion in chapter 8, new lateral forms of the device which are more efficient and more amenable to integration are proposed with the support of preliminary experimental results.

# REFERENCES

- 1. T.Yamamoto and M.Morimoto, Appl. Phys. Letters 20 2269 (1972)

- 2. R.A.Clarke and J.Shewchun, Solid State Electronics 14 957 (1971)

- T.Yamamoto, K.Kawamura and H.A.Shimizu, Solid State Electronics 19 701 (1976)

- 4. H.Kroger and H.A.R.Wegener, Solid State Electronics 21 655 (1978)

- 5. J.G.Simmons and A.El-Badry, The Radio and Electronic Engineer 48 215 (1978)

- A.G.Nassibian, R.B.Calligaro and J.G.Simmons, Solid State Electronics 22 149 (1978)

- 7. A.El-Badry and J.G.Simmons, Solid State Electronics 20 963 (1977)

- 8. H.Kroger and H.A.R.Wegener, Solid State Electronics 21 643 (1978)

- 9. I.Zólomy, Solid State Electronics 28 537 (1985)

- 10. K.Board, Phys. Rev. D: Appl. Phys 12 1595 (1985)

- 11. J.G.Simmons and G.W.Taylor, Solid State Electronics 29 287 (1986)

- C.N.Ahlquist, J.R.Breivogel, J.L.McCollum, W.G.Oldham and A.L.Renninger, IEEE J. Solid-State Ccts SC-11 570 (1976)

- T.Matsushita, N.Oh-uchi, H.Hayashi and H.Yamoto, Appl. Phys. Letters 35 549 (1979)

- 14. D.J.DiMaria and D.W.Dong, J. Appl. Phys. 51 2722 (1980)

# CHAPTER TWO

# Theory of the Non-Equilibrium MIS Diode

### 2.1 Introduction

Several variants of the MIS switching device have been reported, as discussed in the introduction to this thesis. A feature common to all these structures is the reverse biased MIS diode where the 'I' represents some form of thin semi-insulating layer. When the I-layer is sufficiently conductive, communication becomes possible between the sea of electrons up to the Fermi level in the metal and the conduction and valence bands in the semiconductor. Net fluxes of electrons and holes therefore become possible when the device is under bias and the concentration of minority carriers in the MIS depletion layer may depart from its thermal equilibrium value. It will become clear that it is this ability of the MIS diode to depart from thermodynamic equilibrium which forms the basis of the switching phenomenon in MISS devices. For tunnelling-thickness oxide layers the transition from equilibrium to 'disequilibrium' behaviour occurs for thicknesses below about 60Å, at which quantum mechanical tunnelling becomes significant. Polysilicon, SIPOS, SRO and  $SnO_x$  are examples of materials that exhibit sizeable conduction and thus provide for non-equilibrium MIS diodes with I-layer thicknesses in the range 200 to 2000Å. In order to appreciate the importance of deviations from thermodynamic equilibrium, an equilibrium MIS diode with a non-transparent insulating layer (a MIS capacitor) will first be considered.

# 2.2 Equilibrium MIS Diodes

Silicon dioxide layers thicker than a few hundred Ångstroms present an almost infinite impedance to current flow and are fundamental to gate control in MOS transistors (MOST). Due to the immense importance of the MOST to the world microelectronics industry, the metal-oxide-semiconductor structure has become perhaps the most widely researched and technologically developed of all solid state devices.

## 2.2.1 The MIS Diode Under Zero Bias.

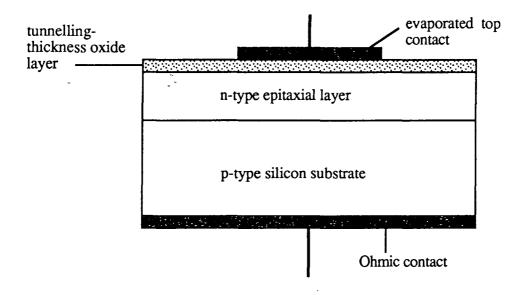

The energy band diagram of a MIS diode with a non-conductive I-layer (not necessarily oxide) and n-type semiconductor is shown in figure 2.1. In general, at zero bias the bands in the semiconductor will not be flat, figure 2.1(a), due to the combination of metal-semiconductor work function difference and the electrostatic effect of charges existing both at the insulator-semiconductor (I-S) interface and within the insulator itself.

The situation can be described by;

$$V_{FB} = \phi_m - \phi_S - \frac{Q_{ss}}{C_{ins}} - \frac{1}{C_{ins}} \int_{0}^{d_{ins}} \rho.dx$$

(2.1)

where  $V_{FB}$  is the voltage required to establish the flat band condition shown in figure 2.1(b).  $\phi_m$  and  $\phi_s$  are the metal and semiconductor work functions,  $Q_{ss}$  the density of interface trapped charge and  $\rho$  the bulk density of trapped charge in the oxide.

### 2.2.2 MIS Diodes Under Reverse Bias.

A MIS diode may be considered to b under reverse bias when a potential difference is applied across its terminals in the sense which causes repulsion of majority carriers from the semiconductor surface. As such, a negative bias would have to be applied to the metal of a M-I-Si(n) structure to achieve this condition.

The effect of a reverse bias is then to deplete the semiconductor surface of majority carriers, leaving a space charge layer of uncompensated donor ions as shown in figure 2.1(c). As a consequence, the semiconductor bands are bent in this region by an amount  $\psi(x)$  which is given by Poissons equation;

$$\frac{\delta^2 \psi(x)}{\delta x^2} = -\frac{\rho(x)}{\epsilon_s \epsilon_o} = -\frac{q}{\epsilon_s \epsilon_o} \left( N_D^+ + p(x) - n(x) \right)$$

(2.2)

Here,  $N_D^+$  is the concentration of fixed, positively charged ionised donors in the depleted region which, at room temperature, may be considered as simply equal to the doping concentration,  $N_D$ . p(x) and n(x) represent the volume densities of free holes and electrons as functions of distance in the depletion layer. As the I-layer prevents any

Figure 2.1; Band diagram of a MIS(n) diode under conditions of (a) Zero bias, (b) Flat bands and (c) Reverse bias.

steady state current flow, the carriers remain in thermal equilibrium with the lattice. Their quasi Fermi levels thus remain equal and identical to the Fermi level of the neutral n-type bulk,  $E_{Fn}$ , which lies flat throughout the surface depletion region. In such a case, the electron and hole densities in the depletion layer are given respectively by;

$$n(x) = n_i \cdot \exp\left(\frac{E_{Fn} - E_i(x)}{kT}\right) = N_D \cdot \exp\left(\frac{\psi(x)}{V_T}\right)$$

(2.3)

$$p(x) = n_i \cdot \exp\left(\frac{E_i(x) - E_{Fn}}{kT}\right) = \frac{n_i^2}{N_D} \cdot \exp\left(\frac{-\psi(x)}{V_T}\right)$$

(2.4)

where  $\psi(x)$  is negative and  $V_T \equiv kT/q \approx 25 \text{mV}$  at room temperature.

In n-type material at room temperature,  $n_i^2/N_D \ll N_D$  such that, prior to the onset of surface inversion,  $p(x) \ll N_D$ . Also, for values of  $\psi(x) > 3.V_T$ ,  $n(x) \to 0$  which allows expression (2.2) to be simplified to;

$$\frac{\partial^2 \psi(x)}{\partial x^2} = -\frac{q}{\epsilon_s \cdot \epsilon_o} N_D \tag{2.5}$$

This corresponds to the so-called 'depletion approximation' in which the distribution of ionised donors is assumed to be a step-function, their density falling abruptly to zero at the depletion edge defined as  $x = W_S$ .

The total potential across the MIS structure,  $V_{MIS}$ , is the sum of the drops across the insulator and surface depletion region plus the correction for the flat band voltage;

$$V_{MIS} = \psi_S + V_{ins} + V_{FB} \tag{2.6}$$

$\psi_S$  is defined as the surface potential and represents the total band bending at the semiconductor surface. It can be obtained by integration of (2.5), taking as boundary conditions the limits  $\psi(0) = \psi_S$  and  $\psi(W_S) = 0$ ;

$$\psi_S = \frac{q}{2.\epsilon_s.\epsilon_o} N_D W_S^2 \tag{2.7}$$

$V_{ins}$ , the voltage dropped across the insulator, is related to the field at the semiconductor surface,  $\mathcal{E}_s$ , by the so-called 'charge neutrality equation' which is an expression of

continuity of the displacement vector at the I-S interface;

$$\epsilon_{ins}.\epsilon_o.\frac{V_{ins}}{d_{ins}} = \epsilon_s.\epsilon_o.\mathcal{E}_s - Q_{ss}$$

(2.8)

An approximate expression for the surface field,  $\mathcal{E}_s$ , is derived in Appendix B. In the absence of any inversion charge, this becomes simply;

$$\mathcal{E}_{s} = -\left(\frac{2kT.N_{D}}{\epsilon_{s}\epsilon_{o}}\right)^{1/2} \cdot \left(\frac{\psi_{S}}{V_{T}}\right)^{1/2}$$

(2.9)

for a MIS diode in depletion.

### 2.2.3 Inversion in MIS Diodes.

As the applied potential across a reverse biased MIS diode is raised,  $\psi_S$  will increase and the depletion region will continue to extend until the onset of strong inversion. This is considered to occur when the concentration of minority carriers at the semiconductor surface becomes equal to the majority carrier concentration in the bulk. Thus, substituting  $p(0) = n_{n0} = N_D$  into (2.4);

$$\psi_S(\text{strong inversion}) = V_T \cdot \ln\left(\frac{N_D^2}{n_i^2}\right) = \frac{2}{q} \cdot (E_{Fn} - E_i) = 2.\phi_{Fn}$$

(2.10)

The presence of an inversion layer at the surface prevents any further growth of the depletion layer thickness with increasing reverse potential. In inversion, any increase in oxide field is satisfied by an increase in the inversion layer charge, p(0) rather than in the number of exposed donor ions. Thus the surface potential reaches a maximum;

$$\psi_{max} = \psi_S(\text{strong inversion}) = 2.\phi_{Fn} \tag{2.11}$$

and the second term becomes important in the expression for the surface field from Appendix B;

$$\mathcal{E}_{s}(\text{inversion}) = -\left(\frac{2kT.N_{D}}{\epsilon_{s}\epsilon_{o}}\right)^{1/2} \cdot \left(\frac{\psi_{max}}{V_{T}} + \frac{p(0)}{N_{V}}\right)^{1/2}$$

(2.12)

In conclusion then, for an equilibrium MIS diode;

(i) No net currents flow and the carriers remain in thermal equilibrium with the semiconductor.

(ii)In the steady state, the semiconductor surface becomes inverted when the applied bias is sufficient to give rise to a surface potential equal to  $2\phi_{Fn}$ .

(ii)  $V_{ins}$ ,  $\psi_S$  and p(0) are related through the charge neutrality condition.

### 2.3 The Non-Equilibrium MIS Diode

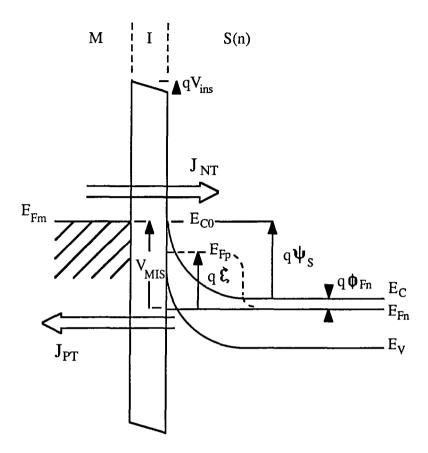

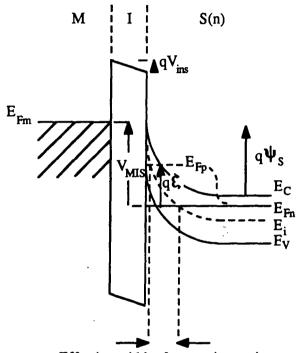

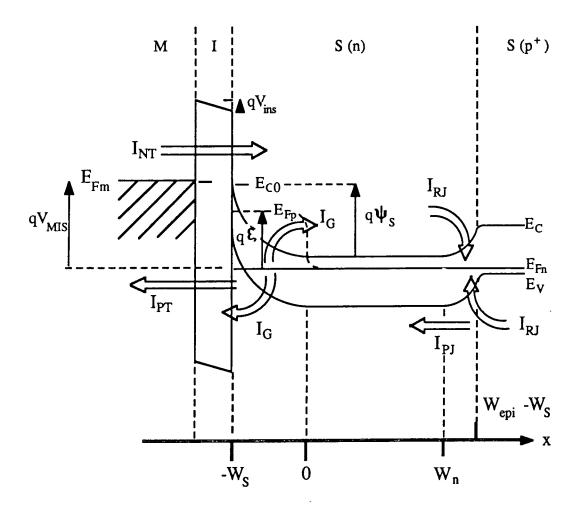

When the insulating layer in a MIS structure is sufficiently conductive, passage of electrons between the semiconductor and the metal becomes possible and net currents may flow. In the case of a tunnelling thickness oxide on silicon, figure 2.2, electrons making a tunnel transition between the metal and the semiconductor conduction band constitute an electron tunnel current,  $J_{NT}$  while those tunnelling into the valence band are equivalent to a hole current,  $J_{PT}$  in the reverse direction. It is also possible for electrons to tunnel in either direction between the metal and bound states at the I-S interface. This flux will constitute a net hole or electron current,  $J_{ST}$ , depending on the type and energy of the interface states and on the position of the metal Fermi level. Equivalent currents to  $J_{PT}$ ,  $J_{NT}$  and  $J_{ST}$  also pass through silicon-rich oxide, the other semi-insulating material of interest in this thesis. Before describing the relevant conduction theories, the electrostatic consequences of leakage through the insulator will first be considered.

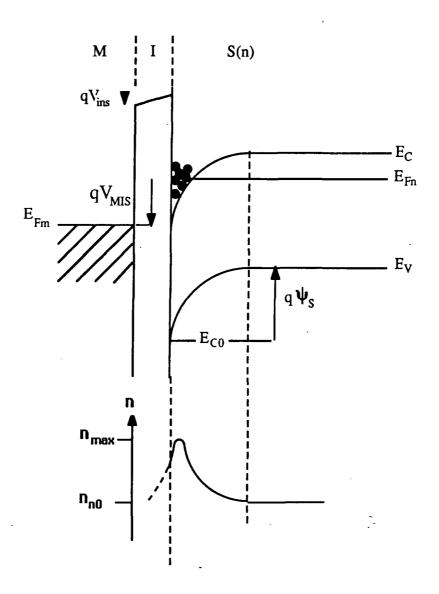

#### 2.3.1 Disequilibrium In Reverse Bias.

In a MIS(n) diode, leakage of holes through the insulating layer will cause the hole density in the depletion layer, as given by (2.4), to fall below its thermal equilibrium value<sup>[1]</sup>. As such, the quasi Fermi level,  $E_{Fp}$ , which describes the hole density will become separated from the bulk Fermi level  $E_{Fn}$  in the depletion layer. The amount of splitting of the Fermi levels, defined as  $\xi = (E_{Fp} - E_{Fn})$  (figure 2.2) is thus a measure of the degree of thermodynamic disequilibrium in this region and is sometimes referred to as the 'disequilibrium potential'<sup>[2]</sup>.

Figure 2.2; Band diagram of a deeply-depleted non-equilibrium MIS(n) diode, showing the band-to-band electron and hole tunnel currents.

The carrier concentrations in the depletion layer become;

$$n(x) = n_i \cdot \exp\left(\frac{E_{Fn} - E_i(x)}{kT}\right) = N_D \cdot \exp\left(\frac{-\psi(x)}{V_T}\right)$$

(2.13)

$$p(x) = n_i \cdot \exp\left(\frac{E_i(x) - E_{Fp}}{kT}\right) = \frac{n_i^2}{N_D} \cdot \exp\left(\frac{\psi(x) - \xi}{V_T}\right)$$

(2.14)

The magnitude of  $\xi$  will be a function of the detailed balance between the rates of supply of holes to and from the depletion region. For a MIS diode in isolation, the main sources of holes are thermal and optical generation in the depletion layer. As such the hole current may be termed 'semiconductor limited'. The contribution from the neutral semiconductor bulk will consist of only those holes generated within a diffusion length of the depletion edge ( $x = W_S$ ) which are collected by the surface field before they recombine.

However, any source of extra hole current will alter the detailed balance existing at the MIS junction and, if sufficiently large, may force the condition at the semiconductor surface closer to thermal equilibrium. For example, a MIS(n) diode biased into deep depletion in the dark may be strongly influenced by illumination. This can increase the supply of holes to the surface by generation of carriers in the depletion region and potentially give rise to a degree of surface inversion with a consequent contraction of the depletion region.

Departure from thermal equilibrium allows the reverse biassed MIS to enter a deeply depleted state where  $\psi_s$  exceeds the limit normally set by strong inversion, (2.10). Assuming the supply of minority carriers remains limited, the depletion region is able to extend further into the neutral region as the reverse bias is increased. In this case, the growth is eventually limited by either;

(i) breakdown of the insulating layer at high field as, from (2.8),  $\mathcal{E}_s$  and hence  $V_{ins}$  will also be increasing;

(ii) where  $N_D$  exceeds about  $10^{16}$  cm<sup>-3</sup>, avalanching in the high depletion field near the surface or;

(iii) where  $N_D$  exceeds about  $10^{18}$  cm<sup>-3</sup>, band-to-band tunneling (Zener breakdown) due to the high surface field.

Condition (ii) in fact corresponds to the switching condition in bistable MIS diodes which have been reported by Hayashi<sup>[3]</sup> and Lai et. al.<sup>[4]</sup>.

# 2.4 Generation in the Surface Depletion Layer

In the absence of injection of minority carriers by any other means, the minority current flow in a MIS diode will be principally controlled by generation of holes in the surface depletion region. Generation and recombination occur via traps in semiconductors and both mechanisms are favoured for traps lying at mid-gap, such that their energy  $E_t = E_i$ . In neutral material in equilibrium, the rate of generation is identical to the rate of recombination. However, where a field exists such as in a depletion region, generated carriers are swept away before they can recombine and a net generation current arises.

From classical Schockley-Read-Hall (SRH) statistics the rate of recombination/ generation is given by;

$$U_{GR} = \frac{1}{\tau_{GR}} \cdot \frac{p.n - n_i^2}{p + n + 2n_i}$$

(2.15)

Here  $\tau_{GR}$  is the recombination lifetime defined as  $\tau_{GR} = (\sigma . v_{th} . N_t)^{-1}$  where  $\sigma$  is the capture cross section of the traps,  $v_{th}$  the thermal velocity and  $N_t$  the trap concentration. The generation current  $I_G$ , is in general obtained by the integration;

$$I_G = q. \int_0^\infty U.dx \tag{2.16}$$

Assuming the generation process occurs uniformly throughout the depletion region, a simple solution for  $I_G$  is then;

$$I_G = \frac{q.n_i.W_S}{2.\tau_{GR}} \tag{2.17}$$

However, it has been pointed out<sup>[2]</sup> that since the recombination process is greatest for traps located at mid-gap, it is probably more realistic to consider only those traps with energy  $E_t = E_i$ . Thus, in a deeply depleted non-equilibrium MIS diode, nearly all the generation will occur in the zone where  $E_i$  lies between  $E_{Fn}$  and  $E_{Fp}$ , as shown in figure 2.3. As a consequence,  $I_G$  should only be evaluated between these limits;

$$I_G = q \cdot \int_{\chi_n}^{\chi_n + \xi} U \cdot \frac{dx}{d\psi} \cdot d\psi$$

(2.18)

where  $\chi_n = E_g/2q - \phi_{Fn}$ . This integral has been solved<sup>[2]</sup> to obtain an approximate

Effective width of generation region.

Figure 2.3; The effective width of the generation region in the surface depletion layer which is a function of the degree of disequilibrium, as represented by  $\xi$ .

expression;

$$I_G = q \cdot \frac{n_i \cdot L_D}{\tau_{GR}} \cdot \frac{1 - \exp(-\xi/V_T)}{1 + \exp(-\xi/2V_T)} \cdot \left[ min\left(\frac{\psi_S}{V_T} - 1, \frac{\chi_n}{V_T} + \frac{\xi}{V_T} - 1\right)^{1/2} - \left(\frac{\chi_n}{V_T} - 1 - \ln 2\right)^{1/2} \right]$$

(2.19)

where *min* implies the minimum of the two arguments applies.

As a consequence, the generation current will in general be less than would arise if the generation process was occurring uniformly throughout the depletion region, as given by expression (2.17).

## 2.5 Tunnelling Currents Through Thin Oxides.

### 2.5.1 Introduction.

Initial studies of the nature of tunnelling in metal-tunnel oxide-semiconductor diodes were undertaken in the early seventies<sup>[5-8]</sup> when there was some interest in the current multiplication effect such junctions may provide. It was appreciated early in the development of the theory that tunnelling between the metal and interface states could not be neglected in relation to direct tunnelling to the semiconductor bands<sup>[5]</sup>. The first order theory to be presented here is essentially that of Green and Shewchun<sup>[5]</sup> and is subject to a number of approximations;

(i) The energy barrier presented by the thin oxide is considered to be trapezoidal, as represented in figure 2.2. Image force effects<sup>[9]</sup> and non-abrupt interfaces, which tend to reduce the barrier height at the edges by rounding the sharp changes in potential, are neglected.

(ii) The tunnelling probability is assumed to be independent of the field in the insulator and thus of the shape of the barrier. In most theoretical works, it is ascribed a constant value corresponding to that of an ideal rectangular barrier with zero field.

(iii) Electrons tunnel independently so there is no interaction between their wavefunctions.

(iv) The WKB approximation for the tunnelling transmission coefficient is invoked.

(v) Reflections of electrons at the insulator-semiconductor and insulator-metal interfaces are neglected.

#### 2.5.2. Electron Tunnel Current.

The net flux of electrons from the metal to the semiconductor conduction band, as derived by Green and Shewchun<sup>[5]</sup>, consists of the forward flux,  $J_{m\to c}$ , less that in the reverse sense,  $J_{c\to m}$  giving;

$$I_{NT} = A_e \cdot T^2 \cdot \exp(-\chi_e^{1/2} \cdot d_{ins}) \cdot \left[ F_1\left(\frac{E_{Fn} - E_{C0}}{kT}\right) - F_1\left(\frac{E_{Fm} - E_{C0}}{kT}\right) \right]$$

(2.20)

where

$$A_e = q \cdot \frac{m_{te} \cdot k^2}{2 \cdot \pi^2 \cdot \hbar^3} \tag{2.21}$$

is the Richardson constant for electrons with  $m_{te}$ , the effective electron mass transverse to the insulator barrier.  $F_1$  are Fermi-Dirac integrals of order one and may be approximated by exponentials<sup>[5]</sup> if the argument is negative

$$i.e.F_1(x) \rightarrow \exp(x) \quad \forall a < 0.$$

The term  $\exp(-\chi_e^{1/2}.d_{ins})$  represents the tunnel transition probability where  $(\chi_e^{1/2}.d_{ins})$  is the tunnel attenuation factor in which  $\chi_e$  represents the nominal barrier height faced by the electrons.

From the band diagram, figure 2.2, it can be seen that  $(E_{Fn} - E_{C0}) = -q.(\psi_S + \phi_{Fn})$ and  $(E_{Fm} - E_{C0}) = q(V_{MIS} - V_{FB} - \psi_S - \phi_{Fn})$ . Consequently, the expression for the electron tunnel current becomes;

$$I_{NT} = -I_{NT_0} \left[ \exp \left( \frac{\psi_S + \phi_{Fn}}{V_T} \right) - \exp \left( \frac{\psi_S + \phi_{Fn} - V_{MIS} + V_{FB}}{V_T} \right) \right]$$

(2.22)

where  $I_{NT_0} = A_e . T^2 . \exp(-\chi_e^{1/2} . d_{ins})$ .

In the case of reasonably large reverse bias, such that  $\psi_s \gg V_T$ , the first exponential term may be neglected. Then, substituting for  $V_{MIS}$  from (2.6),  $I_{NT}$  may be approximated by;

$$I_{NT}(\text{rev}) = -I_{NT_0} \cdot \exp\left(\frac{V_{ins} - \phi_{Fn}}{V_T}\right)$$

(2.23)

The majority carrier current in reverse bias is thus principally a function of the insulator potential drop  $V_{ins}$  which is given by equation (2.8).

Under a forward bias  $V_{fwd}$  however, the second term in (2.22) may be neglected for  $V_{fwd} > 3.V_T$  and the electron current becomes, in terms of the various device potentials;<sup>[6]</sup>

$$I_{NT}(\text{fwd}) = -I_{NT_o} \cdot \exp\left(\frac{\psi_s + \phi_{Fn}}{V_T}\right)$$

(2.24)

For the purpose of converting this expression into an empirical diode equation, Card and Rhoderick<sup>[6]</sup> introduce the thermionic, or Schottky barrier, potential  $\phi_{Bn} = \psi_s^0 + \phi_{Fn}$ , where  $\psi_s^0$  is the surface potential under zero bias, such that;

$$\psi_s + \phi_{Fn} = \psi_s^0 + \Delta \psi_s + \phi_{Fn} = \phi_{Bn} + \Delta \psi_s \tag{2.25}$$

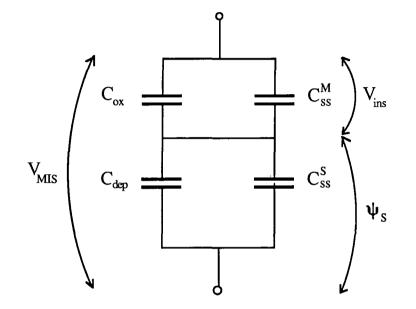

They also define an ideality factor n which allows the change in surface potential,  $\Delta \psi_s$ , to be expressed in terms of the total applied potential;

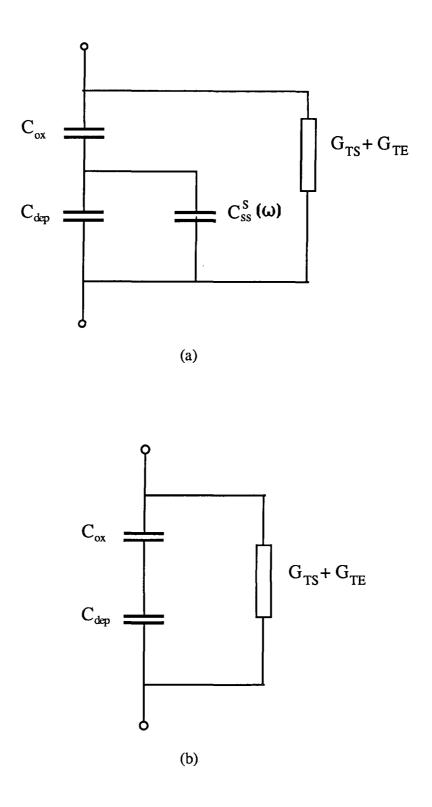

$$n = \left[\frac{\Delta\psi_s}{V_{fwd}}\right]^{-1} = \left[1 + \frac{C_{dep} + C_{ss}^S}{C_{ox} + C_{ss}^M}\right]$$

(2.26)

Here,  $C_{dep}$  and  $C_{ox}$  are respectively the depletion layer and oxide capacitances and  $C_{ss}^{M} = q.N_{ss}^{M}$  and  $C_{ss}^{S} = q.N_{ss}^{S}$  are the interface state capacitances corresponding to states in equilibrium with the metal (M) and semiconductor conduction band (S). This relation for n may be determined from the equivalent circuit for the MIS diode shown in figure 2.4. Equation (2.24) may then be reduced to;<sup>[6]</sup>

$$I_{NT}(\text{fwd}) = -I_{NT_0} \cdot \exp\left(\frac{-\phi_{Bn} + V_{fwd}/n}{V_T}\right)$$

(2.27)

### 2.5.3. Hole Tunnel Current.

The expression for the hole tunnel current is similarly composed of two terms;

$$I_{PT} = A_h \cdot T^2 \cdot \exp(-\chi_h^{1/2} \cdot d_{ins} \cdot \left[ F_1 \left( \frac{E_{V0} - E_{Fp}}{kT} \right) - F_1 \left( \frac{E_{V0} - E_{Fm}}{kT} \right) \right]$$

(2.28)

where  $A_h$  is the Richardson constant for holes, given by an equivalent expression to (2.21).

Figure 2.4; Small-signal equivalent circuit of the tunnelling MIS diode showing the partition of the potential across the device.

Noting that the hole concentration at the silicon surface is given by the expression  $p(0) = N_V \exp[(E_{V0} - E_{Fp})/kT]$ , where  $N_V$  is the density of states in the valence band, (2.28) may be stated alternatively as;

$$I_{PT} = I_{PT_0} \cdot \frac{p(0)}{N_V} \cdot \left[ 1 - \left( \frac{E_{Fp} - E_{Fm}}{kT} \right) \right]$$

(2.29)

where  $I_{PT_0} = A_h \cdot T^2 \cdot \exp -\chi_h^{1/2} \cdot d_{ins}$  As such, the minority carrier current under reverse bias is dependent on the equilibrium concentration of minority carriers at the surface which is in turn a function of the disequilibrium at the surface represented by  $\xi$ . The latter is determined by the detailed balance between the rates of their supply to and removal from the surface as discussed in section 2.3.1.

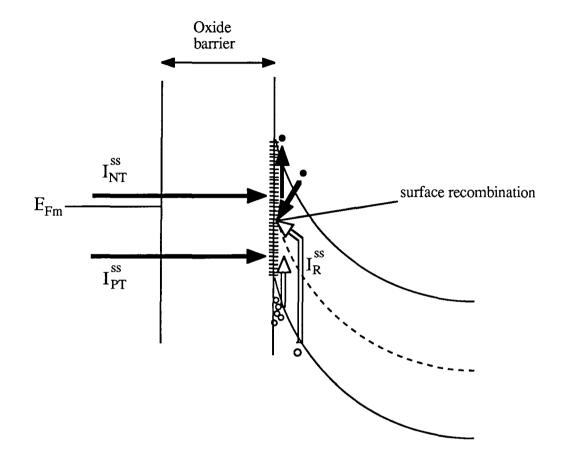

### 2.5.4. Tunnelling Via Surface States.

The electrostatic effect of surface state charge on the band bending in the MIS system has already been discussed in section 2.2.1. Surface states also play a part in charge transfer within the device through two mechanisms which are represented diagramatically in figure 2.5;

(i) They provide a spatially concentrated region of recombination-generation centres which contribute to the total current without involving a tunnel transition.

(ii) They can allow tunnelling transitions between the metal and the semiconductor which constitute a current in parallel with the band-to-band tunnel currents  $I_{NT}$  and  $I_{PT}$ .

Surface states are categorised as donor or acceptor type depending on whether they are associated with electron or hole trapping. In general, they are characterised by thermal capture cross sections  $\sigma_e$  and  $\sigma_h$  for electrons and holes respectively and by the distribution of their density  $N_{ss}(E)$  within the semiconductor energy gap. An electron in a donor trap may tunnel to an empty state in the metal above the Fermi level or an electron may tunnel out of the Fermi sea in the metal and recombine with a hole in an acceptor state. These tunnelling transitions will have associated probabilities,  $P_T^{ss}$ .

$\sigma_e$  and  $\sigma_h$  may take a range of values depending on the oxide thickness and technological parameters such as crystal orientation, surface preparation prior to oxidation

Figure 2.5; Charge transfer mechanisms via the interface involving surface states.

and the type of metal used. They do appear however, to be independent of the surface state energy  $^{[10]}$ .

Although the distribution of  $N_{ss}$  is continuous, characteristic peaks which appear to be related to the metal used for the top contact have been reported by some workers<sup>[11]</sup> The magnitude of  $N_{ss}$  also depends largely on technological parameters and is found to decrease rapidly with increasing insulator thickness. The latter observation may be interpreted as further evidence that metal diffusion from the top contact does indeed make a contribution.

For the purpose of modelling the process of tunnelling via traps, certain generalisations may be made. For instance, practical MIS diodes are found experimentally to exhibit strong peaks in  $N_{ss}$  near the conduction and valence band edges. As such, it is reasonable to treat the distribution as two discrete peaks close to  $E_C$  and  $E_V$  which correspond to donor and acceptor states respectively.

The tunnelling probability for the traps,  $P_T^{ss}$ , may be expressed empirically as;

$$P_T^{ss} \approx P_0 \cdot \exp(-\chi^{1/2} \cdot d_{ins})$$

(2.30)

in which Lundström and Svensson<sup>[12]</sup> have calculated a value of  $10^{13} sec^{-1}$  for the preexponential factor  $P_0$ .

If  $f_t$  and  $f_m$  are respectively the occupation functions of a surface state at an energy  $E_t$  and in the metal at the same energy, then the tunnel current may be given<sup>[13]</sup> as;

$$I_{ss} = q N_{ss} P_T^{ss} \int_{E_1}^{E_2} (f_t - f_m) dE_t$$

(2.31)

$f_t$  takes the following forms<sup>[13]</sup>, depending on whether the traps are donors or acceptors;

$$f_t(\text{donor}) = \frac{\sigma_e.v_{th}.n(0) + P_T^{ss}.f_m}{\sigma_e.v_{th}.(n(0) + n_1) + P_T^{ss}}$$

(2.32)

$$f_t(\text{acceptor}) = \frac{\sigma_h . v_{th} . p(0) + P_T^{ss} . f_m}{\sigma_h . v_{th} . (p(0) + p_1) + P_T^{ss}}$$

(2.33)

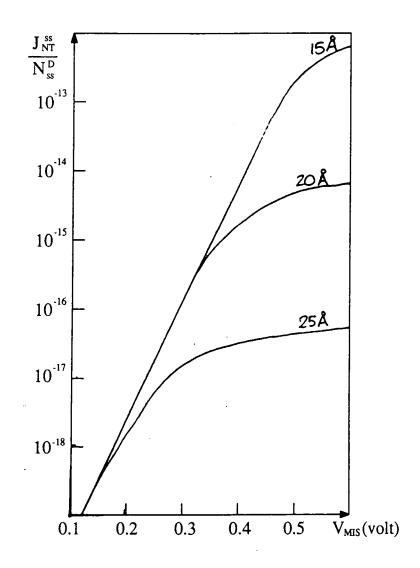

The surface carrier concentrations, n(0) and p(0) are given by (2.14) and (2.13) for x = 0and  $n_1$  and  $p_1$  are the concentrations when the corresponding quasi Fermi levels are at the trap energies  $E_t$ . Sarrabayrouse et. al.<sup>[14]</sup> have solved the set of equations (2.30) to (2.33) for both donor and acceptor traps. Figure 2.6 after reference [14] shows  $I_{NT}^{ss} = I_{ss}$  (electrons) normalised to  $N_{ss}^D = N_{ss}$  (donors) for three values of oxide thickness. The saturated regions of the curves correspond to a tunnel-limited regime where the donor traps are in equilibrium with the semiconductor. In this regime, the current is only slightly affected by the applied bias but it is exponentially dependent on the insulator thickness. Before the tunnel-limited regime is reached, the current flow via donor states is limited by thermal excitation to the semiconductor conduction band and takes the form<sup>[14]</sup>;

$$I_{ss}(\text{electrons}) = I_{\text{NT}}^{\text{ss}} = I_{\text{NT}_0}^{\text{ss}} \cdot \exp\left(\frac{E_{\text{Fn}} - E_{\text{C0}}}{kT}\right) \cdot \left[\exp\left(\frac{V_{\text{MIS}}}{kT}\right) - 1\right]$$

(2.34)

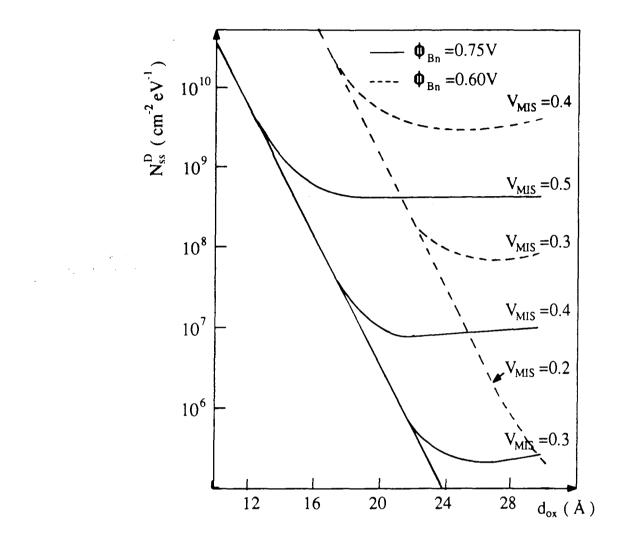

As such, the surface state-assisted current can not be distinguished from the band-toband current given by equation (2.22). The same authors also show that the magnitude of the surface state current will in general exceed the band to band current for realistic surface state densities. Figure 2.7 shows the required value of  $N_{ss}$ (donor) for  $I_{NT}^{ss} > I_{NT}$ .

A similar result is obtained for the hole current via acceptor traps where again it is shown that  $I_{PT}^{ss} > I_{PT}$  for reasonable values of  $N_{ss}$ (acceptor).

#### 2.6 Conclusions

It has been shown that where the insulating layer in a MIS structure is slightly conductive, minority carriers are able to escape from the semiconductor to the metal when the diode is reverse biased. Thus, whereas the surface of an insulating MIS diode becomes inverted when the surface potential reaches a value of  $2\phi_{Fn}$ , the surface of a leaky diode need not invert and its depletion region may continue to extend as the reverse bias is increased. This condition of deep depletion corresponds to a departure from thermodynamic equilibrium at the surface which is represented by a splitting of the majority and minority carrier quasi-Fermi levels. The density of minority carriers in the depletion region is then determined by their rates of supply from the semiconductor and loss to the metal. A return towards equilibrium at the surface, corresponding to the growth of an inversion layer, may be brought about if the flux of minority carriers to the surface is enhanced by some means. It has been noted in this chapter that such an increase in hole flux may result from avalanche multiplication when the field in the surface depletion region is high. It will be shown in chapter 4 that a forward biased pn

Figure 2.6; The ratio of trap-assisted tunnel current to interface state density calculated as a function of the applied forward bias across a MIS diode for several values of oxide thickness (after reference 14).

Figure 2.7; Calculated values of interface state density required for trap-assisted tunnelling to exceed band-to-band tunnelling assuming a capture cross-section,  $\sigma_n = 10^{-16} \text{ cm}^2$  (after reference 14).

junction in close proximity to the MIS may be a highly effective source of hole flux and that this combination forms the basis of the MISS device.

Although a first order theory of tunnelling through very thin silica layers has been outlined in this chapter, the precise nature of the conduction mechanism through the insulating layer is not critical to the non-equilibrium behaviour of the MIS diode. In chapter 6 of this thesis, an alternative semi-insulator, 'silicon rich oxide' will be introduced and shown to exhibit essentially the same characteristics. What the particular choice of insulator will affect, however, is the exact relationship between the majority and minority carrier currents and the field in the insulating layer. As a final point, it has been noted that the influence of interface states on the passage of carriers between the semiconductor and the metal may not be neglected.

## REFERENCES

- 1. R.A.Clarke and J.Shewchun, Solid State Electronics 14 957 (1971)

- A.C.F.Fiore de Mattos, These d'Etat No.1158, Universite Paul Sabatier, Toulouse, France (1984)

- 3. Y.Hayashi, Appl. Phys. Letters 37 407 (1980)

- S.K.Lai, P.V.Dressendorfer, T.P.Ma and R.C.Barker, Appl. Phys. Letters 38 41 (1981)

- 5. M.A.Green and J.Shewchun, Solid State Electronics 17 349 (1974)

- 6. H.C.Card and F.M.Rhoderick, J.Phys.D; Apll. Phys. 4 1589 (1971)

- 7. S.Kar and W.E.Dahlke, Solid State Electronics 15 221 (1972)

- 8. M.A.Green, F.D.King and J.Shewchun, Solid State Electronics 17 (1974)

- 9. A.Tugulea and D.Dascalu, J. Appl. Phys. 56 2823 (1984)

- 10. S.Kar and W.E.Dahlke, Solid State Electronics 15 221 (1972)

- 11. S.Kar and W.E.Dahlke, Appl. Phys. Letters 18 401 (1971)

- 12. I.Lundström and C.Svensson, J. Appl. Phys. 43 (1972)

- 13. L.B.Freeman and W.E.Dahlke, Solid State Electronics 13 483 (1970)

- 14. G.Sarrabayrouse, J.Buxo and D.Esteve, phys. stat. sol. (a) 46 185 (1978)

# CHAPTER THREE

# Fabrication and Characterisation of Tunnel Oxide MIS Diodes

#### 3.1 Introduction

In the introductory chapter, it was noted that switching has been observed in MISS devices incorporating a great variety of semi-insulating films. By far the most widely investigated of these has been tunnelling-thickness oxide grown by thermal oxidation. In fact, the MISS represents only a minor example of the technological importance of tunnel oxides in a range of applications. For example, metal tunnel-oxide silicon solar cells provide very high energy conversion efficiency, exceeding  $24\%^{[1]}$  and bipolar transistors with MIS emitters exhibit the highest current gain yet achieved, of the order of 25,000<sup>[2]</sup>. EEPROM static memory transistors which incorporate tunnelling oxides as a means of injecting and removing charge from a floating gate, are of great commercial significance.

The importance of tunnel oxides can be seen to have arisen from a combination of historical and technological factors. Early research in MIS diodes grew out of an interest in the effects of the interfacial oxide which normally exists in Schottky barriers formed on silicon and can provide current gain. In parallel with a growing interest in tunnelling films, the technology and scaling of MOS transistors to sub-micron dimensions is requiring that gate oxides be used with thicknesses of the order of 100Å.

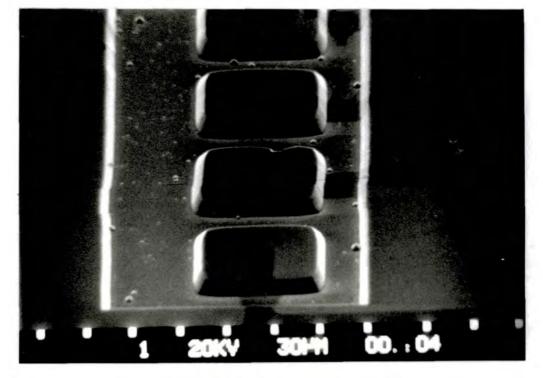

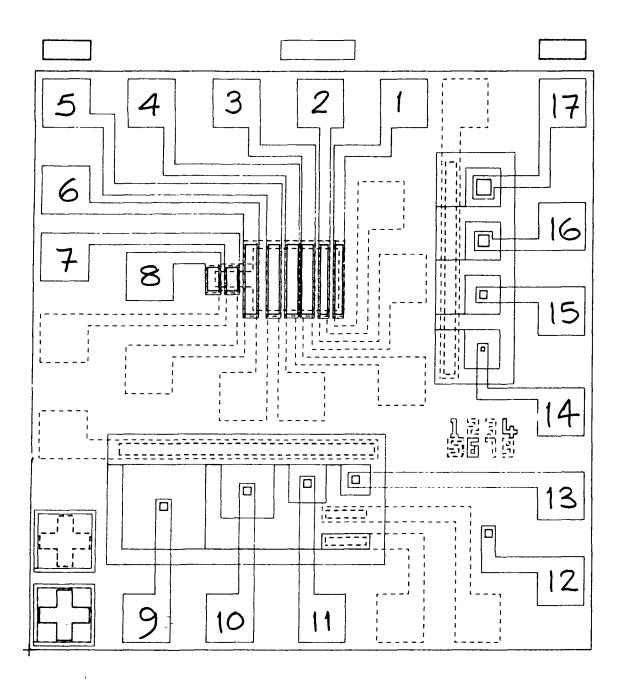

The majority of studies of tunnel oxide MIS diodes have been concerned with aluminium - thermally grown SiO<sub>2</sub> - silicon structures, perhaps because the technologies are readily available. The choice of Al as the top contact metal, although by no means scientifically justified, is also made in the present work. All the tunnel oxide MIS diodes and most of the MISS switching devices reported in this thesis are of quite small dimensions  $(10 \times 10 \mu \text{m} \text{ to } 30 \times 180 \mu \text{m})$  and have been prepared using a mask set designed and fabricated for this purpose by the author. Device 'active areas' are defined in a layer of thick (0.5 to 1.0  $\mu$ m) oxide by photolithography and wet etching. Subsequent to tunnel oxide growth, aluminium is evaporated and top contacts and associated tracks and bond pads are defined. Before describing in some detail the process used for the fabrication of such devices, some consideration is given to the nature of thin oxides and their growth mechanism.

## 3.2 MIS diodes with tunneling thickness SiO<sub>2</sub>

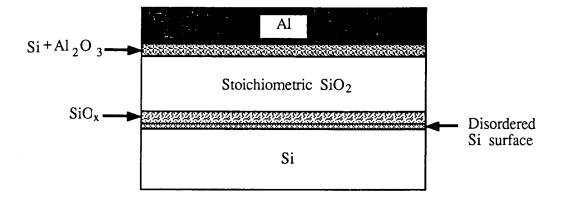

Despite their apparent simplicity, metal- tunnel oxide - silicon structures may be considered to comprise at least six different regions, only three of which may be considered as 'bulk' metal, stoichiometric  $SiO_2$  and silicon. These six regions are represented in figure 3.1 for an Al-SiO<sub>2</sub> diode and may be briefly summarised as follows;

## 3.2.1. Aluminium Top Contact

An important characteristic of the contact metal is its work function which is a factor in determining the potential barrier faced by tunnelling electrons.

## 3.2.2. The Aluminium-Oxide Interface

Good adhesion between a metal and  $SiO_2$  normally implies that some form of chemical reaction<sup>[3]</sup> between the two has occurred. For this reason, gold, which is not reactive with  $SiO_2$  at normal deposition temperatures, is a notably poor adherent to  $SiO_2$ . In contrast, at an aluminium-oxide interface, the following solid state reaction takes place<sup>[3]</sup> ;

$$4.\mathrm{Al} + 3.\mathrm{SiO}_2 \Longrightarrow 2.\mathrm{Al}_2\mathrm{O}_3 + 3.\mathrm{Si} \tag{3.1}$$

providing a chemical bond which makes aluminium a good material to use for interconnect metallisation on integrated circuits. Auger electron analysis (AES)<sup>[5]</sup> and X-ray photoelectron spectroscopy (XPS)<sup>[4]</sup> studies of this interface have confirmed the presence of Al<sub>2</sub>O<sub>3</sub> and free Si precipitates for room temperature deposited films. In the case of tunnel oxides however there is cause for concern because by means of this reaction, Al is able to penetrate a substantial distance into the SiO<sub>2</sub><sup>[3]</sup>. Furthermore the penetration of Al<sub>2</sub>O<sub>3</sub> has been observed to increase with time, even at room temperature and to extend to a depth of 100Åor more into the SiO<sub>2</sub> layer when annealed at between 300-400°C<sup>[6]</sup> One consequence of the formation of an Al<sub>2</sub>O<sub>3</sub> layer is a reduction in the work function difference,  $\phi_{ms}$  of about 0.15eV<sup>[3]</sup> but obviously in the case of tunnel thickness oxides, a more important result could be the complete conversion of the SiO<sub>2</sub> into a mixed layer of Al<sub>2</sub>O<sub>3</sub> and Si.

### 3.2.3. Stoichiometric $SiO_2$

Assuming that the aluminium does not penetrate completely through the oxide layer, a layer of stoichiometric SiO<sub>2</sub> will remain. This layer is considered theoretically to present a potential barrier through which electrons must tunnel and the height of this barrier is assumed to be equivalent to that of bulk SiO<sub>2</sub>. However, oxide layers grown at low temperatures have been shown by EerNisse<sup>(7)</sup> to be under considerable biaxial compressive stress, of the order of 7.10<sup>8</sup> Pascal. Irene et. al.<sup>(8)</sup> have accounted for the build up of strain on the basis of the low viscosity of the SiO<sub>2</sub> during growth. At temperatures below about 900°C the viscosity of the growing oxide layer is too great for the 120% increase in free volume required by the transition from crystalline Si to amorphous SiO<sub>2</sub> to be accomodated by flow. As a consequence, oxide layers grown in the temperature range 600-800°C are found to be substantially denser than fully relaxed SiO<sub>2</sub> as well as containing a high level of residual strain<sup>(8)</sup>. The increased density results in a higher measured value of refractive index (1.48 at 600°C and 1.475 at 700°C) than is expected at more normal growth temperatures (1.462 at 1000°C).

Although it has been shown that the strain may be relaxed by subsequent annealing, this process is very slow at temperatures below 900°C unless  $H_2O$  is present.<sup>[8]</sup> Thus the tunnel oxides in the present work, which were grown in a dry ambient at around 750°C, must be expected to remain in a strained condition. Under these circumstances, it would seem likely that other physical properties of the oxide layer, such as its effective bandgap, will also be modified.

In conclusion it is unlikely that even the stoichiometric component of the MIS 'substructure' is treated realistically in the tunnelling model of Chapter Two.

## 3.2.4. The Oxide-Silicon Interface

In general, this interface is characterised by a transition region between the Si and the stoichiometric  $SiO_2$  and by the presence of traps at or near the interface.

There is some disagreement as to the extent of the transition layer which has an intermediate composition,  $SiO_x$  where 0 < x < 2. Although it is theoretically possible for amorphous  $SiO_2$  to terminate on Si within one bond length<sup>[9]</sup>, experimental investigations have revealed a non-stoichiometric layer of between 5 and 25Ådepending on the technique used. Thus in the case of tunnel oxides, there is some concern that the transition layer may constitute the greater part of the whole oxide layer<sup>[10]</sup>

Evidence for a relatively abrupt interface has been obtained by Feldman<sup>[11]</sup> using He backscattering and Krivanek et. al.<sup>[12]</sup> using high resolution transmission electron microscopy (HRTEM) both of whom report a transition within about 5Å of the interface. Also, diStefano<sup>[13]</sup> using field-dependent internal photoemission spectroscopy found insignificant (0.15%) distortion of the oxide conduction band beyond 4Å of the interface, implying that non-stoichiometry is negligible at this distance. Importantly, Krivanek<sup>[12]</sup> observed with HRTEM both short and long range modulation of the silicon surface. Monatomic steps (3.2Å high on {111} and 1.4Å on {100} surfaces) were seen every 20-40Åas well as more pronounced undulations 3-10Åin height with a period of 200-600Å.

It is significant that most of the evidence for a broad transition region has been gained using ESCA  $(20\text{\AA})^{[14]}$  and Auger surface analysis with depth profiling  $(28\text{\AA})^{[15]}$ Both of these techniques average the composition both in-plane and normal to the interface due to the wide beam and the sputtering action used and may thus misinterpret an undulating interface as being non-stoichiometric<sup>[15]</sup>.

Roughening of the SiO<sub>2</sub>-Si interface has since been correlated with an increase in the density of dangling bonds represented by Si<sup>+3</sup> or Si<sub>3</sub>  $\equiv$  Si· which are thought to be the main cause of interface states in the SiO<sub>2</sub> - Si system<sup>[16]</sup>. Annealing in N<sub>2</sub> at 1050°C has been shown to reduce surface roughness very considerably<sup>[17]</sup> and to improve the electrical breakdown properties of the oxide. Dressendorfer et. al. also demonstrated that an anneal in N<sub>2</sub> at 825°C subsequent to a 10 min oxidation at the same temperature reduced the interface state density N<sub>ss</sub> by a factor of 2 to 3. They also showed that a post-metallization anneal in 10:90 H<sub>2</sub>:N<sub>2</sub> forming gas further reduced N<sub>ss</sub> by a similar factor.

Diffusion of metal from the top contact has also been found to give rise to interface states in MOS systems where the oxide is tunnelling thickness. Kar and Dahlke<sup>[18]</sup> detected peaks in the interface state distribution characteristic of the particular metals used. This link has not always been corroborated by other workers however.

## 3.2.5. The Silicon Surface

In addition to complexities of strain and non-stoichiometry in the oxide transition layer, disorder has been detected in the surface of the silicon itself. Using He backscattering, Sigmon et. al.<sup>[19]</sup> found evidence that Si atoms are displaced from their surface

Figure 3.1; Section through an Al-SiO<sub>2</sub>-Si MIS diode indicating the various regions discussed in the text.

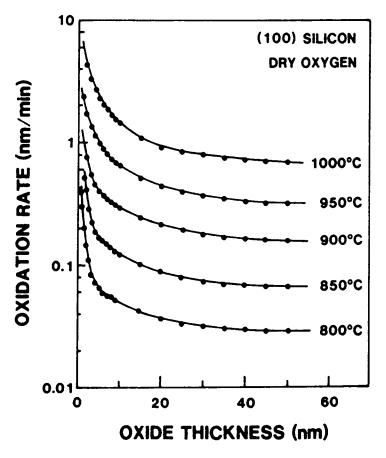

Figure 3.2; Oxidation rate of {100} silicon in dry oxygen after reference [24].

sites to accomodate the structural transition from crystalline to low density amorphous. Disorder, as well as contributing to the density of interface states, may be expected to cause broadening of the trap distribution in energy. Interestingly, the degree of surface disorder has been found to be twice as great for  $\{111\}$  as for  $\{100\}$  oriented silicon<sup>[20]</sup> in line with the measured values of  $N_{ss}$  for these two surfaces.

In conclusion then, it has to be recognized that a tunnel oxide MIS is in reality a far more complex structure than is treated in the theoretical model of chapter 2. It is clearly naïve to treat the potential barrier presented by the oxide as trapezoidal or to neglect the presence of interface states.

## 3.3 Theory of Thin Oxide Growth

A well established model for the growth of oxides on silicon is that due to Deal and Grove<sup>[21]</sup> which accounts quite well for the growth of layers thicker than several hundred Ångstroms. In this model, the growth rate is described by a 'linear-parabolic' relationship;

$$d_{ox}^2 + A.d_{ox} = B.(t+\tau)$$

(3.2)

in which  $\tau$  is included to account for the presence of a nascent oxide (of thickness  $x_i$ ) prior to oxidation and is defined as;

$$\tau = \frac{x_i^2 + A.x_i}{B} \tag{3.3}$$

For thicknesses less than around 200Å, growth is considered to be limited by the rate of surface reaction and thus to be linear with time, independent of the oxide depth. Expression (3.2) then reduces to a linear relationship;

$$d_{ox} = \frac{B}{A}(t+\tau) \tag{3.4}$$

At atmospheric pressure, the linear rate constant is given by;

$$\frac{B}{A} = \frac{k_s \cdot C^*}{N_1} \tag{3.5}$$

where  $k_s$  is the temperature-dependent interfacial reaction constant,  $C^*$  is the equilibrium concentration of the oxidising species in the oxide and  $N_1$  is the number of oxidant

molecules required per unit volume of oxide formed. For greater thicknesses, diffusion of the oxidising species becomes the rate limiting mechanism and the growth rate becomes parabolic.

Clearly, in the growth of tunnelling thickness oxides the parabolic regime is never reached and it might be expected that growth would proceed linearly at a rate determined only by the temperature, orientation of substrate and oxidising species present. Although  $C^*$  is to some extent a function of temperature, the activation energy for the oxidation process,  $E_A$ , predominantly reflects the temperature dependence of  $k_s$  and relates to the energy required to break a Si-Si bond. As such, the activation energy is also influenced by the crystal orientation and for the principle silicon surfaces used follows a progression  $E_A\{100\} > E_A\{111\} > E_A\{110\}$ . The factor  $k_s$  is also dependent on the crystal orientation of the basis of the availability of silicon-silicon bonds at the surface, as accounted for by Ligenza<sup>[22]</sup>. It has since been confirmed experimentally that the growth rate,  $\gamma$ , does indeed follow the sequence  $\gamma_{\{110\}} > \gamma_{\{111\}} > \gamma_{\{100\}}$ .

However, in practice it is found that the initial growth rate is considerably higher than predicted by the simple linear rate expression. For example, recently Massoud et. al. have measured a substantial excess growth rate in dry  $O_2$  over more than 100Å<sup>[23]</sup>

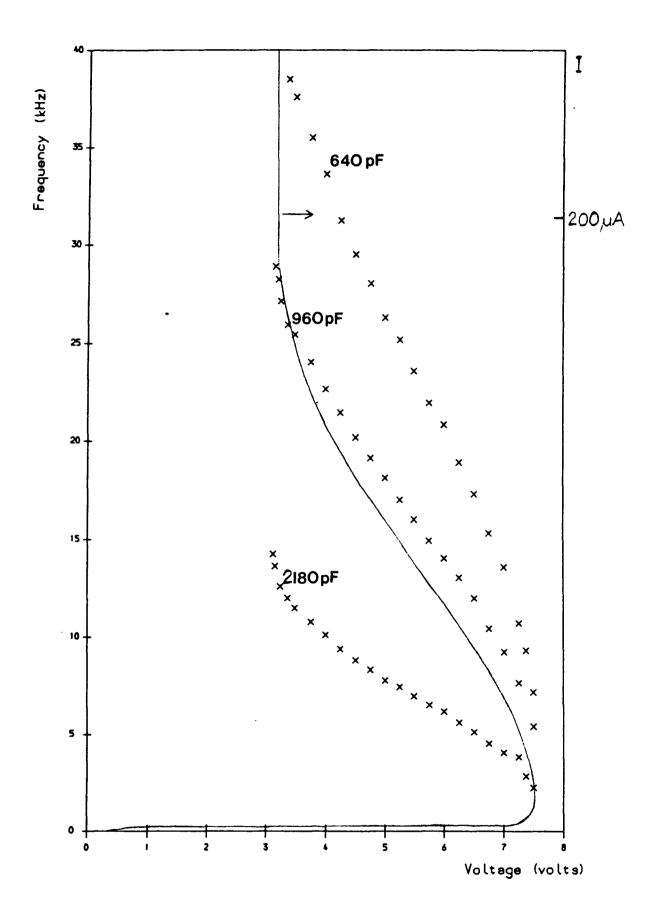

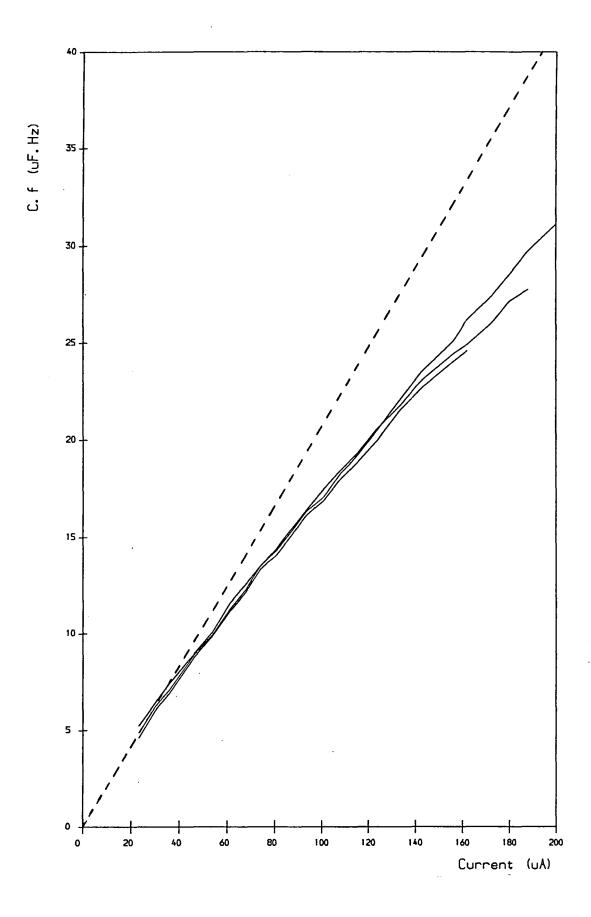

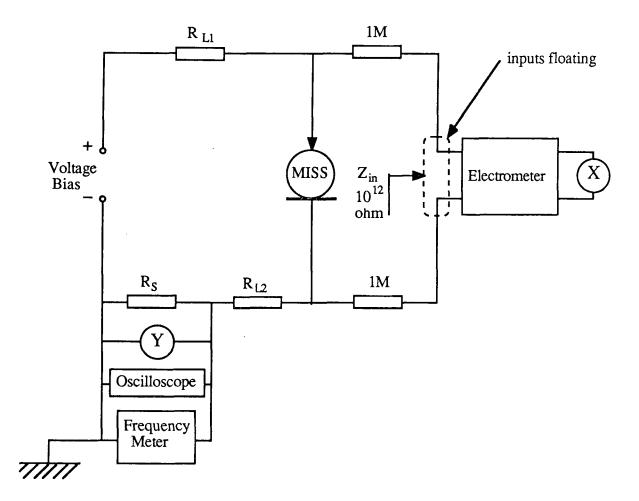

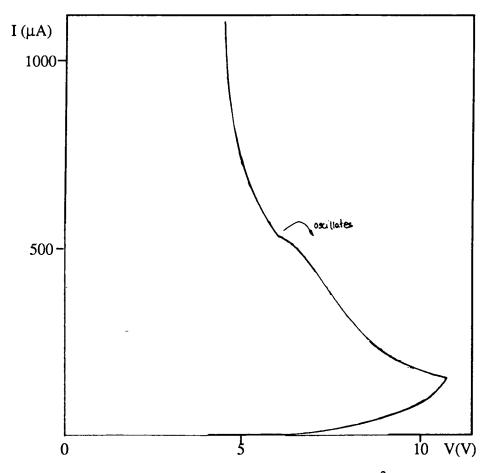

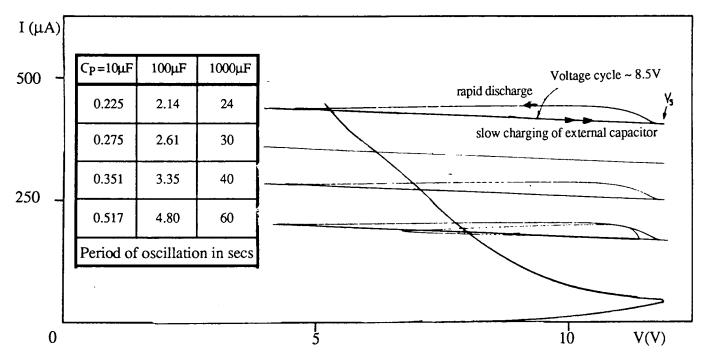

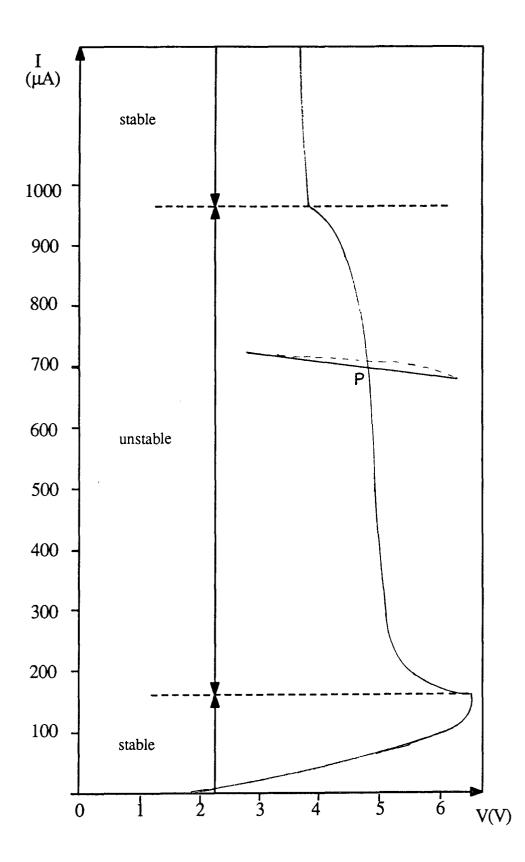

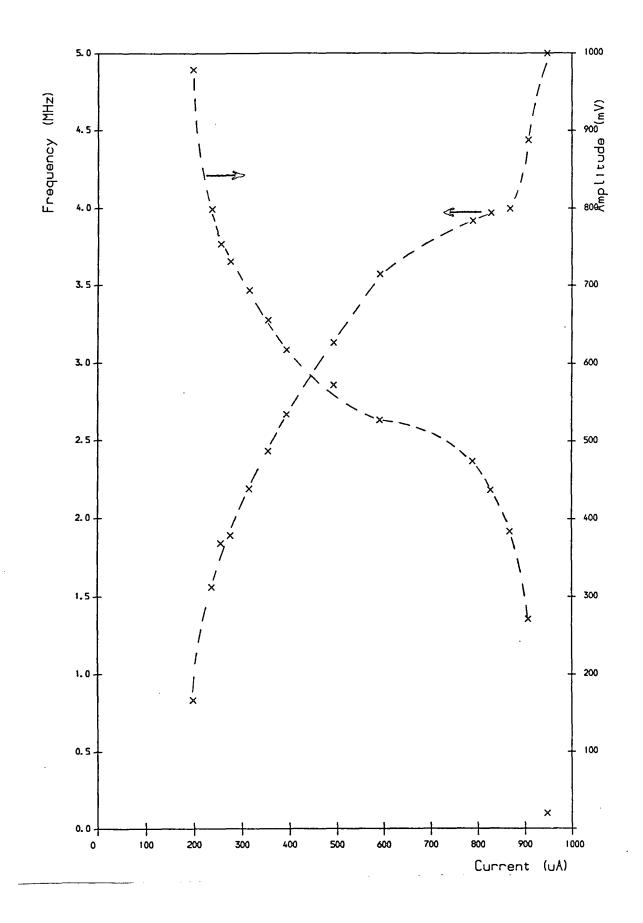

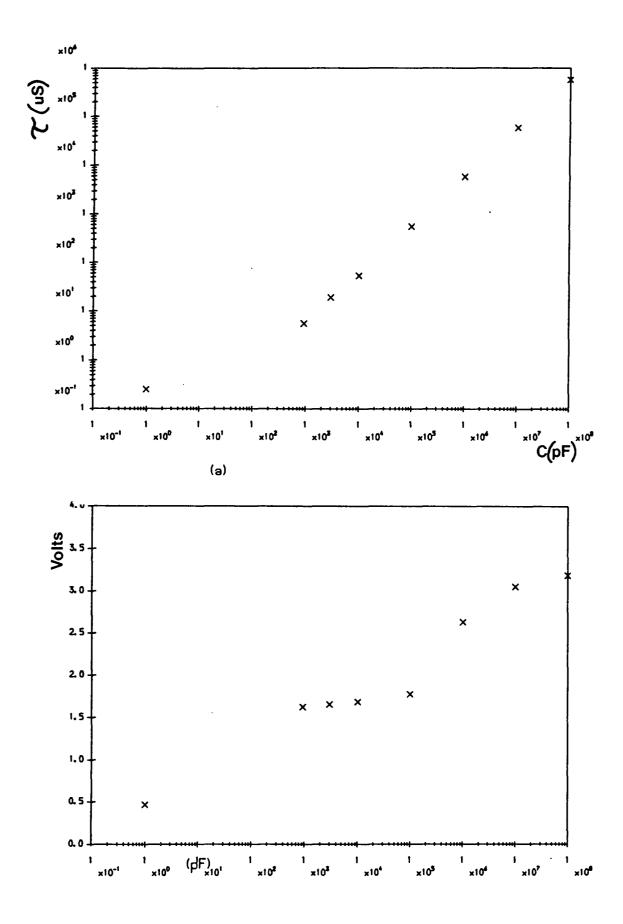

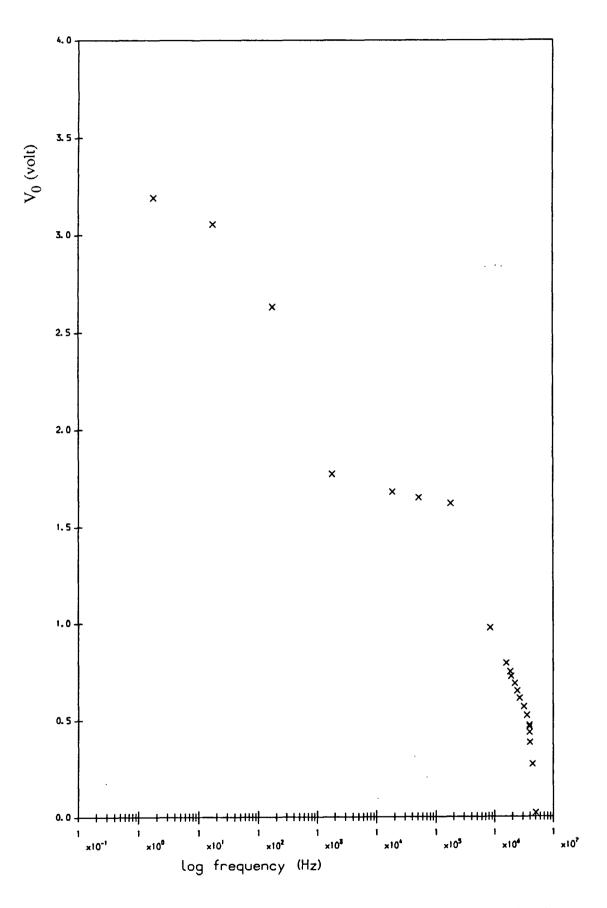

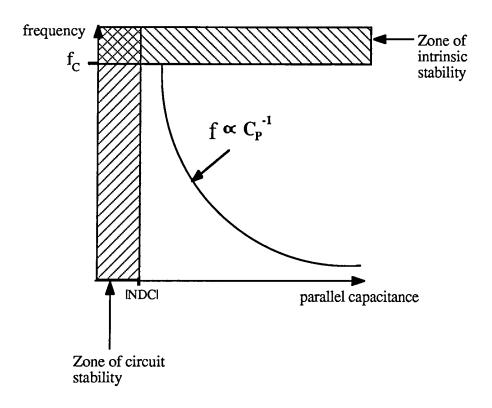

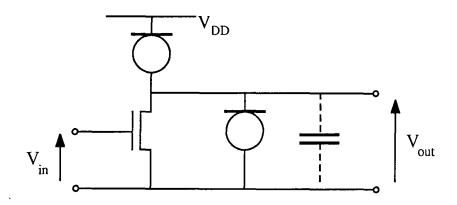

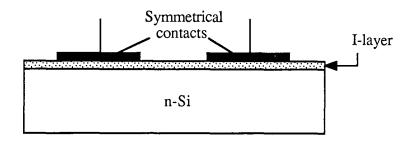

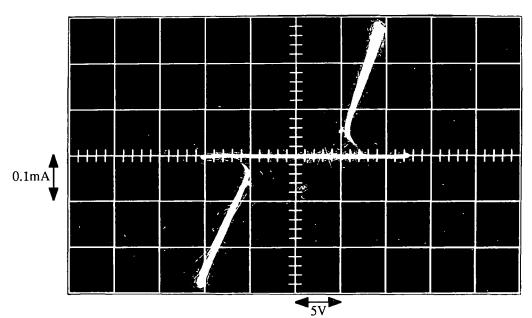

Figure 3.2 after reference [23] shows measured growth rates on  $\{100\}$  silicon in dry oxygen for a range of temperatures. The excess rate observed, in this case up to about 3 to 4nm, has been found to vary exponentially with thickness. Irene first proposed a model<sup>[24]</sup> suggesting that channels form in the relatively open structure of the amorphous SiO<sub>2</sub> network which may extend right through to the interface. It is possible then for the oxidising species to 'stream' through such 'micropores' and produce the anomalously high growth rate.