# **Durham E-Theses**

# Electrical characteristics of SRO-miss devices and their applications

Majlis, Burhanuddin bin Haji Yeop

#### How to cite:

Majlis, Burhanuddin bin Haji Yeop (1988) Electrical characteristics of SRO-miss devices and their applications, Durham theses, Durham University. Available at Durham E-Theses Online: http://etheses.dur.ac.uk/6322/

#### Use policy

The full-text may be used and/or reproduced, and given to third parties in any format or medium, without prior permission or charge, for personal research or study, educational, or not-for-profit purposes provided that:

- a full bibliographic reference is made to the original source

- a link is made to the metadata record in Durham E-Theses

- the full-text is not changed in any way

The full-text must not be sold in any format or medium without the formal permission of the copyright holders.

Please consult the full Durham E-Theses policy for further details.

# ELECTRICAL CHARACTERISTICS OF SRO-MISS DEVICES AND THEIR APPLICATIONS

by

# Burhanuddin bin Haji Yeop Majlis

SmSn(U.K.M'sia), MSc(Wales)

The copyright of this thesis rests with the author.

No quotation from it should be published without his prior written consent and information derived from it should be acknowledged.

This thesis is submitted to the University of Durham in candidature for the degree of Doctor of Philosophy

School of Engineering and Applied Science

University of Durham

October 1988

Dedicated to my mother, wife and sons.

Know that the life of this world is only play, and idle talk, and pageantry, and boasting among you, and rivalry in respect of wealth and children; as the likeness of vegetation after rain, whereof the growth is pleasing to the husbandman, but afterward it drieth up and thou seest it turning yellow then it becometh straw. And in the Hereafter there is grievous punishment, and (also) forgiveness from Allah and His good pleasure, whereas the life of the world is but matter of illusion.

(Holy Qu'ran 57:20)

# **DECLARATION OF ORIGINALITY**

I declare that the work presented here has not been submitted for any other degree. This thesis is my original work, except where indicated by refrence to other work.

# ABSTRACT

The electrical characteristics of the Metal-Insulator-Semiconductor - Switch (MISS) device with Silicon-Rich-Oxide (SRO) as the semi-insulating material have been comprehensively studied at room temperature in an exploratory way. The SRO films were deposited by atmospheric pressure chemical vapour deposition (APCVD) at 650°C with SiH<sub>4</sub> and N<sub>2</sub>O reactant gases and N<sub>2</sub> carrier. The reactant gas phase ratio  $R_o$  varying from 0.09 to 0.25 and the deposition time varying from 0.6 to 2 min. Some preliminary investigations on SRO-MIS devices were also carried out in order to understand the electronic process in the structure. Various parameters which governed the switching behaviour of an MISS were investigated. In general the switching characteristics are similar to those of the tunnel oxide MISS. The geometrical dependence of the switching behaviour in the tunnel oxide MISS has been extended to the present device by looking at the effects of electrode area, junction area, electrode perimeters and of a metal guard ring. Other effects, such as SRO deposition time, work function difference, gold doping, heat treatment, light illumination and film ageing were also observed. The dynamic characteristic of the device was studied using a double pulse technique.

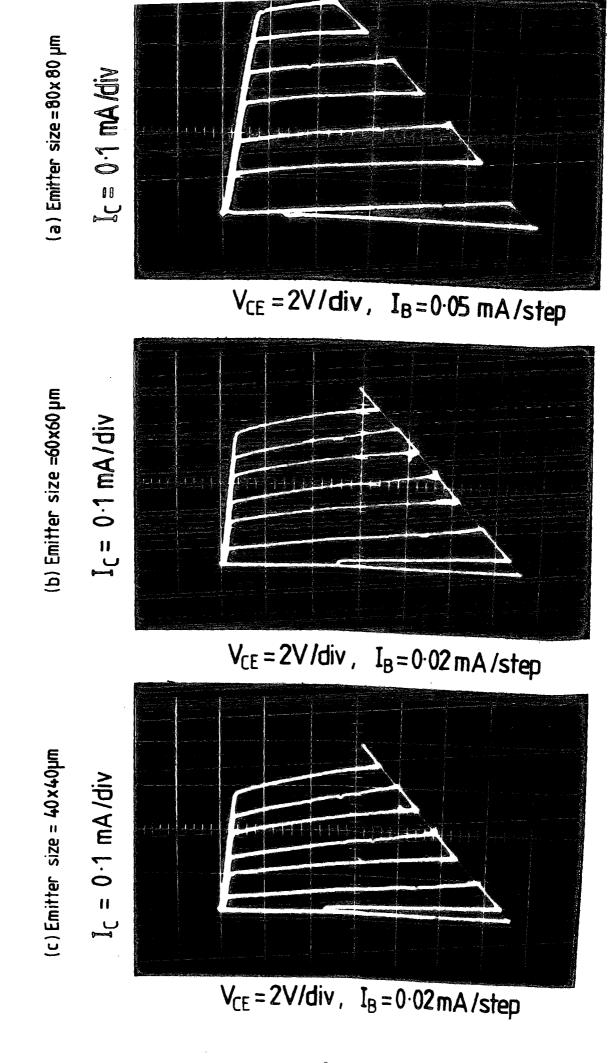

The characteristics of the three-terminal SRO-MISS were studied in both forward and reverse bias. The former exhibited a thyristor-like characteristic and the latter a transistor-like characteristic. A preliminary study on the MIS-emitter transistor was carried out with different emitter areas. In general the characteristics are the same as for the equivalent tunnel oxide devices. However it was also found that if the n-type epilayer is very thin the transistor characteristics exhibits an N-type negative resistance.

The negative resistance region of the two-terminal MISS has been shown to be stable and the stability has been analysed in terms of equivalent circuit elements. The reason for the stability is that the device also has an negative capacitance. This has been proved experimentally and it is a new property of the MISS structure which never been reported before. The negative capacitance has been measured as a function of electrode area, SRO type and light illumination. An important circuit application for the negative capacitance has also been suggested and demonstrated

# **ACKNOWLEDGMENTS**

I would like to take this opportunity to express my appreciation to many people who have assisted me in completing this work. First of all, I wish to express my gratitute to my supervisor Dr. M. J. Morant for his valuable advice and intellectual discussions throughout the period of this work and for his constructive criticism during the preparation of this thesis.

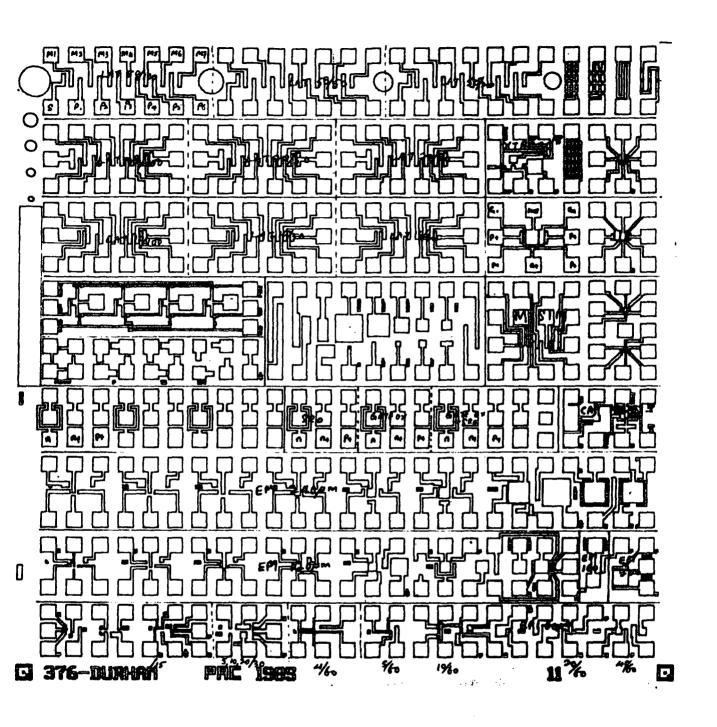

I am also indebted to Mr. P. Clifton who has designed the mask for the multistructure chips. His cooperation and discussion during the first two years of this study are fully acknowledged. I should also like to thank Mr. J. E. Gibson for his technical assistance in the clean room and for the sample fabrication.

My appreciation is extended to the Malaysian government for the award of financial grant and the Universiti Kebangsaan Malaysia for study leave.

Finally, I would like to thank my wife, Norridah Nee, and my sons, Haidar and Hafiz for their patience and understanding during this period of study.

# LIST OF SYMBOLS

$A_i$  - p-n junction area.

$A_o$  - Tunnel insulator area.

$A_e(A_p)$  - Effective Richardson constant for electrons (holes).

$C_i$  - Insulator capacitance per unit area.

$D_n(D_p)$  - Diffusion coefficient for electron (holes).

d - Semi-insulator thickness.

$E_c$  - Lowest conduction band energy level.

E<sub>i</sub> - Intrinsic Fermi level.

$E_v$  - Highest valence band energy level.

$E_q$  - Semiconductor energy gap.

$E_t$  - Interface trap energy level.

$E_{Fm}$  - Fermi level of metal.

$E_{Fp}$  - Fermi level of the p-type semiconductor.

$E_{Fn}$  - Fermi level of the n-type semiconductor.

G - Small-signal total gain.

$G_s$  - Small-signal MIS gain.

G, - Small-signal p-n junction gain.

$I_h$  - Holding current.

*I<sub>s</sub>* - Switching current.

$I_{OFF}$  - Total current through the MISS in the OFF state.

$I_{ON}$  - Total current through the MISS in the ON state.

$I_q$  - Generation current density in the surface depletion region.

$J_{dn}$  - Electron p-n junction diffusion current density.

$J_{dp}$  - Hole p-n junction diffusion current density.

$J_{n_1}$  - Electron diffusion current density in the p-n junction.

$J_{tn}$  - Electron tunnel current density.

$J_{tp}$  - Hole tunnel current density.

$J_{p_1}$  - Hole diffusion current density in the p-n junction.

$J_{r_1}$  - Recombination current density in the p-n junction.

k - Boltzman constant in eV/oK.

L - Length of the neutral n region.

$L_n$  - Diffusion length for electrons in the p region.

Current multiplication factor for MIS in reverse bias.

$M_a$  - Avalanche multiplication coefficient.

$N_a(N_d)$  - Impurity doping density in the p[n] region.

$n_1$  - Intrinsic carrier density in the semiconductor.

q - Magnitude of electronic charge.

Q<sub>i</sub> - Total charge per unit area at the interface.

$Q_f$  - Fixed charge density per unit area.

$Q_s$  - Charge per unit area in the semiconductor.

T - Temperature in degrees Kelvin.

V - Voltage applied to the MISS device.

$V_q$  - Avalanche breakdown voltage of the n-type epilayer.

$V_{FB}$  - Flat-band voltage.

$V_h$  - Holding voltage.

$V_s$  - Switching voltage.

$V_i$  - Voltage drop across the p-n junction.

$V_i$  - Voltage drop across the insulator.

$X_d$  - Width of the surface depletion region.

$W_{ij}$  - Width of the p-n junction depletion region.

$W_n$  - Epitaxial layer thickness.

# **Greek Letters**

$\beta_p$  - p-n junction gain for holes.

$\epsilon_i(\epsilon_s)$  - Permittivity of the insulator (semiconductor) in farad/cm.

$au_{epi}$  - Lifetime of holes in the n-type epitaxial layer.

$au_n$  - Lifetime of electrons in the p-type subtrate.

$\phi_{ms}$  - Metal-semiconductor work function difference.

$\phi_m$  - Metal work function.

$\phi_s$  - Semiconductor work function.

$\phi_b$  - Potential difference between the Fermi level and intrinsic Fermi level.

$\sigma_n(\sigma_p)$  - Capture cross section of electrons (holes).

$\psi_s$  - Surface potential in the semiconductor.

$\psi_{sp}$  - Surface potential in the semiconductor at punch-trough.

$\chi_n(\chi_p)$  - Tunnelling barrier height for electrons (holes).

$\gamma_n(\gamma_p)$  - Injection efficiency of electrons (holes).

$\eta_n(\eta_p)$  - Barrier tunnelling transmision coefficient for electrons (holes).

# **Abbreviations**

APCVD- Atmospheric Pressure Chemical Vapour Deposition

CID - Control-Inversion-Device

CVD - Chemical Vapour Deposition

MIS - Metal-Insulator-Semiconductor

MISS - Metal-Insulator-Semiconductor-Switch

MIST - Metal-Insulator-Semiconductor-Thyristor

MISM - Metal-Insulator-Semiconductor-Metal

MISIM - Metal-Insulator-Semiconductor-Insulator-Metal

SIPOS - Semi-Insulating-Polycrystalline-Silicon

SRO - Silicon-Rich-Oxide

# CONTENTS

|                                                       | Page No |

|-------------------------------------------------------|---------|

| Abstract                                              | i       |

| Acknowledgement                                       | ii      |

| List of Symbols                                       | iii     |

| CHAPTER 1 INTRODUCTION.                               | 1       |

| 1.1 Semiconductor Device Structures.                  | 1       |

| 1.2 The MISS Structure.                               | 1       |

| 1.2.1 Review of MISS Characteristics.                 | 1       |

| 1.2.2 Device Structure and Materials.                 | 2       |

| 1.3 Objective and Thesis Outline.                     | 4       |

| References.                                           | 6       |

| CHAPTER 2 THEORETICAL CONCEPTS FOR MISS DEVICES.      | 8       |

| 2.1 Introduction.                                     | 8       |

| 2.2 The MIS Diode.                                    | 8       |

| 2.2.1 The Ideal MIS Diode.                            | 8       |

| 2.2.2 The Non-Ideal MIS Diode.                        | 12      |

| 2.3 Generation and Recombination in Depletion Layers. | 14      |

| 2.4 The MIS Tunnel Diode.                             | 16      |

| 2.4.1 MIS Tunnel Diode at Reverse Bias.               | 17      |

| 2.4.2 MIS Tunnel Diode at Forward Bias.               | 20      |

| 2.4.3 Current Multiplication in Reverse Bias.         | 21      |

| 2.5 P-N Junction Diode.                               | 22      |

| 2.5.1 Current-Voltage Equations.                      | 22      |

| 2.5.2 P-N Junction Ratio $\beta_p$ for Holes.         | 24      |

| 2.5.3 Practical P-N Junctions.                        | 25      |

| References.                                           | 26      |

| CHAPTER 3 PRINCIPLE OF OPERATION OF MISS DEVICES.     | 28 |

|-------------------------------------------------------|----|

| 3.1 Introduction.                                     | 28 |

| 3.2 Operation with Reverse Bias.                      | 31 |

| 3.3 Operation with Forward Bias.                      | 32 |

| 3.3.1 High Impedance State.                           | 32 |

| 3.3.2 Switching Point in Punch-Through Mode.          | 33 |

| 3.3.3 Switching Point in Avalanche Mode.              | 36 |

| 3.3.4 Switching Point in Generation Controlled Mode.  | 37 |

| 3.3.5 Negative Resistance and Low Impedance States.   | 38 |

| 3.4 Operation of Devices with SRO Films.              | 40 |

| 3.4.1 Electronic Conduction in SRO.                   | 40 |

| 3.4.1.1 Symmetrical Schottky Barrier Mechanism.       | 41 |

| 3.4.1.2 Fowler-Nordheim Tunnelling.                   | 43 |

| 3.4.2 Bolt and Simmons's Model for SIPOS-MISS.        | 45 |

| 3.4.3 Current Equations.                              | 47 |

| 3.5 Summary                                           | 48 |

| References.                                           | 49 |

| CHAPTER 4 FABRICATION AND ELECTRICAL CHARACTERIZATION |    |

| OF THE DEVICES.                                       | 51 |

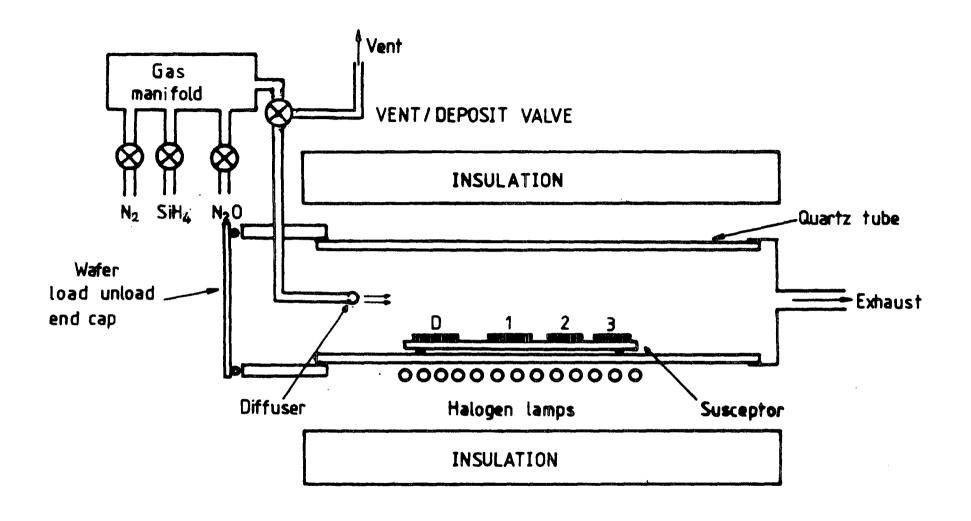

| 4.1 Semi-Insulating SRO Films.                        | 51 |

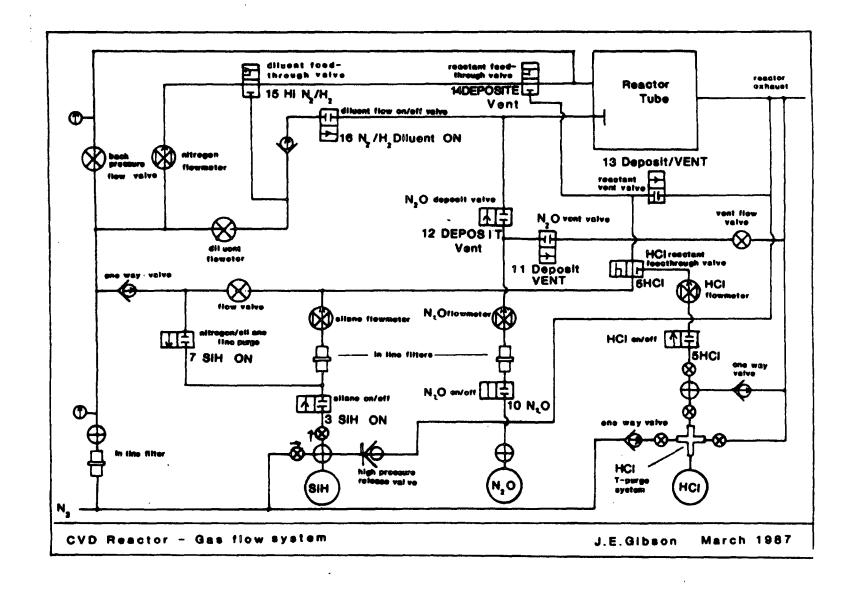

| 4.2 Chemical Vapour Deposition of SRO.                | 52 |

| 4.3 Sample Fabrication.                               | 55 |

| 4.3.1 Cleaning the Wafer.                             | 55 |

| 4.3.2 SRO Deposition Procedure.                       | 55 |

| 4.3.3 Top Contact Preparation.                        | 56 |

| 4.3.4 Back Contact Preparation.                       | 57 |

| 4.4 Current-Voltage Measurement Technique.            | 58 |

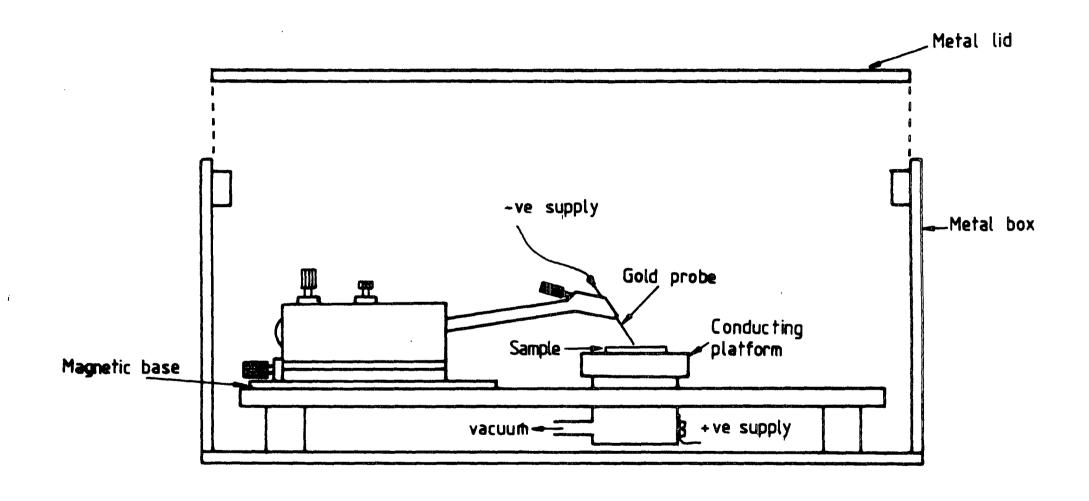

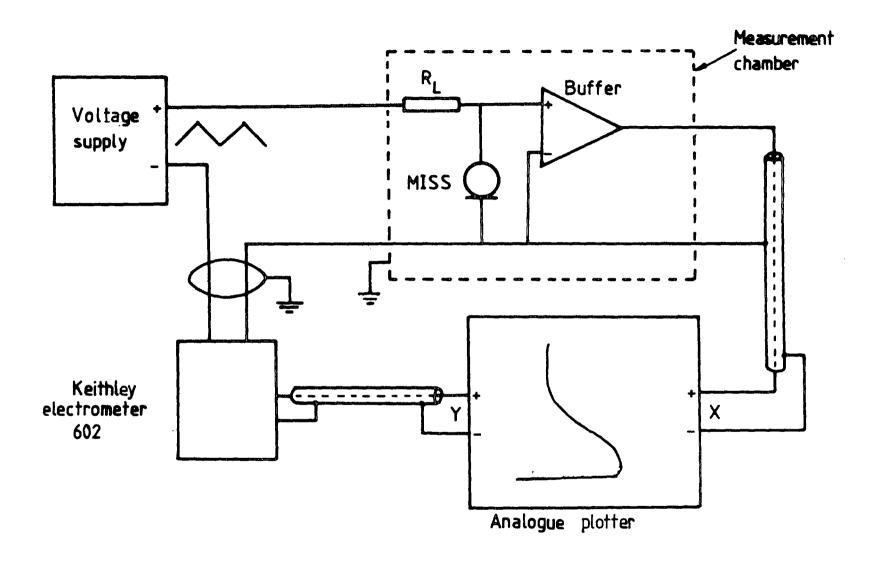

| 4.4.1 Analogue Measurement System.                    | 59 |

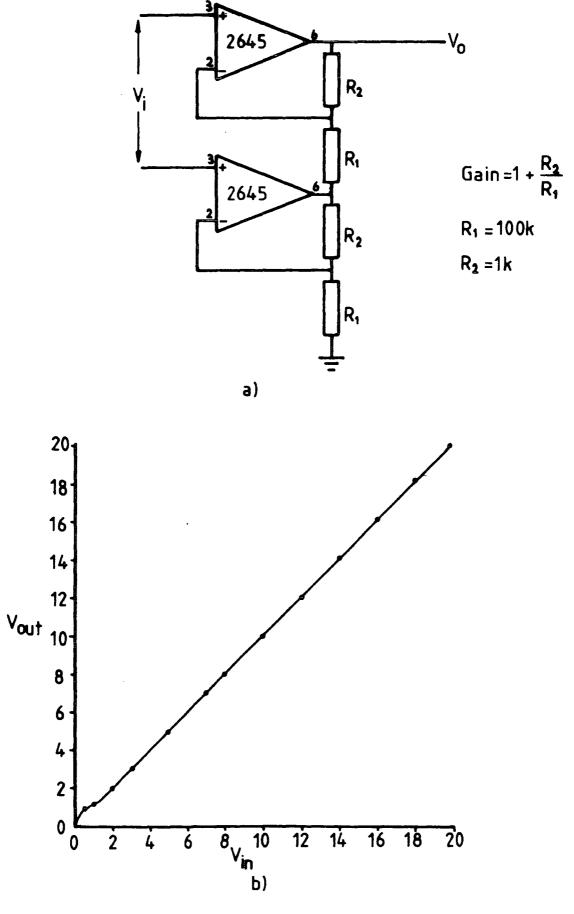

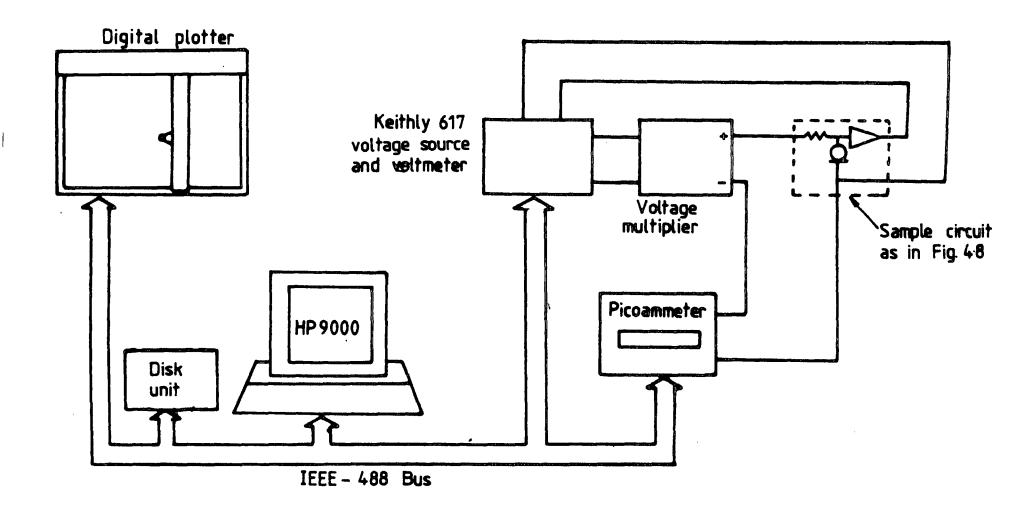

| 4.4.2 Automated Measurement System.                   | 60 |

| References.                                                          | 62   |

|----------------------------------------------------------------------|------|

| CHAPTER 5 SWITCHING CHARACTERISTICS OF THE SRO-MISS.                 | 65   |

| 5.1 Introduction.                                                    | 65   |

| 5.2 Characteristics of MIS Diodes.                                   | 66   |

| 5.2.1 Introduction.                                                  | 66   |

| 5.2.2 Current-Voltage Characteristics.                               | 66   |

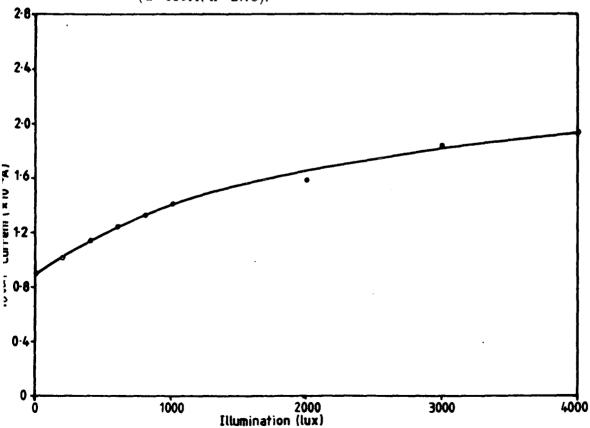

| 5.2.3 Effect of Illumination.                                        | 67   |

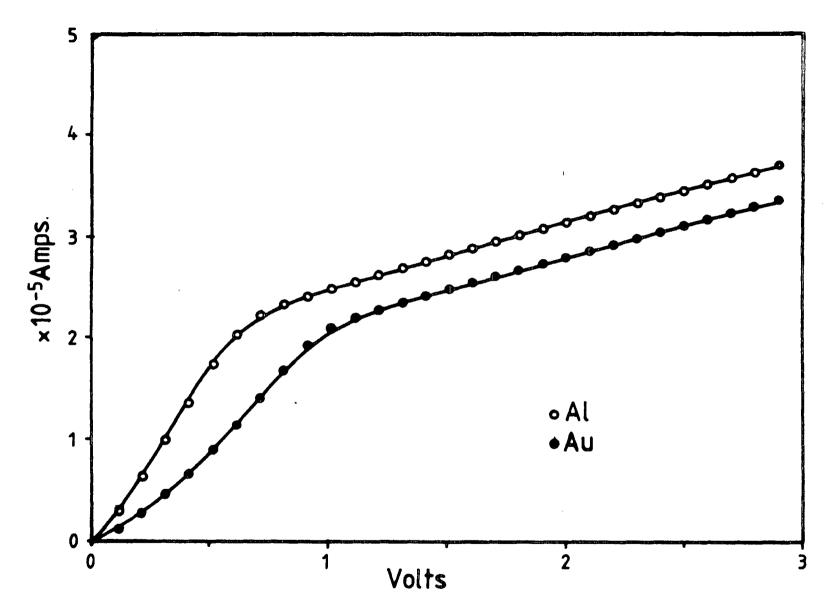

| 5.2.4 Effect of Work Function Difference.                            | 69   |

| 5.3 Two Dimensional Effects in SRO-MISS Devices.                     | 71   |

| 5.3.1 Introduction.                                                  | 71   |

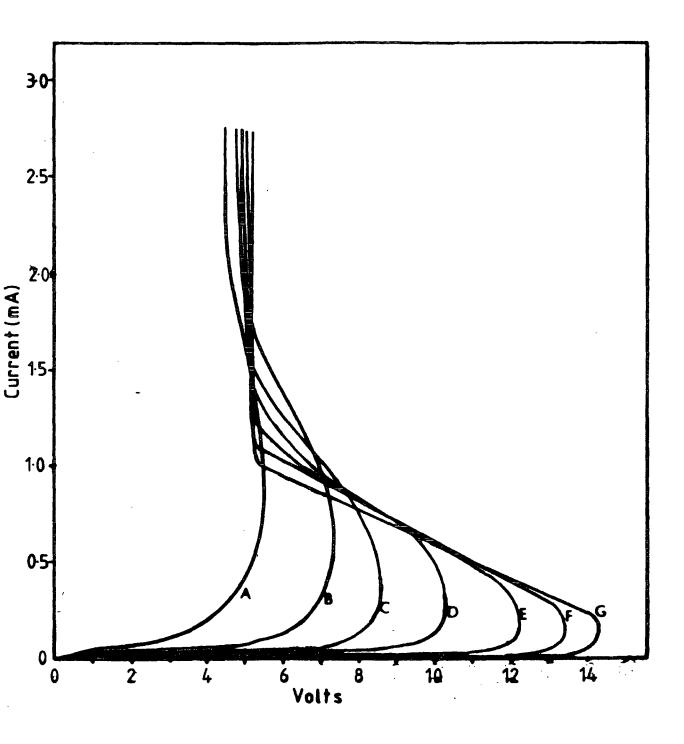

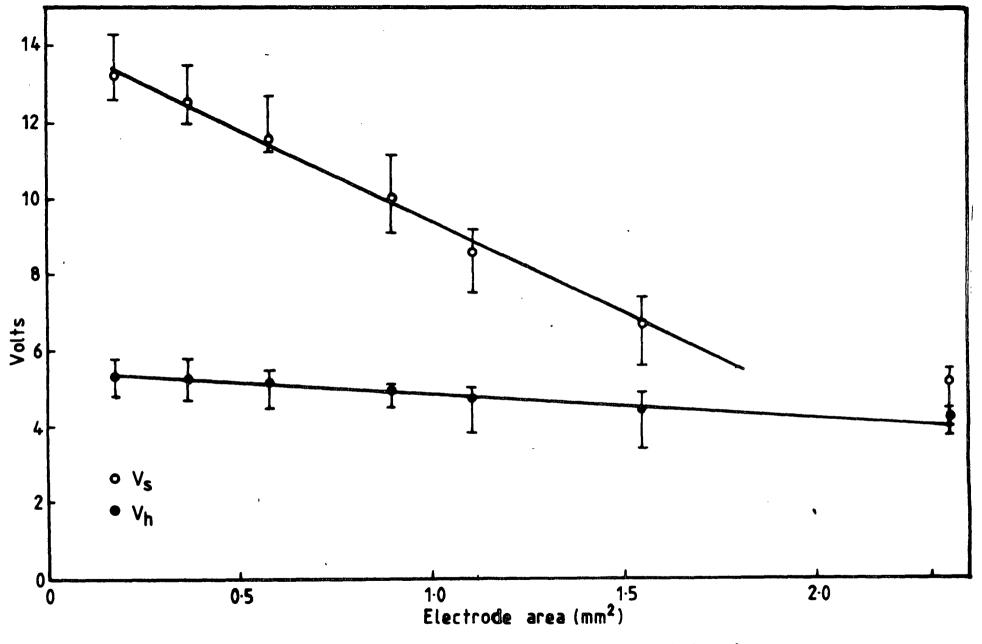

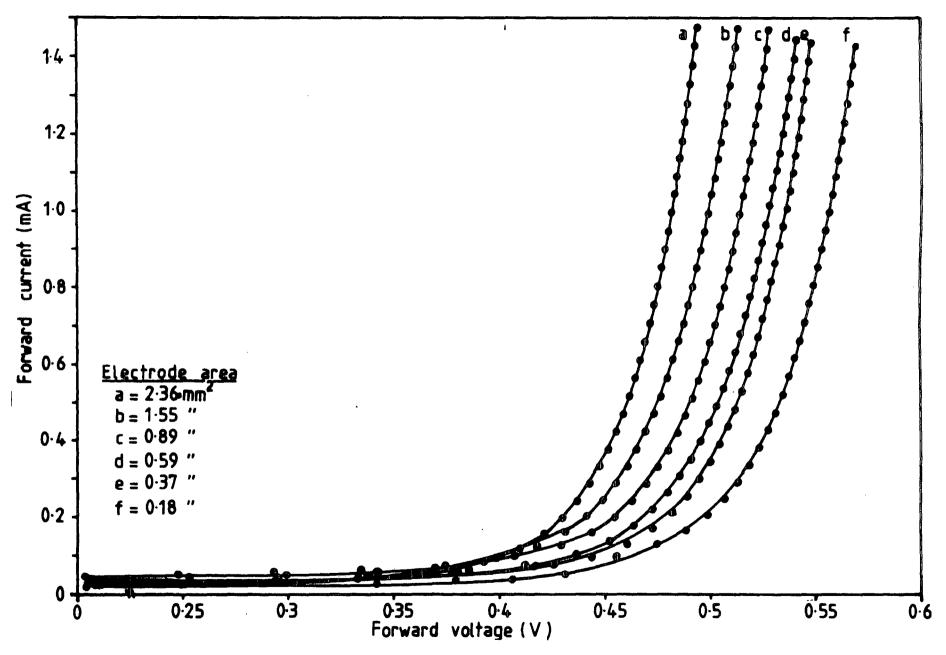

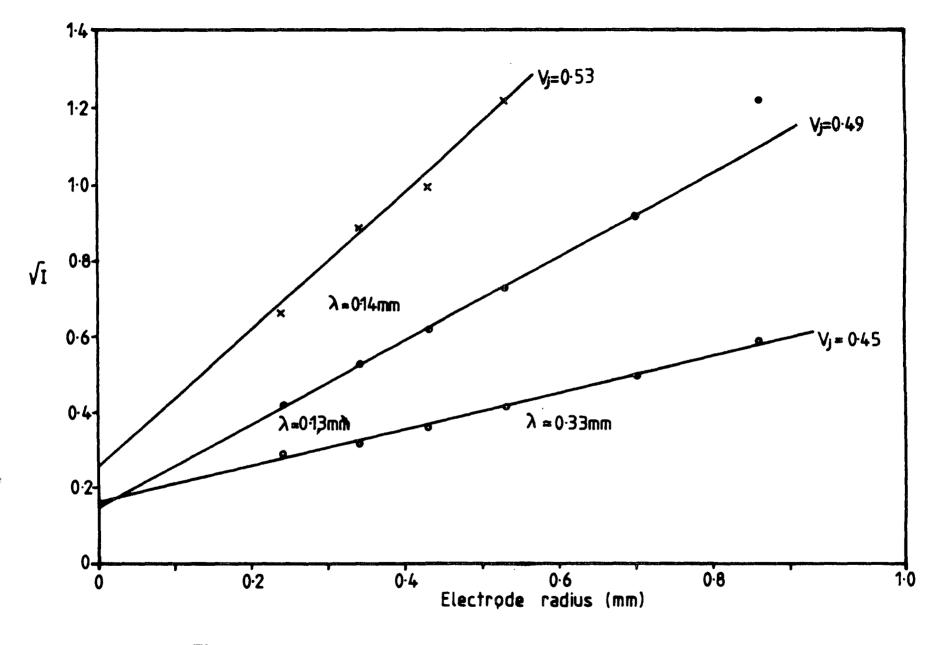

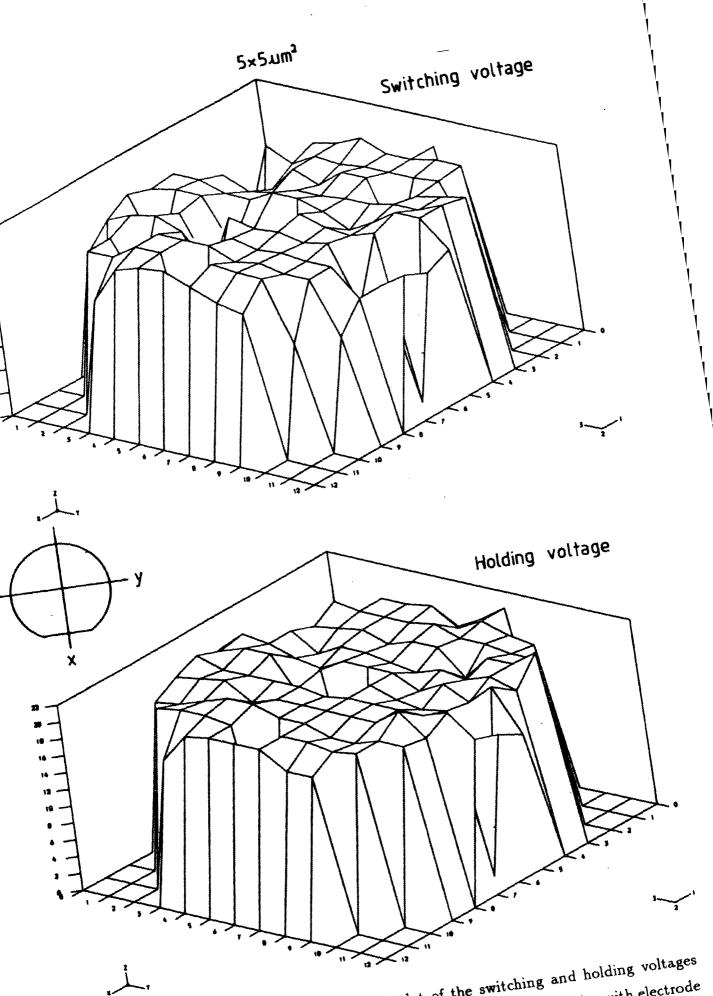

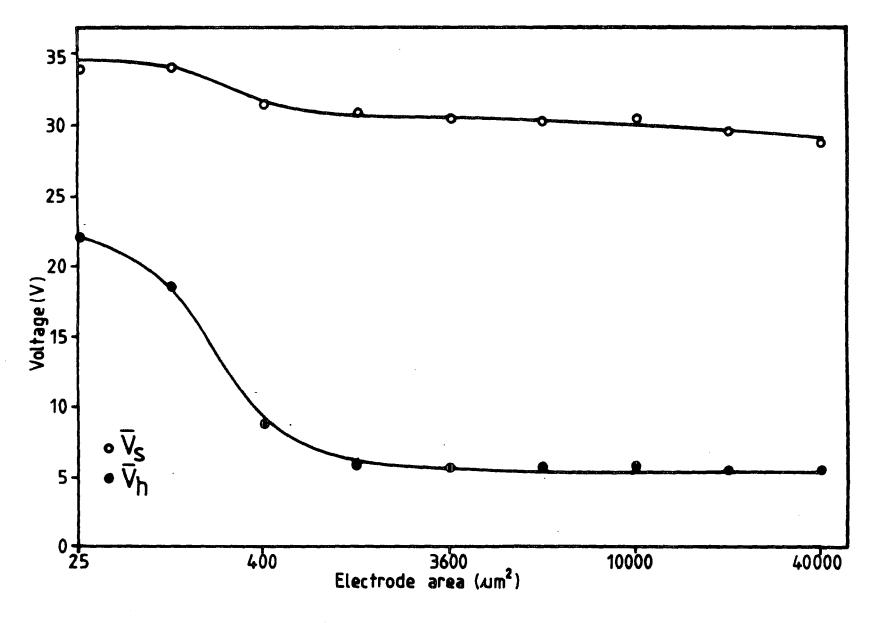

| 5.3.2 Effect of Electrode Area - Large Devices.                      | 72   |

| 5.3.3 Effect of Electrode Area - Small Devices.                      | 77   |

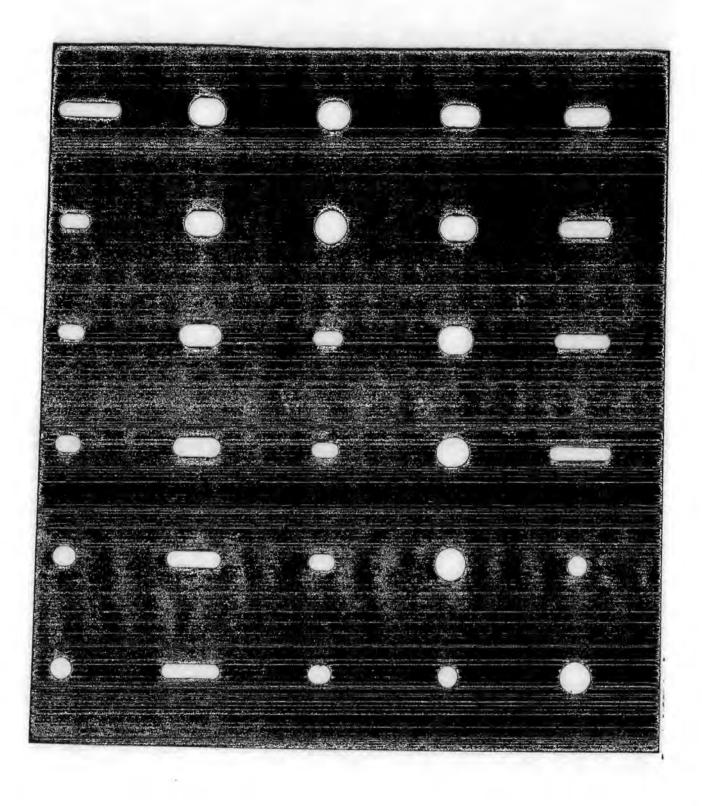

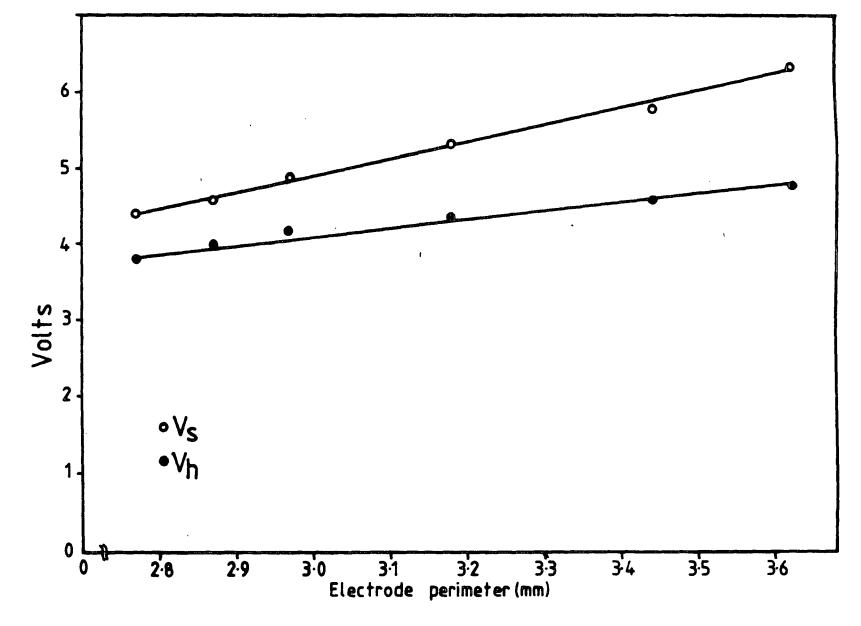

| 5.3.4 Effect of Electrode Perimeter.                                 | 78   |

| 5.3.5 Effect of Junction Area.                                       | 79   |

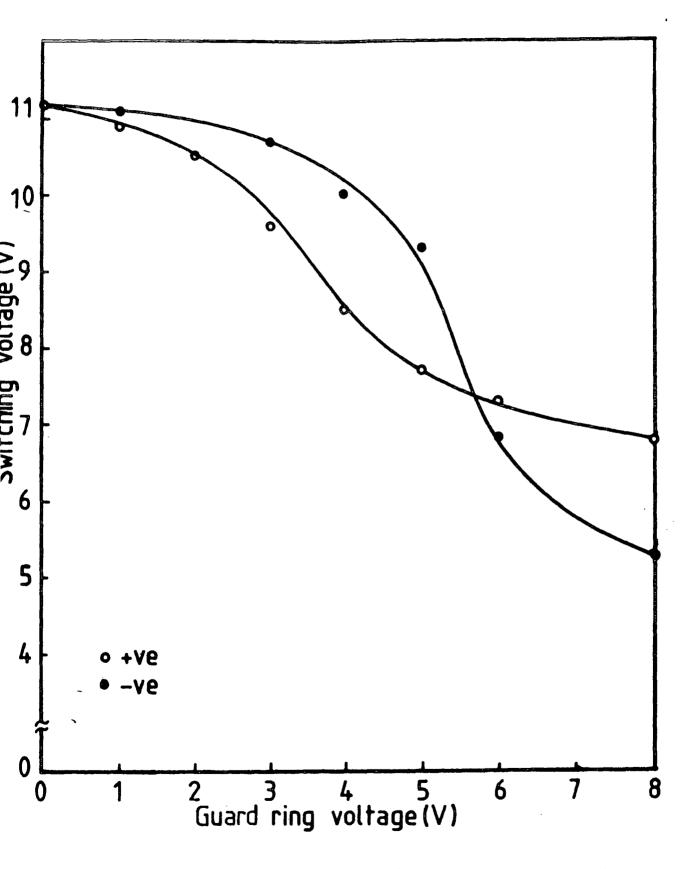

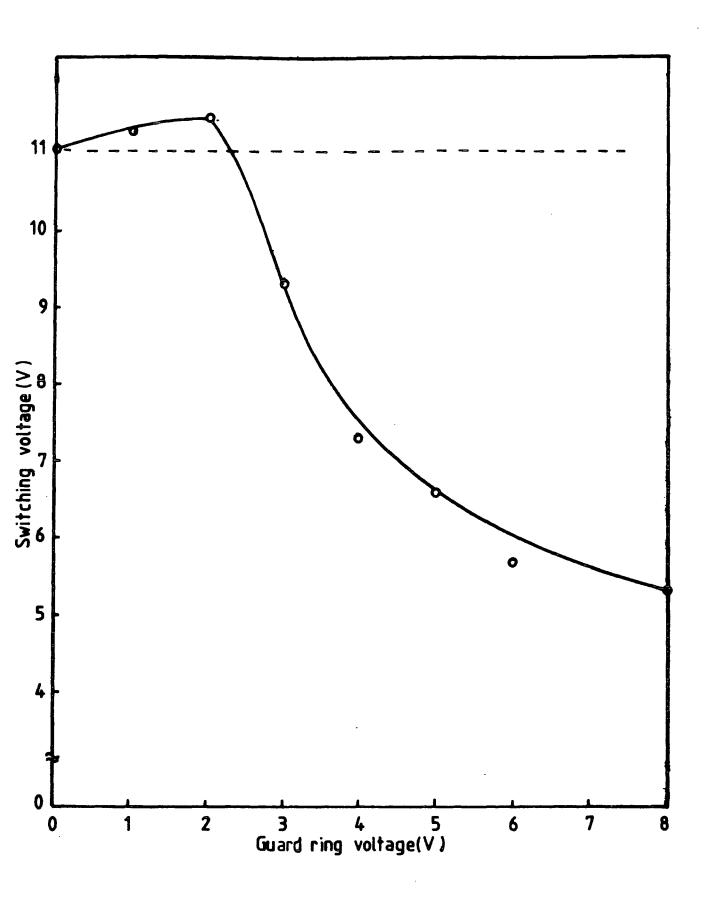

| 5.3.6 Effect of Metal Guard Ring.                                    | 81   |

| 5.3.7 Conclusion on Two-Dimensional Effects.                         | 82   |

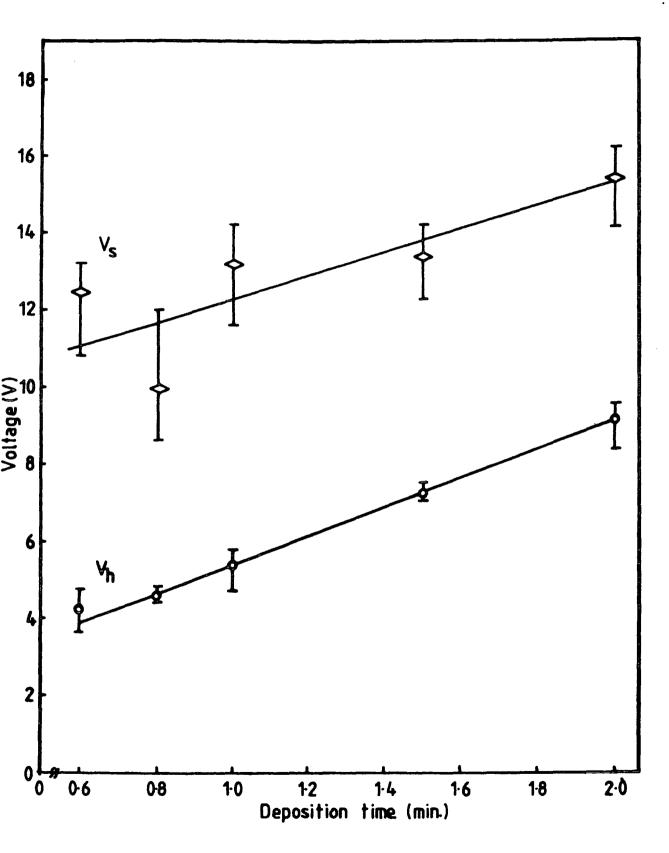

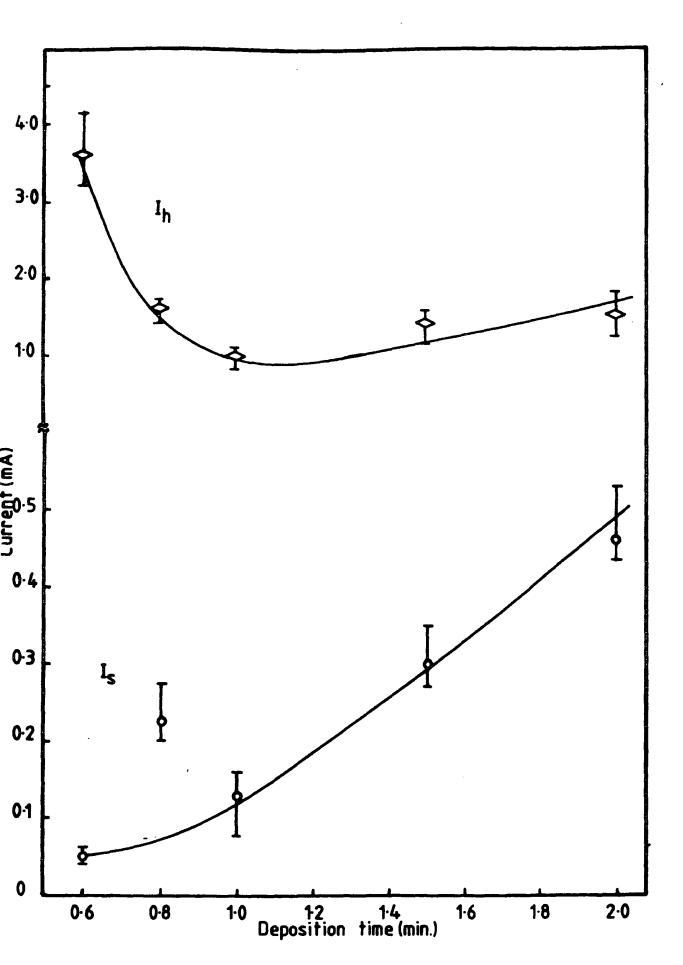

| 5.4 Effect of SRO Deposition Time.                                   | 83   |

| 5.4.1 Introduction.                                                  | 83   |

| 5.4.2 Results and Discussion.                                        | 83   |

| 5.5 Effect of Heat Treatment on Switching Characteristics.           | 85   |

| 5.6 Effect of Gold Diffusion.                                        | 86   |

| 5.6.1 Sample Preparation.                                            | 87   |

| 5.6.2 Results and Discussion.                                        | . 88 |

| 5.7 Effect of Work Function Difference on MISS Switching Parameters. | 90   |

| 5.8 Effect of Illumination on the MISS.                              | 93   |

| 5.8.1 Theoretical Review.                                            | 93   |

| 5.8.2 Results and Discussion.                                        | 94   |

| 5.9 Degradation.                                                     | 95   |

| 5.9.1 Effect of SRO Film Ageing before Metallisation.                | 95   |

| CHAPTER 5 (Cont) SWITCHING CHARACTERISTICS OF THE SRO-MISS. |     |

|-------------------------------------------------------------|-----|

| 5.9.2 Device Degradation.                                   | 95  |

| 5.10 Dynamic Characteristics.                               | 96  |

| 5.10.1 Introduction.                                        | 96  |

| 5.10.2 Double Pulse Technique.                              | 97  |

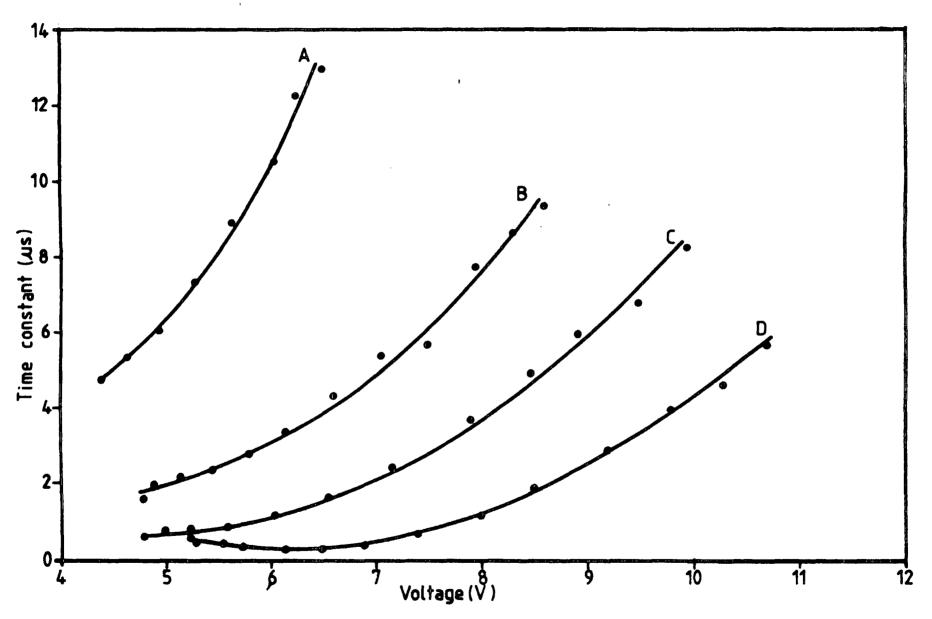

| 5.10.3 Effect of Heat Treatment on Dynamic Characteristics. | 98  |

| 5.10.4 Effect of Gold Doping on Dynamic Characteristics.    | 100 |

| 5.10.5 Effect of Double Pulses with Negative to Positive    |     |

| Voltage Swing.                                              | 100 |

| 5.11 Summary.                                               | 101 |

| References.                                                 | 103 |

| CHAPTER 6 ELECTRICAL CHARACTERISTICS OF THREE-TERMINAL      |     |

| SRO-MISS DEVICES.                                           | 106 |

| 6.1 Introduction.                                           | 106 |

| 6.2 The MIS-Thyristor(MIST).                                | 107 |

| 6.2.1 Introduction.                                         | 107 |

| 6.2.2 Theory of Operation.                                  | 108 |

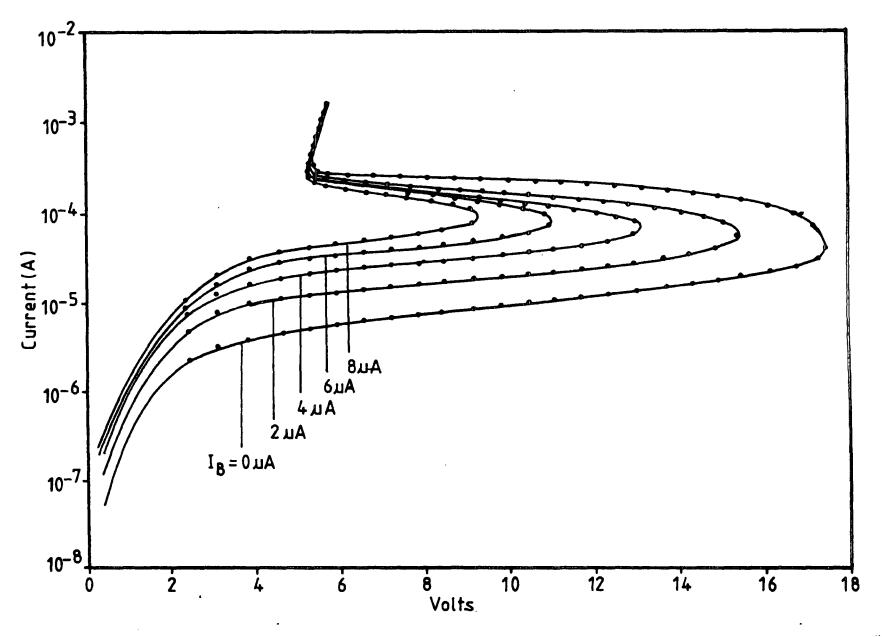

| 6.2.3 Effect of Base Current on Switching Characteristics.  | 109 |

| 6.2.4 Effect of Shunt Resistance.                           | 111 |

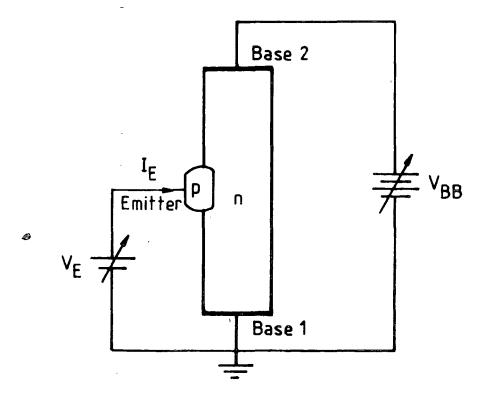

| 6.3 MIS-Emitter Transistor.                                 | 112 |

| 6.3.1 Introduction.                                         | 112 |

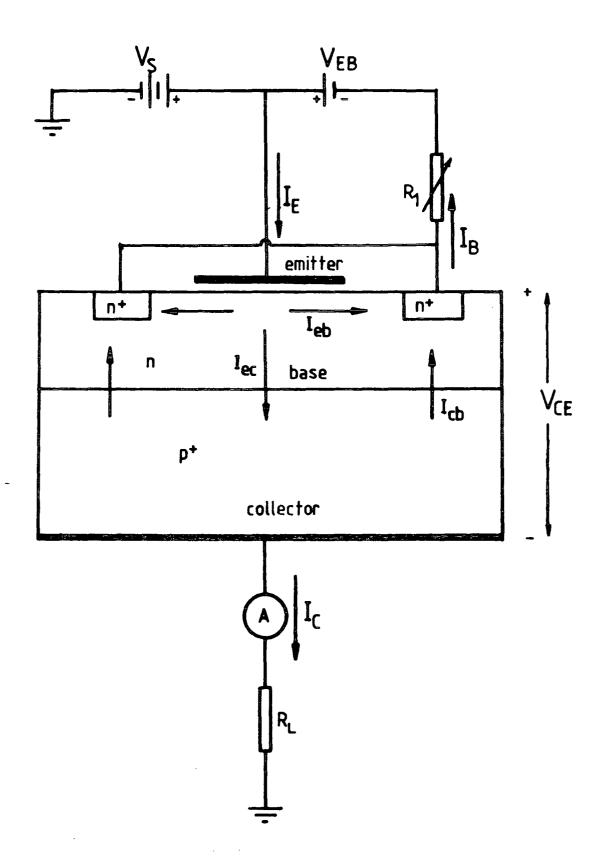

| 6.3.2 Operation of MIS-Emitter Transistor.                  | 113 |

| 6.3.3 Transistor Characteristics.                           | 114 |

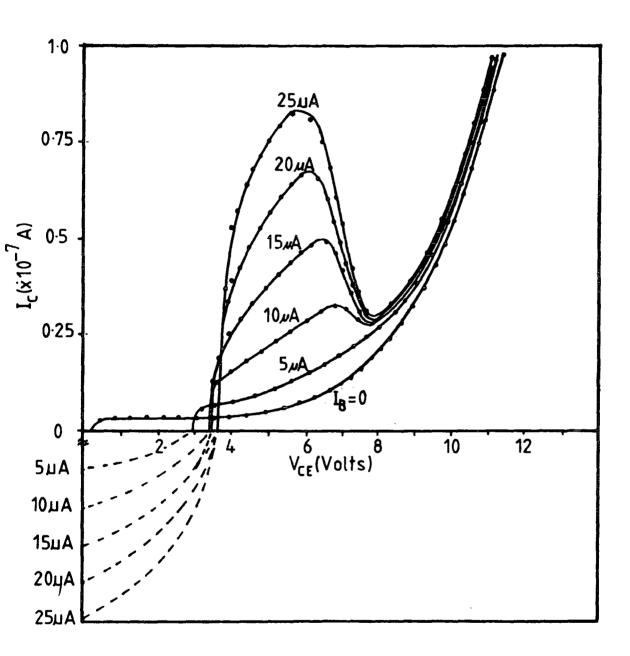

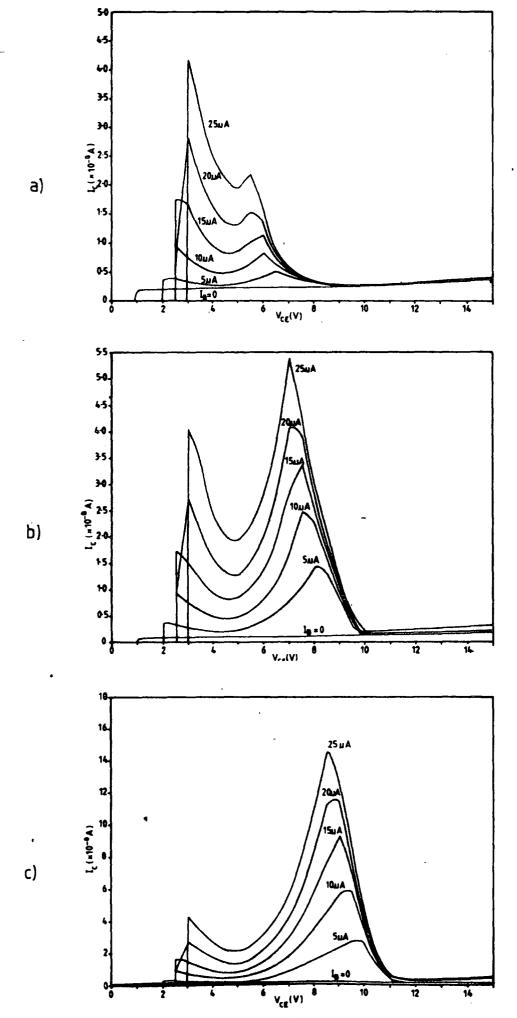

| 6.4 N-Type Negative Resistance Transistor.                  | 116 |

| 6.4.1 Observation.                                          | 116 |

| 6.4.2 Discussion.                                           | 117 |

| 6.5 Conclusion.                                             | 120 |

| References.                                                 | 121 |

# CHAPTER 7 NEGATIVE RESISTANCE AND CAPACITANCE

| OF THE SRO-MISS DEVICE.                                              | 123    |

|----------------------------------------------------------------------|--------|

| 7.1 Introduction.                                                    | 123    |

| 7.2 Electronic Mechanism Giving S-Type Negative Resistance.          | 124    |

| 7.3 Stability of a Negative Resistance Circuit.                      | 126    |

| 7.3.1 Stability Analysis.                                            | 127    |

| 7.3.2 Circuit Stability with Negative Resistance.                    | 129    |

| 7.3.3 Circuit Stability with MISS Devices.                           | 129    |

| 7.3.4 Conclusion.                                                    | 130    |

| 7.4 Measurements of Small-Signal Negative Resistance of the SRO-MISS | S. 131 |

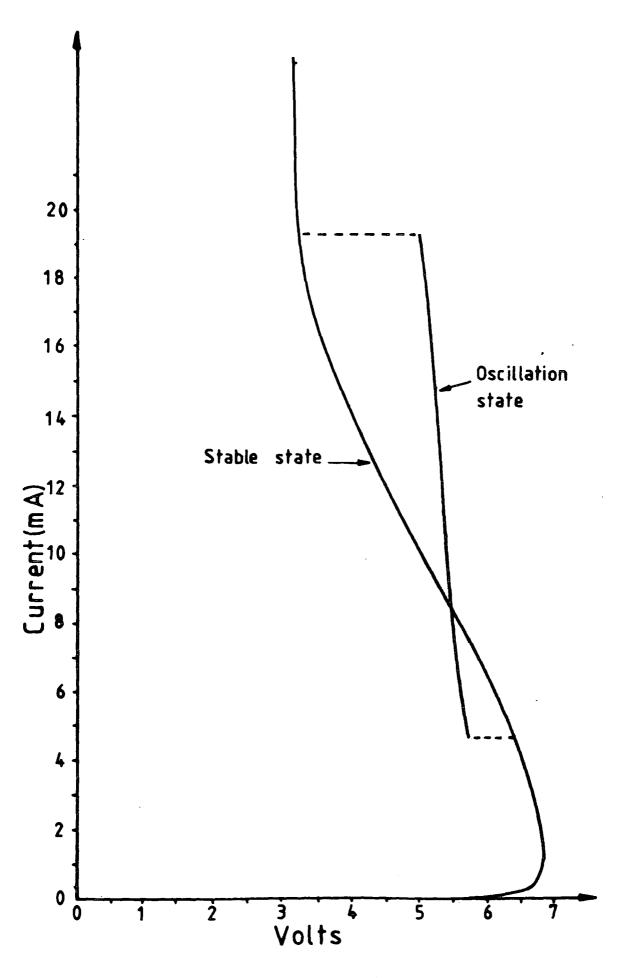

| 7.4.1 Oscillation State.                                             | 131    |

| 7.4.2 A.C. Negative Resistance Measurements.                         | 133    |

| 7.5 Measurements of the Negative Capacitance of the SRO-MISS.        | 133    |

| 7.5.1 Introduction.                                                  | 133    |

| 7.5.2 Measurement Technique of the Negative Capacitance.             | 134    |

| 7.5.3 Variation of a Negative Capacitance with Voltage.              | 135    |

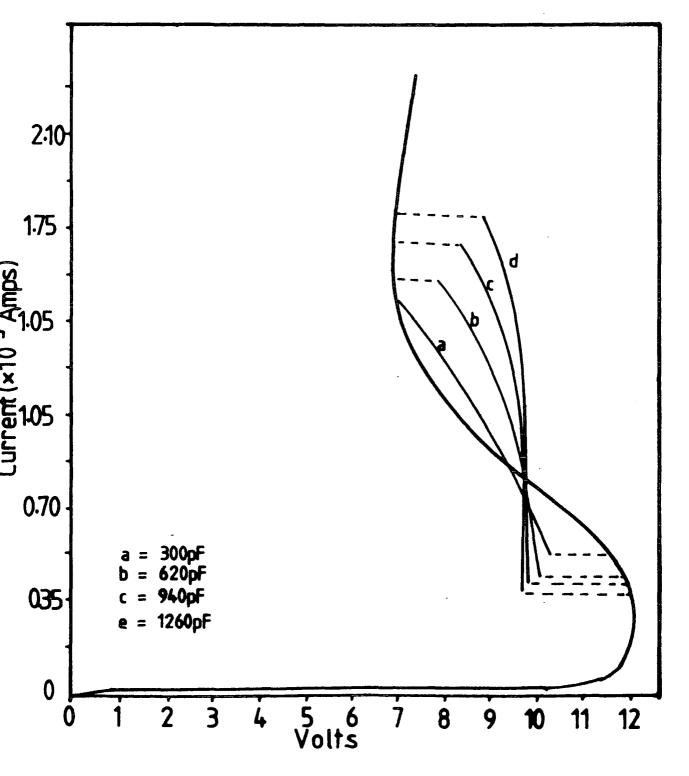

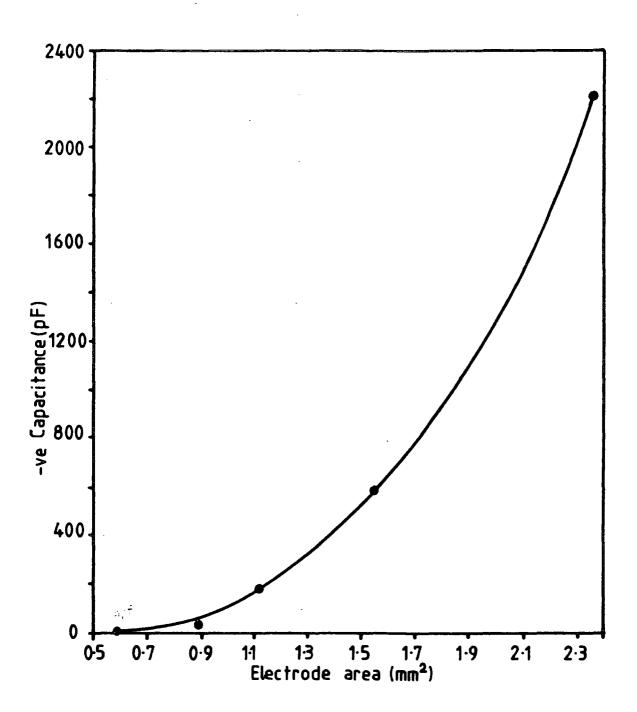

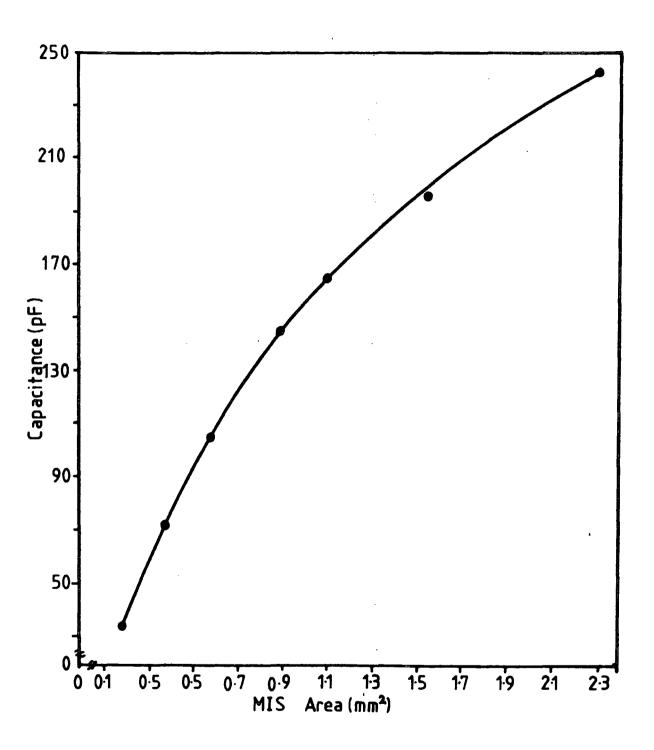

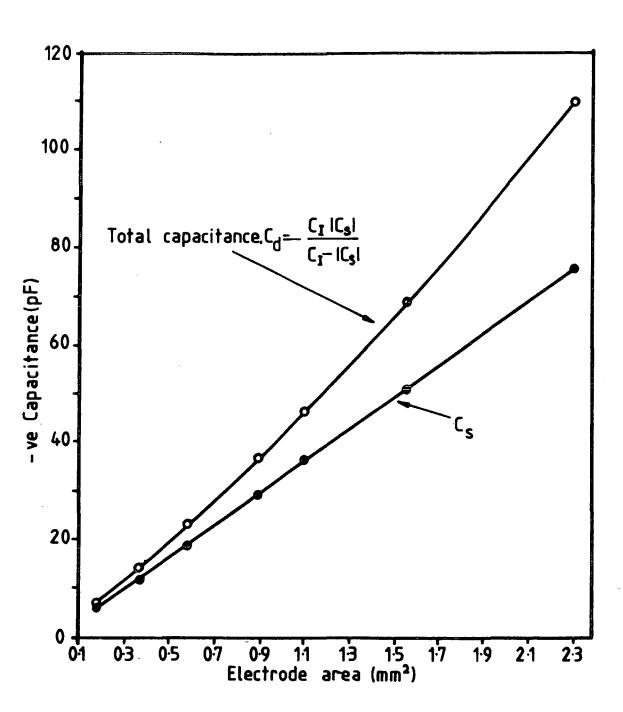

| 7.5.4 Effect of Electrode Area on Negative Capacitance.              | 137    |

| 7.5.5 Effect of SRO Type on Negative Capacitance.                    | 139    |

| 7.5.6 Effect of Light Illumination on Negative Capacitance.          | 139    |

| 7.6 MOS Circuit Applications of Negative Capacitance MISS Devices.   | 140    |

| 7.6.1 Introduction.                                                  | 140    |

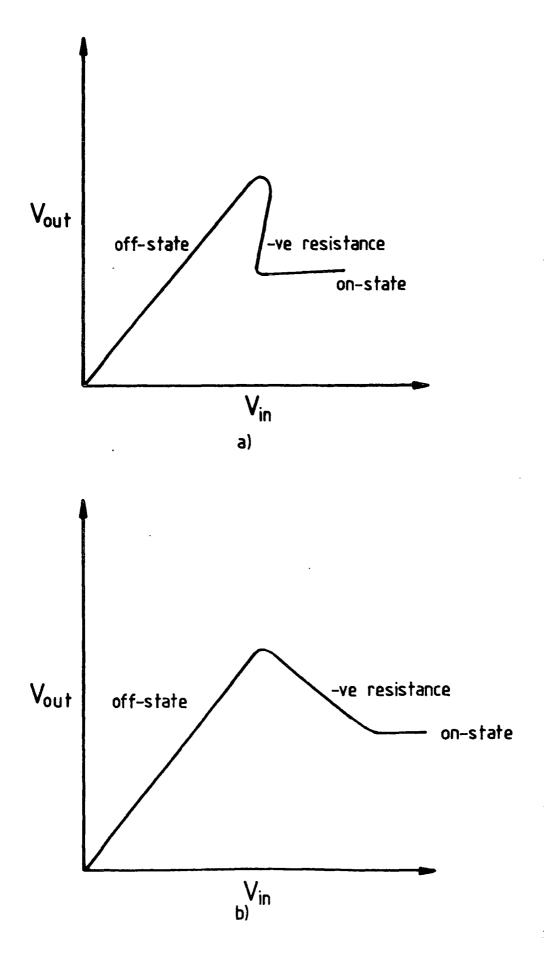

| 7.6.2 Negative Resistance Load Line.                                 | 141    |

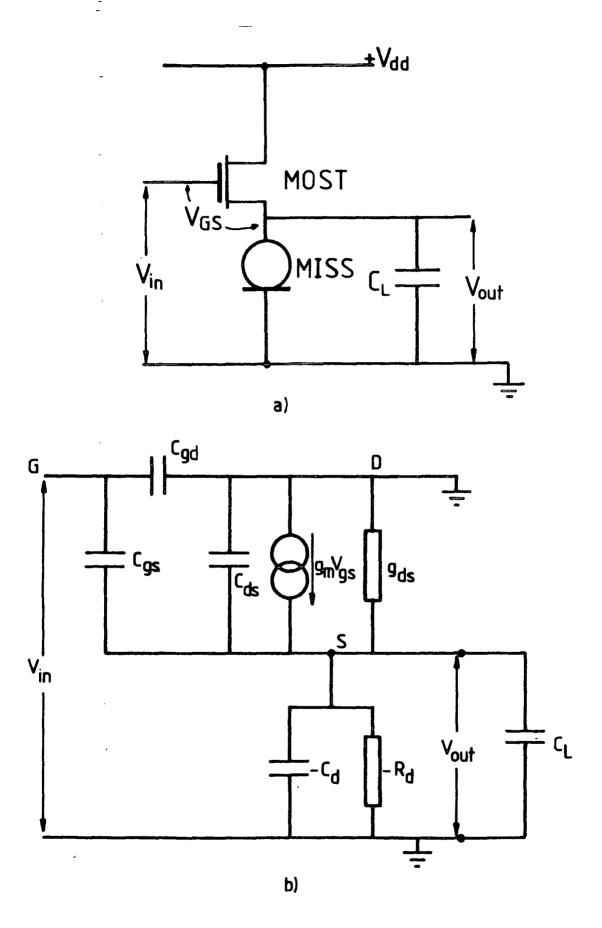

| 7.6.2.1 MOSMISS Common Source Configuration.                         | 141    |

| 7.6.2.2 MOSMISS Common Drain Configuration.                          | 142    |

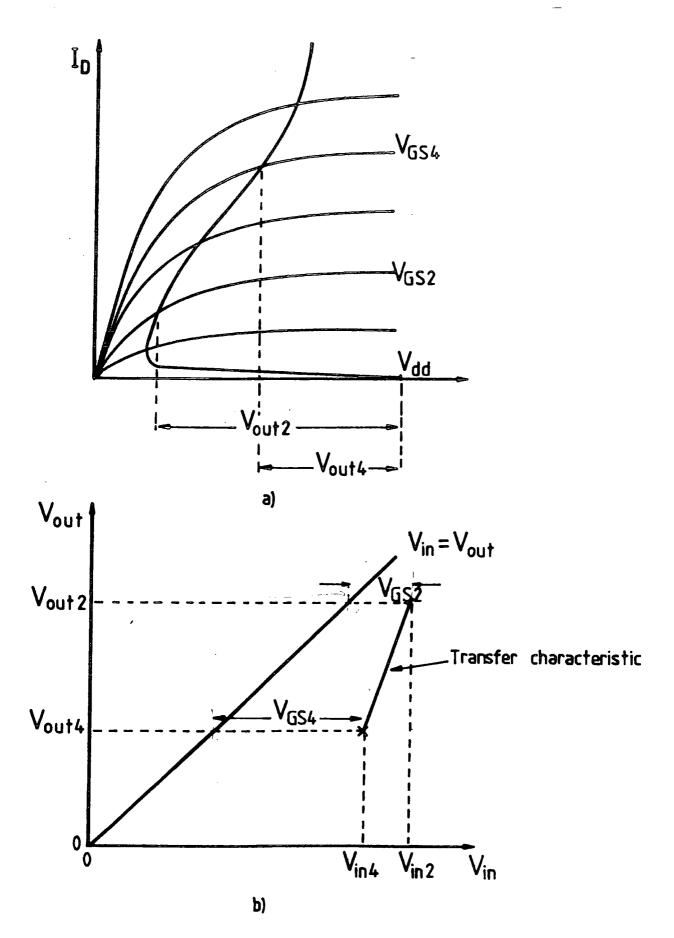

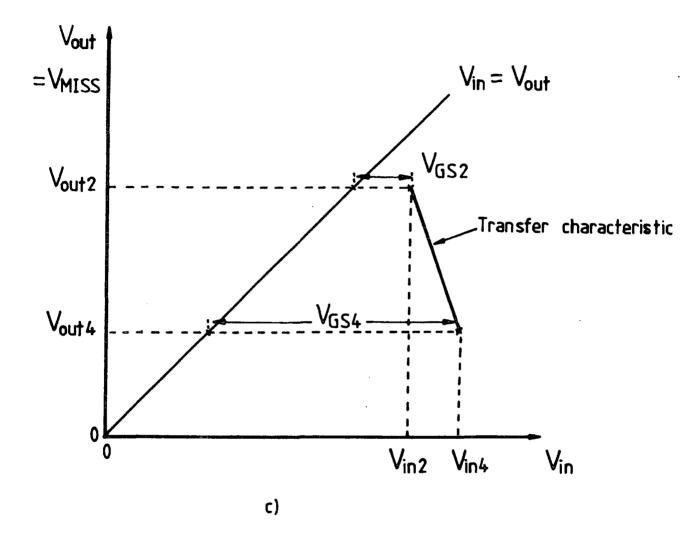

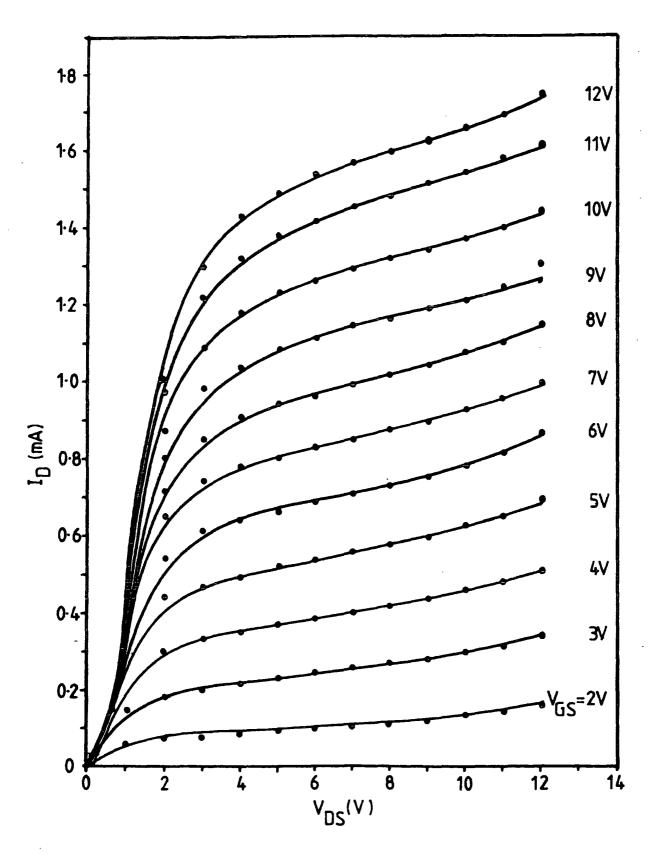

| 7.6.3 Graphical Analysis of a Negative Resistance Load Line.         | 142    |

| 7.6.4 Results and Discussion.                                        | 144    |

| 7.7 Summary.                                                         | 146    |

| References.                                                          | 148    |

| CHAPTER 8 CONCLUSION AND SUGGESTIONS FOR FURHER WORK.     | 150 |

|-----------------------------------------------------------|-----|

| 8.1 Summary of Results.                                   | 150 |

| 8.2 Suggestions for further work.                         | 153 |

| APPENDIX A                                                | 157 |

| Tunnelling Between Metal and Semiconductor.               | 157 |

| APPENDIX B                                                | 159 |

| B.1 Cleaning Procedure for Silicon.                       | 159 |

| B.2 Deposition Procedure for CVD Reactor.                 | 166 |

| B.3 Lapping the Back of the Sample.                       | 162 |

| APPENDIX C                                                | 164 |

| Listing of Computer Program for the Automated Measurement |     |

| System.                                                   |     |

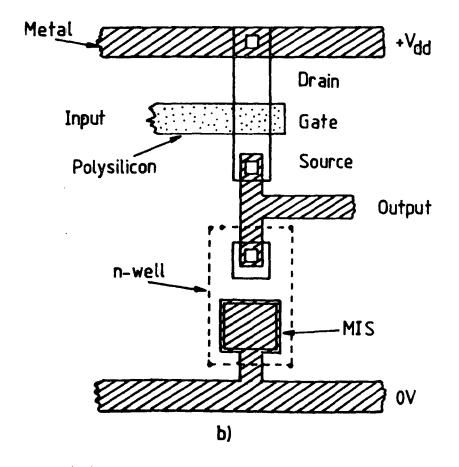

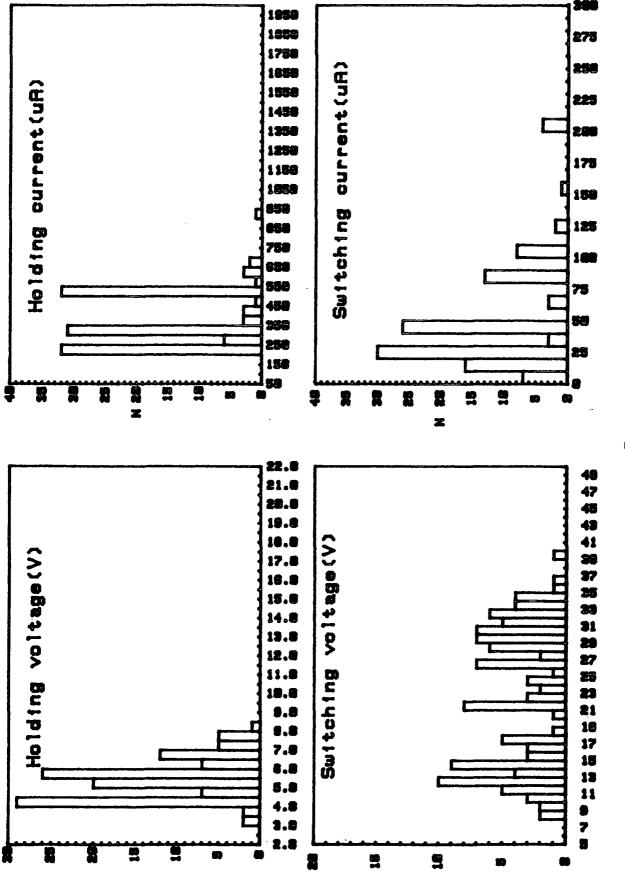

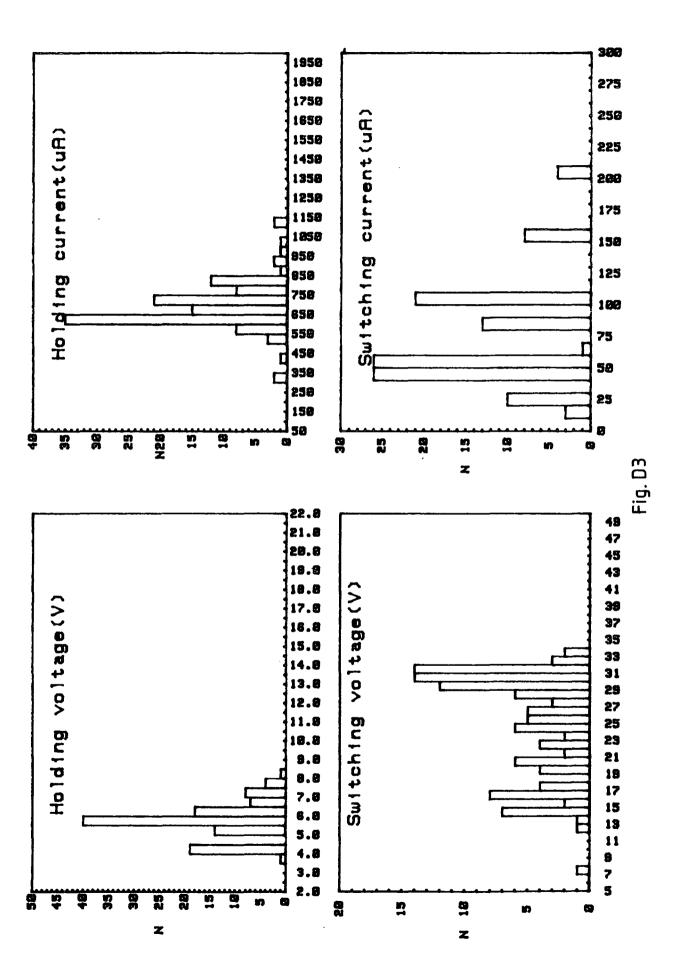

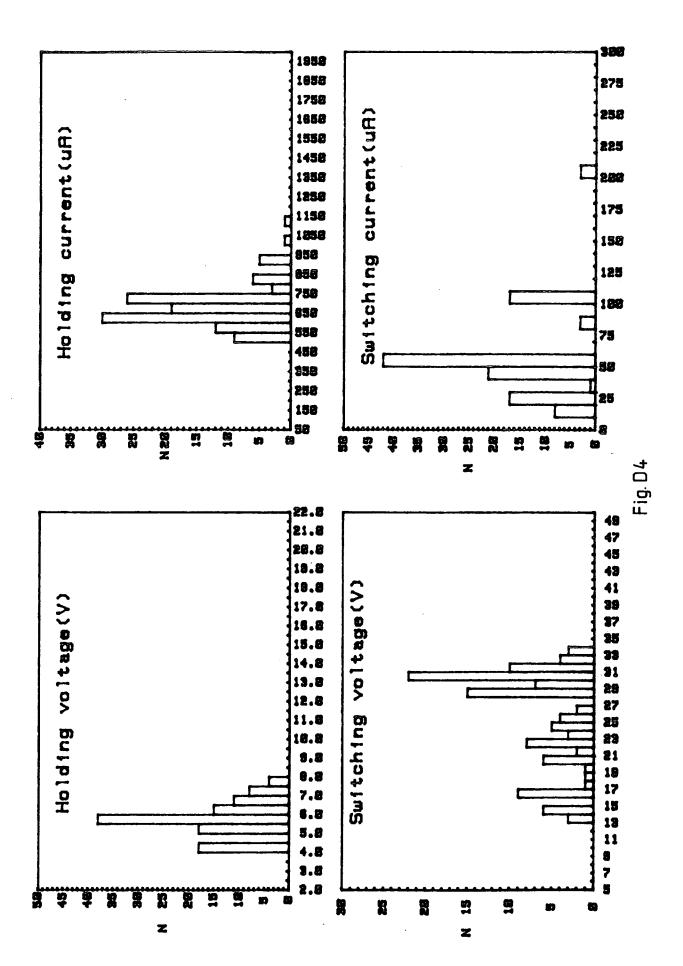

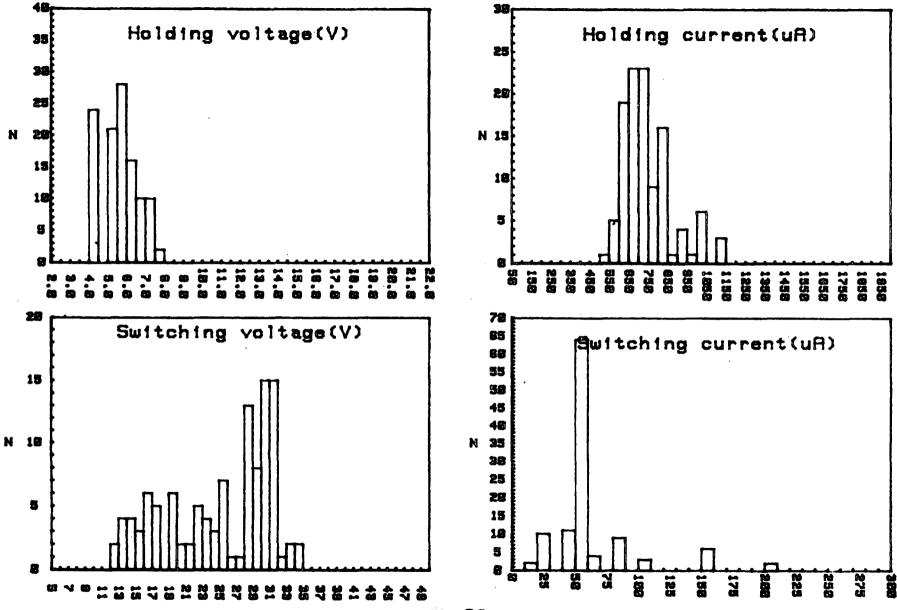

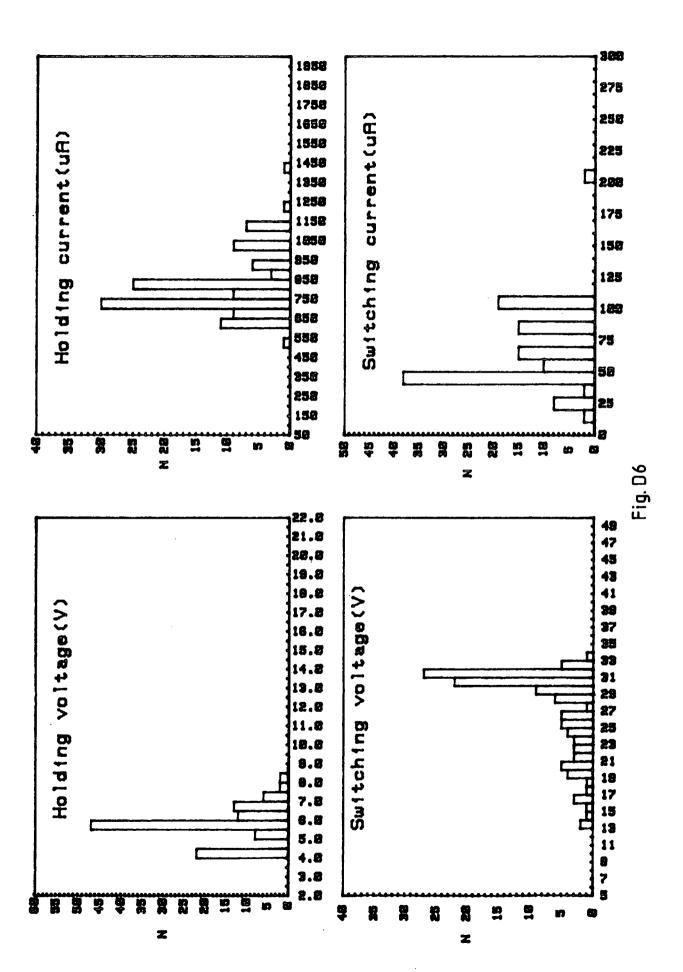

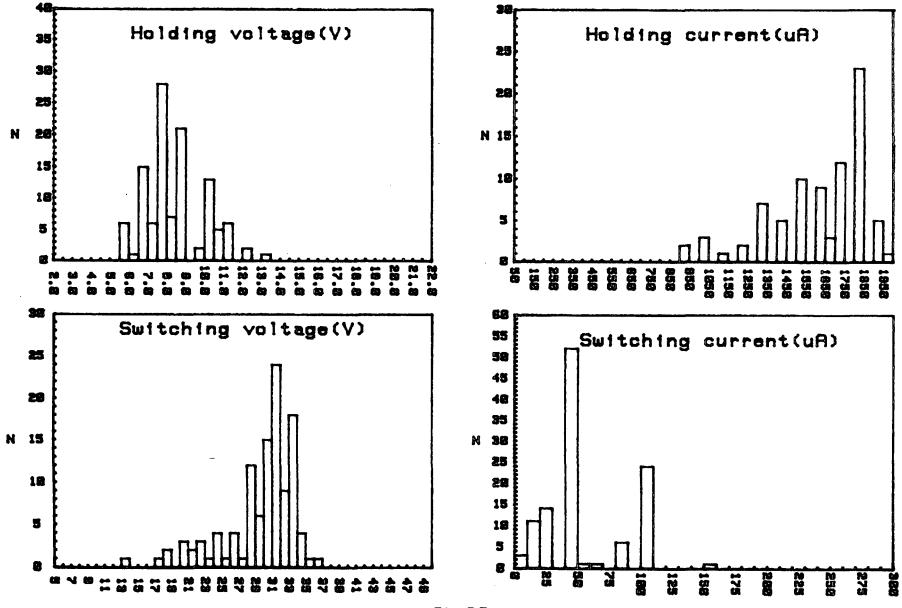

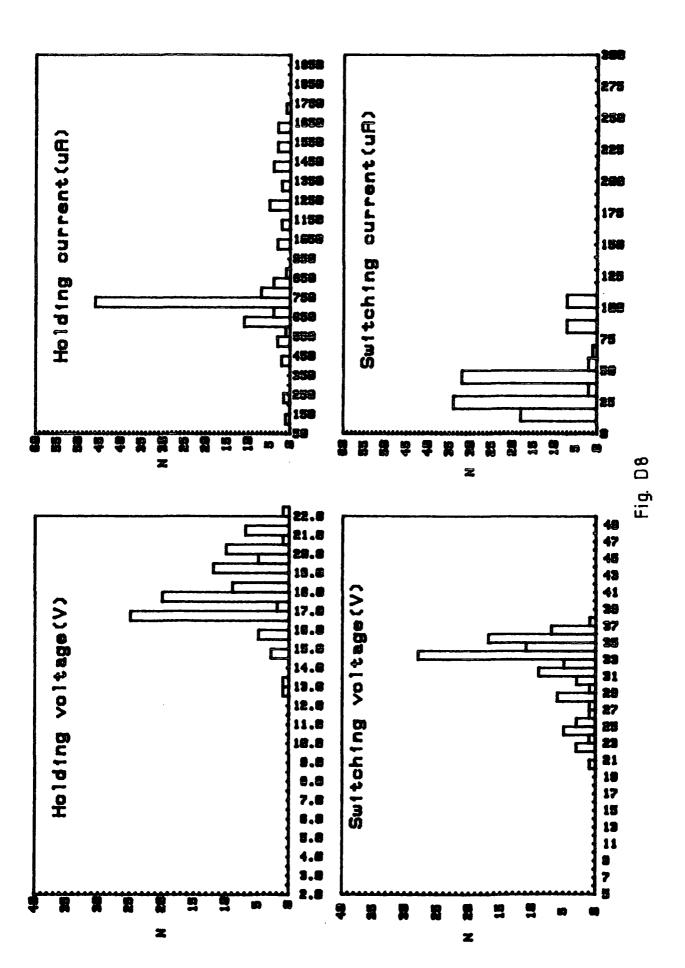

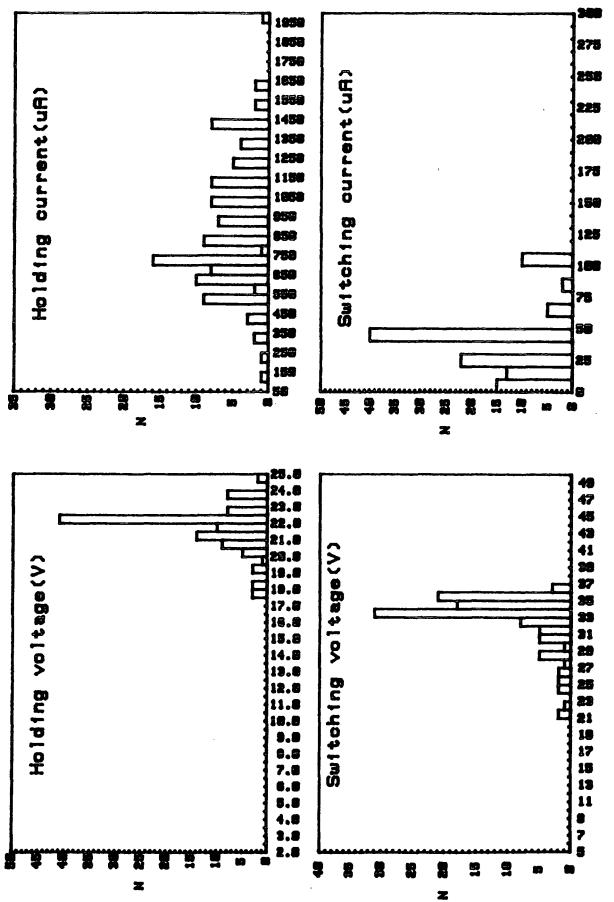

| APPENDIX D                                                | 165 |

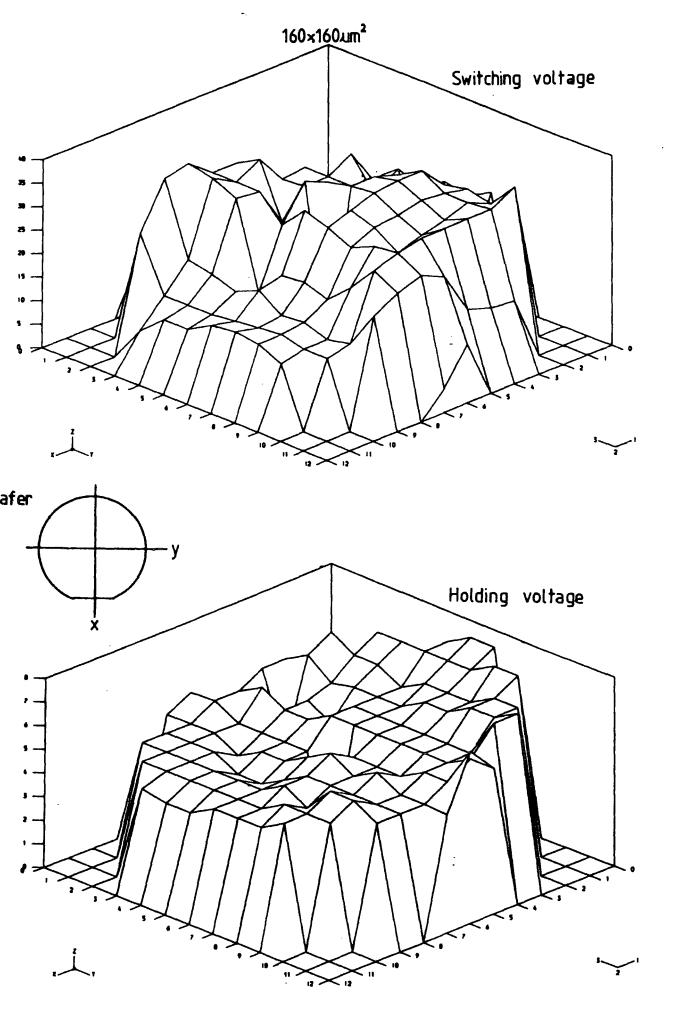

| Statistical Result of Switching Parameters                |     |

| for the Small Device.                                     |     |

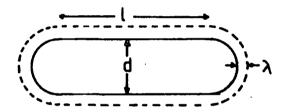

| APPENDIX E                                                | 166 |

| Variation of Spreading Area with Electrode Perimeter.     |     |

| APPENDIX F                                                | 167 |

| Stability of a Circuit Containing Negative Resistance.    |     |

# CHAPTER ONE

# INTRODUCTION

# 1.1 SEMICONDUCTOR DEVICE STRUCTURES

In general semiconductor devices can be classified into two classes, bulk effect and junction (or interface) effect devices. The former are related to the properties of the homogeneous semiconductor, and the latter can be divided in two groups depending on the number of junctions in the device. A single junction device consists of a two layer structure such as the p-n diode, Schottky diode, tunnel diode etc. and a multiple junction device comprises at least a three layer structure such as metal insulator semiconductor diode, junction transistor, p-n-p-n diode etc. This thesis is concerned with a multiple junction device with a four layer structure part of which is a metal insulator semiconductor diode.

# 1.2 THE MISS STRUCTURE

# 1.2.1 Review of MISS Characteristics

The Metal-Insulator(tunnel)-n-p<sup>+</sup> structure has long been known as a switching device, called a Metal-Insulator-Semiconductor-Switch (MISS). Some investigators have called it a Controlled Inversion Device (CID), because its operation is governed by the formation of an inversion layer at the insulator-semiconductor interface. These devices have three regions in their current-voltage characteristics, a high impedance

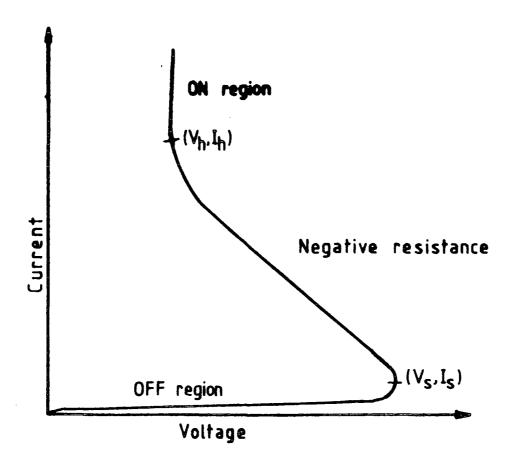

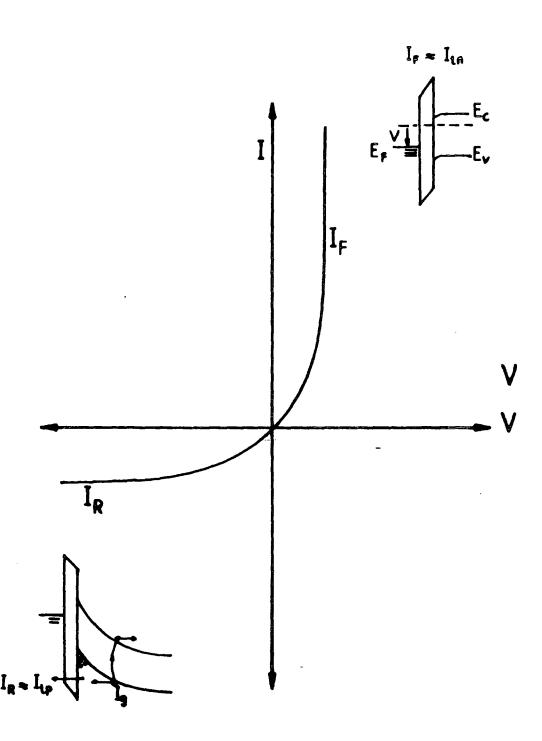

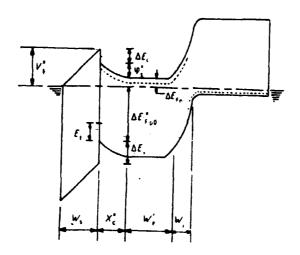

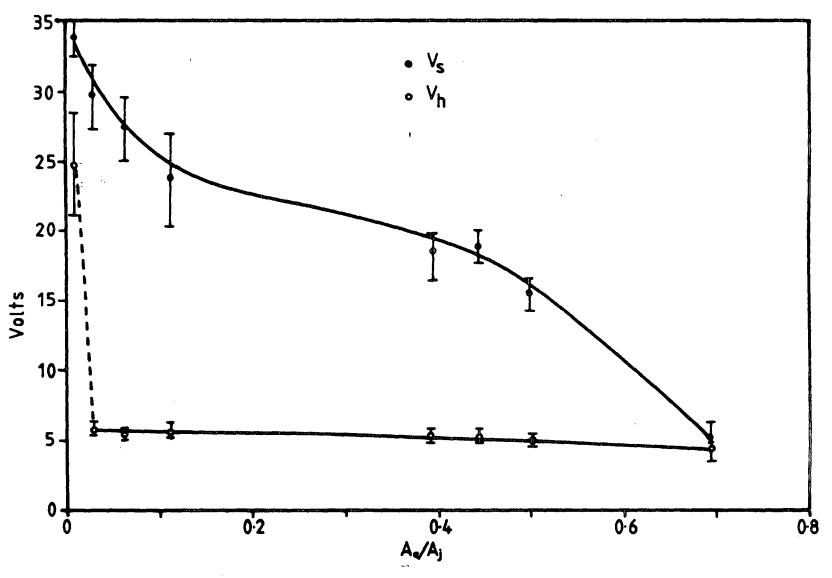

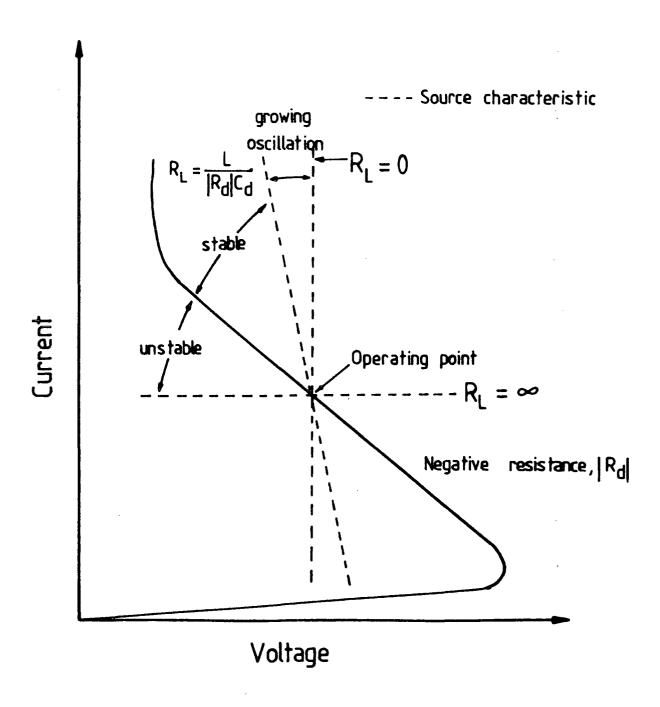

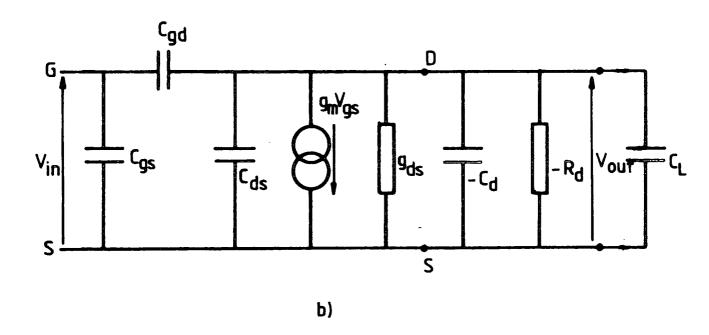

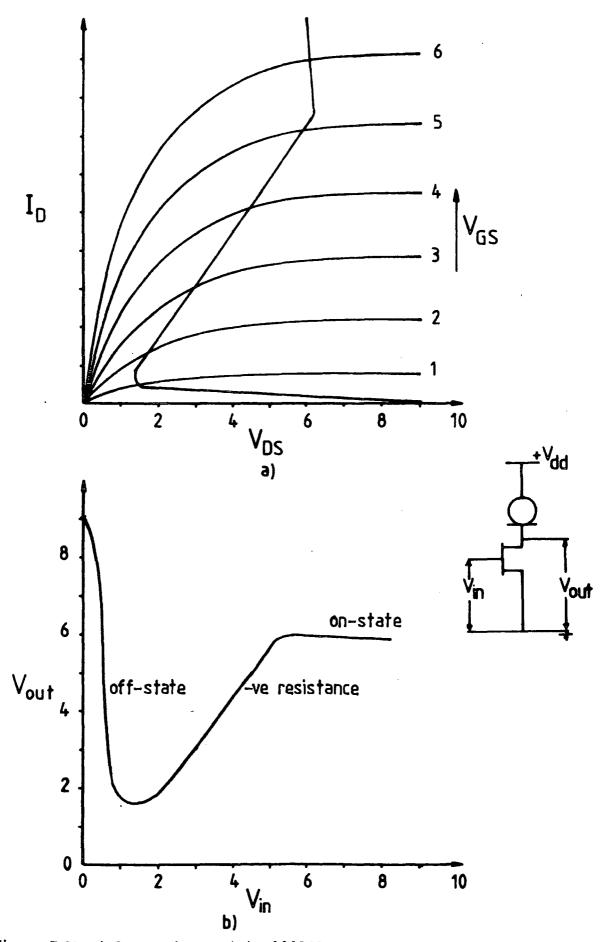

(OFF state)†, a negative resistance region and low impedance (ON state)‡ as shown in figure 1.1. The current and voltage at which the device begins to switch from the high resistance state to the low resistance state are called the switching current  $(I_s)$  and switching voltage  $(V_s)$ . The minimum current to sustain the device in the low impedance state is called the holding current  $(I_h)$ , and the voltage at this point is called the holding voltage  $(V_h)$ .

The negative resistance region is generally regarded as an unstable region in which there is no operating point that is stable with time. This characteristic is similar to that of the p-n-p-n Shockley diode or thyristor, but the physics of the operation is quite different. The MISS device also has a higher switching speed compared to the p-n-p-n diode, and switching times of less than 10ns have been reported [1,4]. The fabrication technology of these two devices is also very different, and MISS devices have better compatibility with standard IC fabrication.

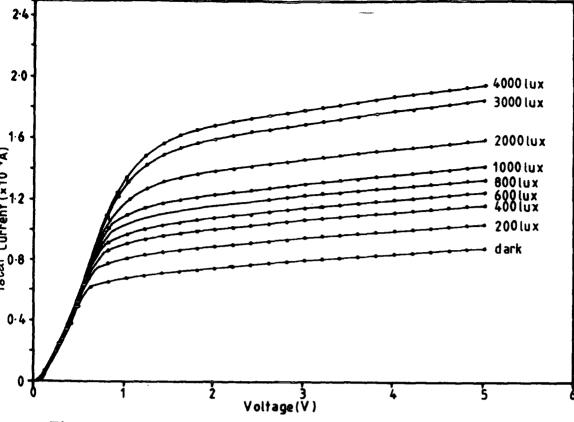

These features have given rise to potential applications of the MISS as an integrated circuit component, such as a memory cell [2,8], a shift register cell [4], a comparator, monostable or astable multivibrator [10]. The device has also been found to be sensitive to light, and hence it can be used as an optical switch [4] in digital optical communication systems. The switching of the MISS device with palladium as the metal electrode has been found to be sensitive to hydrogen, so that can be used in an alarm system for hydrogen leakage [13].

# 1.2.2 Device Structure and Material

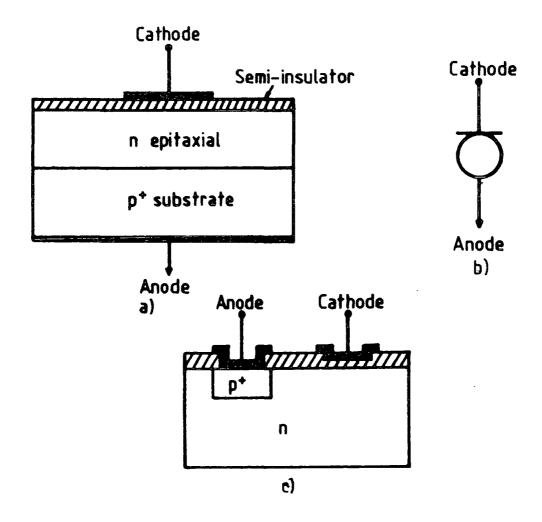

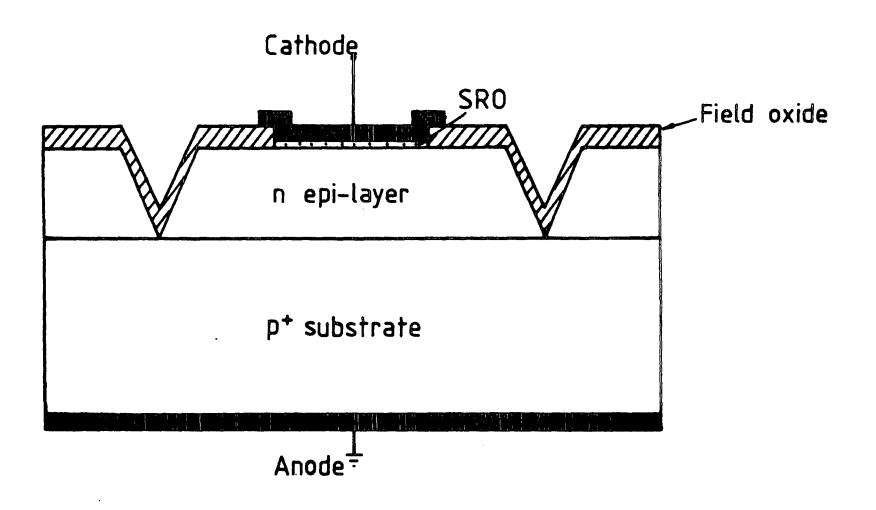

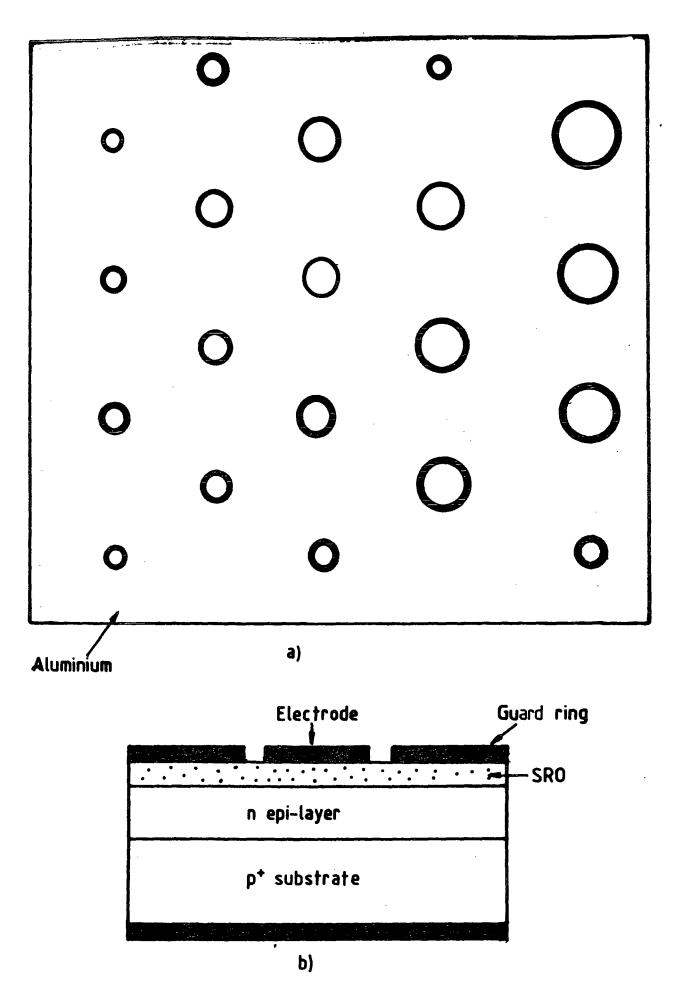

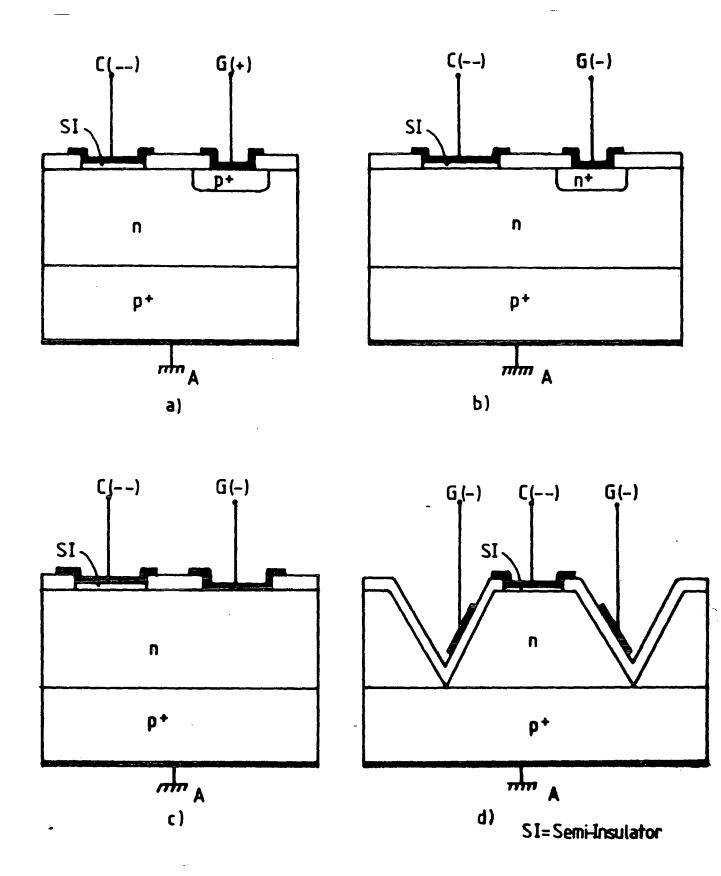

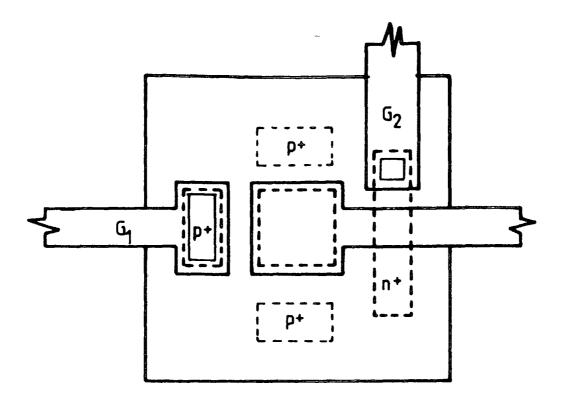

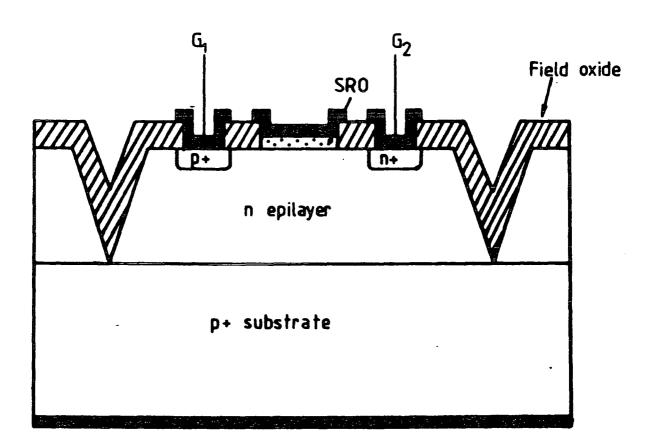

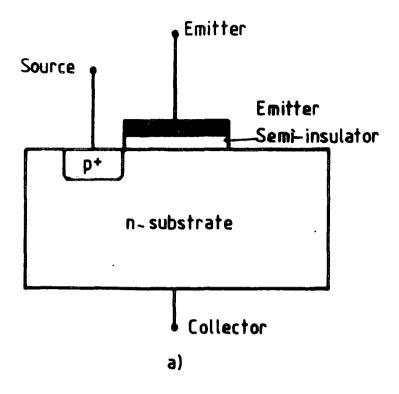

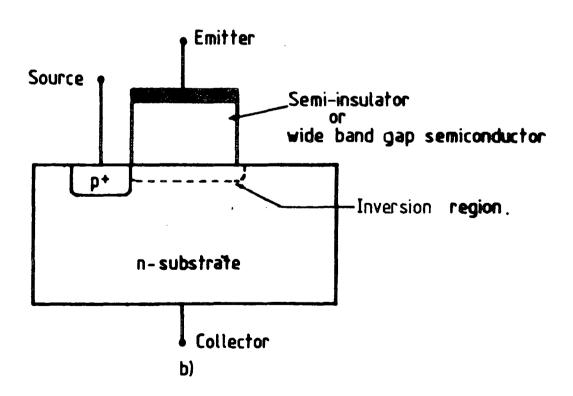

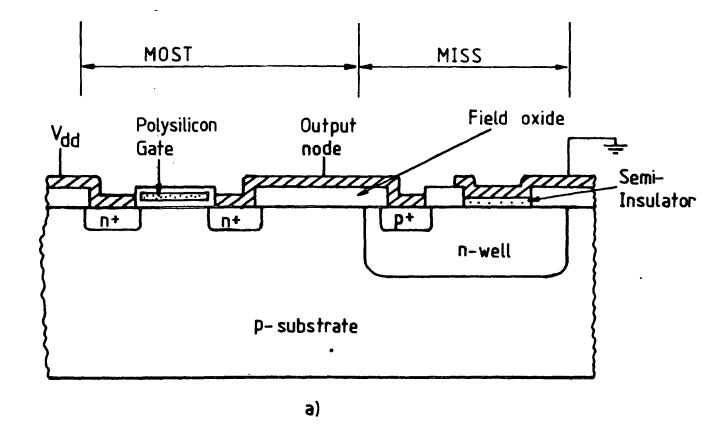

The basic structure of the MISS device is shown in figure 1.2(a), and the symbol which is normaly used for the device is in figure 1.2(b). The device consists of an MIS

<sup>†</sup> A resistance of the order of  $500k\Omega - 10M\Omega$

<sup>‡</sup> A resistance of the order of  $10\Omega - 500\Omega$

Figure 1.1 Current-voltage characteristics of MISS device.

Figure 1.2 a) Basic structure of MISS device.

b) Symbol for MISS device. c) Lateral Miss device

tunnel diode backed by a p-n junction. The p-n junction can be either n-p<sup>+</sup> or p-n<sup>+</sup>, where the n or p layer is often an epitaxial film. A MISS device can also be made in a lateral form as shown in figure 1.2(c) [16,17]. Most of the research on MISS devices has been based on silicon as the semiconductor. However switching has also been reported for a GaAs MISS [4,12]. Metals such as aluminium, gold and molybdenum [1,4] may be used as the top electrode.

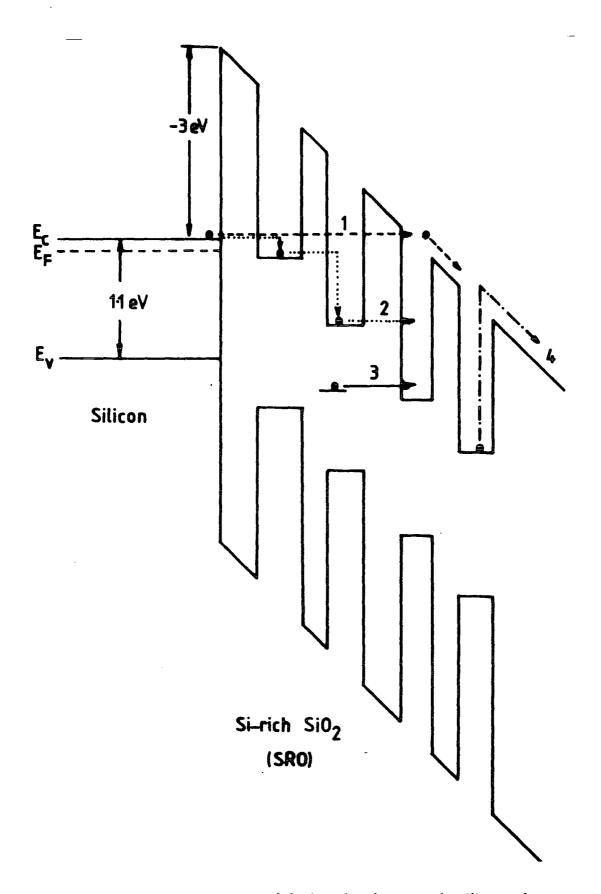

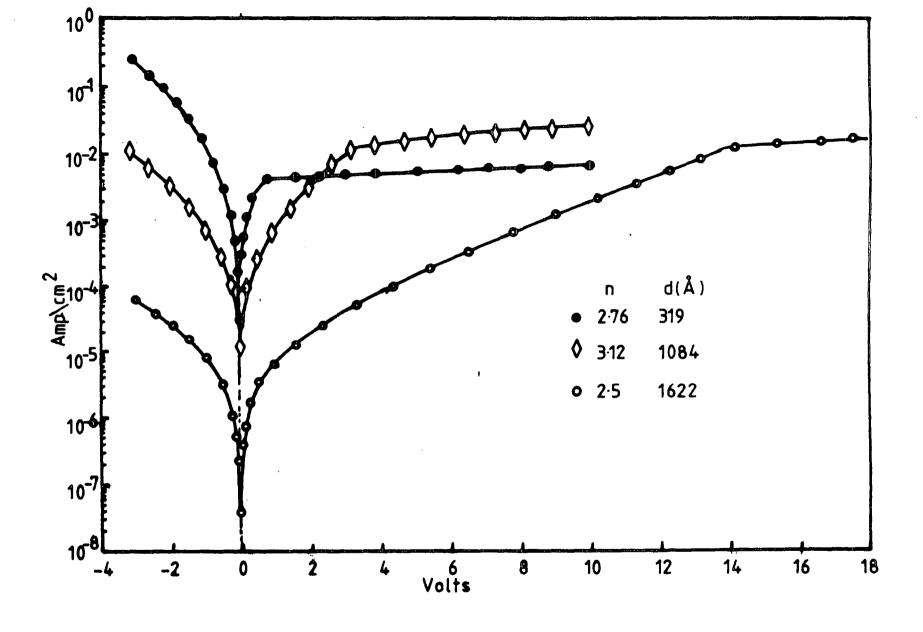

In most of the previous research that has been done, a thin silicon dioxide film (thickness  $< 50\mathring{A}$ ) has been used as a tunnel insulator in the MISS device [1-5,8,11,13]. The conduction of the semi-insulating film has been found to have a considerable effect on the electrical characteristics of the MISS. The conduction of the layer can be controlled by changing the thickness, as is the case for silicon dioxide, or the material. However it is very difficult to control the thickness of silicon oxide, typically a few tens of Ångström sufficiently accurately. Hence, thicker and less insulating materials become of interest. Semi-insulating materials like silicon nitride [5,6], silicon-rich-silicon-nitride, and polycrystalline silicon (1000 – 2000 $\mathring{A}$ ) [7,10,11] and organic films deposited by the Langmuir-Blodgett technique [12], have been found to give similar switching characteristics in MISS devices. For the present study silicon-rich silicon oxide (SRO) was used as the semi-insulator.

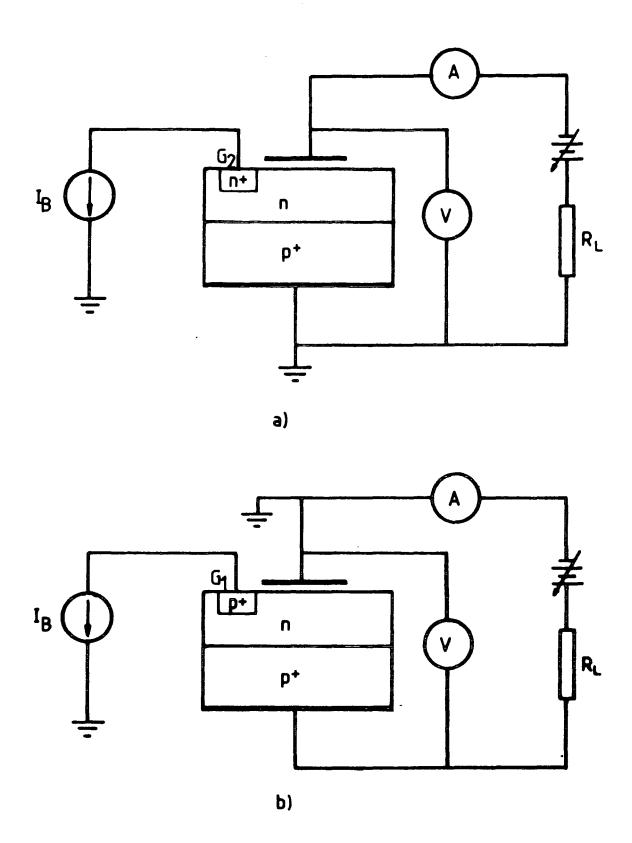

Instead of a p-n junction, a Schottky barrier can be used as a minority carrier injector in the four-layer structure, and this gives rise to a new form of device called MISM for Metal - Insulator - Semiconductor - Metal [9,10,11]. As an extention to this idea, a second MIS diode has also been used as an injector to form a bidirectional switching device, MISIM [14,15]. The switching voltage  $V_s$  of any of these devices can be controlled by a third terminal. For the MISS, injecting or extracting current through the third terminal controls  $V_s$ , and the device structure is then called a Metal - Insulator - Semiconductor - Thyristor (MIST). However the difference compared

with a thyristor is that the switching voltage of the MIST can be increased above, or reduced below the intrinsic switching voltage, depending upon the polarity of the gate voltage.

# 1.3 OBJECTIVE AND THESIS OUTLINE

The objective of this thesis is to study experimentally the electrical characteristics of MISS devices made with SRO as the semi-insulating layer. At the begining of the research SRO had not been used previously in MISS devices but very recently a paper on this has been published [19]. Ever since tunnel oxide MISS device was discovered in 1972 by Yamamoto and Morimoto, almost all the experimental and theoretical investigations by other workers have concentrated on the switching characteristics of the device [2-15], and only very little has been reported [11] about its electrical behaviour in the negative resistance region. In this work we are concerned particularly with the negative resistance region.

The overall work presented in this thesis is deliberately wide and exploratory rather than analytical. This is because it is necessary in investigating a new device to find out first which characteristics are likely to be of use in electronic circuits and to concentrate later on the detailed modelling of the most important ones. Therefore all the electrical characteristics of the MISS with two and three terminals were studied. In Chapter 2 the fundamental device theories which are related to the operation of MISS devices are reviewed. The physical operation of the MISS itself is discussed in detail in Chapter 3. The device fabrication and measurement techniques used in the present work are presented in Chapter 4. The magnitude of the negative resistance of the device is strongly related to  $V_s$ ,  $V_h$ ,  $I_s$ , and  $I_h$ , and experimental results on these switching parameters are presented in Chapter 5. This chapter also contains the experimental results for geometrical effects in the device, and for the effect of

SRO type, gold doping, etc. The dynamic behaviour of the MISS is also studied. In Chapter 6 the switching and transistor characteristics of three terminal MISS devices are presented. A new phenomenon is also reported in this chapter.

A negative capacitance in the MISS device has been reported by Millan et al. [18]. The total capacitance was found to decrease sharply and reach a negative value as the dc bias increases in the high impedance state, the capacitance becoming negative before the switching process takes place. They explained this behaviour as due to the interaction of the carriers with the interface states at the insulator-semiconductor interface and the influence of the electric field on the tunnelling emission rate of these states. In the present work an entirely different type of negative capacitance has been discovered. To the best of our knowledge, the capacitance in the negative resistance region has never been measured previously probably because of circuit instability when one tries to bias the device in this region. In Chapter 7 the stability condition of a circuit containing a negative differential resistance is discussed, and we also present experimental evidence to show that the device does indeed have a negative capacitance as a consequence of its stable S-type negative differential resistance. Later in this chapter we demonstrate how such a negative capacitance device can be used in electronics. It appears to have many potential applications in a digital integrated circuits.

Finally in Chapter 8 we conclude the thesis with a summary of the experimental results and make suggestions for future work in this field with emphasis on the negative capacitance and its application.

#### REFERENCES FOR CHAPTER 1

- [1] T. Yamamoto and M. Morimoto, Thin-MIS-Structure Si Negative-Resistance Diode, Appl. Phys. Lett. 20, pp.269-270 (1972).

- [2] A. El-Badry and J.G. Simmons, Experimental Studies of Switching in Metal Semi-Insulating n-p<sup>+</sup> Silicon Devices, Solid State Electronics, 20, pp.963-966 (1977).

- [3] J. Buxo, A. E. Owen, G. Sarrabayrouse and J. P. Sebaa, *The Characterisation of Metal-Thin Insulator-n-p*<sup>+</sup> Silicon Switching Devices, Revue de Physique Appliquée, **13**, pp.767-770 (1978).

- [4] T. Yamamoto, K. Kawamora and H. Shimizu, Silicon p-n-Insulator- Metal (p-n-I-M) Devices, Solid State Electronics, 19, pp.701-706 (1976).

- [5] H. Kroger and H. A. R. Wegener, Bistable Impedance States in MIS Structures Through Controlled Inversion, Appl. Phys. Lett., 23, pp.397-399 (1973).

- [6] Chang-Yuan Wu, Yuan-Tunges Huang, The Metal Insulator- Semiconductor-Switch (MISS) Device using Thermal Nitride Film as the Tunneling Insulator, Solid State Electronics, 27, pp.203-206 (1984).

- [7] J. Martinez and J. Piqueras, Switching Characteristics of Polysilicon MISS Devices, Solid State Electronics, 27, pp.937-944 (1984).

- [8] K. C. Chick and J. G. Simmons, Characteristics of Three-Terminal Metal-Tunnel Oxide-n-p<sup>+</sup> Devices, Solid State Electronics, 22, pp.589-594 (1979).

- [9] M. Darwish and K. Board, Switching in M.I.S.M. Structures, IEE Proc., 127, Part I, No.6, pp. 317-322 (1980).

- [10] M. N. M. Darwish, Metal- Insulator- Semiconductor and Semiconductor- Barrier Two-State Devices and their Application, PhD Thesis, University of Wales, (1981).

- [11] H. Kroger and H. A. R. Wegener, Steady-State Characteristics of Two Terminal Inversion-Controlled Switches, Solid State Electronics, 21, pp.643-654 (1978).

- [12] N. J. Thomas, GaAs/Langmuir Blodgett Film MIS Devices, PhD Thesis, University of Durham, (1986).

- [13] K. Kawamura, T. Yamamoto, Hydrogen-Sensitive Silicon Tunnel MIS Switching Diodes, IEEE Electron Device Lett., EDL-4, pp.88-89 (1983).

- [14] M. Darwish and K. Board, Experimental Observation of Switching in MISM and MISIM Devices, IEE Proc., 128, Part I, No.5, pp.161-164 (1981).

- [15] M. Darwish and K. Board, Theory of Switching in MISIM Structures, IEE Proc., 128, Part I, No.5, pp.165-173 (1981).

- [16] A. G. Nassibian, A New MOS Type Metal Tunnel Oxide Silicon Switch (MOSMISS), IEEE Electron Device Lett., EDL-1, pp.67-68 (1980).

- [17] P. Clifton, Private Communication, University of Durham, (1986).

- [18] J. Millan, V. Villaronga, J. R. Morante, F. Serra-Mestres and A. Herms, Negative Capacitance in Switching MISS Devices, Physica, 129B, pp.351-355 (1985).

- [19] M. J. B. Bolt, J. G. Simmons, G. W. Taylor and C. Zimmerman, Experimental and Theoretical Electrical Characteristics of Metal-SIPOS-n-p<sup>+</sup> Structures, Semicond. Sci. Technol. 2, pp.666-674 (1987).

# CHAPTER TWO

# THEORETICAL CONCEPTS FOR MISS DEVICES

# 2.1 INTRODUCTION

Although this thesis is largely concerned with the experimental electrical characteristics of MISS devices, it is essential to understand the background physics which is of relevance to the device operation in order to explain the results. The MIS and p-n junction diodes are the two components which are inherent in the operation of the MISS device. This chapter is therefore devoted to a review of the device physics of the MIS structure and of the p-n junction.

#### 2.2 THE MIS DIODE

#### 2.2.1 The Ideal MIS Diode

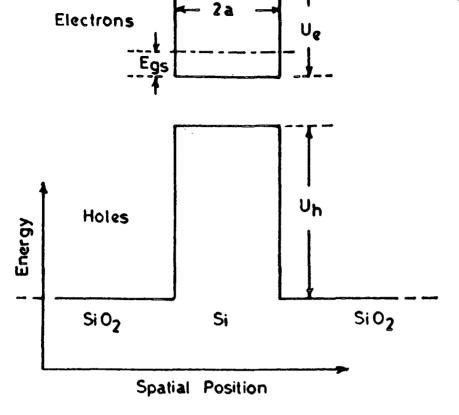

The Metal-Insulator-Semiconductor (MIS) structure was first proposed by Moll in 1959 as a variable capacitor [1], but it is now a fundamental element in microelectronic devices such as the MOS transistor, and the charge-coupled device (CCD). This structure is also used as a tool to study the properties of insulating films. MIS systems with an oxide insulator can be classified into three different types depending upon the thickness of the insulator layer. 1) If the insulator thickness large  $(d > 50\text{\AA})$  the system behaves purely as an MIS capacitor. 2) If the insulator thickness is very low  $(d < 10\text{\AA})$ , the system behaves as a Schottky diode. 3) For intermediate insulator thickness  $(10\text{\AA} < d < 50\text{\AA})$  this structure is called an MIS tunnel diode and it

behaves like a leaky capacitor. For other semi-insulating materials the conductivity of the film must also be taken into consideration.

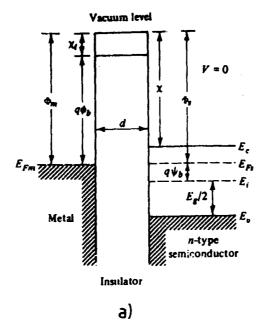

The electronic mechanism of an MIS system can best be explained by using energy band-diagrams. Depending on the applied voltage between the metal and the semiconductor, the energy bands take on one of three different conditions: accumulation, depletion, and inversion. For simplicity we will first consider the ideal MIS system with an n-type semiconductor.

At zero applied voltage, the energy band structure is shown in figure 2.1(a). The work function difference between the metal and the semiconductor is given as,

$$\phi_{ms} = \phi_m - \phi_s = 0 \tag{2.1}$$

$$\phi_{ms} = \phi_m - (\chi + \frac{E_g}{2} - q\psi_b) = 0 2.2$$

where

$\phi_{ms} = \text{work function difference in eV}$

$\phi_s = \text{ semiconductor work function in eV}$

$\chi =$  semiconductor electron affinity in eV

$E_g = \text{semiconductor bandgap energy in eV}$

$\psi_b$  = potential difference between the Fermi level and the intrinsic Fermi level  $\frac{E_F - E_i}{a}$

Since we assume that the system is ideal, the metal work function,  $\phi_m$ , and the semiconductor work function,  $\phi_s$ , are equal, and the metal-semiconductor work function difference,  $\phi_{ms} = 0$ . At zero applied voltage the energy bands are therefore flat, and as a result, the dc current through the structure is zero. Under this condition, the flat band voltage,  $V_{FB}$ , is said to be zero.

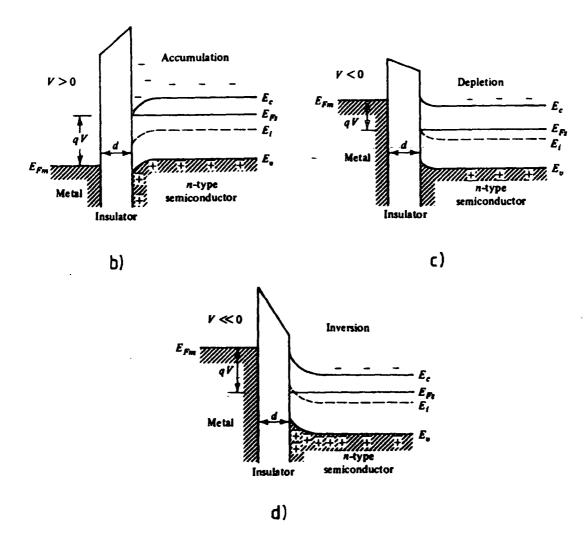

Figure 2.1 Energy band diagram of the MIS, a) at zero bias, b) forward bias, c) reverse bias (depletion), d) reverse bias inversion.

Under steady-state bias, the MIS system is considered to be in equlibrium and the applied potential is dropped partly across the insulator and partly in the semiconductor. The concentration of both electrons and holes in the semiconductor can be expressed as a function of electrical potential,  $\psi(x)$ , which is taken to be zero in the bulk. For an n-type semiconductor the electron and hole concentrations are therefore given by,

$$n_n = n_{n0} \exp\left[\frac{q\psi(x)}{kT}\right]$$

and  $p_n = p_{n0} \exp\left[\frac{-q\psi(x)}{kT}\right]$  2.3

where  $n_{n0}$  and  $p_{n0}$  are the equlibrium bulk concentrations of the majority and minority carriers respectively.

When a positive voltage (forward bias) is applied to the metal of the ideal MIS diode, (figure 2.1(b)), the metal Fermi level is lowered with respect to the semiconductor, and the energy bands at the surface of the semiconductor bend downwards. The band bending causes an accumulation of majority carriers (electrons) near the semiconductor surface, and this condition is known as accumulation.

When a small negative (reverse bias) is applied, as shown in figure 2.1(c), the negative charge on the metal repels the negative charges (electrons) in the semiconductor. As a result the semiconductor bands bend upwards and a region depleted of majority carriers is formed between the semiconductor surface and the bulk. The potential at the semiconductor-insulator interface relative to the bulk is known as the surface potential,  $\psi_s$ , and, it can be expressed in terms of the depletion width,  $X_d$ , by [4],

$$\psi_s = \frac{qN_dX_d^2}{2\epsilon_s} \tag{2.4}$$

where  $\epsilon_s$  and  $N_d$  are the semiconductor permittivity and donor concentration per cm<sup>3</sup> respectively.

If the negative voltage applied to the metal of the MIS diode is increased, the band bends even further upwards as shown in figure 2.1(d) where the intrinsic Fermi level  $E_i$  crosses the Fermi level  $E_F$  at the surface. As a result, the concentration of minority carriers(holes) at the surface becomes greater than that of the majority carriers(electrons), and this situation is known as *inversion*. The MIS is said to be in *strong inversion*, if the intrinsic Fermi level  $E_i$  at the surface is above  $E_F$  by an amount  $\psi_b$ , where  $\psi_b$  is the potential between the Fermi level and the intrinsic Fermi level in the bulk. The condition for strong inversion can be expressed as,

$$\psi_s(\text{inv}) = 2\psi_b \tag{2.5}$$

which can be written as,

$$\psi_s(\text{inv}) = 2\frac{kT}{q} \ln \frac{N_d}{n_i}$$

2.6

When strong inversion occurs, the depletion layer width reaches its maximum value. A further increase in voltage in the semiconductor is prevented by the increase in the number of holes in the inversion layer. The maximum width of the depletion layer,  $X_{d_{max}}$  can be derived from equation 2.4 and 2.6, and is given by,

$$X_{d_{max}} = \sqrt{\frac{4\epsilon_s kT \ln(N_d/n_i)}{q^2 N_d}}$$

2.7

Therefore, at a constant temperature the maximum depletion width decreases with an increase in the impurity concentration,  $N_d$ .

#### 2.2.2 The Non-Ideal MIS Diode

A real MIS diode differs from the ideal in several ways. Firstly for the non-ideal MIS diode the work function difference,  $\phi_{ms}$  is not zero and, as a results a voltage equal to  $V_{FB}(=\phi_{ms})$  would have be applied to get to the flat band condition. In addition to that, the presence of fixed surface charge in the insulator also modifies the value of  $V_{FB}$ . If the fixed charge density is  $Q_f$  per unit area, then,

$$V_{FB} = -\frac{Q_f}{C_i} + \phi_{ms} \tag{2.8}$$

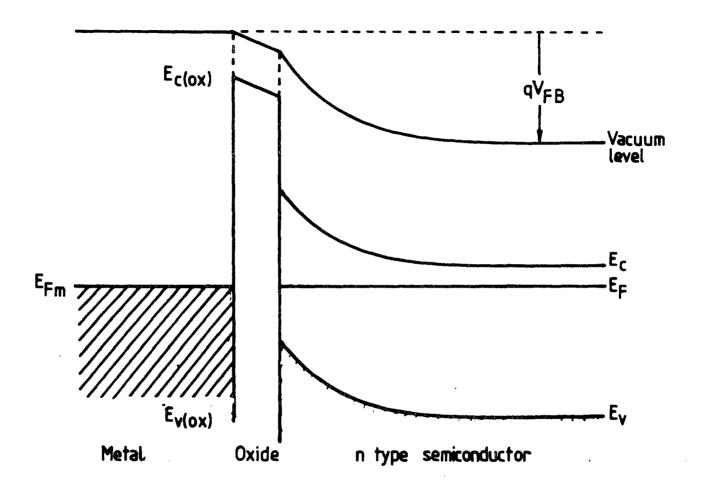

The magnitude of  $V_{FB}$  determines whether the surface is accumulated, depleted or inverted at zero bias. Figure 2.2 shows the energy bands of a non-ideal MIS diode in equilibrium.

A more complicated effect in a non-ideal MIS diode is due to interface states. The surface of real semiconductor always has some imperfections due to incomplete bonding (dangling bonds) and surface contamination or chemical impurities. It has been shown [6,7,8] that, the density and energy distribution of the interface states due to these imperfections are determined by the electrode metal, the crystallographic orientation of the semiconductor, thermal annealing, and the degree of oxidation. These imperfections disturb the periodicity of the crystal potential, and give rise to new states with energy levels lying within the forbidden gap of the semiconductor. Such energy states are often termed either surface or interface states. They can have a very strong influence on the electrical behaviour of a semiconductor device. The interface states also act as recombination centres, electron or hole traps, donor or acceptor centres, etc, depending on the electrical behaviour being considered.

Figure 2.2 Energy band diagram of the non-ideal MIS diode at zero bias.

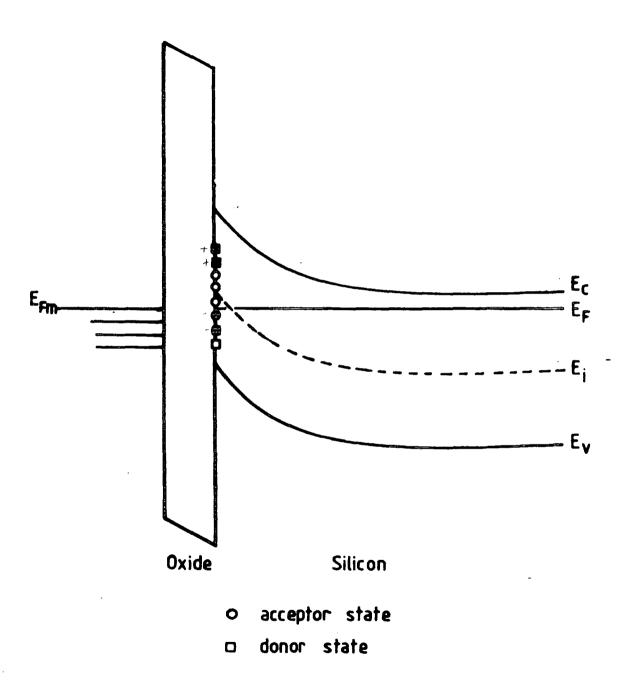

Interface states are considered to be donor-type when those above the Fermi level are empty (ie. positively charged) and those below the Fermi level are full with electrons (ie. neutral) as shown in figure 2.3. On the other hand, acceptor-type states are neutral when empty and negative when filled. Both of them have the ability to exchange charge with the conduction and valence bands by trapping holes or electrons. Their occupancy depends upon their position in the gap relative to the Fermi level at the surface of the semiconductor. The probability, f, of occupancy in thermal equilibrium is governed by Fermi- Dirac statistics and given by,

$$f_d(E_t) = \frac{1}{1 + g \exp(\frac{E_t - E_F}{kT})}$$

2.9a

for donors, and

$$f_a(E_t) = \frac{1}{1 + g \exp(\frac{E_F - E_t}{kT})}$$

2.9b

for acceptors, where g is the spin degeneration factor which is equal to 2 for acceptors and 1/2 for donors, and  $E_t$  is the interface state energy level.

Under biasing conditions, the interface states together with the conduction and valence band edges will move up or down depending on the applied voltage while the Fermi level remains constant. This results in a changing difference between  $E_F$  and  $E_t$ , and hence a change in the occupancy of the interface states. The resulting change in the interface charge affects the electrical characteristics of the MIS.

The interface states associated with the MIS system can be summarised to have the following properties;

1) They are charge storage centres, the amount of charge stored depending on the

Figure 2.3 The band bending gives donor states a tendency to neutral and acceptor states a tendency to be charged negatively.

bias condition.

- 2) They provide a spatially concentrated region of recombination-regeneration centers.

- 3) They can cause additional current flow between the metal and interface states if the insulator allows charge to flow.

Including the charge in the interface states the flat-band voltage of the MIS structure becomes

$$V_{FB} = -\frac{Q_i}{C_i} + \phi_{ms}$$

where  $Q_i$  is the sum of the fixed charge  $Q_f$  and the interface charge  $Q_{is}$ . The MIS concepts described above will be applied to the MISS structure in Chapter 3.

# 2.3 GENERATION-RECOMBINATION IN DEPLETION LAYERS

In the MIS structure, one of the effects that can make it non-ideal is leakage current through the insulator. In this case the surface potential may be affected by the generation or recombination of carriers in the depletion layer of the semiconductor. In the bulk semiconductor there are two types of generation-recombination process, band-to-band and the Shockley-Read-Hall (SRH) mechanism. The former process is very rare in silicon and generation- recombination generally occurs through SRH centres which provide intermediate states or stepping stones in the transition of electrons and holes between conduction and valence bands. These generation-recombination centres are created by impurity atoms in the semiconductor which form deep energy levels near the midgap. In fact, silicon always has some residual impurities such as nickel, iron, manganese, zinc, and copper [9] giving recombination levels in the energy gap.

The theory of the generation-recombination mechanism has been established

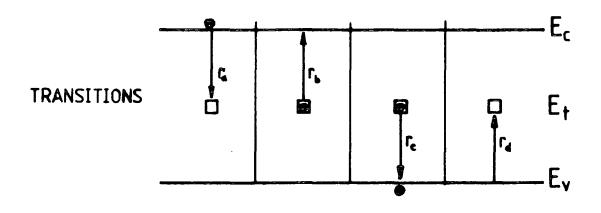

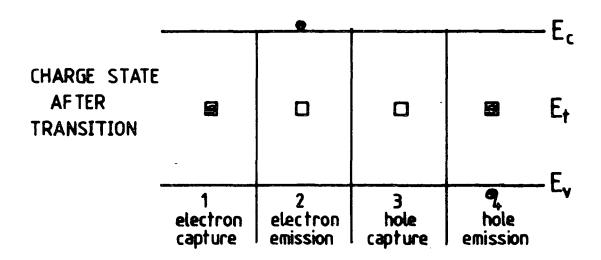

by Shockley, Read and Hall, in term of four basic process involving electrons and holes being captured and emitted by a single impurity level. This process is clearly demonstrated in figure 2.4, where  $r_a$  and  $r_b$  are the rate of electron capture and emission, and  $r_c$ ,  $r_d$  are the rate of hole capture and emission respectively. For simplicity we consider only the case of a single energy level  $E_t$  having a concentration  $N_t f$  filled centres per unit volume and  $N_t (1-f)$  unoccupied (neutral) centres, where f is the probability of the centre being occupied by an electron. In equilibrium, where there is no external generation mechanism, the rates of generation and recombination are equal, thus  $r_a = r_b$  and  $r_c = r_d$ , and the electron and hole emission rates are given by [10],

$$e_n = \upsilon_{th} \sigma_n n_i \exp(\frac{E_t - E_i}{kT})$$

2.10a

for electrons, and,

$$e_p = v_{th}\sigma_p n_t \exp(\frac{E_t - E_t}{kT})$$

2.10b

for holes, where  $v_{th}$  is the thermal velocity,  $\sigma_n$  and  $\sigma_p$  are the capture cross sections of electrons and holes respectively. Note that the emission probability of electrons increases as the SRH level  $E_t$  approaches the conduction band edge,  $E_c$ , and the emission probability of holes increases as it approaches the valence band edge,  $E_v$ .

In the non-equilibrium case, where an external energy source such as light is applied uniformly to the semiconductor, the net generation-recombination rate of a single SRH centre is given by [4],

$$U = \left[ \frac{\sigma_n \sigma_p v_{th}(pn - n_i^2) N_t}{\sigma_n [n + n_i \exp(\frac{E_t - E_i}{kT})] + \sigma_p [p + n_i \exp(\frac{-E_t - E_i}{kT})]} \right]$$

2.11

Figure 2.4 SRH generation-recombination processes.

From this equation it is clear that in either generation or recombination, the most effective centre will have  $E_t$  close to  $E_t$ . Gold has been found to give a very effective trapping centre in silicon with an acceptor level near midgap and a donor level about 0.2eV below midgap. The theory for such a two-level centre is more complicated than for a SRH centre but expressions such as equation 2.11 are still used.

In a depletion region like in reverse biased MIS diode or p-n junction, the concentration of carriers is reduced below the equlibrium concentration and  $pn < n_i^2$ . The depletion region therefore has net generation of carriers. The rate of generation can be obtained from equation 2.11 and is given by,

$$U = -\left[\frac{\sigma_n \sigma_p v_{th} N_t}{\sigma_n \exp(\frac{E_t - E_i}{kT}) + \sigma_p \exp(\frac{E_i - E_t}{kT})}\right] n_i$$

$$U = -\frac{n_i}{\tau_0} \tag{2.12}$$

where  $\tau_0$  is the effective lifetime which is the reciprocal of the term in brackets and the negative sign implies net generation. If the SHR centre is at the middle of the bandgap ( $E_t = E_1$ ), the effective lifetime can be simplified to

$$\tau_o = \frac{\sigma_n + \sigma_p}{\sigma_n \sigma_p v_{th} N_t}$$

#### 2.4 THE MIS TUNNEL DIODE

The MIS diode with a very thin insulator can pass current by quantum mechanical tunnelling through the insulator. This structure is known as an MIS tunnel diode.

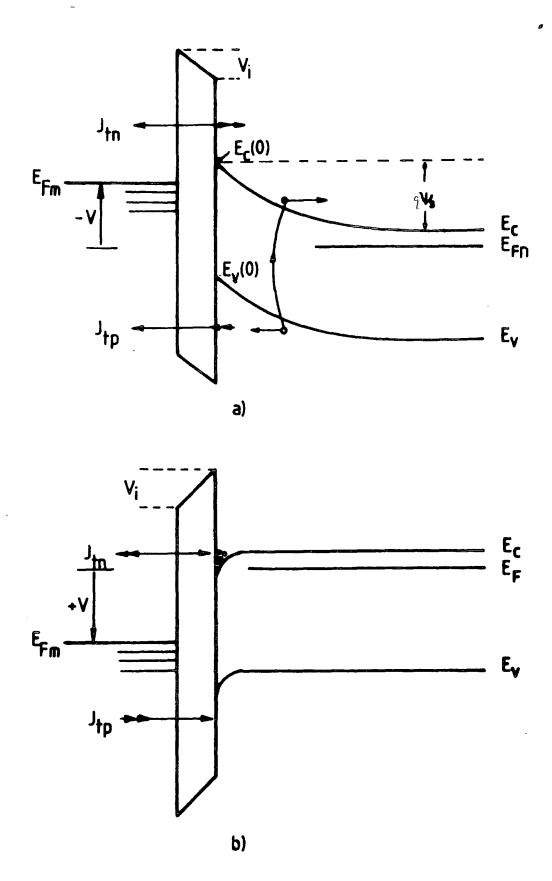

## 2.4.1 MIS Tunnel Diode at Reverse Bias

When the MIS tunnel diode is reverse biased, the energy levels in the semiconductor are bent up as shown in figure 2.5(a), and holes (the minority carriers) tend to accumulate near the surface due to the electric field. Unlike an MIS with a thick insulator (MOS capacitor) the semiconductor will not generally go into strong inversion because the generated holes at the insulator-semiconductor interface leak away through the insulator to the metal electrode and they are unable to maintain the inversion layer at the interface. As a consequence, most of the applied voltage drops in the semiconductor and this causes the silicon surface to be driven into a steady-state deep depletion condition (i.e.  $\psi_s > 2\psi_b$ ). This deep depletion condition is in equilibrium whereas deep depletion in an MOS capacitor never occurs in the steady state condition.

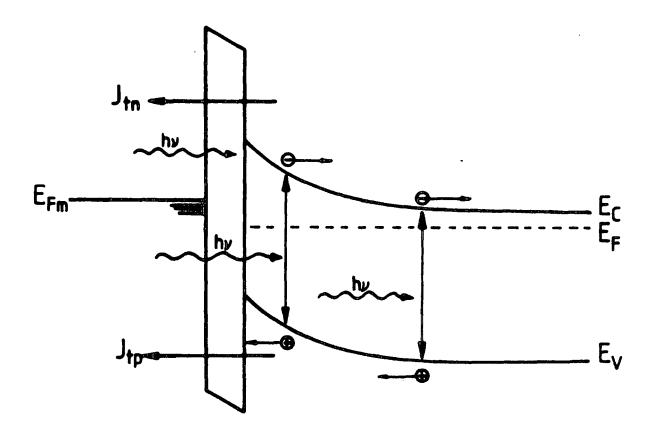

For an MIS structure containing a very thin silicon oxide insulator the electronic conduction between the metal and semiconductor is by a tunnelling mechanism. There are two main tunnel current components, the electron tunnel current,  $J_{tn}$ , from the metal to the semiconductor conduction band, and the hole tunnel current,  $J_{tp}$ , of holes tunnelling from the semiconductor valence band to the metal. The hole tunnel current is controlled by both the probability of holes penetrating the tunnel barrier presented by the insulator and the supply of holes, p(x), at the insulator-semiconductor interface which is taken to be at x=0. This current can be expressed as (see appendix A)[5],

$$J_{tp} = A_p T^2 e^{-\eta_p} \left\{ F_1 \left( \frac{E_v(0) - E_{Fp}(0)}{kT} \right) - F_1 \left( \frac{E_v(0) - E_{Fm}}{kT} \right) \right\}$$

2.12

Figure 2.5 Energy band diagram of the MIS tunnel diode a) reverse biased, b) forward biased.

where

$A_p$  = the effective Richardson constant for holes

$T = \text{temperature in } {}^{o}K$

$\eta_p$  = the barrier tunnelling transmision coefficient

$=\chi_p^{\frac{1}{2}}d$ , where  $\chi_p$  is the tunnelling barrier height for holes

$F_1 =$ Fermi- dirac integral of order 1

$E_{Fp}(0) =$  the quasi Fermi-level of holes at the interface x = 0

$E_v(0) =$  the energy of the valence band edge at x = 0

$E_{Fm}$  = the metal Fermi-level

Since the MIS is reverse biased, the hole tunnel current is limited by the rate at which holes are generated in the depletion region. The generation current can be expressed as

$$J_g = \int_0^{X_d} q|U|dx = q|U|X_d$$

2.13

and from 2.11 this can be written as,

$$J_g = \frac{qn_i X_d}{\tau_2}$$

2.14

Under steady state conditions, the hole tunnel current is equal to the generation current  $(J_{tp} = J_g)$ .

In a similar way, the electron tunnel current,  $J_{tn}$ , associated with electron tunnelling from the metal to the semiconductor conduction is a function of the rate of supply of electrons which are capable of tunnelling to the conduction band from within the metal (figure 2.5(a)). The current is also a function of the probability of the electrons penetrating the tunnel barrier. By analogy to equation 2.12, the electron tunnel current can be written as [5],

$$J_{tn} = A_e T^2 e^{-\eta_e} \left\{ F_1 \left( \frac{E_{Fm} - E_c(0)}{kT} \right) - F_1 \left( \frac{E_{Fn}(0) - E_c(0)}{kT} \right) \right\}$$

2.15

where  $E_{Fn}(0)$  is the quasi Fermi-level of electrons at the interface and  $E_c(0)$  is the energy of the conduction band edge at x = 0.

For a normal case where  $E_{Fm} < E_c(0)$  the hole generation current,  $J_g$ , is much greater than the electron tunnel current,  $J_{tn}$ . So for this system the reverse bias current  $J_R$  is approximately equal to the generation current  $(J_R = J_g)$ .

The total voltage across the reverse biased MIS is the voltage across the insulator plus the voltage drop in the depletion layer which is equal to the surface potential  $\psi_s$

$$V = V_i + \psi_s \tag{2.16}$$

The voltage across the insulator is given by,

$$V_i = \frac{Q_s d}{\epsilon_i}$$

2.17

where  $\epsilon_i$  is the insulator permittivity in farad/cm,  $Q_s$  is the total charge per unit area in the semiconductor and is given by

$$Q_s = \sqrt{2q\epsilon_s N_d \psi_s}$$

2.18

From equation 2.17 and 2.18,  $V_i$  can be expressed as

$$V_i = \frac{\sqrt{2q\epsilon_s N_d \psi_s}}{C_i}$$

2.19

where  $C_i(=\epsilon_i/d)$  is the insulator capacitance per unit area. For the MIS tunnel oxide  $C_i$  is in the order of  $10^{-6}F.cm$ , and the doping density of the semiconductor,  $N_d$  is in

the order of  $10^{15}cm^{-3}$ . By substituting these values in equation 2.19 it can be shown that  $\psi_s \gg V_i$ . Therefore for the reverse bias MIS the majority of the applied voltage drops across the deep depletion region of the semiconductor.

## 2.4.2 MIS Tunnel Diode at Forward Bias

When the MIS is forward biased the energy levels in the semiconductor are bent down as shown in figure 2.5(b), and excess electrons accumulate at the insulator-semiconductor interface. The electron concentration at the surface is given by equation 2.3, so that a small change in surface potential  $\psi_s$  causes a large change in the concentration of the accumulated electrons. These electrons act like a plate capacitor so that most of the applied voltage drops across the insulator  $(V \simeq V_i)$ .

The electron tunnel current,  $J_{tn}$ , is due to the tunnelling of electrons from the semiconductor conduction band to the metal. The hole tunnel current is due to holes tunnelling from the metal to the semiconductor valence band and is a function of the supply of holes and the probability of them penetrating the tunnel barrier. This current is analogous to the electron tunnel current for the case of reverse bias. Thus, the electron current is much greater than hole current and it is the dominant component in the forward bias current of the MIS.

The forward current, depending on the concentration of electrons in the accumulated surface will rise rapidly with voltage. The reverse current is however limited by generation in the depletion layer so that it will become almost constant with voltage. The overall current-voltage characteristic of the MIS tunnel diode has been considered by Simmons and Taylor [12] and it is as illustrated in figure 2.6. This characteristic looks very similar that of a p-n junction.

Figure 2.6 Typical current-voltage characteristic of the MIS tunnel diode.

## 2.4.3 Current Multiplication in Reverse Bias

For the MIS in the reverse biased condition, the tunnel current is limited by the rate at which holes are generated in the depletion region. If additional holes are supplied to the surface of the semiconductor by external processes such as illumination with light or by injection from a third terminal they cannot be lost by increased tunnelling so that their concentration increases and the semiconductor surface becomes inverted. When the surface is in strong inversion, the field at the semiconductor surface increases, and this increases the electric field in the insulator and hence the voltage drop across it. This causes the difference between the metal Fermi-level and the conduction band edge,  $(E_{Fm} - E_c(0))$ , to decrease, and this increases the number of electrons in the metal which are capable of tunnelling from metal to the semiconductor conduction band. This will greatly increase the electron tunnel current and this phenomenon is referred to as current multiplication [2,13]. This not be confused with current multiplication due to impact ionisation.

The multiplication factor, M, due to this effect can be defined as the ratio of the majority carrier to the minority carrier current or,

$$M = \frac{J_{tn}}{J_{tp}}$$

2.20

The magnitude of the current multiplication in the n-type MIS tunnel diode is dependent on the metal work function, insulator thickness, doping concentration,  $N_d$ , temperature and the injected current [2,13]. At the same insulator thickness, the current multiplication, M, increases with decreasing metal work function. The effect of insulator thickness, d, on M has been further investigated by C. W. Jen et al. [2], who showed that a thicker insulator led to a larger multiplication.

## 2.5 P-N JUNCTION DIODE

#### 2.5.1 Current-Voltage Equation

There are two major mechanisms which contribute to the current in a forward biased p-n junction; 1) injection current, and 2) space charge recombination current. For a first-order diode model the latter is ignored, and the analysis assumes that the injection of minority carriers is low. In a forward biased p-n junction, holes are injected from the the p-side over the potential barrier into the n-side where as minority carriers they diffuse away from the junction. Eventually they recombine with majority carriers in the n-side or move to the end contact by diffusion. For a long p type substrate, the hole diffusion current density is given by the Shockley equation [11],

$$J_{dp} = \frac{qD_p p_{no}}{L_p} \left\{ \exp(\frac{qV_j}{kT}) - 1 \right\}$$

2.21

Similarly the injection of electrons from the n-side to the p-side gives an electron diffusion current density

$$J_{dn} = \frac{qD_n n_{po}}{L_n} \left\{ \exp\left(\frac{qV_j}{kT}\right) - 1 \right\}$$

2.22

where  $D_n$  and  $D_p$  are the diffusion constants of electrons and holes,  $n_{po}$  and  $p_{no}$  are the equilibrium minority carrier concentrations in the p-side and the n-side respectively,  $L_p$  and  $L_n$  are the diffusion lengths for holes and electrons,  $V_j$  is a voltage across the junction. The total current density for an ideal p-n diode is the sum of the hole and electron diffusion currents

$$J = J_{dp} + J_{dn} = J_s \left\{ \exp(\frac{qV_j}{kT}) - 1 \right\}$$

2.23

where

$$J_s = \frac{qD_p p_{no}}{L_p} + \frac{qD_n n_{no}}{L_n}$$

2.24

The second component of the current is due to recombination of carriers in the space charge region resulting in an increase in the total current through the device. This current was first explained by Sah et al. [3] by assuming that (i) the doping levels were similar: on opposite sides of the junction, (ii) only single level recombination centres located in the middle of the bandgap are important, and (iii) the recombination rate is approximately constant within the space charge region. The expression for the recombination current density can then be simplified to [4],

$$J_{rj} = \frac{qn_iW_j}{2\tau_o}\exp(\frac{qV_j}{2kT})$$

2.25

where  $au_o$  is the effective carrier lifetime and  $W_j$  is the junction width which is given by

$$W_j = \sqrt{\frac{2\epsilon_s}{q} \left(\frac{N_d + N_a}{N_a N_d}\right) (V_{bi} - V_j)}$$

2.26

where  $\epsilon_s$  is the semiconductor permittivity,  $N_d$  is a donor concentration, and  $V_{bi}$  is the built-in voltage given by,

$$V_{bi} = \frac{kT}{q} \ln(\frac{N_d N_a}{n_i^2})$$

2.27

For the p<sup>+</sup>-n junction of interest in this thesis  $N_a\gg N_d$  and

$$W_j \approx \sqrt{\frac{2\epsilon_s}{qN_d}(V_{bi} - V_j)}$$

2.28

# 2.5.2 P-N Junction Ratio $\beta_p$ for Holes.

The capability of the junction to inject holes or electrons is called the *injection* efficiency,  $\gamma$ . The injection efficiency for holes  $\gamma_p$  is defined as,

$$\gamma_p = rac{ ext{hole current}}{ ext{total current}}$$

i.e.

$$\gamma_p = \frac{J_{dp}}{J_{dp} + J_{dn} + J_{r}}$$

2.29(a)

The injection efficiency for electrons,  $\gamma_n$ , is

$$\gamma_n = \frac{\text{electron current}}{\text{total current}}$$

$$\gamma_n = \frac{J_{dn}}{J_{dp} + J_{dn} + J_{rj}}$$

2.29(b)

The ratio of the hole to electron injection efficiency is called p-n junction ratio,  $\beta_p$ , for holes

$$\beta_p = \frac{\gamma_p}{\gamma_n} = \frac{J_{dp}}{J_{dn}}$$

2.30

For a wider p section of the p-n junction

$$\beta_p = \frac{D_p N_a L_n}{D_n N_d L_p} \tag{2.31}$$

As we can see that the junction ratio for holes increases if the p-substrate has a higher doping density. This is a very important parameter in MISS devices where high hole injection is needed.

#### 2.5.3 Practical PN Junctions

For practical p-n junction diodes, the current expressions discussed earlier would not be seen experimentally. In a practical model of a p-n junction diode, apart from recombination-generation current, the effects of two external resistances in the form of a series resistance  $r_s$  and a shunt resistance  $r_{sh}$  must be included. The series resistance  $r_s$  represents the bulk resistance of the p, and n regions outside the transistion region, and the resistance of the ohmic contacts. The resistance  $r_{sh}$  arises from the leakage current at the edge of the junction. In the case of a good diode this resistance is very large and its effects are negligible.

### REFERENCES FOR CHAPTER 2

- [1] J. L. Moll, Variable Capacitance with Large Capacity Charge, Wescon Convention Record, part 3, p.32 (1959).

- [2] C. W. Jen, C. L. Lee and T. F. Lei, Current Multiplication in MIS Structures, Solid State Electronics, 27, pp.1-11 (1984).

- [3] C. T. Sah, R. N. Noyce and W. Shockley, Carrier Generation and Recombination in P-N Junctions and P-N Characteristics, Proc. IRE, 45, pp.1228-1243 (1957).

- [4] S. M. Sze, *Physics of Semiconductor Devices*, John Wiley and Sons, New York, Chapter 2, p.84 (1981).

- [5] M. Green and J. Shewchun, Current Multiplication in Metal Insulator Semiconductor (MIS) Tunnel Diodes, Solid State Electronics, 17, pp. 349-365 (1974).

- [6] A. H. Marshak and K. M. Van Vliet, On the Separation of Quasi-Fermi Levels and the Boundary Condition for Junction Devices, Solid State Electronics, 23, pp.1223-1228 (1980).

- [7] L. M. Terman, An Investigation of Surface States at a Silicon/Silicon Oxide Interface Employing Metal-Oxide- Silicon Diodes, Solid State Electronics, 5, pp.285-299 (1962)

- [8] V. A. K. Temple and J. Shewchun, Small Signal Equivalent Circuit Model for the Metal- Insulator- Semiconductor Tunnel Diodes, Solid State Electronics, 21, pp.807-812 (1978).

- [9] E. H. Nicollian and J. R. Brews, MOS (Metal Oxide Semiconductor) Physics and Technology, John Wiley and Sons, New York, pp. 178-185 (1982).

- [10] A. G. Grove, Physics and Technology of Semiconductor Devices, John Wiley and Sons, New York (1967).

- [11] W. Shockley, The Theory of p-n Junctions in Semiconductors and p-n Junction Transistors, Bell Syst. J. 28, pp.435-489 (1949).

- [12] J. G. Simmons and G. W. Taylor, Tunneling Dielectric Films, in Solid State Devices, Institute of Physics, pp.85-111 (1981).

- [13] M. A. Green and J. Shewchun, Current Multiplication in Metal- Insulator- Semiconductor (MIS) Tunnel Diodes, Solid State Electronics, 17, pp.349-365 (1974).

## CHAPTER THREE

# PRINCIPLE OF OPERATION OF MISS DEVICES

#### 3.1 INTRODUCTION

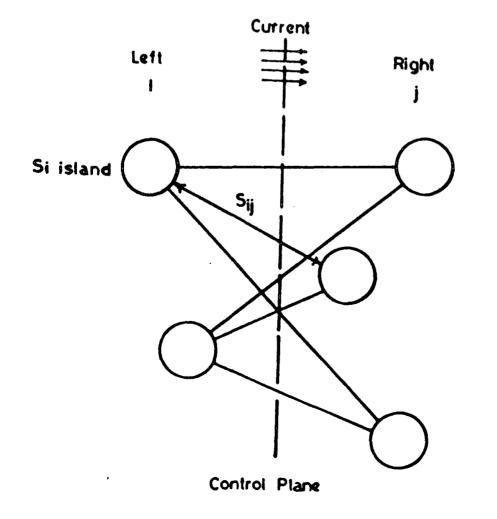

As has been mentioned MISS devices have three regions in their I-V characteristics, a high impedance region which is between zero voltage and the switching point, a negative resistance region, and a low impedance state. A great deal of work has been done to establish the theory of operation of the MISS most of which has been based on the tunnel oxide device. Yamamoto and Morimoto [1] postulated that an inversion layer formed at the insulator-semiconductor interface causing an increase in the tunnelling current so turning the device ON. Kroger and Wegener [2] quite properly recognised that the high impedance state was due to deep depletion in the semiconductor. Five years later the first quantitative model was proposed by Simmons and El-Badry [3,4] in which they assumed that punch-through or avalanching in the semiconductor was responsible for the switching process. For a lightly doped epilayer (< 10<sup>15</sup>cm<sup>-3</sup>) the switching action was thought to be controlled by punch-through and for a heavily doped layer (> 10<sup>17</sup>cm<sup>-3</sup>) it was due to avalanche breakdown.

Habib and Simmons [5] put forward a theory, which appears to be very convincing, in which where the switching mechanism is based on a positive feedback interaction between the p-n junction and the MIS tunnel diode. Sarrabayrouse et al. [6,7] extended the regenerative feedback model and obtained agreement between their calculated variation of switching voltage with illumination and temperature and the experimental evidence. Adán and Zólomy [8] proposed a thyristor like model where positive feedback is normaly used, the MISS being regarded as being composed of two

amplification devices. The first element was a bipolar transistor with p<sup>+</sup> substrate as emitter, the neutral region of the epitaxial layer as base and the semiconductor-semi-insulator interface as collector. The MIS section was treated as the second amplification device.

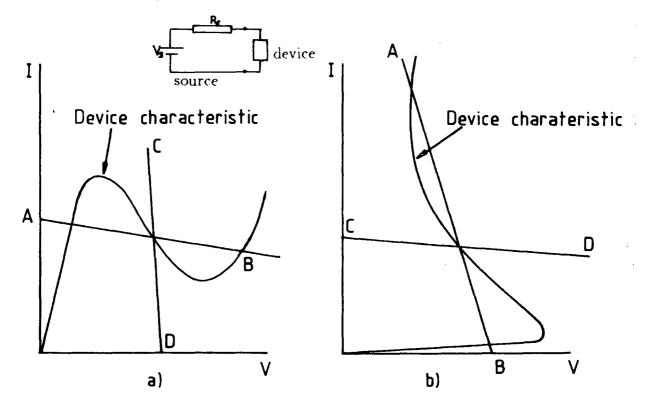

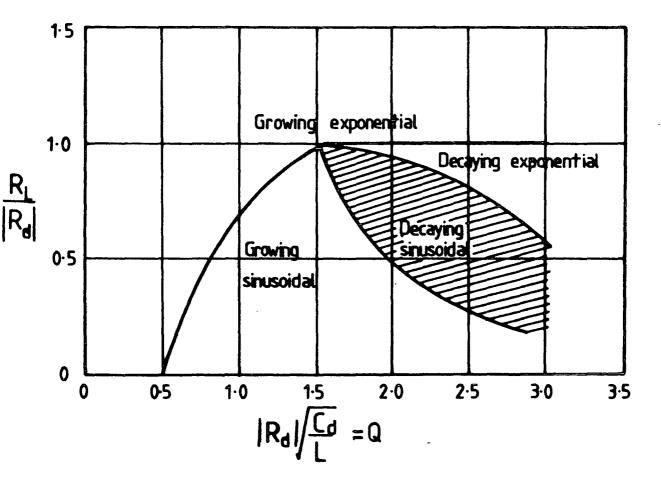

The regenerative positive feedback model had been used by many workers in the field as the general switching mechanism for the MISS [3-8]. Board [10] seems to suggest that this mechanism is responsible for any type of device which exhibits current-controlled negative resistance, although the physics of the operations of MISM, MISIM and thyristor devices may be quite different. According to the positive feedback model, before switching takes place the total loop gain, G, of the system is less than one, at the switching and holding points it is equal to 1, and in the negative resistance region G is greater than 1. The stability condition of the feedback loop is  $G \leq 1$  and the instability condition is G > 1. A stable steady state negative resistance which has been found in earlier work in this department and is now the main interest of the present work, disproves the validity of this model. However, it is generally accepted that a feedback model still applies to the MISS under certain external conditions which will be discussed in Chapter 7.

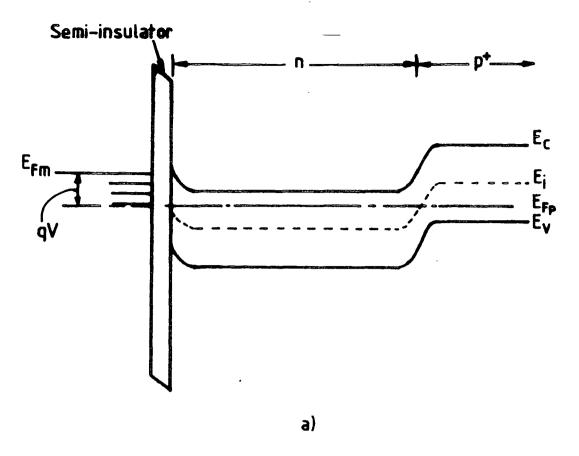

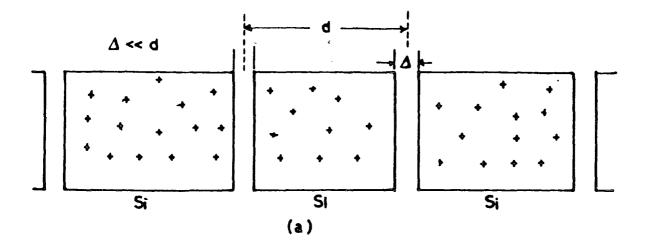

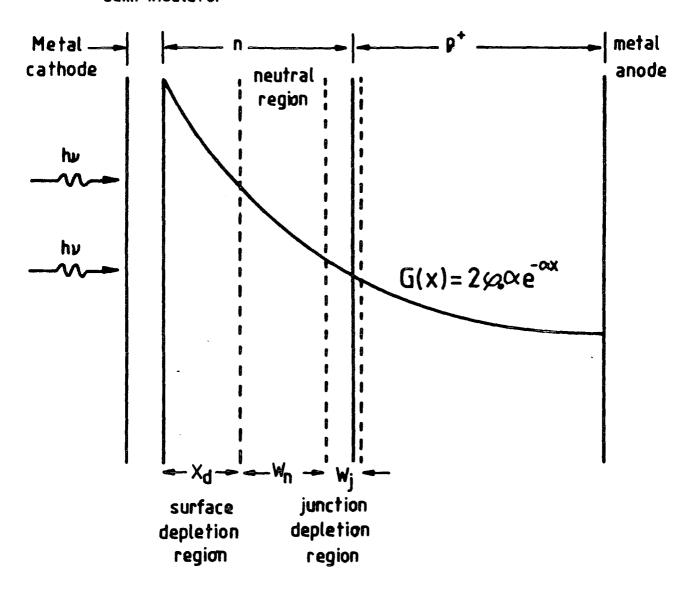

Although this thesis is concerned with MISS devices made with SRO as a semi-insulating material with a different conduction mechanism compared to that of tunnel-oxide, the basic switching process appears to be the same for all types of MISS. Therefore in this chapter we will first consider the principle of operation of one-dimensional MISS devices based on a tunnelling mechanism in the semi-insulator. Later in the chapter the SRO conduction mechanism will be briefly reviewed, followed by speculation about the electronic mechanism which leads to switching in the SRO-MISS device. Experimentally, the device characteristics are found to depend on area and the reasons for this will be described in Chapter 5.

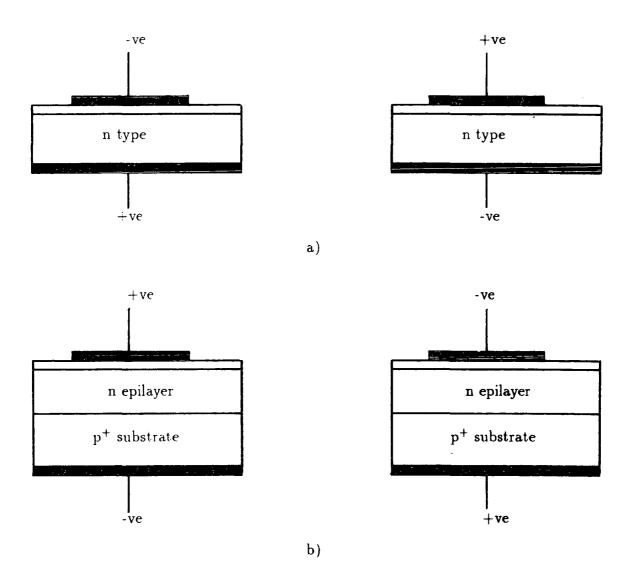

The terms forward and reverse bias as used for the MISS are different from

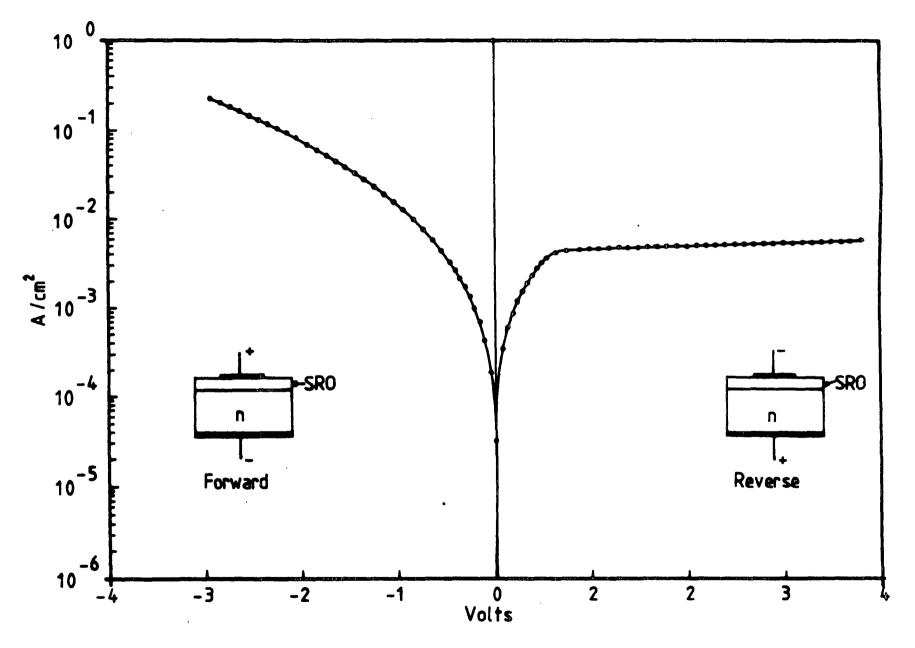

those for MIS. In this thesis we define forward bias for the switching direction or in other words the voltage to enable a large amount of current to flow, biasing the MIS section into what would normally called reverse bias. Reverse bias for the MISS is the non-switching direction where only a small amount of current can flow through the MIS section would normally be said to be forward biased. The forward and reverse bias conditions for the MISS are the opposite of those the MIS as illustrated in figure 3.1.

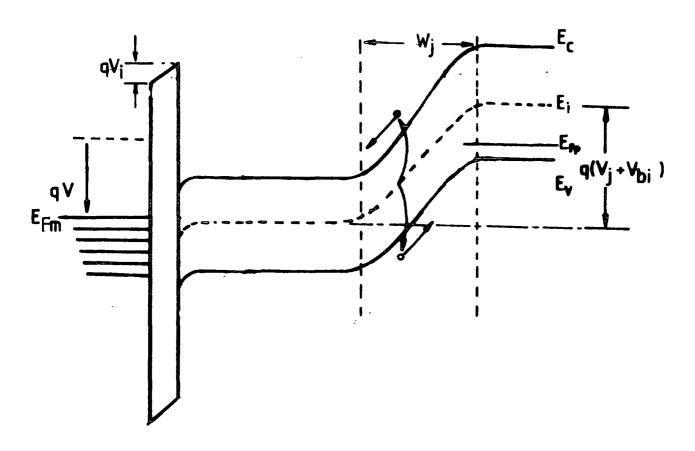

Figure 3.1 a) MIS in reverse and forward bias, b) MISS in reverse and forward bias.

#### 3.2 OPERATION WITH REVERSE BIAS

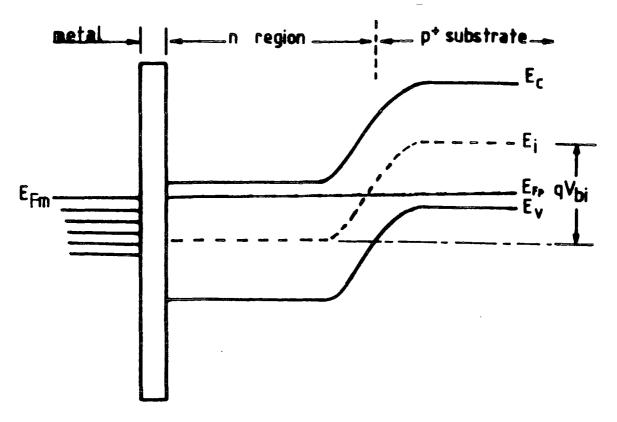

The energy band structure of an idealised MISS device under zero bias condition and thermal equlibrium is shown as in figure 3.2. If a positive voltage is applied to the metal with respect to the substrate the MIS section with its leaky insulator is forward biased while the p<sup>+</sup>-n junction is reverse biased as shown in figure 3.3. As discussed in Chapter 2, the MIS tunnel diode behaves as a rectifier, so that if forward biased it can pass a relatively large current resulting in a small voltage drop. As a consequence, most of the applied voltage is droped across the depletion region of the reverse bias p-n junction. The I-V characteristic in this condition is therefore dominated by the reverse biased p-n junction and the current is limited by generation, predominantly in the depletion region. The reverse bias current of the device can therefore be written approximately as

$$J_g = \frac{n_i}{\tau_c} W_j (V_{bi} + V_j)^{1/2}$$

$$= \frac{n_i}{\tau_o} \left( \frac{q \epsilon_s}{2N_d} \right)^{1/2} (V_{bi} + V - V_i)^{1/2}$$

3.1

where  $V(=V_i+V_j)$ , is the voltage across the device,  $V_{bi}$  is the p-n junction built-in voltage, and  $V_i$  is the voltage drops across the semi-insulator. If the semi-insulator is leaky, the voltage drop in it can be ignored  $(V_i \simeq 0)$ , and, the reverse bias current may be written as,

$$J_R \approx \frac{n_i}{\tau_o} \left(\frac{q\epsilon_s}{2N_d}\right)^{1/2} (V + V_{bi})^{1/2}$$

3.2

Figure 3.2 Energy diagram of the MISS at zero bias.

Figure 3.3 Energy diagram of the MISS at reverse bias.

The reverse current of the MISS therefore increases slowly with voltage until the onset of avalanche breakdown.

#### 3.3 OPERATION WITH FORWARD BIAS

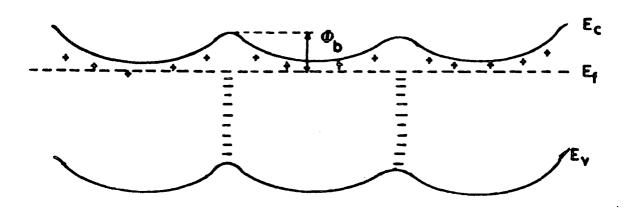

#### 3.3.1 High Impedance State

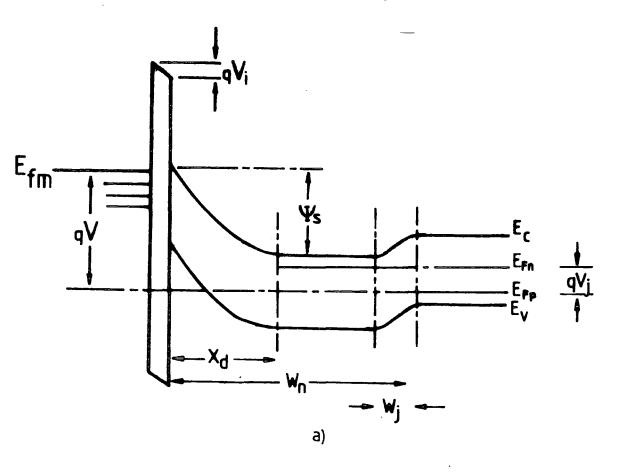

If the voltage on the metal increases negatively with respect to the substrate, the MIS section is reverse biased and the p<sup>+</sup>-n junction is forward biased. As a result, an interfacial depletion region grows in the n type epitaxial layer under the metal electrode. This will cause a net generation of electron-hole pairs within the depletion region, the electrons being swept out through the p-n junction and the holes being swept to the insulator semiconductor (I-S) interface. If the insulator is thick enough and highly insulating the generated holes will accumulate at the I-S interface causing the surface of the n type layer under the insulator to invert. However, since the insulator is leaky in the MISS some of the holes tunnel through the insulator to the metal electrode. Thus as the voltage increases the n-layer becomes more depleted rather than inverted as illustrated in figure 3.4(a). Under this condition, the generated current is given by the same type of expression (equation 3.2) as for the case of reverse bias except that the term  $(V+V_{bi})$  is replaced by a surface potential,  $\psi_s$ , since the majority of the applied voltage drops across the depletion layer. This current is very weakly dependent on voltage and at a relatively high voltage across the device only a very small current can pass through it. This condition is recognised to be the high impedance state or high voltage low current state.

Under these circumstances the junction voltage is just sufficient to enable the generated electron current from the depleted region to flow. These electrons will recombine with holes in the p<sup>+</sup>-n junction and a few will diffuse through it because the junction voltage is very small. Similarly in the deep depletion condition, the voltage across the semi-insulator is just sufficient to allow the very small generated hole current to flow to the metal. The current passed through the junction is limited to the generation current in the surface depletion region which is almost independent of applied voltage, so that the total current passed through the junction remains almost constant. As a result, the voltage dropped across the junction is also constant and very small and it can be neglected compared to the total voltage across the device. It follows that the majority of the applied voltage drops across the depletion region, and is equal to the surface potential,  $\psi_s$ . For an ideal case, where the work function difference,  $V_{FB} = 0$ , the voltage across the MISS can be written as,

$$V = V_i + \psi_s + V_i \tag{3.3}$$

where  $V_i$  and  $V_j$  are the voltage across the semi-insulator and the p<sup>+</sup>-n junction respectively. Since  $\psi_s \gg V_i + V_j$

$$V pprox \psi_s$$

3.4

Therefore the initial forward bias current of the MISS, which is known as the OFF current, is the generation current and is given by,

$$J_{OFF} \simeq \frac{n_i}{\tau_o} \left(\frac{q\epsilon_s V}{2N_d}\right)^{1/2}$$

3.5

### 3.3.2 Switching Point in Punch-Through Mode

When the voltage across the device is increased the depleted region under the semi-insulator extends toward the p<sup>+</sup>-n junction. When it becomes sufficiently high  $(V = V_s)$  the interfacial depletion region reaches the depletion region of the junction

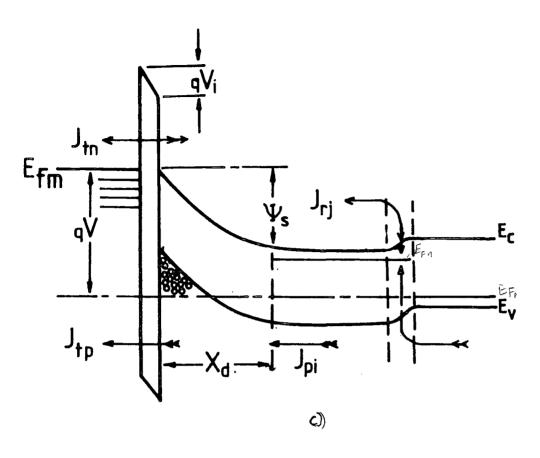

Figure 3.4 Energy band diagram of the MISS, a) in the high impedance state, b) in the punch-through regime.

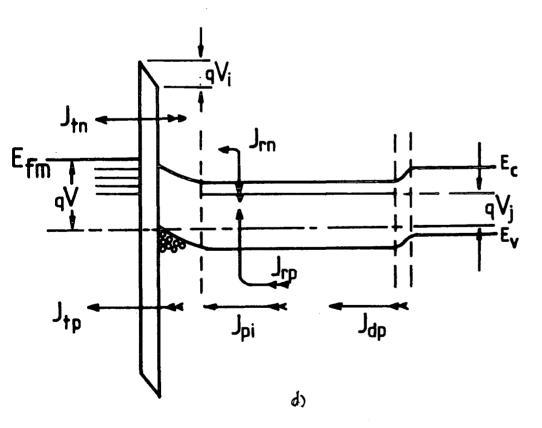

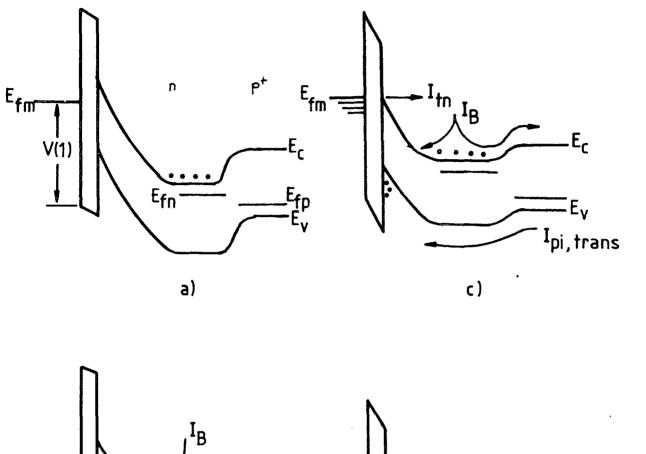

Figure 3.4 (cont.) Energy band diagram of the MISS, c) in the negative resistance region, d) in the low impedance state.

as shown in figure 3.4(b) and this phenomenon is known as punch-through. At punch-through the neutral region disappears completely so that the width of the depletion layer,  $X_{dp}$  can be written approximately as,

$$X_{dp} \simeq W_n - W_j \tag{3.6}$$

where  $W_n$  and  $W_j$  are the thicknesses of the n-type epitaxial layer and the junction depletion region respectively. Hence from equation 2.4 the surface potential at punch-through,  $\psi_{sp}$ , reachs a maximum value given by,

$$\psi_{sp} = \frac{qN_d}{2\epsilon_s}(W_n - W_j)^2$$

3.7

Thus, the voltage across the device which is equal to the switching voltage,  $V_s$  may be written as,

$$V_s \approx \psi_{sp} = \frac{qN_d}{2\epsilon_s} (W_n - W_j)^2$$

3.8

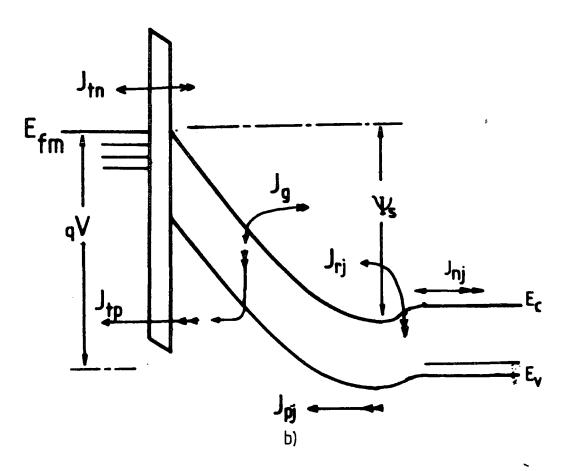

After punch-through has been reached a further increase in the applied voltage will appear across the junction and the semi-insulator. Since the injected hole current from the  $p^+$ -n junction depends exponentially on the junction potential  $(J_{pj} \simeq J_s e^{qV_j/kT})$ , a large number of holes are injected into the depletion region for a very small increment in the applied voltage. These holes travel to the semi-insulator semiconductor interface where they leak (tunnel) through the semi-insulator to the metal. When the rate at which holes reach the interface becomes greater than the rate at which which they can tunnel through the semi-insulator they will accumulate rapidly at the interface and the semiconductor surface will become inverted. As a consequence the potential across the depletion layer decreases and the electric field in the

semi-insulator increases allowing a larger electron tunnel current,  $J_{tn}$ , to flow from the metal into the semiconductor. Thus the p<sup>+</sup>-n junction becomes more forward biased and it injects more holes into the n-type epitaxial layer.

This explains the transition to the highly conducting state in qualitative way.

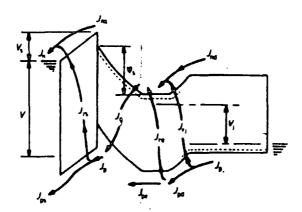

The process is a regenerative one and it can be simplified to

$$dJ_{pj} \rightarrow dJ_{tp} \rightarrow dJ_{tn} \rightarrow dJ_{rj} \rightarrow dJ_{pj}$$

3.9

where  $J_{tn}(J_{tp})$  is the electron(hole) tunnel current,  $J_{pj}$  is the hole current from the  $p^+$ -n junction, and  $J_{rj}$  is the recombination current in the junction. These currents are shown in figure 3.4(b). The ratio of  $dJ_{tn}$  to  $dJ_{tp}$  is defined as the MIS gain,  $G_s$ , and the ratio of  $dJ_{pj}$  to  $d(J_{rj} + J_{nj})$  is the p-n junction gain,  $G_j$ . Therefore, a total gain,  $G(=G_s,G_j)$  of the current loop system can be written as,

$$G = \frac{dJ_{tn}}{dJ_{tp}} \cdot \frac{dJ_{pj}}{d(J_{rj} + J_{nj})}$$

$$3.10$$

From the continuity of the currents

$$dJ_{tn} = dJ_{r1} - dJ_{g} + dJ_{n1} 3.11$$

and

$$dJ_{pj} = dJ_{tp} + dJ_q 3.12$$

where  $J_{nj}$  is the electron diffusion current of the junction. Hence

$$G = \frac{dJ_{rj} - dJ_g + dJ_{nj}}{dJ_{tv}} \cdot \frac{dJ_{tp} + dJ_g}{d(J_{rj} + J_{nj})}$$

3.13

At the switching point, the depletion layer growth ceases, hence the rate of increase of the generation current  $J_g$  becomes zero. Hence  $dJ_g = 0$  so that the total gain becomes unity, G = 1.

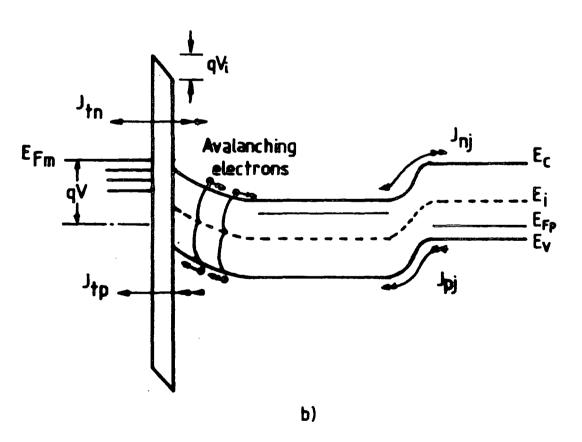

### 3.3.3 Switching in Avalanche Mode

The avalanche mode of switching will take place if the epitaxial layer is heavily doped. In this case the depletion layer will be thin and the electric field will be high. Extra carriers will then be produced by avalanche multiplication at a sufficiently high voltage. The magnitude of the switching voltage is then lower than the punch-through switching voltage because avalanching will occur first. The energy band structure for this case is shown in figure 3.5. When a negative voltage is applied to the metal electrode, the device first enters the high impedance state where the total current is dominated by the generation current as previously. However as the voltage rises the electric field at the insulator-semiconductor interface will exceed  $10^5 V/cm$  [11] and the avalanching process begins with multiplication of the carriers generated in the depletion layer. Thus the generation current is given by [3],

$$J_{ga} = \frac{M_a n_i X_d}{2\tau_o} = \frac{M_a n_i}{\tau_o} \left( \frac{2\epsilon_s V}{q N_d} \right)$$

3.14

where  $M_a$  is the multiplication factor which is given by

$$M_a = \frac{1}{1 - (V/V_a)^{1/2}}$$

3.15

where  $V_a$  is the avalanche breakdown voltage. As we can see the OFF current therefore increases more rapidly than in the punch-through mode.

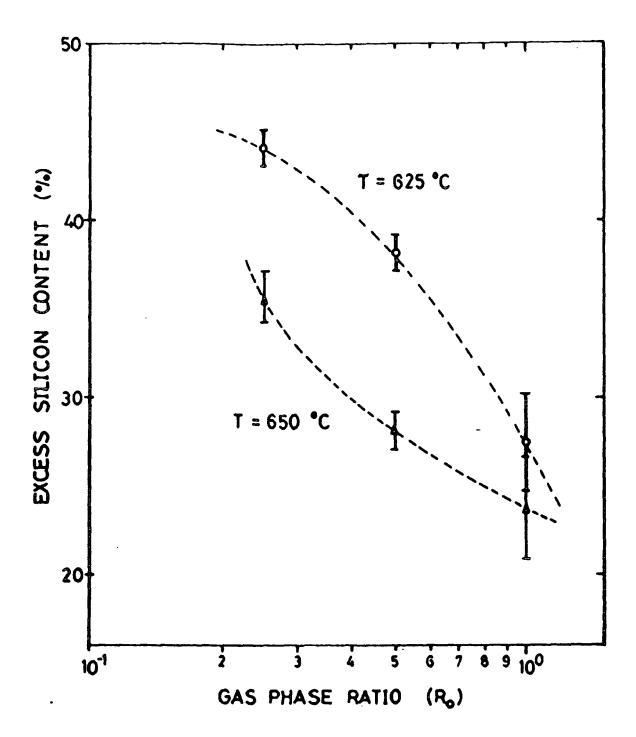

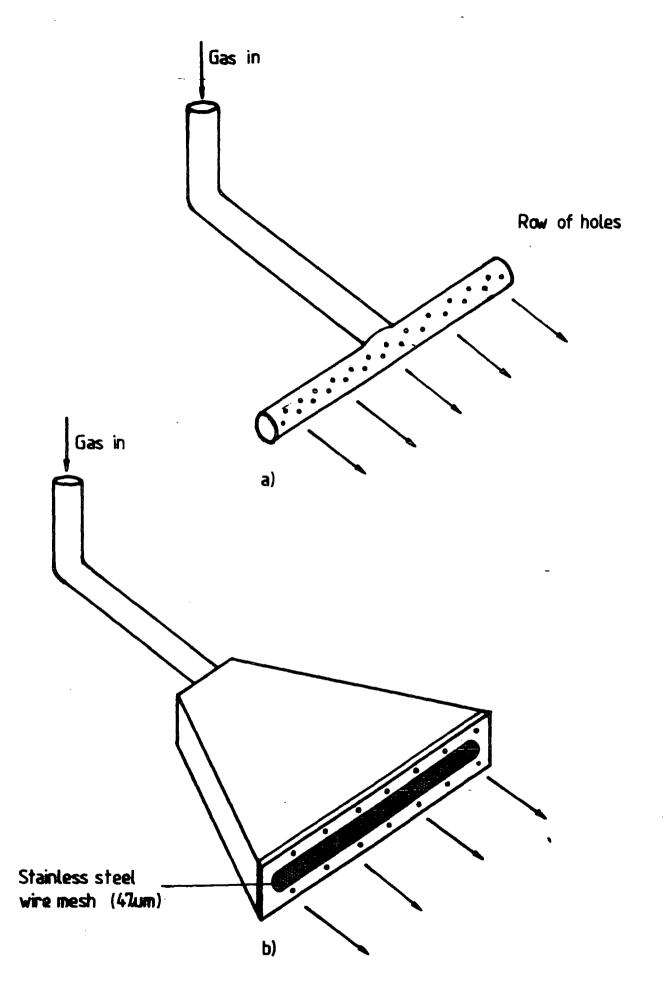

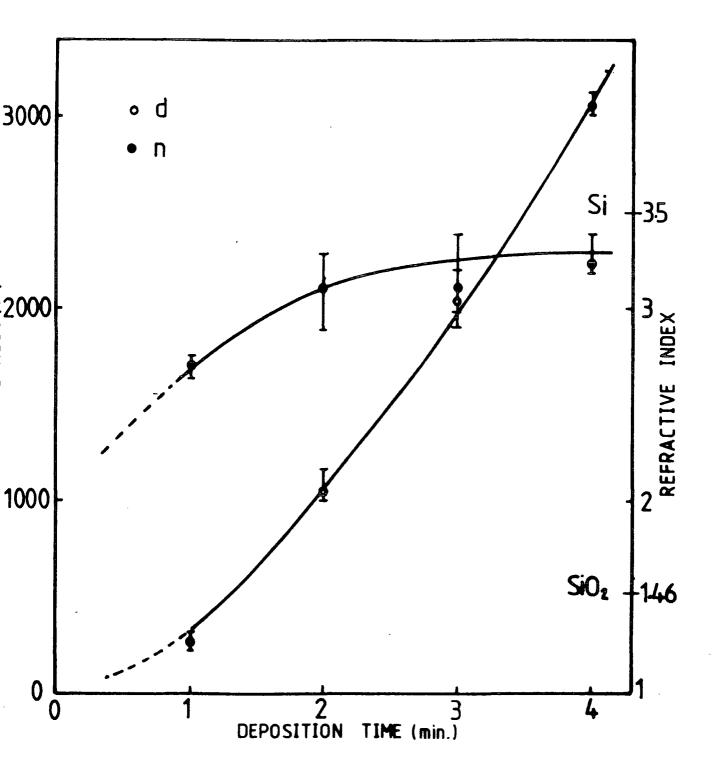

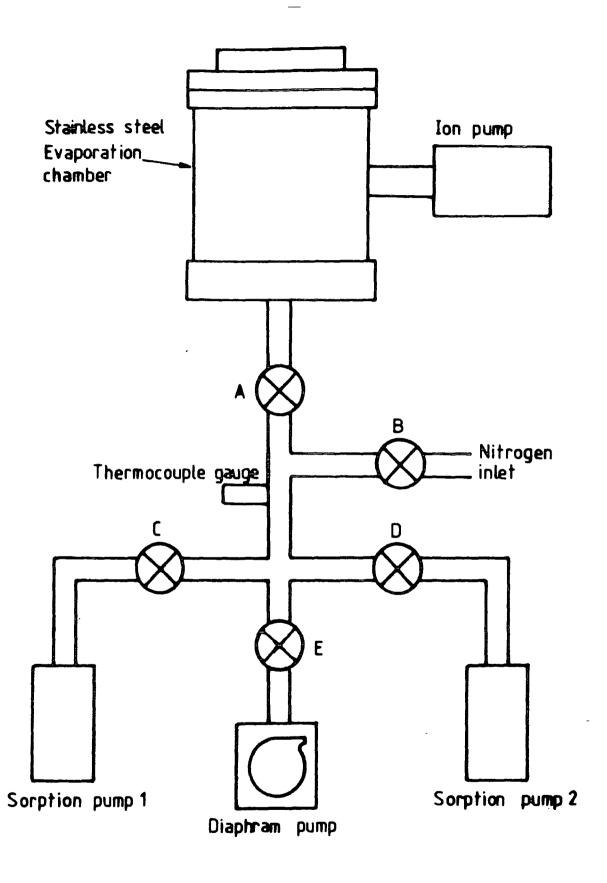

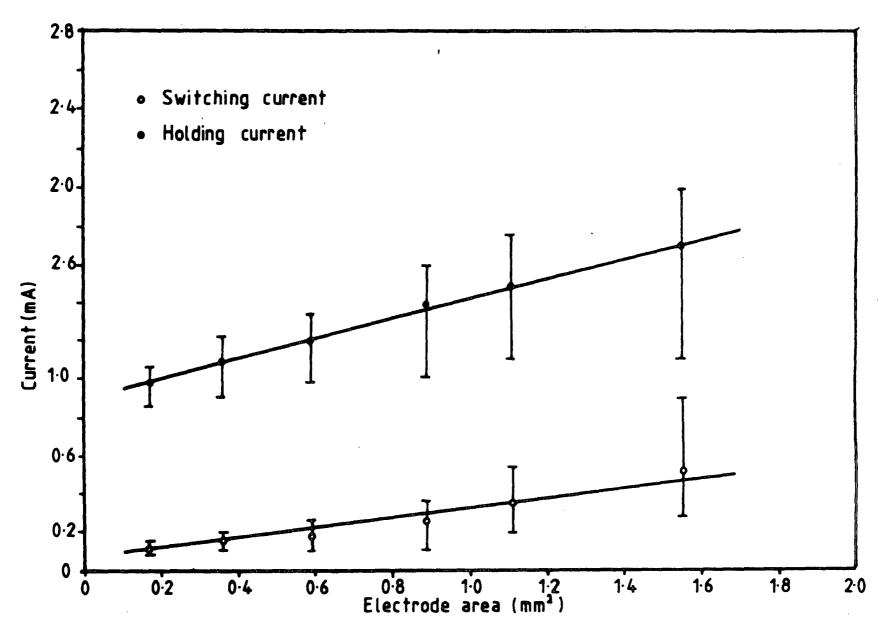

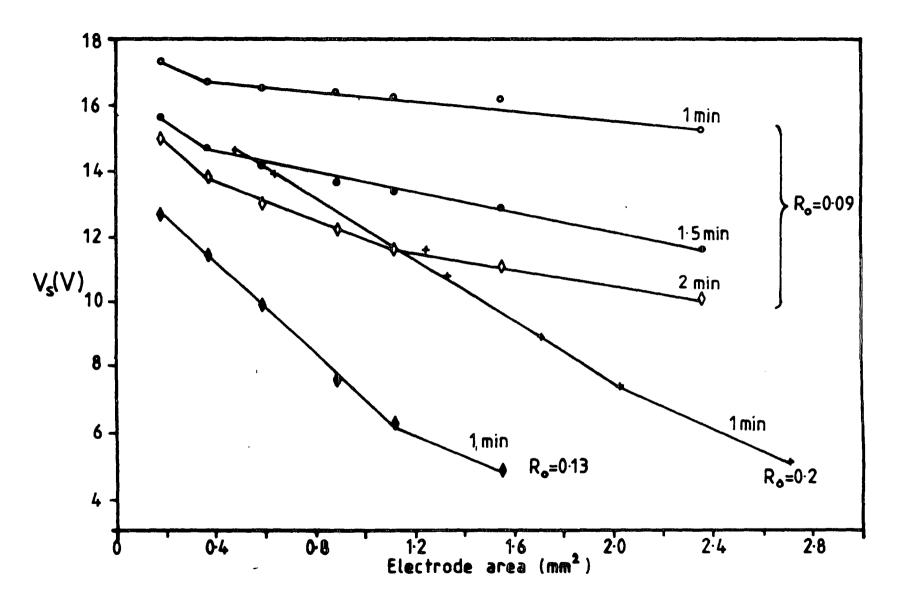

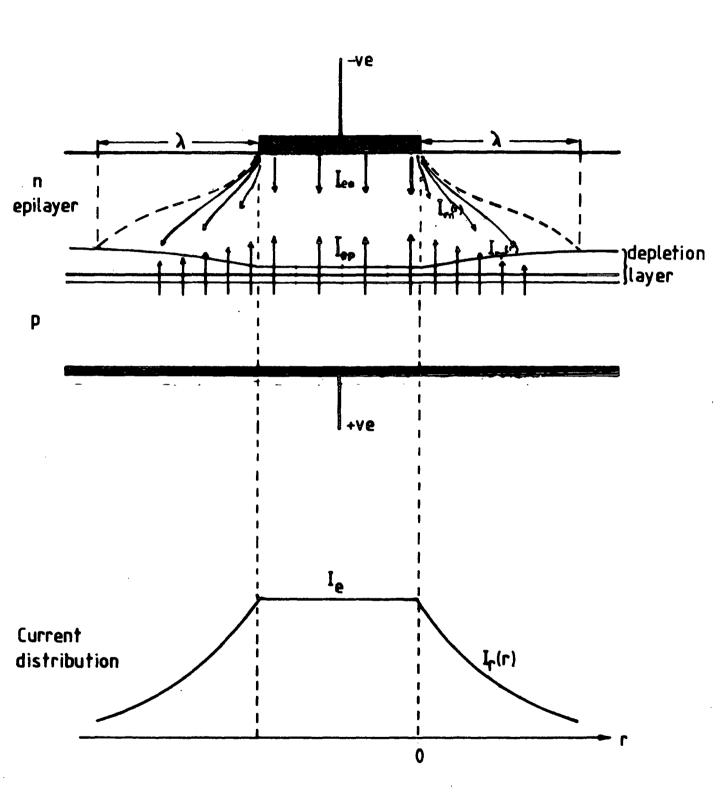

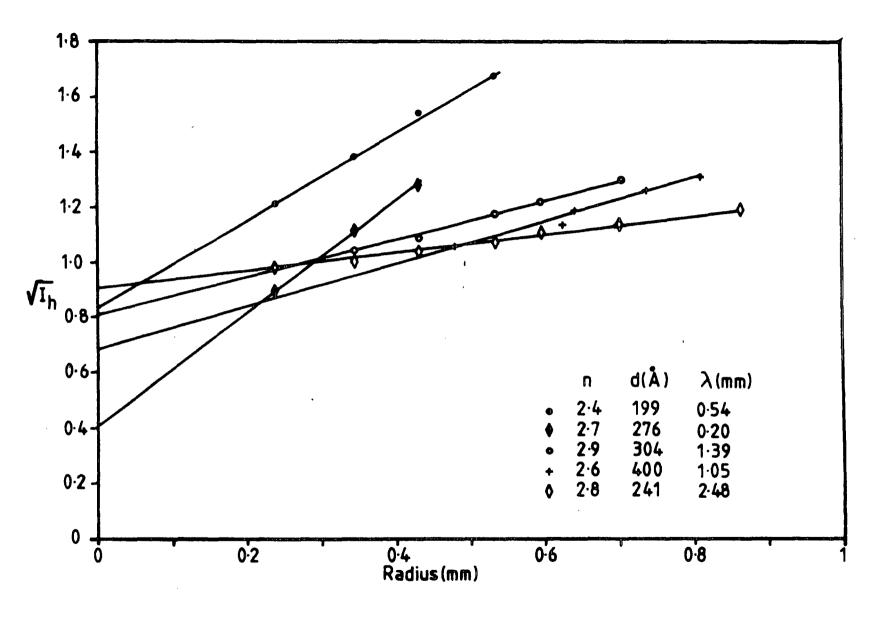

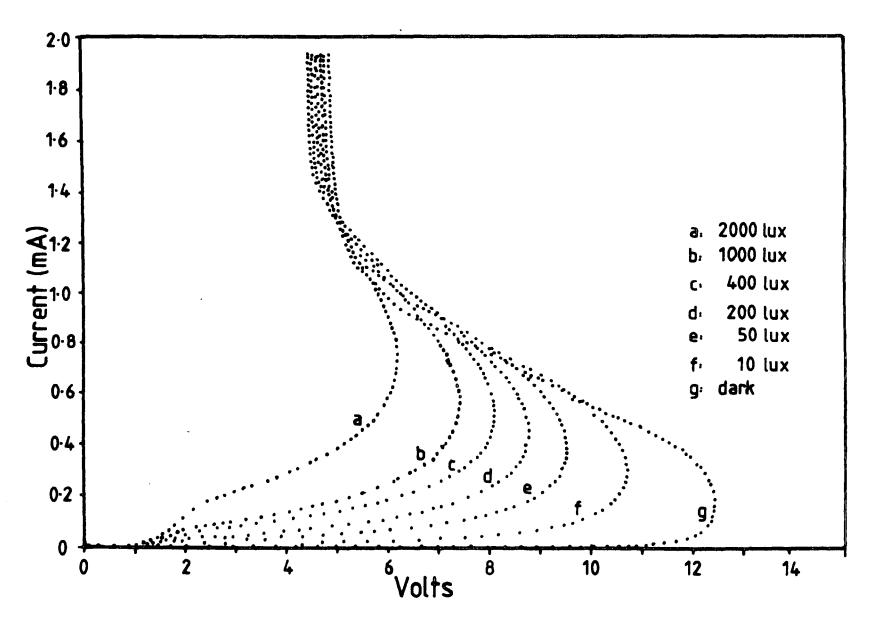

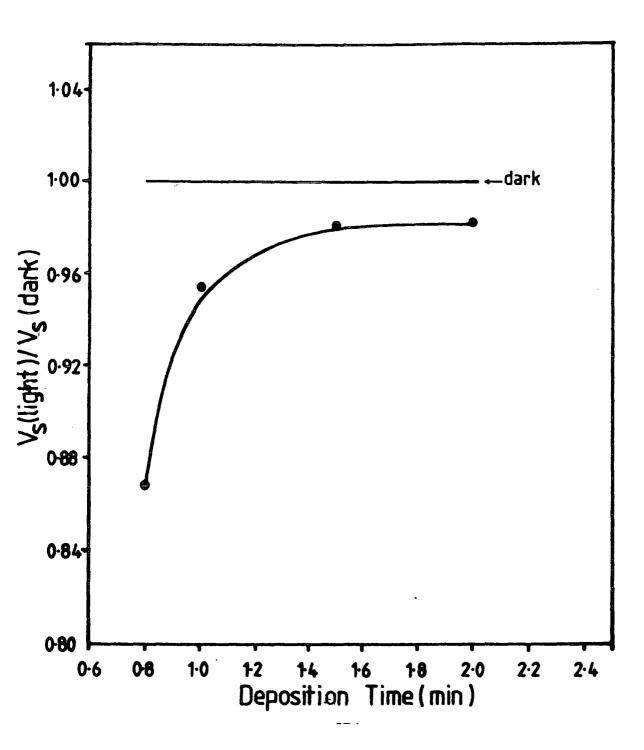

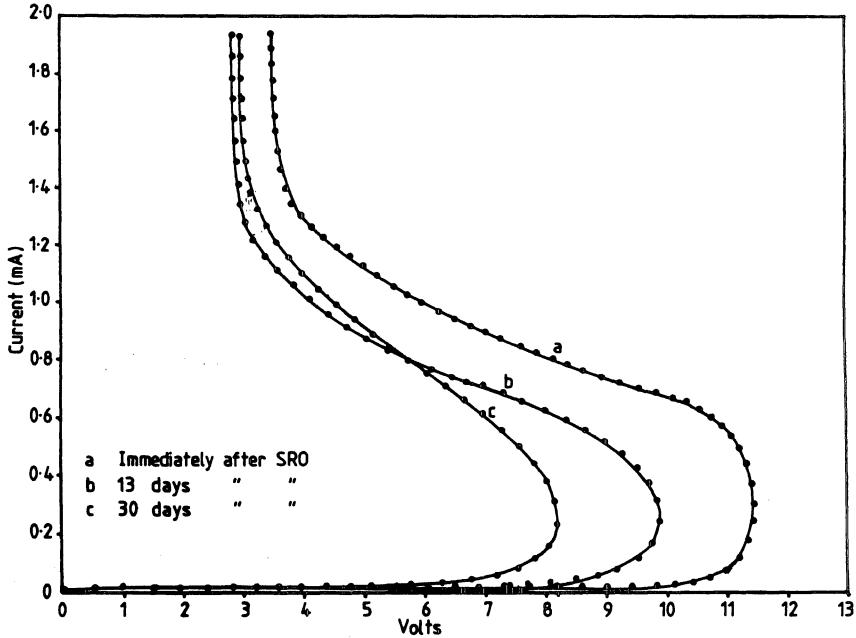

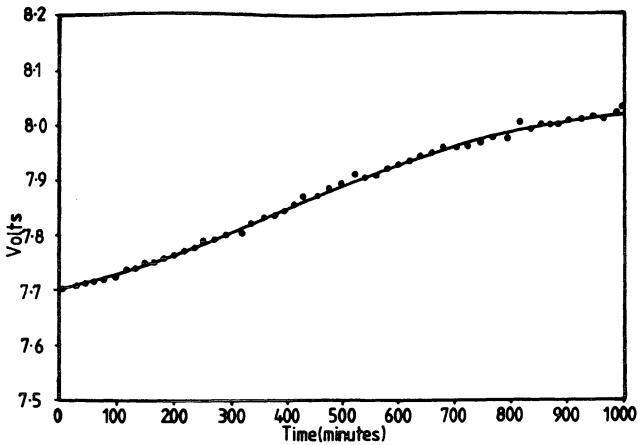

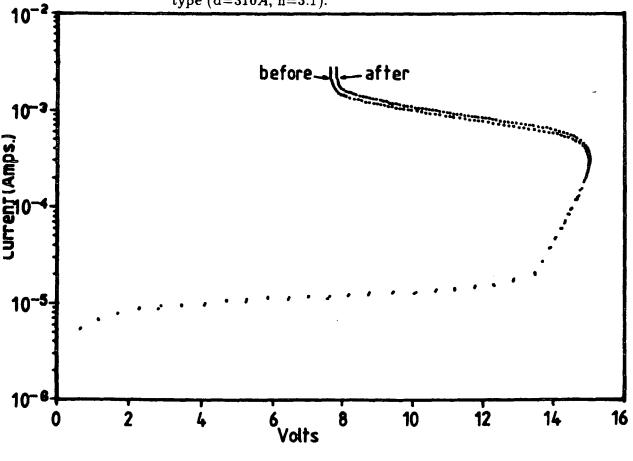

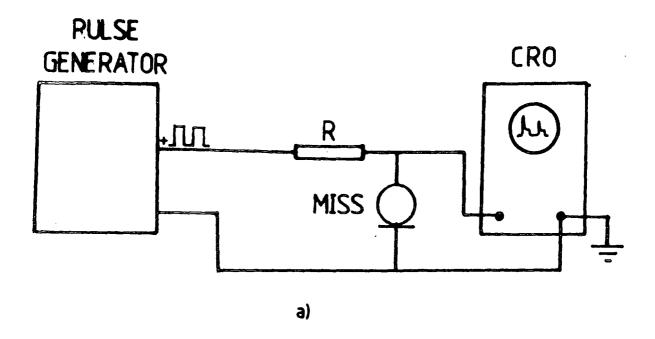

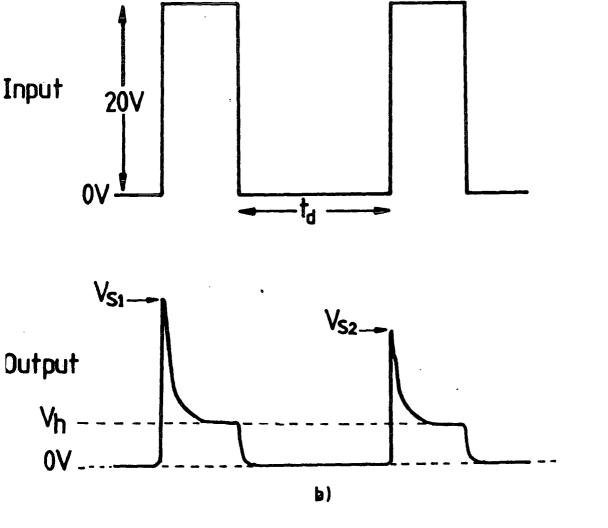

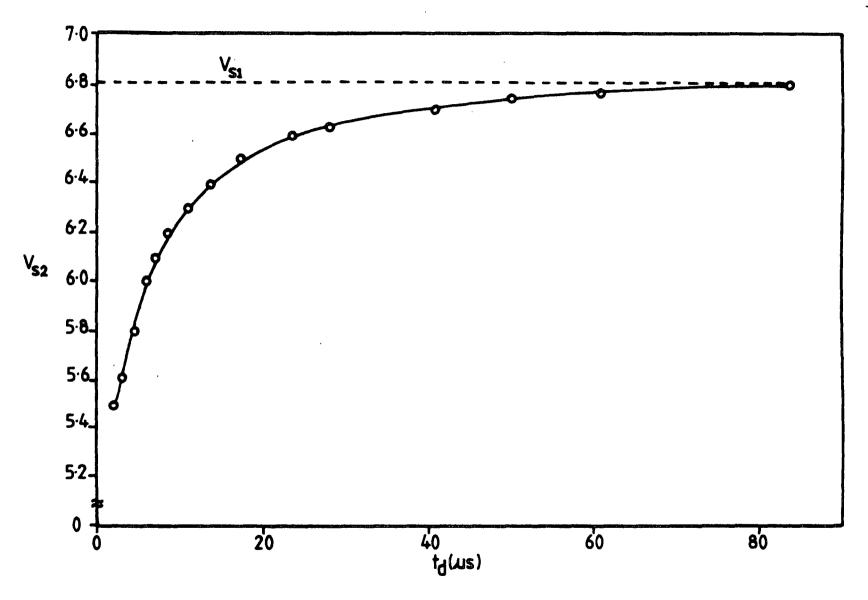

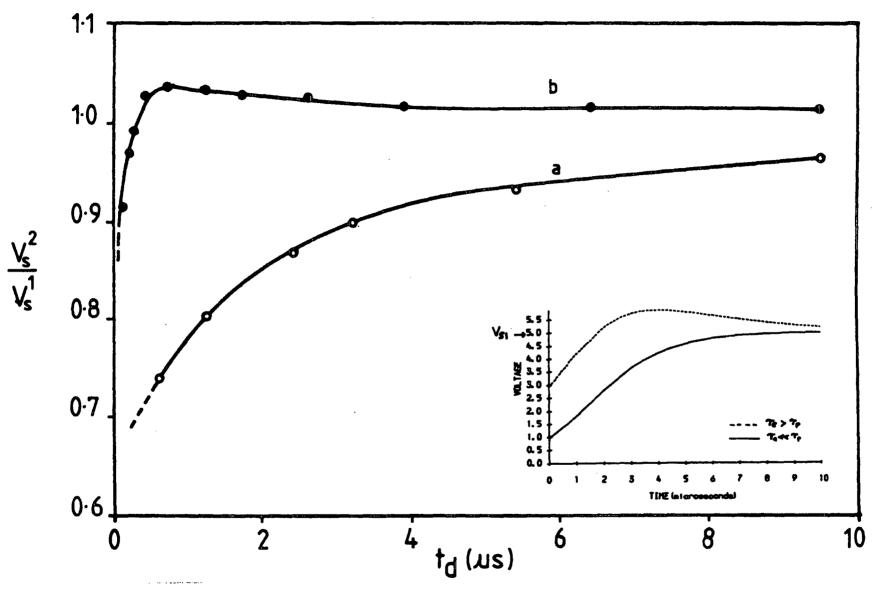

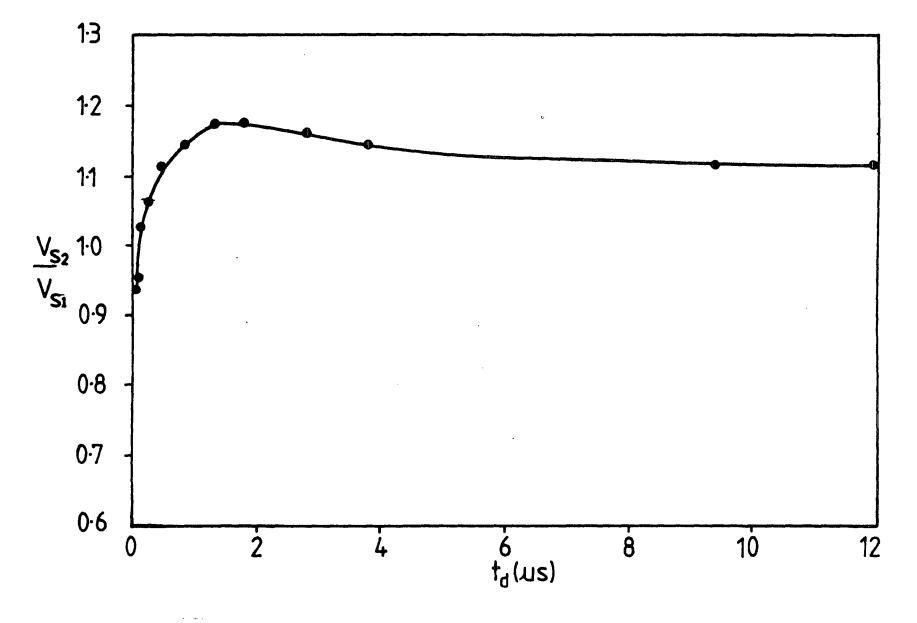

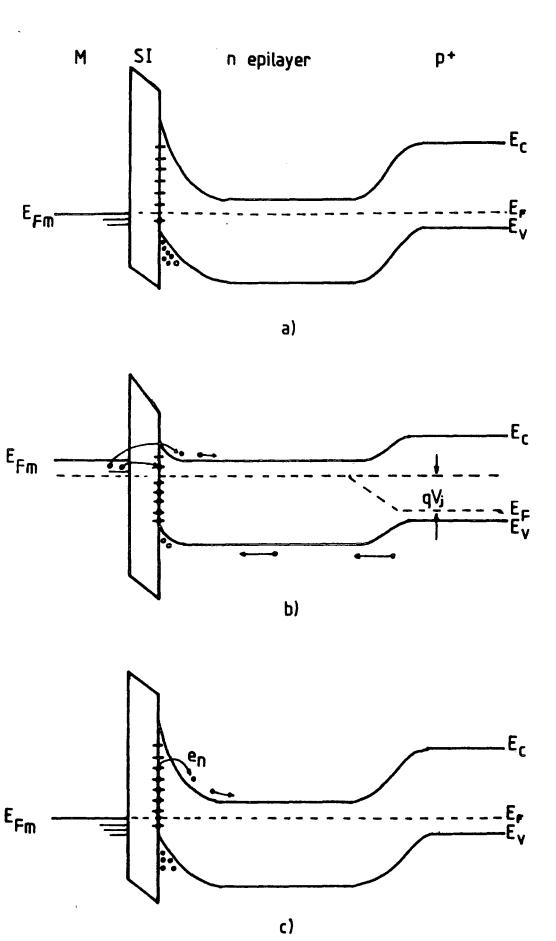

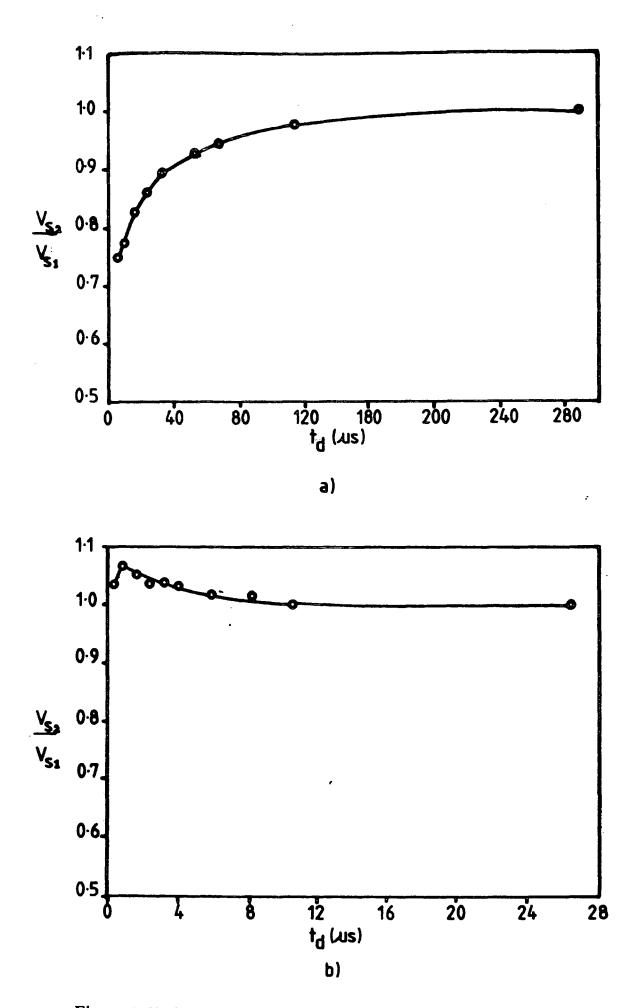

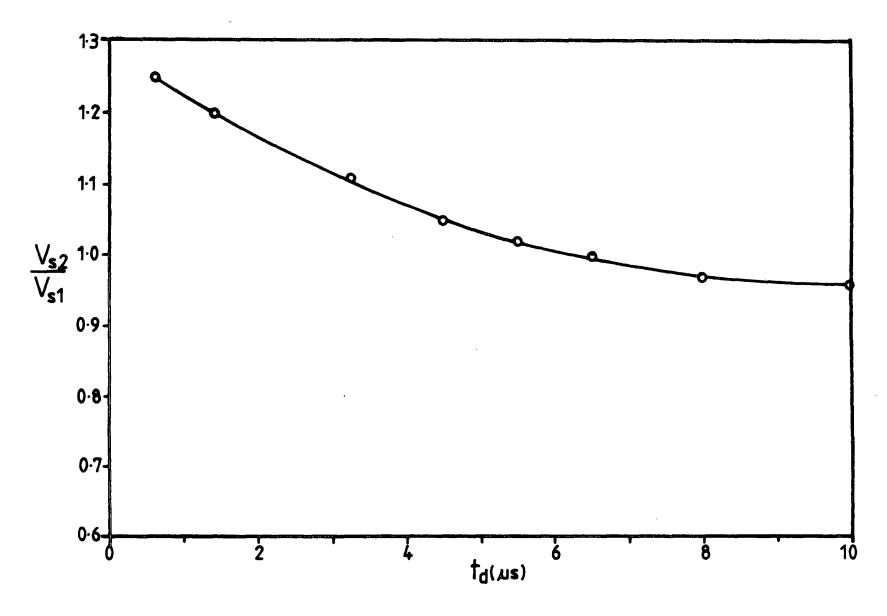

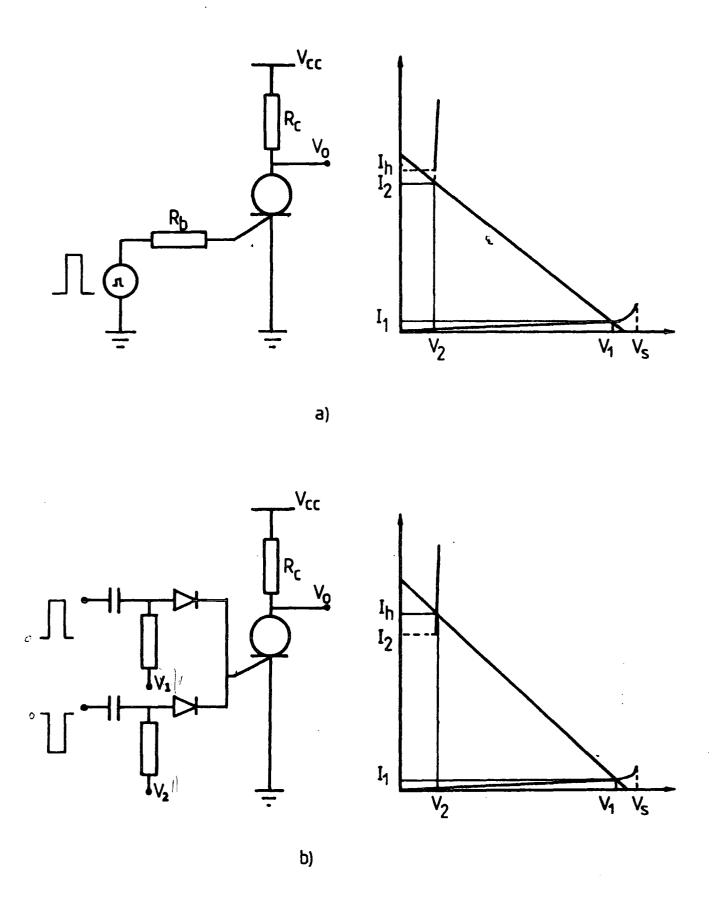

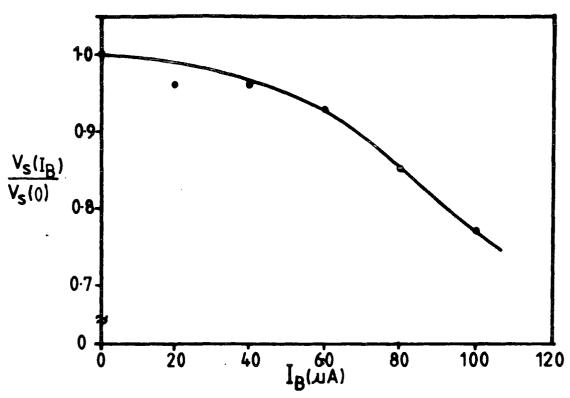

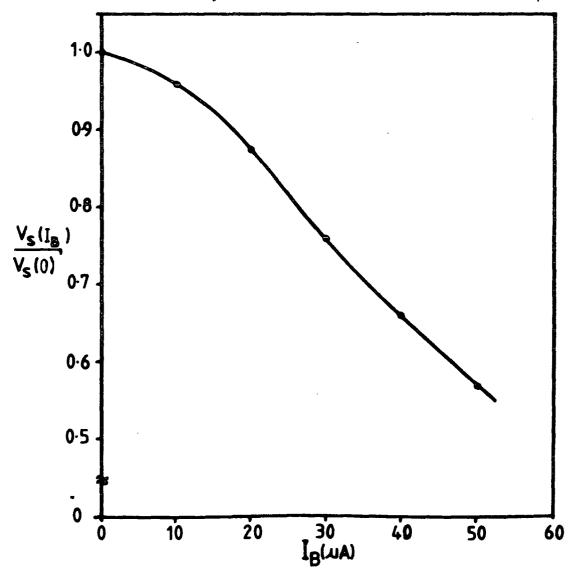

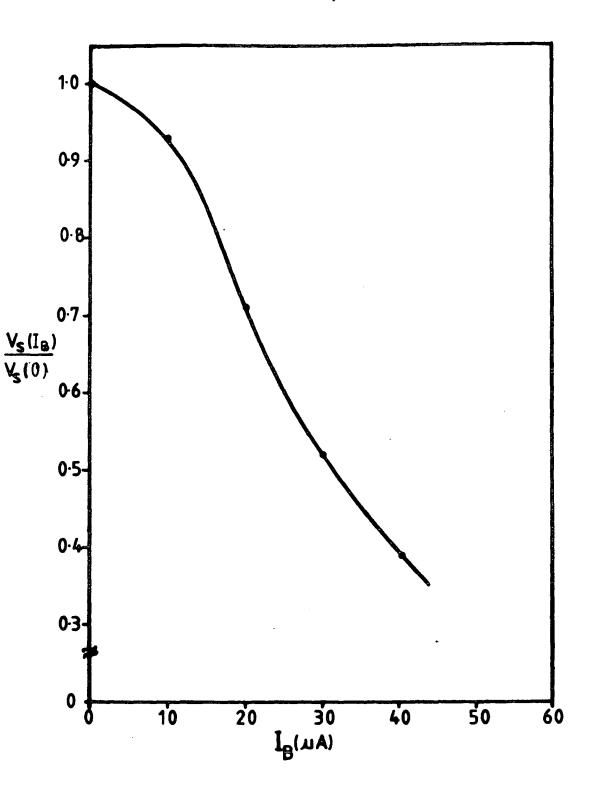

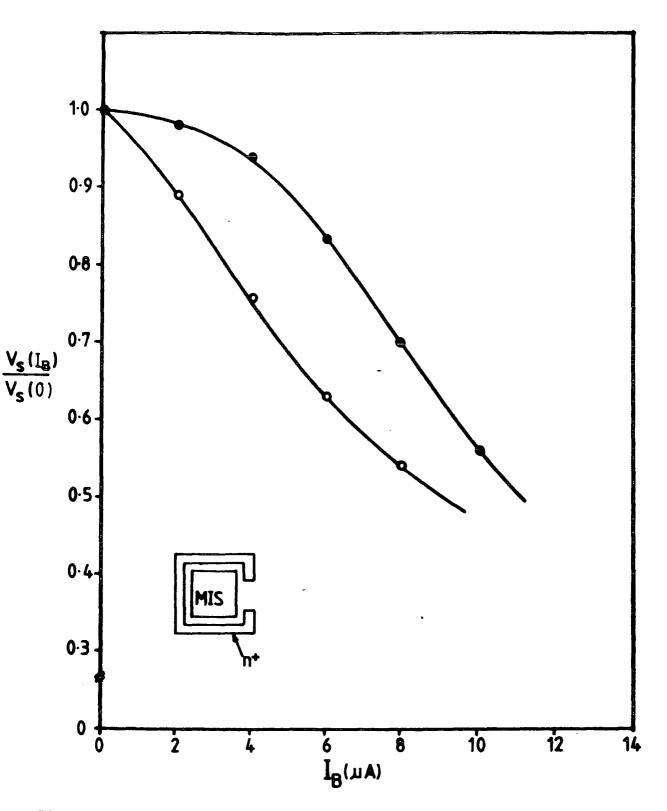

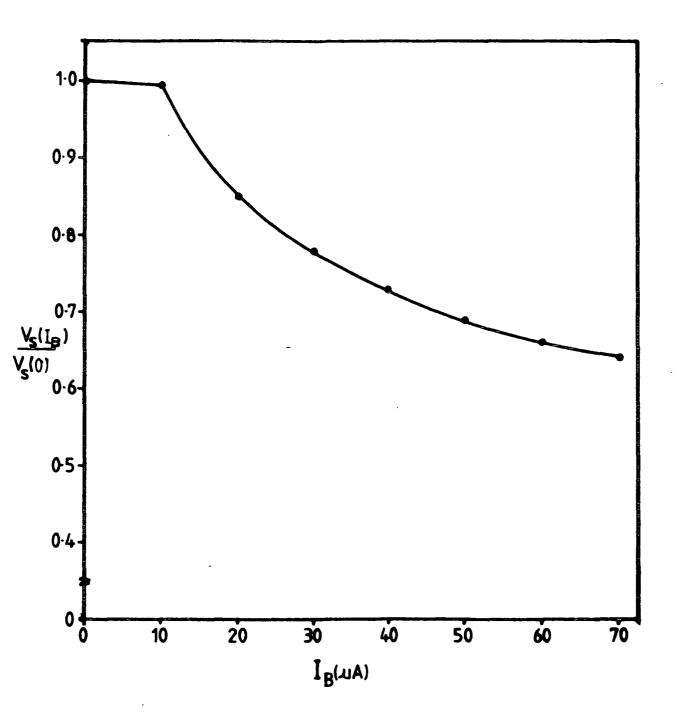

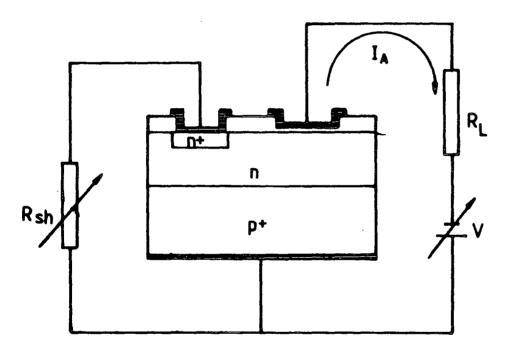

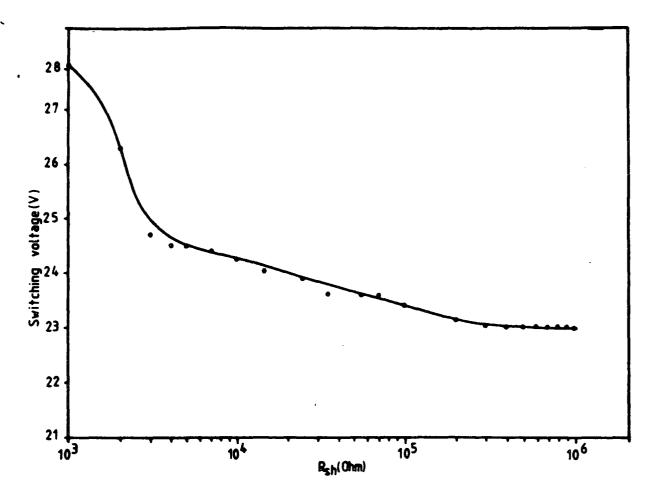

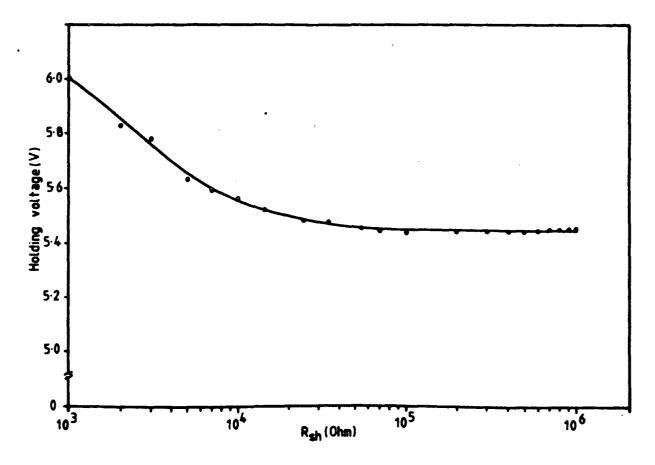

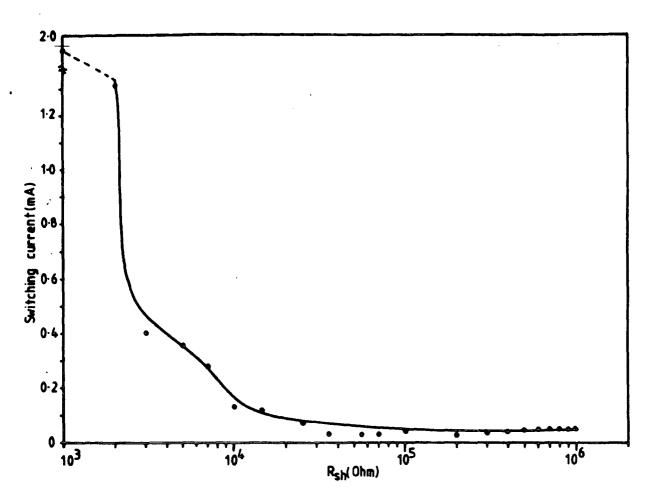

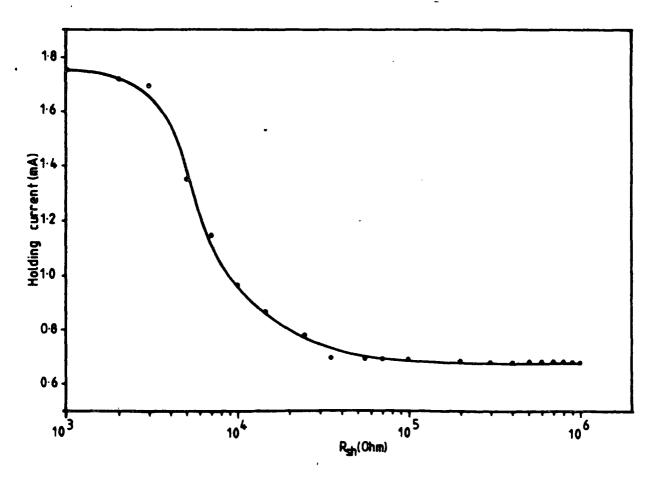

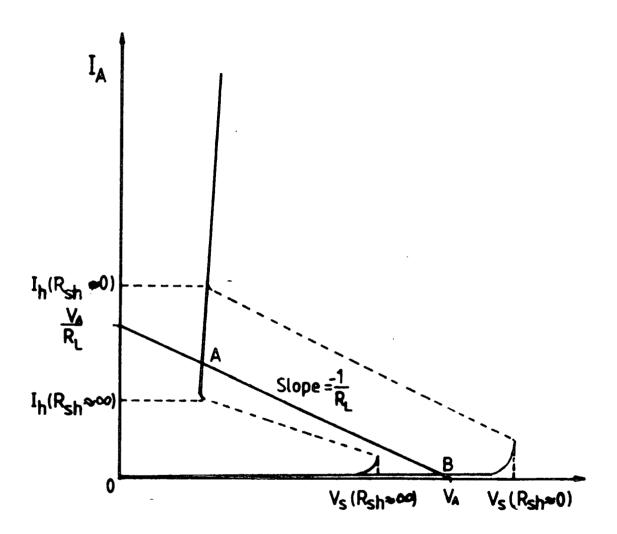

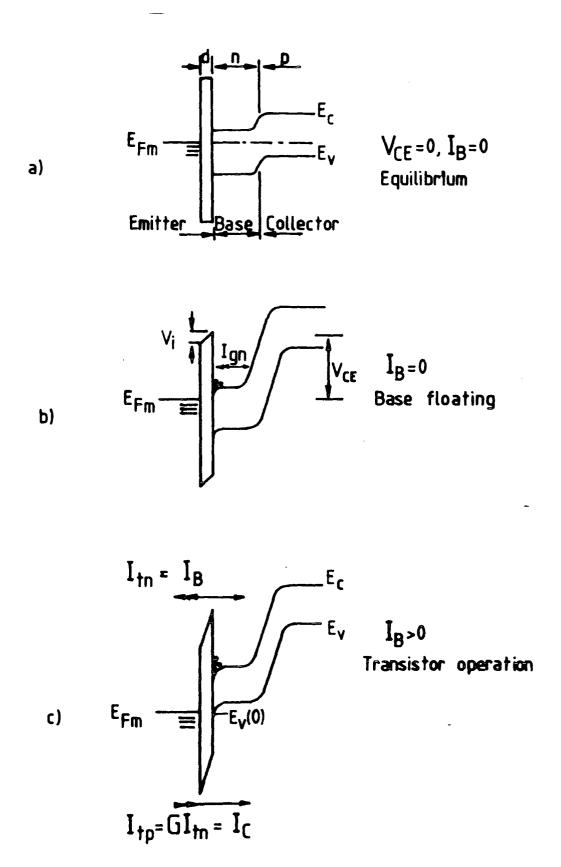

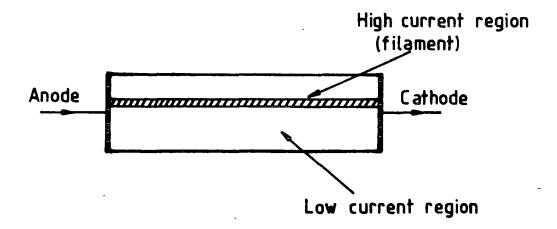

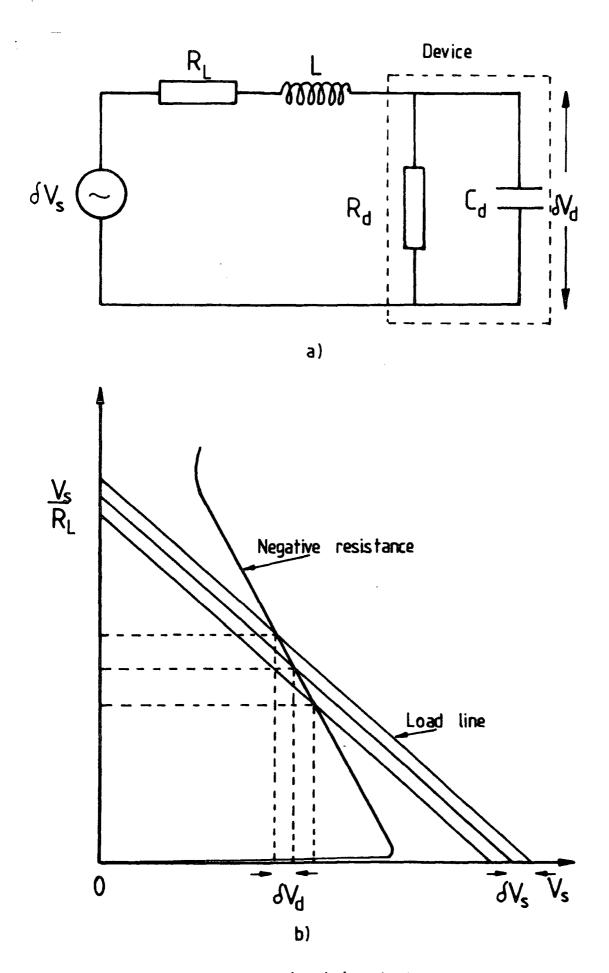

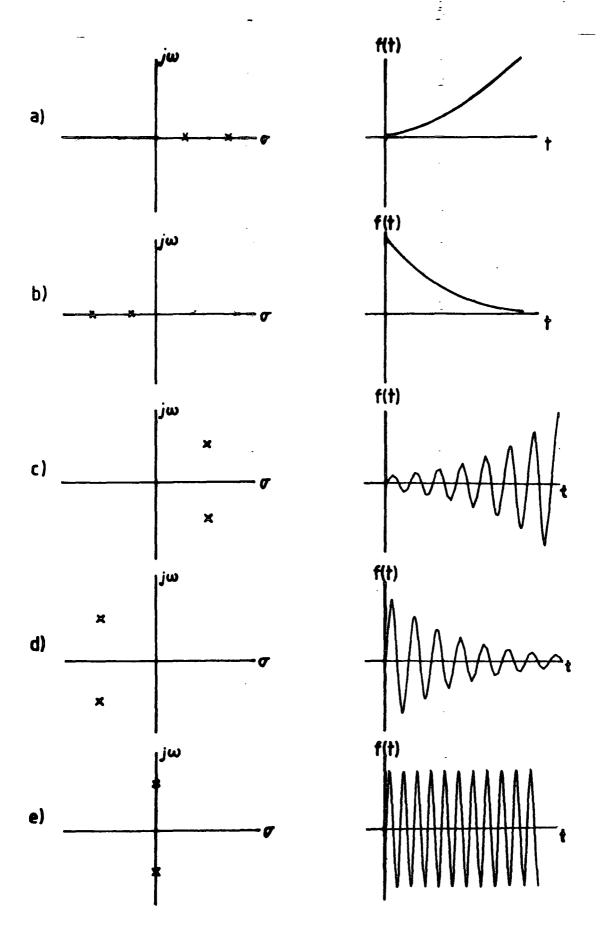

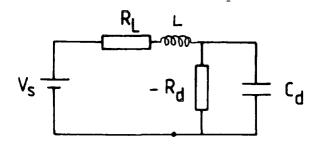

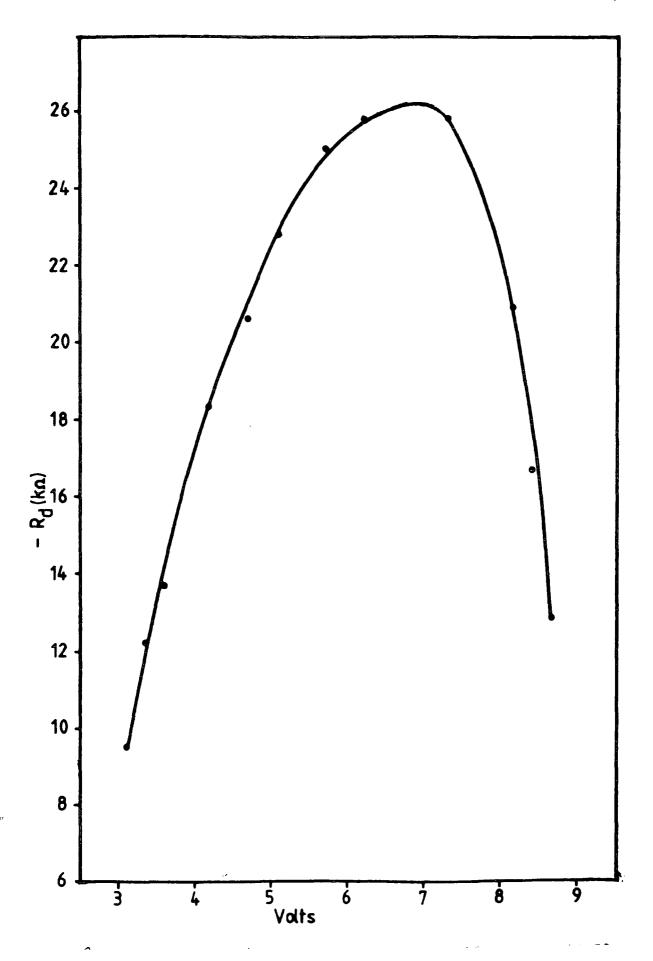

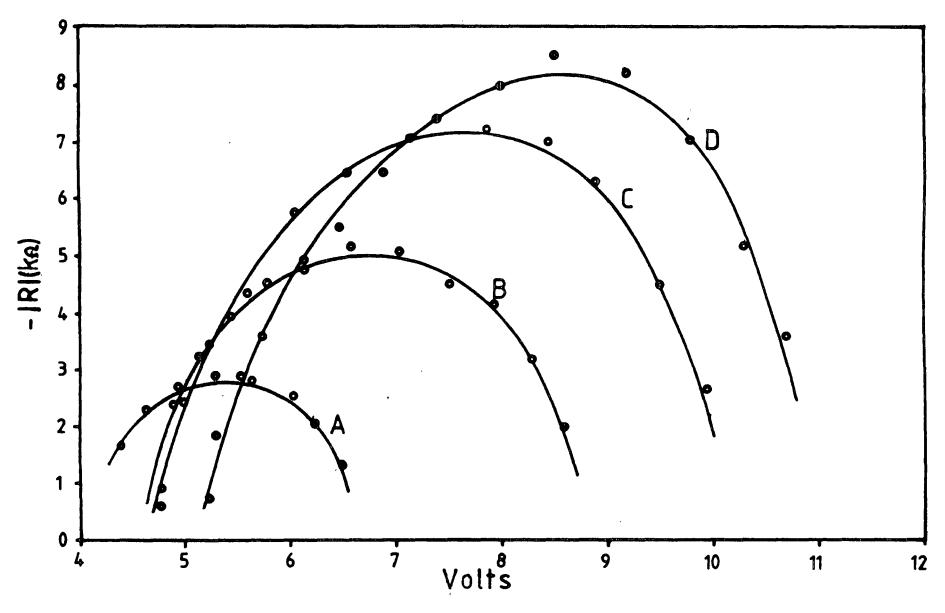

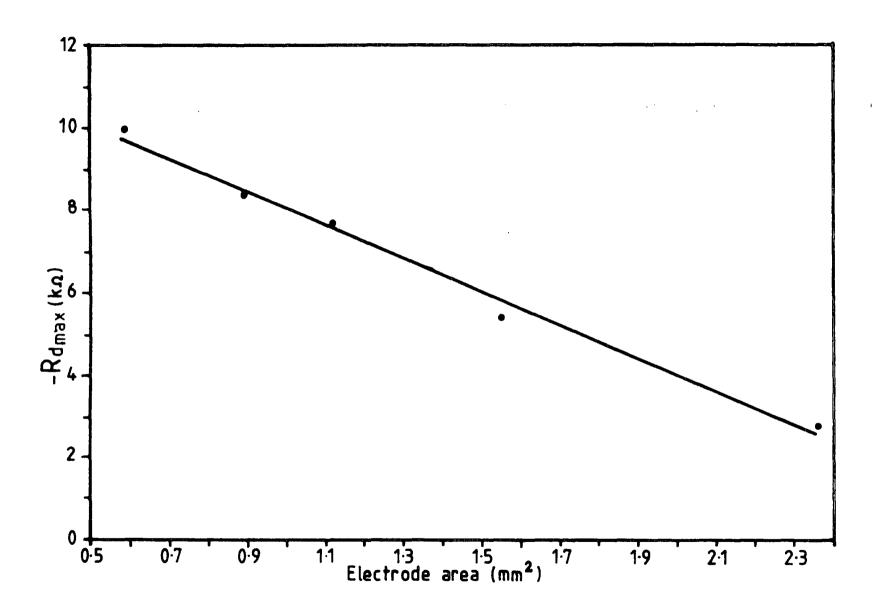

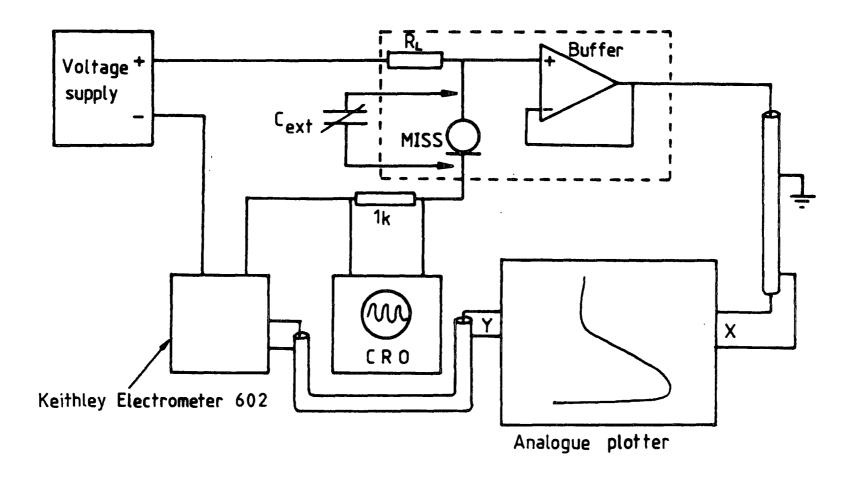

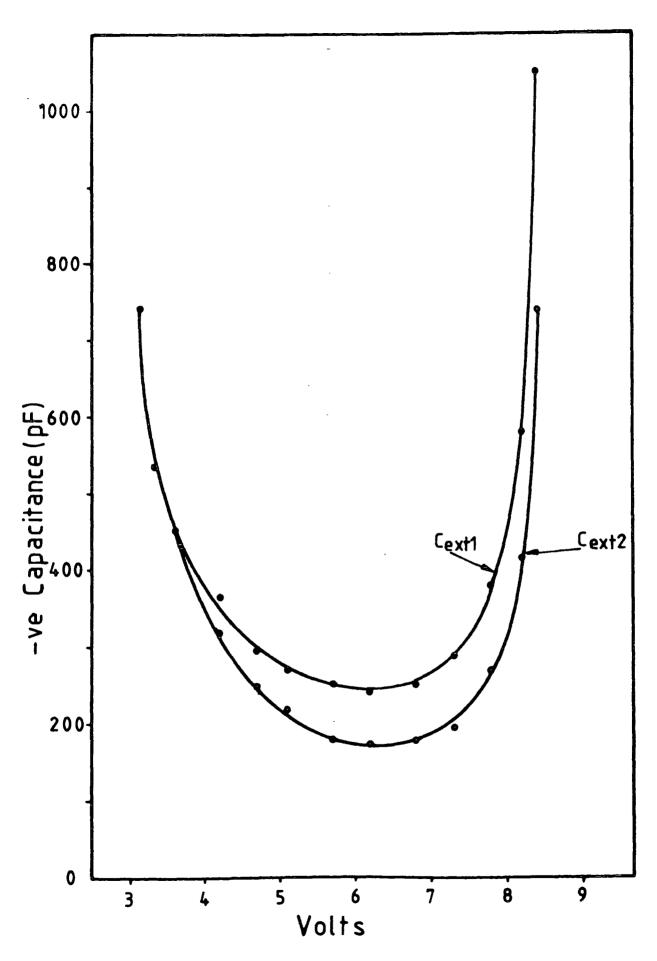

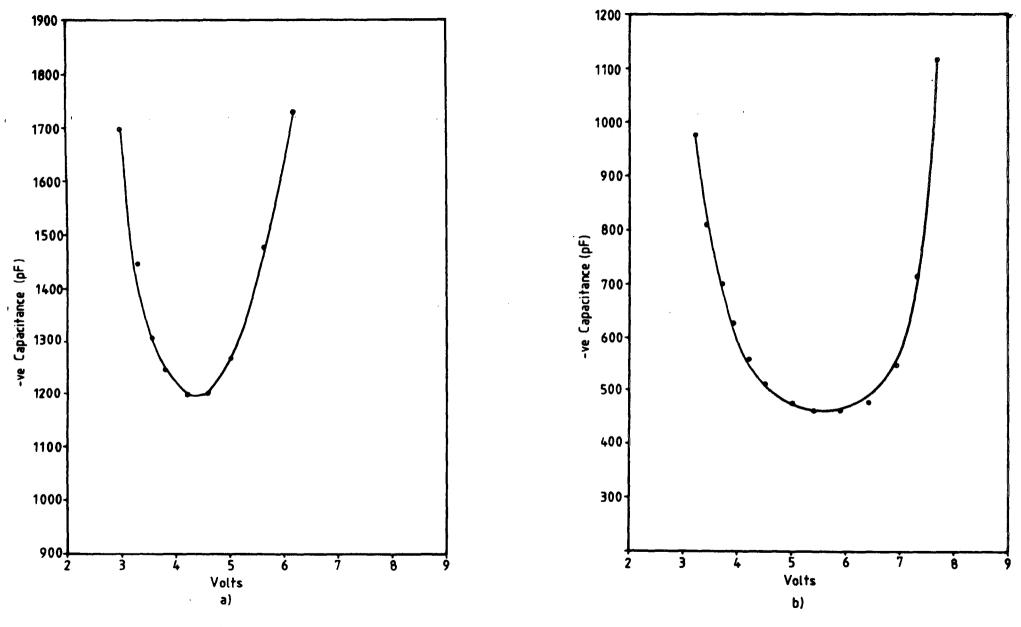

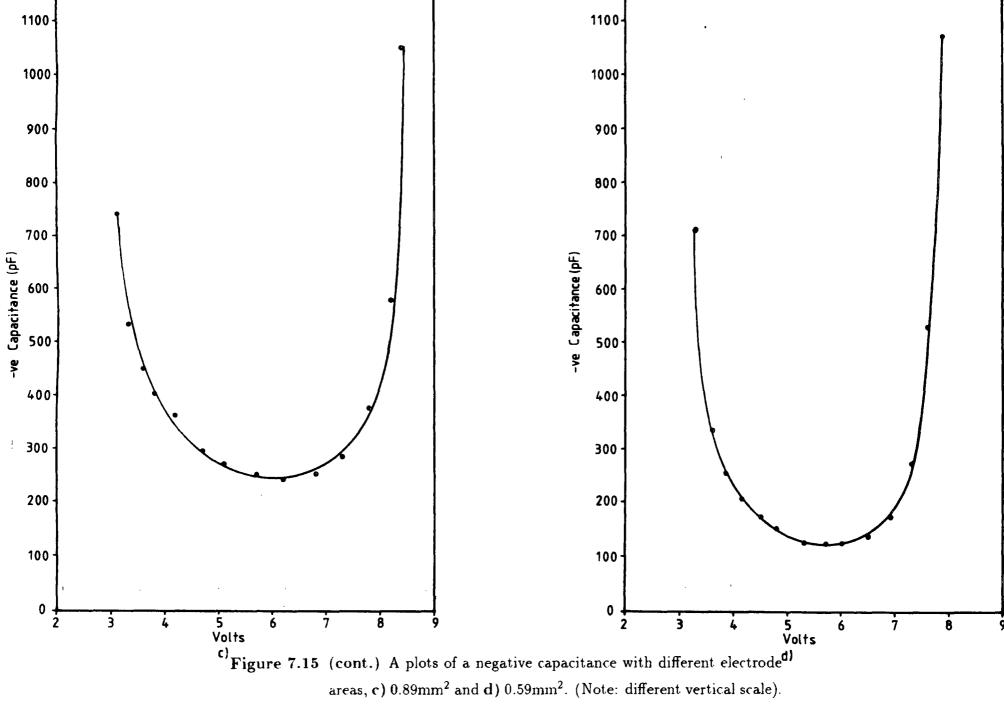

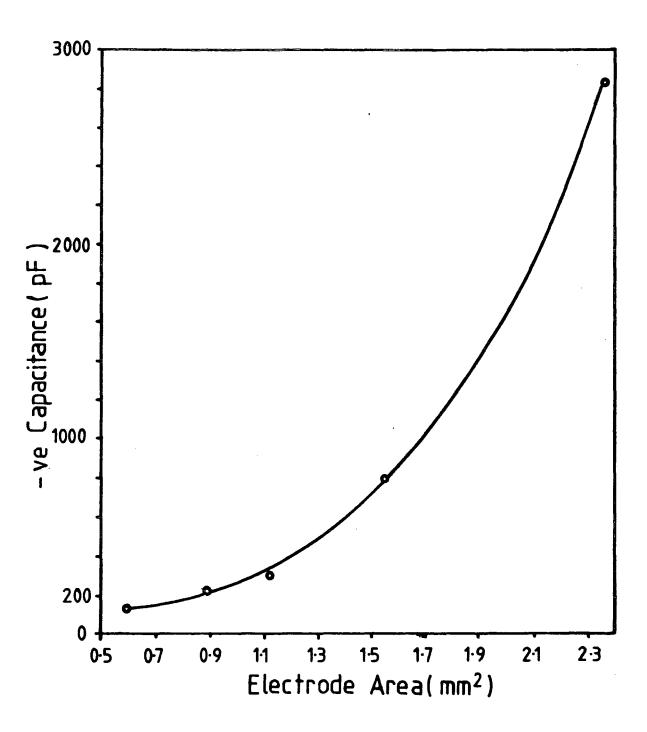

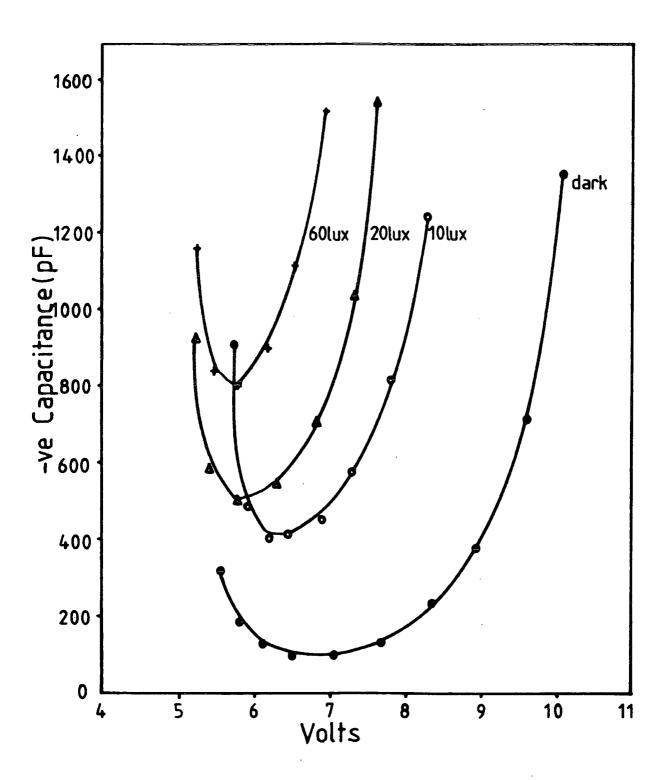

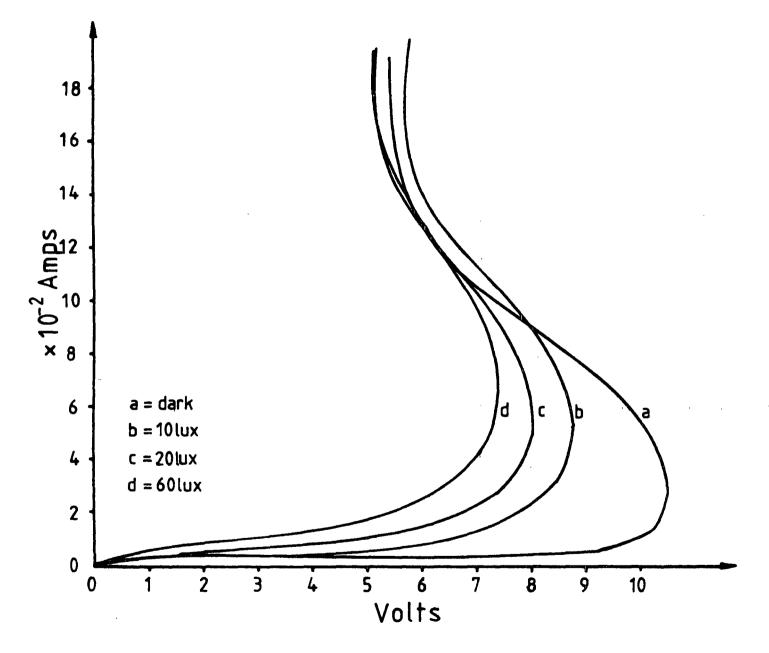

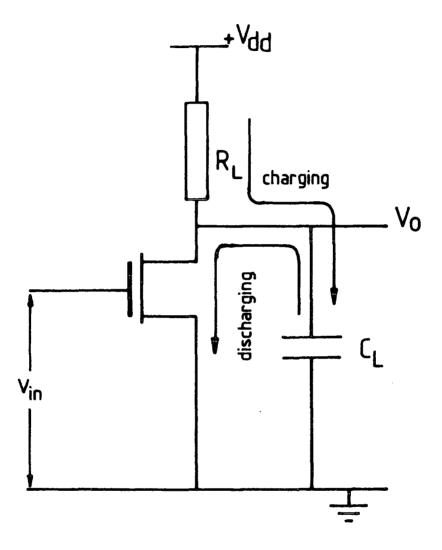

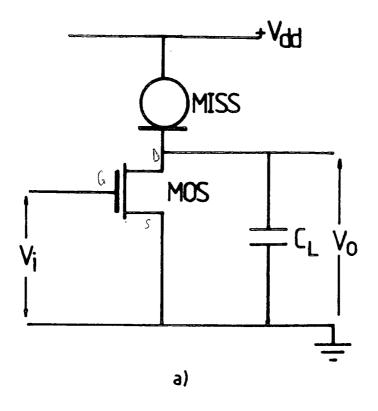

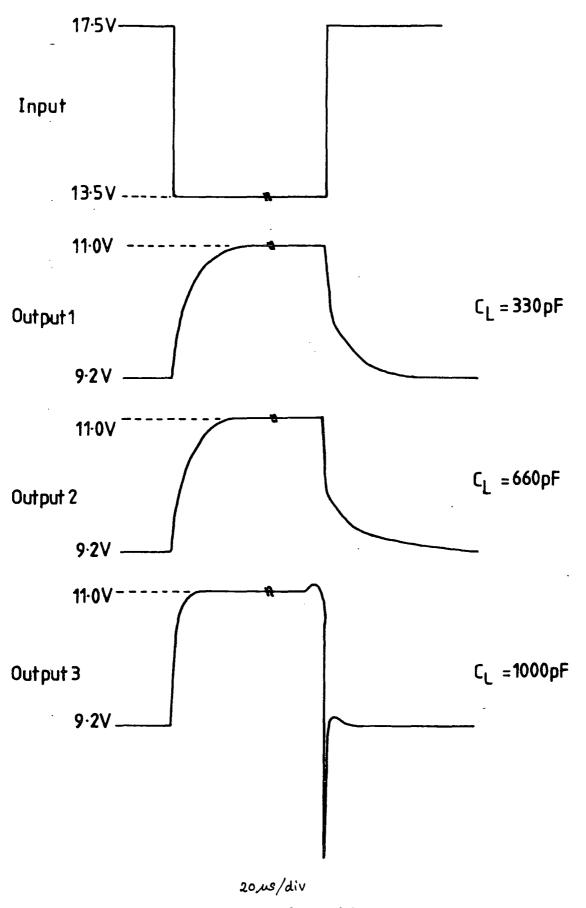

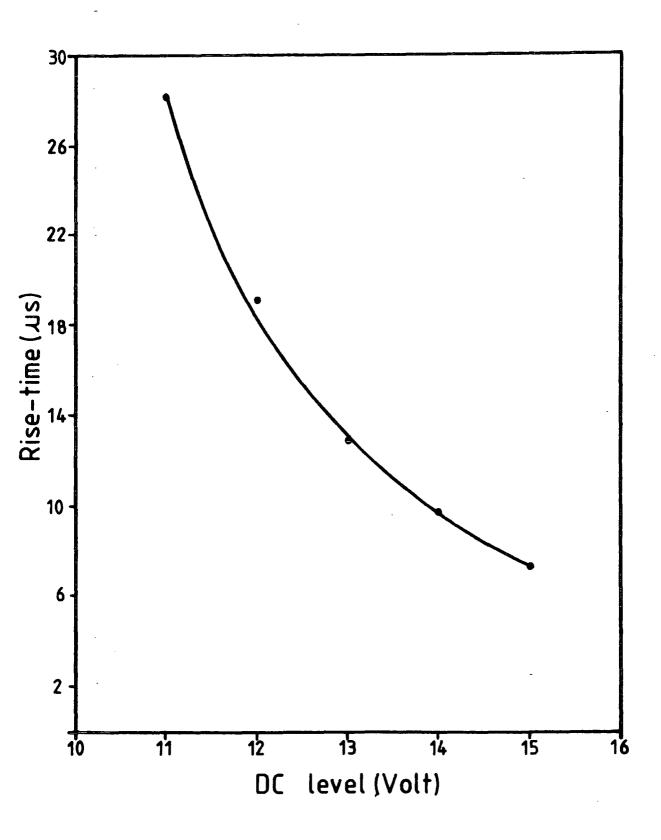

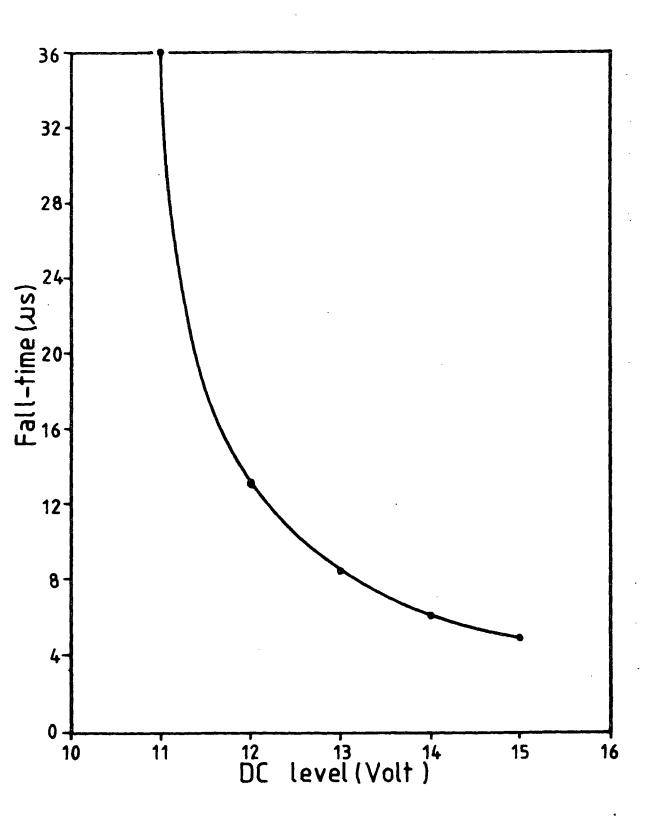

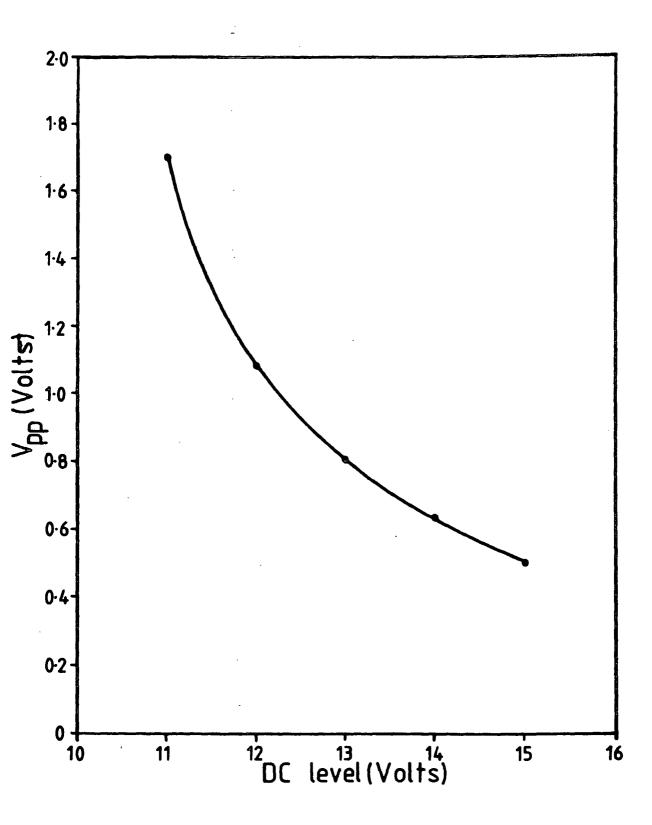

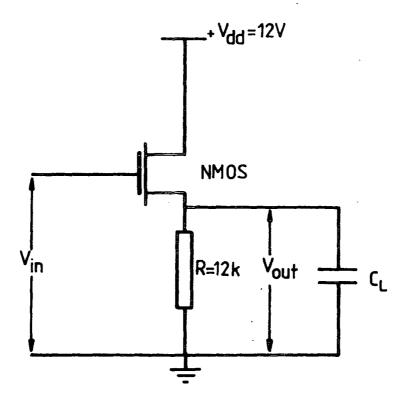

The avalanche voltage of the n-type depletion layer is given by [9],