## **Durham E-Theses**

## Software implemented fault tolerance for microprocessor controllers: fault tolerance for microprocessor controllers

Wingate, Guy A.S.

#### How to cite:

Wingate, Guy A.S. (1992) Software implemented fault tolerance for microprocessor controllers: fault tolerance for microprocessor controllers, Durham theses, Durham University. Available at Durham E-Theses Online: http://etheses.dur.ac.uk/5811/

#### Use policy

$The full-text\ may\ be\ used\ and/or\ reproduced,\ and\ given\ to\ third\ parties\ in\ any\ format\ or\ medium,\ without\ prior\ permission\ or\ charge,\ for\ personal\ research\ or\ study,\ educational,\ or\ not-for-profit\ purposes\ provided\ that:$

- a full bibliographic reference is made to the original source

- a link is made to the metadata record in Durham E-Theses

- the full-text is not changed in any way

The full-text must not be sold in any format or medium without the formal permission of the copyright holders.

Please consult the full Durham E-Theses policy for further details.

Academic Support Office, Durham University, University Office, Old Elvet, Durham DH1 3HP e-mail: e-theses.admin@dur.ac.uk Tel: +44 0191 334 6107 http://etheses.dur.ac.uk The copyright of this thesis rests with the author. No quotation from it should be published without his prior written consent and information derived from it should be acknowledged.

## SOFTWARE IMPLEMENTED FAULT TOLERANCE FOR MICROPROCESSOR CONTROLLERS

by

Guy A.S. Wingate, B.Sc.(Hons), M.Sc.

A Thesis submitted in fulfilment of the requirement for the degree of Doctor of Philosophy

.5

**Engineering Science**

The University of Durham 1992

2 6 AUG 1992

### DECLARATION

None of the work contained within this thesis has previously been submitted for a degree at this or any other university. The work contained in this thesis is not part of a joint research project.

### Copyright ©1992 Guy A.S. Wingate

The copyright of this thesis rests with the author. No quotation from it should be published without Guy A.S. Wingate's prior written consent, and information derived from it should be acknowledged.

### SOFTWARE IMPLEMENTED FAULT TOLERANCE FOR MICROPROCESSOR CONTROLLERS

Guy A.S. Wingate, B.Sc.(Hons), M.Sc.

#### ABSTRACT

It is generally accepted that transient faults are a major cause of failure in microprocessor systems. Industrial controllers with embedded microprocessors are particularly at risk from this type of failure because their working environments are prone to transient disturbances which can generate transient faults.

In order to improve the reliability of processor systems for industrial applications within a limited budget, fault tolerant techniques for uniprocessors are implemented. These techniques aim to identify characteristics of processor operation which are attributed to erroneous behaviour. Once detection is achieved, a programme of restoration activity can be initiated.

This thesis initially develops a previous model of erroneous microprocessor behaviour from which characteristics particular to mal-operation are identified. A new technique is proposed, based on software implemented fault tolerance which, by recognizing a particular behavioural characteristic, facilitates the self-detection of erroneous execution. The technique involves inserting detection mechanisms into the target software. This can be quite a complex process and so a prototype software tool called Post-programming Automated Recovery UTility (PARUT) is developed to automate the technique's application. The utility can be used to apply the proposed behavioural fault tolerant technique for a selection of target processors. Fault injection and emulation experiments assess the effectiveness of the proposed fault tolerant technique for three application programs implemented on an 8, 16, and 32bit processors respectively. The modified application programs are shown to have an improved detection capability and hence reliability when the proposed fault tolerant technique is applied. General assessment of the technique cannot be made, however, because its effectiveness is application specific.

The thesis concludes by considering methods of generating non-hazardous application programs at the compilation stage, and design features for incorporation into the architecture of a microprocessor which inherently reduce the hazard, and increase the detection capability of the target software. Particular suggestions are made to add a 'PARUT' phase to the translation process, and to orientate microprocessor design towards the instruction opcode map.

#### ACKNOWLEDGEMENTS

Firstly, I would like to thank my supervisor Dr. Clive Preece for his tremendous support and encouragement throughout the duration of the research project. I am also grateful to British Gas plc. for funding the research; in particular I would like to thank Dr. Ken Jenkins and colleagues at the Engineering Research Station, Killingworth. In addition, I owe thanks to: Prof. Ed Czeck (Computer Science, Carnegie-Mellon University, USA) for his comments on the work contained within Chapter 5 and 7; Mr. Alan Timothy (Microprocessor Centre, University of Durham) for comments on the design and implementation of an Advanced Micro Device Am29000 processor system C compiler and its implications on the work presented in Chapter 8; Prof. Dan Siewiorek (Carnegie-Mellon University, USA), Dr. Janusz Sosnowski (Warsaw Technical University, Poland), and Prof. Hermann Kopetz (Vienna Technical University, Austria) for the provision of details of their related research; and finally, Mr. Jim Roper (Computer Science, University of Durham) and Dr. Per Nylen (University of Stockholm, Sweden) for access to an Intel 80386 processor and Motorola 68(7)05 processor emulator respectively.

My time at Durham has not been all work! I would like to thank my friends over the years for making my stay so enjoyable: especially the 'tea room boys' – Sabah, Lee, Ken, Jean, and Norman; Hatfield College Middle Common Room; and the university squash and badminton teams for helping me release tension. Thanks also to Grandma for constant provision of orange cake.

Whilst writing this thesis I have phoned home many times to report "It's finished !". The natural reply soon became "Except for ... ?". Lastly then, I would like to thank my parents and my fianc e Sarah for their patient support and to assure them that I really have finished.

(Submitted November 1990)

The examination of this thesis was delayed by illness. I would like to thank the staff of Dryburn Hospital (County Durham), and R.N.H. Haslar (Gosport, Hants) for their care in the intervening period.

(Examined April 1992)

"Bloody instructions, which, being learned, return to plague the inventor."

> 'Macbeth': Act 1, Scene 7, Lines 8-10 by William Shakespeare.

> > v

المتعارين العالي فتراجع التناكين

2 T T S A 1 MAR 7

100.001

| ABSTRACT                | iii  |

|-------------------------|------|

| ACKNOWLEDGEMENTS        | iv   |

| CONTENTS                | vi   |

| LIST OF FIGURES         | xiv  |

| LIST OF TABLES          | xvi  |

| LIST OF ABBREVIATIONS x | viii |

| LIST OF SYMBOLS         | xx   |

## Chapter 1

18 - 587 C. S. S. A.

### RELIABILITY AND MICROPROCESSOR-BASED CONTROLLERS

| 1.1. | Introduction                                       | 1 |

|------|----------------------------------------------------|---|

| 1.2. | Microprocessor-Based Control Systems               | 3 |

| 1.3. | Faults, Errors, and Failures in Electronic Systems | 4 |

| 1.4. | Engineering Reliability Through Design             | 4 |

|      | 1.4.1. Reliable Hardware                           | 5 |

|      | 1.4.2. Reliable Software                           | 5 |

| 1.5. | Evaluating Controller Reliability                  | 6 |

|      | 1.5.1. Hardware Reliability                        | 7 |

|      | 1.5.2. Software Reliability                        | 7 |

|      | 1.5.3. Interface Reliability                       | 8 |

| 1.6. | Low-Cost Enhancement of Controller Reliability     | 8 |

| 1.7. | Thesis Preview                                     | 9 |

## Chapter 2

170

### TEMPORARY FAULTS: GENERATION, IMPLICATION, & DETECTION

| 2.1. | Introduction                                                      | 12 |

|------|-------------------------------------------------------------------|----|

| 2.2. | Faults and Their Implication on Microprocessor System Reliability | 13 |

| 2.3. | Erroneous Behaviour of Microprocessor Systems                     | 18 |

|      | 2.3.1. Data Flow Errors                                           | 21 |

|      | 2.3.3. Program Flow Errors                                        | 21 |

| 2.4. | Assessing Error Detection Techniques for Microprocessor Systems   | 23 |

|      | 2.4.1. Watchdog Timers                                            | 23 |

|      | 2.4.2. Capability Checking                                        | 23 |

|      | 2.4.3. Program Flow Monitoring                                    | 24 |

|      | 2.4.4. Hazards Associated with Error Detection Techniques         | 27 |

|      | 2.4.5. A Novel Error Detection Technique                          | 27 |

| 2.5. | Reliability Evaluation                                            | 28 |

| 2.6. | Summary and Conclusions                                           | 29 |

## Chapter 3

### MODELLING ERRONEOUS MICROPROCESSOR BEHAVIOUR

| 3.1. | Introduction                                              | 31 |

|------|-----------------------------------------------------------|----|

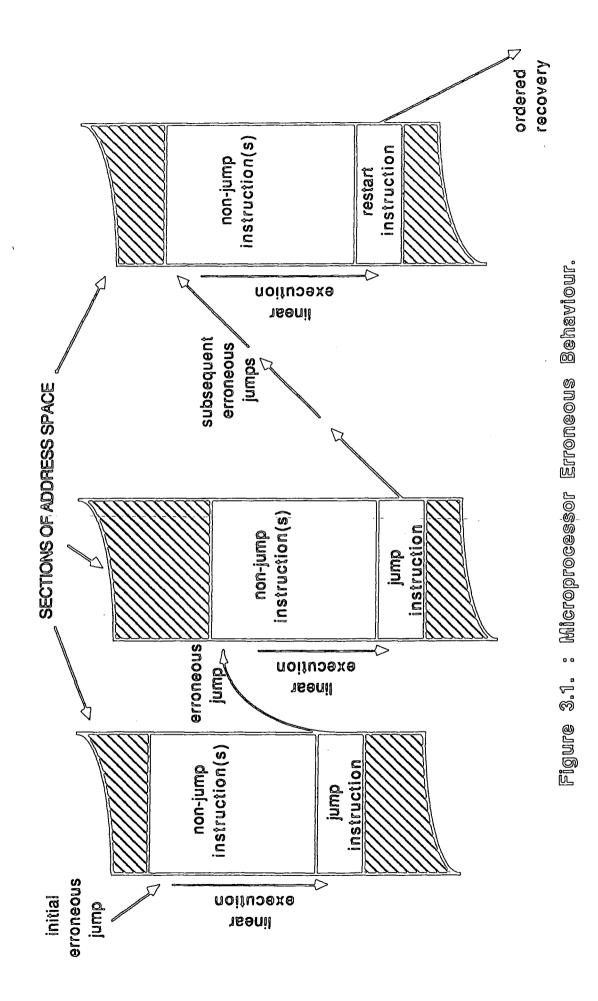

| 3.2. | Initiating Erroneous Microprocessor Behaviour             | 31 |

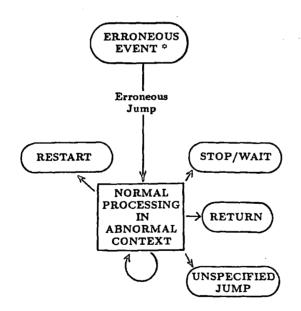

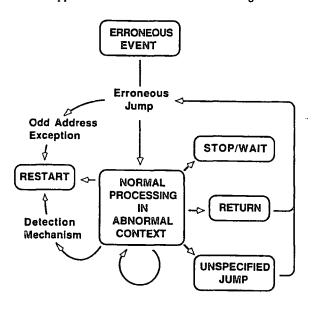

| 3.3. | Erroneous Behaviour                                       | 32 |

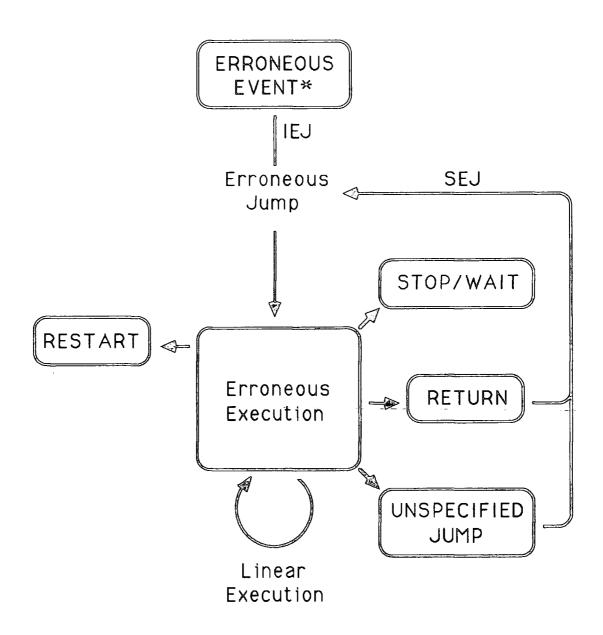

| 3.4. | Erroneous Execution                                       | 34 |

| 3.5. | Halse Execution Model                                     | 36 |

| 3.6. | Hybrid Execution Model                                    | 38 |

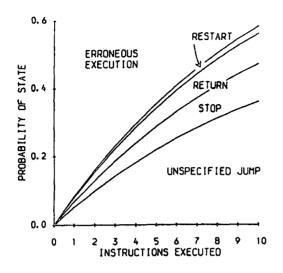

|      | 3.6.1. Linear Erroneous Execution                         | 38 |

|      | 3.6.2. Propagating Further Periods of Erroneous Execution | 40 |

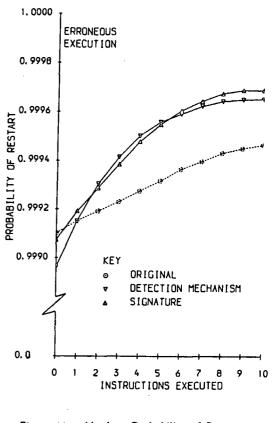

|      | 3.6.3. Detection of Erroneous Execution                   | 41 |

|      | 3.6.4. Erroneous Execution Stall                          | 44 |

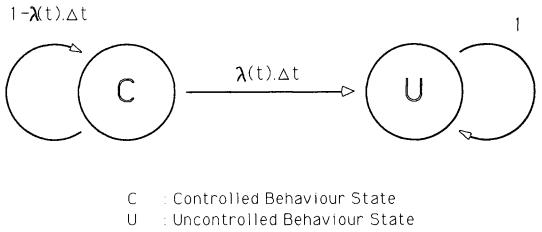

| 3.7. | Reliability Analysis                                      | 45 |

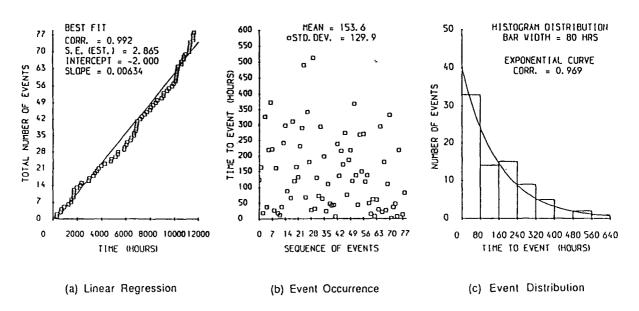

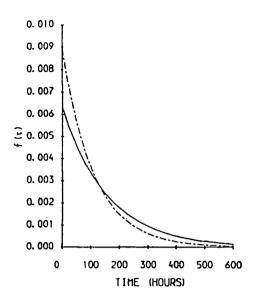

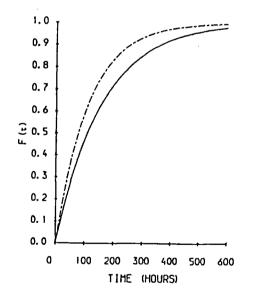

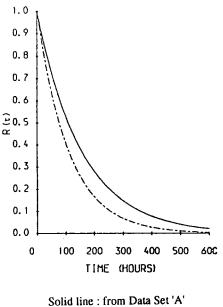

|      | 3.7.1. Failure Rate                                       | 46 |

|      | 3.7.2. Probability of an Event Leading to Failure         | 48 |

|      | 3.7.3. Reliability Evaluation                             | 49 |

|      | 3.7.4. Mean Time To Failure                               | 51 |

| 3.8. | Availability Analysis                                     | 52 |

| 3.9. | Summary                                                   | 53 |

## Chapter 4

### EVALUATING MICROPROCESSOR BEHAVIOUR

| Introduction                                            | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Instruction Mix Analysis                                | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Architecture Parameters for the Microprocessor Model    | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4.3.1. Built-In Microprocessor Detection Capability     | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4.3.2. Modelling the Microprocessor Program Counter     | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4.3.3. Instruction Processing Exceptions                | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Evaluating Microprocessor Models of Erroneous Behaviour | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

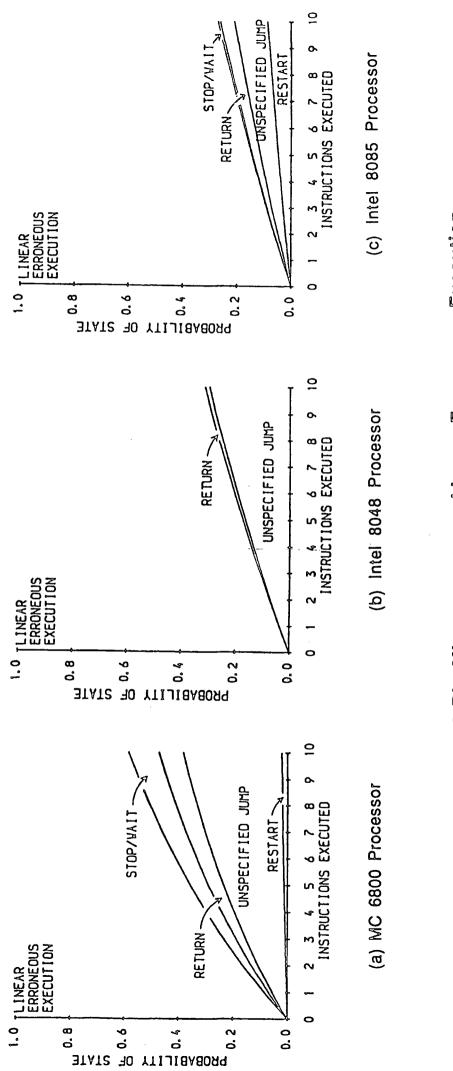

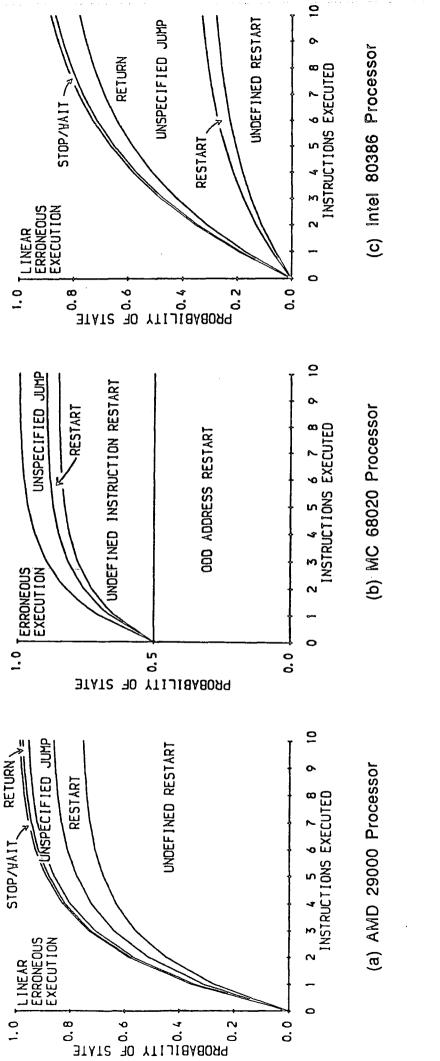

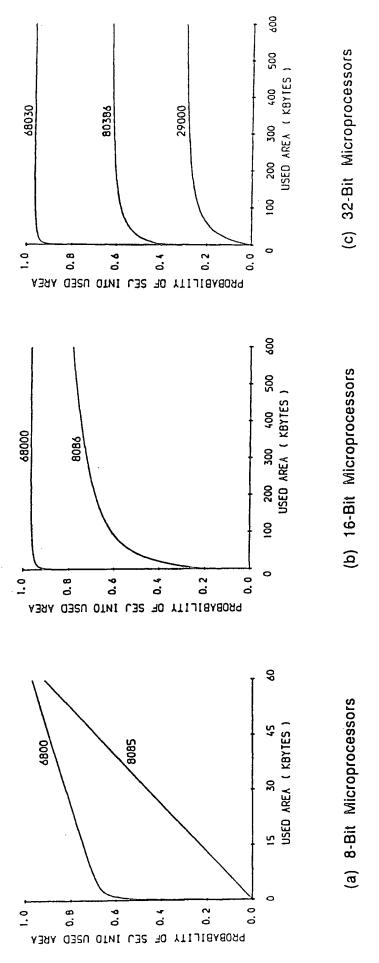

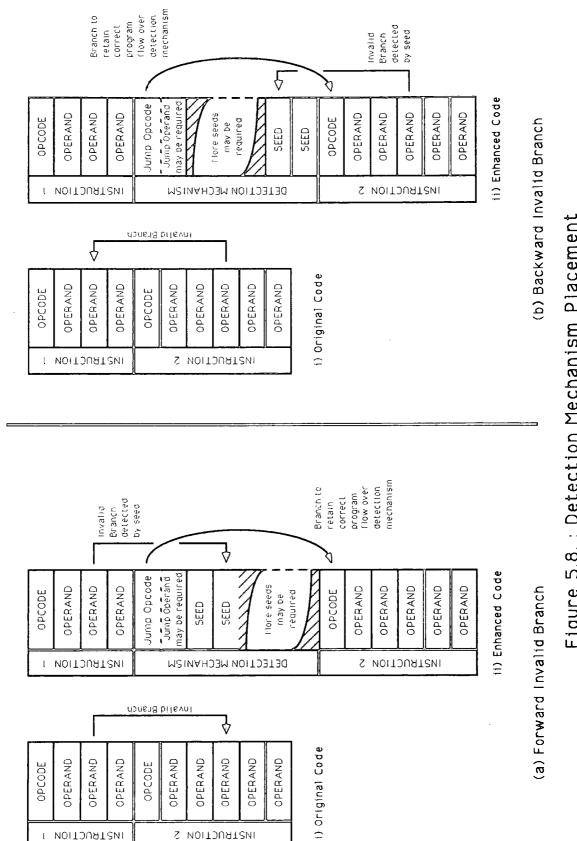

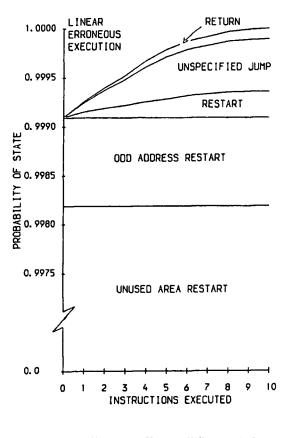

| 4.4.1. 8-Bit Processor Evaluations                      | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

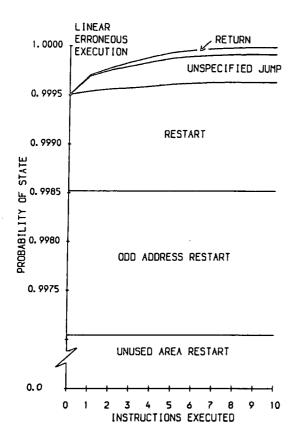

| 4.4.2. 16-Bit Processor Evaluations                     | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

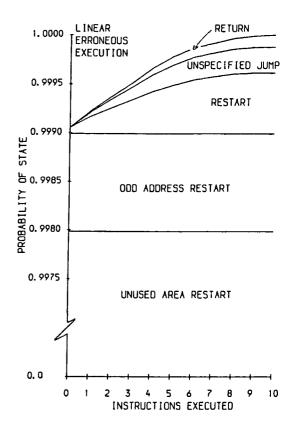

| 4.4.3. 32-Bit Processor Evaluations                     | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

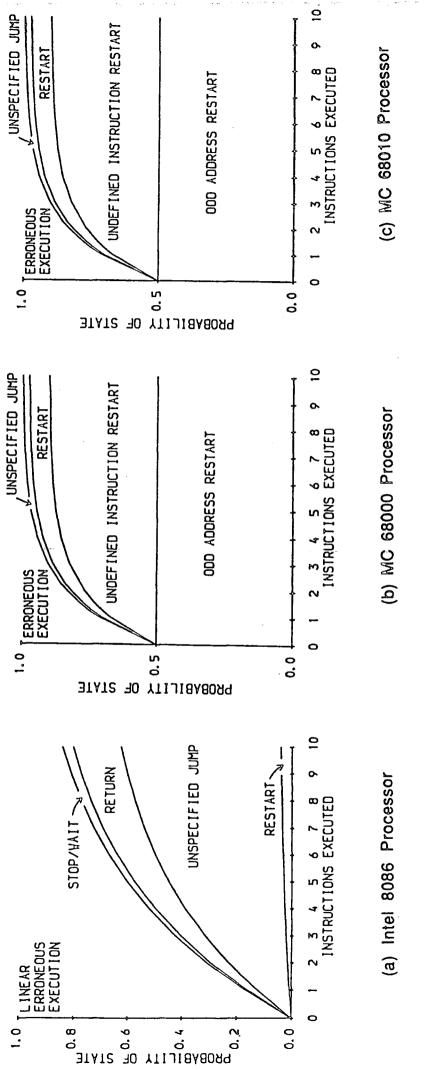

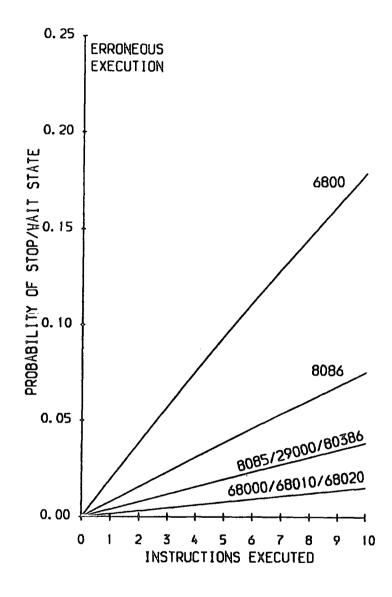

| Catastrophic Failure Analysis                           | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Recovery Through The Detection of Erroneous Execution   | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Evaluating Microprocessor Reliability                   | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Evaluating Microprocessor Availability                  | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Conclusions                                             | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                         | Instruction Mix AnalysisArchitecture Parameters for the Microprocessor Model4.3.1. Built-In Microprocessor Detection Capability4.3.2. Modelling the Microprocessor Program Counter4.3.3. Instruction Processing ExceptionsEvaluating Microprocessor Models of Erroneous Behaviour4.4.1. 8-Bit Processor Evaluations4.4.2. 16-Bit Processor Evaluations4.4.3. 32-Bit Processor EvaluationsCatastrophic Failure AnalysisRecovery Through The Detection of Erroneous ExecutionEvaluating Microprocessor ReliabilityEvaluating Microprocessor Reliability |

## Chapter 5

### DETECTING ERRONEOUS MICROPROCESSOR BEHAVIOUR

| 5.1. | Introduction                                                | 78 |

|------|-------------------------------------------------------------|----|

| 5.2. | Address Space Allocation                                    | 78 |

| 5.3. | Erroneous Execution in the Unused Area of the Address Space | 79 |

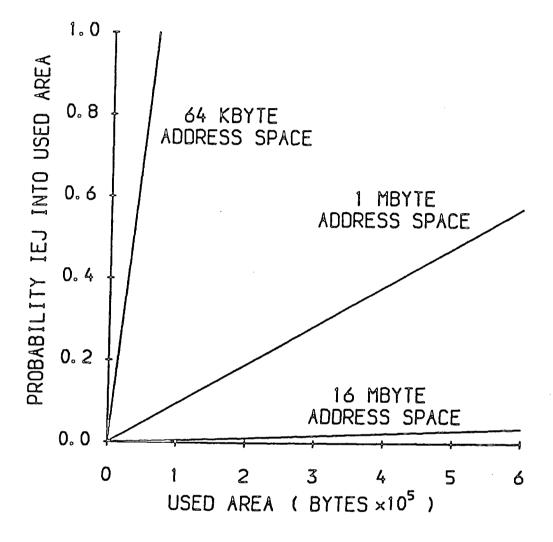

|      | 5.3.1. The Initial Erroneous Jump Characteristic            | 81 |

|      | 5.3.2. Detecting Erroneous Execution                        | 81 |

|      | 5.3.2.1. A Software Based Technique                         | 83 |

|      | 5.3.2.2. Watchdog Timers and Smart Watchdogs                | 84 |

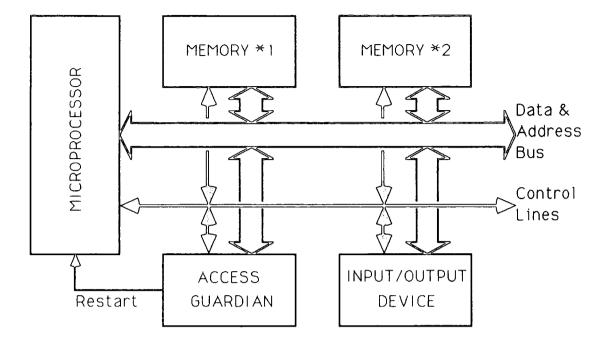

|      | 5.3.2.3. The Access Guardian Proposal                       | 84 |

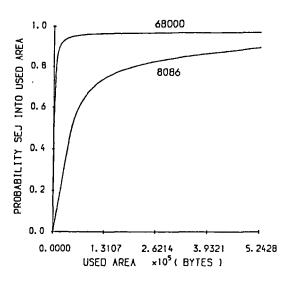

| 5.4. | Erroneous Execution in the Used Area of the Address Space   | 87 |

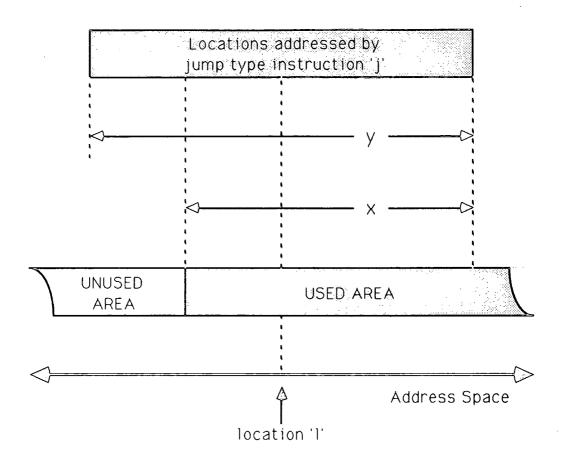

|      | 5.4.1. The Subsequent Erroneous Jump Characteristic         | 87 |

|      | 5.4.2. Detection Using Software Implemented Fault Tolerance | 91 |

|      | 5.4.2.1. Program Areas                                      | 91 |

|      | 5.4.2.2. Data Areas and Reserved Input/Output Areas         | 96 |

| 5.5. | The Overheads of Implementing Fault Tolerance               | 97 |

|      | 5.5.1. Hardware Fault Tolerance                             | 97 |

|      | 5.5.2. Software Implemented Fault Tolerance              | 98  |

|------|----------------------------------------------------------|-----|

| 5.6. | A Fault Tolerant Strategy for Microprocessor Controllers | 99  |

| 5.7. | Summary                                                  | 104 |

256 C. #4

## Chapter 6

. ...

# POST-PROGRAMMING, AUTOMATED, RECOVERY UTILITY (PARUT)

| 6.1. | Introduction                                              | 107 |

|------|-----------------------------------------------------------|-----|

| 6.2. | Design and Development Objectives for the PARUT Prototype | 107 |

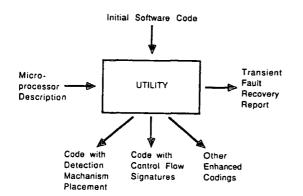

| 6.3. | A Functional Overview of PARUT                            | 108 |

| 6.4. | Design Features Incorporated within the PARUT Prototype   | 110 |

|      | 6.4.1. Programming Language                               | 110 |

|      | 6.4.2. Programming Style                                  | 110 |

|      | 6.4.3. The Diagnostic Facility                            | 110 |

|      | 6.4.4. Target Software                                    | 111 |

|      | 6.4.5. Target Processors                                  | 112 |

| 6.5. | A Description of the PARUT Prototype Operation            | 112 |

|      | 6.5.1. Data Code Analysis                                 | 114 |

|      | 6.5.2. Program Code Analysis                              | 115 |

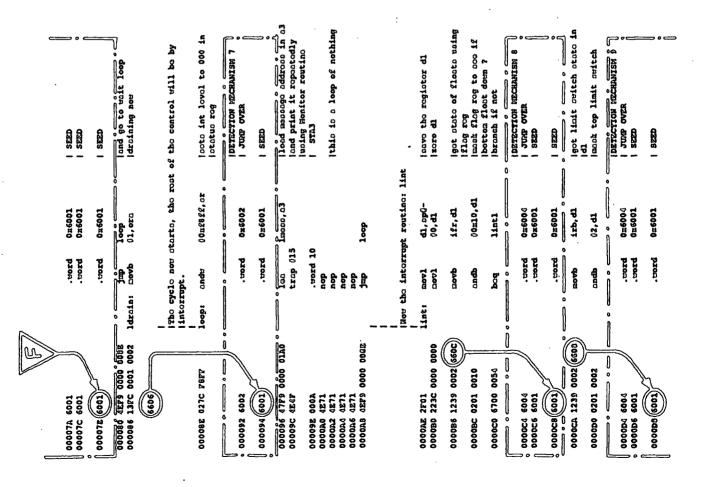

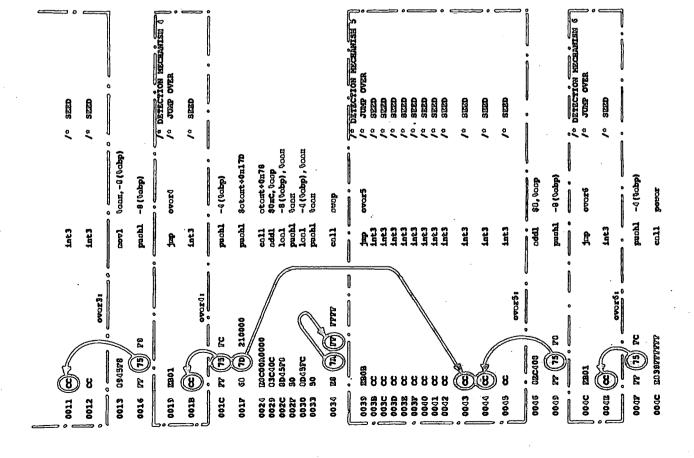

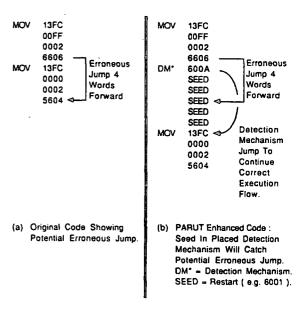

|      | 6.5.3. The 'Seeding' Algorithm                            | 116 |

| 6.6. | PARUT: A Review of the Prototype                          | 122 |

| 6.7. | PARUT: Developing a Standard Programming Tool             | 123 |

| 6.8. | Summary                                                   | 124 |

## Chapter 7

### ASSESSING FAULT TOLERANCE

| 7.1. | Introduction                                             | 125 |

|------|----------------------------------------------------------|-----|

| 7.2. | Assessing the Fault Tolerance of a Microprocessor System | 126 |

|      | 7.2.1. Assessment Parameters                             | 126 |

|      | 7.2.2. Parameter Evaluation                              | 126 |

|      | 7.2.3. Internal Microprocessor Faults                    | 128 |

|      | 7.2.4. Assessment Dependence on Application Software     | 128 |

|      | 7.2.5. Behavioural Observations                          | 130 |

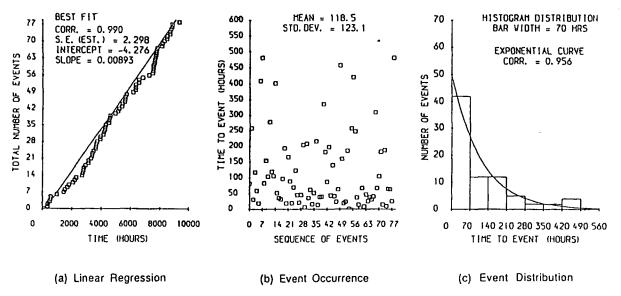

| 7.3. | Single-Bit Fault Injection Experiment                     | 130          |

|------|-----------------------------------------------------------|--------------|

|      | 7.3.1. Fault Injection Experiment                         | 130          |

|      | 7.3.2. Microprocessor Application Under Investigation     | 132          |

|      | 7.3.3. Programme of Injected Faults                       | 1 <b>33</b>  |

|      | 7.3.4. Selected Single-Bit Faults                         | 135          |

|      | 7.3.5. Decoupling the Microprocessor Detection Mechanisms | 1 <b>3</b> 7 |

|      | 7.3.6. Performance Evaluation                             | 138          |

| 7.4. | Multiple-Bit Fault Emulation Experiment                   | 144          |

|      | 7.4.1. Emulation and Fault Investigation                  | 144          |

|      | 7.4.2. Microprocessor Applications Under Investigation    | 145          |

|      | 7.4.3. Programme of Emulated Faults                       | 146          |

|      | 7.4.4. Behavioural Analysis                               | 147          |

|      | 7.4.5. Identified Phases of Erroneous Execution           | 147          |

|      | 7.4.5.1. The Initial Erroneous Jump Phase                 | 148          |

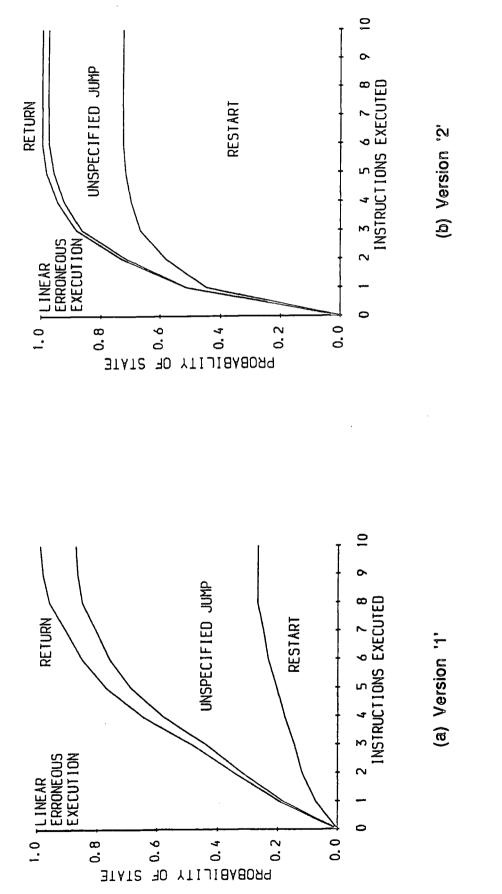

|      | 7.4.5.2. The Subsequent Erroneous Jump Phase              | 151          |

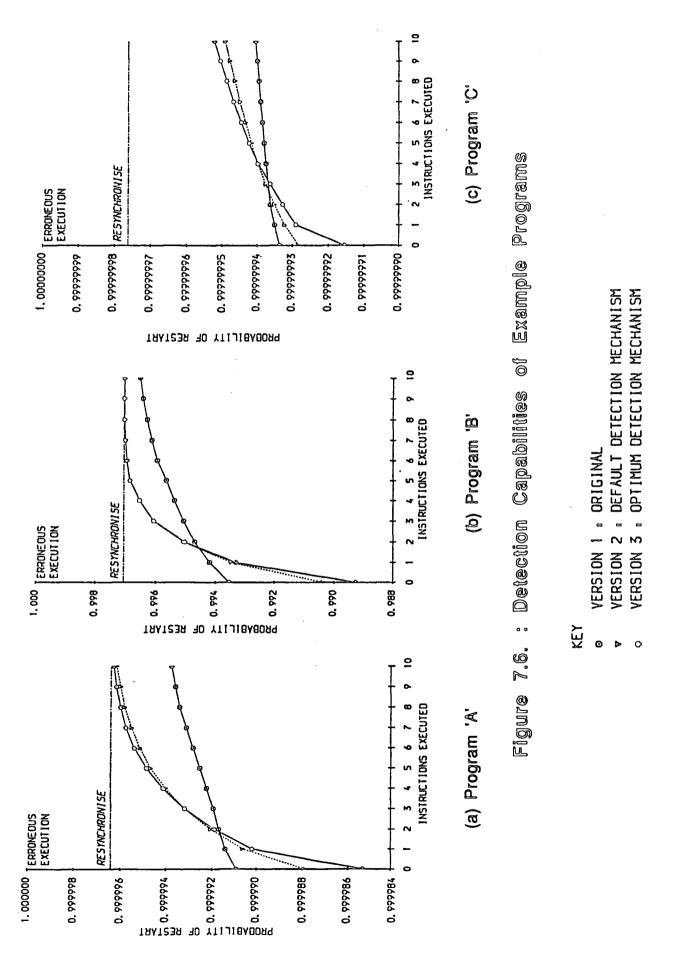

|      | 7.4.6. Analysing Detection Capability                     | 151          |

|      | 7.4.7. Critical Hazards of Erroneous Behaviour            | 157          |

|      | 7.4.7.1. Cessation of Processing                          | 158          |

|      | 7.4.5.2. Infinite Execution Loops                         | 158          |

|      | 7.4.5.3. Placement Deadlock                               | 158          |

|      | 7.4.8. Re-synchronized Erroneous Execution                | 160          |

| 7.5. | Summary and Conclusions                                   | 160          |

|      |                                                           |              |

Chapter 8

and the second second second

### GENERATING NON-HAZARDOUS SOFTWARE

| 8.1. | Introduction                                | 162 |

|------|---------------------------------------------|-----|

| 8.2. | Bridging the Semantic Gap                   | 163 |

| 8.3. | The Risks of Erroneous Execution            | 163 |

|      | 8.3.1. Catastrophic Processing Failures     | 163 |

|      | 8.3.2. Critical Hazard Coverage             | 164 |

| 8.4. | Non-Hazardous Program Area Code             | 165 |

|      | 8.4.1. Hazardous Instruction Formats        | 165 |

|      | 8.4.2. Hazardous Opcodes                    | 166 |

|      | 8.4.3. Hazardous Operands                   | 168 |

|      | 8.4.3.1. Prevention of Address Mode Hazards | 168 |

|      | 8.4.3.2. Inherent Addressing                | 168 |

|      | 8.4.3.3. Manipulating Direct Addressing     | 169 |

|      | 8.4.3.4. Manipulating Immediate Addressing        | 170         |

|------|---------------------------------------------------|-------------|

|      | 8.4.3.5. Manipulating Indirect Addressing         | 170         |

|      | 8.4.3.6. Manipulating Indexed Addressing          | 171         |

|      | 8.4.3.7. Manipulating Register-Indexed Addressing | 171         |

|      | 8.4.3.8. Manipulating Relative Addressing         | 172         |

| 8.5. | Influencing Translator Practices                  | 1 <b>74</b> |

|      | 8.5.1. Instruction Selection                      | 174         |

|      | 8.5.2. Coupling and Cohesion                      | 174         |

|      | 8.5.3. Macros                                     | 175         |

|      | 8.5.4. Peephole Optimization                      | 176         |

| 8.6. | Non-Hazardous Data Area Code                      | 176         |

| 8.7. | Non-Hazardous Input/Output Reserved Area Code     | 177         |

| 8.8. | Influence of the Instruction Set                  | 177         |

|      | 8.8.1. Undefined Instructions                     | 177         |

|      | 8.8.2. Restart Instructions                       | 178         |

|      | 8.8.3. Stop/Wait and Return Instructions          | 178         |

|      | 8.8.4. Unspecified Jump Instructions              | 179         |

| 8.9. | Conclusions                                       | 179         |

|      |                                                   |             |

المراجع المراجع المستحد المراجع المتحدين والمتهز والمتعلي والمعاط والمعام والمحاص والمحاص المحاص المراجع المراجع

# Chapter 9

and the state of the state of the state

1.14.1

and the second second

### MICROPROCESSOR DESIGN FOR FAULT TOLERANCE

| 9.1. | Introduction                                  | 181         |  |  |  |

|------|-----------------------------------------------|-------------|--|--|--|

| 9.2. | The Effectiveness of Fault Tolerance          |             |  |  |  |

| 9.3. | Implementing Fault Tolerance                  |             |  |  |  |

| 9.4. | Influences on Microprocessor Design           |             |  |  |  |

| 9.5. | Instruction Set Architectures                 | 183         |  |  |  |

|      | 9.5.1. Instruction Set Mix                    | 184         |  |  |  |

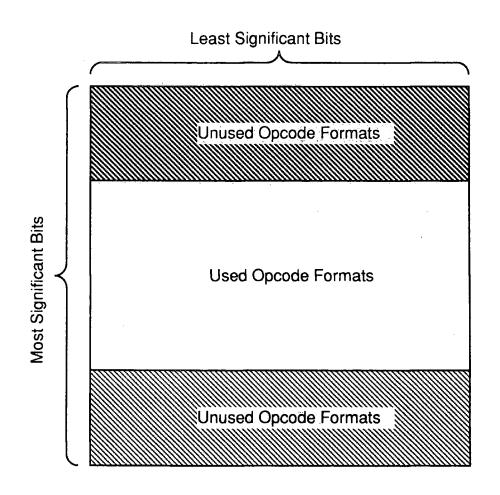

|      | 9.5.2. Opcode Maps                            | 185         |  |  |  |

|      | 9.5.3. Operand requirements and Specification | 188         |  |  |  |

| 9.6. | Input/Output Communication Ports              | 189         |  |  |  |

| 9.7. | Memory Organization                           | 189         |  |  |  |

|      | 9.7.1. Memory Alignment                       | 189         |  |  |  |

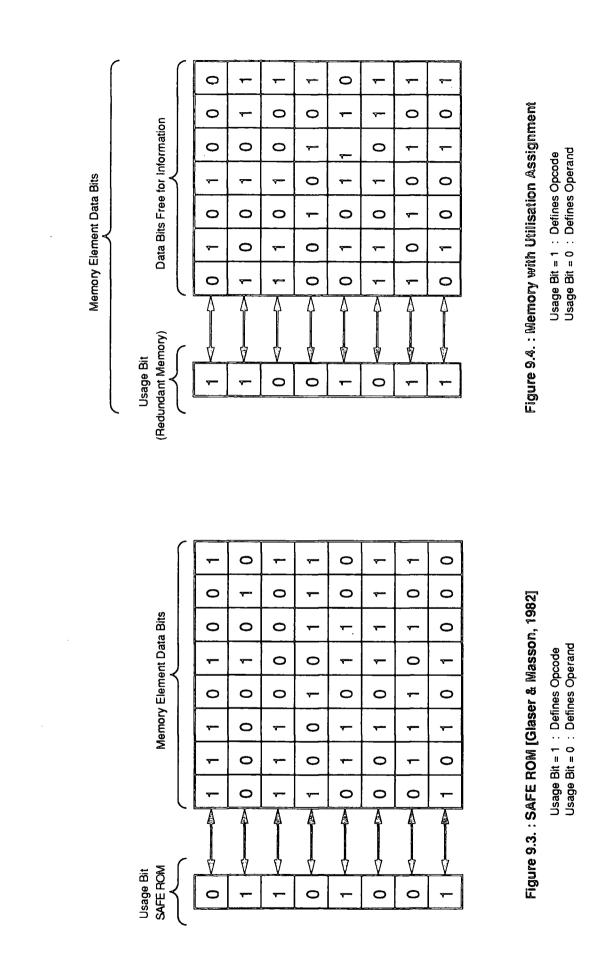

|      | 9.7.2. Defining Memory Utilization            | 1 <b>92</b> |  |  |  |

| 9.8. | Monitoring Branch Activity                    | 194         |  |  |  |

| 9.9. | 9.9. Conclusion                               |             |  |  |  |

## Chapter 10

### CONCLUSION

| 10.1. | Microprocessor Controllers for Industrial Applications | 196         |

|-------|--------------------------------------------------------|-------------|

| 10.2. | Reliable Microprocessor Controllers                    | 196         |

| 10.3. | Modelling Erroneous Microprocessor Behaviour           | 1 <b>97</b> |

| 10.4. | Detecting Erroneous Microprocessor Execution           | 199         |

| 10.5. | Evaluating Fault Tolerance                             | 201         |

| 10.6. | Generating Non-Hazardous Software                      | 201         |

| 10.7. | Microprocessor Design for Fault Tolerance              | 202         |

| 10.8. | Summary                                                | 202         |

## Bibliography & References ...... 204

## Appendix A

### INSTRUCTION SET PARAMETERS

| A.1. | Introduction                              | 214 |

|------|-------------------------------------------|-----|

| A.2. | Instructions Influencing Program Flow     | 214 |

| A.3. | Microprocessor Jump Type Instruction Data | 215 |

## Appendix B

### THE DESIGN OF AN ACCESS GUARDIAN

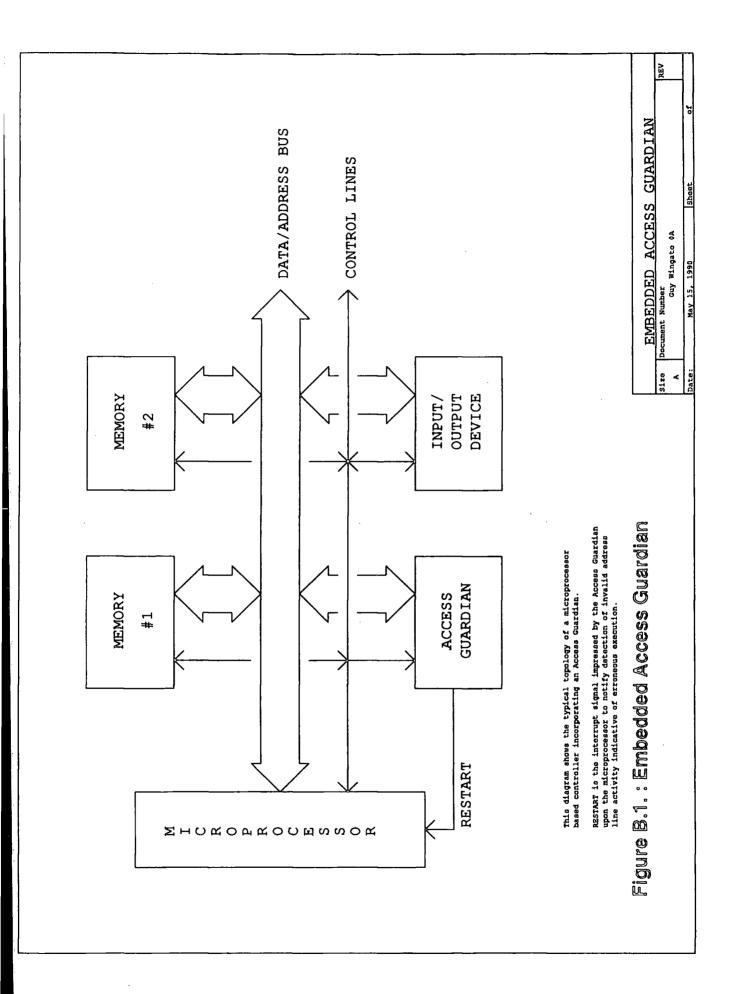

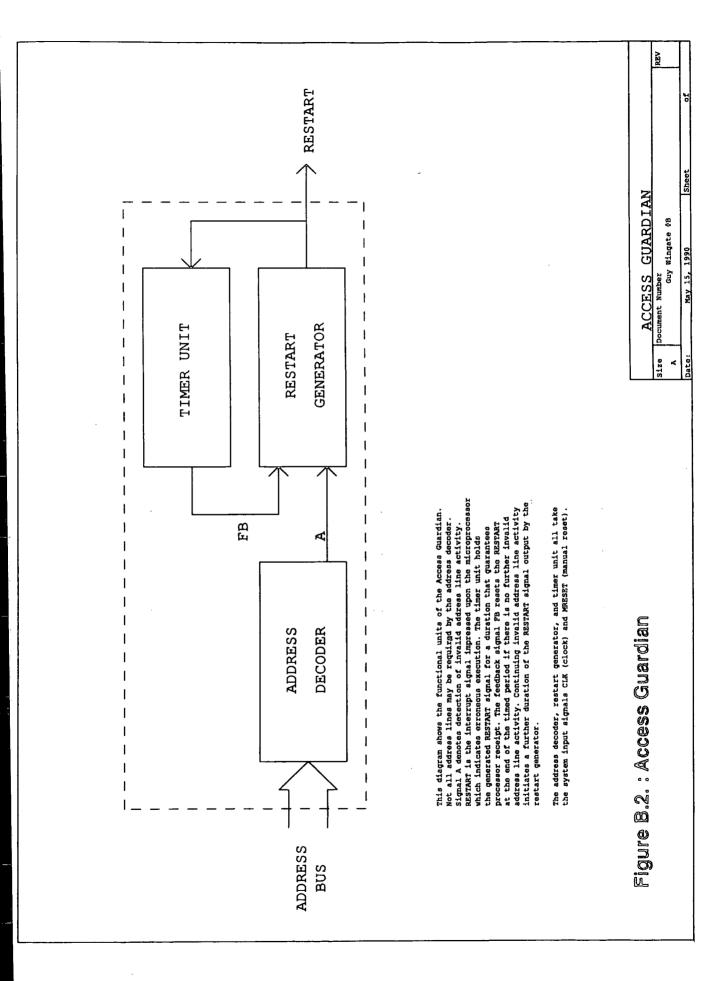

| B.1. | Introduction                      | 222 |

|------|-----------------------------------|-----|

| B.2. | An Access Guardian Design         | 222 |

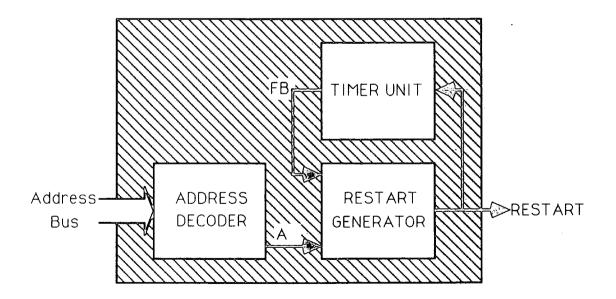

| B.3. | The Address Decoder               | 225 |

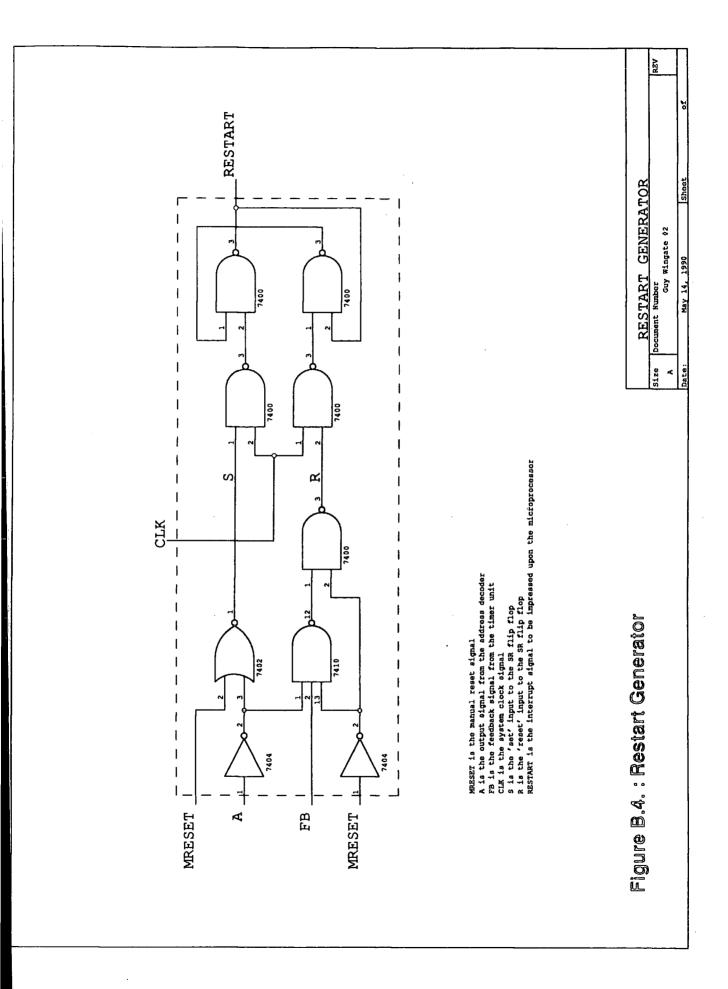

| B.4. | The Restart Generator             | 225 |

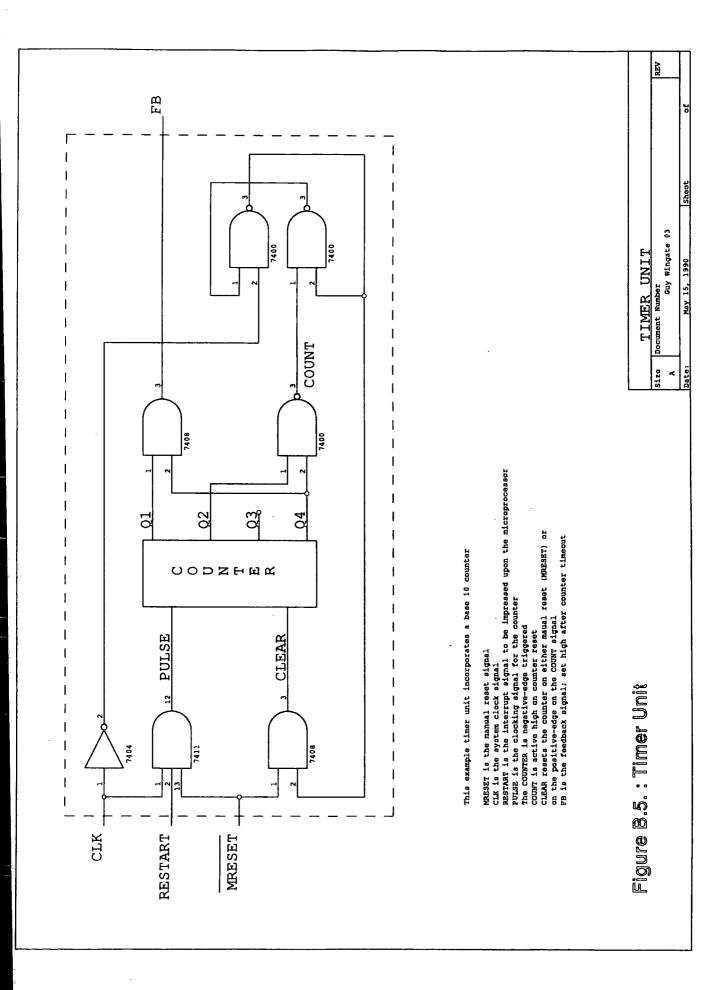

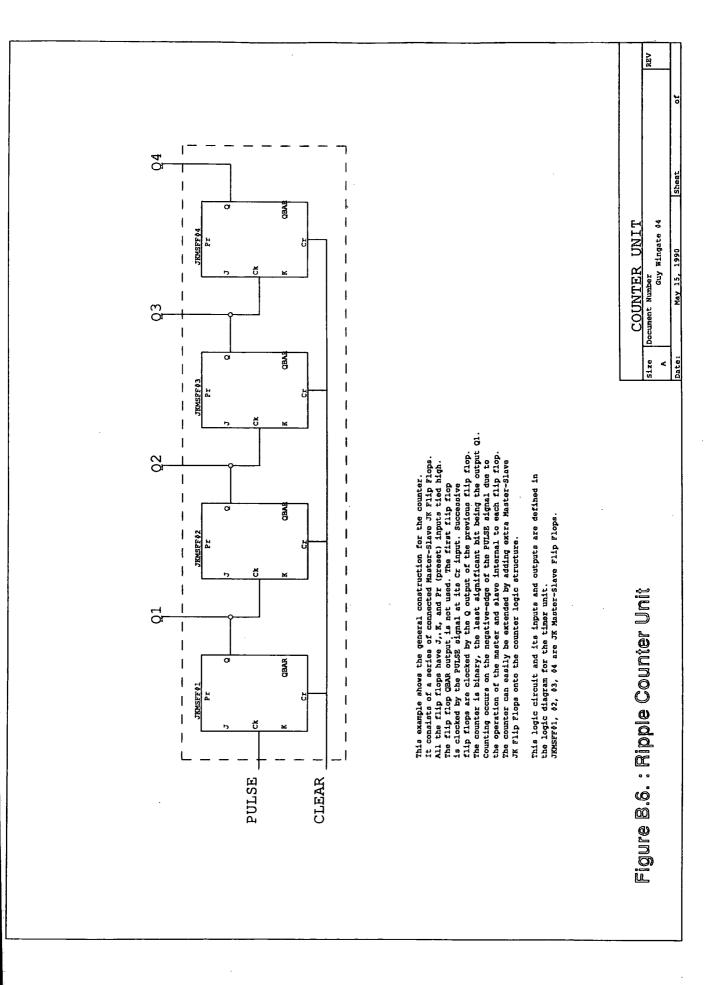

| B.5. | The Timer Unit                    | 228 |

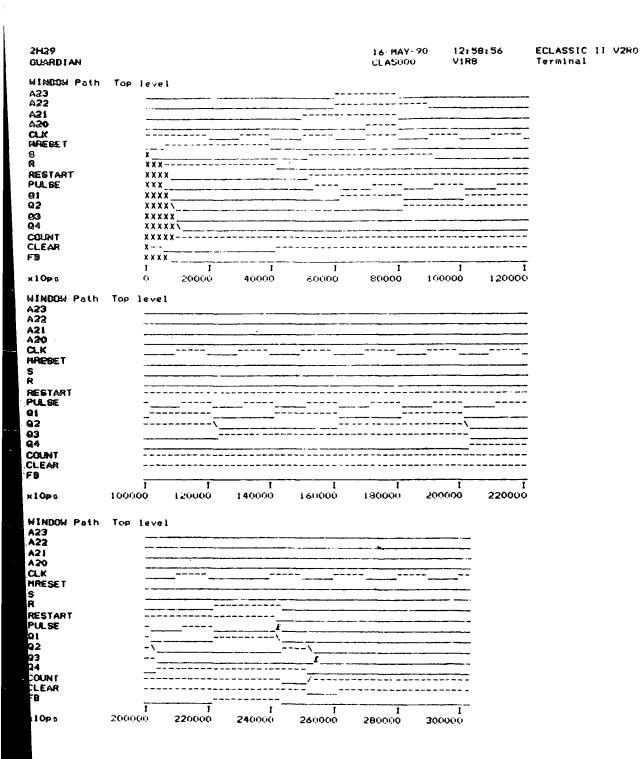

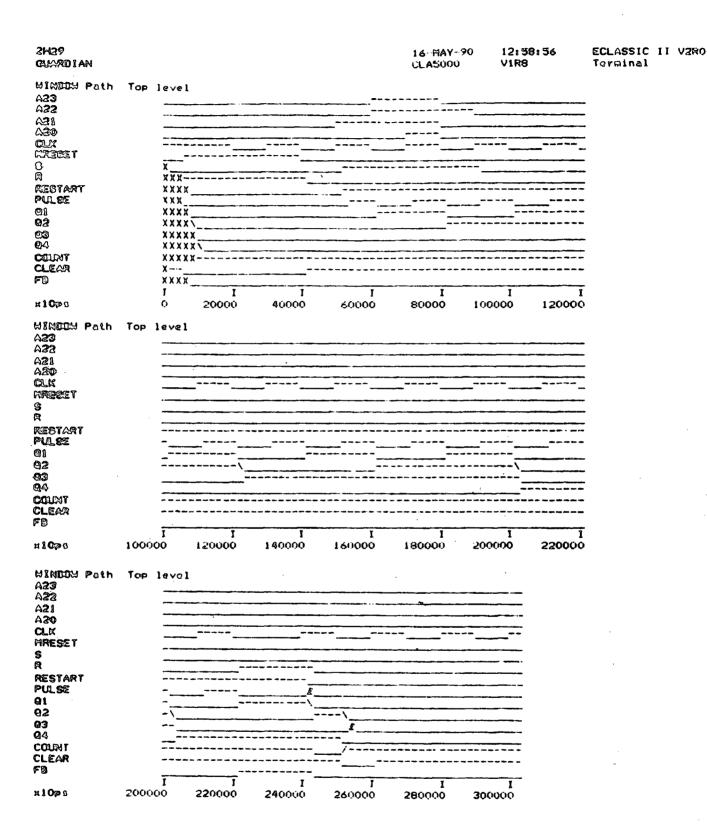

| B.6. | Design Simulation                 | 231 |

| B.7. | The Design's Hardware Requirement | 235 |

| B.8. | Summary                           | 235 |

## Appendix C

### PARUT AND OTHER RELATED CODE LISTINGS

| C.1. | Introduction                                      | 237 |

|------|---------------------------------------------------|-----|

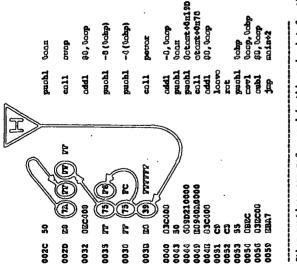

| C.2. | PARUT Listing                                     | 237 |

| C.3. | Microprocessor Description File, MICRO_FILE       | 257 |

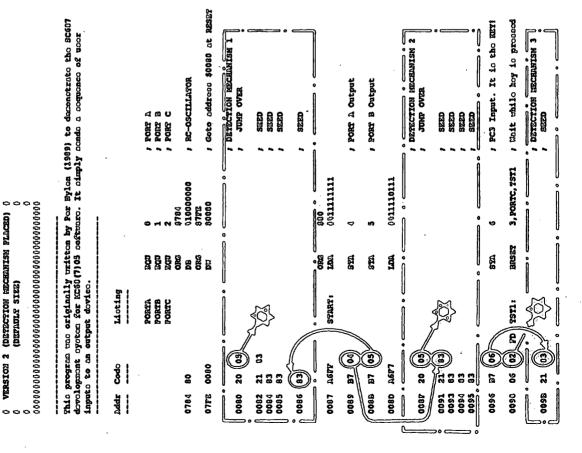

| C.4. | Target Software, CODE_FILE                        | 261 |

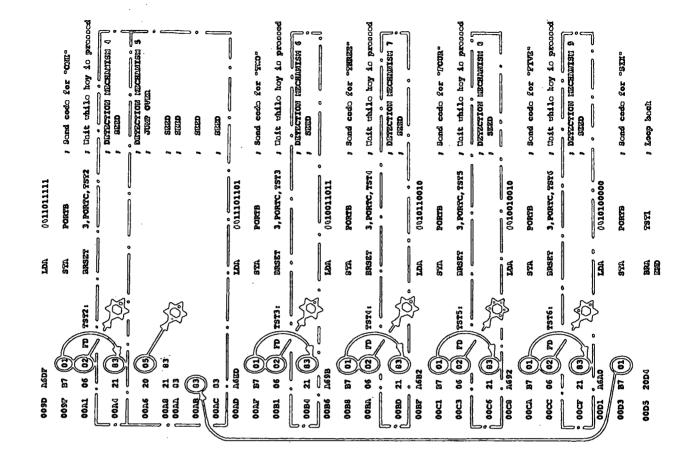

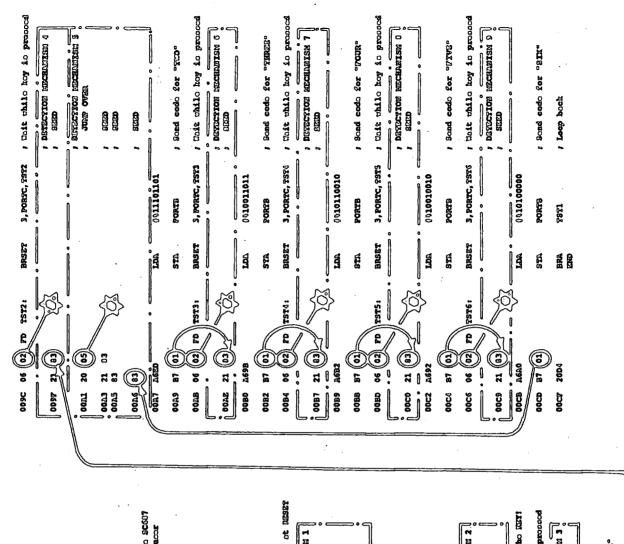

| C.5. | Target Software with Fault Tolerance, RESULT_FILE | 263 |

| C.6. | PARUT Report File, ANALYSIS_FILE                  | 266 |

| C.7. | PARUT Diagnostics, TRACE_FILE                     | 269 |

## Appendix D

### EXAMPLE PROGRAMS

| D.1. | Introduction                                              | 273 |

|------|-----------------------------------------------------------|-----|

| D.2. | Program 'A' Targeting the Motorola 68000 Microprocessor   | 274 |

| D.3. | Program 'B' Targeting the Motorola 68(7)05 Microprocessor | 284 |

| D.4. | Program 'C' Targeting the Intel 80386 Microprocessor      | 288 |

Appendix E

### PUBLICATIONS

|      | Introduction        |     |

|------|---------------------|-----|

| E.2. | EUROMICRO '88 Paper | 299 |

| E.3. | EUROMICRO '89 Paper | 307 |

| E.4. | IEE '89 Paper       | 315 |

| E.5. | IEE '90 Paper       | 318 |

| E.6. | EUROMICRO '91 Paper | 323 |

### FIGURES

~

in the second second

1.042

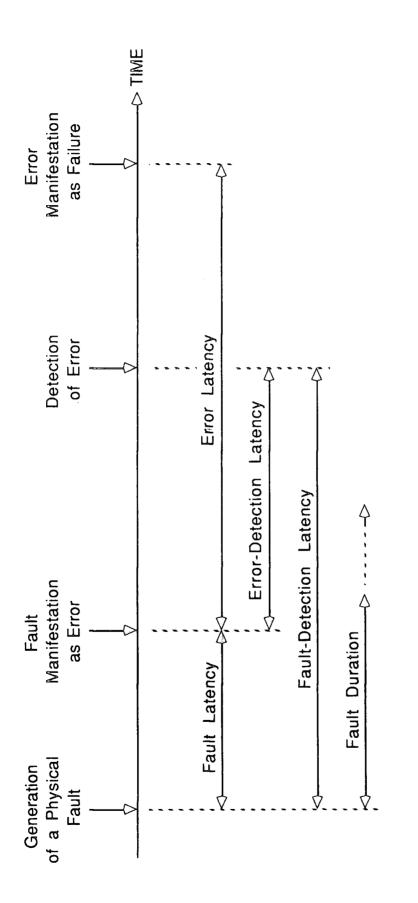

| Figure 2.1. : Fault and Error Latencies                              | 14           |

|----------------------------------------------------------------------|--------------|

| Figure 3.1. : Microprocessor Erroneous Behaviour                     | 33           |

| Figure 3.2. : Erroneous Execution Model                              | 35           |

| Figure 3.3. : Reliability Model                                      | 37           |

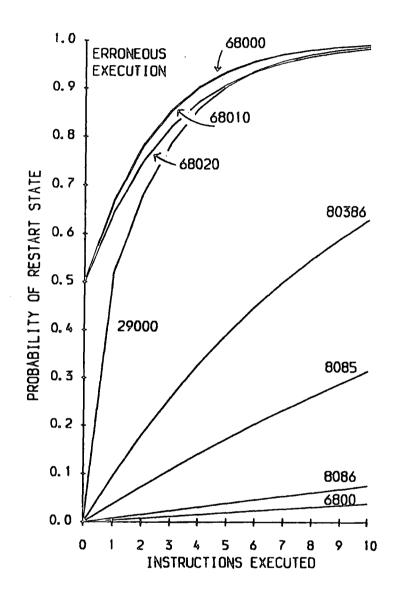

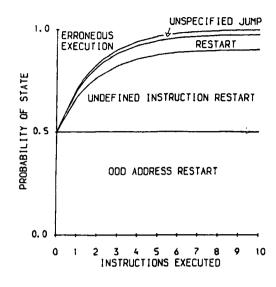

| Figure 4.1. : 8-Bit Microprocessor Linear Erroneous Execution        | 61           |

| Figure 4.2. : 16-Bit Microprocessor Linear Erroneous Execution       | 62           |

| Figure 4.3. : 32-Bit Microprocessor Linear Erroneous Execution       | 63           |

| Figure 4.4. : Catastrophic Failure - Instruction Mix Analysis        | 68           |

| Figure 4.5. : Recovery Through Detection - Instruction Mix Analysis  | 70           |

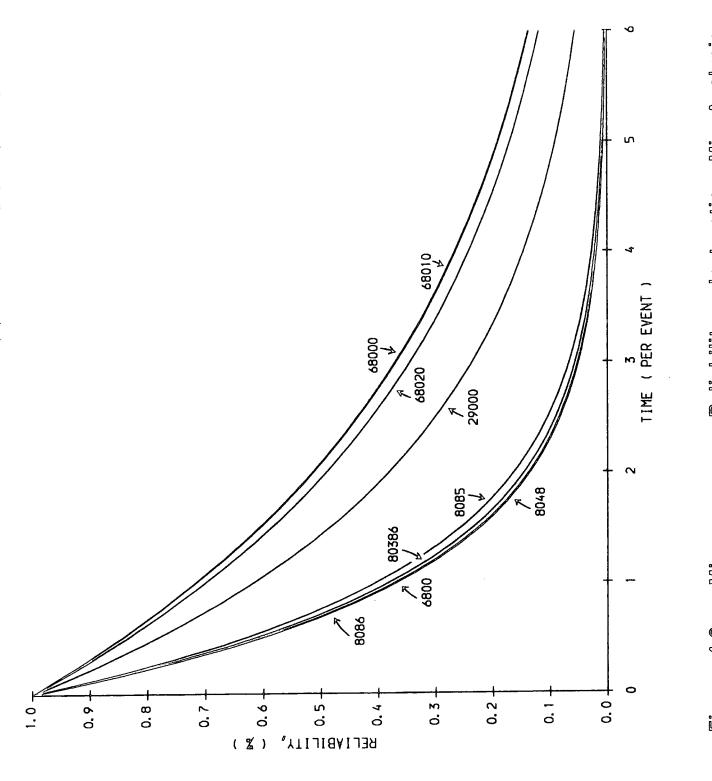

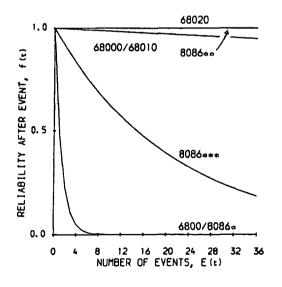

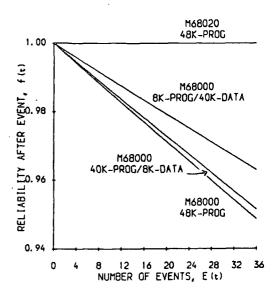

| Figure 4.6. : Microprocessor Reliability - Instruction Mix Analysis  | 72           |

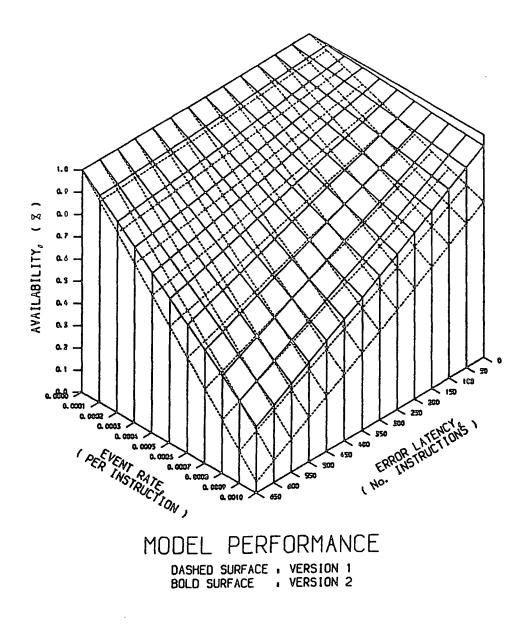

| Figure 4.7. : Microprocessor Availability - Instruction Mix Analysis | 75           |

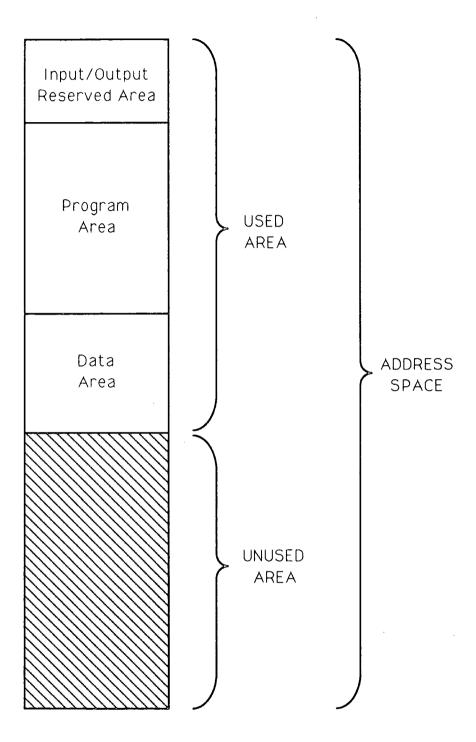

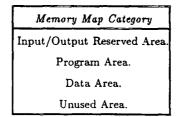

| Figure 5.1. : Functional Address Space Allocation                    | 80           |

| Figure 5.2. : The IEJ Characteristic                                 | 82           |

| Figure 5.3. : Embedded Access Guardian                               | 86           |

| Figure 5.4. : Access Guardian                                        | 86           |

| Figure 5.5. : The HIT Function                                       | 89           |

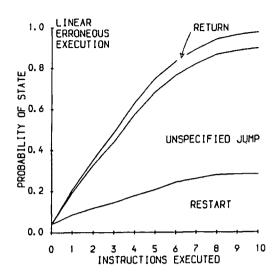

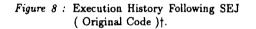

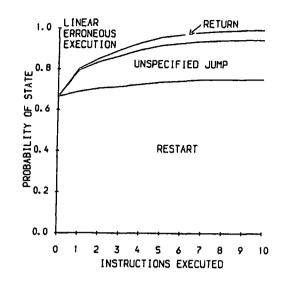

| Figure 5.6. : The SEJ Characteristic                                 | 90           |

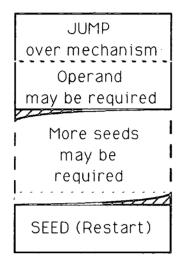

| Figure 5.7. : Detection Mechanism Constructions                      | 93           |

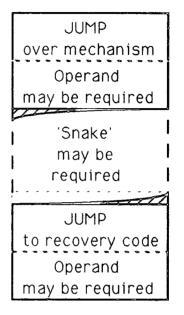

| Figure 5.8. : Detection Mechanism Placement                          | 94           |

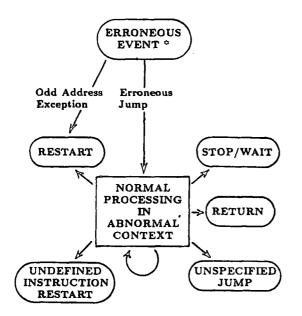

| Figure 5.9. : Erroneous Execution Model : Enhanced Fault Recovery    | 100          |

| Figure 5.10. : Microprocessor Reliability with Access Guardian       | 102          |

| Figure 5.11. : Enhanced Microprocessor Reliability                   | 105          |

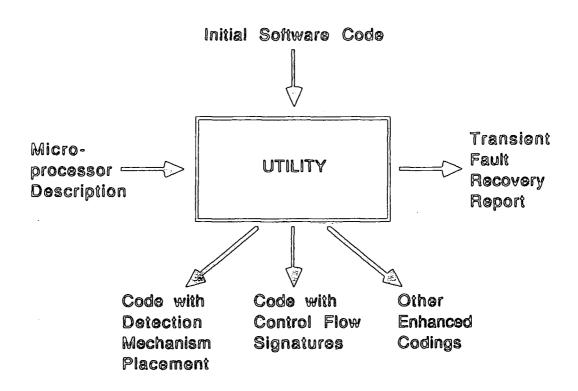

| Figure 6.1. : PARUT Overview                                         | 109          |

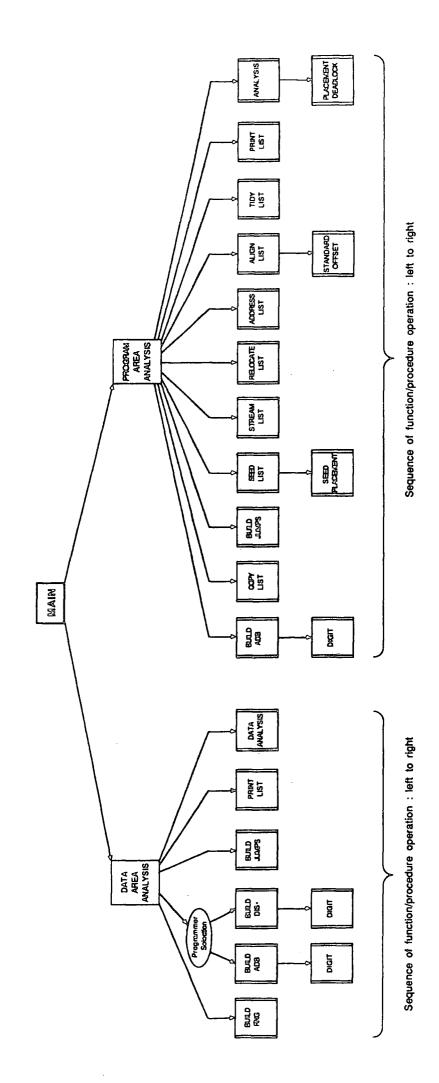

| Figure 6.2. : Program 'MAIN' Call Chart                              | 113          |

| Figure 6.3. : Screen Dump of PARUT User Interface                    | 117          |

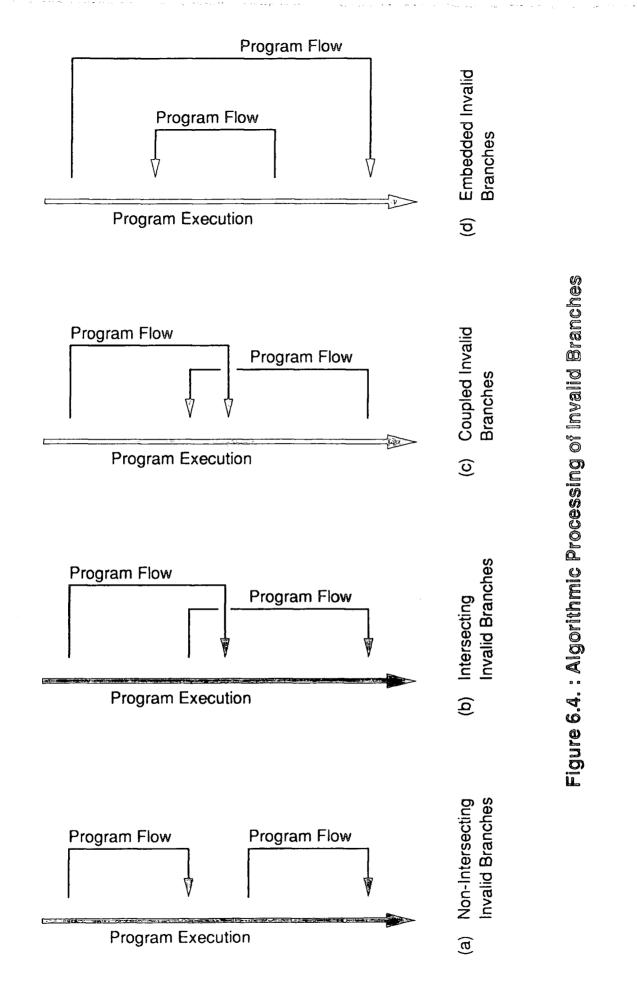

| Figure 6.4. : Algorithmic Processing of Invalid Branches             | 118          |

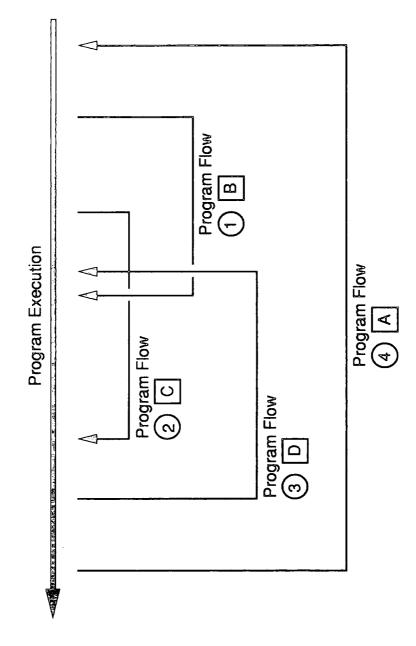

| Figure 6.5. : A Complex Example of Algorithmic Processing            | 1 <b>2</b> 1 |

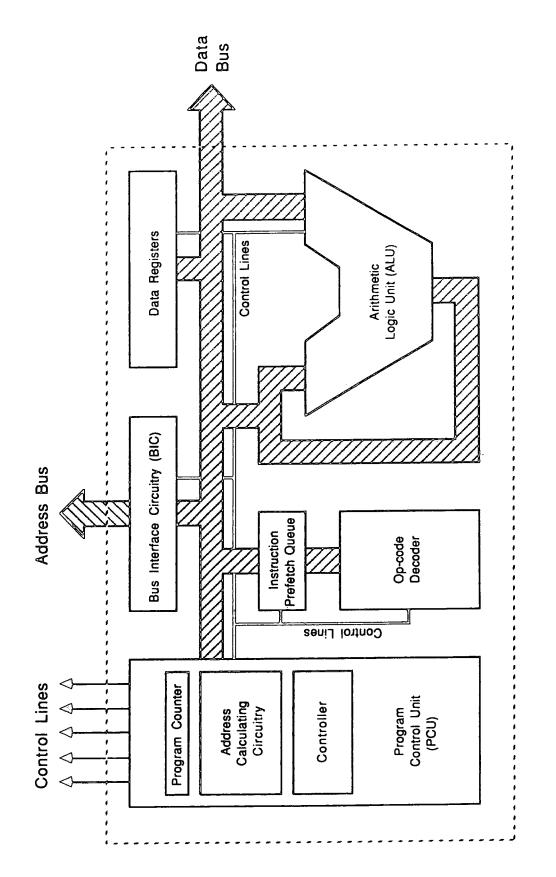

| Figure 7.1. : Basic Microprocessor Topology                          | 129          |

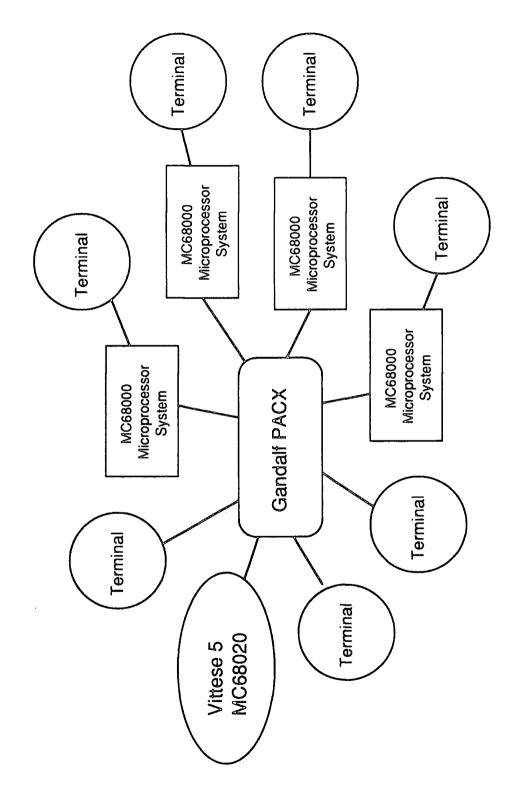

| Figure 7.2. : Microprocessor Laboratory System Topology              | 131          |

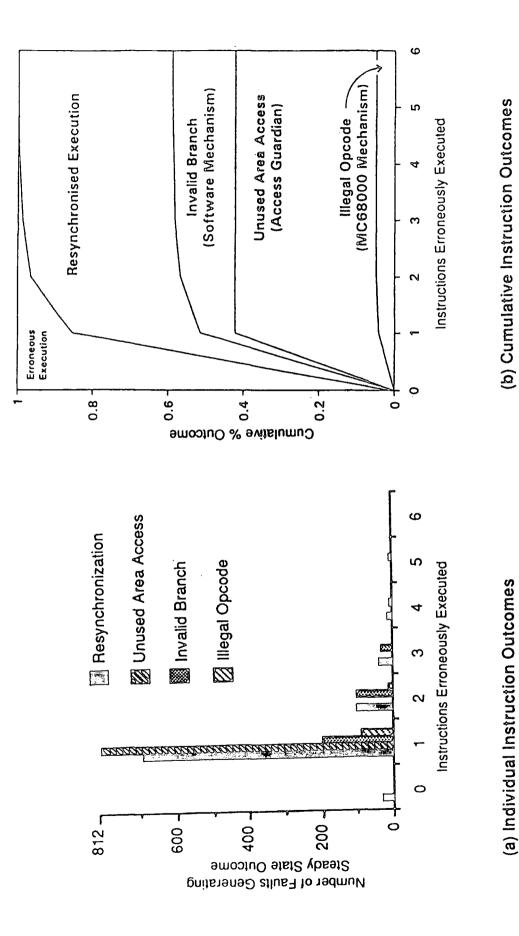

| Figure 7.3. : Nature of Fault Injection Outcomes                     | 142          |

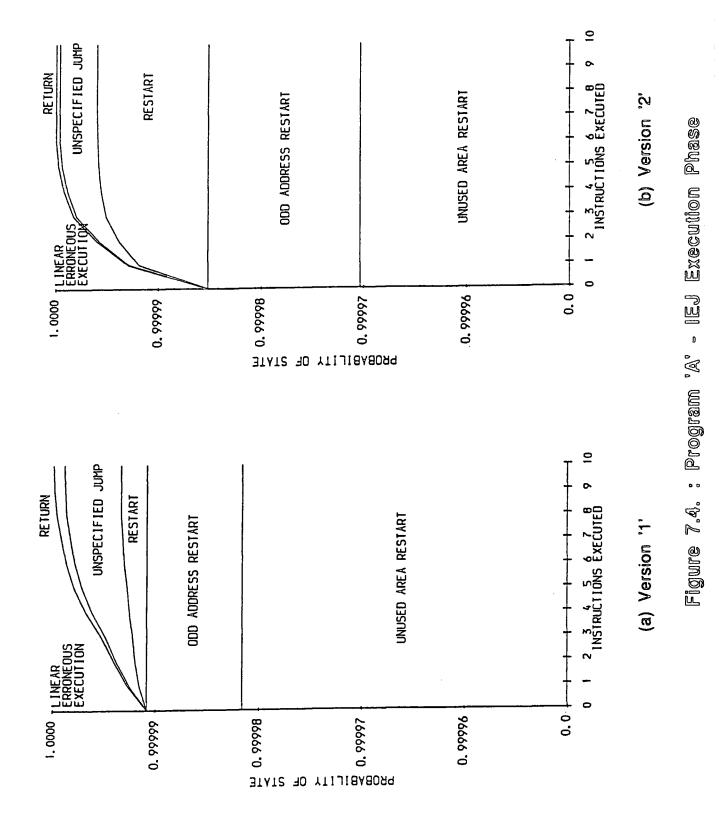

| Figure 7.4. : Program 'A' IEJ Execution Phase            | 150 |

|----------------------------------------------------------|-----|

| Figure 7.5. : Program 'A' SEJ Execution Phase            | 152 |

| Figure 7.6. : Detection Capabilities of Example Programs | 155 |

|                                                          |     |

| Figure 9.1. : Microprocessor Opcode Map                  | 187 |

| Figure 9.2. : Input/Output Location Content              | 190 |

| Figure 9.3. : SAFE ROM                                   | 193 |

| Figure 9.4. : Memory with Utilization Assignment         | 193 |

|                                                          |     |

| Figure B.1. : Embedded Access Guardian                   | 223 |

| Figure B.2. : Access Guardian                            | 224 |

| Figure B.3. : Address Decoder                            | 226 |

| Figure B.4. : Restart Generator                          | 229 |

| Figure B.5. : Timer Unit                                 | 230 |

| Figure B.6. : Ripple Counter Unit                        | 231 |

| Figure B.7. : Access Guardian Circuit Description        | 233 |

| Figure B.8. : Access Guardian Timing Simulation          | 234 |

- - -

## TABLES

......

| Table 2.1. : Observed Temporary & Permanent Errors                                                                                          | 15  |

|---------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 2.2. : Fault Emulation/Simulation Experiments                                                                                         | 19  |

| Table 2.3. : Fault Injection Experiments                                                                                                    | 20  |

| Table 2.4. : Capability Checks                                                                                                              | 25  |

|                                                                                                                                             |     |

| Table 4.1. : Microprocessor Instruction Set Evaluation                                                                                      | 56  |

| Table 4.2.       : Microprocessor Undefined Instruction Evaluation                                                                          | 57  |

| Table 4.3. : Random Data Instruction Interpretation                                                                                         | 59  |

| Table 4.4. : Microprocessor 'Mean Time To Failure' Evaluation                                                                               | 73  |

|                                                                                                                                             | 109 |

| Table 5.1. : MTTF with Unused Area Detection                                                                                                | 103 |

| Table 5.2. : MTTF Enhancement with Used Area Detection                                                                                      | 103 |

| Table 7.1. : Single-Bit Fault Injection Programme                                                                                           | 136 |

| Table 7.2. : Fault Injection Outcomes                                                                                                       | 139 |

| Table 7.3. : Nature of Fault Injection Outcomes                                                                                             | 141 |

| Table 7.4. : Observed Behaviour of Program 'A'                                                                                              | 149 |

| Table 7.5. : Observed Behaviour of Program 'B'                                                                                              | 153 |

| Table 7.6. : Observed Behaviour of Program 'C'                                                                                              | 154 |

| Table 7.7. : Erroneous Infinite Execution Loop                                                                                              | 159 |

| Table 7.8. : Placement Deadlock                                                                                                             | 159 |

|                                                                                                                                             | 017 |

| Table A.1. : MC 6800 Microprocessor Instruction Set Evaluation                                                                              | 217 |

| Table A.2. : Intel 8048 Microprocessor Instruction Set Evaluation         Table A.2. : Intel 8048 Microprocessor Instruction Set Evaluation | 217 |

| Table A.3. : Intel 8085 Microprocessor Instruction Set Evaluation         Table A.4. : Intel 8085 Microprocessor Instruction Set Evaluation | 217 |

| Table A.4. : Intel 8086 Microprocessor Instruction Set Evaluation                                                                           | 217 |

| Table A.5. : MC 68000 Microprocessor Instruction Set Evaluation         Table A.5. : MC 68000 Microprocessor Instruction Set Evaluation     | 217 |

| Table A.6. : MC 68010 Microprocessor Instruction Set Evaluation         Table A.6. : MC 68010 Microprocessor Instruction Set Evaluation     | 217 |

| Table A.7. : AMD 29000 Microprocessor Instruction Set Evaluation         Table A.7. : AMD 29000 Microprocessor Instruction Set Evaluation   | 217 |

| Table A.8. : MC 68020 Microprocessor Instruction Set Evaluation         Table A.8. : MC 68020 Microprocessor Instruction Set Evaluation     | 217 |

| Table A.9. : Intel 80386 Microprocessor Instruction Set Evaluation                                                                          | 217 |

| Table A.10. : MC 6800 Jump Instructions         Table A.10. : MC 6800 Jump Instructions                                                     | 218 |

| Table A.11. : Intel 8048 Jump Instructions                                                                                                  | 218 |

| Table A.12. : Intel 8085 Jump Instructions                                                                                                  | 219 |

| Table A.13. : Intel 8086 Jump Instructions                                                                                                  | 219 |

| Table A.14. : MC 68000, MC 68010, and MC 68020 Jump InstructionsTable A.15. : AMD 29000 Jump InstructionsTable A.16. : Intel 80386 Jump Instructions |            |

|------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Table B.1. : Truth Table for SRFF Control LogicTable B.2. : Set-Reset Flip Flop Transition TableTable B.3. : Access Guardian Parts List              | 227<br>227 |

| Table C.1. : Chronological Order of Functions in PARUT Listing                                                                                       | 238        |

\* \* \* ,

1.4

### LIST OF ABBREVIATIONS

· 15.

.

| ADB     | UNIX 'A DeBugger' Facility                                      |

|---------|-----------------------------------------------------------------|

| ALU     | Arithmetic Logic Unit                                           |

| AMD     | Advanced Micro Device                                           |

| BG-Rig  | British Gas Rig (experimental)                                  |

| BIC     | Bus Interface Circuitry                                         |

| Cdf     | Cumulative Density Function                                     |

| CISC    | Complex Instruction Set Computer                                |

| CLASSIC | Custom Logic Analysis Simulation System for Integrated Circuits |

| Cm*     | Carnegie-Mellon Multi-processor                                 |

| CMOS    | Complementary Metal-Oxide Semiconductor                         |

| CMUA    | Carnegie-Mellon University 'A' File System                      |

| CMU-AFS | Carnegie-Mellon University Andrew File System                   |

| C.vmp   | Carnegie-Mellon Voting Multi-processor                          |

| DIS     | UNIX 'DIS-assembler' Facility                                   |

| ECL     | Emitter-Coupled Logic                                           |

| EMI     | Electro-Magnetic Interference                                   |

| ESD     | Electro-Static Discharge                                        |

| FMECA   | Failure-Mode, Effects and Criticality Analysis                  |

| FORTRAN | 'Formula Translation' Programming Language                      |

| FTA     | Fault Tree Analysis                                             |

| FTMP    | Fault Tolerant Multi-Processor                                  |

| IBM     | International Business Machines                                 |

| IC      | Integrated Circuit                                              |

| IEE     | Institution of Electrical Engineers                             |

| IEEE    | Institute of Electrical and Electronics Engineers               |

| IEJ     | Initial Erroneous Jump                                          |

| IPQ     | Instruction Prefetch Queue                                      |

| HDL     | Hardware description Language                                   |

| JPI     | Jensen and Partners International                               |

| LP      | Low Pressure                                                    |

| MC      | Motorola Corporation                                            |

| MTTF    | Mean Time To Failure                                            |

| MTTR    | Mean Time To Repair                                             |

| NASA    | National Aeronautics Space Administration                       |

| NMOS    | N-Type Metal-Oxide Semiconductor                                |

|         |                                                                 |

| PARUT | Post-programming Automated Recovery UTility |

|-------|---------------------------------------------|

| PC    | Program Counter                             |

| PCU   | Program Control Unit                        |

| pdf   | Probability Density Function                |

| RAM   | Random Access Memory                        |

| RISC  | Reduced Instruction Set Computer            |

| RFI   | Radio-Frequency Interference                |

| ROM   | Read Only Memory                            |

| SEJ   | Subsequent Erroneous Jump                   |

| SLAC  | Stanford Linear Accelerator Centre          |

| SRFF  | Set-Reset Flip Flop                         |

| TMR   | Triple Modular Redundancy                   |

| TTL   | Transistor-Transistor Logic                 |

| VLSI  | Very Large Scale Integration                |

|       |                                             |

### LIST OF SYMBOLS

· · • •

• • •

· · · ·

| Λ              | Set of Faults Detected by Access Quardian                     |

|----------------|---------------------------------------------------------------|

| A              | Set of Faults Detected by Access Guardian                     |

| $A_d$          | Physical Address in the Address Space                         |

| $A_v$          | Availability<br>Binnla Counter Boss                           |

| $C_n$          | Ripple Counter Base                                           |

| D(k)           | Probability of Detecting Erroneous Execution                  |

| $D_{IEJ}(k)$   | Probability of Detecting Erroneous Execution Following an IEJ |

| $D_{SEJ}(k)$   | Probability of Detecting Erroneous Execution Following an SEJ |

| E              | Error Detection Coverage                                      |

| $E_f$          | Event Leading to Failure                                      |

| $E_r$          | Event Leading to Recovery                                     |

| $E_s$          | Set of Events Disrupting Processor Execution                  |

| f(t)           | Probability Density Function                                  |

| F              | Set of Injected Faults                                        |

| F(t)           | Cumulative Density Function                                   |

| H(l,j)         | HIT Function: Probability of an SEJ Target in Used Area       |

| i              | Number of Defined Opcodes within Instruction Set              |

| Ι              | Mean Period of Linear Erroneous Execution, (No. Instructions) |

| $I_f$          | Microprocessor Instruction Frequency, (No. Instructions/s)    |

| j              | Jump Type Instruction                                         |

| J              | Set of Jump Type Instructions                                 |

| J'             | Return or Unspecified Jump Outcome                            |

| k              | Instruction Index During Linear Erroneous Execution           |

| l              | Jump Type Instruction Location in Used Area                   |

| L              | Set of Address Space Locations                                |

| $L_d$          | Error Detection Latency (No. Instructions)                    |

| L <sub>s</sub> | Stalling Latency (No. Instructions)                           |

| m              | Integer                                                       |

| Μ              | Set of Faults Detected by Hardware                            |

| n              | Number of Bits in Opcode Format                               |

| $Ne_J$         | Effective Number of 'Jump' Outcome Instructions               |

| $Ne_{RN}$      | Effective Number of 'Return' Outcome Instructions             |

| $Ne_{RT}$      | Effective Number of 'Restart' Outcome Instructions            |

| $Ne_{SW}$      | Effective Number of 'Stop/Wait' Outcome Instructions          |

| $Ne_{UJ}$      | Effective Number of 'Unspecified Jump' Outcome Instructions   |

| $N_L$          | Number of Locations Open to Instruction Interpretation        |

|                |                                                               |

| $N_R$                     | Number of Instructions in Recovery Routine                           |

|---------------------------|----------------------------------------------------------------------|

| P                         | Set of Faults Detected by Software                                   |

| $P_c(t)$                  | Probability of Controlled State                                      |

| $P_{IEJ}(UsedArea)$       | Probability of IEJ Target in Used Area                               |

| $P_{IEJ}(UnusedArea)$     | Probability of IEJ Target in Unused Area                             |

| $P_{J}$                   | Probability of a 'Jump' Instruction Outcome                          |

| $P_J(k)$                  | Functional Probability of a 'Jump' Outcome                           |

| P <sub>J</sub>            | Probability of a 'Jump' Instruction Outcome                          |

| $P_{J'}(k)$               | Functional Probability of a 'J' Outcome                              |

| $P_{J'}^{y}(k)$           | Functional Probability of a ' $J'$ ' Outcome Following an IEJ or SEJ |

| $P_L^{\boldsymbol{y}}(k)$ | Functional Probability of Linear Erroneous Execution                 |

| $P_{NJ}$                  | Probability of a 'Non-Jump' Instruction Outcome                      |

| $P_{NJ}(k)$               | Functional Probability of a 'Non-Jump' Instruction Outcome           |

| $P_{RN}(k)$               | Functional Probability of a 'Return' Instruction Outcome             |

| $P_{RT}(k)$               | Functional Probability of a 'Restart' Instruction outcome            |

| $P_{SEJ}(UsedArea)$       | Probability of SEJ Target in Used Area                               |

| $P_{SEJ}(UnusedArea)$     | Probability of SEJ Target in Unused Area                             |

| $P_{SW}(k)$               | Functional Probability of a 'Stop/Wait' Instruction Outcome          |

| $P_{UJ}(k)$               | Functional Probability of a 'Unspecified Jump' Instruction Outcome   |

| $P_u(t)$                  | Probability of Uncontrolled State                                    |

| $P_x(k)$                  | Functional Probability of a ' $x$ ' Outcome                          |

| $P_x^{IEJ}(k)$            | $P_x(k)$ following an IEJ                                            |

| $P_x^{SEJ}(k)$            | $P_x(k)$ following an SEJ                                            |

| $Pr{}$                    | Probability Function                                                 |

| q                         | Event Rate, (per hour)                                               |

| R                         | Set of Faults Generating Re-synchronization                          |

| R()                       | Reliability Function                                                 |

| $R^F()$                   | Reliability Signature Monitoring Hardware                            |

| $R_s()$                   | Reliability of Microprocessor Employing Signature Monitoring         |

| RN                        | Return Outcome                                                       |

| RT                        | Restart Outcome                                                      |

| S                         | Number of Bytes in Memory Fetch                                      |

| S(k)                      | Probability of Erroneous Execution Stall                             |

| $S_{IEJ}(k)$              | Probability of Erroneous Execution Stall following an IEJ            |

| $S_{SEJ}(k)$              | Probability of Erroneous Execution Stall following an SEJ            |

| SW                        | Stop/Wait Outcome                                                    |

| t                         | Time, (s)                                                            |

| Т                         | Set of Locations Addressed by Jump Type Instruction                  |

| UJ                        | Unspecified Jump Outcome                                             |

| x                         | Member of the Set $\{RN, RT, SW, UJ\}$                               |

|                           |                                                                      |

| y            | Member of the Set $\{IEJ, SEJ\}$                  |

|--------------|---------------------------------------------------|

| Z(t)         | Hazard Rate, (per hour)                           |

|              |                                                   |

|              |                                                   |

| $\beta$      | Probability Hardware Exception: 'Restart' Outcome |

| $\gamma$     | Probability Software Exception: 'Restart' Outcome |

| $\lambda$    | Constant Failure Rate, (per hour)                 |

| $\lambda(t)$ | Failure Rate, (per hour)                          |

| $\Psi$       | Recursive Element of Function $D(k)$ and $S(k)$   |

|              |                                                   |

5.

## Chapter 1

1.1.4

## RELIABILITY AND MICROPROCESSOR-BASED CONTROLLERS

. . . . .

| 1.1. | Introduction                                       | 1 |

|------|----------------------------------------------------|---|

| 1.2. | Microprocessor-Based Control Systems               | 3 |

| 1.3. | Faults, Errors, and Failures in Electronic Systems | 4 |

| 1.4. | Engineering Reliability Through Design             | 4 |

|      | 1.4.1. Reliable Hardware                           | 5 |

|      | 1.4.2. Reliable Software                           | 5 |

| 1.5. | Evaluating Controller Reliability                  | 6 |

|      | 1.5.1. Hardware Reliability                        | 7 |

|      | 1.5.2. Software Reliability                        | 7 |

|      | 1.5.3. Interface Reliability                       | 8 |

| 1.6. | Low-Cost Enhancement of Controller Reliability     | 8 |

| 1.7. | Thesis Preview                                     | 9 |

|      |                                                    |   |

#### CHAPTER ONE

#### RELIABILITY AND MICROPROCESSOR-BASED CONTROLLERS

#### 1.1. Introduction

The continuing technological evolution of microprocessor design has resulted in a large number of commercially available devices with a wide variety of characteristics. Many microprocessors are embedded within control systems to automatically operate, monitor, or control a physical process. Applications range from relatively simple control of domestic appliances such as toasters or washing machines, to the complex control of industrial plant such as power stations or chemical works. An important feature of all these control systems is their reliability, that is, the probability that the system will perform its function under stated environmental conditions, without malfunction, over a specified period of time or operational duration (adapted from [Bennetts, 1979]).

British Gas use microprocessor systems to manage individual governors controlling the transmission of gas to industrial and public customers. Such microprocessor controllers require high reliability because of the proximity of their installation, with the hazard of gas, to the general public.

The United Kingdom gas distribution system involves the transmission of gas at high- and medium- low pressures between the off-shore gas fields, local consumer districts, and end-customers respectively. The low pressure (LP) system dates back to the production of town gas in the 19th century and serves local districts and individual users. The LP network has traditionally been controlled by independent pneumatic governors. Governors are devices which control, through a valve action, the gas pressure in a pipeline. The governors implement a clocking mechanism which alters the gas pressure depending on predicted daily fluctuations in demand. Gas pressures that fall below a critical level allow air to enter the gas pipework and can produce potentially explosive mixtures. To prevent this situation arising the governor system implements a shut-down operation, called 'slam-open', when the

gas pressure falls at an excessive rate or when the gas pressure falls beneath the statutory safety limit of 12.3 mbar. The slam-open operation involves completely opening the governor valve so that adjacent normal and hazardous gas pressures across the valve are equalized. Slam-open operations may cascade through several consecutive governor systems before the mean pressure along a section of pipeline is acceptable.

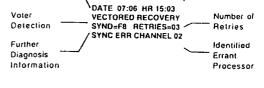

In order to increase management efficiency of the LP network it is necessary to improve control of the gas distribution. The small value of gas handled by each governor system in the gas network means that a low-cost upgrade is required. To this end, microprocessors have been embedded within the governor control systems [Clark et al, 1987] to facilitate more effective and integrated control of the LP gas distribution system [Wynne et al, 1988]. The distribution of gas can now be managed in an efficient and interactive manner. Seasonal and diurnal load variations can be monitored and appropriate responsive action taken automatically in a real-time environment. Stringent safety regulations of the gas industry require the back-up of electronic systems failure by traditional pneumatic slam-open operation.

British Gas predict failures of the microprocessor assisted governors to occur once every 10 years, a failure rate approximately one thousandth of the original pneumatic governor systems [Clark et al, 1987]. The slam-open back-up ensures that microprocessor controller failures are not catastrophic. Nevertheless, loss of the governor management function incurs a financial penalty; reduced gas distribution efficiency, and repair of the controller which may reside at a remote site. An overall improvement in the reliability of the microprocessor controller is required. British Gas are particularly interested in the effect of software, 'which may become highly unpredictable' under the influence of hardware faults, on system reliability [Clark et al, 1987].

This thesis presents techniques for enhancing the operational reliability of microprocessor-based controllers without adversely increasing their cost. These techniques are applicable to any microprocessor system, including those used by British Gas to manage governors.

2 -

#### 1.2. Microprocessor-Based Control Systems

Many control systems have their designs based on complex logic circuits incorporating flip-flops, analogue-to-digital converters, shift-registers, and other logic gate structures. In these cases it is often convenient to incorporate, or replace, such circuitry with a dedicated microprocessor and its support chips. The control system behaviour can now to a large extent be governed by the software stored on a microprocessor memory chip. Software can be maintained without physically altering the system hardware. Sucl flexibility can be valuable as in a recently reported incident when a car manufacturer discovered a design error in a fuel injection system [IEEE, 1989]. Replacing the system with an alternative was extremely expensive. However, replacement was not necessary: the system was controlled by a microprocessor which was re-programmed to compensate for, and effectively mask, the design error. The problem was rectified at little cost. In such instances the maintenance engineers must be careful not to introduce new errors (the 'Software Death Cycle', [Rigby & Norris, 1990]).

In recent years digital techniques have become so powerful that tasks well suited to analogue systems are often partially or totally controlled by digital systems. For example, a temperature meter based on a thermocouple or thermistor might incorporate a microprocessor and memory in order to improve accuracy by compensating for the instrument's departure from perfect linearity.

Although ever more powerful microprocessors are being developed, most controllers do not require further advanced processing capabilities. A recent Japanese survey [Fujimura, 1989] reported that approximately 80% of microprocessor-based controllers incorporated either an 8 or 16-bit machine. Despite the commercial availability of 32-bit processors for over five years, they were only used in approximately 11% of the controllers. The remaining 9% of controllers had embedded 4-bit microprocessors. Obviously the 4-bit microprocessor-based controllers had a very simple function.

#### 1.3. Faults, Errors, and Failures in Electronic Systems

A system failure is said to occur when the behaviour of the system first deviates from that required by the specification of the system (as defined by [Anderson & Lee, 1982]). System failures are caused by the external exposure of a defective internal state. Deficiencies in the internal state of a system, referred to as 'errors', can exist without the generation of a failure.

A system consists of a set of components (or sub-systems) which interact under the control of a design. Errors originate from the activation of defective system components. Defective components are referred to as 'faults'.

A fault in a digital electronic system is characterized by its nature, extent, and duration [Avizienis, 1976]. The nature of the fault can be classified as either logical or non-logical. A logical fault causes the logic value at a point in the digital circuit to become opposite to the specified value. Non-logical faults include the remaining faults such as a malfunction of the clock signal. The extent of a fault specifies whether the effect of the fault is localized or distributed in the the digital system. Finally, the duration of a fault refers to whether the fault is permanent or temporary.

McCluskey & Wakerly [1981] distinguish between two classes of temporary fault, transient and intermittent. Transient faults are non-recurring temporary faults which are caused by environmental influences. They are not repairable because there is no physical damage to the hardware. Intermittent faults are recurring temporary faults caused by deteriorating or ageing hardware. Intermittent faults may eventually become permanent and can be repaired.

#### 1.4. Engineering Reliability Through Design

Reliability can be engineered in a digital system by implementing a disciplined design process. The reliability of a microprocessor-based system depends on its hardware and software design, deficiencies in either are expensive to correct. It is therefore prudent, when developing reliable systems, for the design to be fault-free or faulttolerant.

#### 1.4.1. Reliable Hardware

Poor specification, design, and manufacture can individually or collectively introduce faults within digital electronic systems. Specifications are normally written in natural language which makes their integrity extremely difficult to check. Specifications can be written using Formal Methods, enabling designs to be proven to comply with their specification, but this technique does not ensure that the specification itself is defect-free [Cullyer, 1988].

The integrity of manufacture can be validated using 'black-box' tests. Digital systems, however, can be complex and comprehensive black-box testing extremely expensive. Intel only test 98% of the logic nodes for faults in each manufactured 80486 microprocessor (even though untested nodes may be faulty) because, as for many other digital systems, complete testing is considered prohibitively expensive [IEEE, 1990].

The methods outlined above for the procurement of reliable hardware are all fault avoidance techniques. A complementary approach involves tolerating faults through the implementation of special design features. Fault tolerant techniques can be divided into those that detect faults and initiate recovery such as parity checking and watchdogs, and those that mask faults such as Triple Modular Redundancy (TMR) and error-correcting codes [Carter, 1985].

#### 1.4.2. Reliable Software

Software faults (commonly called 'bugs') can arise from the specification, design, or coding process. Typically more than half the faults which are recorded during the software development originate in the specification [O'Connor, 1985]. This is mainly due to the use of natural language for documenting the 'non-technical' user requirements specification [Hitt & Webb, 1985]. Engineering principles are being proposed [Sommerville, 1985] to enable defect-free development and maintenance of software.

Software verification involves semantic and syntactic checks on the program code for programmer error, and structured walk-through checks for functional correctness. Black-box tests can be used to identify faults but the complexity of software often prevents exhaustive checking due to prohibitive costs. The complexity of software testing can be reduced by adopting a modular code structure. Many methods have been proposed to assess acceptable test-set coverage for software [Musa et al, 1987] but they all are subject to the Dijkstra maxim 'testing reveals the presence of faults, not their absence' [Dijkstra, 1972].

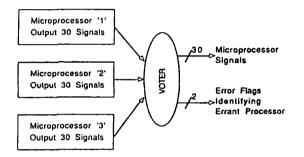

Software can be manipulated to tolerate faults. Two well known approaches to fault tolerant software are N-Version Programming [Chen & Avizienis, 1978], and Recovery Blocks [Randall, 1975]. Both techniques rely on design diversity, the availability of multiple implementation of a specification, to tolerate faults. N-Version Programming requires the independent implementation of multiple, 'N', versions of the specification. These versions are processed in parallel with the same inputs. A voter collects the outputs and a majority decision made to select the perceived correct output. Theory implies high reliability for this method, but in practice the multiple program versions can share common mode failures [Eckhardt & Lee, 1988].

Recovery Blocks consist of a primary routine, which normally performs a task; an acceptance test which checks the primary routine result; and an alternative routine which is executed if the check fails. Unlike N-Version Programming where routine independence is assumed, Recovery Blocks require ensured independence between the primary routine, the acceptance test, and the alternative routine. Application of recovery blocks improves reliability. The degree of reliability can be enhanced by extending the number of independent alternative routines ensuring each acceptance test is also wholly independent.

Software data structures can also be manipulated so that they can tolerate the presence of faults. Taylor et al [1980] briefly outline this topic and propose fault tolerant structures for linear lists and binary trees.

### 1.5. Evaluating Controller Reliability

To evaluate the reliability of a microprocessor-based controller it is necessary to apply a 'systems approach'. The systems approach involves integrating the interdependencies of all sub-systems constituting a whole system. Microprocessor-based controllers consist of two entities; hardware and software. Many authors, including Hitt & Webb [1985], and Ferrara et al [1989], integrate calculations for hardware and software reliability. However such reliability assessments do not involve any allowance for the internal interaction of hardware faults on software. Internal hardware/software interaction occurs across what is referred to as the 'interface'. To determine system reliability more accurately it is necessary to integrate assessments of hardware reliability, software reliability, and interface reliability.

#### 1.5.1. Hardware Reliability

It is valuable to calculate the reliability of a hardware product for the duration of its 'useful' lifetime. Historical failure data which takes into account benign operating conditions and general age degradation is used to assess the expected lifetime of the hardware. Popular compilations of such data include the United States Air Force 'Reliability Prediction for Electronic Systems' (MIL-HDBK-217), and the United Kingdom British Telecom 'Handbook of Reliability Data' (HRD-4). Techniques for manipulating this data to reflect hardware architecture are well understood [Lala, 1985].

#### 1.5.2. Software Reliability

Methods of establishing the reliability of software are still under development. Although many techniques have been proposed none have had the widespread acceptance given to the corresponding assessment of hardware reliability.

Assessments of software reliability usually involve the prediction of errors existing in the software. However, the reliability of the software depends not only on the existence of a fault but also its activation. Many authors have used Markov processes to model software reliability [Musa, 1987]. There are two types of Markovian software reliability model widely used; Poisson and binomial. The Poisson models assume an infinite number of faults in the software, whilst the binomial models assume a fixed number of faults. Both model types assume faults exist randomly within the software. Musa [1975] refined the basic Poisson model so that fault activation is a function of the time for which the software is executed. In reality, however, fault exposure is dependent on the fault location within the software and its associated probability of activation by program execution. Littlewood [1981] attempts to model this situation with a binomial model that weights software faults according to the probability of their execution. Trachtenberg [1990] has recently reviewed and suggested a general theory of software reliability models based on Markovian processes.

The Markov software reliability models provide a valuable indication of the likelihood that a fault will be exposed during software execution. The hazard attributed to fault exposure can be further estimated by using *ad hoc* methods such as 'Fault Tree Analysis' (FTA) or 'Failure-Mode, Effects, and Criticality Analysis' (FMECA).

#### 1.5.3. Interface Reliability

In software controlled digital systems, failures can occur which are difficult to diagnose as being due to the exposure of a hardware fault or software error. A distinction is not clear usually because the systems internal hardware/software interface has not been defined. The interface occurs within electronic devices such as processors and memories. For example, a fault in an individual cell on a memory device holding a program can cause what appears to be a software error. Memory devices are sometimes referred to as firmware to reflect their hardware/software interface. Other faults may occur on a data bus line with similar effect.

Permanent faults relating to interface reliability should be identified by the burnin procurement of the hardware. However because of their limited duration, temporary faults are rarely located during the burn-in process. Assessment of the interface reliability requires knowledge of the occurrence of faults and errors they induce.

#### 1.6. Low-Cost Enhancement of Controller Reliability

The reliability of microprocessor controllers can be enhanced by addressing the problem of faults introduced during procurement and operation. Techniques for procuring reliability have been briefly outlined. Operational faults are generated by component aging and transient disturbances in the working environment such as power supply fluctuations, electro-magnetic interference (EMI), and electro-static discharge (ESD) [Siewiorek & Swarz, 1982].

Transient disturbances are associated with temporary faults in digital systems. Unlike analogue or mechanical systems which tend to pass the effect of a transient disturbance as a temporary signal discrepancy whilst retaining overall function, digital systems are susceptible to malfunction in the presence of temporary faults because of their discrete state nature. Indeed it is becoming established that, even in 'benign' working environments, about 90% of microprocessor system failures can be attributed to temporary faults [Siewiorek & Swarz, 1982].

Control systems are often required to operate in 'harsh' industrial environments liable to produce transient disturbances. Although shielding can be employed to reduce the effects of transient disturbances on digital systems, their elimination is rarely possible [Horowitz & Hill, 1986]. The benefit of tolerating temporary faults induced by transient disturbances can be considerable. Industrial microprocessor controllers, however, are often developed within a limited budget which cannot support the redundancy incurred by many established fault tolerant techniques. This thesis approaches the topic of interface reliability, proposing a low-cost software-implemented fault tolerant technique for temporary hardware faults.

#### 1.7. Thesis Preview

The topic of reliability for microprocessor-based controllers has been introduced with respect to the requirement for low-cost fault tolerance (the objective of the research presented in this thesis). Chapter 2 surveys literature investigating the faulterror-failure mechanism in microprocessor systems. The failure process is identified with malfunction, particular hazard being associated with the corruption of program flow. Current techniques to detect this class of fault are reviewed, but many require considerable expense to implement.

As a first step to developing new and more cost-effective techniques to detect program flow corruption, it is useful to consider the character of associated erroneous microprocessor behaviour. Chapter 3 presents a model for erroneous microprocessor execution. Performance parameters are evolved to show the benefit of implementing a detection capability together with a recovery mechanism. These parameters

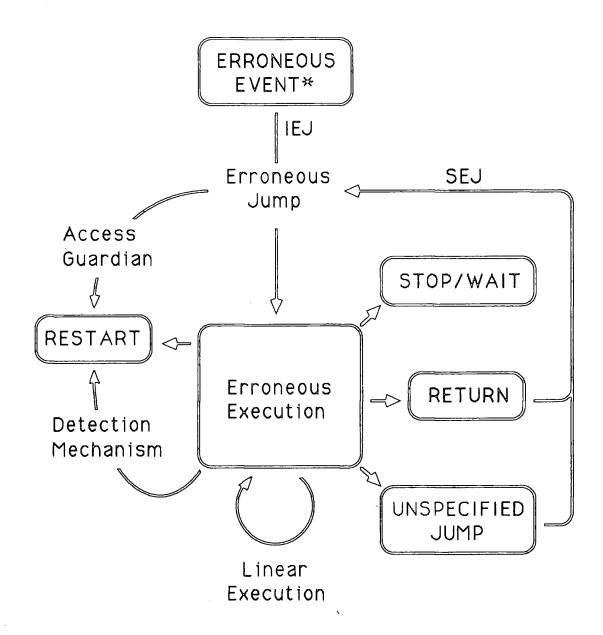

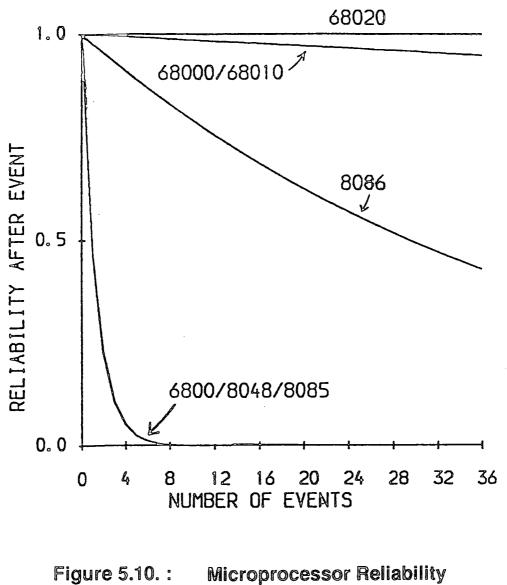

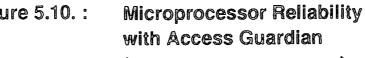

include detection latency, reliability, Mean Time To Failure (MTTF), and availability. The model is applied to a selection of microprocessors commonly embedded within controllers, results are discussed in Chapter 4.