## **Durham E-Theses**

# All-Pairs Shortest Path Algorithms Using CUDA

KEMP, JEREMY, MARK

#### How to cite:

KEMP, JEREMY, MARK (2012) All-Pairs Shortest Path Algorithms Using CUDA, Durham theses, Durham University. Available at Durham E-Theses Online: http://etheses.dur.ac.uk/5564/

#### Use policy

The full-text may be used and/or reproduced, and given to third parties in any format or medium, without prior permission or charge, for personal research or study, educational, or not-for-profit purposes provided that:

- a full bibliographic reference is made to the original source

- a link is made to the metadata record in Durham E-Theses

- the full-text is not changed in any way

The full-text must not be sold in any format or medium without the formal permission of the copyright holders.

Please consult the full Durham E-Theses policy for further details.

# All-Pairs Shortest Path Algorithms Using CUDA

#### Jeremy M. Kemp

Utilising graph theory is a common activity in computer science. Algorithms that perform computations on large graphs are not always cost effective, requiring supercomputers to achieve results in a practical amount of time. Graphics Processing Units provide a cost effective alternative to supercomputers, allowing parallel algorithms to be executed directly on the Graphics Processing Unit. Several algorithms exist to solve the All-Pairs Shortest Path problem on the Graphics Processing Unit, but it can be difficult to determine whether the claims made are true and verify the results listed. This research asks "Which All-Pairs Shortest Path algorithms solve the All-Pairs Shortest Path problem the fastest, and can the authors' claims be verified?" The results we obtain when answering this question show why it is important to be able to collate existing work, and analyse them on a common platform to observe fair results retrieved from a single system. In this way, the research shows us how effective each algorithm is at performing its task, and suggest when a certain algorithm might be used over another.

# All-Pairs Shortest Path Algorithms Using CUDA

### Jeremy M. Kemp

Submitted for the degree of MScR Computer Science to the School of Engineering and Computing Sciences, Durham University, 2012

# Contents

| $\mathbf{G}$ | lossa             | ry                                                            | 7               |

|--------------|-------------------|---------------------------------------------------------------|-----------------|

| 1            | Inti              | roduction                                                     | 9               |

|              | 1.1               | Research Overview                                             | 9               |

|              | 1.2               | Intended Outcomes                                             | 10              |

|              | 1.3               | Thesis Overview                                               | 10              |

| 2            | Def               | initions                                                      | 11              |

|              | 2.1               | Parallel Computing                                            | 11              |

|              |                   | 2.1.1 Bernstein's Conditions                                  | 12              |

|              |                   | 2.1.2 Common Problems with Parallel Programming               | 13              |

|              |                   | 2.1.3 Flynn's Taxonomy                                        | 15              |

|              | 2.2               | GPGPU                                                         | 18              |

|              | 2.3               | What is CUDA?                                                 | 19              |

|              | 2.4               | CUDA Hardware Model                                           | 20              |

|              |                   | 2.4.1 Coalesced Memory Access                                 | $\frac{20}{22}$ |

|              | 2.5               | CUDA Software Model                                           | 23              |

|              | $\frac{2.6}{2.6}$ | Occupancy                                                     | $\frac{25}{25}$ |

|              | $\frac{2.0}{2.7}$ | Thread and Block Heuristics                                   | 26              |

|              | 2.8               | Bank Conflicts                                                | 27              |

|              | 2.9               | Chapter Summary                                               | 28              |

| 3            | Tooks             | roduction to the All-Pairs Shortest Path Problem              | 29              |

| 3            | 3.1               | What is the APSP Problem?                                     | 29<br>29        |

|              | $\frac{3.1}{3.2}$ | Sequential Algorithms                                         | 30              |

|              | 3.2               | 3.2.1 The Floyd-Warshall APSP Algorithm (Floyd, 1962)         | 30              |

|              |                   | 3.2.2 Dijkstra's Algorithm (Dijkstra, 1959)                   | 31              |

|              |                   | 3.2.3 The Bellman-Ford Algorithm (Bellman, 1958)              | $\frac{31}{32}$ |

|              |                   | 3.2.4 Blocked Algorithm (Venkataraman et al., 2003)           | 33              |

|              | 3.3               | Chapter Summary                                               | 37              |

|              | ა.ა               | Chapter Summary                                               | 31              |

| 4            | Imp               | plementation of APSP Algorithms Using CUDA                    | <b>38</b>       |

|              | 4.1               | Graph Representations with CUDA                               | 38              |

|              |                   | 4.1.1 Adjacency Lists                                         | 38              |

|              |                   | 4.1.2 Adjacency Matrices                                      | 39              |

|              | 4.2               | Mapping Threads to Vertices                                   | 40              |

|              | 4.3               | Harish and Narayanan's Algorithm (Harish and Narayanan, 2007) | 41              |

|              |                   | 4.3.1 Modifications                                           | 42              |

| 4.4 | Quoc-Nam Tran's Floyd-Warshall Algorithm (Tran, 2010)                                                 | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.5 | Quoc-Nam Tran's CUDA APSP Algorithm (Tran, 2010)                                                      | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 4.6 | Katz and Kider's Algorithm (Katz and Kider, 2008)                                                     | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     | 4.6.1 Limitations                                                                                     | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 4.7 | Modified Katz and Kider's Algorithm                                                                   | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 4.8 | Chapter Summary                                                                                       | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Res | ults and Evaluation                                                                                   | <b>53</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5.1 | Evaluation Method                                                                                     | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5.2 | Algorithm Summary                                                                                     | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5.3 | Evaluation Setup                                                                                      | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5.4 | Quoc-Nam Tran's Floyd-Warshall Results                                                                | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5.5 | Quoc-Nam Tran's CUDA APSP Results                                                                     | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5.6 | Katz and Kider's Results                                                                              | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5.7 | Modified Katz and Kider's Results                                                                     | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5.8 | Harish and Narayanan's Results                                                                        | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5.9 | CUDA Results Comparison                                                                               | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     | 5.9.1 Quoc-Nam Tran's Algorithms                                                                      | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     | 5.9.2 Katz and Kider's Algorithm                                                                      | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     | 5.9.3 Harish and Narayanan's Algorithm                                                                | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Cor | nclusions                                                                                             | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6.1 | Future Work                                                                                           | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6.2 | Final Conclusion                                                                                      | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     | 4.5<br>4.6<br>4.7<br>4.8<br><b>Res</b><br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9 | 4.5 Quoc-Nam Tran's CUDA APSP Algorithm (Tran, 2010) 4.6 Katz and Kider's Algorithm (Katz and Kider, 2008) 4.6.1 Limitations 4.7 Modified Katz and Kider's Algorithm 4.8 Chapter Summary  Results and Evaluation 5.1 Evaluation Method 5.2 Algorithm Summary 5.3 Evaluation Setup 5.4 Quoc-Nam Tran's Floyd-Warshall Results 5.5 Quoc-Nam Tran's CUDA APSP Results 5.6 Katz and Kider's Results 5.7 Modified Katz and Kider's Results 5.8 Harish and Narayanan's Results 5.9 CUDA Results Comparison 5.9.1 Quoc-Nam Tran's Algorithm 5.9.2 Katz and Kider's Algorithm 5.9.3 Harish and Narayanan's Algorithm  Conclusions 6.1 Future Work |

# List of Figures

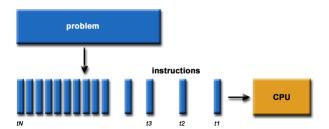

| 2.1 | A representation of a sequential algorithm on the CPU (Barney, 2010) | 11 |

|-----|----------------------------------------------------------------------|----|

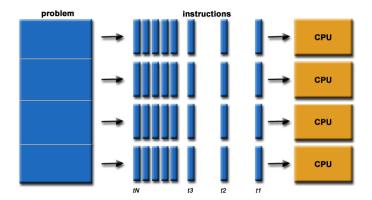

| 2.2 | A representation of a parallel algorithm on multiple CPU (Bar-       |    |

|     | ney, 2010)                                                           | 12 |

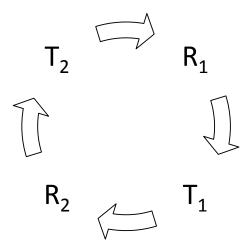

| 2.3 | A Diagram Showing Two Threads in Circular Deadlock                   | 14 |

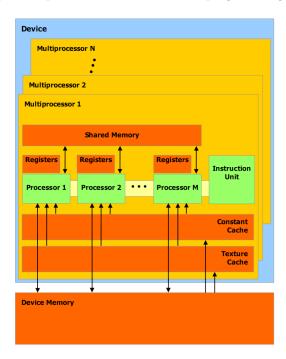

| 2.4 | CUDA Hardware Model, Demonstrating Memory Hierarchy and              |    |

|     | Overall Hardware Architecture of CUDA GPUs (NVIDIA, 2009)            | 21 |

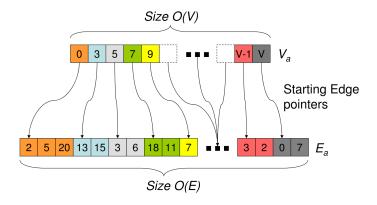

| 4.1 | Graph Representation as a Compacted Adjacency List (Harish           |    |

|     | et al., 2009)                                                        | 39 |

| 4.2 | Equation to Skip Over $x$ Thread Blocks                              | 48 |

| 4.3 | Equation to Skip Over $y$ Thread Blocks                              | 48 |

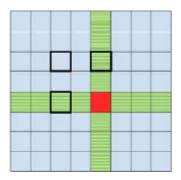

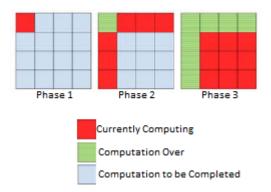

| 4.4 | Overview of Katz's Data Access During Phase 3 (Katz and Kider,       |    |

|     | 2008)                                                                | 49 |

| 4.5 | Overview of Katz's Algorithm Executing where 0,0 is the Primary      |    |

|     | Block (Katz and Kider, 2008)                                         | 49 |

| 5.1 | Experimental PC Specifications                                       | 54 |

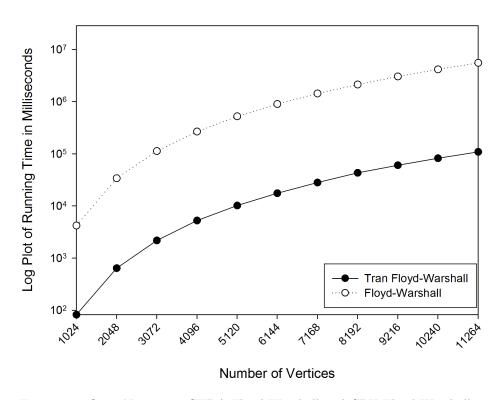

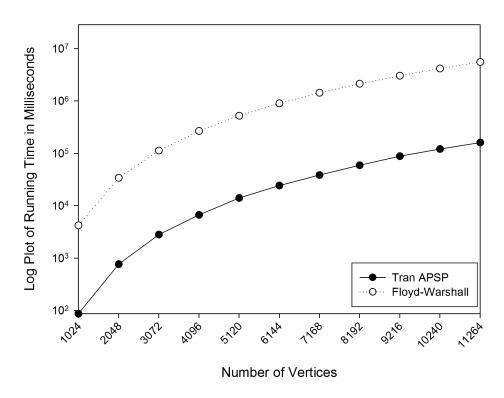

| 5.2 | Quoc-Nam Tran CUDA Floyd-Warshall and CPU Floyd-Warshall             | 56 |

| 5.3 | Quoc-Nam Tran CUDA APSP and CPU Floyd-Warshall                       | 58 |

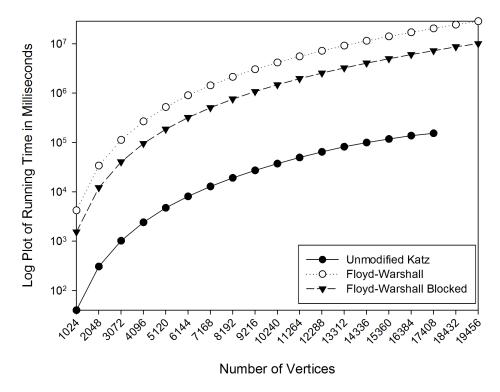

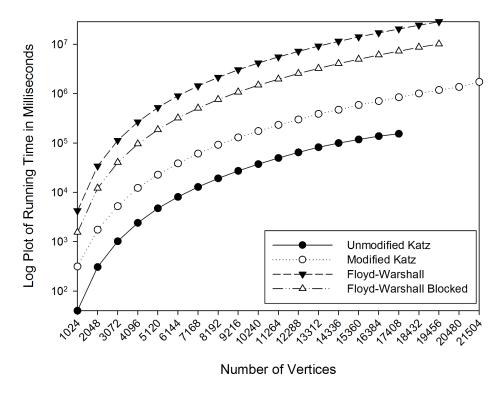

| 5.4 | Katz and Kider's Algorithm, CPU Floyd-Warshall and CPU Blocked       |    |

|     | Floyd-Warshall                                                       | 59 |

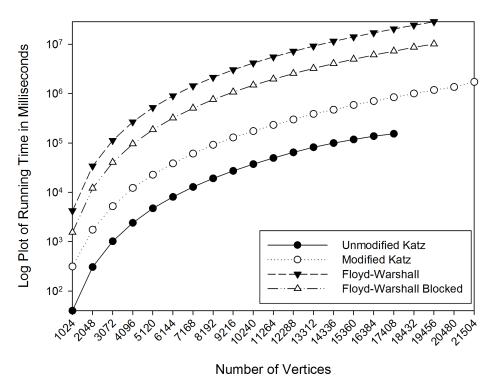

| 5.5 | Katz and Kider's Algorithm, Modified Algorithm, CPU Floyd-           |    |

|     | Warshall and CPU Blocked Floyd-Warshall                              | 61 |

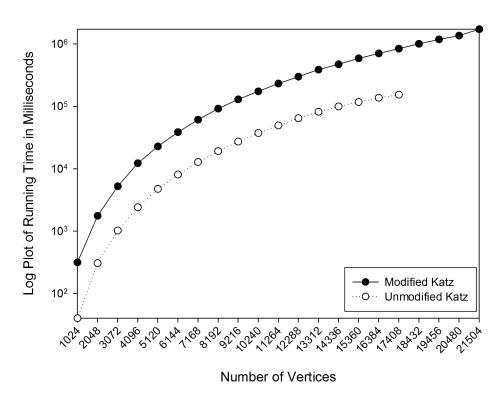

| 5.6 | Katz and Kider's Shared Algorithm and Modified Algorithm             | 62 |

| 5.7 | Katz and Kider's Shared and Modified Algorithms with Floyd-          |    |

|     | Warshall and Blocked Floyd-Warshall                                  | 63 |

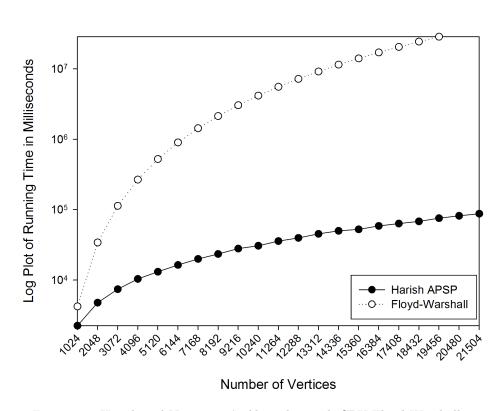

| 5.8 | Harish and Narayanan's Algorithm with CPU Floyd-Warshall             | 65 |

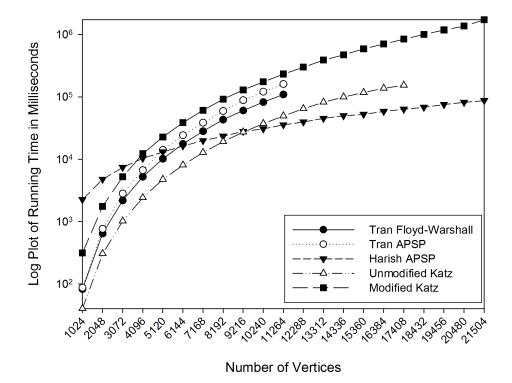

| 5.9 | All CUDA Algorithms                                                  | 66 |

# List of Tables

| 2.1 | Flynn's Taxonomy                       | 15 |

|-----|----------------------------------------|----|

| 2.2 | Single Instruction, Single Data        | 15 |

| 2.3 | Single Instruction, Multiple Data      | 16 |

| 2.4 | Multiple Instruction, Single Data      | 16 |

| 2.5 | Multiple Instruction, Multiple Data    | 17 |

| 2.6 | Device Memory Features (NVIDIA, 2012)  | 20 |

|     |                                        |    |

| 5.1 | A Sumary of Each Implemented Algorithm | 54 |

# Glossary

API Application Programming Interface.

**APSP** All-Pairs Shortest Path.

CPU Central Processing Unit.

**CUDA** Compute Unified Device Architecture.

**device memory** is the largest storage available on the GPU, similar to RAM on a PC.

**DRAM** Dynamic Random Access Memory.

**GB** Gigabyte  $(10^9 \text{ bytes})$ .

GPGPU General-Purpose Computing on Graphics Processing Units.

**GPU** Graphics Processing Unit.

**KB** Kilobyte  $(10^3 \text{ bytes})$ .

**kernel** is a CUDA function that allows code to be executed in parallel on the GPU.

**MB** Megabyte  $(10^6 \text{ bytes})$ .

MIMD Multiple Instruction, Multiple Data.

MISD Multiple Instruction, Single Data.

RAM Random Access Memory.

${\bf SIMD}\,$  Single Instruction, Multiple Data.

SISD Single Instruction, Single Data.

SSSP Single-Source Shortest Path.

thread block is a collection of CUDA threads that all execute on a single CUDA core.

warp is a group of CUDA threads that reside in a thread block, and that all execute the same instructions at the same time. Usually, in groups of 32.

## ${\bf Copyright}$

The copyright of this thesis rests with the author. No quotation from it should be published without the author's prior written consent and information derived from it should be acknowledged.

## Acknowledgements

I would like to thank my supervisor, Professor Iain Stewart, for his many useful and insightful suggestions in regards to this work and the advice given during our many meetings! I would also like to thank my family for their continued support during my time at Durham, as well as Charlotte Hawkins for checking my work many times over!

## Chapter 1

## Introduction

#### 1.1 Research Overview

Parallel computing on the Graphics Processing Unit (GPU) has been selected for use in an increasing number of systems and applications. The software supporting parallel computing on the GPU is becoming more and more comprehensive, with multiple Application Programming Interfaces (APIs) supporting the so-called General-Purpose Computing on Graphics Processing Units (GPGPU) era of parallel computing. With the growth in availability of said APIs, coupled with powerful, discrete GPUs, software developers and researchers are putting a greater amount of effort into parallelising their software to leverage the excellent performance benefits that GPGPU has to offer.

A lot of effort has gone into creating highly optimised solutions on the Central Processing Unit (CPU) in an attempt to squeeze as much performance out of existing CPU technology as possible. A common method of such optimisation is making the application dependent on a particular CPU architecture, in order to gain the benefits of using every feature available on that architecture. GPGPU programming allows applications to be offloaded onto the GPU and enjoy much greater performance than is currently available on the CPU by simply leveraging hardware that already exits, and has existed, in modern computers for many years.

Not all applications can enjoy this benefit however, as some problem areas are far more susceptible to parallel computing than others. The research area of graph theory has had some slight focus on GPGPU in recent years, with several solutions being developed for classic graph theory problems such as state space searching and implementing graph cuts (Vineet and Narayanan, 2008).

There has been an effort of research, investigating the All-Pairs Shortest Path (APSP) problem using Compute Unified Device Architecture (CUDA). CUDA is a GPGPU API from NVIDIA and is explained in much greater detail in Chapter 2. Judging the results of this research, and determining which algorithms are best to use in a given situation can be difficult, especially as they are often tested on completely different platforms, with different inputs and analysis. This research asks "Which All-Pairs Shortest Path algorithms solve their problem the fastest, and can the authors' claims be verified?".

#### 1.2 Intended Outcomes

As discussed in Section 1.1, this research intends to look at APSP algorithms with CUDA, and compare their performance against each other. In doing so, several additional research questions were considered and formulated to deliver:

- How do CUDA algorithms compare against their CPU counterparts?

- Can these CUDA algorithms be improved or modified in any beneficial way?

#### 1.3 Thesis Overview

This thesis aims to answer the research question that was asked in Section 1.1. In Chapter 2, we look at key concepts behind parallel computing, GPGPU, and CUDA. In doing so, several frameworks around parallel computing and parallel computing classifications are examined. Some problems with parallel computing are examined, such as race conditions and deadlocks as well as the problem of barriers. In classifying a parallel computer, Flynn's Taxonomy is observed, providing a solid ground for parallel classification. Additionally, Chapter 2 looks at the world of GPGPU and describes in detail NVIDIAs CUDA API.

In Chapter 3, we investigate the APSP problem, and how it can be solved on the CPU with several different algorithms using varying techniques. The algorithms observed serve as the basis of the algorithms that this thesis will implement with CUDA and so are important to understand.

In Chapter 4, the APSP problem is looked at in greater detail, specifically in relation to how the problem can be solved with CUDA. Firstly, existing methods of storing graphs on the GPU are examined, weighing their benefits and shortcomings against each other. Finally, the CUDA implementations are described in detail, complete with algorithmic listings showing their pseudo code. Improvements to selected algorithms are also shown where possible, as well as limitations that hamper algorithms where applicable.

In Chapter 5, the results of all CUDA and CPU algorithms are analysed, comparing their results with each other. The authors' claims are also examined to see whether their comments can be verified. Each CUDA algorithm is cross examined with every other, in an attempt to determine if there is a clear winner amongst them, or if some are suited to specific tasks.

Finally, in Chapter 6, the findings of this thesis are summarised, providing a clear overview of the entire body of work, the considerations to be taken into account when creating CUDA algorithms, and areas for future work.

# Chapter 2

# **Definitions**

#### 2.1 Parallel Computing

Traditionally, computer programs have been written for standard CPUs, i.e., they have been written with sequential execution in mind. A sequential program executes instructions in order, with each instruction occurring after the previous instruction has completed.

Parallel computing is "a form of computation in which many calculations are carried out simultaneously" (Almasi and Gottlieb, 1988). In order to obtain parallelism, the computer hardware must be designed with parallel execution in mind, so that many instructions can be executed at the same time. The hardware could simply include having multiple processors or cores in the CPU, having networked computers execute parallel executions, super computers, and now, GPU.

Figures 2.1 and 2.2 show a visual comparison between a standard sequential algorithm and a parallel algorithm running on a CPU with one core and a CPU with four cores respectively. Barney (2010) describes a useful example to help illustrate how a parallel algorithm relates to the real world. He states that parallel computing is simply an evolution of sequential computing that attempts to emulate what has always occurred in the real world with many complex, interrelated events happening at the same time while also in sequence.

Figure 2.1: A representation of a sequential algorithm on the CPU (Barney, 2010)

Figure 2.2: A representation of a parallel algorithm on multiple CPU (Barney, 2010)

#### 2.1.1 Bernstein's Conditions

There are many challenges in creating parallel algorithms. Data dependency issues are key in implementing parallel algorithms, as not fully comprehending them can severely affect the performance of an algorithm. In understanding the data dependencies of a sequential program, we can see whether it can be successfully parallelised or not.

Bernstein (1966) devised a set of conditions that must exist if two or more processes can be executed in parallel. We say that  $I_i$  is the set of all inputs for a process  $P_i$ . Similarly,  $O_i$  is the set of all outputs for a process  $P_i$ .

When given two processes  $P_1$  and  $P_2$ , they may execute in parallel if the following rules are observed:

$$I_1 \cap O_2 = \emptyset$$

$$I_2 \cap O_1 = \emptyset$$

$$O_1 \cap O_2 = \emptyset$$

The rules defined by Bernstein (1966) state that two processes cannot execute in parallel unless they are flow independent (rule one), anti independent (rule two) and output independent (rule three).

Flow Dependent  $S_1$  precedes  $S_2$  where at minimum one output of  $S_1$  is an input to  $S_2$

**Anti Independent**  $S_1$  precedes  $S_2$  where the output of  $S_2$  overlaps input to  $S_1$

Output Independent  $S_1$  and  $S_2$  write to the same unique output

For example, Algorithm 1 below cannot be implemented in parallel successfully as there are issues with flow dependency. If we look at line four, we can see that this line cannot be executed before line three, as line four requires an input that depends on the outcome of line three.

However, Algorithm 2 is an example of a program that may be implemented in parallel, as there are no dependencies between data and instruction. Each line is independent and does not depend on the outcome of any other line.

#### **Algorithm 1** dependency(int i, int j)

```

1: int k;

2: int l;

3: k = i * j;

4: l = 3 * k;

```

#### **Algorithm 2** noDependency(int i, int j)

```

1: int k;

2: int l;

3: int m;

4: k = i * j;

5: l = 3 * j;

6: m = i + j;

```

#### 2.1.2 Common Problems with Parallel Programming

Often, when creating parallel algorithms, desired tasks are split into threads whose purpose is to solve some task in parallel with other threads. Often, multiple threads will want to read, and modify a common variable in order to perform some task. This can lead to a serious problem known as a race condition. Race conditions occur when separate threads both depend on a shared state. Without proper management, the threads can hold incorrect data or process incorrect data that has not been updated correctly by a different thread (Netzer et al., 1992).

Consider Algorithm 3 that helps to clarify race conditions.  $T_i$  refers to a resident thread of the parallel algorithm. Likewise,  $T_i$  refers to a register.

#### **Algorithm 3** raceCondition()

```

1: int i = 0

2: T_1 reads i into R_1

3: T_2 reads i into R_2

4: T_1 i = i + 1 (in R_1)

5: T_2 i = i + 1 (in R_2)

6: T_1 writes R_1 back to memory

7: T_2 writes R_2 back to memory

```

In Algorithm 3, the result in i at the end of the algorithm is 1. However, the expected result is 2. To avoid this common problem, mutual exclusion must be provided by using a lock. The lock will allow a thread to assume control of a variable (in this case, i) and therefore stop any other thread from reading and/or writing to it until the controlling thread has released the lock.

In utilising locks to solve race conditions, another serious problem is introduced. Deadlocks occur when two or more threads are waiting for the other(s)

to finish and neither of them ever do (Silberschatz et al., 2006). For example, imagine two threads  $(T_x)$  and two printers  $(R_x)$ . Now, imagine each thread requesting the other's printer. This situation will cause a deadlock as the printers have not yet been released by the original threads. E.g.  $T_1$  is in control of  $R_1$ , but is also requesting  $R_2$ . However,  $T_2$  currently controls  $R_2$ ; causing a deadlock. This form of deadlock is known as circular deadlock, or a circular chain, and can be seen in Figure 2.3.

Figure 2.3: A Diagram Showing Two Threads in Circular Deadlock

#### 2.1.3 Flynn's Taxonomy

When looking at the world of parallel computing, there are several ways in which you can classify a parallel computing machine. These classes could be based on the hardware architecture of the machine. For example, Flynn (1972) presents a method of classifying a parallel computing machine based on its hardware architecture, and therefore, programmability.

Flynn's classification is based on two separate dimensions, Instruction and Data. Furthermore, these dimensions are split into two states, Single or Multiple. This leads to four possible classifications that form Flynn's Taxonomy and can be seen in Table 2.1.

|               | Single Instruction | Multiple Instruction |  |

|---------------|--------------------|----------------------|--|

| Single Data   | SISD               | MISD                 |  |

| Multiple Data | SIMD               | MIMD                 |  |

Table 2.1: Flynn's Taxonomy

As we will see in Section 2.4, the GPU used for this project is a Single Instruction, Multiple Data (SIMD) processor, capable of performing thousands of identical instructions on any number of pieces of data.

#### Single Instruction, Single Data (SISD)

- Only a **Single Instruction** is being executed by the CPU during any given clock cycle.

- Only a **Single Data** is being used as input for the current instruction during any given clock cycle.

- "Represents most conventional computing equipment available today" (Flynn, 1972).

| Previous Instruction |

|----------------------|

| load A(1)            |

| load B(1)            |

| C(1) = A(1) + B(1)   |

| store C(1)           |

| Next Instruction     |

Table 2.2: Single Instruction, Single Data

#### Single Instruction, Multiple Data (SIMD)

- Only a **Single Instruction** is being executed by the CPU during any given clock cycle.

- Multiple Data can be used by each processor to allow for multiple inputs.

- Best suited for systems with multiple streams of data, with a single instruction. E.g. a modern GPU.

| Previous Instruction | Previous Instruction |

|----------------------|----------------------|

| load A(1)            | load $A(n)$          |

| load B(1)            | load $B(n)$          |

| C(1) = A(1) + B(1)   | C(n) = A(n) + B(n)   |

| store C(1)           | store $C(n)$         |

| Next Instruction     | Next Instruction     |

| (a) Processor 1      | (b) Processor n      |

Table 2.3: Single Instruction, Multiple Data

#### Multiple Instruction, Single Data (MISD)

- Multiple Instructions are being executed by each processor during any given clock cycle.

- Only a **Single Data** is used by each processor for input in any given clock cycle.

| Previous Instruction | Previous Instruction |

|----------------------|----------------------|

| load A(1)            | load A(1)            |

| load B(1)            | load B(1)            |

| C(1) = A(1) + 1      | C(1) = A(1) + 1      |

| store C(1)           | store C(1)           |

| Next Instruction     | Next Instruction     |

| (a) Processor 1      | (b) Processor n      |

Table 2.4: Multiple Instruction, Single Data

#### Multiple Instruction, Multiple Data (MIMD)

- Multiple Instructions are being executed by each processor during any given clock cycle.

- Multiple Data can be used by each processor to allow for multiple inputs.

- Execution on a MIMD can be either synchronous or asynchronous.

- The most common form of parallel computer.

- The majority of the world's super computers follow the MIMD architecture.

| Previous Instruction | Previous Instruction |

|----------------------|----------------------|

| load A(1)            | load $Z(n)$          |

| load B(1)            | foo()                |

| C(1) = A(1) + B(1)   | bar()                |

| store C(1)           | while Z is true      |

| Next Instruction     | Next Instruction     |

| ( ) =                | (1) =                |

(a) Processor 1

(b) Processor n

${\bf Table~2.5:~Multiple~Instruction,~Multiple~Data}$

#### 2.2 GPGPU

In recent years, the advent of GPGPU has popularised the use of parallel computing on the GPU in achieving significant performance gains on a relatively cheap hardware device. GPGPU is a method of using the GPU to perform computations that would usually be executed by the CPU, rather than performing calculations to handle computer graphics, as is their traditional use. When the GPU is used for GPGPU, it can be viewed as a coprocessor to the CPU, offloading complex tasks that the GPU can tackle in parallel.

GPGPU provides an extremely cost effective alternative for parallel algorithms that would normally be exclusive to supercomputers, with a low-end CUDA enabled GPU costing approximately £25 compared to a super computer such as IBM's Blue Gene system at \$1.3million.

Multiple GPUs in a single system can be utilised for a single problem, often increasing the performance of parallel applications. This project does not utilise multiple GPU however. The applications of GPGPU are far reaching and include some of the following:

- Graph Theory.

- Ray Tracing.

- Matrix and/or Vector Operations.

- Signal Processing.

- Image Processing.

- Speech Recognition.

- Physics Simulations.

- Medical Computation.

Multiple GPGPU APIs exist to utilise the GPU for parallel computing. Popular APIs include NVIDIAs CUDA, OpenCL Khronos (2011) and DirectX's DirectCompute platform (Microsoft, 2012). This research focuses solely on NVIDIAs CUDA API. Each have their advantages and disadvantages, but all provide a solid parallel computing API to utilise the powerful hardware of modern GPU.

Modern graphics cards have a specialised hardware architecture that can be represented as a parallel computer. Unlike traditional graphics cards, GPUs such as NVIDIAs 580GTX are equipped with 16 multiprocessors, each with 32 cores, providing an impressive 512 cores. Each core has access to a global bank of memory, much like the Random Access Memory (RAM) on a PC, as well as a block of shared memory per multiprocessor which provides fast storage that can be used to share data between parallel processes. The potential of GPGPU is extremely great, given this unique hardware architecture that can provide great performance benefits to algorithms at a relatively low cost.

#### 2.3 What is CUDA?

CUDA is a parallel computing solution developed by NVIDIA, encompassing both a software and hardware architecture for using an NVIDIA GPU as a parallel computing device without the need for a graphics API. CUDA is available for all NVIDIA GPU following (and including) their G80 series of GPUs.

The CUDA API is an extension of the C programming language, providing programmers with a set of tools to create parallel algorithms. By providing the API in C, CUDA gives many programmers who already know C to quickly pick up their tools and begin creating CUDA applications.

CUDA enabled GPUs now have an install base of at least 100 million units (NVIDIA, 2009). Clearly, from this number, parallel algorithms utilising CUDA can be distributed easily to the mass market with a large number of machines supporting the technology, making CUDA an ideal candidate to boost the performance of a wide range of applications, both academically and commercially, examples of which are given in Section 2.2.

As a parallel computing platform, CUDA is designed to run thousands of threads at the same time, each thread executing the same code, but acting on multiple pieces of data, usually chosen programmatically to ensure that each thread works on a different pieces of unique data. Using this method, applications can be executed on the GPU, rather than the CPU as described above.

The CUDA API provides both high and low level APIs to suit the programmers needs. The lower level API provides a greater level of granularity and closeness to the underlying hardware, but decreases the readability and maintainability of CUDA code. These APIs are known as the runtime and driver APIs, respectively. In older versions of CUDA, the driver API provided a greater level of detail in querying the GPU memory, in providing more information than the runtime API. However, large strides have been made in the latest CUDA releases, both in API usability, and CUDA compiler performance. The two APIs are mutually exclusive however, and their use must never overlap.

Despite providing greater control, the lower level driver API does not provide a performance increase over runtime code, and should simply be used if a greater amount of control over the GPU is required. Older versions of CUDA provided an emulator, so that CUDA may be programmed without the presence of a CUDA GPU. Emulation was not supported by the driver API, and the emulation program was deprecated with CUDA 3.0.

Since its inception, there has been strong evidence showing that parallel algorithms on the GPU can greatly improve the performance of classic problems when compared to their sequential (CPU) equivalents, providing a justification for research in this area.

#### 2.4 CUDA Hardware Model

The architecture of a CUDA enabled GPU can be represented as a massive SIMD processor, examined in further detail in Section 2.1.3. A CUDA device consists of a number of multiprocessors, each with an identical number of processors (cores). Key to the architecture of CUDA devices is the different types of memory available, and their layout. Or, in other words, CUDAs memory hierarchy.

Table 2.6 gives a brief overview of the differing memory types, their access types, scope and locality. Additionally, Figure 2.4 shows these different types of memory that form CUDAs memory hierarchy and how they interact with the CUDA architecture on a higher level.

| Memory   | On/Off | Cached      | Access | Scope         | Lifetime |

|----------|--------|-------------|--------|---------------|----------|

|          | Chip   |             |        |               |          |

| Register | On     | N/A         | R/W    | Thread        | Thread   |

| Local    | Off    | Compute 2.x | R/W    | Thread        | Thread   |

| Shared   | On     | N/A         | R/W    | Block         | Block    |

| Global   | Off    | Compute 2.x | R/W    | Host + Device | Host     |

| Constant | Off    | Yes         | R      | Host + Device | Host     |

| Texture  | Off    | Yes         | R      | Host + Device | Host     |

Table 2.6: Device Memory Features (NVIDIA, 2012)

Firstly and perhaps most importantly is shared memory. Shared memory is located directly on-chip with the multiprocessors, providing extremely fast read and write times to and from the processor. In utilising shared memory, an impressive performance gain of over 100x can be gained over global memory (NVIDIA, 2011a).

When possible, the greatest amount of data should be moved from device memory into shared memory to try and squeeze as much performance out of CUDA as possible. Once data is in shared memory, computations can be performed there before writing the results back to device memory and thus, reducing the effects of latency between the multiprocessors and device memory. Latency simply describes the delay in clock cycles between some action being requested, and the action completing.

Unfortunately, shared memory is very small in comparison to the other memory types in CUDA. Older compute devices had just 16kb per multiprocessor to leverage. Newer compute devices however are graced with an additional 16kb, totalling 32kb per multiprocessor. Using shared memory wherever possible in CUDA code is clearly very beneficial from a performance standpoint when utilised correctly, but the programmer should be wary of the memory constraints that go hand-in-hand with shared memory.

As well as shared memory, registers are located on-chip providing extremely quick access for local variables stored in CUDA code. The use of too many registers, increasing register pressure, can have a negative effect on system performance and is explained in more detail in Section 2.6.

As we can see in Figure 2.4, texture and constant caches are provided on top of shared memory, also located on-chip. Cache memory is read only, and must be populated with data before CUDA code is executed. This can be performed with one of the many memory allocation features provided by the CUDA driver and runtime APIs. Whilst not as fast as shared memory, they

provide a greater amount of storage, and are significantly faster than device memory (global memory).

Device memory, (also known as global memory or Dynamic Random Access Memory (DRAM)) is available to all multiprocessors and their cores, effectively acting as the GPUs RAM. Device memory offers by far the greatest amount of storage capacity on the GPU but also suffers from being the slowest of all forms of memory. Device memory takes several clock cycles to both read and write data to and from the multiprocessors. It is often necessary to use device memory, due to its sheer capacity, so its speed must be kept in mind at all times to ensure the greatest performance benefits when programming for CUDA.

Figure 2.4: CUDA Hardware Model, Demonstrating Memory Hierarchy and Overall Hardware Architecture of CUDA GPUs (NVIDIA, 2009)

Fundamentally, understanding the benefits and drawbacks of these contrasting memory types is important and can greatly affect the performance of code. In knowing which storage type to use before creating a CUDA application, we can speed-up our applications as much as possible.

When programming for CUDA, it is important to take into consideration the time taken to physically move data between the host and the device. Minimising data transfer between host and device is important because those transfers are subject to much lower bandwidth than when moving data internally on the device (NVIDIA, 2011a). In some cases, it may be beneficial to just compute the data you need on the device, rather than copying it from host memory to device memory. Due to the high bandwidth, low latency of shared memory, it is always beneficial to use it wherever possible. Either by copying data from device memory to shared, and performing calculations there, or by simply computing the data required directly into shared memory (NVIDIA, 2011a).

#### 2.4.1 Coalesced Memory Access

"Perhaps the single most important performance consideration in programming for the CUDA architecture is coalescing global memory accesses" (NVIDIA, 2011a).

Dehne and Yogaratnam (2010) state that the goal of coalescing memory access is to combine multiple global memory access requests, by multiple threads, concurrently, into a single memory transaction for an independent portion of memory. The benefits of using this technique are vast, greatly improving the performance of the application. Using coalesced memory access can be a difficult task to master, as the GPU hardware support for the system has changed quite significantly with each version of CUDA.

Early versions of CUDA (1.0/1.1) required that the kernel explicitly align memory access patterns so that each thread had to access consecutive memory blocks that related to the order of the threads. Kernels are explained in greater detail in Section 2.5. Imagine four threads,  $T_0$  to  $T_3$ . To achieve coalesced memory access, each thread must access memory locations  $A_0$  to  $A_3$  where  $A_0 < A_1 < A_2 < A_3$  and are in a block of contiguous memory (Dehne and Yogaratnam, 2010). The memory accesses by these threads are coalesced using a half-warp (explained a little further on) of threads, where a full warp consists of thirty two threads. In this way, sixteen thirty two bit reads are coalesced into one sixty four byte memory access. As noted by Dehne and Yogaratnam (2010), this method of memory coalescing is really quite inflexible and rather complicated to implement successfully.

With the release of CUDA 1.2, the rules for coalesced memory access were relaxed, allowing for easier, and more successful use of the system (NVIDIA, 2011b). With CUDA 1.2 and above, if sixteen data accesses fit into a thirty two byte memory segment, then a single memory access of thirty two bytes is performed. If however, those sixteen accesses do not fit into a thirty two byte segment, but do fit into a sixty four byte segment, a sixty four byte segment is performed instead.

If the data stored in global memory does not map well for coalescing, it can be beneficial to pad your data so that it may match the coalesced access patterns. Padding data simply means to add extra data that has no meaning in order to achieve some storage constraint. In that way, you can still benefit from the performance improvement of coalesced access. This is only possible however, if you have enough free memory that you can waste with data padding (NVIDIA, 2011b). Clearly, using this coalesced system allows for a significant performance improvement by allowing multiple pieces of data to be accessed in parallel, rather than sequentially.

#### 2.5 CUDA Software Model

As explained in Section 2.3, two APIs are provided in order that CUDA might be programmed. Both APIs allow programmers to write special functions known as kernels that will be executed on the GPU. These kernels are structured in the same way as normal C functions, but are provided with additional intrinsics such as threadIdx that allow the executing thread to access information about itself. In this case, a 3-Dimensional vector (threadIDx) that holds the current thread's address. Each component of the vector represents the threads x, y, and z co-ordinates inside the thread block (explained below). This information can be used in a number of ways; most commonly in determining what data the thread should operate on.

In order to create a CUDA application, it is not necessary to understand the underlying hardware architecture, as it is hidden from the programmer. While a programmer does not need to understand the hardware architecture, it is extremely beneficial in being able to gain the most out of CUDA. By understanding the hardware architecture, as well as the intricate details of how CUDA threads operate and interact, the programmer can tailor his or her kernels to obtain the best performance possible from the code in utilising the many memory types and features of the CUDA architecture.

Instead of seeing the CUDA architecture when programming, threads are seen as being organised into blocks. Blocks are a convenient structure to think about threads in. A block is simply a 1, 2, or 3-Dimensional structure in which threads reside. In this way, groups of threads can easily be partitioned, allowing the programmer to easily decide how and where blocks should operate on data, and how shared memory should be utilised. Each thread is executed following the Single Program, Multiple Data (SPMD) model (see NVIDIA (2012)).

A programmer can define how many threads are executed for each kernel that is written. Taking the NVIDIA 8800GTX as an example, the programmer can define no more than 512 threads per block. Blocks can also be ordered into grids, with each grid holding at most 2<sup>32</sup> blocks. Therefore, 2<sup>41</sup> total threads can be executed per kernel. CUDA handles the assignment of threads and blocks to multiprocessors as well as other tasks including thread scheduling by utilising its GigaThread technology (see NVIDIA (2011b)).

The way in which threads are scheduled on the GPU differs greatly from the CPU. Whilst one might say that threads execute independently on the CPU, CUDA threads are scheduled in groups. These groups, known as warps, execute following the Single Instruction Multiple Thread (SIMT) model as described in Section 2.1.3. The minimum number of threads per warp is 32, with each thread inside the warp executing exactly the same instruction. Therefore, if the code being executed by the warp contains branches, each branch is expanded by filling in with null values where appropriate. Clearly, avoiding branches is critical as the performance of algorithms containing branches degrade as thread execution time is increased by expanding both branches.

CUDA provides functions that allow threads to be synchronised within a block. This synchronisation process acts as a barrier within the kernel which forces all threads in a block to hang until every thread in the block has reached the barrier. Blocks cannot be synchronised within a grid. Threads can be addressed using either a 1, 2, or 3-Dimensional index. Likewise, blocks may be addressed by a 1, 2, or 3-Dimensional index. CUDA provides thread and block

ID variables which can be used in a variety of ways to ensure that the threads in a kernel are performing the correct tasks on the correct piece or pieces of data.

A very important aspect of a block, is that threads within a block can communicate via the GPU shared memory. This is the only form of thread communication available with CUDA. The GPU automatically schedules where and how blocks should be executed on the device. Blocks are always contained to one core, i.e. a block and its threads can never be split between different cores. This restriction ensures that each thread in the block can communicate via shared memory as shared memory is located on-chip (as discussed in Section 2.4). Organising threads and the data allocated to shared memory is often a complex task, with additional issues such as avoiding bank conflicts.

Bank conflicts occur where one block's shared memory data overlaps another's. Bank conflicts are discussed in more detail in Section 2.8. Evidently, utilising shared memory is highly beneficial but requires skill to accomplish it successfully. As mentioned previously, the programmer specifies the number of threads that are used for each kernel. The programmer can also specify the block size that is to be used for each kernel. A kernel can also be executed multiple times with differing thread and block sizes for each execution to create the desired results.

CUDA refers to the GPU as the device, whereas the CPU is the host. Executing a kernel does not stop the host from executing it's own code, allowing both device and host code to run simultaneously. This feature was only introduced in a recent version of CUDA however, and kernel calls used to be blocking. Having blocking code means that the CPU would not be able to continue the CPU section of a CUDA program until the kernel returned control to the host.

If the host wishes to access device memory whilst a kernel is executing, it is necessary for the kernel to finish its execution. Therefore, the host code is blocked until kernel execution finishes, at which point the host may proceed. As of CUDA compute version 1.1 and above, asynchronous memory access is supported whilst a kernel is executing, allowing host code to access device memory during kernel execution. This feature can be useful in certain problem domains, but for this project, its use is limited at best.

If the programmer wishes, multiple kernels can be executed asynchronously, allowing multiple differing tasks to be completed at once. In this regard, the kernels must be carefully written to ensure that enough memory is available for each kernel and that performance isn't harmed by executing more than one kernel at any one time.

#### 2.6 Occupancy

CUDA executes instructions sequentially within a thread block, so executing a warp whilst another is paused or blocked is the only way in which CUDA can hide latencies and attempt to keep the GPU busy. CUDA defines a metric, occupancy, that allows determination of how effectively the GPU is being kept busy by CUDA (NVIDIA, 2012).

NVIDIA define occupancy as the "ratio of the number of active warps per multiprocessor to the maximum number of possible active warps" (NVIDIA, 2012). Having a low occupancy can interfere with the ability of CUDA to hide the performance issues related to memory latency which in turn results in a decrease in performance of CUDA code. Conversely, having a high occupancy rating does not always equal a higher performance rating of CUDA code. NVIDIA (2012) state that there is a point in which additional occupancy does not improve CUDAs performance.

Register availability is one of the major factors that can affect the occupancy of CUDA code. Kernels use registers to enable threads to store local variables in extremely efficient memory, allowing for low latency access by the thread. The number of registers available are limited, making them a scarce resource for thread blocks. They must be shared between all threads and blocks that reside on a single multiprocessor. As registers are allocated by the CUDA compiler all at one time, the number of threads that may reside on a multiprocessor is reduced as there are a limited number of registers. This leads to a lower occupancy rating due to the simple fact that fewer threads can be allocated to a multiprocessor when lots of registers need to be allocated to a thread block.

In calculating occupancy, the number of registers used by a thread is very important. CUDA devices with compute capability 1.0/1.1 have 8,192 registers per multiprocessor and can also have at most 768 threads resident on a multiprocessor at any one time (NVIDIA, 2012). With these statistics, each thread would have to use at most 10 registers to achieve 100% occupancy.

The exact nature of the relationship between register use and occupancy can be difficult to determine (NVIDIA, 2012). Due to the fact that register allocation differs slightly between different compute versions of CUDA devices, and the fact that a multiprocessor's shared memory is also partitioned between differing thread blocks, exact occupancy calculation is a difficult task. To combat this, NVIDIA provide CUDA developers with a spreadsheet in which critical data about CUDA kernels can be entered to provide an occupancy rating for the code. Additionally, NVIDIA provide a profiling tool that allows the CUDA code to be executed and monitored to calculate an occupancy rating.

#### 2.7 Thread and Block Heuristics

When choosing the number of threads per block, a multiple of 32 threads is recommended by NVIDIA as to ensure "optimal computing efficiency" and facilitate coalescing (NVIDIA, 2012). By ensuring the correct parameters for the number of threads per thread block, the balance between the latency of a CUDA application and resource utilisation can be found.

Occupancy and latency hiding depend on the number of active warps per multiprocessor which in turn depends on the register and shared memory constraints set by the compute capability of the GPU. To balance occupancy with resource allocation, the correct execution parameters should be chosen (NVIDIA, 2012).

Kernels should be designed to try and keep the GPU as active as possible, ensuring that there is as little idle time as possible whilst a kernel is executing. A simple way of doing this is to ensure that the number of blocks specified is greater than the number of multiprocessors on the GPU. Different GPUs have contrasting numbers of multiprocessors however, which is important to keep in mind. In this way, each multiprocessor has at least one thread block to execute. Increasing the number of thread blocks so that each multiprocessor is assigned multiple thread blocks by the compiler is important. In doing this, if a thread block is forced to wait by a \_\_syncthreads() command, execution can be switched to another thread block, thus helping to keep the GPU busy at all times. NVIDIA recommend using thousands of thread blocks per kernel launch to ensure scalability with future GPUs (NVIDIA, 2011a).

Clearly, occupancy is not just determined by block size as many blocks may be present on a single multiprocessor at any one time. NVIDIA (2012) give the example that having a block size of 512 threads may result in occupancy of 66% as the maximum number of threads is 768. Therefore, only one active block would reside on a multiprocessor. However, a smaller block of 256 threads could result in 100% occupancy as there would be three active blocks on the multiprocessor.

Selecting the correct block size is important for the reasons described above, but there are several factors in choosing the block size, depending on the task at hand. Currently, experimenting with block sizes is needed to obtain the best performance, but NVIDIA (2012) provide the following rules that should be followed to ensure block and thread heuristics are set correctly.

- Threads per block should be a multiple of warp size to avoid wasting computation, and to facilitate coalescing.

- At least 64 threads per block should be used.

- Between 128 and 256 threads per block is a better choice however. This

provides a good base range for initial experimentation of different block

sizes.

- If latency is an issue, use smaller thread blocks rather than one large one. This is especially useful if \_\_syncthreads() is frequently used.

#### 2.8 Bank Conflicts

As we know from Sections 2.4 and 2.5, shared memory has a much higher bandwidth and lower latency than global memory. This is not the case however where bank conflicts occur. Shared memory is divided into equally sized block (banks) that are accessible simultaneously by threads resident on a single multiprocessor. "Therefore, any memory load or store of n addresses that spans n distinct memory banks can be serviced simultaneously" (NVIDIA, 2012). As a result, thread blocks can achieve a bandwidth that is n times as great as the bandwidth capabilities of a single bank on its own.

If however, there are several memory addresses in a request that map to the same bank of shared memory, a bank conflict occurs and the access to the bank is serialised, impacting the performance of the kernel. In an attempt to reduce the effects of bank conflicts, the GPU will attempt to split each memory request that will result in a bank conflict into as many requests as necessary, so as to avoid conflicts, thus decreasing the bandwidth of the memory access.

#### 2.9 Chapter Summary

In this chapter, a general overview of parallel computing was discussed, as well as an in-depth look at GPGPU and more specifically, CUDA.

We have seen how Bernstein's Conditions can be used to identify whether an algorithm or process can be implemented in parallel by understanding what inherent dependencies are present in the process. In order that a process might be implemented in parallel, it must be flow independent, anti independent, and output independent.

Many new and interesting problems may present themselves in parallel computing. We have seen how race conditions can drastically effect how a program operates, in potentially resulting in incorrect data being read/written. This problem can lead to deadlock, whereby different threads end up waiting for other threads to finish a task, and therefore stall due to neither of them ever finishing.

Flynn's Taxonomy is an important framework for identifying how a parallel computer might be implemented. Flynn (1972) presents three classifications, SIMD, MISD, MIMD for identifying a parallel computer, and how it operates. As well as one classification, SISD, which identifies a traditional sequential computer. These classifications were later used in identifying how a CUDA GPU operates.

On looking at the GPGPU space, we have seen many useful applications of GPGPU, as well as several high profile APIs available for utilising the technology. CUDA was identified as a GPGPU API, as well as the one that will be utilised for this thesis. We have seen in great detail how the CUDA hardware and software models are composed, providing a parallel platform in which many thousands of resident threads may be executed in order to improve the performance of a subject problem. Technicalities of CUDA were presented, such as bank conflicts, and deciding on what memory type(s) should be utilised when implementing applications for CUDA.

## Chapter 3

# Introduction to the All-Pairs Shortest Path Problem

Graphs are an extremely common data structure in the field of computer science. There are many different problems that can and are represented as graphs, and algorithms to manipulate them are very important and widely used. This section looks at graph algorithms in terms of the APSP problem.

#### 3.1 What is the APSP Problem?

Imagine trying to find the shortest distance between all pairs of cities in an atlas. This problem can be solved using an APSP algorithm by representing the cities and roads between them as vertices and edges respectively. More formally, given a directed, weighted graph G = (V, E), we wish to find for every pair of vertices  $u, v \in V$ , a least weight (shortest) path from u to v, whose weight is the sum of all edges in the path (Cormen et al., 2001). |V| denotes the number of vertices in the set and |E| similarly denoting the number of edges in G.

The problem can be solved by running an algorithm that solves the Single-Source Shortest Path (SSSP) problem by running it on every vertex in G. A popular way of solving the problem using this means is using Dijkstra's SSSP algorithm. The edges' weights must be non-negative in order to use Dijkstra's algorithm for APSP. If negative edge weights are allowed, the slower Bellman-Ford algorithm must be used (Cormen et al., 2001). Where negative cycles are allowed, there is no shortest path as the traversal of such a cycle continually reduces the cost of the path. An algorithm using this approach is described in Section 4.3. A "true" APSP algorithm does not take this approach however. The following algorithms are expanded on in the following sections.

#### 3.2 Sequential Algorithms

#### 3.2.1 The Floyd-Warshall APSP Algorithm (Floyd, 1962)

The majority of CUDA algorithms described in Chapter 4 are originally based upon this algorithm so it is important to fully understand the theory behind it, and how it is implemented correctly.

The Floyd-Warshall algorithm utilises a dynamic programming technique and runs in  $O(n^3)$  time (Cormen et al., 2001). The algorithm operates on a directed graph G = (V, E) with non-negative edge weights. The algorithm can however operate if required with negative edge weights. If a cycle was to exist with total negative weight, the Floyd-Warshall algorithm can be used to detect them. Initially, all path lengths are 0. If negative cycles exist between two vertices, the path length between those two vertices will be negative.

Using the observations in Cormen et al. (2001), for any pair of vertices u and v, observe all paths from u to v where the intermediate vertices are from some subset of V  $\{1, 2, ..., k\}$  for any k. Additionally, let p be a path amongst u and v that is of a minimum weight.

Floyd-Warshall uses the relationship between p and all shortest paths between both u and v with all of the intermediate vertices in the set  $\{1,2,...,k-1\}$ . Depending on whether k is an intermediate vertex or not, one of two things can happen. Where k is not an intermediate vertex of p, all of the intermediate vertices in p must be in  $\{1,2,...,k-1\}$ . To that end, the least cost path between u and v will also be in the set  $\{1,2,...,k\}$ .

However, if k is an intermediate vertex of p, p can be split into two paths such that  $p_1$  is that path from u to k and the path  $p_2$  is from k to v. As k is no longer an intermediate vertex,  $p_1$  is the shortest path from u to k where all intermediate vertices are in  $\{1, 2, ..., k-1\}$  and  $p_2$  is the shortest path from k to v where all intermediate vertices are in  $\{1, 2, ..., k-1\}$ . This observation holds in that a subpath of a shortest path is in itself, a shortest path, as described by Cormen et al. (2001).

#### Algorithm 4 Floyd-Warshall

```

1: for k = 0 to n

2: for u = 0 to n

3: for v = 0 to n

4: graph[u][v] = min(graph[u][v], graph[u][k] + graph[k][v])

5: end

6: end

7: end

```

Algorithm 4 demonstrates how simple the Floyd-Warshall algorithm is to implement on the CPU. The computations can be done in place, meaning that the graph does not need to be copied and therefore, keeping the same amount of memory. This basic construct is used and modified by the majority of the following CUDA algorithms, and is a classic solution to the APSP problem.

#### 3.2.2 Dijkstra's Algorithm (Dijkstra, 1959)

As mentioned in Section 3.1, Dijkstra's algorithm, which solves the SSSP problem, can be used to solve APSP by repeating the algorithm on every vertex in a graph. Harish and Narayanan (2007) describe a CUDA algorithm based on Dijkstra's algorithm which is detailed in Section 4.3. A good implementation of Dijkstra's algorithm has a lower running time than that of the Bellman-Ford algorithm described in Section 3.2.3.

Dijkstra's algorithm maintains a set S of vertices whose shortest path weights from the source vertex s have already been determined. The algorithm repeatedly selects a vertex  $v \in V - S$  with "the minimum shortest path estimate" and then adds u to S, finally relaxing the edges that leave u. To improve on the Bellman-Ford algorithm, a minimum-priority queue Q is used. The original algorithmic description by Dijkstra does not use a minimum-priority queue (Dijkstra, 1959).

#### Algorithm 5 Pseudo Code for Dijkstra's Algorithm (Cormen et al., 2001)

```

1: S \leftarrow \emptyset

2: Q \leftarrow V

3: while Q \neq \emptyset

4: do u \leftarrow \text{EXTRACT-MIN}(Q)

5: S \leftarrow S \cup \{u\}

6: for each vertex v \in adj[u]

7: do RELAX(u, v, w)

```

We can see from Algorithm 5 that the loop invariant on line three will be true at the start of the algorithm. As the algorithm proceeds through the loop, a vertex u is extracted from Q and immediately added to S. This process maintains the invariant, and from it, we can see that the algorithm loops exactly |V| times. This holds as each vertex is removed from Q and added to S exactly once each. As edges are relaxed on lines four to seven, the path cost estimate is updated if the shortest path can be improved by passing through u to get to v (Cormen et al., 2001).

Dijkstra's algorithm uses a greedy approach in that it chooses the next closest or lightest vertex. Greedy algorithms are not always optimal but in Dijkstra's case, this algorithm does present an optimal solution. A proof for this can be found in the work by Cormen et al. (2001).

Dijkstra's algorithm gives us a running time of  $O(|E| + |V| \log |V|)$  when implemented using a minimum-priority queue that is represented by a Fibonacci heap. With this method, each call to EXTRACT-MIN only takes  $O(\log |V|)$  and each RELAX call takes just O(1) of which there are |E| calls. The Relax algorithm is explained in Section 3.2.3 and shown in Algorithm 7.