## **Durham E-Theses**

# $Parallel\ simulation\ techniques\ for\ telecommunication\\ network\ modelling$

Hind, Alan

#### How to cite:

Hind, Alan (1994) Parallel simulation techniques for telecommunication network modelling, Durham theses, Durham University. Available at Durham E-Theses Online: http://etheses.dur.ac.uk/5520/

#### Use policy

The full-text may be used and/or reproduced, and given to third parties in any format or medium, without prior permission or charge, for personal research or study, educational, or not-for-profit purposes provided that:

- a full bibliographic reference is made to the original source

- a link is made to the metadata record in Durham E-Theses

- the full-text is not changed in any way

The full-text must not be sold in any format or medium without the formal permission of the copyright holders.

Please consult the full Durham E-Theses policy for further details.

The copyright of this thesis rests with the author.

No quotation from it should be published without his prior written consent and information derived from it should be acknowledged.

# Parallel Simulation Techniques for

## Telecommunication Network Modelling

Alan Hind  $B.S\hat{c}$ . (Salford)

School of Engineering and Computer Science

University of Durham

A thesis submitted in partial fulfilment of the requirements of the Council of the University of Durham for the Degree of Doctor of Philosophy (Ph.D.).

January 1994

#### Abstract

In this thesis, we consider the application of parallel simulation to the performance modelling of telecommunication networks.

A largely automated approach was first explored using a parallelizing compiler to speedup the simulation of simple models of circuit-switched networks. This yielded reasonable results for relatively little effort compared with other approaches. However, more complex simulation models of packet- and cell-based telecommunication networks, requiring the use of discrete event techniques, need an alternative approach.

A critical review of parallel discrete event simulation indicated that a distributed model components approach using conservative or optimistic synchronization would be worth exploring. Experiments were therefore conducted using simulation models of queueing networks and Asynchronous Transfer Mode (ATM) networks to explore the potential speed-up possible using this approach. Specifically, it is shown that these techniques can be used successfully to speed-up the execution of useful telecommunication network simulations.

A detailed investigation has demonstrated that conservative synchronization performs very well for applications with good lookahead properties and sufficient message traffic density and, given such properties, will significantly outperform optimistic synchronization. Optimistic synchronization, however, gives reasonable speed-up for models with a wider range of such properties and can be optimized for speed-up and memory usage at run time. Thus, it is confirmed as being more generally applicable particularly as model development is somewhat easier than for conservative synchronization. This has to be balanced against the more difficult task of developing and debugging an optimistic synchronization kernel and the application models.

$\mathcal{DEO}$  GRATIA

## Acknowledgments

The following people have been vital to the production of this work; either in their direct advice and input or just in putting up with the fact that I was busy doing this.

- To my wife, Angie, and my children, Ben and Heather for their love.

- To my parents for their encouragement.

- To my supervisor, Professor Phil Mars of the University of Durham for his direction and advice.

- To Neil Macfadyen of BT. Laboratories, Core and Global Networks Division for discussions without number and enthusiasm without bounds.

- To Richard Earnshaw of the University of Twente, The Netherlands for friendship, working partnership and the ATM. Simulator.

- To Bruno Preiss and Wayne Loucks at the University of Waterloo, Ontario, Canada

for their kind hospitality when visiting their country and for YADDES.

- To Ron Kerr and Kevin Conner of the Computing Laboratory of the University of Newcastle-upon-Tyne – for allowing me access to NEWTON, and for their time and advice.

- To Steve Turner at the University of Exeter and Brian Roberts, Chris Booth and David Bruce at DRA. Malvern for their friendship, lively discussion and TWSIM.

- To John, Raghu, Matt, Phillip, Jeremy, Chen and David in the lab for a good laugh when in vital need.

- To Sylvia for all the arrangements.

The following trademarks are acknowledged: BT. and British Telecom are trademarks of British Telecommunications plc.; IMS. and occam are trademarks of Inmos Limited; IBM., SNA. and PC/AT. are a trademarks of International Business Machines Corp.; 3L is a trademark of 3L Limited; VAX is a trademark of Digital Equipment Corp.; Sun is a trademark of Sun Microsystems Corp.; Ethernet is a trademark of Xerox Corp.; Multimax is a trademark of Encore Computer Corp.; and Sim++ and Jade is a trademark of Jade Simulations International Corp.; Comnet II.5 and ModSim are trademarks of CACI Products Company Inc.

## Declaration

I hereby declare that this thesis is a record of work undertaken by myself, that it has not been the subject of any previous application for a degree, and that all sources of information have been duly acknowledged.

#### © Copyright 1994, Alan Hind

The copyright of this thesis rests with the author. No quotation from it should be published without his written consent, and information derived from it should be acknowledged.

## Contents

| 1 | Intr | oduction                                                     | 1  |

|---|------|--------------------------------------------------------------|----|

|   | 1.1  | Performance Evaluation                                       | 1  |

|   | 1.2  | Simulation Objectives                                        | 3  |

|   | 1.3  | Simulation Speed-up                                          | 5  |

|   |      | 1.3.1 Amdahl's Law                                           | 9  |

|   | 1.4  | Parallel Hardware Architectures                              | 11 |

|   | 1.5  | Outline of Thesis                                            | 16 |

| 2 | A B  | Review of Parallel Discrete Event Simulation                 | 19 |

|   | 2.1  | Introduction                                                 | 19 |

|   | 2.2  | Parallelizing Compilers                                      | 21 |

|   | 2.3  | Distributed Simulation Experiments                           | 24 |

|   | 2.4  | Distributed Simulation Functions                             | 25 |

|   | 2.5  | Distributed Simulation Events                                | 27 |

|   | 2.6  | Distributed Simulation Model Components                      | 28 |

|   | 2.7  | Combined Approaches                                          | 29 |

|   | 2.8  | Time Parallelism                                             | 30 |

|   | 2.9  | Summary                                                      | 32 |

| 3 | Syn  | chronization Approaches for Distributed Model Components     | 34 |

|   | 3.1  | Introduction                                                 | 34 |

|   | 3.2  | Synchronization in Action                                    | 35 |

|   | 3.3  | Conservative Synchronization Approaches                      | 38 |

|   |      | 3.3.1 Performance of Conservative Synchronization Approaches | 4: |

|   |      | 3.3.2 Critique of Conservative Synchronization Approaches    | 4  |

|   | 3.4  | Synchronous Approaches                                       | 4  |

|   |     | 3.4.1   | Performance of Synchronous Approaches                        | 48  |

|---|-----|---------|--------------------------------------------------------------|-----|

|   |     | 3.4.2   | Critique of Synchronous Approaches                           | 48  |

|   | 3.5 | Optim   | istic Synchronization Approaches                             | 49  |

|   |     | 3.5.1   | Enhancements to Optimistic Synchronization Approaches        | 50  |

|   |     | 3.5.2   | Performance of Optimistic Synchronization Approaches         | 57  |

|   |     | 3.5.3   | Critique of Optimistic Synchronization Approaches            | 59  |

|   | 3.6 | Summ    | ary                                                          | 61  |

| 4 | Par | allel S | imulation of Circuit-Switched Networks using a Parallelizing | ;   |

|   | Con | npiler  |                                                              | 63  |

|   | 4.1 | Introd  | uction                                                       | 63  |

|   | 4.2 | The T   | estbed Architecture                                          | 65  |

|   |     | 4.2.1   | Hardware Architecture                                        | 65  |

|   |     | 4.2.2   | Software Architecture                                        | 66  |

|   |     | 4.2.3   | Execution Model                                              | 67  |

|   | 4.3 | Discus  | ssion of Results                                             | 68  |

|   |     | 4.3.1   | Introduction                                                 | 68  |

|   |     | 4.3.2   | Uniprocessor Simulation Results                              | 71  |

|   |     | 4.3.3   | Multiprocessor Simulation Results for the Five-node Model    | 72  |

|   |     | 4.3.4   | Multiprocessor Simulation Results for the Ten-node Model     | 73  |

|   |     | 4.3.5   | Multiprocessor Simulation Results for the Twenty-node Model  | 74  |

|   | 4.4 | Concl   | usions                                                       | 75  |

| 5 | Par | allel S | imulation of Queueing Networks                               | 85  |

|   | 5.1 | Introd  | luction                                                      | 85  |

|   | 5.2 | YADI    | DES — Yet Another Distributed Discrete Event Simulator       | 86  |

|   |     | 5.2.1   | Sequential Event-list Synchronization                        | 87  |

|   |     | 5.2.2   | Distributed Multiple Event-list Synchronization              | 88  |

|   |     | 5.2.3   | Conservative Distributed Event-list Synchronization          | 88  |

|   |     | 5.2.4   | Optimistic Distributed Simulation Synchronization            | 89  |

|   | 5.3 | The S   | imulation Models                                             | 90  |

|   | 5.4 | Discus  | ssion of Results                                             | 93  |

|   |     | 5.4.1   | Initial Results for the Closed Stochastic Queueing Network   | 93  |

|   |     | 5 4 9   | Main Beaulte for the Closed Stochastic Queueing Network      | 0.4 |

|   |      | 5.4.3    | Virtual Time (VT) Memory Management Results for the Closed Stochas | S-  |

|---|------|----------|--------------------------------------------------------------------|-----|

|   |      |          | tic Queueing Network                                               | 98  |

|   |      | 5.4.4    | Discussion of Results for the Tandem Queueing Network              | 100 |

|   | 5.5  | Conclu   | isions                                                             | 102 |

| 6 | Para | allel Si | imulation of Asynchronous Transfer Mode Networks                   | 135 |

|   | 6.1  | Introd   | uction                                                             | 135 |

|   | 6.2  | Broad    | band Networks                                                      | 137 |

|   | 6.3  | Simula   | ator Architecture                                                  | 139 |

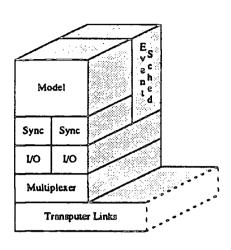

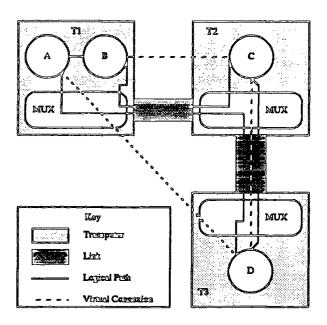

|   |      | 6.3.1    | The Multiprocessor Testbed                                         | 139 |

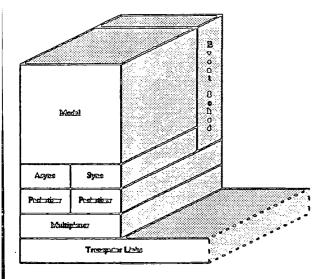

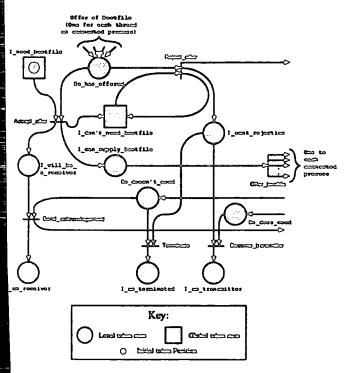

|   |      | 6.3.2    | The Software Architecture                                          | 139 |

|   | 6.4  | The S    | ynchronization Mechanism                                           | 140 |

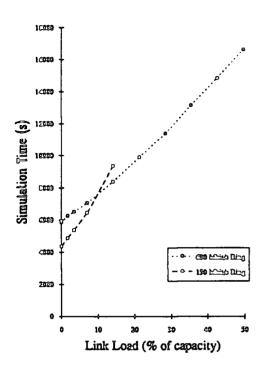

|   | 6.5  | The S    | imulator Results                                                   | 142 |

|   | 6.6  | Perfor   | mance Analysis of the Simulator                                    | 142 |

|   |      | 6.6.1    | Performance of Production Runs                                     | 142 |

|   |      | 6.6.2    | Variations in Lookahead                                            | 145 |

|   |      | 6.6.3    | Asymmetric Traffic                                                 | 147 |

|   | 6.7  | Concl    | usions                                                             | 147 |

| 7 | Con  | ıclusio  | ns and Further Work                                                | 159 |

|   | 7.1  | Concl    | usions                                                             | 159 |

|   | 7.2  | Furth    | er Work                                                            | 162 |

| A | Sim  | ulatio   | n Model Files                                                      | 183 |

| В | Pul  | olished  | Papers                                                             | 184 |

## List of Figures

| 1.1  | Amdahl's law                                                                   | 18 |

|------|--------------------------------------------------------------------------------|----|

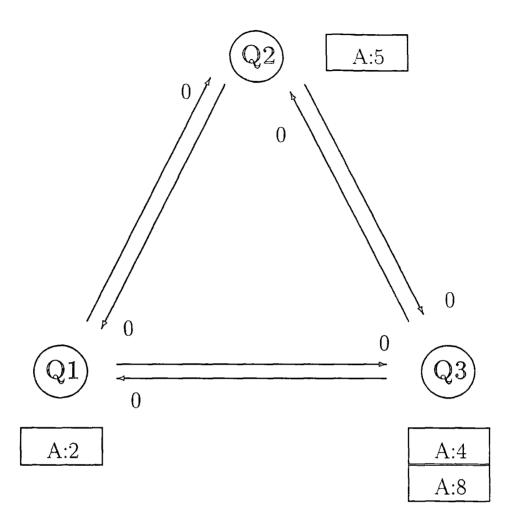

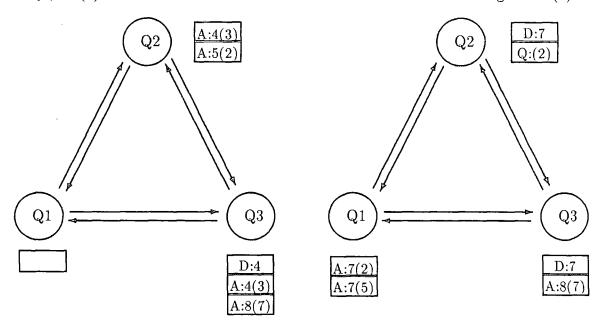

| 3.1  | Example network of processes at initialisation — all link-times are at zero    | 37 |

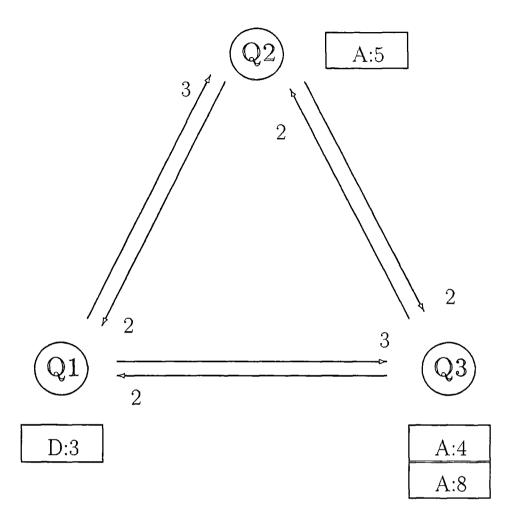

| 3.2  | Example network of processes at time 2—the link-times represent the time-      |    |

|      | stamp of the last message to cross the link                                    | 38 |

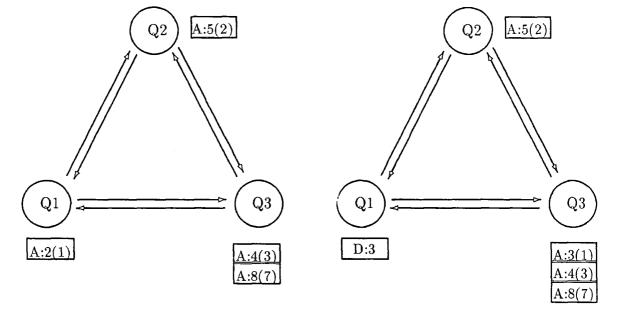

| 3.3  | Example network of processes—simulated using time windows                      | 46 |

| 3.4  | Example network of processes—simulated using time windows                      | 47 |

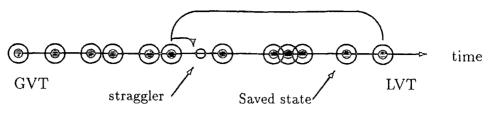

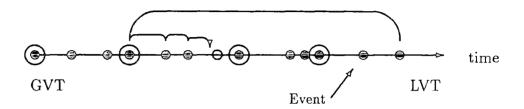

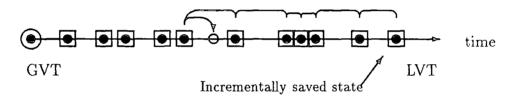

| 3.5  | Time warp rollback using different state-saving schemes                        | 54 |

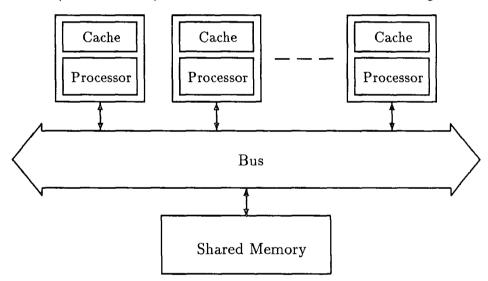

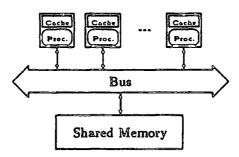

| 4.1  | Shared memory multiprocessor architecture with a single bus and local caches.  | 65 |

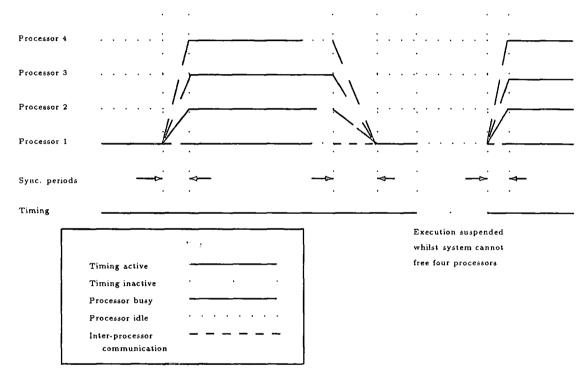

| 4.2  | Execution trace of a parallelized program on the Multimax shared memory        |    |

|      | multiprocessor                                                                 | 68 |

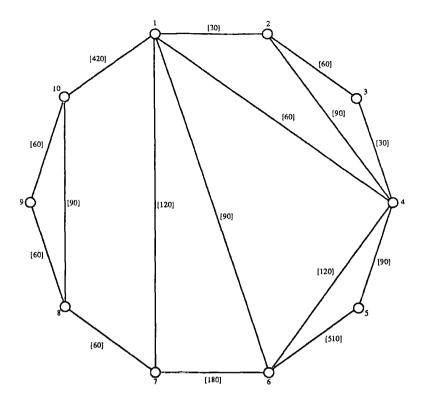

| 4.3  | The ten-node sparsely-connected network. The numbers in the square brack-      |    |

|      | ets indicate the capacity in circuits of each link                             | 70 |

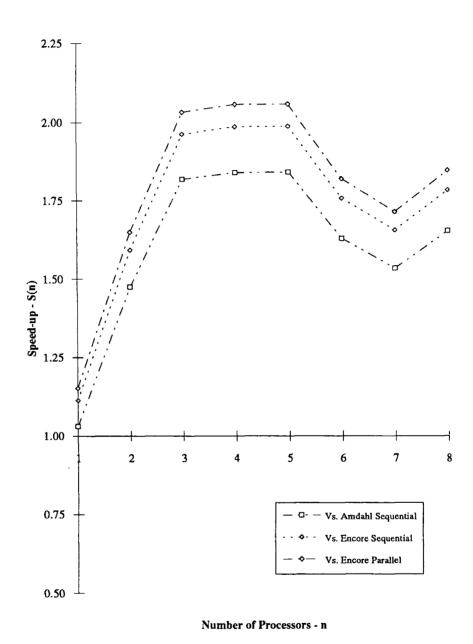

| 4.4  | Speed-up results for the ten-node fully-connected network comparing the        |    |

|      | alternative reference times                                                    | 77 |

| 4.5  | Speed-up results for the five-node fully-connected network model               | 78 |

| 4.6  | Comparison of percentage run-times used by the two most expensive pro-         |    |

|      | cesses using the automatically parallelized simulator                          | 79 |

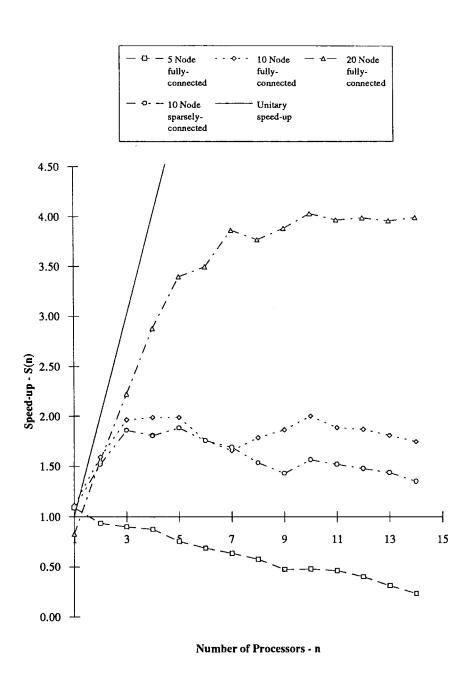

| 4.7  | Speed-up results for the ten-node fully- and sparsely-connected network models | 80 |

| 4.8  | Speed-up results for the ten-node fully-connected network model showing        |    |

|      | means and standard deviations from ten simulation runs                         | 81 |

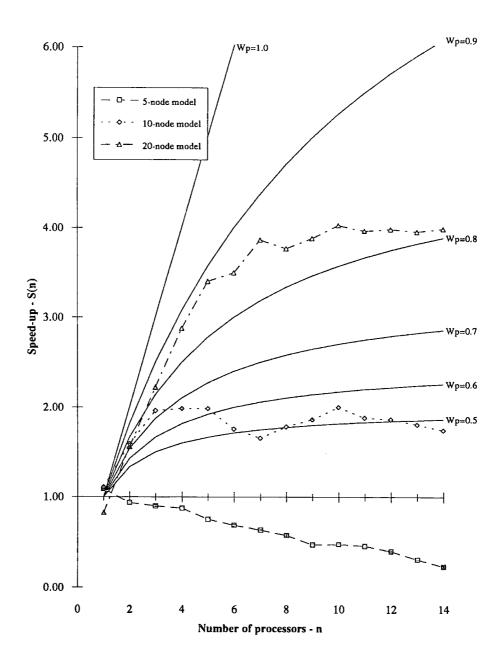

| 4.9  | Speed-up results for the twenty-node fully-connected network model             | 82 |

| 4.10 | Speed-up results comparing the performance of the hand optimized simulator     |    |

|      | for all network models                                                         | 83 |

| 4.11 | Speed-up results showing the performance of the hand optimized simulator         |     |

|------|----------------------------------------------------------------------------------|-----|

|      | for the fully-connected network models with Amdahl's law                         | 84  |

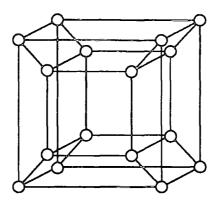

| 5.1  | A 4-dimensional hypercube                                                        | 91  |

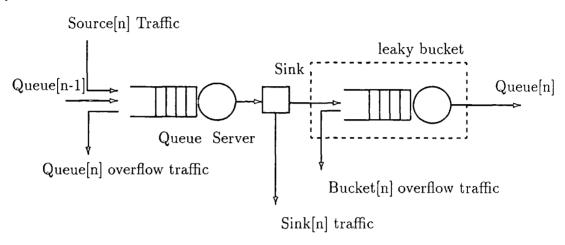

| 5.2  | YADDES process model of one switch of the tandem queueing network                | 92  |

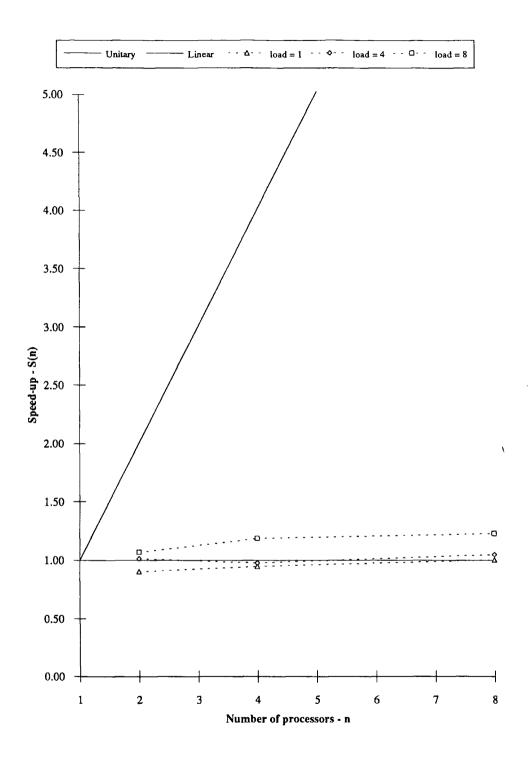

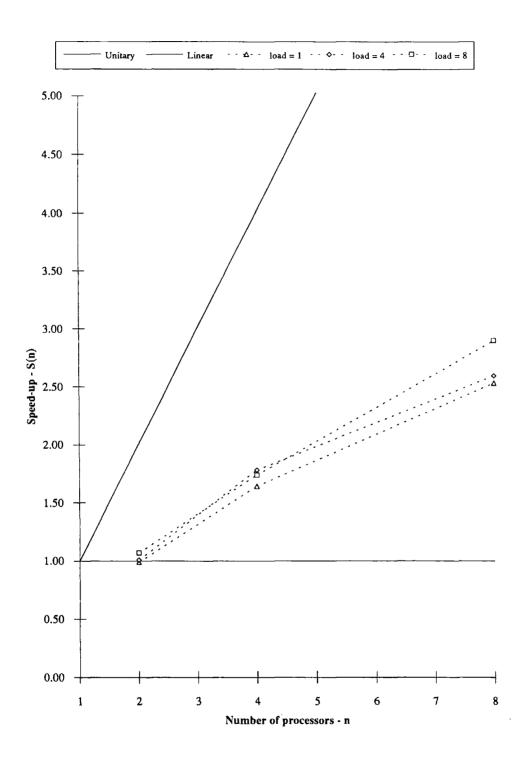

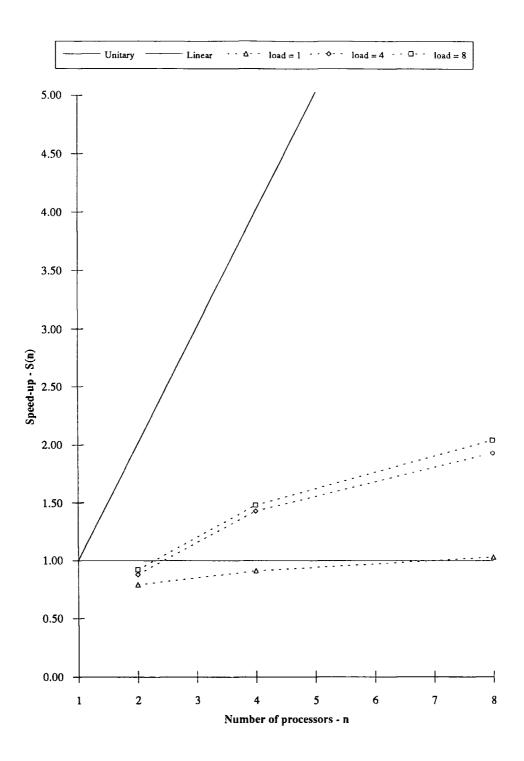

| 5.3  | Speed-up using multiple distributed event-list (ML) synchronization for the      |     |

|      | hypercube of queues                                                              | 104 |

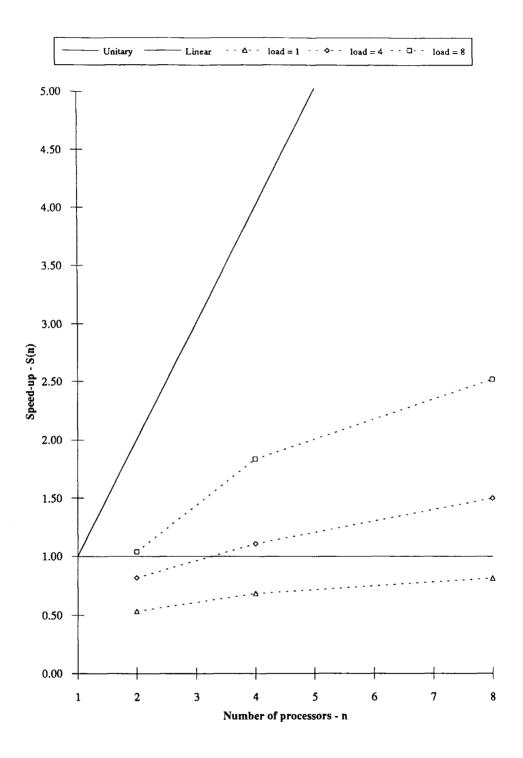

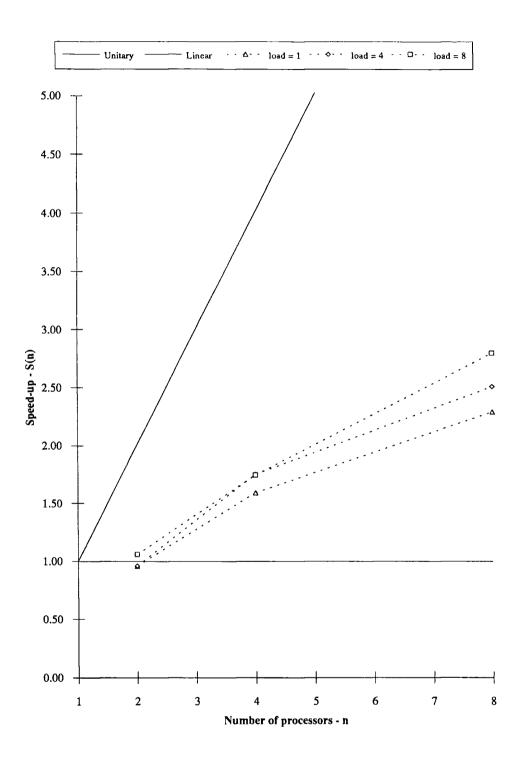

| 5.4  | Speed-up using conservative Chandy-Misra synchronization (CM) without            |     |

|      | Null-message cancellation for the hypercube of queues                            | 105 |

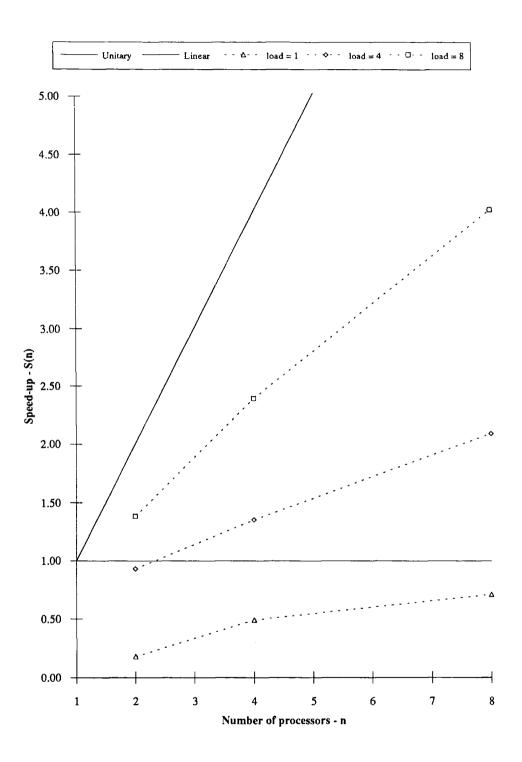

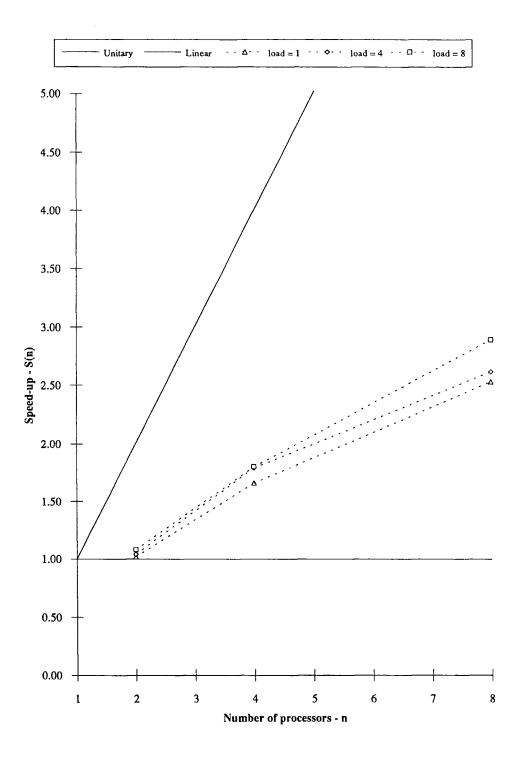

| 5.5  | Speed-up using conservative Chandy-Misra synchronization (CM) with Null-         |     |

|      | message cancellation (NMC) for the hypercube of queues                           | 106 |

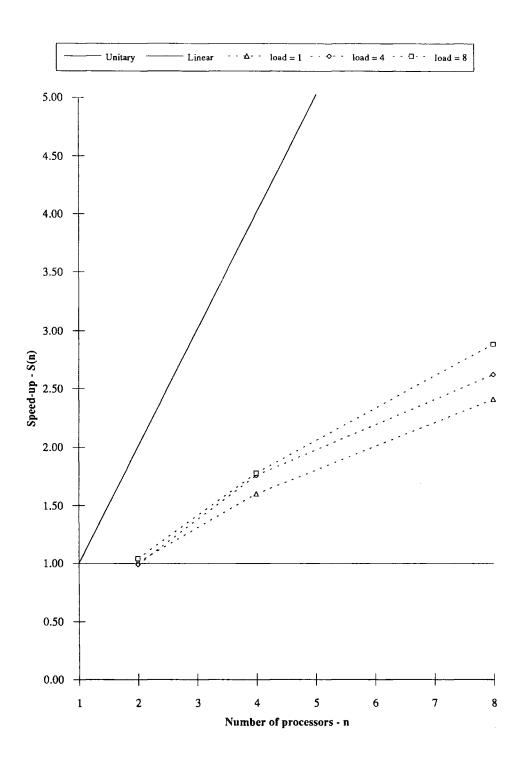

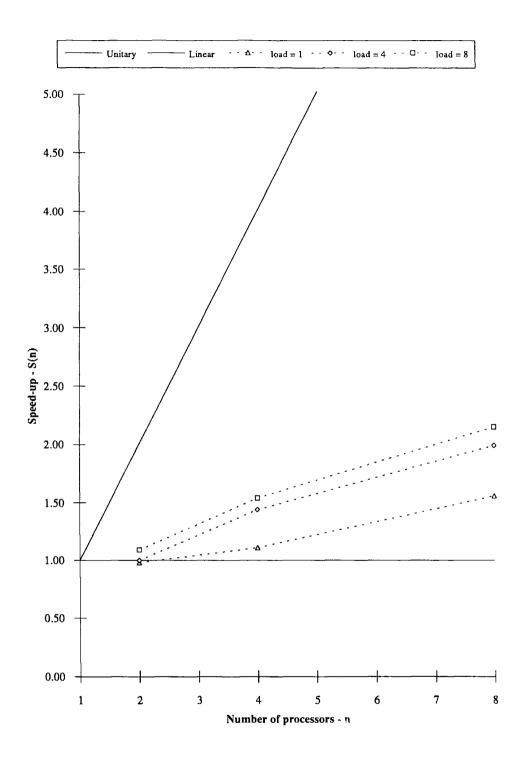

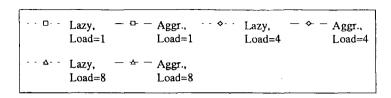

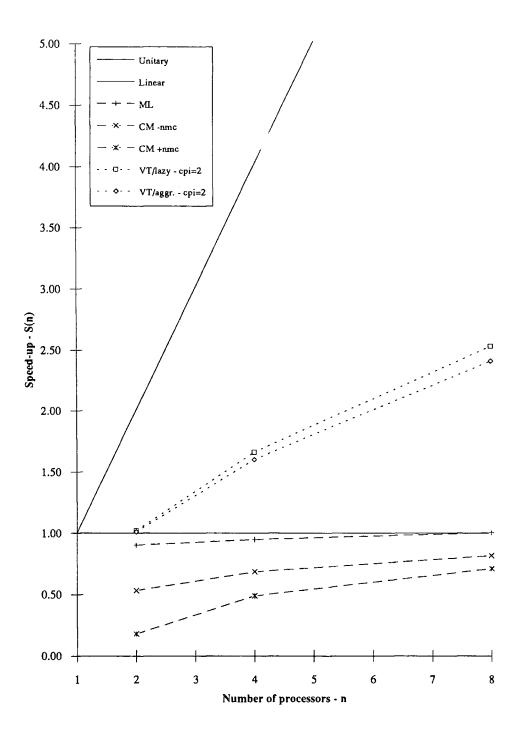

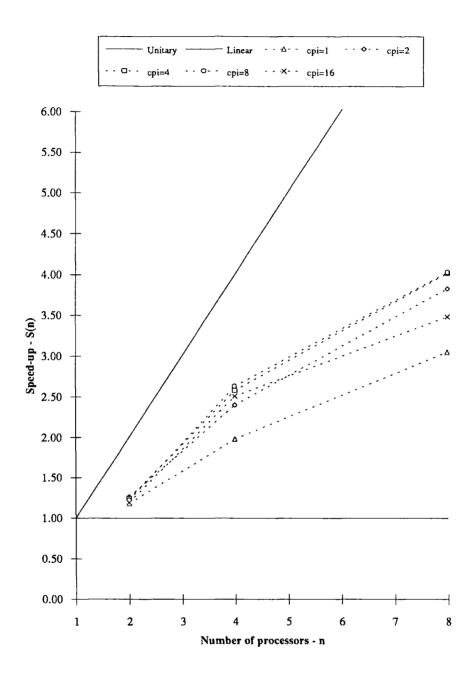

| 5.6  | Speed-up using virtual time synchronization (VT) with lazy cancellation and $\ $ |     |

|      | a CPI of one for the hypercube of queues                                         | 107 |

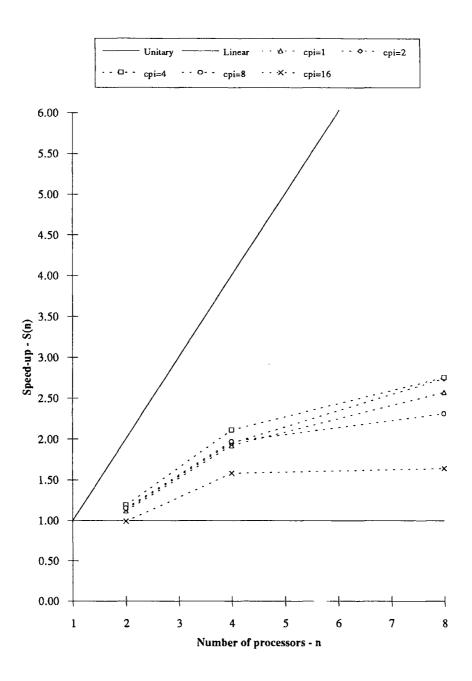

| 5.7  | Speed-up using virtual time synchronization (VT) with aggressive cancella-       |     |

|      | tion and a CPI of one for the hypercube of queues                                | 108 |

| 5.8  | Speed-up using virtual time synchronization (VT) with lazy cancellation and      |     |

|      | a CPI of two for the hypercube of queues                                         | 109 |

| 5.9  | Speed-up using virtual time synchronization (VT) with aggressive cancella-       |     |

|      | tion and a CPI of two for the hypercube of queues                                | 110 |

| 5.10 | Speed-up using virtual time synchronization (VT) with lazy cancellation and      |     |

|      | a CPI of four for the hypercube of queues                                        | 111 |

| 5.11 | Speed-up using virtual time synchronization (VT) with aggressive cancella-       |     |

|      | tion and a CPI of four for the hypercube of queues                               | 112 |

| 5.12 | Speed-up using virtual time synchronization (VT) with lazy cancellation and      |     |

|      | a CPI of eight for the hypercube of queues                                       | 113 |

| 5.13 | Speed-up using virtual time synchronization (VT) with aggressive cancella-       |     |

|      | tion and a CPI of eight for the hypercube of queues                              | 114 |

| 5.14 | Speed-up using virtual time synchronization (VT) with lazy cancellation and      |     |

|      | a CPI of sixteen for the hypercube of queues                                     | 115 |

| 5.15 | Speed-up using virtual time synchronization (VT) with aggressive cancella-       |     |

|      | tion and a CPI of sixteen for the hypercube of queues                            | 116 |

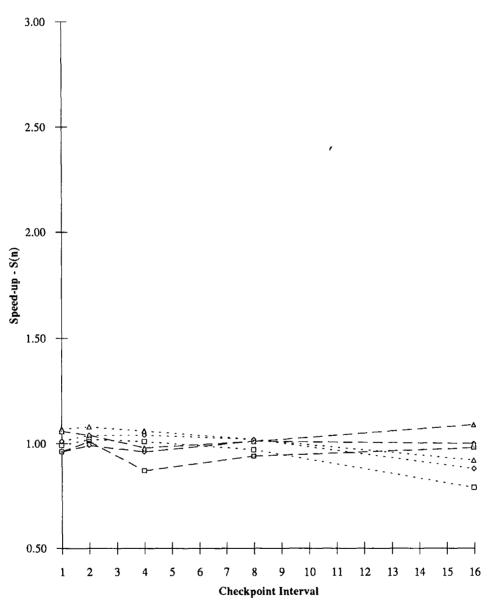

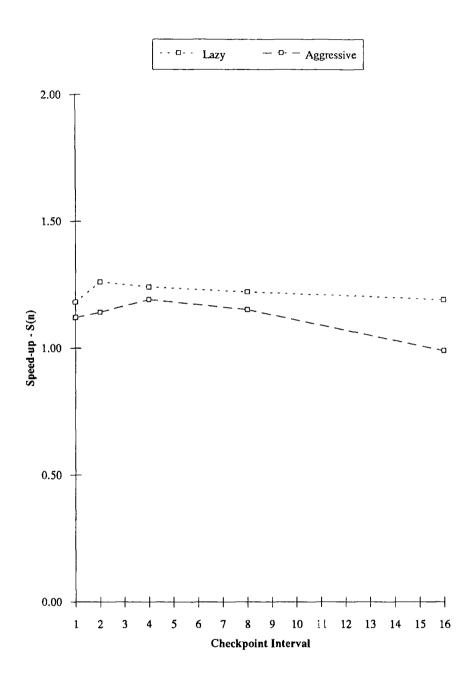

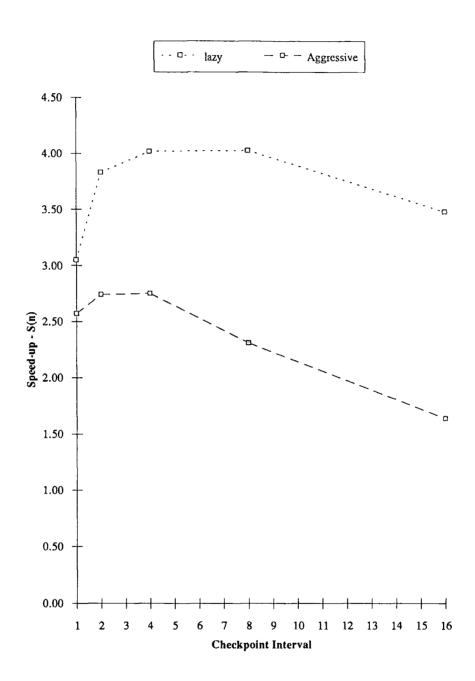

| 5.16 | Speed-up against CPI for virtual time synchronization (VT) on two proces-        |     |

|      | sors for the hypercube of queues                                                 | 117 |

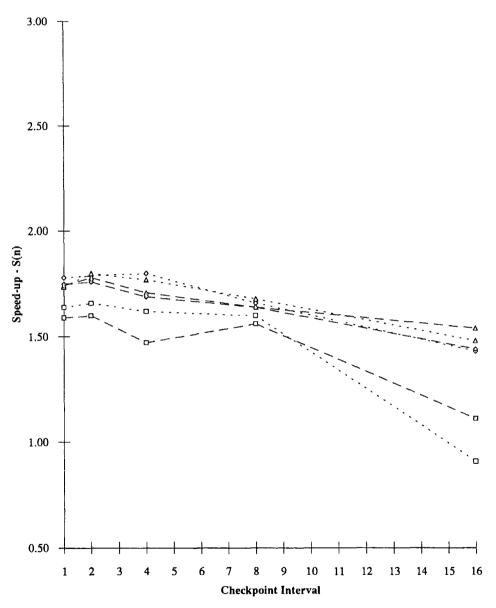

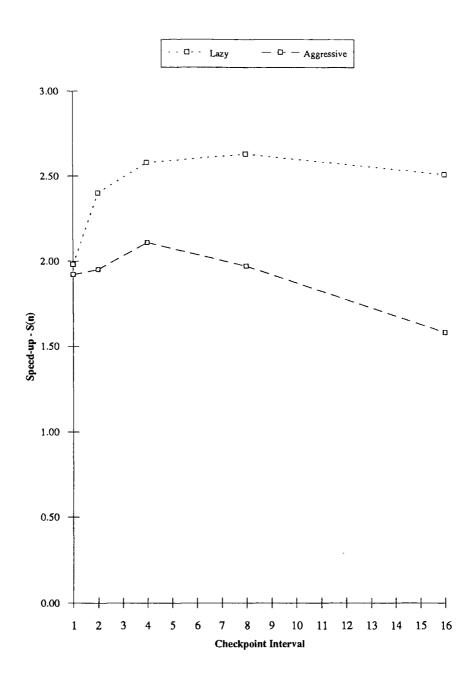

| 5.17 | Speed-up against CPI for virtual time synchronization (VT) on four proces-    |     |

|------|-------------------------------------------------------------------------------|-----|

|      | sors for the hypercube of queues                                              | 118 |

| 5.18 | Speed-up against CPI for virtual time synchronization (VT) on eight proces-   |     |

|      | sors for the hypercube of queues                                              | 119 |

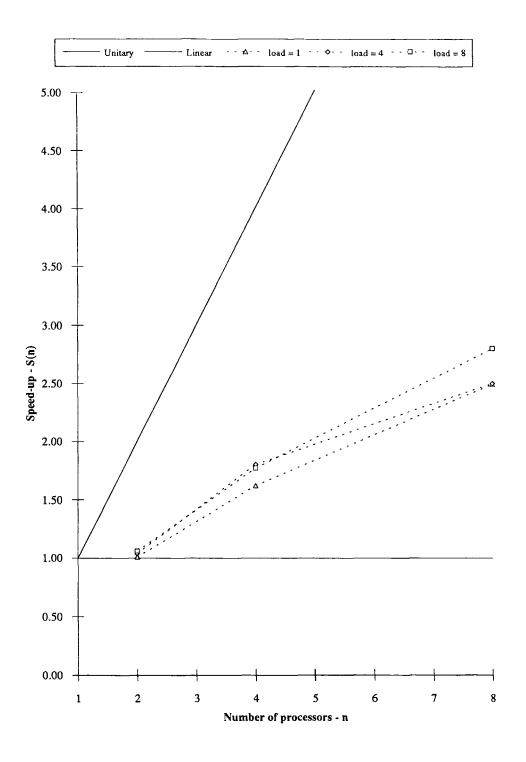

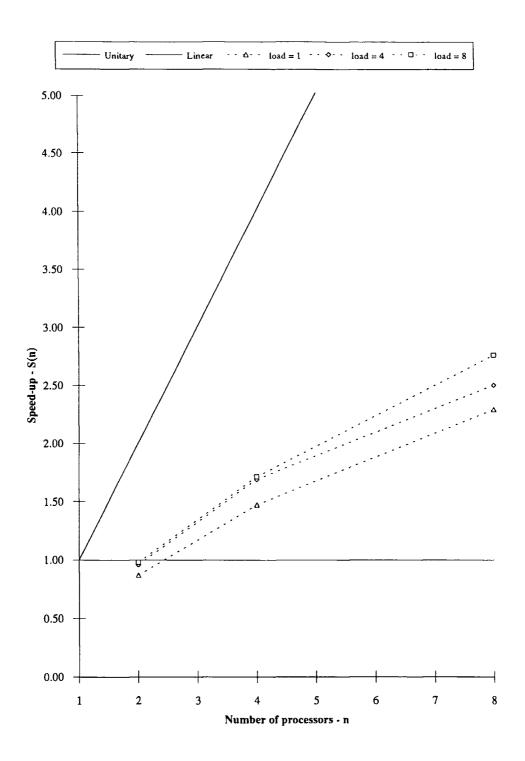

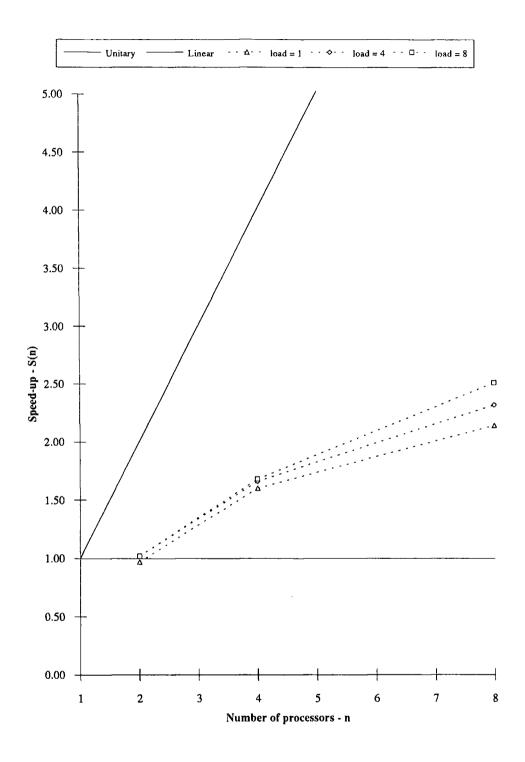

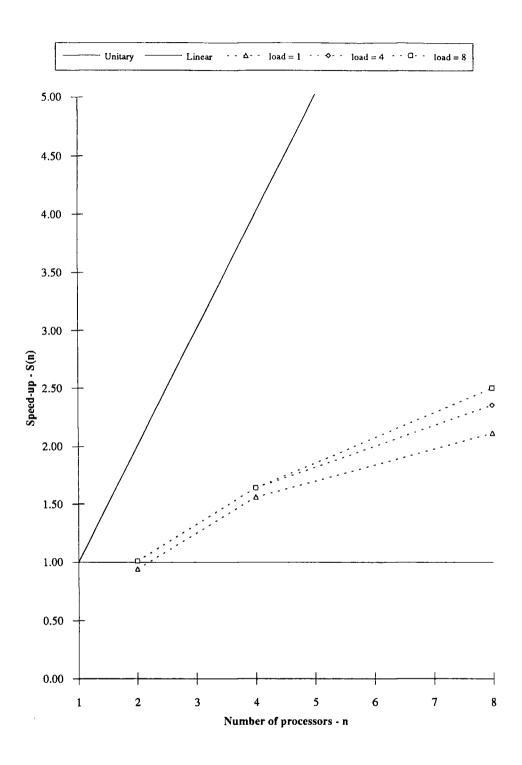

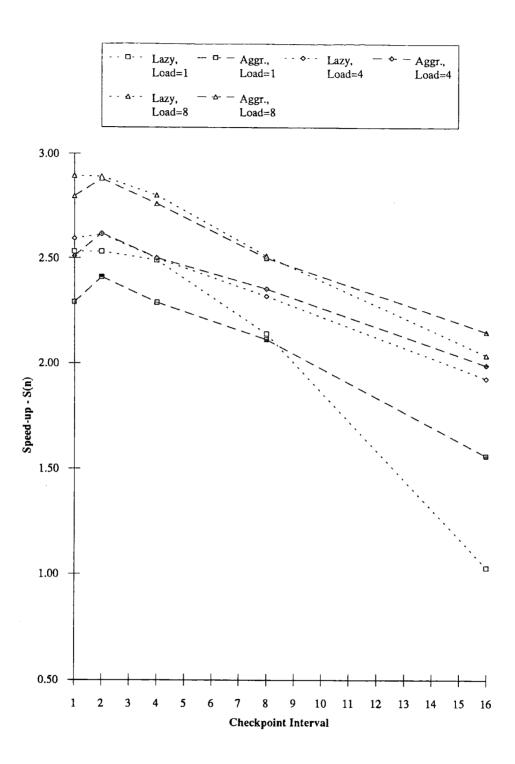

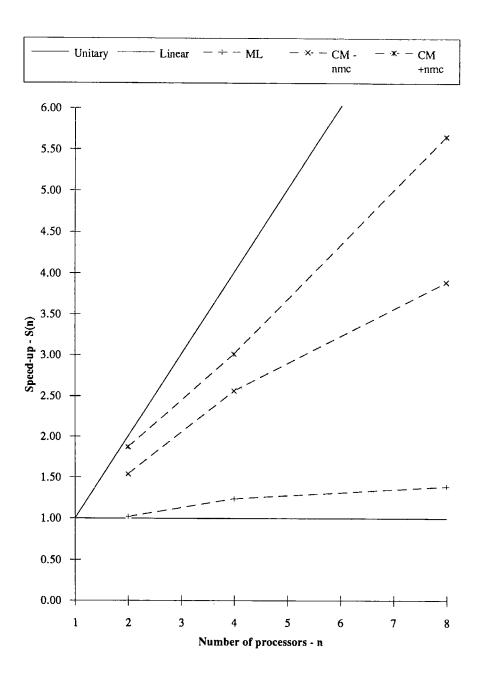

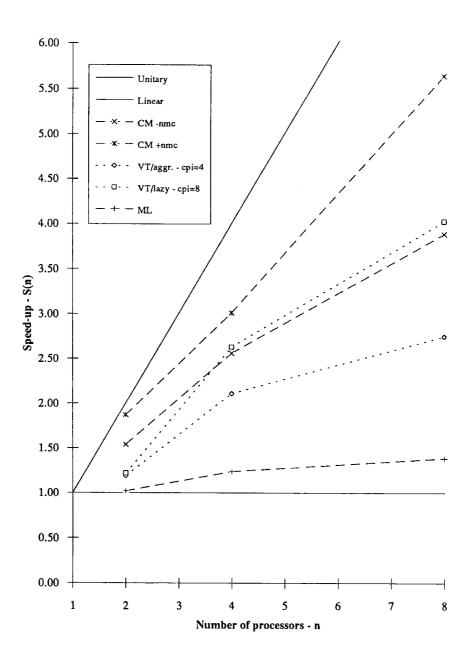

| 5.19 | Comparison of synchronization mechanisms for a load of one customer per       |     |

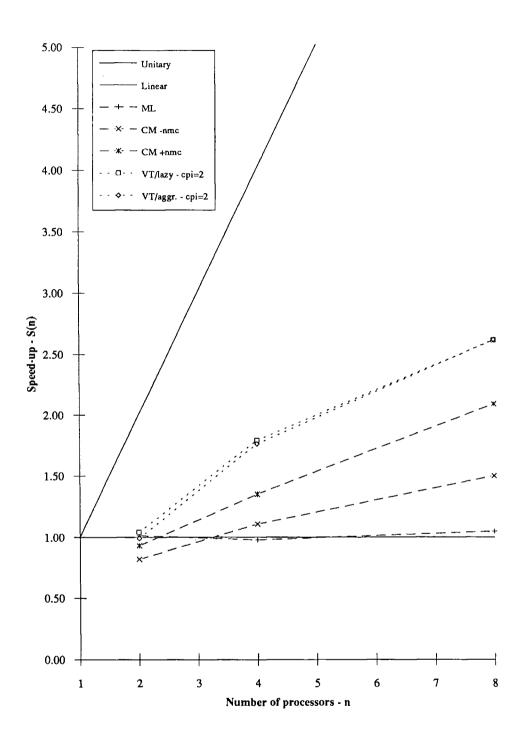

|      | queue for the hypercube of queues                                             | 120 |

| 5.20 | Comparison of synchronization mechanisms for a load of four customers per     |     |

|      | queue for the hypercube of queues                                             | 121 |

| 5.21 | Comparison of synchronization mechanisms for a load of eight customers per    |     |

|      | queue for the hypercube of queues                                             | 122 |

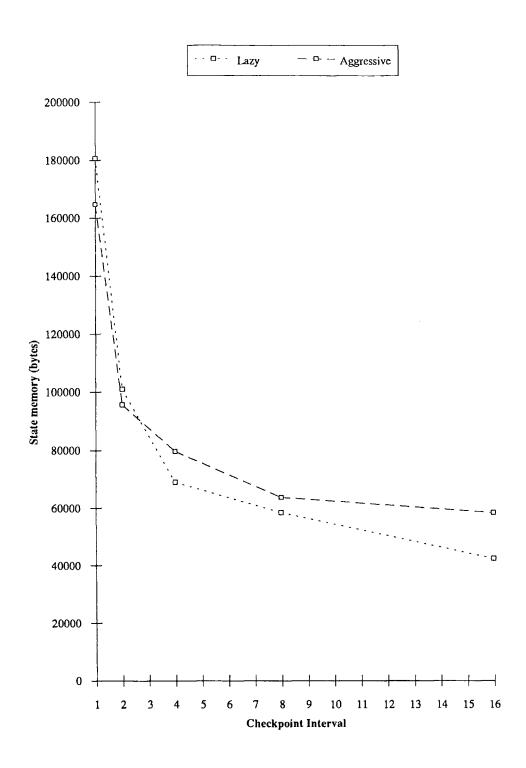

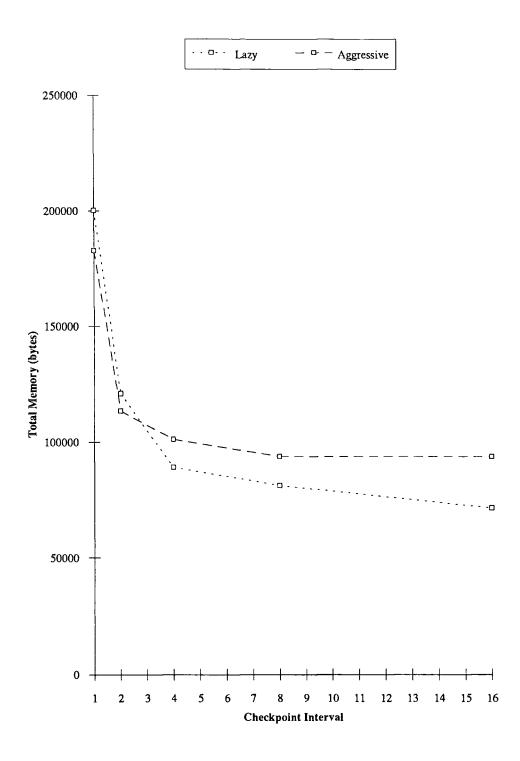

| 5.22 | State memory usage for virtual time synchronization (VT) on eight processors  |     |

|      | at a load of four customers per queue for the hypercube of queues             | 123 |

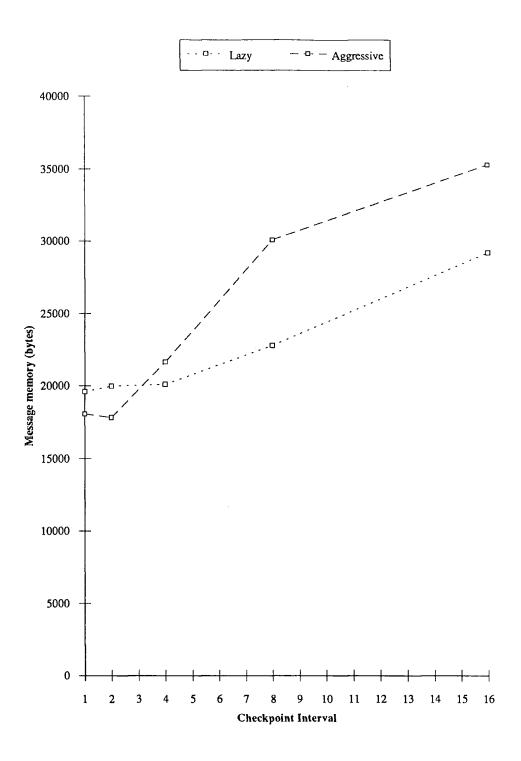

| 5.23 | Message memory usage for virtual time synchronization (VT) on eight pro-      |     |

|      | cessors at a load of four customers per queue for the hypercube of queues     | 124 |

| 5.24 | Total memory usage for virtual time synchronization (VT) on eight processors  |     |

|      | at a load of four customers per queue for the hypercube of queues             | 125 |

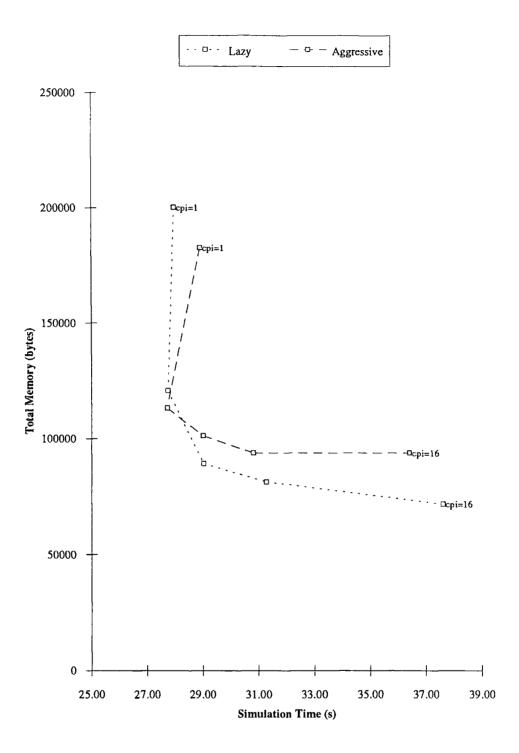

| 5.25 | Total memory usage against simulation time for a CPI of 1, 2, 4, 8 and 16     |     |

|      | using virtual time synchronization (VT) on eight processors at a load of four |     |

|      | customers per queue for the hypercube of queues                               | 126 |

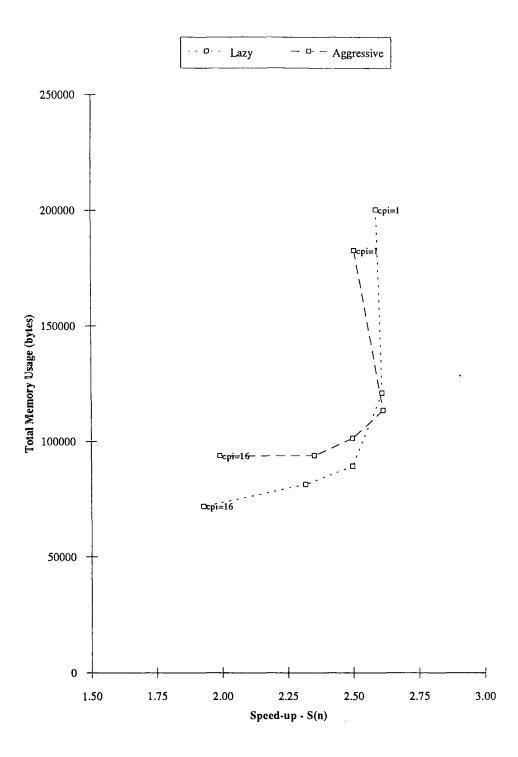

| 5.26 | Total memory usage against speed-up for a CPI of 1, 2, 4, 8 and 16 us-        |     |

|      | ing virtual time synchronization (VT) on eight processors at a load of four   |     |

|      | customers per queue for the hypercube of queues                               | 127 |

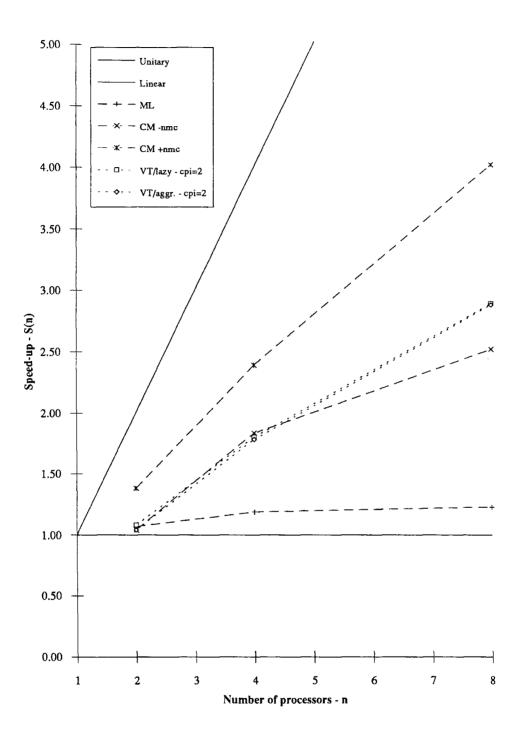

| 5.27 | Speed-up comparison of conservative synchronization methods for the tan-      |     |

|      | dem queueing network                                                          | 128 |

| 5.28 | Speed-up using virtual time synchronization (VT) with lazy cancellation for   |     |

|      | the tandem queueing network                                                   | 129 |

| 5.29 | Speed-up using virtual time synchronization (VT) with aggressive cancella-    |     |

|      | tion for the tandem queueing network                                          | 130 |

| 5.30 | Speed-up against CPI for virtual time synchronization (VT) with two pro-      |     |

|      | cessors for the tandem queueing network                                       | 131 |

| 5.31 | Speed-up against CPI for virtual time synchronization (VT) with four pro-     |     |

|      | cessors for the tandem queueing network                                       | 132 |

| 5.32 | Speed-up against CPI for virtual time synchronization (VT) with eight pro-             |     |

|------|----------------------------------------------------------------------------------------|-----|

|      | cessors for the tandem queueing network                                                | 133 |

| 5.33 | $Speed-up\ comparison\ of\ all\ synchronization\ mechanisms\ for\ the\ tandem\ queue-$ |     |

|      | ing network                                                                            | 134 |

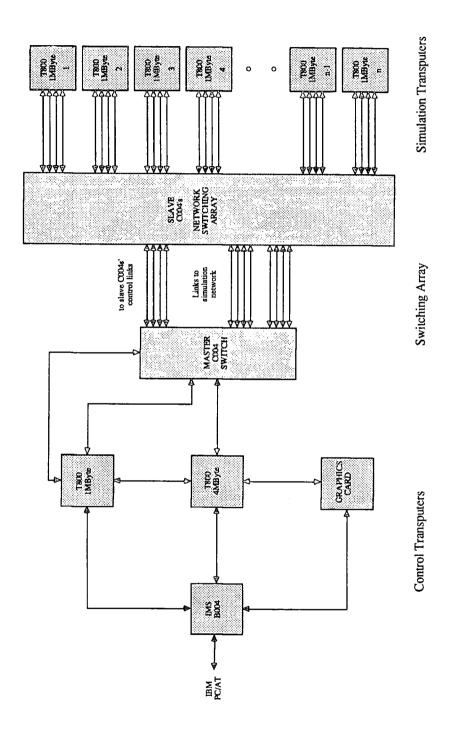

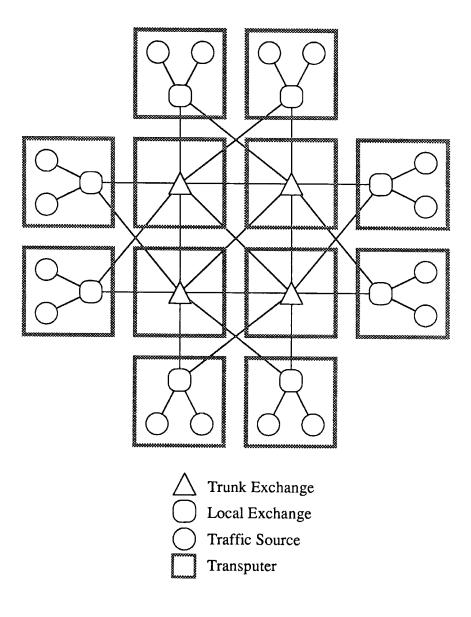

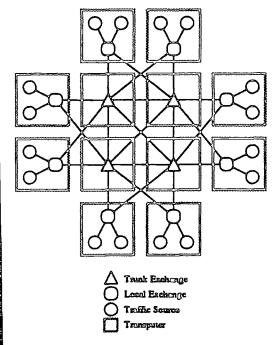

| 6.1  | ${\it High-speed transputer-based telecommunication network simulator hard-}$          |     |

|      | ware configuration                                                                     | 149 |

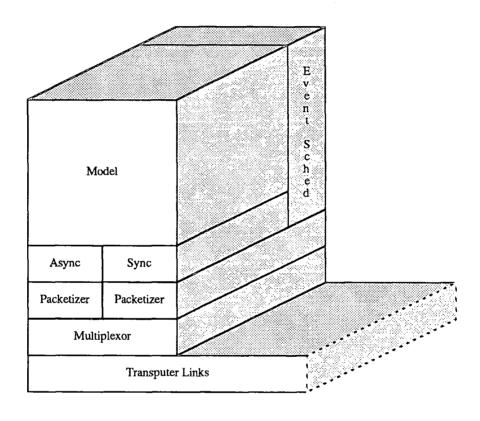

| 6.2  | The overall hierarchy of the simulation model. The Event scheduler is a                |     |

|      | control-plane for all of the upper layers                                              | 150 |

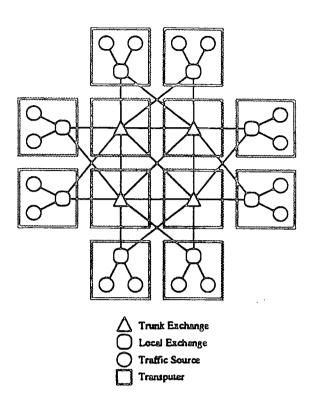

| 6.3  | Basic network topology used for the simulator performance analysis runs.               |     |

|      | The processor assignments are also shown                                               | 151 |

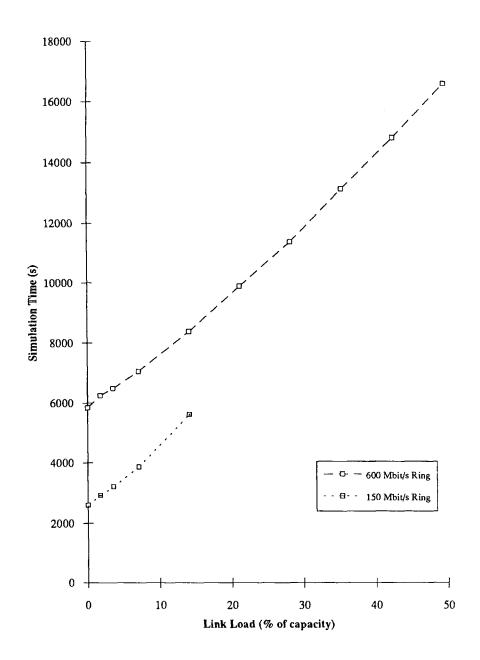

| 6.4  | Parallel simulation run times as a function of traffic load for the twelve-node        |     |

|      | networks on twelve transputers. The 150 Mbits/s times are scaled to take               |     |

|      | account of the difference in simulation length                                         | 152 |

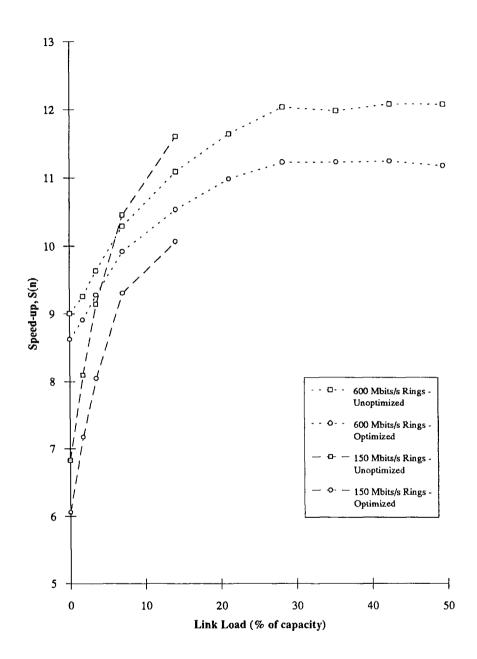

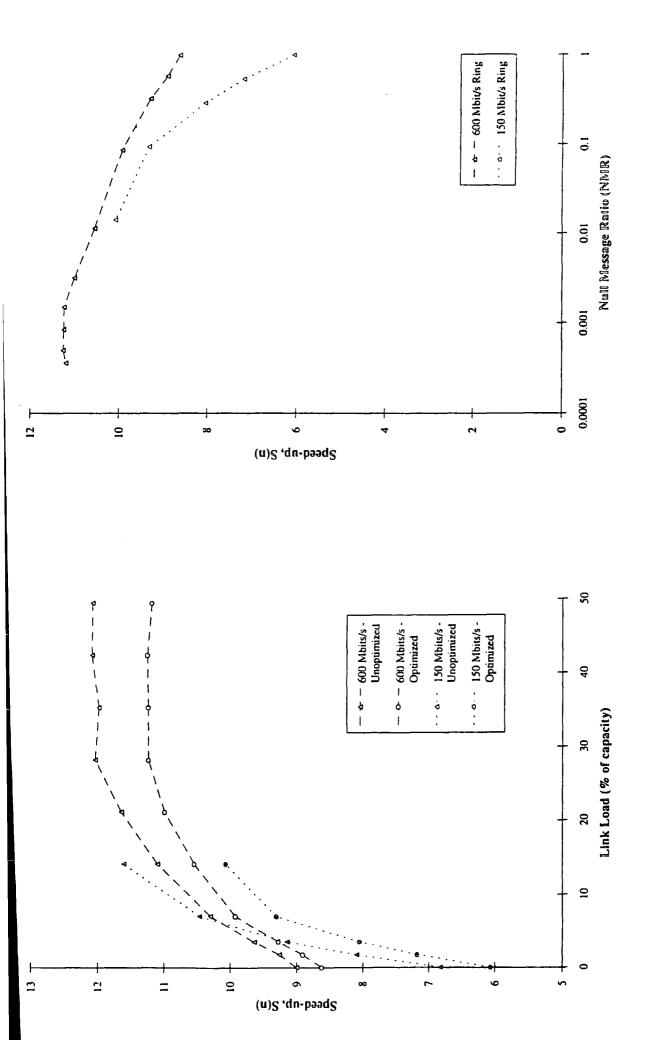

| 6.5  | Speed-up curves as a function of traffic load. Speed-up is calculated relative         |     |

|      | to the optimized or unoptimized uniprocessor simulations                               | 153 |

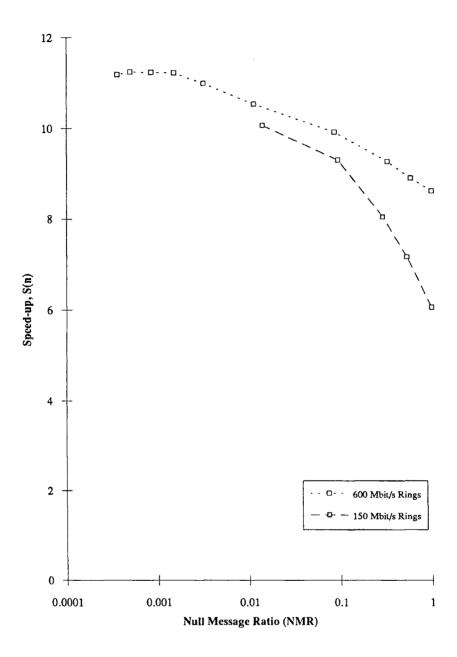

| 6.6  | Speed-up (optimized) as a function of NULL-message ratio. The difference               |     |

|      | between the two curves represents the extra parallelism that can be extracted          |     |

|      | from the higher speed rings                                                            | 154 |

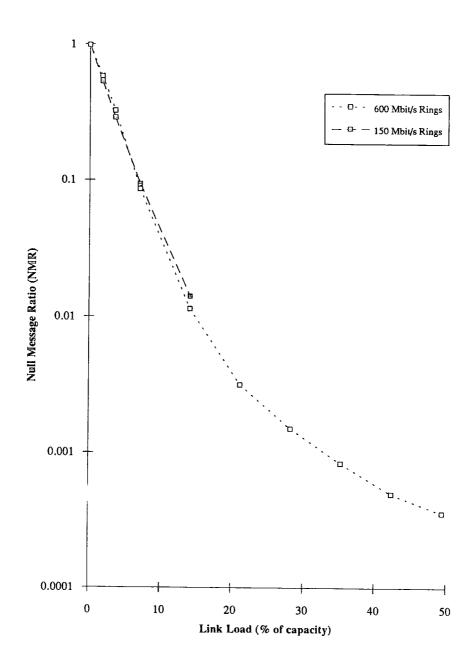

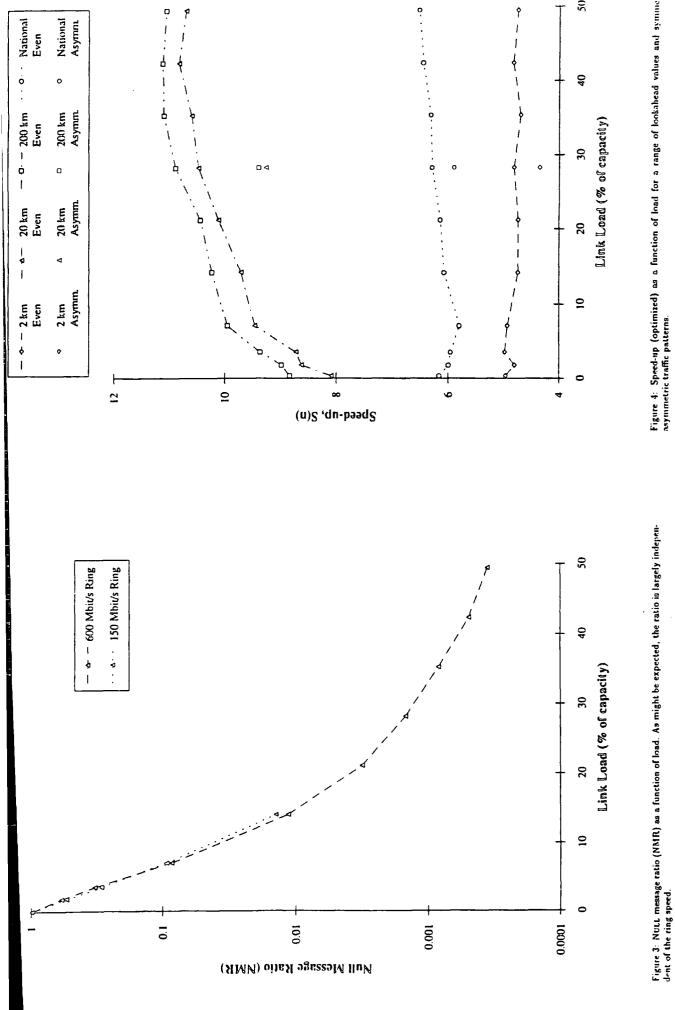

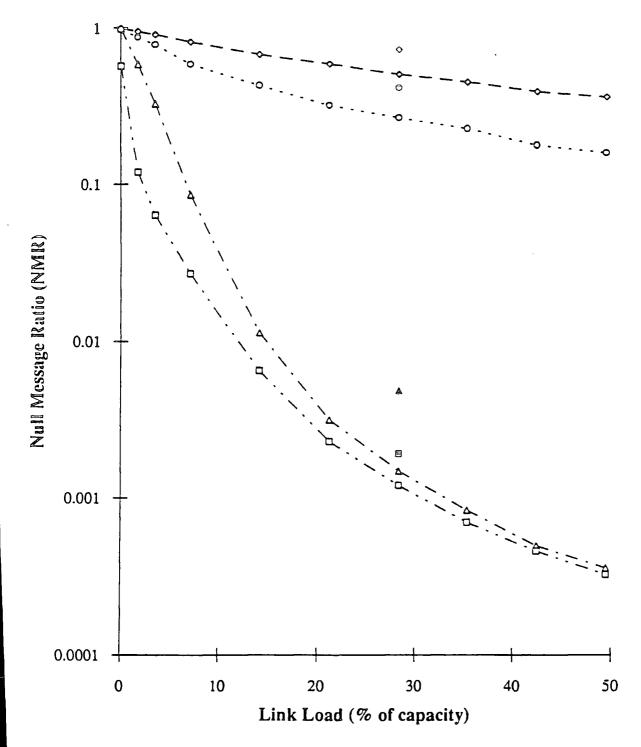

| 6.7  | Null-message ratio (NMR) as a function of load. As might be expected, the              |     |

|      | ratio is largely independent of the ring speed                                         | 155 |

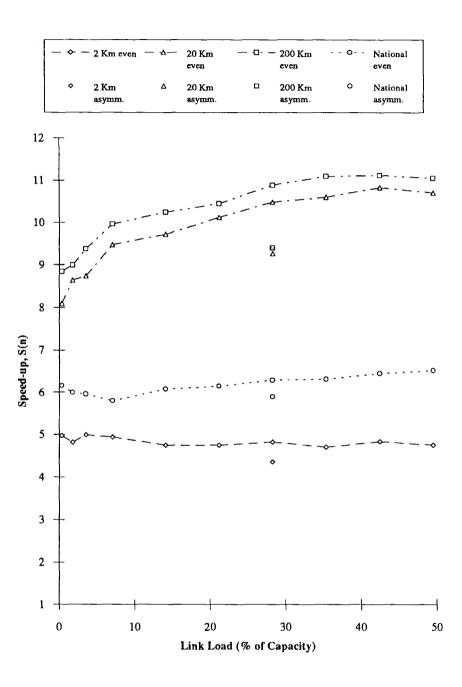

| 6.8  | Speed-up (optimized) as a function of load for a range of lookahead values             |     |

|      | and symmetric and asymmetric traffic patterns                                          | 156 |

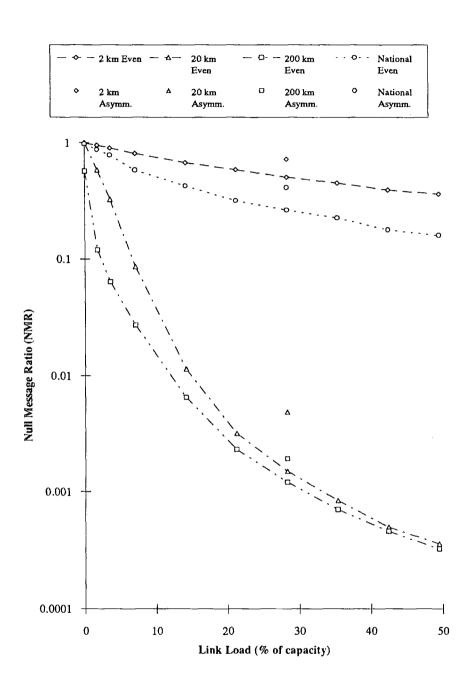

| 6.9  | Null-message ratio (NMR) as a function of load for a range of lookahead                |     |

|      | values and symmetric and asymmetric traffic patterns                                   | 157 |

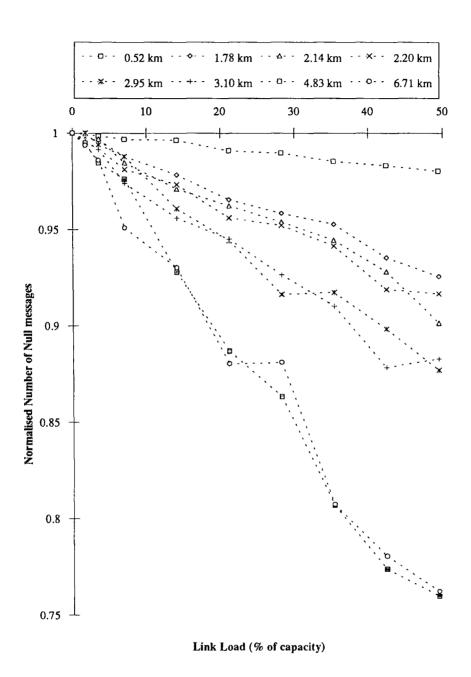

| 6.10 | Number of NULL-messages normalised against the number at the lowest load               |     |

|      | (0.05 calls/source/s) plotted against link load for a selection of source-switch       |     |

|      | links                                                                                  | 158 |

## List of Abbreviations

ATM

Asynchronous Transfer Mode

**B-ISDN**

Broadband Integrated Services Digital Network

CM

Chandy-Misra

CMB

Chandy-Misra-Bryant

CPI

Checkpoint Interval

**FCFS**

First-Come-First-Served

GVT

Global Virtual Time

**IBM**

International Business Machines

**ISDN**

Integrated Services Digital Network

I/O

Input and Output

LAN

Local Area Network

LVT

Local Virtual Time

$\mathbf{LP}$

Logical Process

MIMD

Multiple Instruction stream Multiple Data stream

MISD

Multiple Instruction stream Single Data stream

MMT

Minimum Message Time

MVT

Minimum Virtual Time

NMC

NULL-Message Cancellation

NMR

NULL-Message Ratio

**PDES**

Parallel Discrete Event Simulation

PP

Physical Process

RR

Round-Robin

SIMD

Single Instruction stream Multiple Data stream

SISD

Single Instruction stream Single Data stream

VT

Virtual Time

WAN

Wide Area Network

YADDES

Yet Another Distributed Discrete Event Simulator

## Chapter 1

## Introduction

### 1.1 Performance Evaluation

and complexity. As a direct result of this evolution, a large number of computer aided engineering techniques have been developed to help the engineer in the design, development and management of these networks. One of the main issues at stake, particularly in the design stage, is that of performance evaluation.

So that we can understand the aims and objectives of performance evaluation, we must first examine the structure of the telecommunication network itself. Its basic function is to transmit information through a common transmission facility. The network consists of switching nodes, multiplexers and demultiplexers connected by various transmission media. Network users generate messages which must be transmitted from sources to destinations within the network. The network itself will also generate its own internal signalling messages to control network operation. The engineer must therefore consider several issues; message formats, multiplexing and demultiplexing techniques, switching techniques, storage, error control, routing strategies, flow control, network operation, management functions: to name but a few. The method used to resolve each of these issues will have some impact on the overall network performance.

The performance measures of interest to the engineer will depend on the type of network under study, its application, and whether the network uses circuit- or packet-switching. For a circuit-switched network the important performance measures are the probability of blocked calls and the associated grade of service. For a packet-switched network, through-

put, average message delay, link utilisation and buffer use statistics are more useful. Evaluating network architectures with respect to such performance measures is the job of the performance engineer.

There are three general approaches that can be used to obtain estimates of such performance measures. We can perform measurements on a *real* system; we can use analytical techniques in order to calculate performance estimates from a mathematical model; or we can use computer simulation techniques.

The most direct approach is obviously to measure the performance of an existing network. This is usually difficult due to the size, complexity and accessibility of such networks. Access can be difficult as the systems are in constant use and to build a duplicate system just for performance evaluation purposes is often prohibitive. However, small model systems are still often built, particularly to aid the design and development stage of a new system. Such a system is often termed a testbed or system emulation. If experimentation is required on an existing network, it may be economically impracticable or even dangerous to suspend the normal operation of the network in order to perform experiments. Nevertheless some measurements are always required from existing networks in order to validate performance estimates obtained by other means. Indeed, there is a growing trend to incorporate measurement and monitoring tools as an integral part of the network management software. The data from such tools can be used to feed capacity planning tools to answer "what-if" type questions about changes to the network capacity and architecture. BEST/1-SNA is such a capacity planning tool for IBM SNA (System Network Architecture) networks which uses measurement data [1].

Another method of obtaining performance estimates is to use mathematical analysis. Analytic models generally require a high degree of abstraction in order to ensure that the model is tractable. This means that the development of an analytic model which accurately reflects the network under study is difficult and requires considerable effort and skill. Analytic models have great difficulty with transient conditions, such as traffic fluctuations or component failures, as these are difficult to express mathematically. Also, in making the model tractable, a model may be distorted due to the omission or approximation of system characteristics which are difficult to solve analytically. However, once the model is developed, its solution is generally very fast.

<sup>&</sup>lt;sup>1</sup>The word model is used here in the sense of a small imitation of the real thing.

Simulation techniques allow a network to be modelled at an arbitrary level of detail. This means that less abstraction is required and also the process of model construction can be more straightforward. In practice, however, the more secondary detail that can be abstracted out the faster the simulation will be. Generally speaking, the execution of a simulation model will use substantially more computing time than an analytical model. However, in many cases simulation is the only option as an analytic model is inaccurate, intractable or unavailable. There are interesting statistics concerning the use of RESQ [2], the research queueing package developed at the IBM Thomas J. Watson Research Centre. This package allows the user to develop simulation models of communication systems using either analytic or simulation models based on queueing networks and it was found that over 99% of all the models developed used simulation [3].

These three approaches to network performance evaluation should be used in a complementary manner in order to validate results and obtain the fastest results to the required accuracy. Reviews of simulation approaches can be found in Frost et. al. [4] and in Kurose and Mouftah [3].

## 1.2 Simulation Objectives

The simulation of a telecommunication network may have one or more objectives: understanding the behaviour of a system, obtaining estimates of average or worst/best case performance parameters, guiding the selection of design parameters and/or operating strategies and verifying the simulation results against measurements taken from a real system.

The simulation objective can have a profound impact on how the simulation should be designed and how it should be run. If we are only interested in understanding the behaviour of the system, then we would perhaps like an animated graphical output presentation, adjustable simulation speed and system parameters: all of this controlled via a good user interface. If we are interested in obtaining estimates of performance parameters then we need the simulation to give us results to the required accuracy with confidence intervals as fast as possible. For the selection of design parameters, the simulation becomes part of an optimization loop. Thus the simulation needs to be interactive and fast with controllable accuracy. The information obtained from the simulation can consist of a number of estimates of a performance measure corresponding to the random variation of particular parameters. The information is then used to calculate gradient estimates to predict how to optimize

design parameters. If we are fitting a simulation model to measurements taken from a real system a number of simulations will have to be performed with different parameter settings that correspond to the measured result conditions. In this case the statistical properties of the results are very important so as to be able to predict the accuracy of the simulated results.

It is well established that simulations of telecommunication networks are generally slow to develop and slow to run. As we have already mentioned, the telecommunication networks we are interested in simulating are large and complex consisting of a great variety of component parts. This means that our simulation models will reflect this. Existing networks are also constantly changing with time as new equipment is installed, old equipment is replaced and software up-graded. Thus the simulation model of an existing system must keep pace with the current and predicted changes. Networks always seem to grow and never shrink, so ever larger simulations are required. A frustrating re-occurrent factor for the performance engineer is that when larger computing resources become available the network which needs to be simulated has also grown.

Simulations are also slow for statistical reasons as, for any result to be statistically significant (ie. to a given accuracy), a sufficient run length, or a number of runs, has to be performed. The generation of events by a simulation program is usually driven by an input stream of pseudo-random numbers. These are used to generate lengths of time, lengths of messages, probabilities etc. As the event generation depends on random numbers then the performance measures output by the simulation model are themselves stochastic in nature. Therefore a simulation represents a statistical experiment and the results should be subjected to careful statistical analysis.

In some cases we may be interested in the behaviour of a system as it progresses from some initial condition. This is known as the transient response. This usually lasts for a well-defined period of (simulated) time. If we are interested in long term average results (steady state), the transient response must be detected and discarded, or the simulation must be run for long enough so that the effects of the initial conditions are negligible. The problem of identifying the transient phase of a simulation is addressed by Schruben [5], Welch [6] and Heidelberger and Welch [7].

If steady state average results of performance measures are required then we find that every time we run the simulation with different random number streams we get variations in our results. If we were to run a simulation ten times and get results within one per cent (say) then we may be confident of our result. If the variation were much greater, then our confidence would be less. The generation of confidence intervals based on the variance of the performance measure over the simulation(s) is therefore very important. These can be generated by dividing up a single long simulation, without the transient period, into n equal length time periods and constructing the confidence interval from values of the performance measure in each interval. Otherwise we can do n separate simulation runs with different random input streams, again without the transient period. How large n should be is a difficult but crucial problem, as also is the length of the time periods. These problems are dealt with by Welch [6] and by Law [8].

For the single run case, if n is too small the samples will be correlated, if n is too large, excessive simulation time will be used. Nevertheless, the single run case has the advantage of only having to discard a single transient period. Also, the longer the simulation, the smaller the variance in the result will be. Where to stop is very much governed by the law of diminishing returns.

Apart from the two more obvious methods described above, there are other methods of obtaining confidence intervals from simulation results. The regenerative method is also based on partitioning a single simulation into independent runs which have the same regeneration state. This is a state such that the future progress of the simulation is statistically the same each time the state is entered. The problem is in recognising a regeneration state for the particular system of interest. This method is described by Crane and Lemoine [9]. A fourth method, known as the spectral method which also uses a single run, takes into account the correlation between data gathered by the simulation in successive time periods. This is described by Heidelberger [10].

Reviews of simulation objectives and their impact on simulation studies have been written by Kurose [3] and Righter and Walrand [11].

## 1.3 Simulation Speed-up

So far we have discussed reasons for the complexity, size and slowness of telecommunication network simulations; we now need to consider methods of speeding them up. Simulation run times can be reduced by three methods which may also be used together. The use of parallel multiprocessor systems, the integration of analytical models into the simulation where possible (as their solution is faster) known as hybrid simulation, and the use of

statistical methods known as variance reduction techniques.

In parallel simulation, the ultimate goal is to obtain a simulator that runs as quickly as possible; if the speed of the parallel simulator is less than that of a conventional simulator then there is no reason for using it (and many good reasons for not doing so). However, it is normally impossible to compare parallel and sequential simulators directly since the two are written in an entirely different manner and the programmer rarely wants to write both. Simulation speed-up is defined as the time it takes a single processor system to perform a simulation divided by the time it takes a multiprocessor system to perform the same simulation. This definition is incomplete however, as we have to specify what we mean by performing the simulation on a single or a multiprocessor system. We might think that a safe definition would be to specify the use of the same type of processor for the single and multiprocessor systems. However, memory requirements would dictate that the single processor system would need a much larger memory than any individual processor in the multiprocessor system: we must therefore allow for this. Another method of estimating speed-up is to measure the total busy time of each processor during the parallel simulation. This would give a greater speed-up measure than is actually available in distributing the simulation over multiple processors.

A good indication of the possible behaviour of the conventional simulator can sometimes be obtained by running a version of the parallel simulator optimized to run on a uniprocessor. The time taken for the uniprocessor version can be compared with that of the multiprocessor version. The *speed-up* of the simulator is then the ratio of the time for the multiprocessor version to that for the uniprocessor. Most processors will perform badly though due to the overhead of multiple task scheduling necessary.

The speed-up should normally lie in the range between one and n when the multiprocessor version is run on n processors. A speed-up of n is said to be unitary, and the success of the parallel simulator is measured by how close we can approach to unitary speed-up. A speed-up of less than one, sub-linear, would indicate that the uniprocessor simulation is faster; which is clearly unacceptable.

Helmbold and McDowell [12] have defined a family of useful qualitative terms for speed-up (see table 1.1) which includes terms for speed-up greater than n. Super-linear speed-up, where the measured speed-up grows without bound as the number of processors is increased, has not been observed practically, or even predicted theoretically, for any real application. Linear super-unitary speed-up however, has been observed; but not for parallel

simulation [12]. Such super-unitary applications are characterised by one of two factors. Firstly, the sequential algorithm used by the uniprocessor version may be constrained to an inferior method compared with that of the parallel algorithm. Thus, when the uniprocessor version uses the "same" algorithm as the multiprocessor, the super-unitary speed-up becomes unattainable. Secondly, the problem may be NP-complete<sup>2</sup> and the best known algorithm is some form of randomized search whose run time is highly dependent on the initial search point. When the search is done in parallel with multiple initial search points the expected run time will drop rapidly as the number of processors is increased.

| Term                 | Speed-up, $S(n)$                          |

|----------------------|-------------------------------------------|

| sub-linear           | $\lim_{n\to\infty} S(n)/n = 0$            |

| linear sub-unitary   | $0 < \lim_{n \to \infty} S(n)/n < 1$      |

| unitary              | $\lim_{n\to\infty} S(n)/n = 1$            |

| linear super-unitary | $1 < \lim_{n \to \infty} S(n)/n < \infty$ |

| super-linear         | $\lim_{n\to\infty} S(n)/n = \infty$       |

Table 1.1: Qualitative terms for speed-up figures.

A practical argument against using parallel simulation is the well-known difficulty of debugging parallel programs. In some cases this is tackled by debugging a sequential version of the parallel program on a single processor using standard debugging tools. For instance, this technique can be used on a program before using a parallelizing compiler which produces parallel code automatically from a sequential program (see chapters 2 and 4). Certain microprocessors used in parallel multiprocessor machines, such as the Inmos transputer, can effectively support the running of an actual parallel program on a single processor (given sufficient memory) by task switching. The debugging process is then one step closer to true parallel debugging. In practice, the problem of debugging a parallel program whilst running on a multiprocessor can only be addressed by either writing a specialised parallel debugging tool for the particular multiprocessor, or, by embedding large amounts of tracing code within the program which prints out information on all the relevant details of the programs progress. Such detailed tracing will obviously affect the programs run time performance and will only be required during development and actual debugging. Therefore it is usually configured so that it can be switched on (or off) at run time or, preferably, at compile time. Indeed, this is the technique used by three parallel simulation tools<sup>3</sup> discussed in

<sup>&</sup>lt;sup>2</sup>Non-deterministic Polynomial or NP-complete problems are not solvable in polynomial time by any known deterministic algorithm and the only guarantee of a globally optimum solution is by exhaustive search

<sup>&</sup>lt;sup>3</sup>YADDES (Yet Another Distributed Discrete Event Simulator) described in chapter 5, TWOS (the Time

later chapters.

In hybrid simulation, a simulation model is combined in some way with an analytical model. As the solution of analytical models is generally much faster than that of simulation models we will get a net speed-up. Hybrid simulation can be approached by decomposition of the simulation model or by replacing the simulation model with an analytic model, known as conditional expectation. The simulation model can be decomposed into sub-models, often in a hierarchical manner, and those parts which have known analytical models are solved analytically. A little intelligence is also usually applied to the decision of which simulation sub-models to replace by considering which sub-models have most bearing on the performance measure(s) of interest. Those sub-models requiring modelling in greater depth, or to a greater accuracy, are not replaced. Conditional expectation is useful when an analytic model of a complete system is available but when the vital parameters are not known but can be simulated. In this case the simulation model feeds the analytic model in a subordinate manner.

The speed-up obtained by using hybrid simulation techniques is offset somewhat by its disadvantages. The application of these techniques is highly dependent on the model. If analytic models are not known for a given situation then a significant amount of expert knowledge will be required in order to explore whether one is possible and to generate it if it is. In moving to analytic models there is also a consequent loss of the detail compared with that in the simulation model. This may, or may not, be significant; again expert knowledge is required to assess this. The loss of detail can also mean that the variance of the results obtained from a hybrid simulation is significantly increased. For instance, each simulated traffic source in a packet-switched network model may be replaced by a simple random number generator and an appropriately chosen shaping distribution. Thus, some accuracy is lost in return for faster model execution.

Hybrid simulation is a subject in its own right, but does not depend on the use of parallel or distributed architectures, though it may be used in such an environment. General discussions of hybrid simulation have been written by Shanthikumar and Sargent [13], Frost et. al. [4].

Variance reduction techniques exploit the statistical nature of simulation models to reduce the variance, or uncertainty, in the output results. Thus, for a given length of

Warp Operating System) described in chapter 3 and the University of Durham ATM simulator described in Chapter 6.

simulation run-time a more accurate result is obtained, or, for a given accuracy a shorter simulation run is possible. This is usually described as statistical speed-up. There are many well known techniques that fall into the category of variance reduction techniques such as, antithetic sampling, common random number streams, control variates, importance sampling and stratified sampling. These techniques have been studied extensively and are well documented but have not often been used in real simulation applications. This may be due to ignorance or, more possibly, to the added complication of their use. Also, most experiments using variance reduction techniques have reported only modest speed-ups. An excellent survey of variance reduction techniques has been written recently by McGeoch [14].

Statistical speed-up can be exploited in multiple processor systems. In this case, we define speed-up as the time taken for a single processor to obtain the estimated performance measure(s) of interest to a given accuracy divided by the time taken for the multiple processor system to obtain the same estimate to the same accuracy. We can now consider using n processors to do n short simulation runs instead of one long one on a single processor. Heidelberger [15] discusses these statistical speed-up issues. His, and other work in the area, will be discussed in chapter 2.

#### 1.3.1 Amdahl's Law

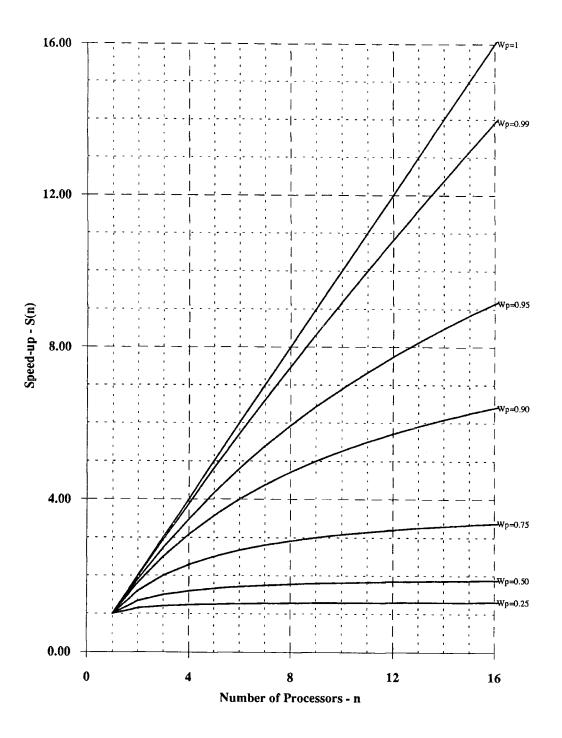

The speed-up, S(n), of a multiprocessor with n processors is defined to be the ratio of the total execution time on a uniprocessor to the total execution time on the multiprocessor. Let us first define a simple model for the execution of a parallel program on a multiprocessor. We define the total number of operations performed by the complete program as W. Various types of operation are involved, so we define  $W_i$  as the number of times that operations of type i are performed. Each operation has a cost in processor time, so we can define  $C_i(n)$  as the time taken by all the processors to perform one operation of type i on an n processor system. Let  $W_s$  represent the number of sequential operations and  $C_s(n)$  the cost of performing a single sequential operation on an n processor system. Likewise, let  $W_p$  and  $C_p(n)$  be the amount and cost of work which exhibits n-fold parallelism. Therefore, speed-up is defined as;

$$S(n) = \frac{W_s C_s(1) + W_p C_p(1)}{\frac{W_s C_s(n)}{n} + \frac{W_p C_p(n)}{n}}$$

(1.1)

If we define the cost of one sequential operation to be one unit of processor time, then

$C_s(1) = 1$ . Also we can assume that when performing a single sequential operation on an n processor system, one processor is working and the other n-1 are idle; hence  $C_s(n) = nC_s(1) = n$ . Further, if we assume that the cost of one operation is the same for sequential and parallel operation,  $C_p(1) = 1$  and  $C_p(n) = 1$ , then equation (1.1) reduces to Amdahl's law [16].

$$S(n) = \frac{W_s + W_p}{W_s + \frac{W_p}{n}} \tag{1.2}$$

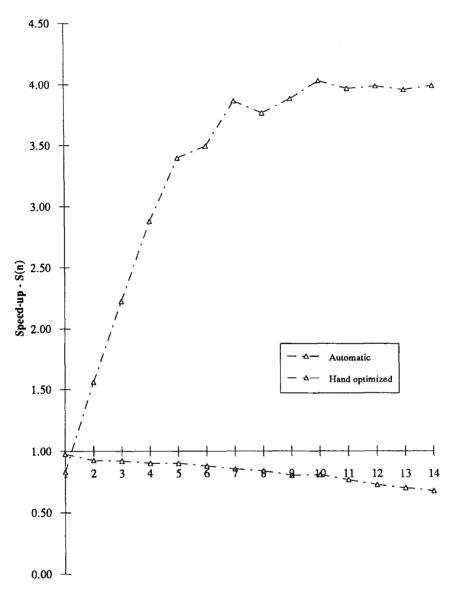

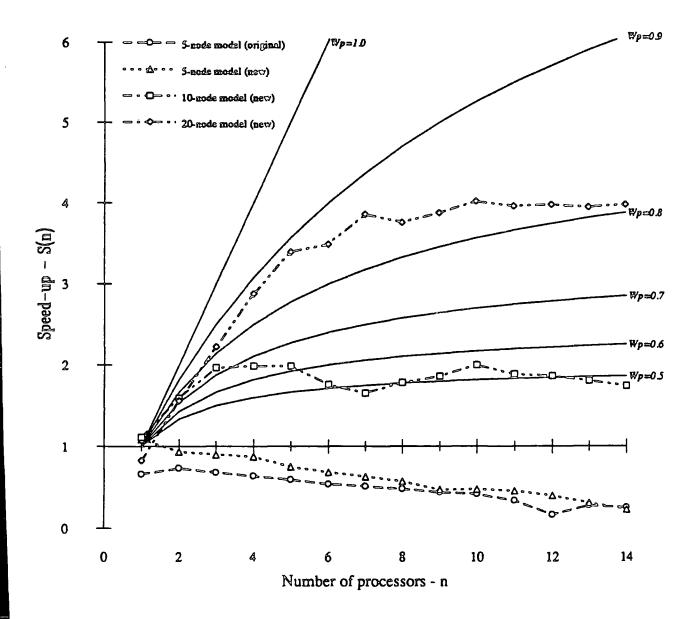

Amdahl's law for various values of  $W_p$ , where  $W_p$  and  $W_s$  are expressed as a fraction of the total number of operations (ie.  $W_p + W_s = 1$ ), is shown graphically in figure 1.1. Comparing this with our qualitative terms for speed-up in table 1.1, we can see that the curve for  $W_p = 1$  is effectively the unitary speed-up curve. Above this, is the region of super-unitary speed-up and below it, sub-unitary. Also, notice that for any  $W_p > 0$ , the speed-up is never sub-linear.

Amdahl's law also leads to a theoretical upper-bound for speed-up for this model of;

$$\lim_{n \to \infty} S(n) = \frac{W_s + W_p}{W_s} = \frac{1}{1 - W_p}$$

(1.3)

These can be observed in figure 1.1 (particularly for values of  $W_p \leq 0.95$ ) as the curves move asymptotically to the upper bounds given in table 1.2.

| $W_p$ | $Speed$ - $up$ - $S(\infty)$ |

|-------|------------------------------|

| 0.25  | 1.33                         |

| 0.50  | 2                            |

| 0.75  | 4                            |

| 0.90  | 10                           |

| 0.95  | 20                           |

| 0.99  | 100                          |

Table 1.2: Upper bounds on speed-up predicted by Amdahl's law

There are several consequences of Amdahl's law and the predicted upper bounds. First of all, this model does not take any account of any overheads. In the case of a shared memory multiprocessor, for instance, there will be overheads in synchronization, communication and memory reference overheads due to local cache misses. Also, whatever the architecture of the multiprocessor, there is invariably a small period of time at the beginning and end of any program which is unavoidably sequential; even if it only consists of reading code and data files from mass storage, downloading them to each processor and writing the final

results back. These two factors on their own mean that the curves in figure 1.1 and the "upper bounds" in table 1.2 are in reality upper bounds on the speed-up we can expect to achieve. Other, more practical, limits on the speed-up achievable are the number of processors available and the number of processes into which we can decompose the problem; in this case the simulation model. It may often be possible to decompose a model into more processes (ostensibly to exploit more parallelism) but this may result in greater overheads in communication between processes/processors, synchronization and load balancing problems. Such problems are addressed in chapters 2 and 3.

### 1.4 Parallel Hardware Architectures

The last decade has seen the advent of a huge variety of new computer architectures for parallel processing. This variety can be bewildering to the non-specialist in computer architecture who needs to know which architecture is the most suitable for his application. In order to make an informed choice we need to be able to classify the different types of architecture which are available and which are possible. This is usually addressed by a taxonomy. A taxonomy is a classification scheme based on the salient features of the things being classified: in this case the things are parallel computers and the salient feature is the type of parallelism employed. In any computer system design the parallelism can be achieved at various levels. These are defined as the task level, process level, instruction level and arithmetic or bit level.

The task level is the highest level at which parallelism can occur. It occurs in multiprogrammed systems where multiple tasks are executed concurrently using time-sharing. True parallelism occurs when we have multiple processors and each task is allocated to a separate one. A task is usually defined as a complete program, though it should be obvious that it is possible to define a task as a complete phase of a program. Thus there is an overlap with the next lower level of parallelism. Here we are clearly describing multiprocessor systems.

The process level is usually taken to mean parallel processing at the sub-program, procedure or sub-routine level. Also included are separate instances of loops and even iterations of loops, if there is no data dependency. At this level we are describing vector, array and multi-function processors. Instruction level parallelism is where individual instructions are executed in parallel. This is normally described as pipeline processing.

The final, and lowest, level is the arithmetic or bit level. A good example is the widely

used parallel adder. This level is more the domain of the integrated circuit logic designer rather than a primary topic in a discussion of parallel processing. So we will restrict ourselves to the three higher levels of parallelism.

Duncan [17] believes we should go further and "exclude architectures incorporating only low-level parallel mechanisms that have become common place features of modern computers". In this category he places instruction pipelining (for overlapping decode, fetch, execute and store operations) and co-processors (for mathematics and logic or input/output control).

There are several classification schemes available, the most popular of which is the taxonomy proposed by Flynn [18]. The problem with any formal classification scheme is that several well established architectures do not fit into them very neatly. This has led to several suggested modifications to Flynn's taxonomy and alternative approaches based on descriptive notations. The taxonomy used in this survey is that of Duncan [17]. This is an informal high-level taxonomy based on Flynn's work which distinguishes between the principle parallel computer architectures which are currently being explored.

Let us first briefly introduce Flynn's taxonomy. Flynn [18] considered the sequential (often called the von Neumann) model as a single stream of instructions controlling a single stream of data (hence SISD). One step towards parallelism can be made be adding multiple data steams (SIMD), and a second by adding multiple instruction streams (MIMD). The SIMD machine consists of a single control unit and several processors carrying out the same instructions on many different items of data. These are usually array or vector processors. The MIMD machine is a *true* multiprocessor machine with each processor executing its own instructions on its own data. The MISD machine, multiple instructions acting on the same data item, is sometimes deemed impractical, though it seems to describe a multiprocessor pipeline. The taxonomy is summarised in table 1.3 below.

|                             | Single data stream | Multiple data stream     |

|-----------------------------|--------------------|--------------------------|

| Single instruction stream   | SISD               | SIMD                     |

|                             | (von Neumann)      | (Array/Vector processor) |

| Multiple instruction stream | MISD               | MIMD                     |

|                             | (Pipeline)         | (true multiprocessor)    |

Table 1.3: Flynn's Taxonomy.

Flynn's taxonomy has the attraction of simplicity, providing a useful shorthand, but is insufficient for classifying many modern architectures of which almost all would be classed

as MIMD. Therefore many modifications to it have been suggested. Duncan summarises much of the work on extending Flynn's taxonomy in his paper [17]. He also introduces an informal high-level taxonomy, based around Flynn's taxonomy, to distinguish between principle approaches to parallel computer architectures. This is shown in figure 1.4.

| Synchronous | SIMD               | Processor array    |  |

|-------------|--------------------|--------------------|--|

|             |                    | Associative memory |  |

|             | Vector             |                    |  |

|             |                    | Systolic           |  |

| MIMD        | Distributed memory |                    |  |

|             | Shared memory      |                    |  |

|             | MIMD/SIMD          |                    |  |

| MIMD-based  | Dataflow           |                    |  |

| paradigm    | paradigm Reduction |                    |  |

|             |                    | Wavefront          |  |

Table 1.4: Duncan's Taxonomy.

Duncan begins at the highest level with three classes, Synchronous, MIMD and MIMD-based architectural paradigms. Synchronous parallel architectures co-ordinate concurrent operations in lock-step through the use of global clocks, central control units, or vector unit controllers. His MIMD class matches Flynn's MIMD class, in that multiple processors can execute independent instruction streams using local data. His MIMD-based paradigm class embraces hybrid architectures that do not comfortably fall into either Flynn's MIMD or SIMD classes. Duncan ignores SISD as he is only interested in parallel architectures. The following is a short summary of Duncan's classifications.

Vector processors are characterised by multiple, pipelined functional units which implement arithmetic and Boolean operators for both vector and scalar quantities and can operate concurrently. Thus parallel vector processing is provided by streaming many vector elements sequentially through a number of functional pipeline units in parallel. Because of the existence of the pipelines there is always a significant start-up overhead. So efficient operation is only achieved if the pipelines are continuously full. Also it has been found that the vector operand lengths need to be multiples of the vector register size (ie. the number of pipelines). If not then some of the pipelines will be idle while smaller vectors are processed and vectors which are too large will have to be processed in batches.

SIMD architectures normally consist of interconnected processors with a central control unit. The control unit broadcasts instructions to the processors which execute them in lock-step on local data. The interconnections allow communication between processors and

also between processors and local memory.

Processor array architectures are a type of SIMD architecture which are structured for numerical SIMD execution. These have been used extensively for large-scale scientific calculations such as image processing and nuclear energy modelling. The interconnection networks used have usually been nearest-neighbour meshes or crossbar approaches, though recently hypercube topologies have been explored. A variant on this architecture is the use of large numbers of 1 bit processors in processor grid arrangement. These are very much geared to image processing applications by mapping pixels to the grid processing elements.

Associative memory processor architectures are another a type of SIMD architecture based on the idea of data stored in an associative memory which can be addressed by its contents. The major advantage over random access memory (RAM) is its capability of performing parallel search and comparison operations. These facilities are frequently needed in many applications such as dynamic databases, image processing and artificial intelligence. The major disadvantage is the increased hardware cost.

Systolic architectures (arrays) are pipelined multiprocessors in which data is pulsed in a rhythmic fashion from memory through a network of processors before returning to memory. This idea was formulated to balance intensive computations with demanding input/output bandwidths. A global clock is used to synchronize the data flow through the interconnected processors. Each processor performs a specific invariant sequence of instructions on the data. A high degree of parallelism is obtained by pipelining the data through multiple processors typically arranged as two-dimensional arrays. Systolic architectures are best suited for algorithm specific applications, particularly in signal processing. Some machines have been constructed which are programmable, and so are not limited to implementing a single algorithm.

MIMD architectures, as defined by Flynn, use multiple processors to execute independent instruction streams using local data. Therefore MIMD machines are highly suited to applications that require processors to operate in a substantially autonomous manner. The software processes executing on each processor are synchronized by passing messages via an interconnection network or via shared memory. Thus there is no central control and MIMD architectures are asynchronous. They therefore support higher level parallelism at the task and process level. Another advantage is that they can be extended much more easily than SIMD machines. MIMD architectures can be further distinguished by their memory organisation.

Distributed memory MIMD architectures need the processing nodes (processor plus local memory, or cache) to be connected using some interconnection network. Nodes can then share data by explicitly passing messages through the interconnection network. Various static interconnection network topologies have been explored to support various applications, such as pipelines, meshes, trees, rings, chordal rings, cubes, hypercubes etc. Each of these are particularly suited to certain applications. For instance, a mesh topology is suited to matrix oriented algorithms, tree topologies are suited to searching and sorting algorithms. Dynamic, or reconfigurable topologies, are also possible by using a programmable switching matrix. These can be single stage, multi-stage or a crossbar. Interconnection networks are examined in detail by Feng [19], Siegel et. al. [20] and Almasi and Gottlieb [21]. A disadvantage is that the communication overhead associated with this architecture, particularly where data has to be queued and forwarded by intermediate nodes, can significantly reduce the performance.

Shared memory MIMD architectures allow communication between processors via a common shared memory which each processor can access. Shared memory architectures thus replace message sending problems with data access synchronization and cache coherency problems. To coordinate processors with shared variables a synchronization mechanism is required to prevent one process accessing a piece of data before another finishes updating it. Also, each processor in a shared memory architecture often has a local cache memory. Therefore we can have multiple copies of the same shared memory data in the caches of various processors. Maintaining consistent versions of the shared data is the cache coherency problem. As in the case of distributed memory MIMD architectures, there are several alternatives for the interconnection of the multiple processors to the shared memory. Some major examples are time-shared bus interconnections, crossbar interconnections and various forms of multi-stage interconnection network.

Duncan's category of MIMD-based architectural paradigms is meant to cover a variety of hybrid architectures which don't fit neatly into most orderly taxonomies of parallel architectures, including Flynn's. Though all the types included are based on the MIMD principle of multiple instructions and data streams and asynchronous operation, each has a distinctive fundamental operating principle.

A MIMD/SIMD architecture describes a machine which is a MIMD architecture but can be controlled in an SIMD manner. This is usually implemented using a master/slave approach. For instance, let us consider a tree-structured machine as an example. The root processor of a sub-tree can act as an SIMD controller broadcasting instructions to descendant nodes which then execute the instructions on local data. This is a very flexible approach and one which is receiving a great deal of attention.

Dataflow architectures depend on an execution paradigm where instructions are enabled for execution as soon as all their data becomes available. This is known as a data-driven architecture, in contrast with the normal instruction-driven architecture with which we are most familiar. This means that the sequence in which instructions are executed is data dependent. This allows dataflow architectures to exploit parallelism at the task, process and instruction levels. Dataflow machines are a direct result of research effort into new computational models and languages to effectively exploit large-scale parallelism.

Reduction architectures are often referred to as demand-driven architectures and, like dataflow architectures, have their own execution paradigm. In this case, an instruction is enabled for execution when its results are required as data for another instruction which has been enabled for execution. Reduction architecture research has the aim of producing parallel architectures which will support functional programming languages.

Wavefront array architectures combine systolic data pipelining with an asynchronous dataflow execution paradigm. Wavefront and systolic architectures are both characterised by modular processors and local interconnection networks. However, the wavefront array architecture co-ordinates inter-processor data movement using asynchronous handshaking. Therefore, when a processor has finished its processing and is ready to pass on its data, it informs the next processor, and sends the data when it indicates that it is ready. Once the processor receives an acknowledgement that the transmission was successful, it can proceed to its next task. Thus computational wavefronts pass through the array in correct sequence.

More detailed discussions of parallel computer architectures can be found in Almasi and Gottlieb [21], Patterson and Hennessey [22] and Trew and Wilson [23].

### 1.5 Outline of Thesis

The main body of the thesis following this introduction is divided into five parts which are covered in the following chapters. Chapter 2 and 3 review parallel discrete event simulation in some detail with particular emphasis on work relevant to the modelling of telecommunication networks. Chapter 2 explores the various methods used to decompose a simulation model into a set of communicating parallel processes; highlighting their strengths and

weaknesses. Chapter 3 concentrates on a particular decomposition approach called here the distributed model components approach and the fundamental problem of synchronization. This involves decomposing the system model into loosely-coupled components (sub-models) and simulating each with a logical process. One or more processes are then allocated to each processor. The distributed model components approach is often referred to in the literature as parallel discrete event simulation (PDES) as it is by far the most popular approach. Chapters 4, 5 and 6 describe the results of the original work performed.

Chapter 4 describes the parallel simulation of circuit-switched telecommunication networks using a parallelizing compiler on a shared memory multiprocessor computer. Work has been conducted previously using this technique to attempt to speed-up parallel discrete event simulations of queueing networks with little success. Here, a simple model of a circuit-switched network, which is not a discrete event model, is used to explore the use of a parallelizing compiler. The results showed good speed-up figures with reasonably large networks of ten nodes and greater.

Chapter 5 describes the parallel simulation of closed and tandem queueing network models. Such models are often used as the basis for modelling packet-switched telecommunication networks. This work was conducted on a distributed memory multiprocessor computer using the YADDES<sup>4</sup> tool from the University of Waterloo, Ontario, Canada. This simulator enabled the comparison of the performance of several different parallel simulation synchronization approaches using common model specifications.

Chapter 6 describes the parallel simulation of asynchronous transfer mode (ATM) networks. This work was also conducted on a distributed memory multiprocessor computer using a simulator written at the University of Durham. Simulation studies of ATM systems have thus far largely centred on the behaviour of single traffic sources, multiplexors or switching nodes. Here, the parallel simulation of a complete network has been implemented allowing realistic network performance to be studied with reasonable simulation run times.

Chapter 7 draws all of the conclusions together and attempts to highlight areas which appear worthy of further study. There are also two appendices. Appendix A contains information on the availability of a floppy disk formatted for an IBM. PC. compatible computer. This contains examples of the simulation model files used in this study. Appendix B contains the journal and conference papers published as a result of this work.

<sup>&</sup>lt;sup>4</sup>YADDES is an acronym for Yet Another Distributed Discrete Event Simulator.

Figure 1.1: Amdahl's law

## Chapter 2

## A Review of Parallel Discrete Event Simulation

#### 2.1 Introduction

discrete event simulation is a computer program model for a system where changes in the state of the system occur at discrete points in (simulated) time. Thus, the simulation model only makes the transition from one state to another when an event occurs. The system state is represented by a set of state variables which each event may modify (thus changing the system state) and/or schedule new events in the future. An event-list is maintained containing all the pending events that have been scheduled but not yet processed. Each event has its own unique time-stamp and the simulation progresses by removing the event from the event-list with the lowest time-stamp. A global clock variable is used to keep track of how far the simulation has progressed.

This type of model is suitable for modelling many types of communication network. For a packet-switched network model, say, state variables may represent the amount of traffic carried on links, lengths of packet queues, processor status etc. Typical events may include, new call arrivals, call clear downs, packet arrivals at a switching node, packet departures after processing and routeing and, even, equipment failures. Such a system model is termed an asynchronous system in that events occur at irregular intervals which can be modelled by stochastic processes; that is, they are not synchronized by a global system-wide clock. For such systems, the occurrence of events with the same time-stamp is very small so that parallel processing techniques based on lock-step execution under the control of a global

simulation clock tend to perform poorly.

Parallel discrete event simulation (PDES) refers to the execution of a single discrete event simulation program on a parallel multiprocessor computer. For a given simulation, five techniques for decomposing it into parallel processes for execution on a multiprocessor machine have been identified [11,24].

- A Parallelizing Compiler can be used to compile a sequential simulation, written in a conventional sequential language to run on a sequential uniprocessor, so that it will run on a particular multiprocessor machine.

- Distributed Simulation Experiments may be conducted by running separate simulations on separate processors in parallel. This is often called replicated trials.

- Distributed Simulation Functions involves different subroutines or tasks of a simulation being placed on separate processors. For instance processors may be dedicated to random number generation, event-list processing, statistics collection etc.

- Distributed Simulation Events uses a global event-list, as in sequential simulation, to schedule available processors to process the next event on the list.

- Distributed Simulation Model Components involves decomposing our system model into loosely coupled components (sub-models) and simulating each with a process. One or more processes are then allocated to each processor.

- Time Parallelism involves partitioning a simulation model into a set of time periods. Each time period is simulated in parallel and then the results from each period are joined, or merged, together. This joining process is performed so that the final set of results is the same as that which would be produced by a single long simulation run. This is radically different from all of the above approaches which may be said to exploit space parallelism.

Where the term PDES is found in the literature, it almost invariably refers to distributed model components, as it is by far the most popular. The term distributed model components approach will be used here to (hopefully) avoid any confusion. The good and bad points of all of the above decomposition methods are discussed in the following sections giving examples of work done in each area particularly emphasising work directly (or indirectly) related to the simulation of telecommunication networks. The section on the distributed

model components approach merely introduces the subject as it is dealt with in much more detail in chapter 3. Obviously some combined approaches are also possible which are some combination of the above techniques and these are also discussed.

## 2.2 Parallelizing Compilers

We are very familiar with the concept of a compiler which takes a high-level language source code and compiles it to produce the machine-level object code which runs directly on a sequential uniprocessor system. One approach to tackling the production of code for a multiprocessor computer is to apply a compiler which takes, as its input, a conventional sequential high-level language and produces, as its output, the object code to run on each of the multiprocessors. This is termed a parallelizing compiler. The compiler thus has the responsibility to recognise sequences in the source code which can be executed in parallel and scheduled to run on separate processors. This definition thus distinguishes a parallelizing compiler from a compiler which takes a high-level parallel language and compiles it to run on a multiprocessor computer. Though such a compiler could be made responsible for automatically assigning processes to processors. An excellent survey of such compilers and automatic parallelization generally has been produced recently by Bannerjee et. al. [25].

The overwhelming advantage is that the approach is largely transparent to the user. A new parallel language does not have to be learned, the multiprocessor architecture should not impact the original program structure and existing sequential software, so-called dusty decks, may be ported. The disadvantage often found is that the problem has been coded in sequential form, thus largely ignoring any parallelism in the structure of the problem. This results in relatively small portions of the available parallelism in the problem being exploited and, hence, the speed-up in moving to the multiprocessor architecture is generally disappointing.

Parallelizing compilers are usually constructed such that they are effective in translating a wide range of sequential programs for use on the particular multiprocessor. Indeed, many of the algorithms used in the program analysis and transformation may well have been developed with many classes of scalable parallel multiprocessor in mind. This means in practice that a parallelizing compiler written for and running on a particular architecture is unlikely to give the best performance in terms of speed-up for *one* particular application. The best performance will always be obtained by writing the application from scratch.

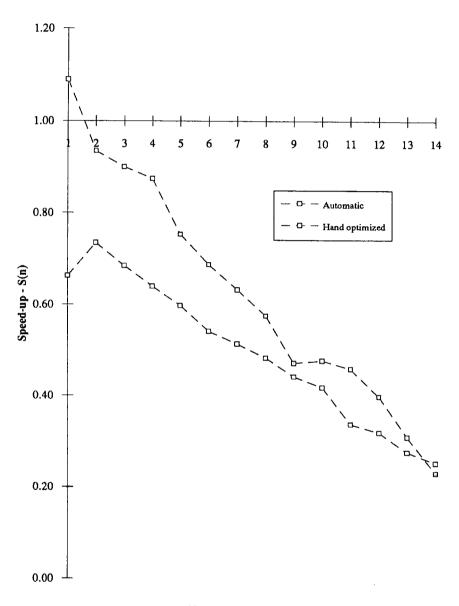

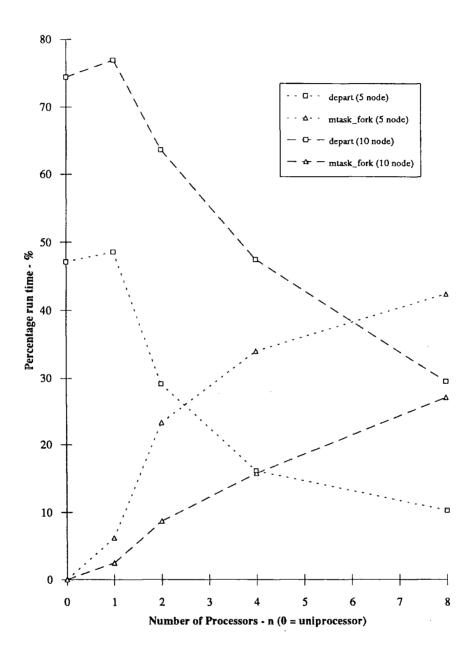

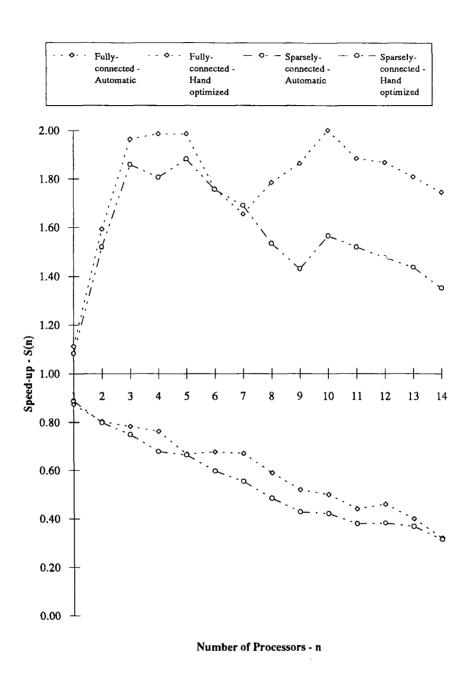

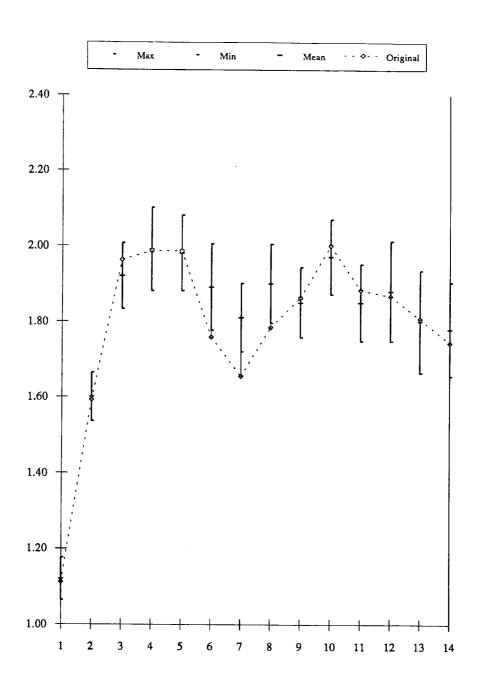

There are two basic approaches to converting sequential code to run on multiprocessor architectures. A parallelizing compiler takes sequential code directly and produces parallel code to run on the target multiprocessor system. Alternatively, intelligent run-time support and parallel routine libraries can be provided with a programming environment which allows the conversion of sequential into parallel code.