## **Durham E-Theses**

# The hardware implementation of an artificial neural network using stochastic pulse rate encoding principles

Glover, John Sigsworth

#### How to cite:

Glover, John Sigsworth (1995) The hardware implementation of an artificial neural network using stochastic pulse rate encoding principles, Durham theses, Durham University. Available at Durham E-Theses Online: <a href="http://etheses.dur.ac.uk/5423/">http://etheses.dur.ac.uk/5423/</a>

#### Use policy

The full-text may be used and/or reproduced, and given to third parties in any format or medium, without prior permission or charge, for personal research or study, educational, or not-for-profit purposes provided that:

- a full bibliographic reference is made to the original source

- a link is made to the metadata record in Durham E-Theses

- the full-text is not changed in any way

The full-text must not be sold in any format or medium without the formal permission of the copyright holders.

Please consult the full Durham E-Theses policy for further details.

# The Hardware Implementation Of An Artificial Neural Network

## Using Stochastic Pulse Rate Encoding Principles

John Sigsworth Glover

M.Eng. (Leeds)

School of Engineering University of Durham

A thesis submitted in partial fulfillment of the requirements of the Council of the University of Durham for the Degree of Doctor of Philosophy (Ph.D.).

September 1995

The copyright of this thesis rests with the author.

No quotation from it should be published without his prior written consent and information derived from it should be acknowledged.

#### Abstract

In this thesis the development of a hardware artificial neuron device and artificial neural network using stochastic pulse rate encoding principles is considered.

After a review of neural network architectures and algorithmic approaches suitable for hardware implementation, a critical review of hardware techniques which have been considered in analogue and digital systems is presented. New results are presented demonstrating the potential of two learning schemes which adapt by the use of a single reinforcement signal.

The techniques for computation using stochastic pulse rate encoding are presented and extended with new novel circuits relevant to the hardware implementation of an artificial neural network. The generation of random numbers is the key to the encoding of data into the stochastic pulse rate domain. The formation of random numbers and multiple random bit sequences from a single PRBS generator have been investigated. Two techniques, Simulated Annealing and Genetic Algorithms, have been applied successfully to the problem of optimising the configuration of a PRBS random number generator for the formation of multiple random bit sequences and hence random numbers.

A complete hardware design for an artificial neuron using stochastic pulse rate encoded signals has been described, designed, simulated, fabricated and tested before configuration of the device into a network to perform simple test problems. The implementation has shown that the processing elements of the artificial neuron are small and simple, but that there can be a significant overhead for the encoding of information into the stochastic pulse rate domain. The stochastic artificial neuron has the capability of on-line weight adaption. The implementation of reinforcement schemes using the stochastic neuron as a basic element are discussed.

#### Acknowledgements

The following people have been vital to the production of this thesis, but many others have also contributed to my welfare during the development of this thesis.

- Professor Phil Mars of the University of Durham for all his guidance and advice.

- Dr Simon Johnson of the University of Durham for discussions on the hardware implementation techniques available at the University of Durham.

- University of Teesside for their assistance in the fabrication of the artificial neuron devices.

- Raghu, Chen, Alan, Jeremy, David, Matthew, Martin and Stephen, my colleagues in the lab for their support.

#### Declaration

I hereby declare that this thesis is a record of work undertaken by myself, that it has not been the subject of any previous application for a degree, and that all sources of information have been duly acknowledged.

#### ©Copyright 1995, John Sigsworth Glover

The copyright of this thesis rests with the author. No quotation from it should be published without his written consent, and information derived from it should be acknowledged.

## Contents

| C                | Contents            |        |                                                       | iv  |  |

|------------------|---------------------|--------|-------------------------------------------------------|-----|--|

| $\mathbf{L}^{:}$ | List of Figures vii |        |                                                       |     |  |

| Li               | ist of              | Abbro  | eviations                                             | xiv |  |

| 1                | Inti                | roduct | ion                                                   | 1   |  |

|                  | 1.1                 | Outlin | ne of Thesis                                          | 3   |  |

| 2                | Asp                 | ects o | f Artificial Neural Networks                          | 5   |  |

|                  | 2.1                 | The B  | Biological Inspiration for Artificial Neural Networks | 6   |  |

|                  | 2.2                 | Basic  | Processing Element Model                              | 8   |  |

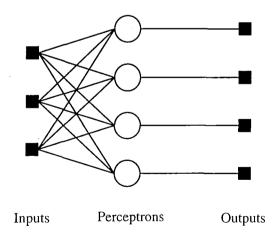

|                  | 2.3                 | Single | -layer Perceptron and Multi-layer Perceptron          | 9   |  |

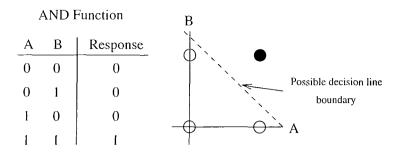

|                  |                     | 2.3.1  | SLP and the Perceptron Convergence Procedure          | 10  |  |

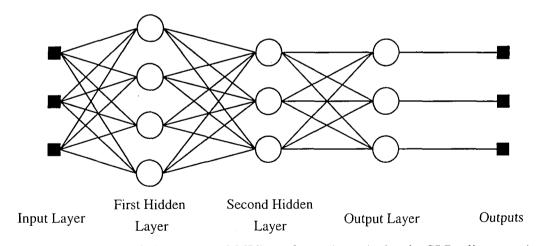

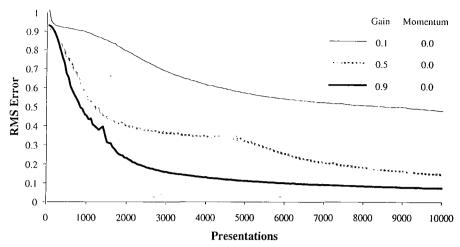

|                  |                     | 2.3.2  | MLP and Backpropagation                               | 12  |  |

|                  |                     | 2.3.3  | MLP and Backpropagation Implementation                | 17  |  |

|                  | 2.4                 | Kohon  | nen Self-Organising Feature Map                       | 19  |  |

|                  |                     | 2.4.1  | Training                                              | 20  |  |

|                  |                     | 2.4.2  | Kohonen Self-Organising Map Implementation            | 22  |  |

|                  | 2.5                 | The H  | opfield Network                                       | 24  |  |

|                  |                     | 2.5.1  | Architecture and Operation                            | 25  |  |

|                  | 2.6                 | Boltzn | nann Machine                                          | 27  |  |

|                  |                     | 2.6.1  | Architecture and Operation                            | 27  |  |

|                  | 2.7                 | Reinfo | preement Learning Schemes                             | 29  |  |

|                  |                     | 2.7.1  | Barto Reinforcement Learning                          | 35  |  |

|   | 2.8 | Two                                  | New Extensions for Reinforcement Learning: Q-model and T-model |     |

|---|-----|--------------------------------------|----------------------------------------------------------------|-----|

|   |     | $\mathbf{A}_{\mathbf{R}-\mathbf{R}}$ | P                                                              | 38  |

|   |     | 2.8.1                                | Evaluating the Four $\mathbf{A_{R-P}}$ Strategies              | 39  |

|   | 2.9 | Concl                                | usions                                                         | 41  |

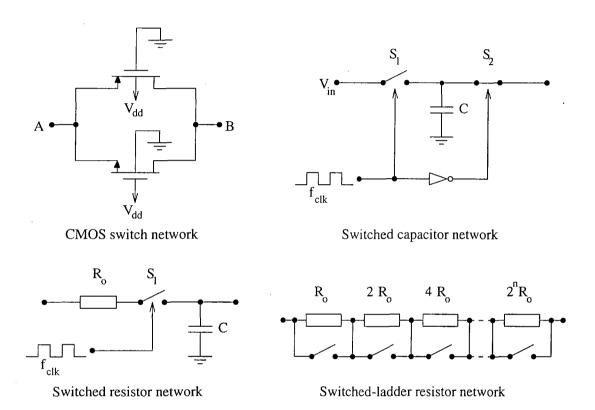

| 3 | Har | rdware                               | Implementation: A Critical Review                              | 65  |

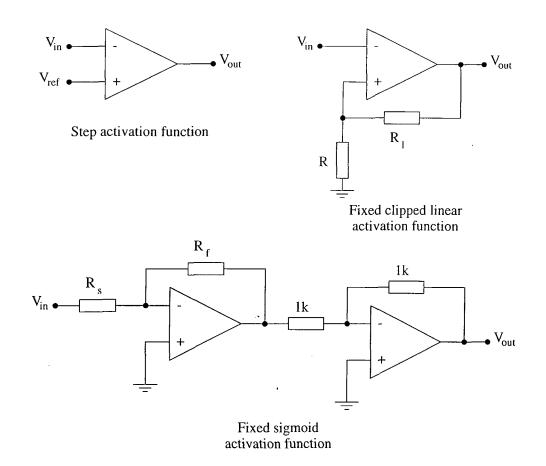

|   | 3.1 | Analo                                | gue Artificial Neural Networks                                 | 66  |

|   | 3.2 | Digita                               | d Artificial Neural Networks                                   | 68  |

|   | 3.3 | Hybri                                | d Artificial Neural Networks                                   | 69  |

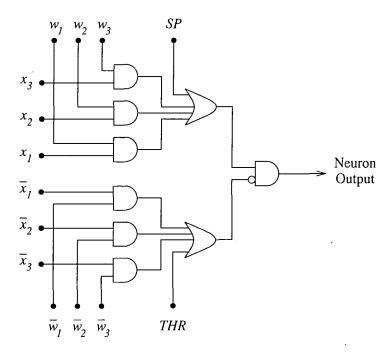

|   | 3.4 | Pulse                                | Coded Hardware Implementations                                 | 69  |

|   |     | 3.4.1                                | Deterministic Pulse Coding Circuits                            | 71  |

|   |     | 3.4.2                                | Stochastic Pulse Coding Circuits                               | 73  |

|   | 3.5 | Comm                                 | nercial Hardware Realisations                                  | 75  |

|   | 3.6 | Concl                                | usions                                                         | 76  |

| 4 | Sto | chastic                              | Pulse Rate Computation                                         | 82  |

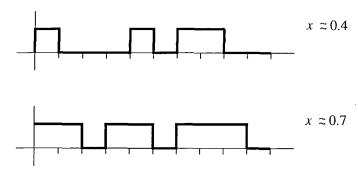

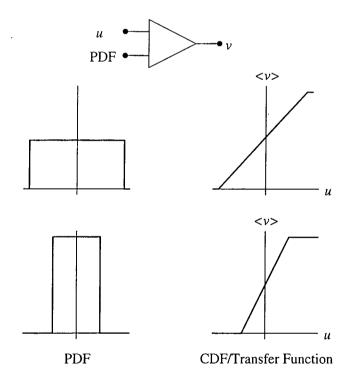

|   | 4.1 | Encod                                | ing or Input Mapping into the Stochastic Pulse Rate Domain     | 83  |

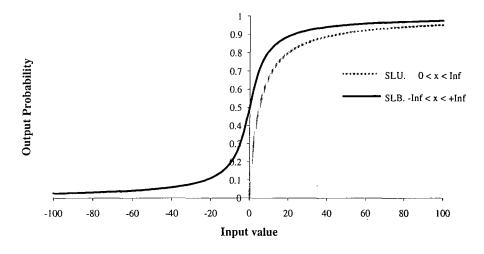

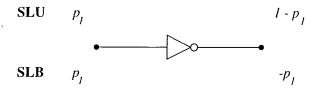

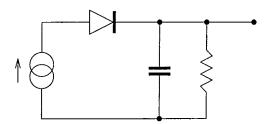

|   |     | 4.1.1                                | SLU Input Mapping                                              | 83  |

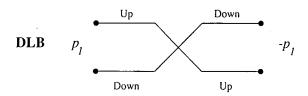

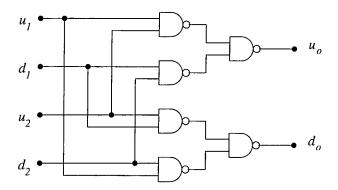

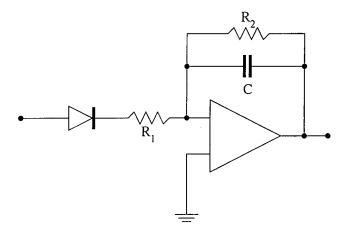

|   |     | 4.1.2                                | DLB Input Encoding                                             | 86  |

|   |     | 4.1.3                                | SLB Input Encoding                                             | 88  |

|   |     | 4.1.4                                | Non-linear Input Encoding                                      | 89  |

|   | 4.2 | Inversi                              | ion                                                            | 90  |

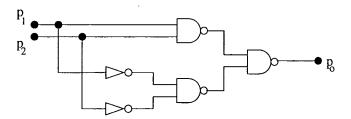

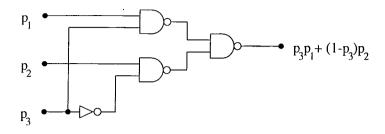

|   | 4.3 | Multip                               | olication                                                      | 91  |

|   | 4.4 | Additi                               | on                                                             | 94  |

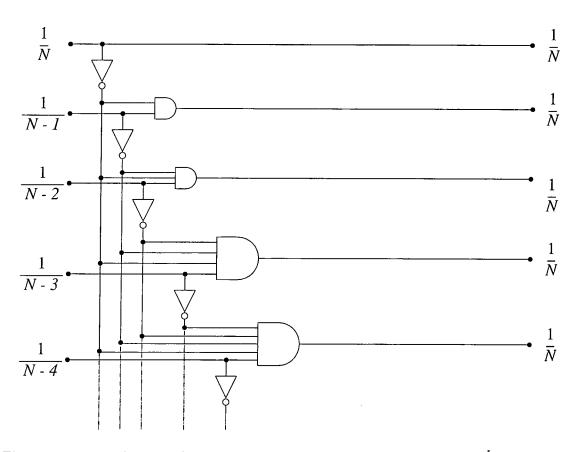

|   |     | 4.4.1                                | An $N$ Input Adder Proposal                                    | 97  |

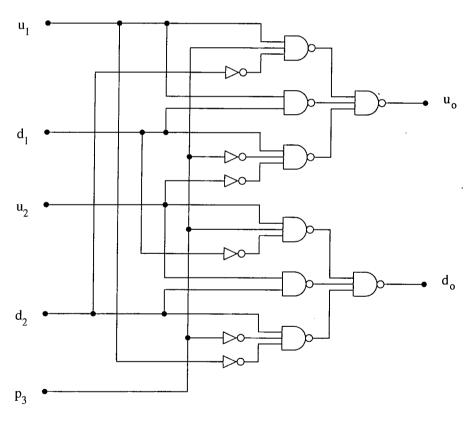

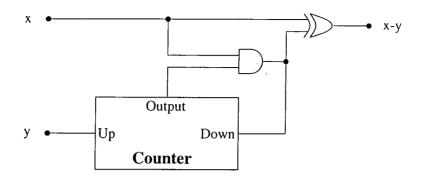

|   | 4.5 | Subtra                               | action                                                         | 98  |

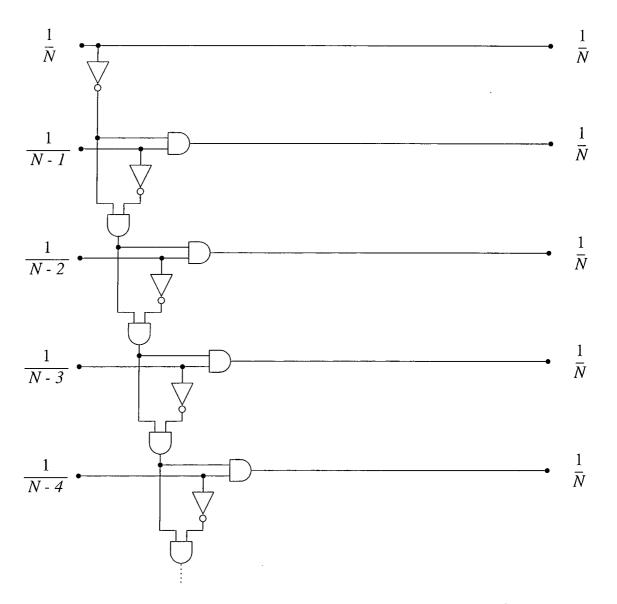

|   | ٠   | 4.5.1                                | A Subtracter Proposal                                          | 98  |

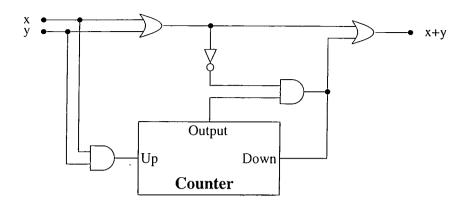

|   | 4.6 | Integra                              | ation and the ADDIE                                            | 99  |

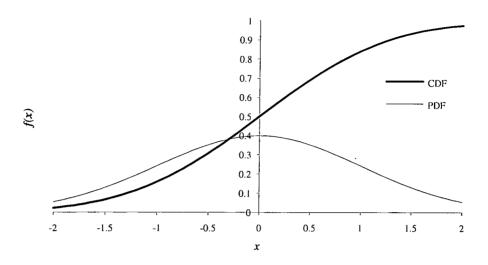

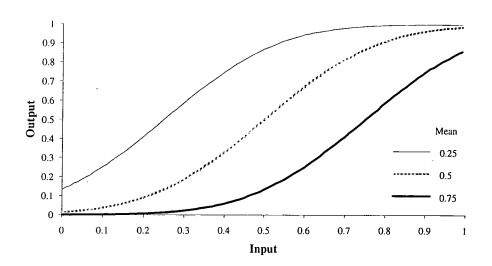

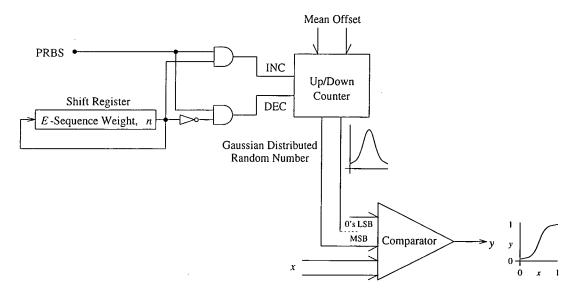

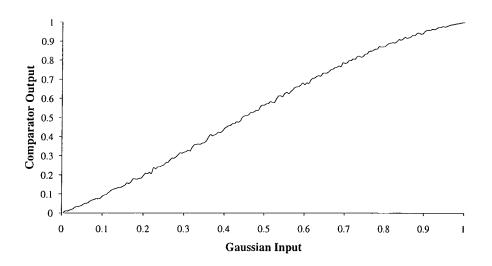

|   | 4.7 | Sigmoi                               | idal Transform Proposal                                        | 03  |

|   |     | 4.7.1                                | Even-Shift Orthogonal Sequences                                | 04  |

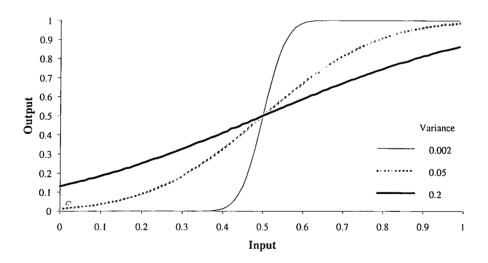

|   |     | 4.7.2                                | Sigmoidal Transform Production Using Gaussian Distributed Ran- |     |

|   |     |                                      | dom Numbers                                                    | 05  |

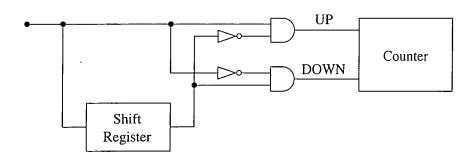

|   |     | 4.7.3                                | Sigmoidal Transform Production Using E-Sequences               | 06  |

|   |     | 1.71                                 | E-Sequence Conclusions                                         | ns. |

|   | 4.8 | Decod                                                                                                       | ling and Output Interfacing                                                                                                                                                                                                                                                                                                              |

|---|-----|-------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 4.9 | Summ                                                                                                        | nary                                                                                                                                                                                                                                                                                                                                     |

| 5 | Mu  | ltiple l                                                                                                    | Random Number Generation 124                                                                                                                                                                                                                                                                                                             |

|   | 5.1 | Introd                                                                                                      | luction                                                                                                                                                                                                                                                                                                                                  |

|   | 5.2 | Gener                                                                                                       | ation of Random Numbers                                                                                                                                                                                                                                                                                                                  |

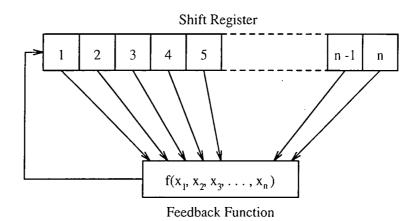

|   | 5.3 | Pseud                                                                                                       | o Random Binary Sequence Generators                                                                                                                                                                                                                                                                                                      |

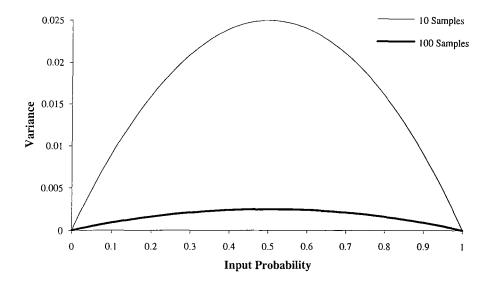

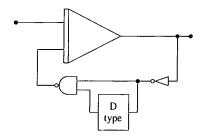

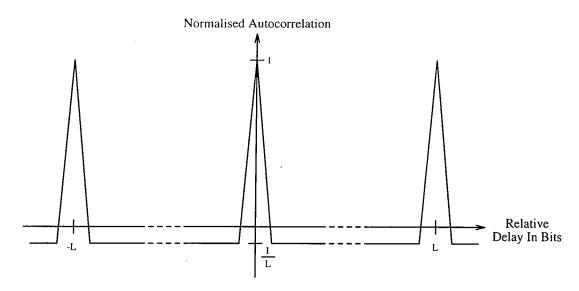

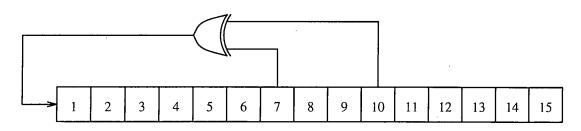

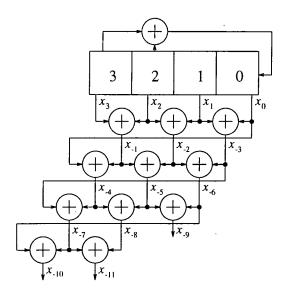

|   |     | 5.3.1                                                                                                       | Basic PRBS Generator Considerations                                                                                                                                                                                                                                                                                                      |

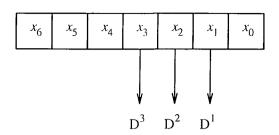

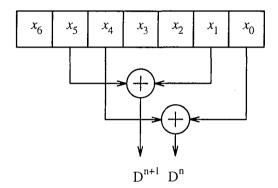

|   |     | 5.3.2                                                                                                       | Delayed PRBSs                                                                                                                                                                                                                                                                                                                            |

|   |     | 5.3.3                                                                                                       | Multiple PRBS                                                                                                                                                                                                                                                                                                                            |

|   |     | 5.3.4                                                                                                       | PRBS to Random Number Conversion                                                                                                                                                                                                                                                                                                         |

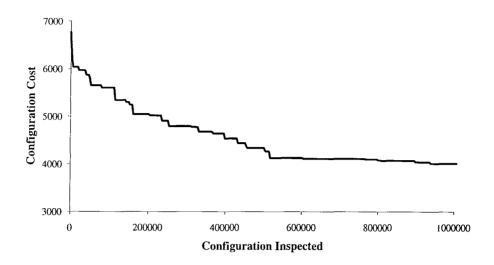

|   | 5.4 | Simula                                                                                                      | ated Annealing                                                                                                                                                                                                                                                                                                                           |

|   | 5.5 | Genet                                                                                                       | ic Algorithms                                                                                                                                                                                                                                                                                                                            |

|   | 5.6 | Result                                                                                                      | s                                                                                                                                                                                                                                                                                                                                        |

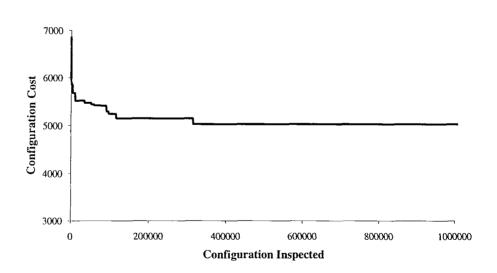

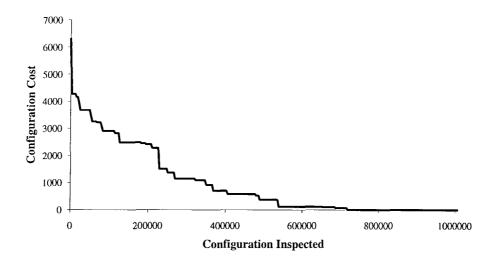

|   |     | 5.6.1                                                                                                       | Simulated Annealing                                                                                                                                                                                                                                                                                                                      |

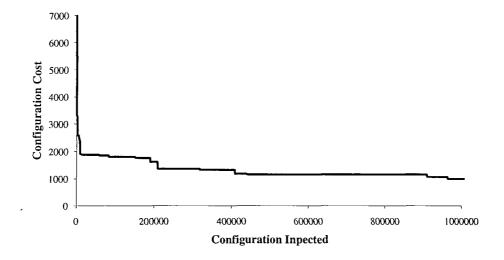

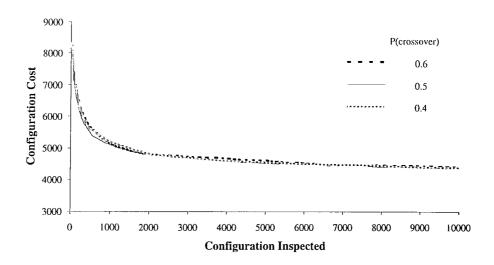

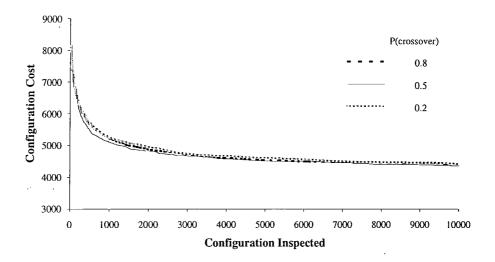

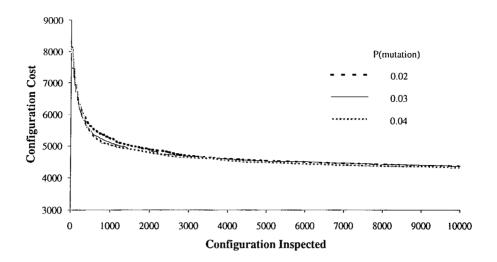

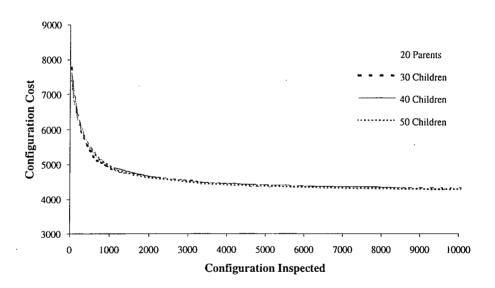

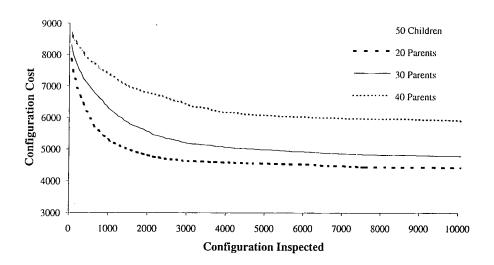

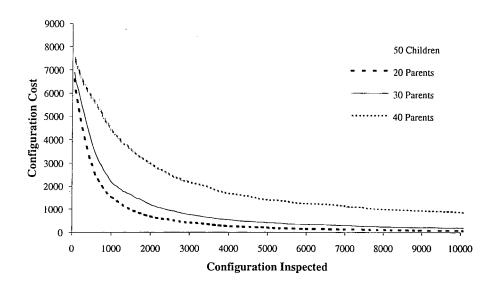

|   |     | 5.6.2                                                                                                       | Genetic Algorithm                                                                                                                                                                                                                                                                                                                        |

|   | 5.7 | Conclu                                                                                                      | asions                                                                                                                                                                                                                                                                                                                                   |

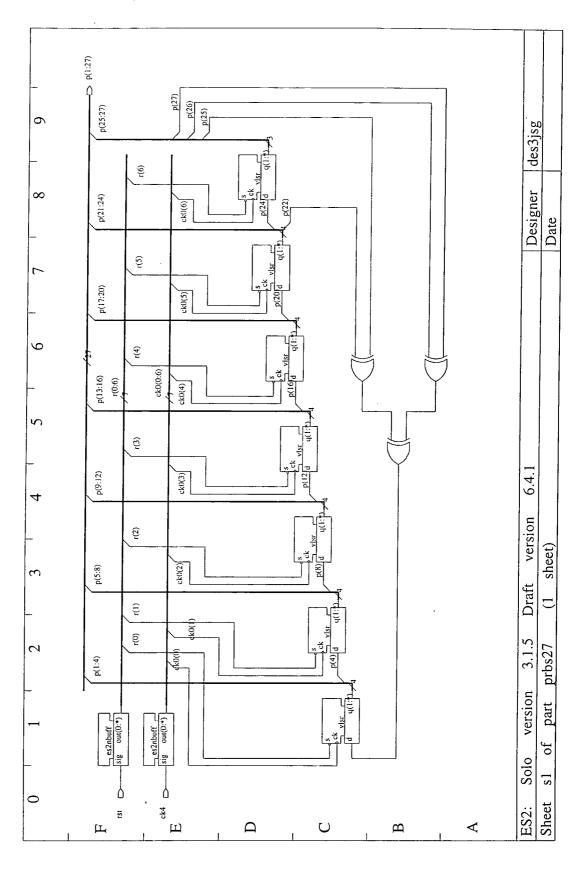

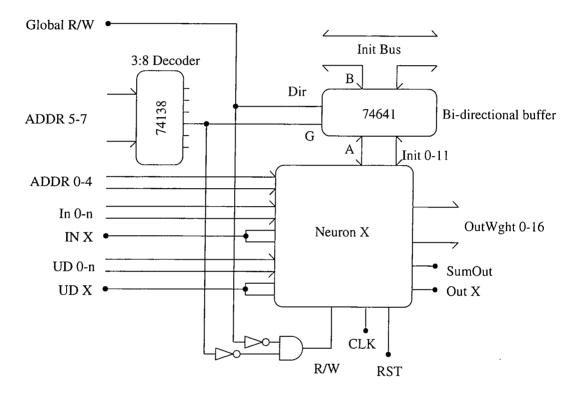

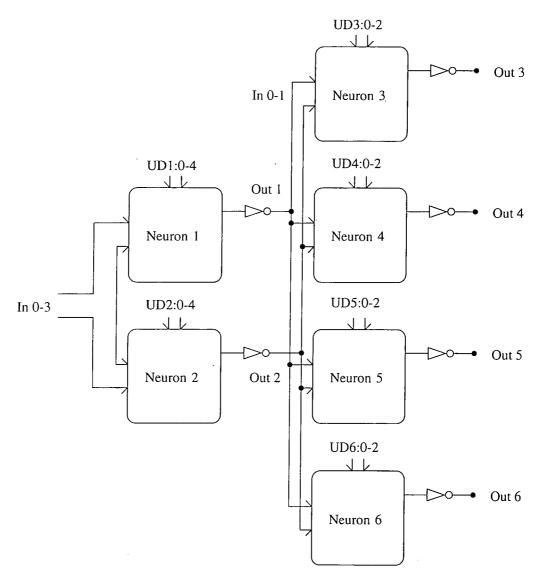

| 6 | An  | Artific                                                                                                     | tial Neuron VLSI Design and Implementation 154                                                                                                                                                                                                                                                                                           |

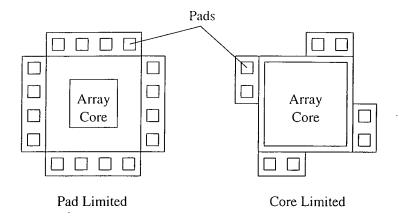

|   | 6.1 | NT                                                                                                          | n Overview                                                                                                                                                                                                                                                                                                                               |

|   |     | neuro                                                                                                       | II Overview                                                                                                                                                                                                                                                                                                                              |

|   | 6.2 |                                                                                                             | Tools                                                                                                                                                                                                                                                                                                                                    |

|   | 6.2 |                                                                                                             |                                                                                                                                                                                                                                                                                                                                          |

|   | 6.2 | Design                                                                                                      | Tools                                                                                                                                                                                                                                                                                                                                    |

|   |     | Design                                                                                                      | Tools                                                                                                                                                                                                                                                                                                                                    |

|   |     | Design<br>6.2.1<br>Artific                                                                                  | Tools                                                                                                                                                                                                                                                                                                                                    |

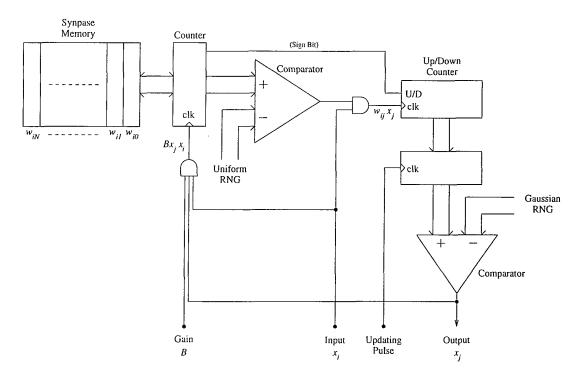

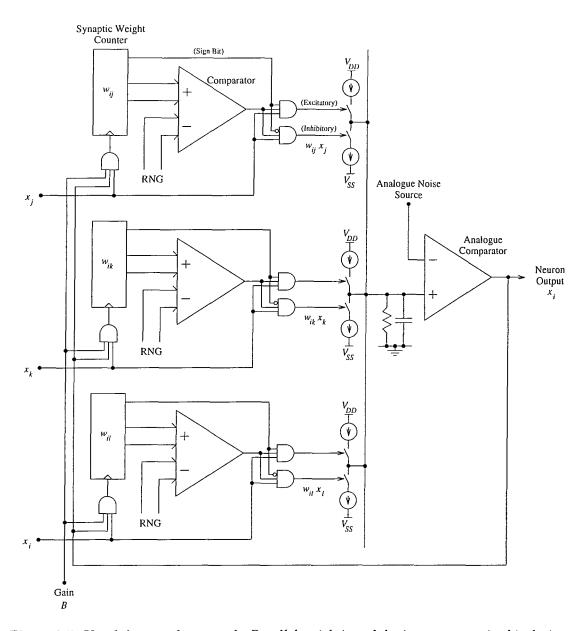

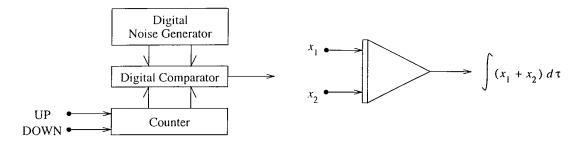

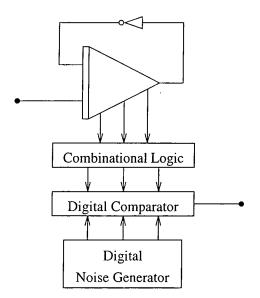

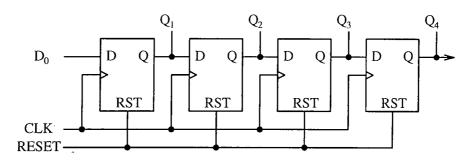

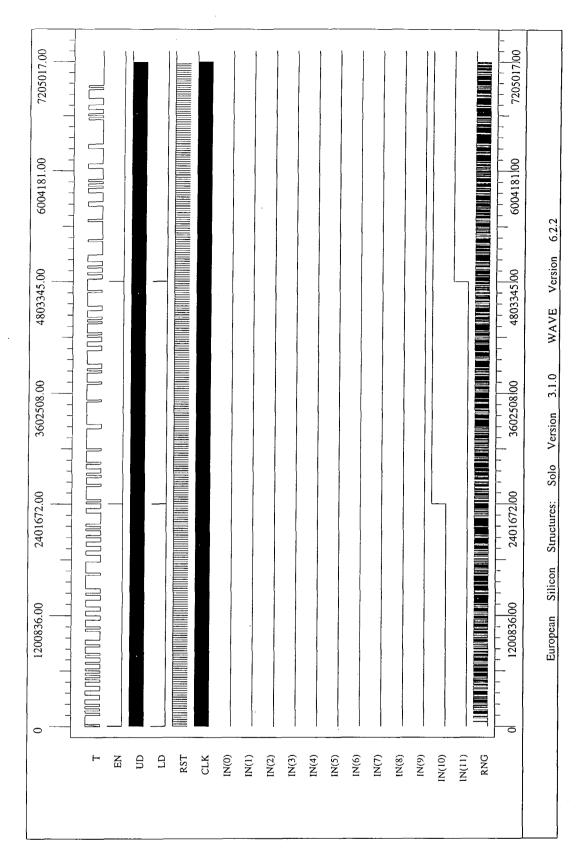

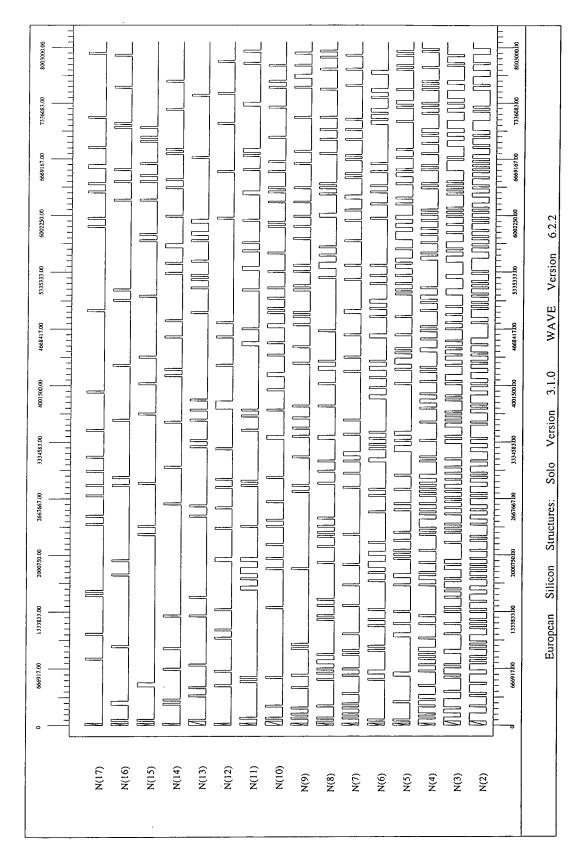

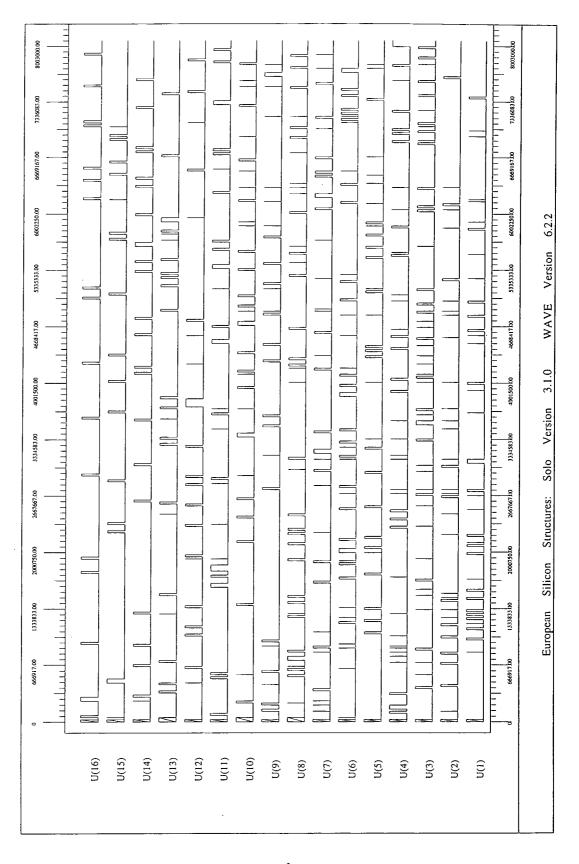

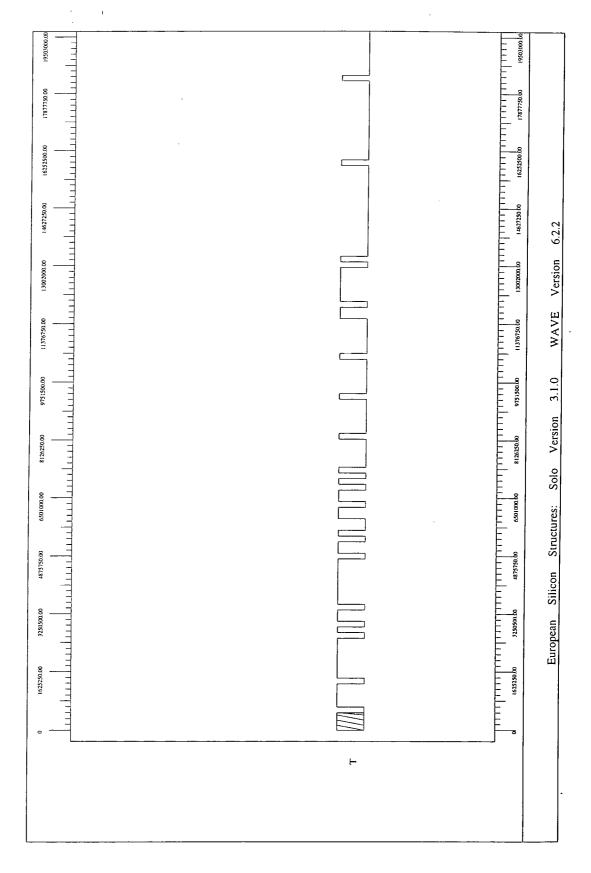

|   |     | Design<br>6.2.1<br>Artific<br>6.3.1                                                                         | Tools       155         The Solo 1400 Program Suite       157         rial Neuron Design       159         PRBS Generator       160                                                                                                                                                                                                      |

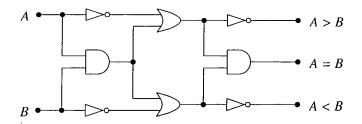

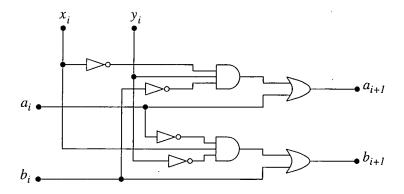

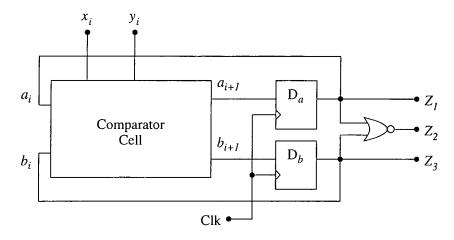

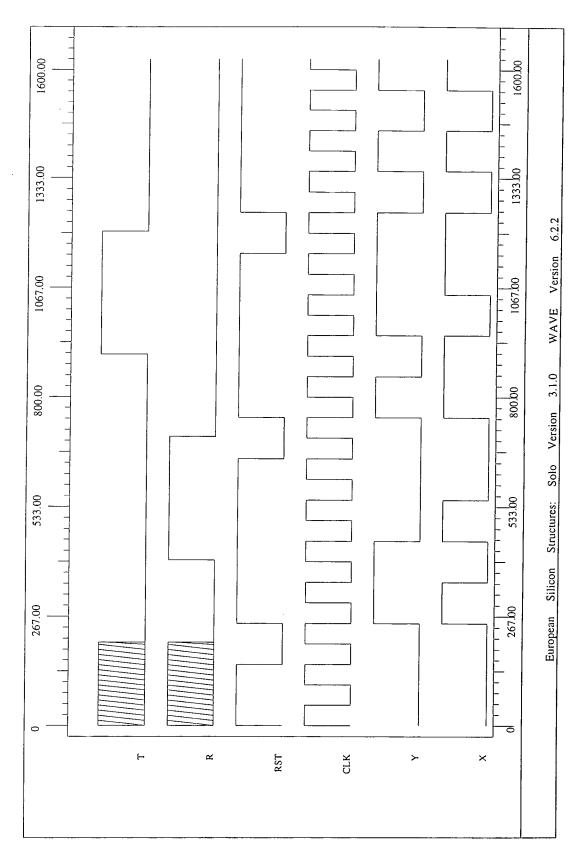

|   |     | Design<br>6.2.1<br>Artific<br>6.3.1<br>6.3.2                                                                | Tools       155         The Solo 1400 Program Suite       157         ial Neuron Design       159         PRBS Generator       160         12-bit Comparator       161                                                                                                                                                                   |

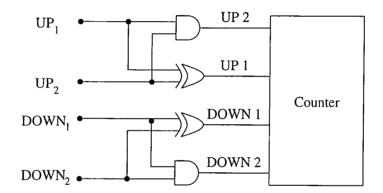

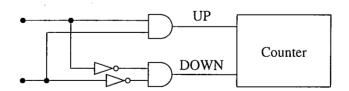

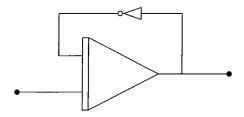

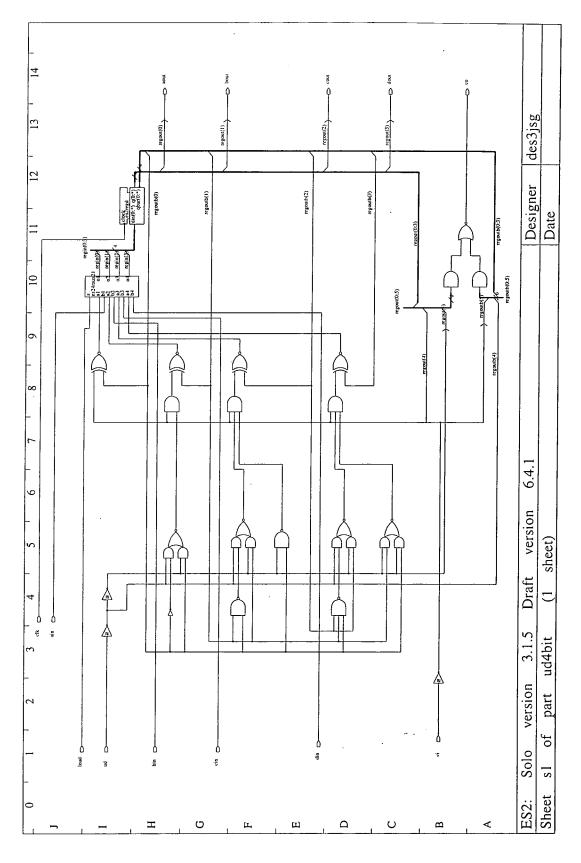

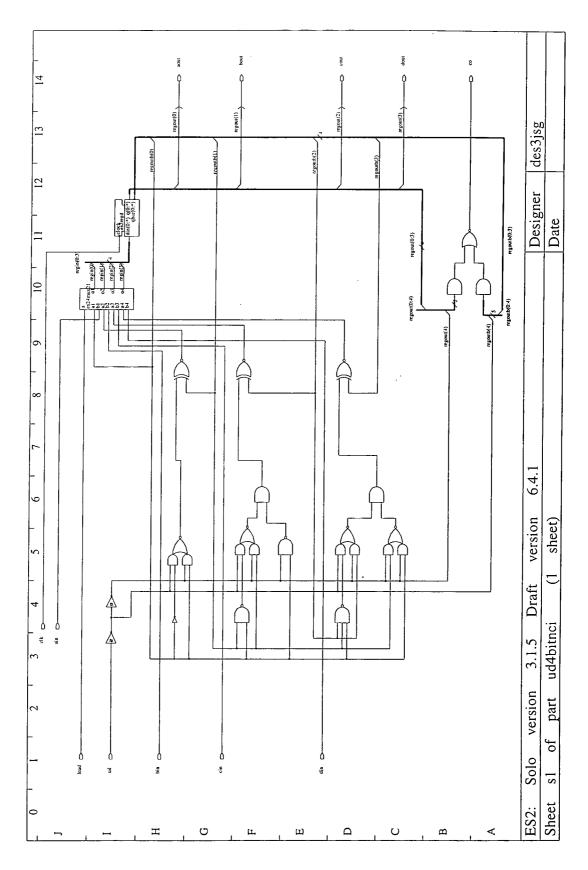

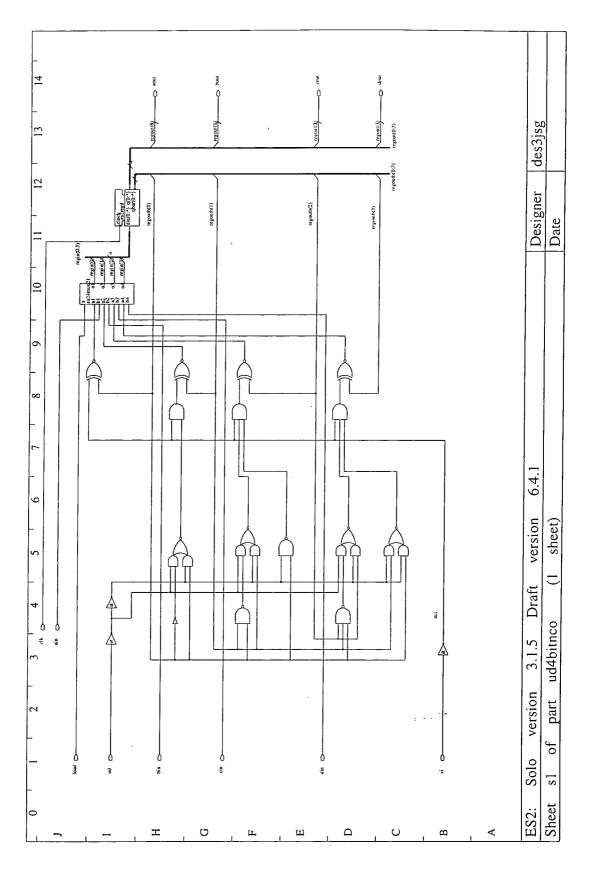

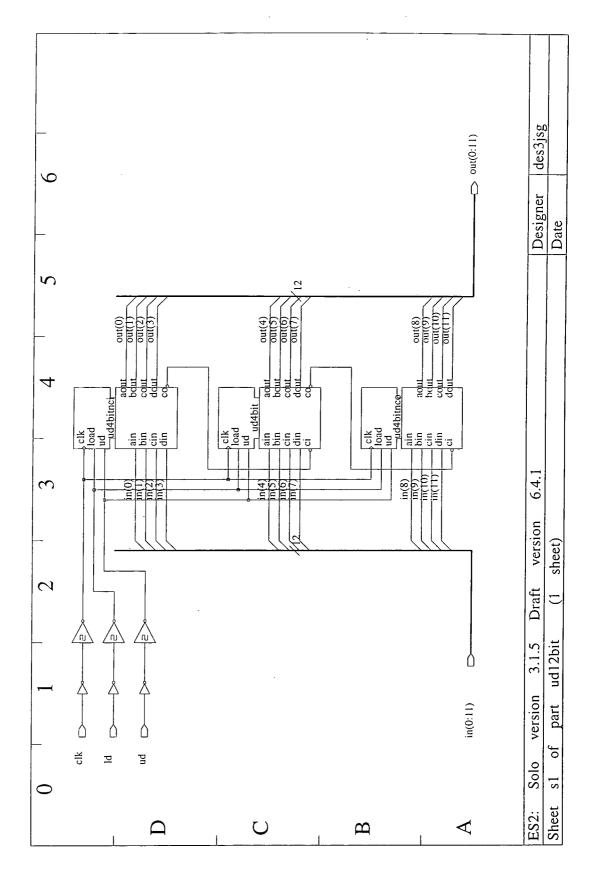

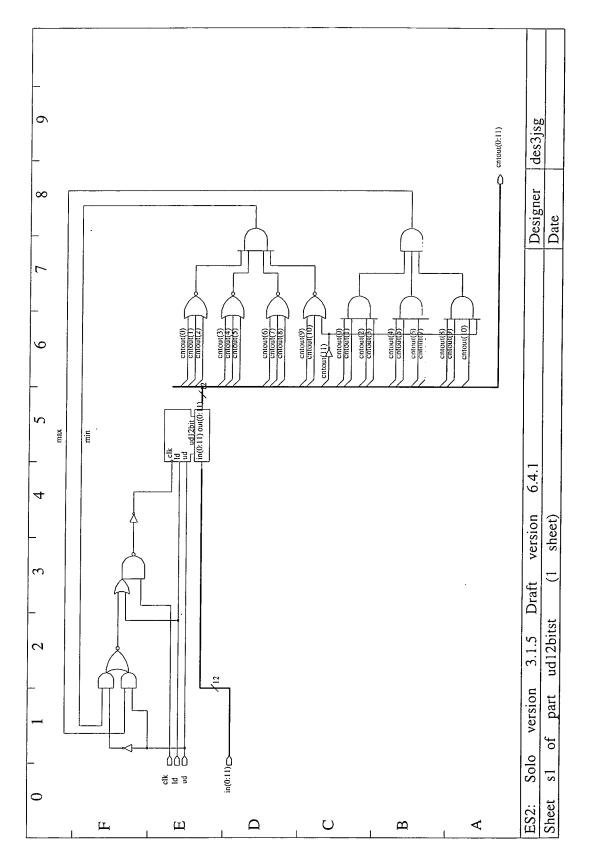

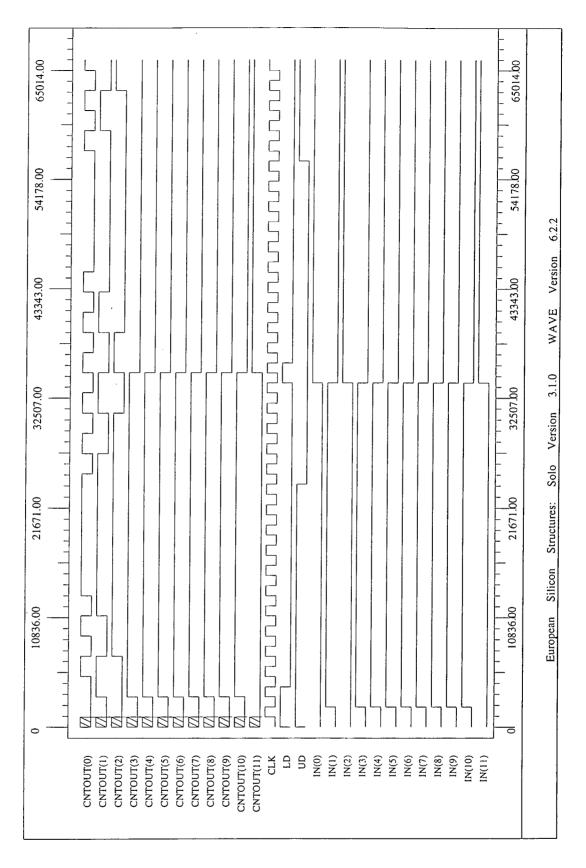

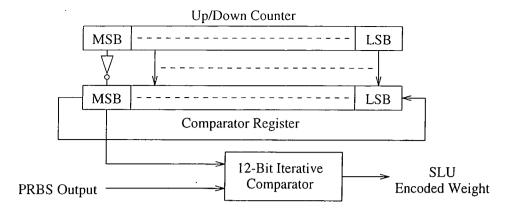

|   |     | Design<br>6.2.1<br>Artific<br>6.3.1<br>6.3.2<br>6.3.3                                                       | Tools       155         The Solo 1400 Program Suite       157         rial Neuron Design       159         PRBS Generator       160         12-bit Comparator       161         Counters       162                                                                                                                                       |

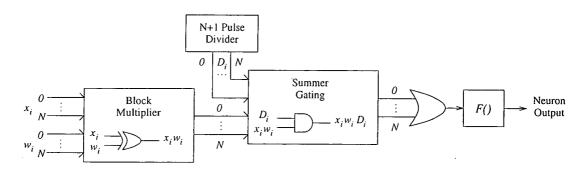

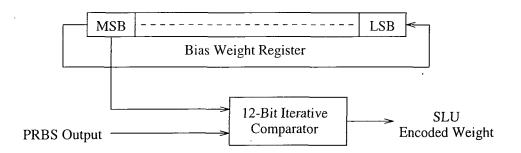

|   |     | Design<br>6.2.1<br>Artific<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4                                              | Tools                                                                                                                                                                                                                                                                                                                                    |

|   |     | Design<br>6.2.1<br>Artific<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4<br>6.3.5                                     | Tools                                                                                                                                                                                                                                                                                                                                    |

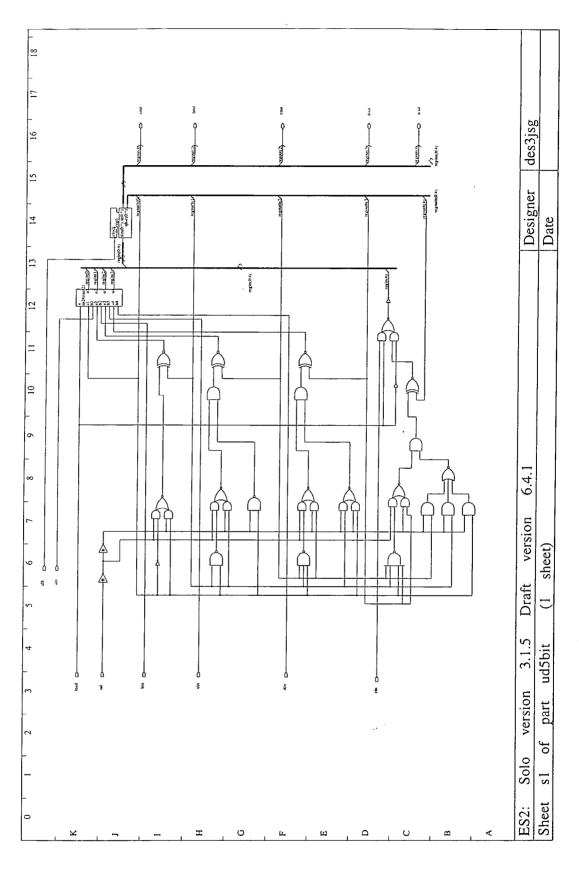

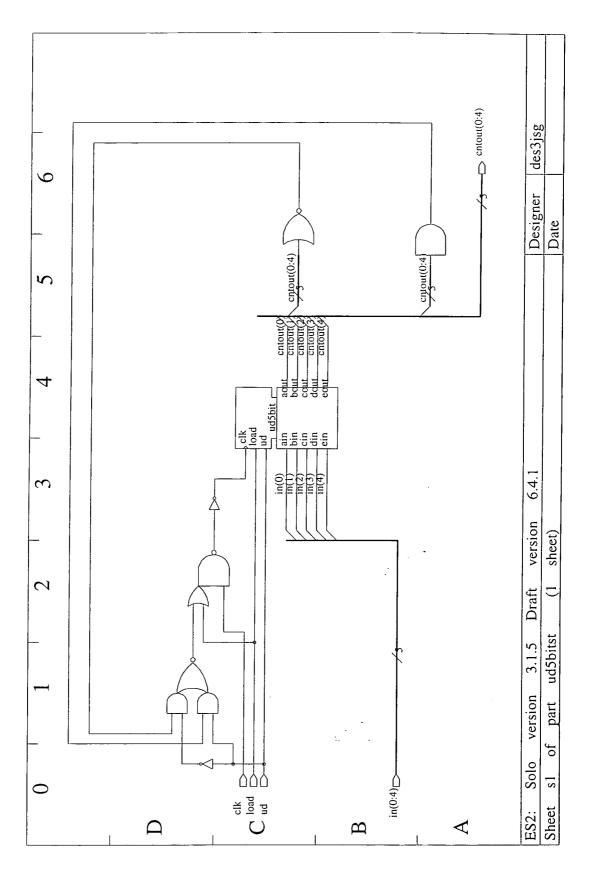

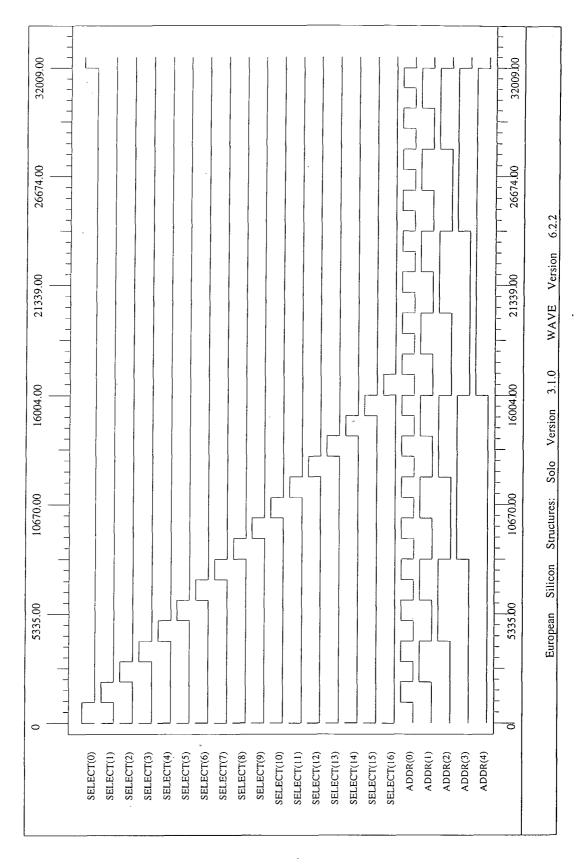

|   |     | Design<br>6.2.1<br>Artific<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4<br>6.3.5<br>6.3.6                            | Tools       155         The Solo 1400 Program Suite       157         ial Neuron Design       159         PRBS Generator       160         12-bit Comparator       161         Counters       162         Input Weight Storage and Encoding       164         N Pulse Divider Weight Encoder       165         N Pulse Divider       166 |

|   |     | Design<br>6.2.1<br>Artific<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4<br>6.3.5<br>6.3.6<br>6.3.7                   | Tools                                                                                                                                                                                                                                                                                                                                    |

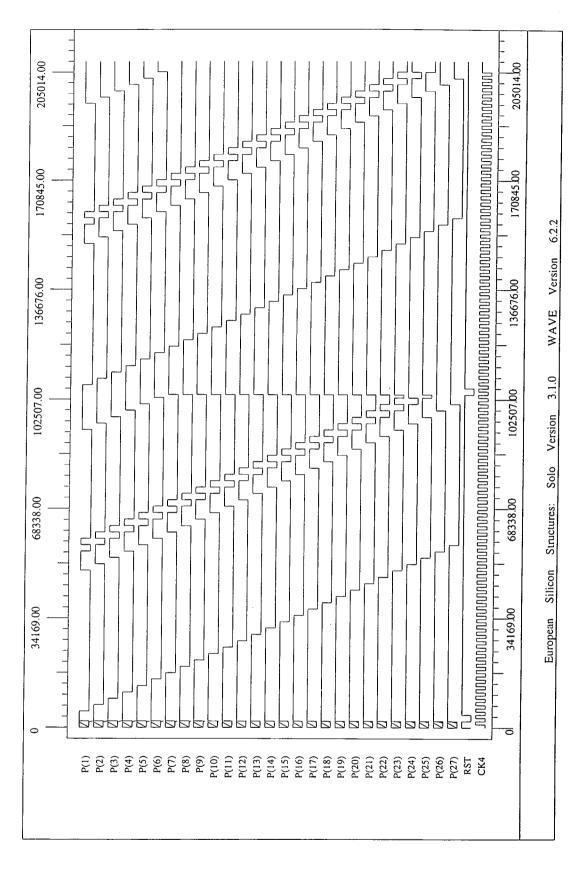

|   |     | Design<br>6.2.1<br>Artific<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4<br>6.3.5<br>6.3.6<br>6.3.7<br>6.3.8<br>6.3.9 | Tools                                                                                                                                                                                                                                                                                                                                    |

|              |       | 6.5.1        | System Implementation: 1st Proposal                                  | 174 |

|--------------|-------|--------------|----------------------------------------------------------------------|-----|

|              |       | 6.5.2        | System Implementation: 2nd Proposal                                  | 175 |

|              |       | 6.5.3        | Weight Determination                                                 | 175 |

|              |       | 6.5.4        | Results of System Operation                                          | 178 |

|              | 6.6   | Summ         | ary                                                                  | 178 |

| 7            | Cor   | clusio       | ns and Further Work                                                  | 219 |

|              | 7.1   | Conclu       | isions                                                               | 219 |

|              | 7.2   | Furthe       | er Work                                                              | 222 |

| $\mathbf{A}$ | Rar   | ndom I       | Number Generation                                                    | 225 |

|              | A.1   | Hardw        | vare Random Number Generators                                        | 225 |

|              | A.2   | Softwa       | re Random Number Generators                                          | 226 |

|              |       | A.2.1        | Middle Square Generator                                              | 227 |

|              |       | A.2.2        | Linear Congruential Generators                                       | 227 |

|              |       | A.2.3        | Lagged-Fibonacci Generators                                          | 228 |

|              |       | A.2.4        | ${\bf Add\text{-}WithCarry\ and\ SubtractWithBorrow\ .\ .\ .\ .\ .}$ | 228 |

|              | A.3   | Rando        | m Number Generator Tests                                             | 229 |

| В            | Test  | ting th      | e Quality of the Random Numbers from a PRBS                          | 232 |

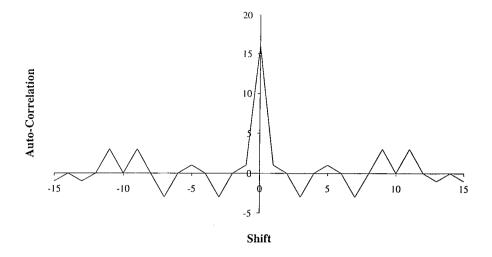

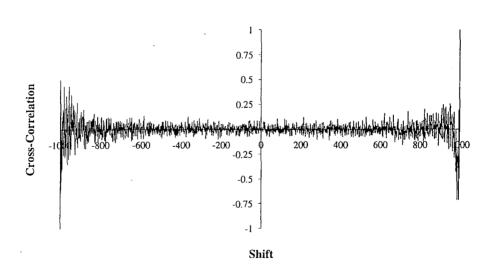

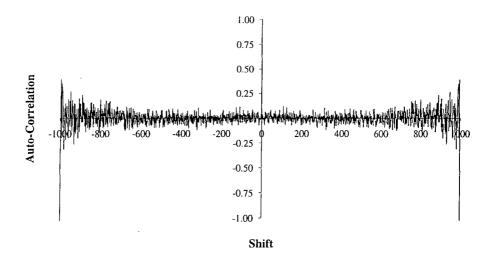

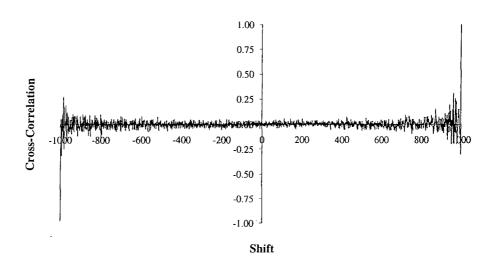

|              | B.1   | Correl       | ation Tests                                                          | 232 |

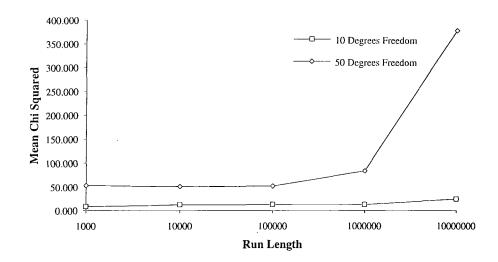

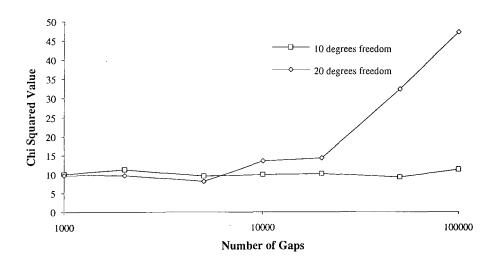

|              | B.2   | $\chi^2$ Tes | t/Frequency Test                                                     | 233 |

|              | B.3   | Gap T        | est                                                                  | 236 |

|              | B.4   | Summ         | ary                                                                  | 236 |

| $\mathbf{C}$ | A C   | ++ P         | RBS Class                                                            | 242 |

| D            | Neu   | ron Te       | est Board Configuration                                              | 251 |

| E            | 4-2-  | -4 Enc       | oder/Decoder Board Configuration                                     | 254 |

| Ri           | hliog | ranhy        |                                                                      | 259 |

## List of Figures

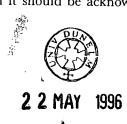

| 2.1  | Illustration of a Biological Neuron Structure                                                 | 43         |

|------|-----------------------------------------------------------------------------------------------|------------|

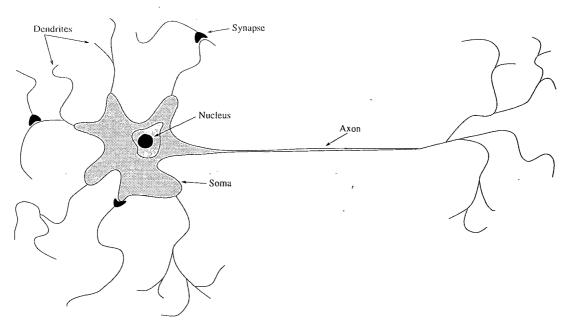

| 2.2  | General Artificial Neuron Architecture of McCulloch and Pitts                                 | 43         |

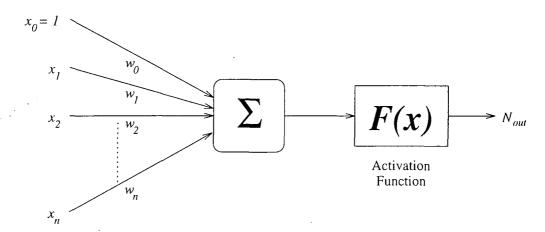

| 2.3  | Common Neuron Activation Functions.                                                           | 44         |

| 2.4  | Single layer perceptron configuration                                                         | 44         |

| 2.5  | Example of AND and XOR functions for the Perceptron.                                          | 45         |

| 2.6  | Three layer fully connected MLP configuration                                                 | 45         |

| 2.7  | Example of the file setup.mlp                                                                 | 46         |

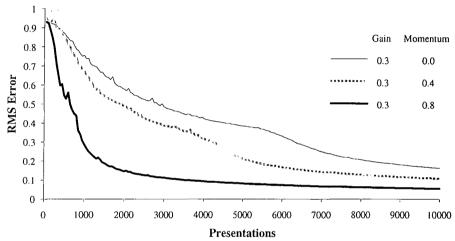

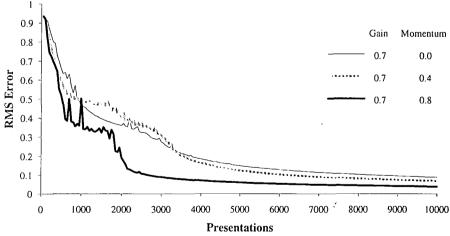

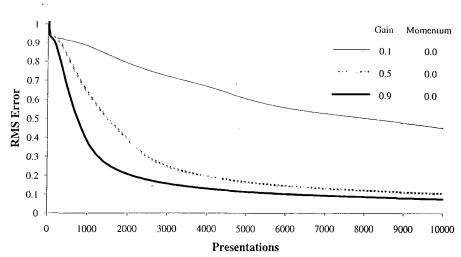

| 2.8  | Error curves for 8-3-8 coder/decoder MLP, Random presentation                                 | 47         |

| 2.9  | Error curves for 8–3–8 coder/decoder MLP, Random presentation                                 | 47         |

| 2.10 | Error curves for 8–3–8 coder/decoder MLP, Random presentation                                 | 47         |

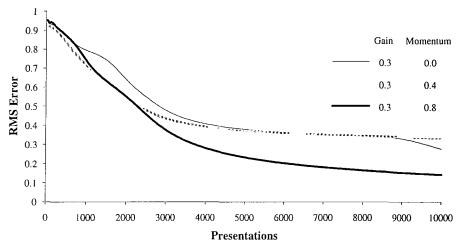

| 2.11 | Error curves for 8-3-8 coder/decoder MLP, Batch presentation                                  | 48         |

| 2.12 | Error curves for 8-3-8 coder/decoder MLP, Batch presentation                                  | 48         |

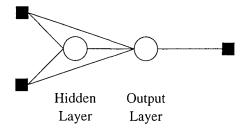

| 2.13 | Rumelhart $\mathit{et}$ $\mathit{al}$ network architecture to solve the XOR problem           | 48         |

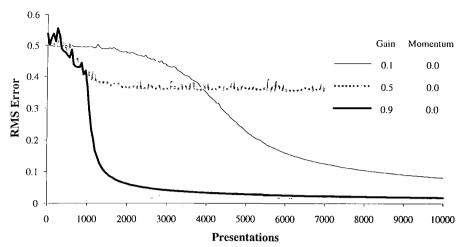

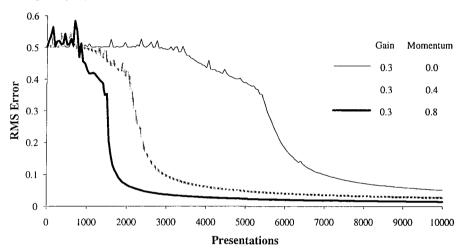

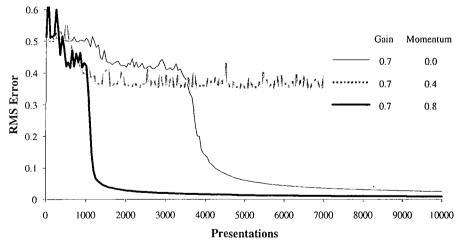

| 2.14 | Error curves for 2-2-1 XOR MLP                                                                | 49         |

| 2.15 | Error curves for 2-2-1 XOR MLP                                                                | <b>4</b> 9 |

| 2.16 | Error curves for 2–2–1 XOR MLP                                                                | 49         |

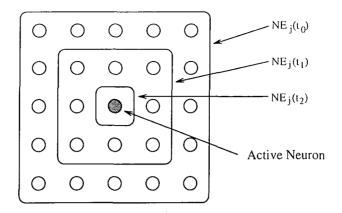

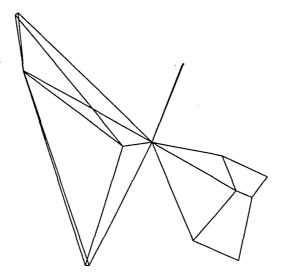

| 2.17 | Kohonen Self-Organising Feature Map Network Neighbourhood Layout, $1.$                        | 50         |

| 2.18 | Kohonen Self-Organising Feature Map Network Neighbourhood Layout, $2.$                        | 50         |

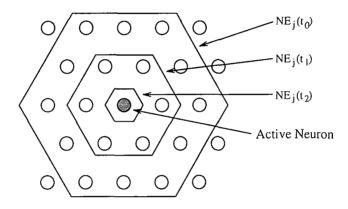

| 2.19 | Variation in Training Gain, $\eta$ , vs Distance from Active Neuron                           | 50         |

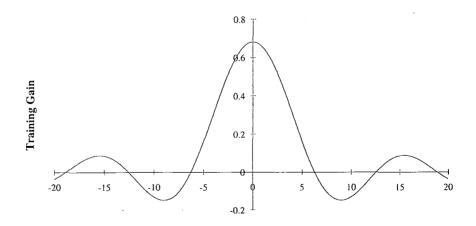

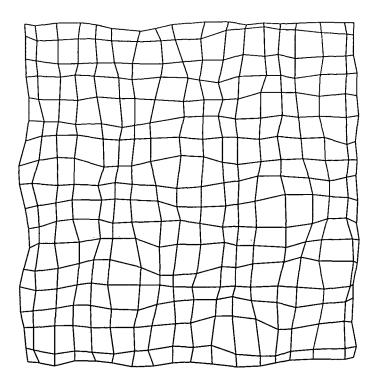

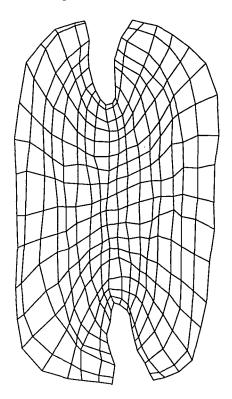

| 2.20 | Ideal Uniform 10 by 10 Mesh                                                                   | 51         |

| 2.21 | Kohonen Self-Organising Layer, 10 iterations                                                  | 51         |

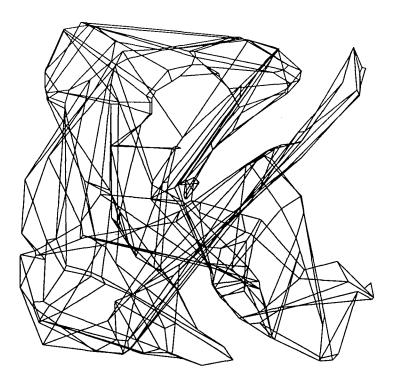

| 2.22 | Kohonen Self-Organising Layer, 1000 iterations, Uniform (x,y) distribution.                   | 52         |

| 2.23 | $Kohonen \ Self-Organising \ Layer, \ 100000 \ iterations, \ Uniform \ (x,y) \ distribution.$ | 52         |

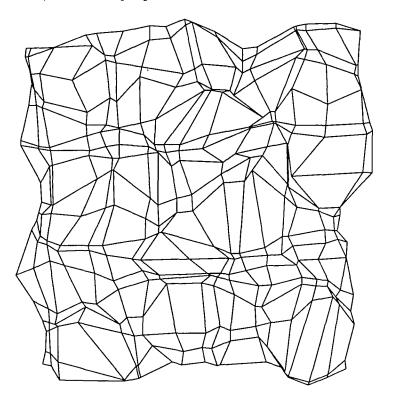

| 2.24 | Kohonen Self-Organising Layer, 300000 iterations, Uniform (x,y) distribution.                 | 53         |

| 2.25 | Kohonen Self-Organising Layer, 300000 iterations, Normal (x), Uniform (y)                     |            |

|      | distribution                                                                                  | 53         |

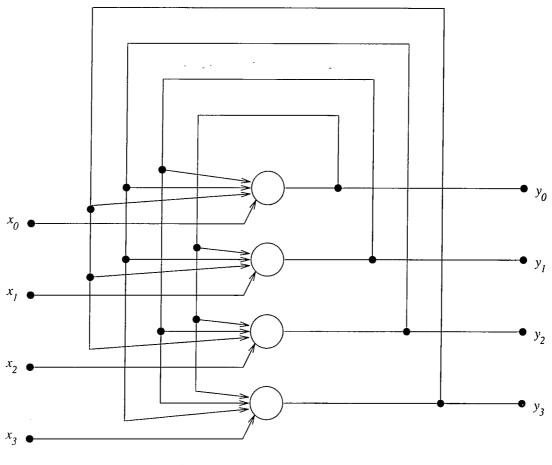

| 2.26 | General Architecture of a Hopfield Net, four neurons                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 54 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

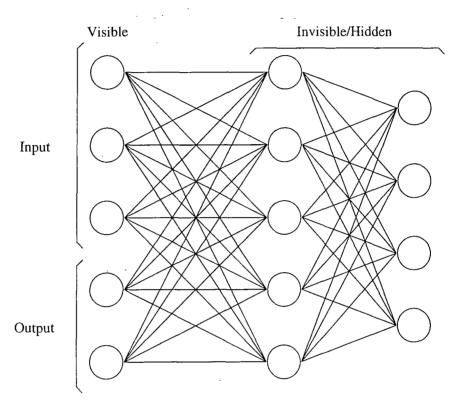

| 2.27 | General Architecture of a Boltzmann Machine.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 55 |

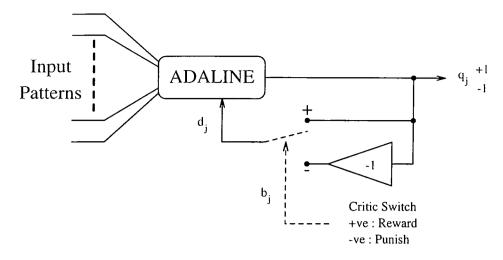

| 2.28 | Criticised ADALINE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 56 |

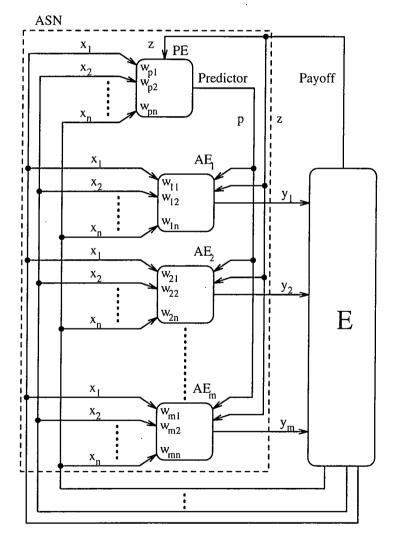

| 2.29 | Associative Search Network Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 56 |

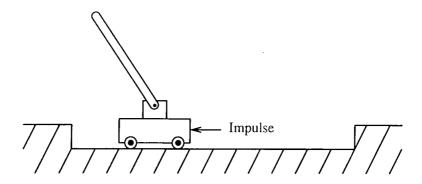

| 2.30 | Cart-Pole balancing system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 57 |

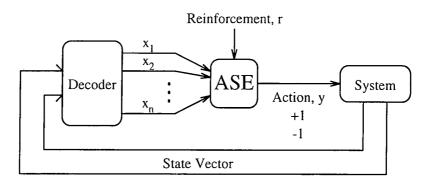

| 2.31 | Associative Search Element (ASE) configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 57 |

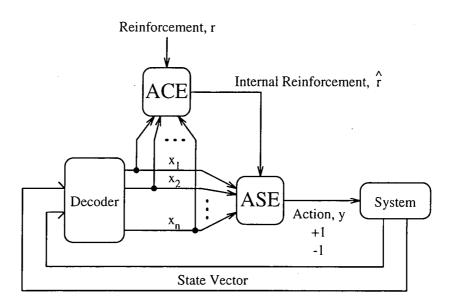

| 2.32 | Associative Search Element with Adaptive Critic Element (ACE) Configu-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

|      | ration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 57 |

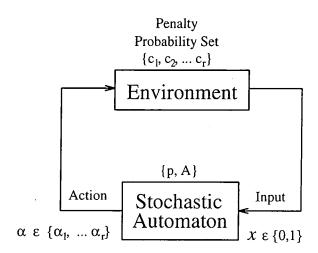

| 2.33 | Learning Automaton                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 58 |

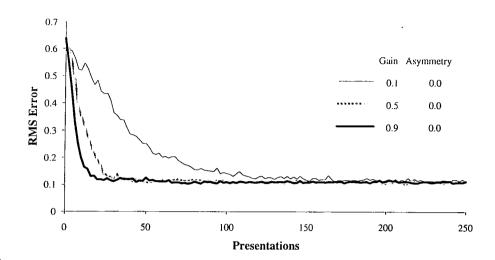

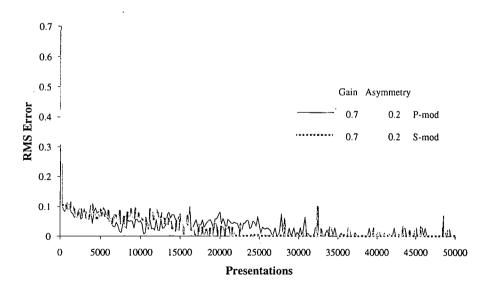

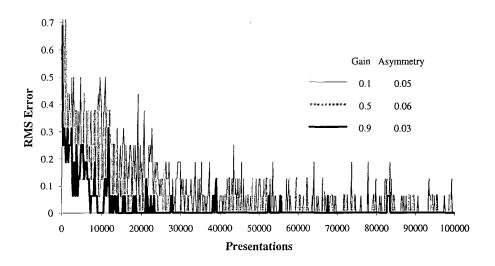

| 2.34 | Initial adaption rate for 8–3–8 encoder/decoder P-model $A_{R-P}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 59 |

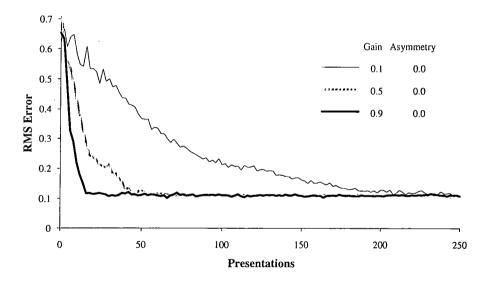

| 2.35 | Initial adaption rate for 8–3–8 encoder/decoder S-model $A_{R-P}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 59 |

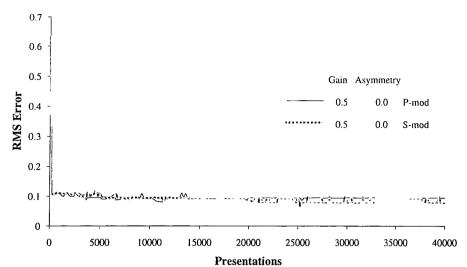

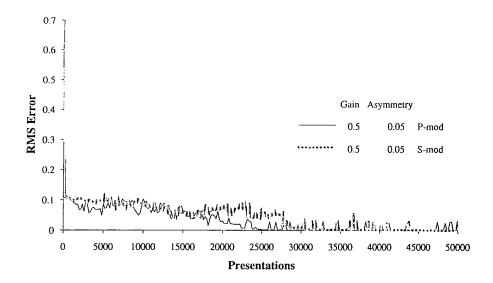

| 2.36 | Long term adaption for 8–3–8 encoder/decoder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 60 |

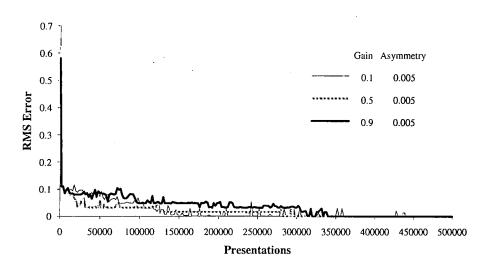

| 2.37 | Long term adaption for 8–3–8 encoder/decoder with $\lambda > 0.$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 60 |

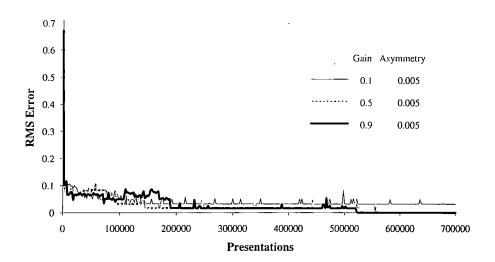

| 2.38 | Long term adaption for 8–3–8 encoder/decoder with small $\lambda$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 61 |

| 2.39 | XOR learning P-model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 61 |

| 2.40 | XOR learning S-model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 62 |

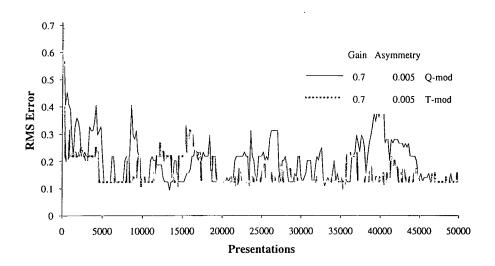

| 2.41 | Poor learning of 8–3–8 by Q and T models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 62 |

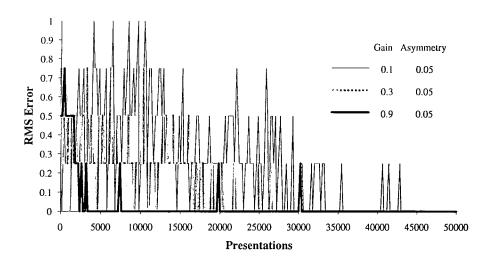

| 2.42 | Q-model XOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 63 |

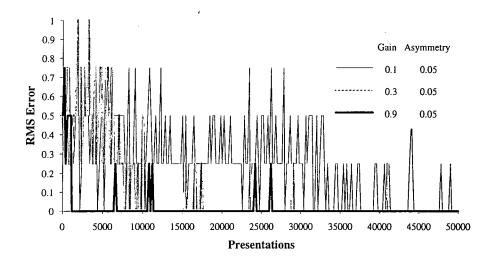

| 2.43 | T-model XOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 63 |

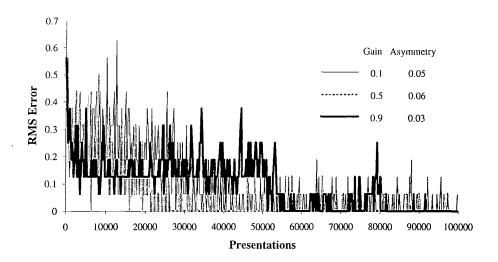

| 2.44 | Q-model learning for the 4-2-4 encoder/decoder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 64 |

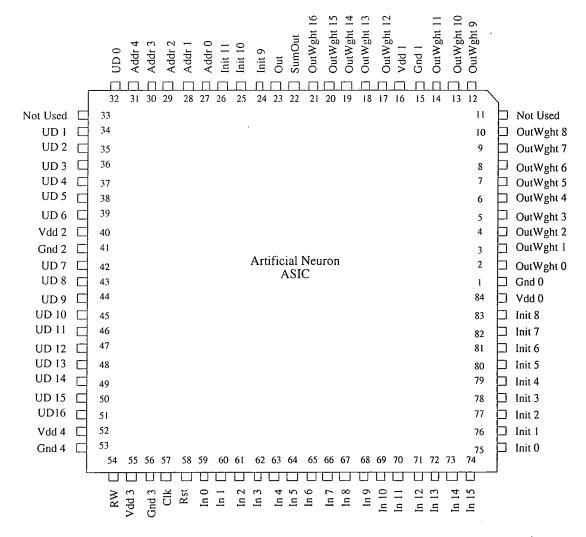

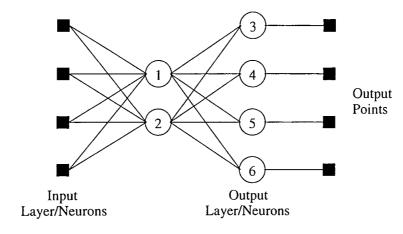

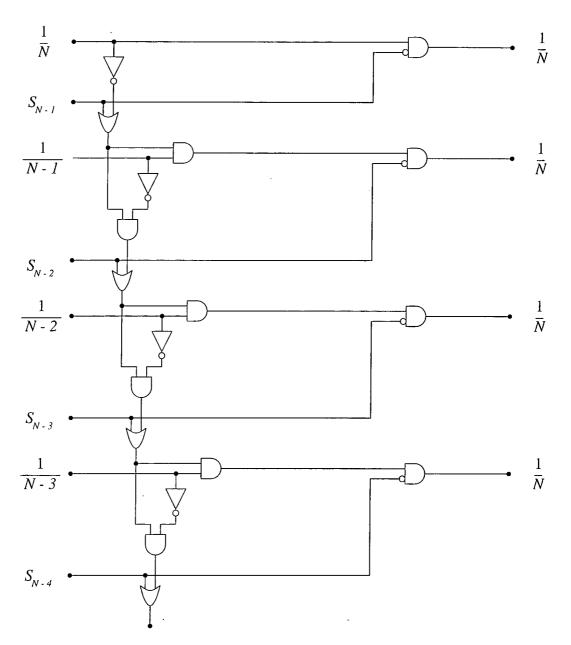

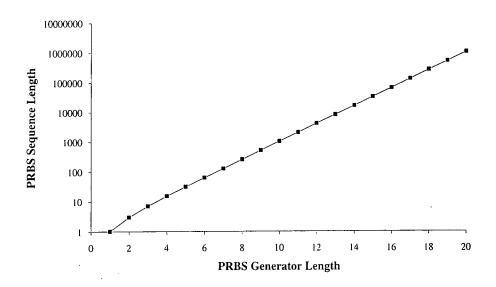

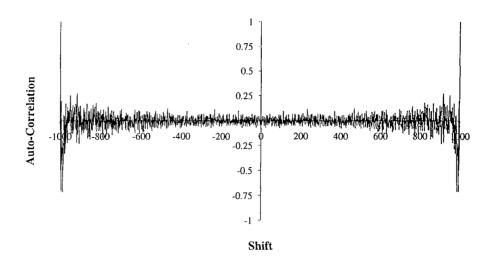

| 2.45 | T-model learning for the 4-2-4 encoder/decoder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 64 |