## Study of Organic Molecules and Nano-Particle/Polymer Composites for Flash Memory and Switch Applications

by

Sarah Paydavosi

B.Sc., Electrical Engineering, University of Tehran 2005

M.Sc., Electrical Engineering, University of Tehran 2007

M.Sc., Electrical Engineering, Massachusetts Institute of Technology 2011

Submitted to the Department of Electrical Engineering and Computer Science

in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy in Electrical Engineering

at the

Massachusetts Institute of Technology

MASSACHUSETTS INSTITUTE OF TECHNOLOGY JUL 0 1 2012 LIBRARIES

ARCHIVES

© 2012 Massachusetts Institute of Technology All rights reserved

June 2012

Signature of Author ...... Department of Electrical Engineering and Computer Science April 27, 2012 //  $\Lambda$ Certified by ..... Vladimir Bulović **Professor of Electrical Engineering** Thesis Supervisor . 1 Accepted by ..... Leslie A. Kolodziejski

Professor of Electrical Engineering Chair, Department Committee on graduate Students

#### Study of Organic Molecules and Nano-Particle/polymer Composites for Flash

#### **Memory and Switch Applications**

By

Sarah Paydavosi

Submitted to the Department of Electrical Engineering and Computer Science on April 27, 2012 in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy in Electrical Engineering and Computer Science

#### Abstract

Organic materials exhibit fascinating optical and electronic properties which motivate their hybridization with traditional silicon-based electronics in order to achieve novel functionalities and address scaling challenges of these devices. The application of organic molecules and nano-particle/polymer composites for flash memory and switch applications is studied in this dissertation.

Facilitating data storage on individual small molecules as the approach the limits in miniaturization for ultra-high density and low power consumption media may enable orders of magnitude increase in data storage capabilities. A floating gate consisting of a thin film of molecules would provide the advantage of a uniform set of identical nano-structured charge storage elements with high molecular area densities which can result in a several-fold higher density of charge-storage sites as compared to quantum dot (QD) memory and even SONOS devices. Additionally, the discrete charge storage in such nano-segmented floating gate designs limits the impact of any tunnel oxide defects to the charge stored in the proximity of the defect site. The charge retention properties of molecular films was investigated in this dissertation by injecting charges via a biased conductive atomic force microscopy (AFM) tip into molecules comprising the thin films. The Kelvin force microscopy (KFM) results revealed minimal changes in the spatial extent of the charge trapping over time after initial injection. Fabricated memory capacitors show a device durability over 10<sup>5</sup> program/erase cycles and hysteresis window of up to 12.8 V, corresponding to stored charge densities as high as  $5.4 \times 10^{13}$  cm<sup>-2</sup>, suggesting the potential use of organic molecules in high storage capacity memory cells. Also, these results demonstrate that charge storage properties of the molecular trapping layer can be engineered by rearranging molecules and their  $\pi$ -orbital overlaps via addition of dopant molecules.

Finally, the design, fabrication, testing and evaluation of a MEMS switch that employs viscoelastic organic polymers doped with nano-particles as the active material is presented in this dissertation. The conductivity of the nano-composite changes 10,000-fold as it is mechanically compressed. In this demonstration the compressive squeeze is applied with electric actuation. Since squeezing initiates the switching behavior, the device is referred to as a "squitch". The squitch is essentially a new type of FET that is compatible with large area processing with printing or photolithography, on rigid or flexible substrates and can exhibit large on-to-off conduction ratio.

Thesis Supervisor: Vladimir Bulović Title: Professor of Electrical Engineering

·

To my mother, a truly caring and loving soul. Her support, personal sacrifices, encouragement, and constant love have sustained me throughout my life.

To my dear father, who has been my role-model for hard work and persistence, who has been proud of my work and has been supportive throughout my life.

To Shahriyar, my dear and loving husband, who instilled in me the inspiration to set high goals and the confidence to achieve them, and who has shared the many uncertainties, challenges and sacrifices for completing this dissertation.

#### Acknowledgments

This work would not have been possible without the support of many talented people and organizations.

First of all, I would like to thank my research supervisor, Prof. Vladimir Bulovic for all his guidance, encouragement, support, and patience throughout the completion of this dissertation. I feel very fortunate for the opportunity to have him as my research advisor.

I'm infinitely grateful to my dissertation committee members, Prof. Jeffery H. Lang and Prof. Judy L. Hoyt for their very helpful insights, comments and suggestions. I would also like to thank Prof. Dimitri Antoniadis for his thoughtful comments.

I am thankful to my fellow lab members past and present who have taught me so much. It was a pleasure to work in such a friendly, multi-cultural working environment. Specifically, I would like to thank Dr. Pouya Hashemi for all his help and for being a good friend for me; Dr. Katherine Aidala, Dr. Timothy P. Osedach, Patrick Brown, Dr. Ivan Nausieda, Dr. Polina Anikeeva, Dr. Osama Nayfeh, Hassen Abdu, Dr. Corinne Packard, Dr. Elizabeth Young, Dr. Alexi Arango, Yasu Shirasaki, Geoffrey Supran, Dr. Trisha Andrew, Apoorva Murarka, Jill Rowehl, Dr. Annie Wang, Farnaz Niroui, Dr. Burag Yaglioglu, Dr. Matt Panzer, Gleb Akselrod and everyone else in the Laboratory of Organic and Nanostructured Electronics (ONE lab).

Additionally, I would like to acknowledge the staff at MIT Microsystems Technology Laboratories for their technical support and assistance including Vicky Diadiuk, Paul Tierney, Bernard Alamariu, Eric S. Lim, Robert Bicchieri, Donal Jamieson, Paudely Zamora, Kurt Broderick, and Dennis Ward.

I am also thankful to the staffs at Department of Material Science and Engineering of MIT specially Dr. Yong Zhang, for training me on TEM and spending long hours helping me with sample preparation and TEM imaging. I would also like to express my gratitude to Mrs. Monica Pegis. She has always ensured that all the administrative hurdles were handled in time.

I am enormously grateful to my family. I am forever indebted to my parents for their understanding, endless love, patience and support. I'm truly thankful to my brother, Navid, a passionate learner, in whose footsteps I follow as an educational leader, for his invaluable guidance and for his psychological, and intellectual support and to my dear sisters, Fahimeh, Naeemeh and Maryam who have been my emotional anchors through not only the vagaries of graduate school, but my entire life.

I would like to express my sincere and very special gratitude to my husband, Shahriyar, for his unconditional love and constant support.

## Contents

| List of I | Figures                                                                 | 13 |

|-----------|-------------------------------------------------------------------------|----|

| List of 7 | Гables                                                                  | 25 |

| Chapter   | r 1                                                                     | 27 |

| Disserta  | ntion Motivation and Outline                                            | 27 |

| 1-1       | Molecular charge storage elements                                       |    |

| 1-2       | MEMS Switches Employing Active Metal-Polymer Nano-Composites            |    |

| Chapter   | r 2                                                                     | 33 |

| Introdu   | ction to Flash Memory                                                   | 33 |

| 2.1       | Memory Industry and Applications                                        |    |

| 2.2       | Flash Memory Structure                                                  |    |

| 2.3       | Types of Flash Memory                                                   |    |

| 2.4       | Program and erase mechanisms                                            |    |

| 2.5       | Flash memory Reliability                                                |    |

| 2.6       | Future Scaling Challenges                                               | 50 |

| 2.7       | Segmented Floating Gate memories                                        |    |

| 2.8       | Summary                                                                 |    |

| Chapter   | r 3                                                                     | 63 |

| Molecu    | lar Floating Gate Memory                                                | 63 |

| 3.1       | Introduction to Organic Molecular Floating gate Memories                | 64 |

| 3.2       | Molecular Floating Gate Capacitors                                      | 65 |

| 3.3       | Chapter Summary                                                         | 95 |

| Chapter   | r 4                                                                     | 97 |

| Detectio  | on of Charge Storage on Molecular Thin Films by Kelvin Force Microscopy | 97 |

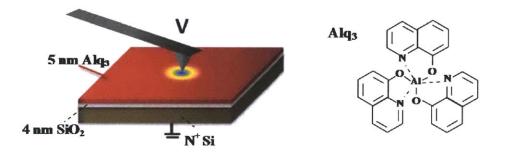

| 4.1       | Tris(8-hydroxyquinoline) aluminum (Alq <sub>3</sub> ) Molecules         | 97 |

|     | 4.2   | Scanning Probe Microscopy (SPM)                                      |     |

|-----|-------|----------------------------------------------------------------------|-----|

|     | 4.3   | Direct Detection of Charge Storage within Alq <sub>3</sub> Molecules |     |

|     | 4.4   | Charge Storage on C <sub>60</sub> Molecules                          |     |

|     | 4.5   | Chapter Summary                                                      |     |

| Cha | apte  | r 5                                                                  | 129 |

| Adj | justi | ng the Memory Properties of the Molecules                            | 129 |

|     | 5.1   | Origin of Charge Transport in Organic Semiconductors                 |     |

|     | 5.2   | C <sub>60</sub> and PTCBI Memory Capacitors                          |     |

|     | 5.3   | Mobility measurements                                                |     |

|     | 5.4   | PTCBI/C <sub>60</sub> Memory Capacitor                               |     |

|     | 5.5   | Conclusion                                                           |     |

| Cha | apte  | r 6                                                                  | 149 |

| ME  | MS    | Switches Employing Active Metal-Polymer Nanocomposites               | 149 |

|     | 6.1   | Introduction                                                         |     |

|     | 6.2   | Elastomeric Materials                                                |     |

|     | 6.3   | Metal-Polymer Nanocomposite                                          |     |

|     | 6.4   | Squitch Fabrication                                                  |     |

|     | 6.5   | Test Results                                                         | 161 |

|     | 6.6   | Modeling of the Device                                               | 164 |

|     | 6.7   | Discussion & Conclusions                                             | 166 |

| Cha | apte  | r 7                                                                  | 169 |

| 7.1 | Su    | mmary and Suggestions, Molecular Flash memories                      | 169 |

|     | 7.2   | Summary and Suggestions, Squitch                                     |     |

|     | 7.2.  | 2 Possible Future Directions                                         |     |

|     | 7-3   | Contributions                                                        |     |

| Арр | pend  | lix A                                                                | 185 |

| Арр | pend  | lix B                                                                | 187 |

| Fab | orica | tion of Memory Transistors Using Gate-Last Fabrication Process       |     |

| Appendix C                                            |     |

|-------------------------------------------------------|-----|

| Studying the Effect of Annealing on Organic Molecules |     |

| Appendix D                                            | 196 |

| Sample Preparation for TEM Cross Section Imaging      | 196 |

| Appendix E                                            | 199 |

| Electrostatic Actuators and Pull-in                   | 200 |

| Appendix F                                            |     |

| Patents and Publications                              |     |

| Bibliography                                          |     |

## **List of Figures**

| Figure 2-1: (a) Schematic cross section of conventional flash memory; (b) Flash memory energy                   |

|-----------------------------------------------------------------------------------------------------------------|

| band diagram; (c) Threshold voltage shift during programming and erasing                                        |

| Figure 2-2: Schematic cross section and energy band diagram of conventional flash memory                        |

| during programming and erasing                                                                                  |

| Figure 2-3: Schematic cross-sections and circuit diagrams for NOR and NAND flash memory.                        |

| In NOR memory, the basic unit is one memory transistor. For NAND memory, the                                    |

| basic unit is 16 memory and 2 select transistors [12]. (WL: wordline; SG(D): select                             |

| gate drain; SG(S): select gate source)                                                                          |

| Figure 2-4: Writing mechanism in floating-gate devices [11, 36]                                                 |

| <b>Figure 2-5:</b> Rectangular potential barrier in insulating film between metal electrodes for V> $\varphi_0$ |

| /e                                                                                                              |

| Figure 2-6: FN tunneling current as a function of electric field [10]                                           |

| Figure 2-7: (a) The MOS capacitor structure. The substrate (body) is grounded and a voltage                     |

| $V_{GB}$ is applied to the gate; (b) Capacitance vs. gate voltage (C-V) diagram of a MOS                        |

| Capacitor. The flatband voltage $(V_{FB})$ separates the Accumulation region from the                           |

| Depletion regime. The threshold voltage $(V_T)$ separates the depletion regime from                             |

| the inversion regime [38] 43                                                                                    |

| Figure 2-8: Schematic representation of P-MOS structure under bias resulting in accumulation                    |

| mode, (a) biasing condition, (b) charge distribution, (c) energy band diagram [39]. 44                          |

| Figure 2-9: Schematic representation of P-MOS structure under bias resulting in depletion                       |

mode, (a) biasing condition, (b) charge distribution, (c) energy band diagram...... 45

Figure 2-10: Schematic representation of P-MOS structure under bias resulting in inversion mode, (a) biasing condition, (b) charge distribution, (c) energy band diagram [39].

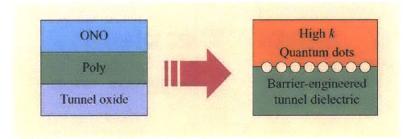

Figure 2-16: High-level depiction of floating-gate transistor improvement. The ONO dielectric in the traditional transistor (left) is replaced by a high-k insulating dielectric (right). A floating-gate (poly in the diagram) is replaced by either floating [12]. 55

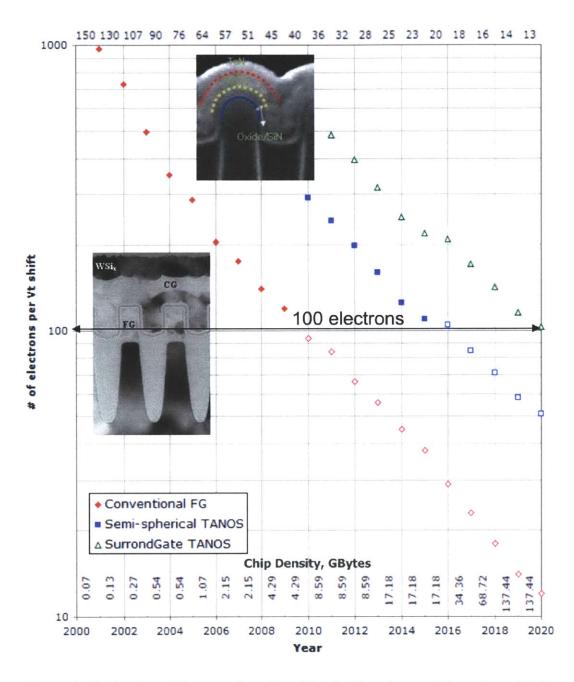

Figure 2-19: Number of Electrons Stored in a Floating Gate (source: Chung Lam, IBM)...... 59

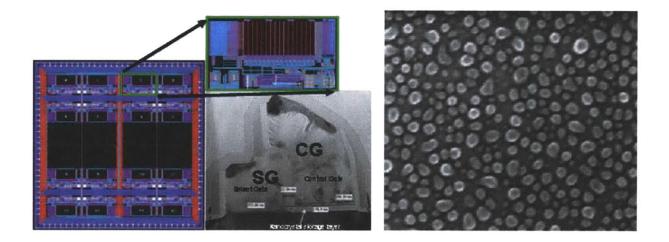

| Figure2-20: | Segmented floating gate with | 10-15 nm in diameter | nanocrystals (source:freescale). |

|-------------|------------------------------|----------------------|----------------------------------|

|             |                              |                      |                                  |

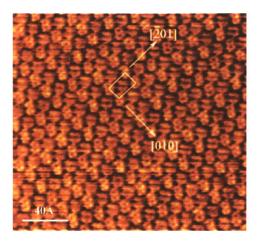

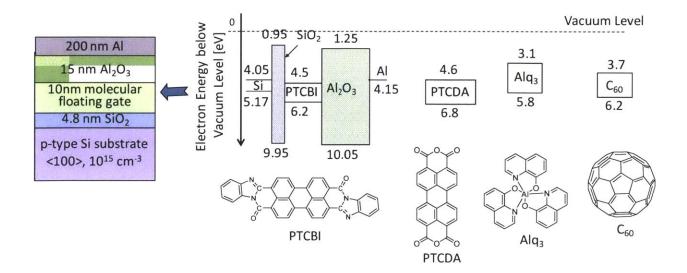

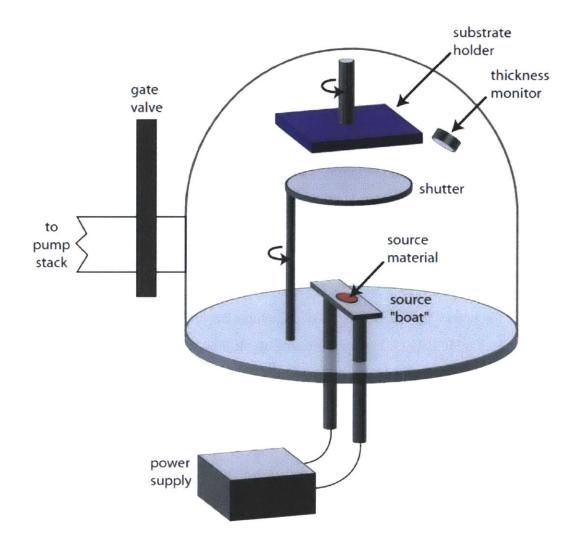

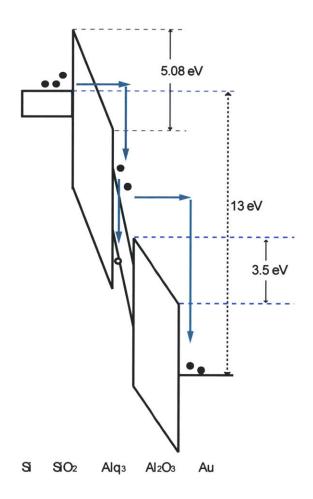

- Figure 3-2: (a) The schematic cross-section of the device structure; (b) Suggested energy-band diagrams of four different organic memory devices with chemical structure of each material (energy values are in eV). The terms for organic HOMO and LUMO are analogous to valence and conductive bands used for inorganic solid state physics. According to this analogy electrons or negative charges are mobile across the LUMO level, while holes or positive charges are mobile across the HUMO level.

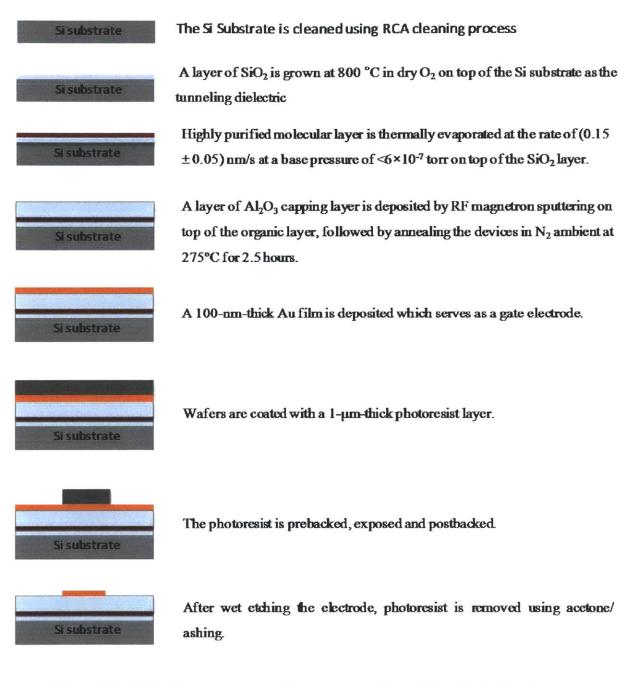

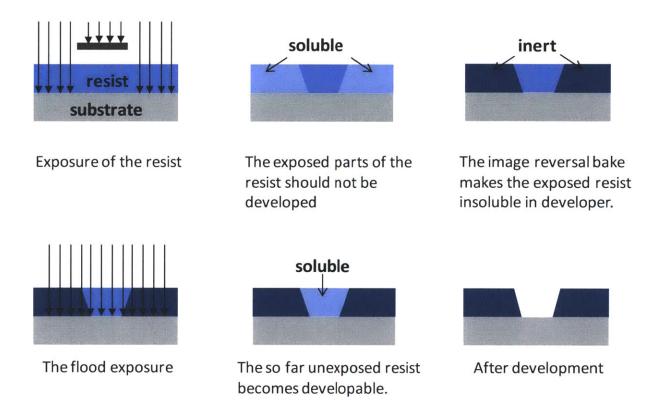

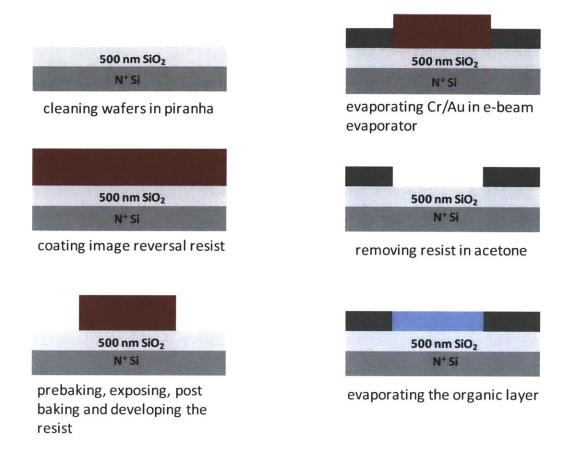

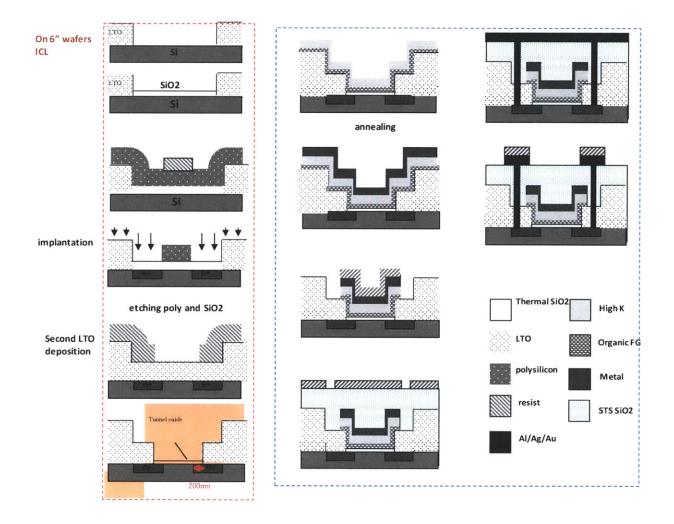

- Figure 3-4: Fabrication process steps of memory capacitors with molecular floating gate. ..... 69

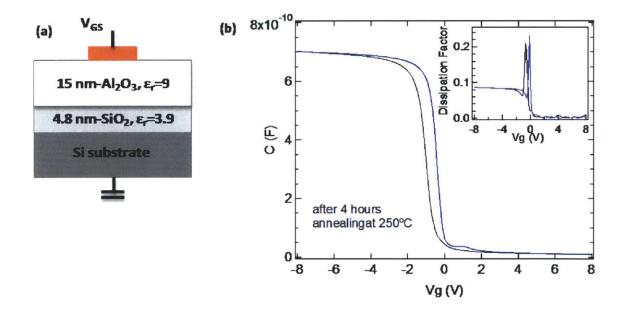

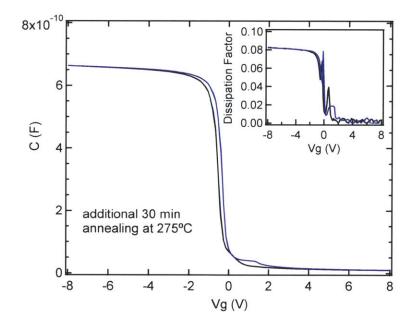

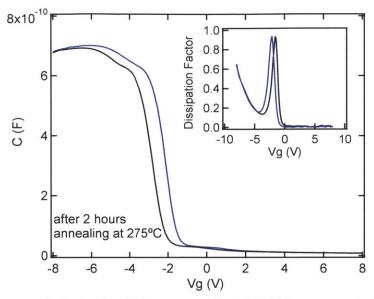

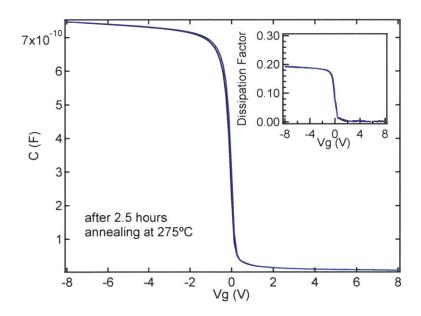

- Figure 3-7: Capacitance and dissipation factor measured at 100 kHz versus gate bias. MOS capacitors were annealed at 250°C for 4 hours and then at 275 °C for 30 min..... 72

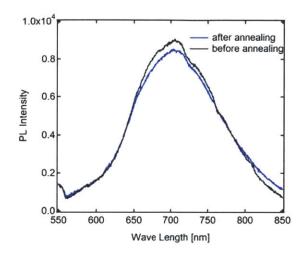

| Figure 3-10: | Photoluminescence spectra of PTCDA; before and after annealing74                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

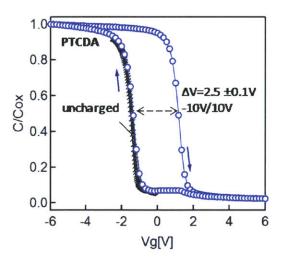

| Figure 3-11: | The $C$ - $V$ characteristics of memory devices with a 10nm thick layer of PTCDA. 75                                                                                                                                                                                                                                                                                                                                                                                                                                |

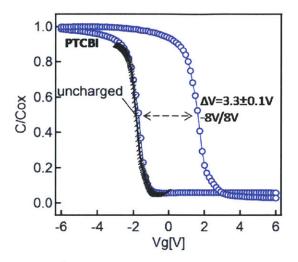

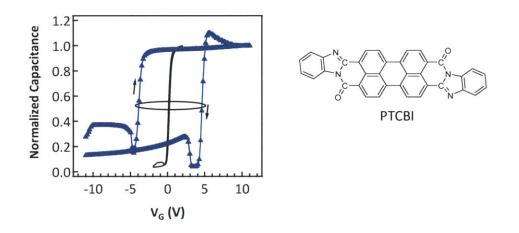

| Figure 3-12: | The $C-V$ characteristics of memory devices with a 10nm thick layer of PTCBI 76                                                                                                                                                                                                                                                                                                                                                                                                                                     |

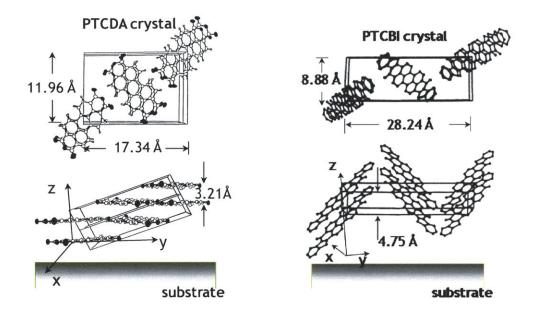

| Figure 3-13: | Perspective views of a PTCBI and PTCDA unit cell [48]77                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

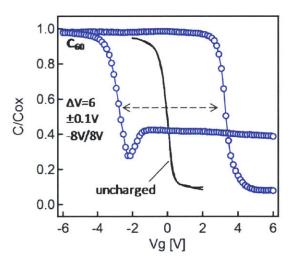

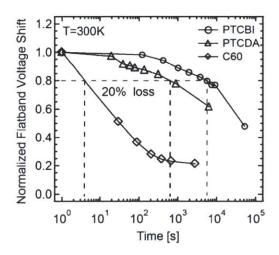

| Figure 3-14: | The <i>C</i> - <i>V</i> characteristics of memory devices with a 10 nm thick layer of $C_{60}$ 77                                                                                                                                                                                                                                                                                                                                                                                                                   |

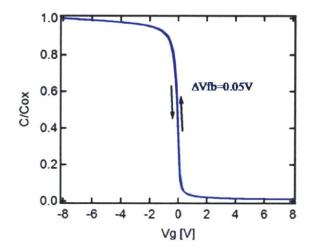

| Figure 3-15: | The $C$ - $V$ characteristics of a control device without organic layer measured in the - 8 V/8 V sweep range                                                                                                                                                                                                                                                                                                                                                                                                       |

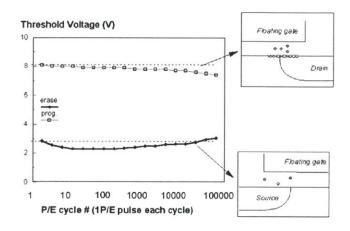

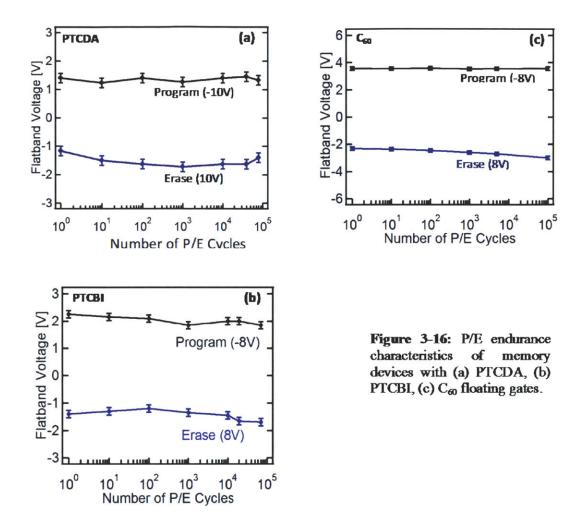

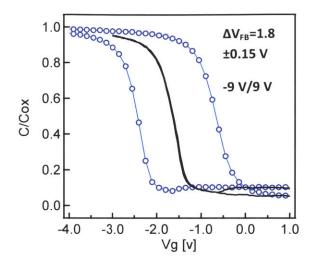

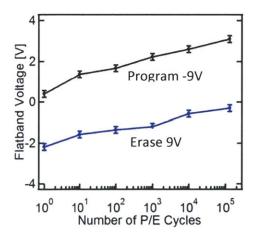

| Figure 3-16: | P/E endurance characteristics of memory devices with (a) PTCDA, (b) PTCBI, (c) C <sub>60</sub> floating gates                                                                                                                                                                                                                                                                                                                                                                                                       |

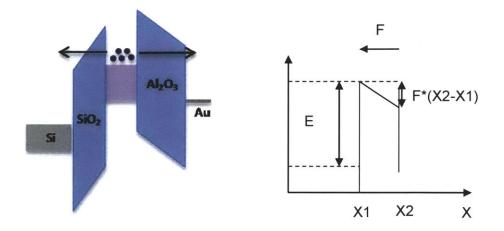

| Figure 3-17: | Schematic of the trapezoidal energy barrier in data retention mode                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Figure 3-18: | Simulation of normalized retention characteristics for (a) a memory device with polysilicon floating gate with different tunneling oxides of 6 nm, 3 nm and 2.5 nm; (b) Charge retention comparison of polysilicon flash memories with memories with higher effective mass like organic materials. The devices were assumed to be programmed with the stored charge density of 10 <sup>13</sup> cm <sup>-2</sup> and only charge loss mechanism through direct tunneling has been considered for these simulations. |

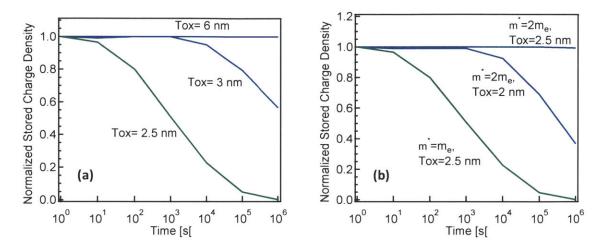

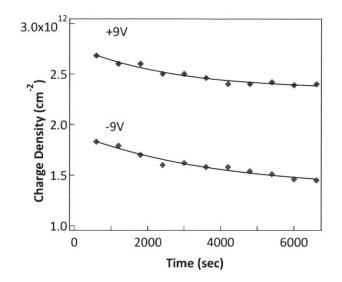

| Figure 3-19: | Normalized retention characteristics measured at room temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

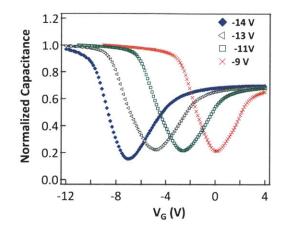

| Figure 3-20: | The C-V characteristics of memory devices with a 10nm thick layer of $Alq_3[44].85$                                                                                                                                                                                                                                                                                                                                                                                                                                 |

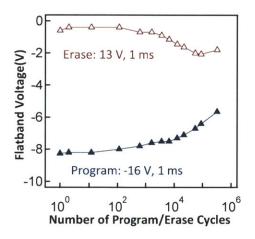

| Figure 3-21: | P/E endurance characteristics of memory devices with 10 nm Alq <sub>3</sub> floating gates.                                                                                                                                                                                                                                                                                                                                                                                                                         |

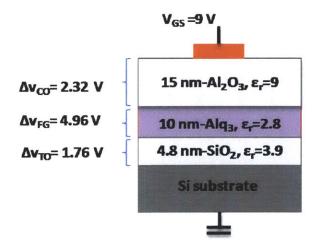

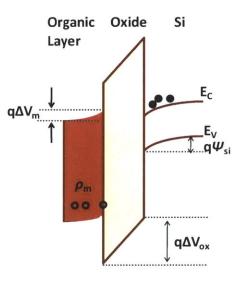

| Figure 3-22: | The schematic cross section of the device showing the voltage drop across the layers                                                                                                                                                                                                                                                                                                                                                                                                                                |

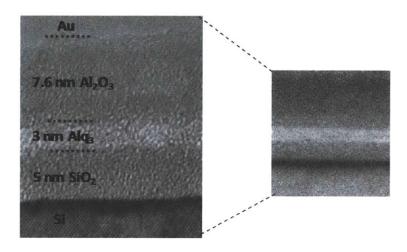

| Figure 3-23: | A transmission electron microscope cross-section image of the Alq <sub>3</sub> -containing memory                                                                                                                                                                                                                                                                                                                                                                                                                   |

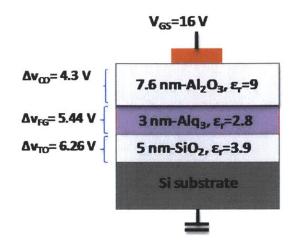

| Figure 3-24: | The schematic cross section of the device showing the voltage drop across the layers                                                                                                                                                                                                                         |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3-25: | The <i>C-V</i> characteristics of memory devices comprising a 3 nm thick layer of Alq3 (program time: 50 msec)                                                                                                                                                                                               |

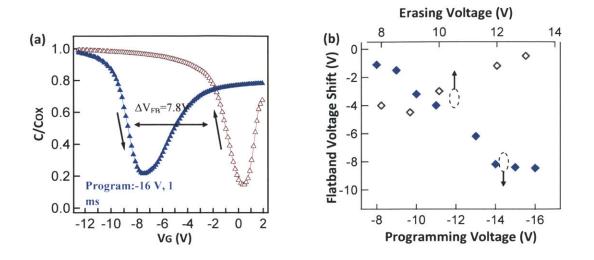

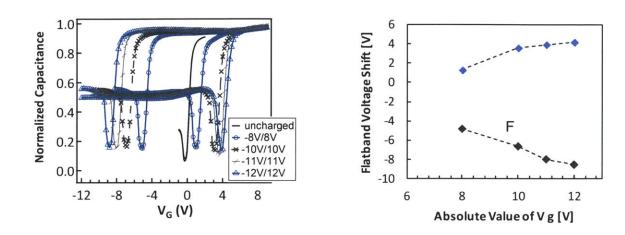

| Figure 3-26: | (a) the <i>C-V</i> characteristics with a charged (programmed) and discharged (erased) floating gate; (b) the flatband voltage shift as a function of programming/erasing voltage                                                                                                                            |

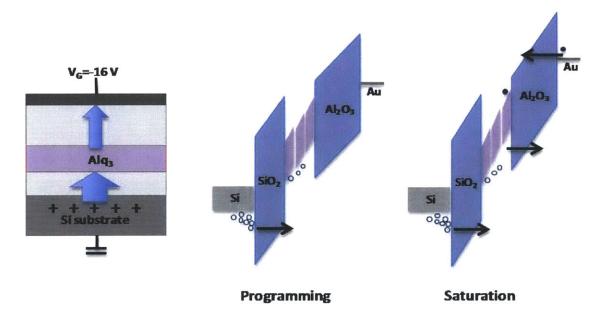

| Figure 3-27: | During –FN programming, out tunneling of the holes through the top oxide causes<br>programming saturation                                                                                                                                                                                                    |

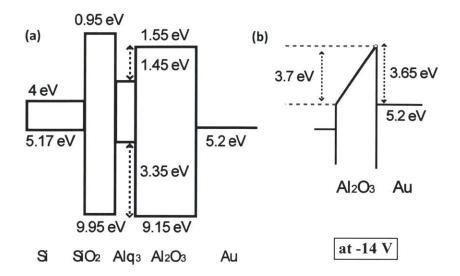

| Figure 3-28: | (a) Suggested energy band diagram for a memory device with 3-nm thick Alq <sub>3</sub> layer as the floating gate; (b) By applying larger negative bias to the top electrode, triangular energy barrier forms which causes the increased out tunneling from the floating gate and programming saturation. 92 |

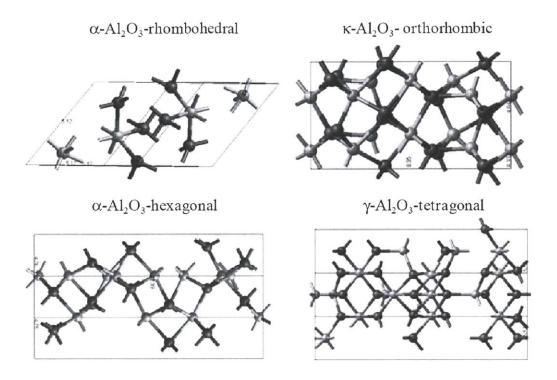

| Figure 3-29: | Illustration of the different symmetry associated to the crystal phases of $Al_2O_3$ .<br>The Al and O atoms are depicted in grey and black, respectively [62]                                                                                                                                               |

| Figure 3-30: | Suggested energy band diagram of the memory capacitor at +13 V applied to the gate electron                                                                                                                                                                                                                  |

| Figure 3-31: | Program/Erase endurance characteristics of memory capacitors with 3 nm thick Alq <sub>3</sub> floating gate                                                                                                                                                                                                  |

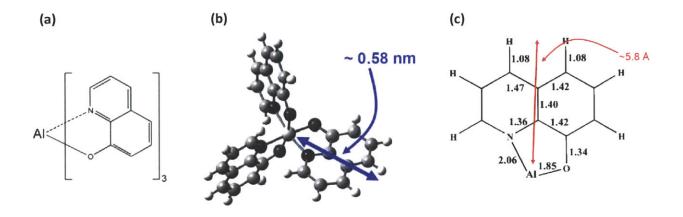

| Figure 4-1:  | (a) The structural formula for Alq <sub>3</sub> ; (b) The ball and stick representation of the mer-Alq <sub>3</sub> isomer in the ground state ; (c) Diagram of the quinolate ligand of Alq <sub>3</sub> with bond lengths indicated [50]                                                                    |

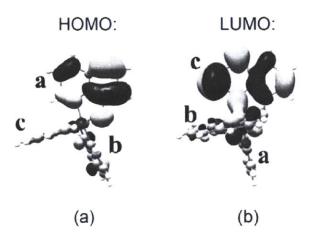

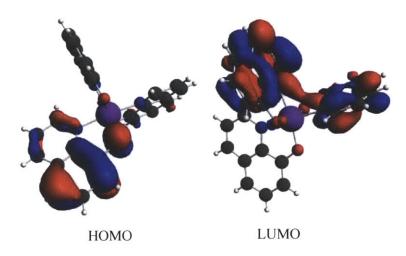

| Figure 4-2:  | HOMO (a) and LUMO (b) of Alq <sub>3</sub> [65]                                                                                                                                                                                                                                                               |

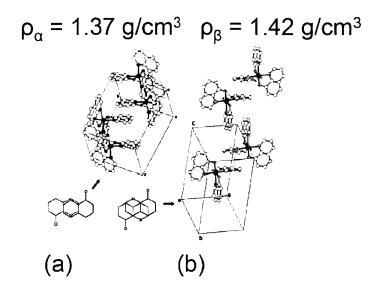

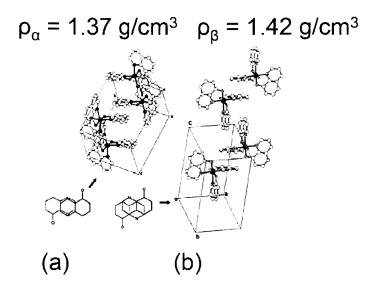

| Figure 4-3:  | Crystal structure of (a) $\alpha$ and (b) $\beta$ phases of Alq <sub>3</sub> . Both phases consist entirely of the mer-isomer. These figures are reproduced from [66]                                                                                                                                        |

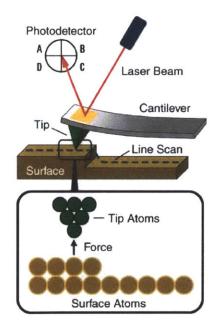

| Figure 4-4:  | Basic AFM principles [82]105                                                                                                                                                                                                                                                                                 |

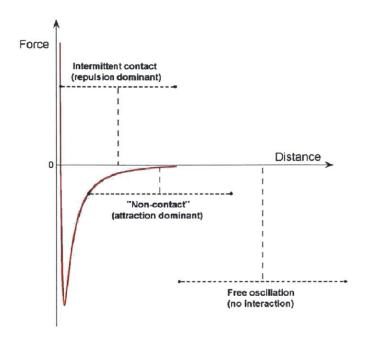

Figure 4-5: Zones of interaction as the tip approaches the sample [82]...... 105

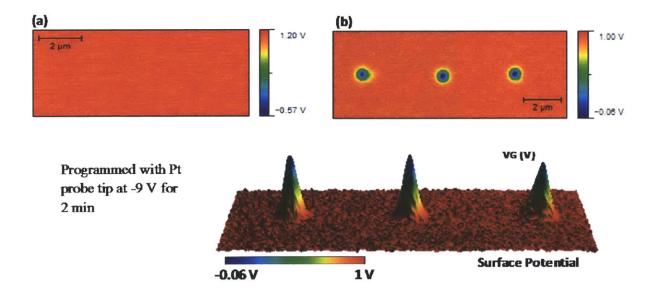

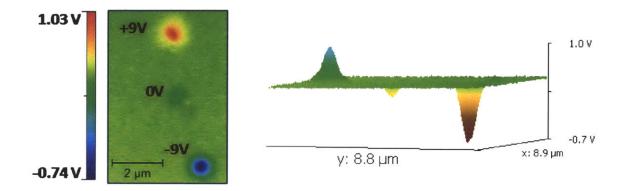

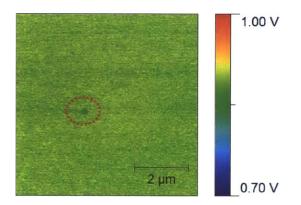

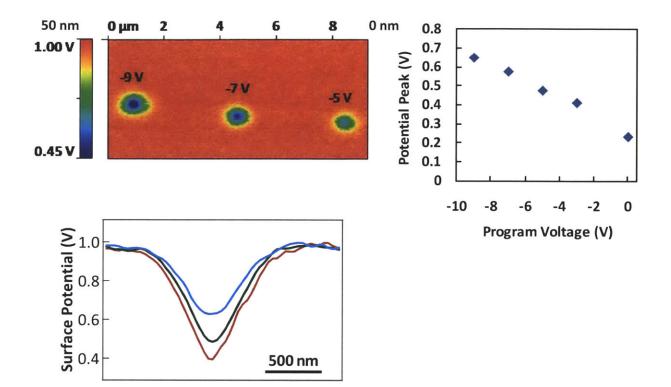

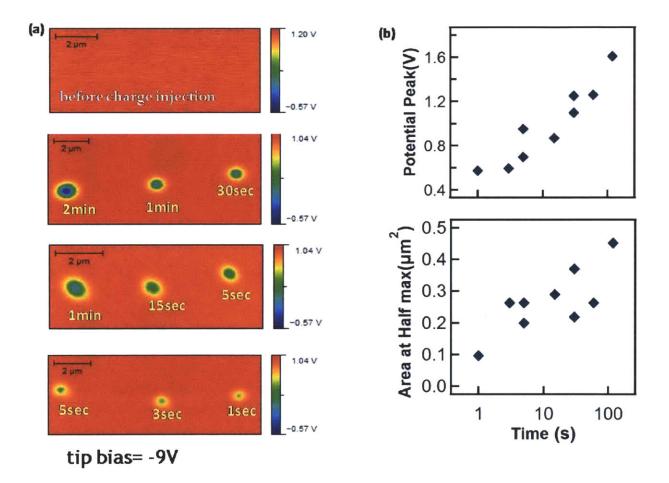

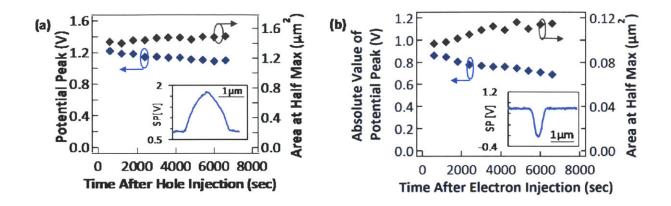

- Figure 4-11: Dependence of the amount of stored charge on tip bias (a) KFM image of charged spots created by applying different tip biases (the tip was brought into contact with the surface for 10 sec) and surface potential profiles along the line crossing the center of the spots; and (b) Potential peak and charged area at half maximum of the charged spots versus injection time; -9 V was applied to the tip during charge injection. The results revealed the increased area and maximum value for longer charging times.

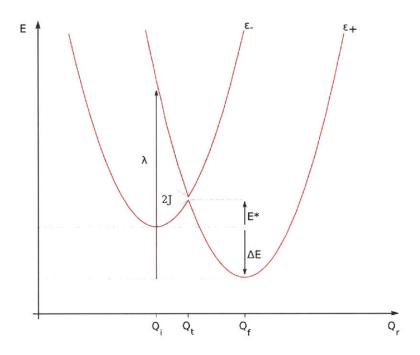

Figure 4-18: The potential energy of 2 molecules (M<sub>1</sub> and M<sub>2</sub>) are shown as a function of nuclear coordinates, where the complex multi-dimensional rearrangement of M<sub>1</sub> and M<sub>2</sub> has been reduced to the one-dimensional 'reaction coordinate' Qr [91]. 118

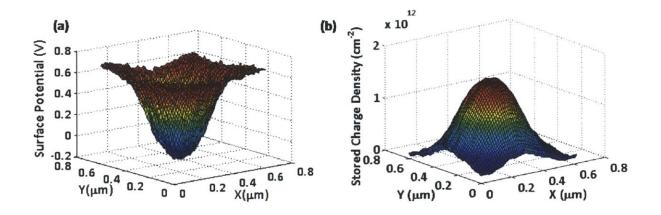

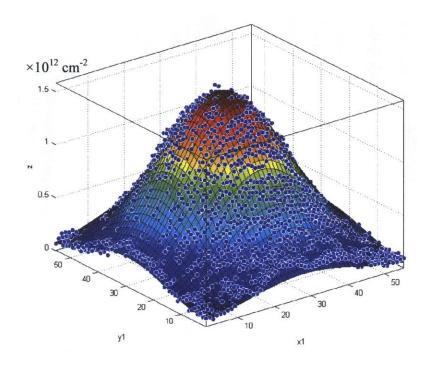

| Figure 4-20: Describing the stored charge density by fitting a Gaussian profile to the | calculated |

|----------------------------------------------------------------------------------------|------------|

| stored charge density from the surface potential                                       | 120        |

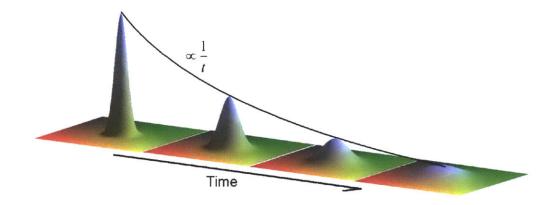

Figure 4-22: Schematic diagram of charges diffusion from their original entry point with time.

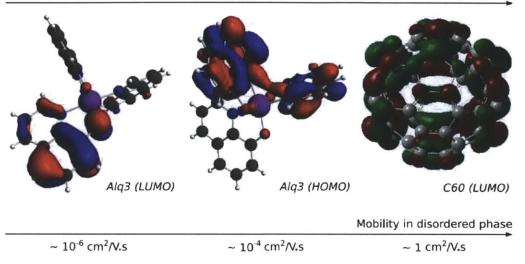

| Figure 4-25 | $C_{60}$ molecule with 60 carbon atoms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 4-26 | : The increase in symmetry of frontier orbitals is associated with an increase in charge mobility [91]                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

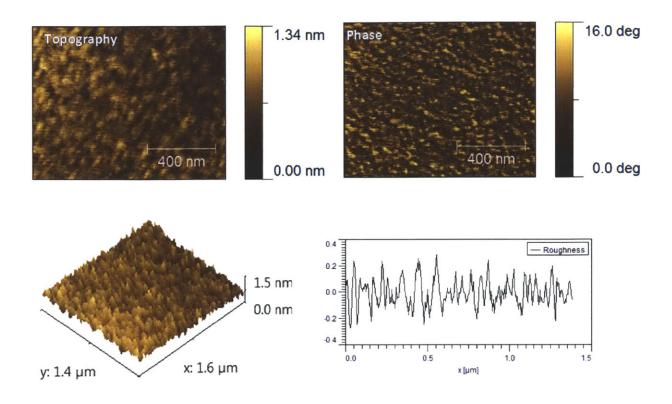

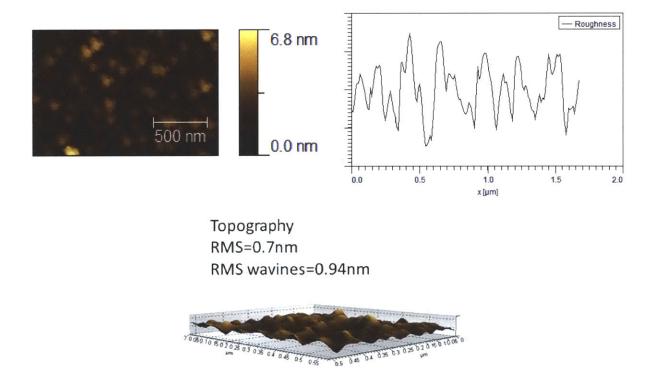

| Figure 4-27 | : AFM topography and phase images of 5 nm-thick layer of $C_{60}$ , deposited on top of a 4-nm thick layer of thermal SiO <sub>2</sub>                                                                                                                                                                                                                                                                                                                                                                                                                              |

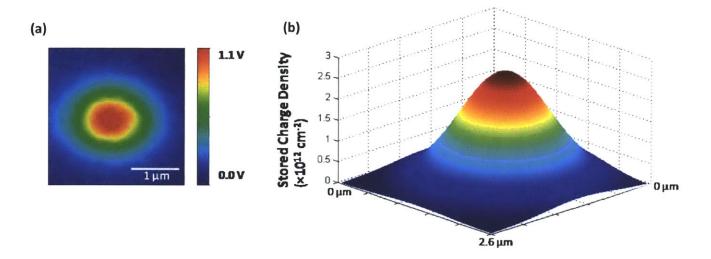

| Figure 4-28 | : (a) The KFM image of a charged spot with holes; (b) Calculated stored charge density from the surface potential                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

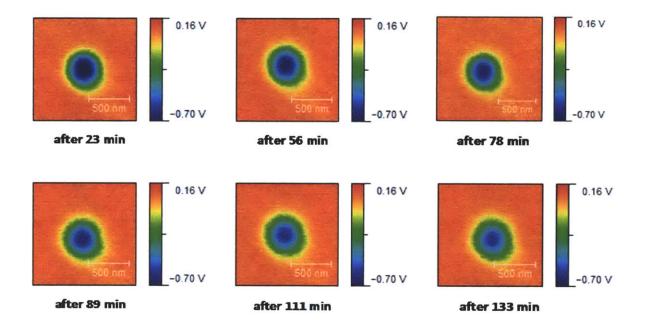

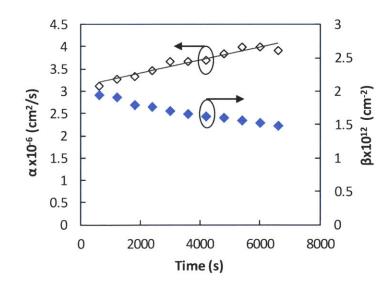

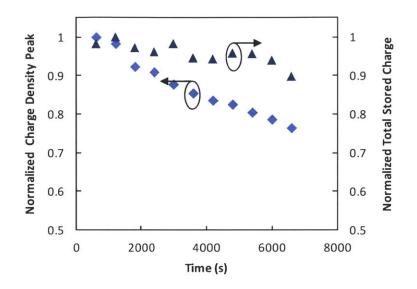

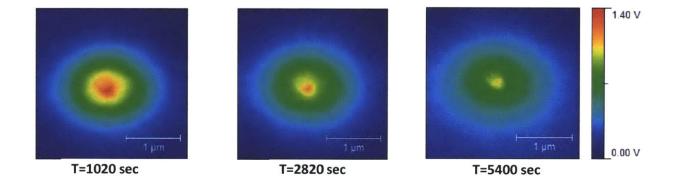

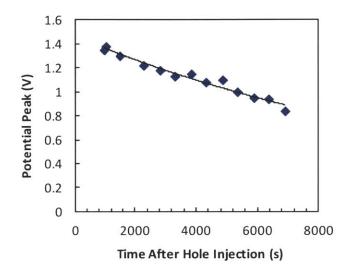

| Figure 4-29 | : KFM images of the positively charged spots over time illustrating the spreading<br>and net decrease in the surface potential change and consequently the stored<br>charges within molecules                                                                                                                                                                                                                                                                                                                                                                       |

| Figure 4-30 | The variation of potential peak with time for a positively charged spot 127                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

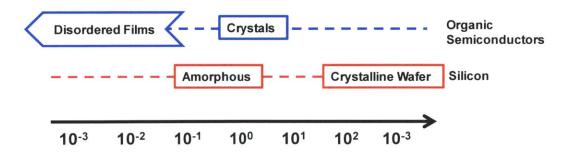

| Figure 5-1: | Mobility in organic/inorganic materials [91]130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Figure 5-2: | The increase in symmetry of frontier orbitals is associated with an increase in charge mobilities [91]                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Figure 5-3: | C <sub>60</sub> face-centered cubic (fcc) crystall                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

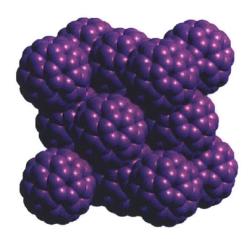

| Figure 5-4: | (a) Schematic cross section of $C_{60}$ containing memory capacitor. (b) The <i>C-V</i> characteristics of the control device without organic layer; (c) The <i>C-V</i> characteristics of $C_{60}$ -containing device, showing a large hysteresis window of 11.8 V for program /erase condition of -11 V/+11 V. (d) P/E endurance characteristic shows device durability over 10 <sup>5</sup> program/erase cycles. The high mobility and consequently low retention time of $C_{60}$ memory devices compromises their otherwise remarkable memory characteristics |

| Figure 5-5: | PTCBI containing memory capacitor shows hysteresis window of 8.4 V for forward and backward sweep between -11 V and 11 V                                                                                                                                                                                                                                                                                                                                                                                                                                            |

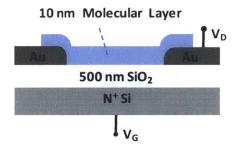

| Figure 5-6: | Schematic of bottom-gate OTFT for mobility measurement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

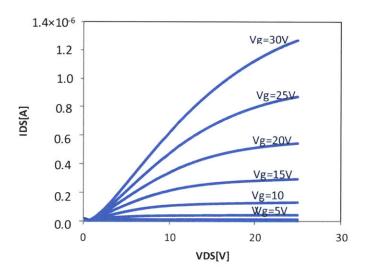

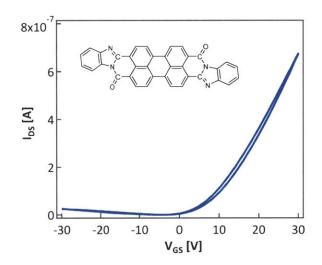

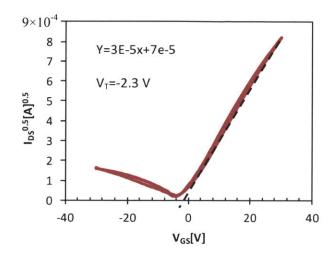

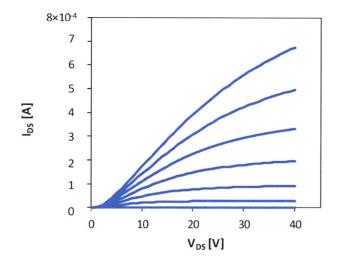

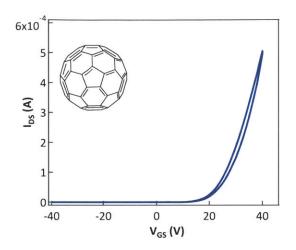

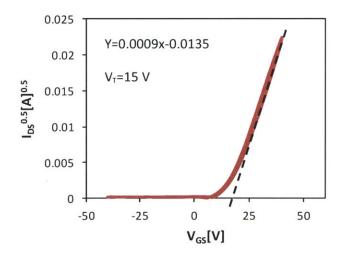

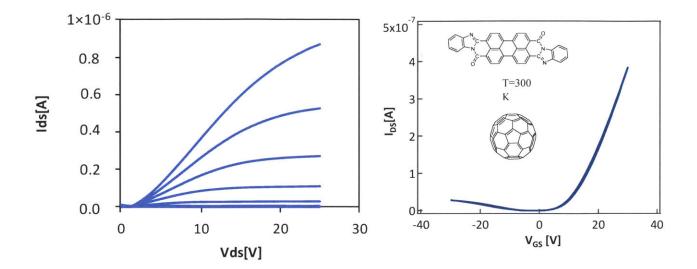

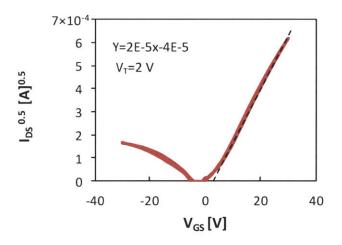

- Figure 5-14: Threshold voltage for  $C_{60}$  OTFT with silicon dioxide insulator and gold contacts was defined as  $V_T$ =15 V, by fitting linear curve to the square root of  $I_{DS}$  vs.  $V_{GS}$ where  $V_{DS}$ =40 V......143

| Figure 5-17: PTCBI: $C_{60}$ containing memory shows the hysteresis window of 11.9 V for                                                                                                                                                                                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| forward and backward sweep between -11 V and 11 V, while its lateral mobilit                                                                                                                                                                                                                                                                                                |

| has been decreased dramatically compared to $C_{60}$                                                                                                                                                                                                                                                                                                                        |

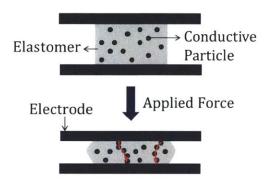

| Figure 6-1: Formation of conduction paths in metal-polymer composites when compressed. 150                                                                                                                                                                                                                                                                                  |

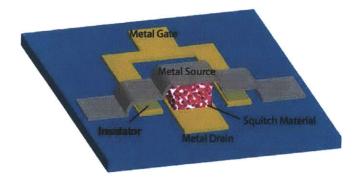

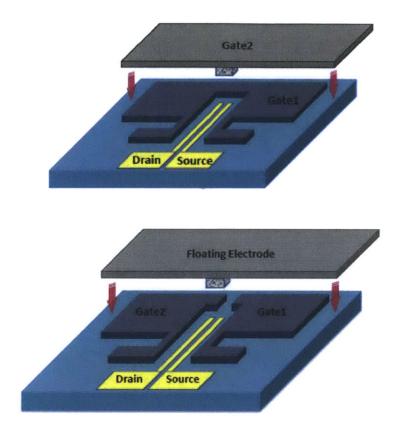

| Figure 6-2: Three-terminal "Squitch" design                                                                                                                                                                                                                                                                                                                                 |

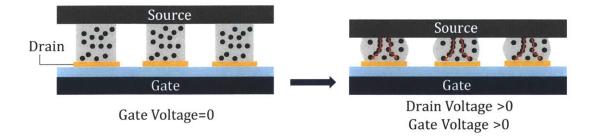

| Figure 6-3: Operation mechanism of the squitch                                                                                                                                                                                                                                                                                                                              |

| Figure 6-4: An embodiment of a two gate squitch                                                                                                                                                                                                                                                                                                                             |

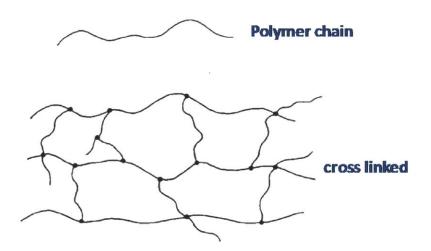

| Figure 6-5: Conceptual diagram of an elastomer's polymer chains and crosslinks                                                                                                                                                                                                                                                                                              |

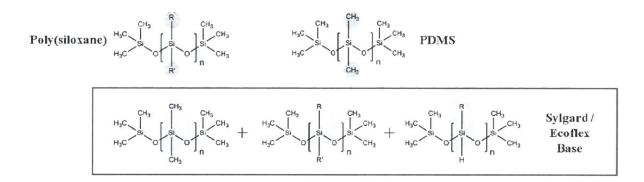

| Figure 6-6: Chemical structures of various poly(siloxane)s. R = R' = long alkyl chains (e.g<br>C12H25, C14H28, etc.)                                                                                                                                                                                                                                                        |

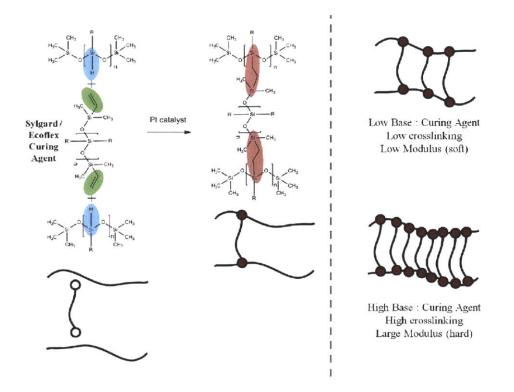

| <b>Figure 6-7:</b> Crosslinking reaction of commercial silicone kits and tunable mechanical propertie of the resulting crosslinked elastomer                                                                                                                                                                                                                                |

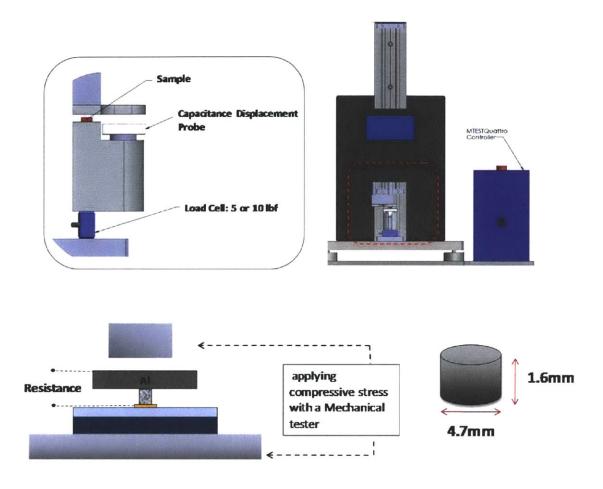

| Figure 6-8: (a) BSEM image of Ni-PDMS composite where nickel particles are approximately<br>2.5 μm in diameter. (b) Stess-strain characteristics of the nickel-doped-PDMS<br>composite pills with the height of 1.6mm and diameter of 4.7mm                                                                                                                                 |

| Figure 6-9: Mechanical compression testing of the nickel-doped-PDMS composite pills 158                                                                                                                                                                                                                                                                                     |

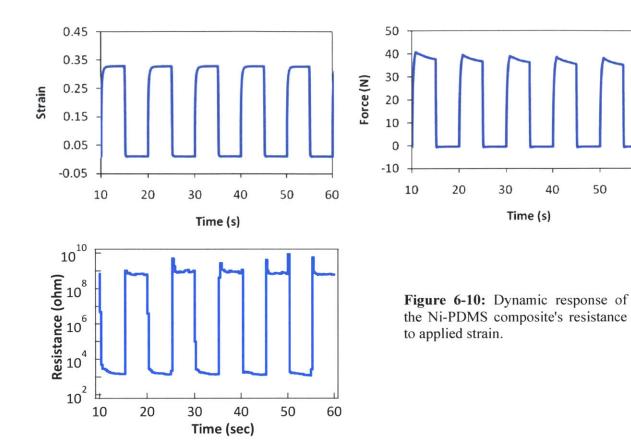

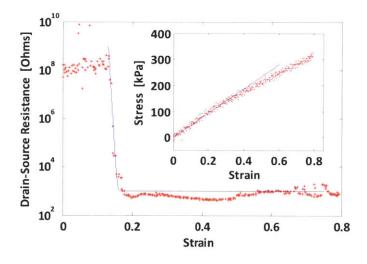

| Figure 6-10: Dynamic response of the Ni-PDMS composite's resistance to applied strain 159                                                                                                                                                                                                                                                                                   |

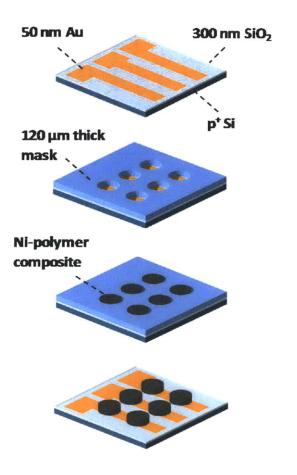

| Figure 6-11: Fabrication process for the squitch                                                                                                                                                                                                                                                                                                                            |

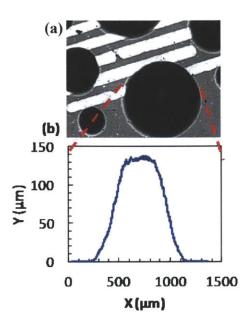

| Figure 6-12: (a) Photomicrograph of patterned Ni- PDMS composite on top of Au electrode using a 120 μm-thick chemically etched stainless steel mask with 200 μm, 500 μm and 1 mm diameter openings. The composite is prepared by mixing 1.0 g of PDMS with 1.5 g of nickel particles; (b) Surface profile of a patterned composite pillar was obtained with a profilometer. |

| Figure 6-13: Resistance change of the Ni-PDMS composite with applied pressure. The inse                                                                                                                                                                                                                                                                                     |

| shows the stress-strain characteristic of the polymer                                                                                                                                                                                                                                                                                                                       |

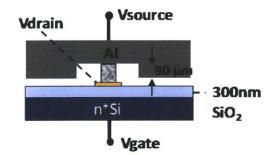

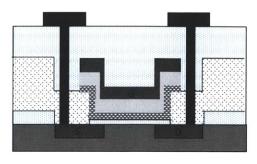

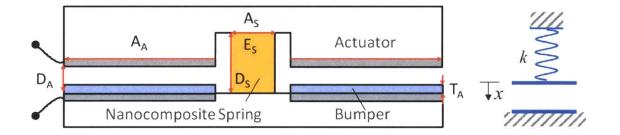

| Figure 6-14: Schematic cross section of the first-demonstration squitch | 10 | 63 | 3 |

|-------------------------------------------------------------------------|----|----|---|

|-------------------------------------------------------------------------|----|----|---|

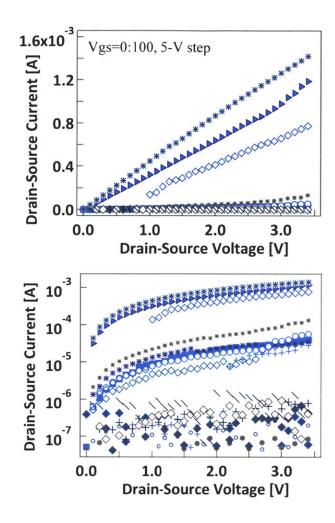

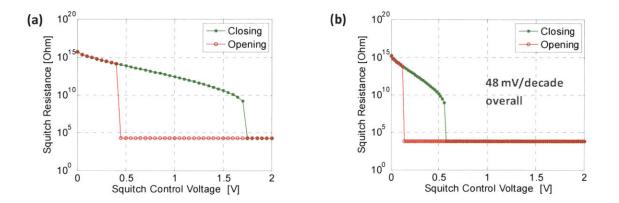

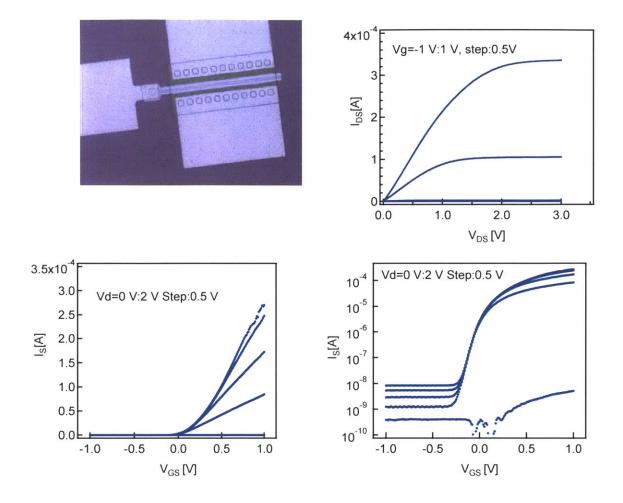

| Figure 6-15:        | (a), (b) The squitch conduction characteristics on linear and log scales, showing 4                                                                                                              |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | orders of magnitude change in the drain-source current by applying voltage to the                                                                                                                |

|                     | gate terminal; the gate current during all experiments is less than 10 nA 164                                                                                                                    |

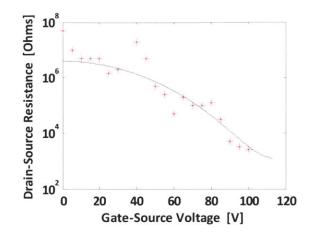

| Figure 6-16:        | The drain-source resistance as a function of the gate-source voltage 165                                                                                                                         |

| Figure 7-1:         | Simulation results of resistance vs. gate voltage of the 200 $\mu$ m <sup>2</sup> devices with (a) 500 and (b) 167 nm vertical profile                                                           |

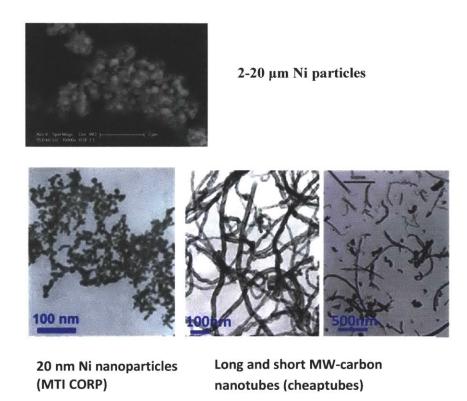

| Figure 7-2:         | SEM image s of filler particles such as Ni nanoparticles and carbon nanotubes that<br>can rep lace Ni microparticles currently used to provide an optimized composite<br>for squitch application |

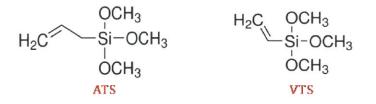

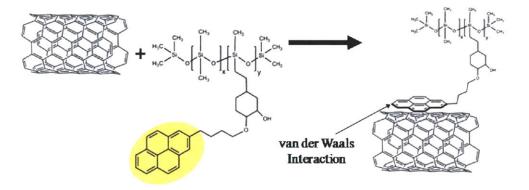

| Figure 7-3:         | Coupling agents suitable for composite synthesis 175                                                                                                                                             |

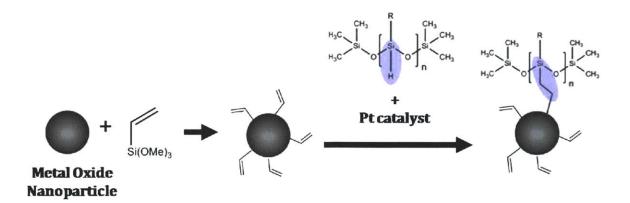

| Figure 7-4:         | Coupling of filler particles to PDMS 176                                                                                                                                                         |

| Figure 7-5:         | Coupling of carbon nanotubes to PDMS [158]176                                                                                                                                                    |

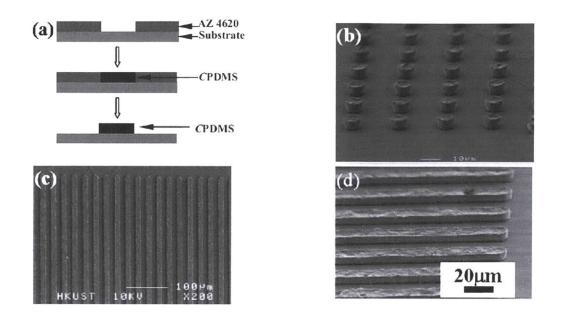

| Figure 7-6:         | (a) Process flow chart illustrating the patterning of conductive PDMS by soft                                                                                                                    |

|                     | lithography. (b–d) SEM images showing the various fabricated conductive patterns [159]                                                                                                           |

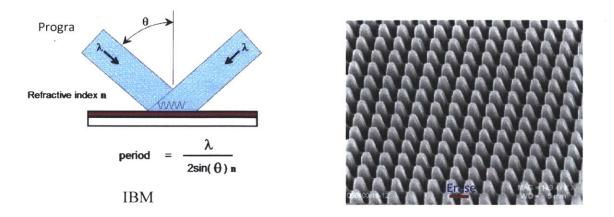

| Figure 7-7:         | (a) Schematic diagram of interferometic lithography; (b) SEM image of 2D mask<br>fabricated at Nanonex using interference lithography. The pattern period can be as<br>small as 200 nm           |

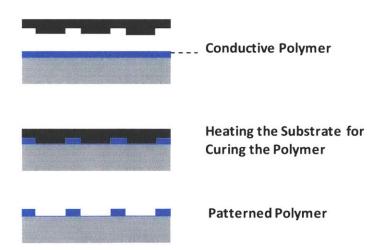

| Figure 7-8:         | Patterning conductive polymer using nano-imprinting technique                                                                                                                                    |

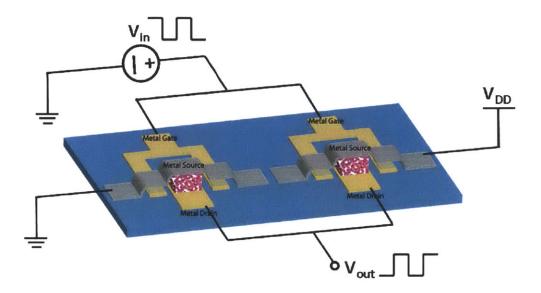

| Figure 7-9:         | An embodiment of a digital inverter using a squitch180                                                                                                                                           |

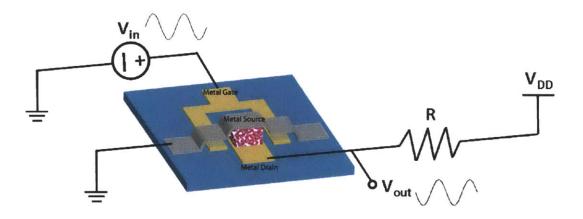

| Figure 7-10:        | An embodiment of a common source analog amplifier182                                                                                                                                             |

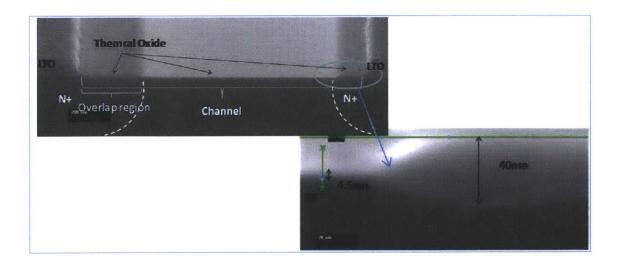

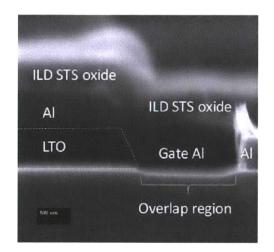

| Figure <b>B-1</b> : | The cross section of the designed molecular memory transistor and the process                                                                                                                    |

|                     | flow used to fabricate memory transistors                                                                                                                                                        |

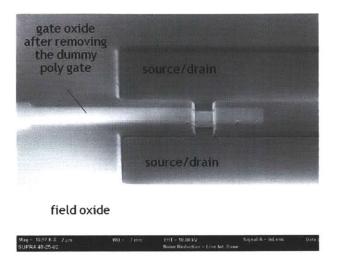

| Figure B-2: | SEM image of the device after removing the dummy gate; the dummy g | gate is used |

|-------------|--------------------------------------------------------------------|--------------|

|             | tin order to define sour-drain regions.                            | 189          |

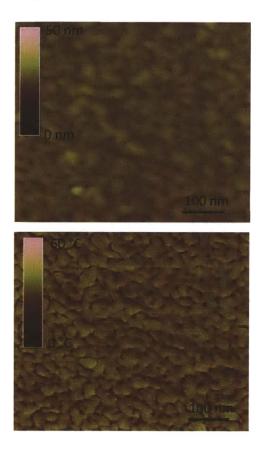

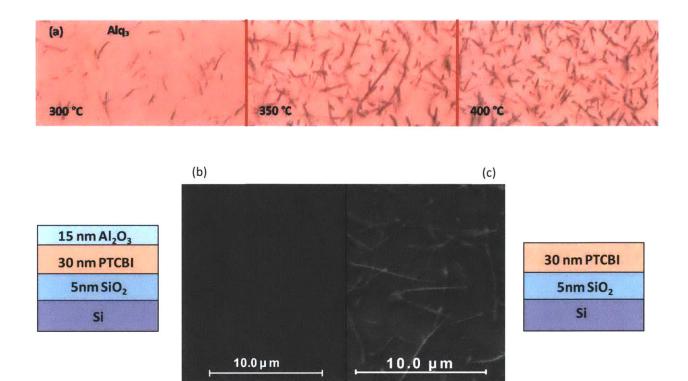

- Figure C-1: (a) Microscopic images of un-encapsulated PTCBI films (30nm thick) annealed in N<sub>2</sub> ambient at 300 °C, 350 °C,400 °C for 3 hours; SEM images of a sample annealed at 350 °C (b) covered with Al<sub>2</sub>O<sub>3</sub> layer and (c) without Al<sub>2</sub>O<sub>3</sub> layer... 194

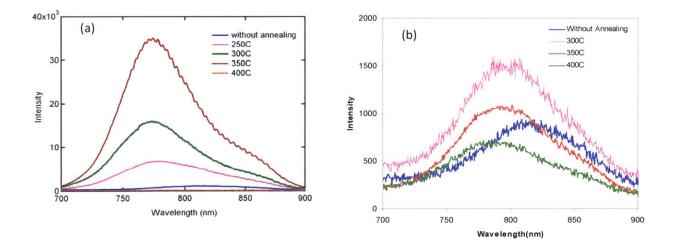

| Figure C-2: | Luminescence as a proxy of film stability for (a) a sample without $Al_2O_3$ , (b) a |

|-------------|--------------------------------------------------------------------------------------|

|             | sample cover by Al <sub>2</sub> O <sub>3</sub> layer                                 |

| Figure D-1: | JEOL 2010 FEG TEM system used in this dissertation 195                               |

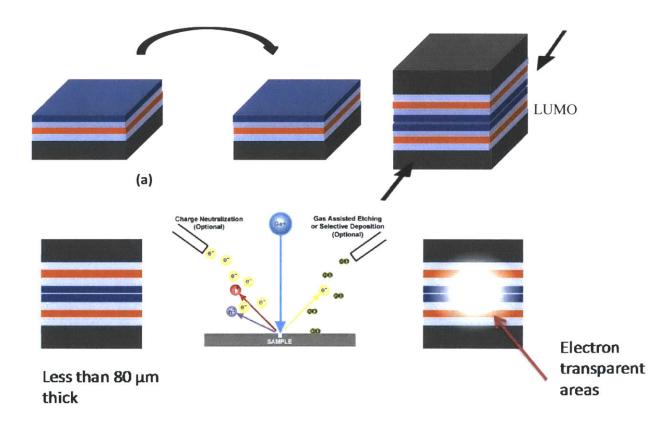

| Figure D-2: | Sample preparation for TEM cross section imaging                                     |

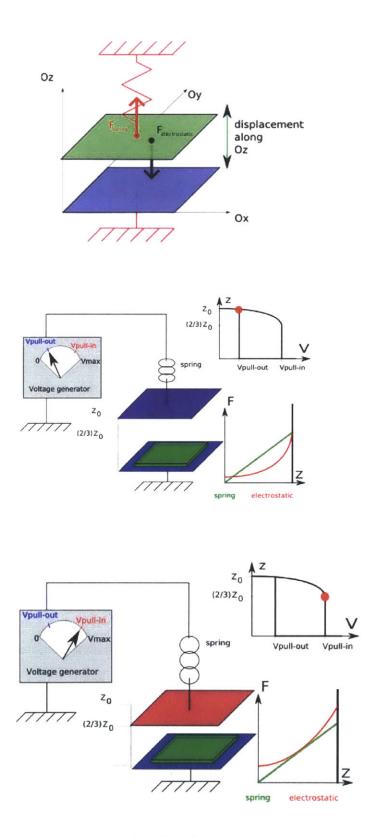

| Figure E-1: | Schematics and graphics showing the electrostatic actuation cycle with pull-in. 201  |

## **List of Tables**

| Table 2-1: | QD-to-QD distance for technology design nodes [13]                                                                                                                                         |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 3.1: | Parameters of the monoclinic unit cell of PTCDA. a, b, c, and $\beta$ are the parameters of the three-dimensional bulk unit cell, and d <sub>102</sub> is the inter-planar spacing for the |

|            | (102)-plane. Taken from [86, 88, 89]75                                                                                                                                                     |

| Table 3-2: | 20% Charge loss time versus electron lateral mobility                                                                                                                                      |

| Table 5.1: | Field effect mobility and charge storage capacity of organic thin films 146                                                                                                                |

## **Chapter 1**

## **Dissertation Motivation and Outline**

The future of computing lies in small and low-power solutions coupled with cloud services. Smartphones are becoming personal computers, powerful enough to run simple desktop computing environments. Tablets are cannibalizing laptops. Even entire home entertainment experiences are being jammed into tiny set-top boxes and embedded into televisions. For many decades, silicon based electronics have been successfully scaled down in size and cost while at the same time achieving higher speed with higher density devices. However, these technologies have recently started to expose their lower limits and have resisted the creation of higher density products.

Organic electronics is an active area of research due to its application in the low-cost manufacture of lightweight, large-area electronic devices and solar cells [1-3]. Molecules and polymers exhibit fascinating optical and electronic properties [4-9]. Researchers have discovered that they can be tailored for specific properties and are compatible with inorganic materials - a significant finding that has encouraged their hybridization with traditional silicon based electronics in order to achieve novel functionalities.

They can be tailored for specific properties and are compatible with inorganic materials that motivate their hybridization with traditional silicon based electronics in order to achieve novel functionalities.

This dissertation is mainly focused on charge storage properties of small organic molecules for potential application in flash memories. In addition, it addresses viscoelastic organic polymers doped with nano-particles as the active element in squishable electronically-controlled switches.

#### **1-1 Molecular charge storage elements**

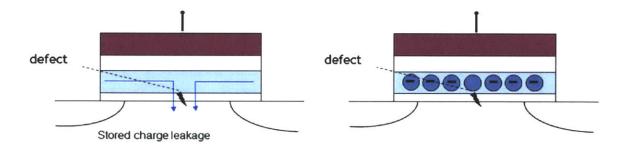

Conventional flash memory technology stores charges in the floating gate of individual memory cells, with the floating gate sandwiched between the gate oxide and the tunneling oxide of each cell [10, 11]. Technological advancements have led to a reduction in the lateral size (and increase in the areal density) of flash memory cells, with an associated decrease in the thickness of the tunneling oxide layer. The tunneling oxide is responsible for retaining the charge in the floating gate for more than 10 years, but reductions in the tunneling oxide thickness and presence of intrinsic defects in the oxide can lead to poor charge retention, limiting the ability for continued scaling of conventional flash memories. The number of electrons stored in the floating gate decreases with each new technology node while the defect-related charge leakage increases, with the consequence that oxide defects have an increasing impact on the cell operation as the size of memory cells is reduced [12, 13].

One technological solution that can enable continued scaling of flash memory cells is to replace the conventional polysilicon floating gate by an array of segmented charge storage elements such as quantum dots (QDs) [14-16], molecules [17-21] and dielectric traps, as has been done for the SONOS flash memory technology [16, 22, 23]. The discrete charge storage in such a nano-segmented floating gate inhibits charge transport between the nano-segments, limiting the impact of any one tunnel oxide defect to the charge stored in the proximity of the defect site. Charge stored in the remaining segments of the nano-segmented floating gate would remain unaffected. One challenge with this approach is that the array of discrete charge-storage segments may cumulatively store a smaller number of electrons than a continuous floating gate of same dimensions. The self-charging energy of individual nano-segments could limit the number of charges stored on each to one electron. In addition, spatial density of nano-segments may have to be small to maintain sufficient spacing between the segments and inhibit charge transport between them, as otherwise charge tunneling between the segments would obviate the intended benefit of nano-structuring the floating gate to preserve the charge on individual segments. Therefore, the benefit of nano-segmenting the floating gate will be manifested only if high charge storage capability can be maintained.

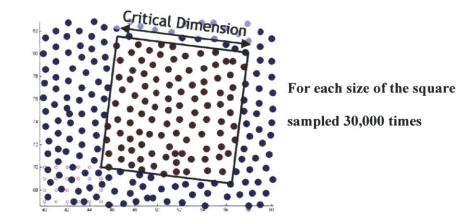

Unfortunately, semiconductor nanocrystal/QDs memories may not be the ultimate solution to flash memory scaling, although it is a novel memory structure that still attracts a lot of attention now [14, 16]. It is hard to control the uniformity of the nanocrystals' size and their physical locations in the channel. It is not a surprise that nanocrystal memories exhibit large device-to-device variation. Also, in order to have a negligible lateral tunneling between the nanocrystals, the spacing between nanocrystals should be greater than 5 nm that limits the maximum stored charge density in this kind of memories.

Charge storage in dielectric traps is also vulnerable to trap density and energy variations. In comparison, a combination of the top-down lithography and the bottom-up molecule self-assembly processes can offer a uniform charge density and possible stable multilevel storage in a single memory cell [17, 24, 25]. The monodisperse nature of the molecular orbitals (MOs) can potentially reduce cell variations, whereas the distinct energy levels may enable stepwise charging for precise control of each memory state.

Although organic compounds have recently attracted growing interest for nonvolatile memory applications, many of the devices reported so far are two-terminal resistive memories, rather than reversible charge-storage elements [19-21]. Memory behavior of a series of molecular thin films embedded in metal-oxide-semiconductor (MOS) structures was investigated in this dissertation.

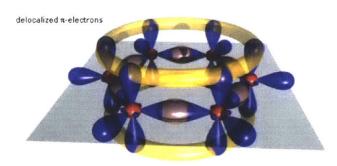

A floating gate consisting of a thin film of molecules would provide the advantage of a uniform set of identical nanostructured charge storage elements, with low density of states and high binding energy that results in low intermolecular interactions. The minimal overlap between the neighboring molecular electron wavefunctions contributes to organic thin film electron/hole mobilities in the range of  $10^{-1}$  cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> to  $10^{-7}$  cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>. Compared to QDs which typically exhibit size and order variability, molecular films have the highly desirable size and morphological consistency that provides relative constancy in the electronic energy level structure of molecular films.

# **1-2 MEMS Switches Employing Active Metal-Polymer** Nano-Composites

For decades much research has been directed towards utilizing the piezoresistive properties of polymer materials doped with conductive particles in developing a broad range of devices from tactile sensors to fuses [26-29]. These composite materials in general can be fabricated such that they act as poor conductors but exhibit an increased electrical conduction due to tunneling between particles. This property of conductive composites is employed in this dissertation to develop an electrostatically actuated squishable switch or "squitch" which functions as a gated transistor.

Some advantages of this MEMS switch are that: (1) it is an aditive technology compatible with large area processing with printing or photolithography on rigid or flexible substrates; (2) it can exhibit large on-to-off conduction ratio of  $10^7$ :1; (3) it can exhibit voltage-controlled conduction with a gain greater than 1 decade per 60 mV - a fundamental limit for silicon-based semiconductor switches; and (4) its contacts are not subject to the usual wear associated with point-contact electromechanical switches.

This low-loss squishable MEMS switch can be used for power management of digital IC's. Lowering power consumption in digital IC's is becoming increasingly important in order to increase mobile device battery life and to decrease cooling costs for enterprise server farms. Power gating of digital logic using MEM relays may provide significant power savings over conventional MOS power gating [30].

The squitch can also be used as the integrated electronics in sensory skins for signal processing and the local amplification of sensor signals. The lightweight and flexible sensory skins are capable of recording external pressure, sound waves, liquid flow, or changes in temperature or chemical environment.

Formed as an array of integrated detectors embedded in a flexible matrix, sensory skins will enable phased-array detection for directional location of external stimuli. The squitch can be used to construct analog and digital circuitry that can then process the signals produced by the sensors. The objective is to develop environmentally responsive sensory skins that both probe their environment and process the sensed signals, mimicking the capabilities of living skins that possess both sensory cells and a signal-processing "nervous system". ". Such skins may enable the development of devices like sensors that can measure the stresses and strains in parachute fabrics, large-scale "listening" devices that can be unobtrusive, wearable sensors of the battlefield environment for soldier protection and wearable sensors that can monitor soldier health.

### **1.2 Dissertation Outline**

The structure and operational basics of conventional flash memories are discussed in Chapter 2.

The background physics and methods incorporated in the next chapters will be briefly described to facilitate the understanding of the rest of this dissertation. After an introduction of the general scaling requirement, charge storage on segmented floating gates as a solution for scaling limits are proposed. Finally, challenges and essential properties of the segmented floating gate are briefly discussed.

In chapter 3, new kind of memories with molecular floating gate is introduced. Charge-storage behavior in a series of molecular thin films was investigated using MOS structures with SiO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub> as the tunneling and control oxides, respectively. It was shown that molecular floating gates can reach record-high densities of  $5.4 \times 10^{13}$  cm<sup>-2</sup> and durability over  $10^5$  charging/discharging cycles.

In chapter 4, retention and diffusion of charge in tris(8-hydroxyquinoline) aluminum (Alq<sub>3</sub>) and  $C_{60}$  molecular thin films were visualized and investigated using Kelvin force microscopy. Chapter 5 presents molecular memories with increased storage capacity. It was demonstrated that charge storage properties of the molecular trapping layer can be engineered by rearranging molecules and their  $\pi$ -orbital overlaps via addition of dopant molecules. Chapter 6 presents the design, fabrication, testing and evaluation of a MEMS switch that employs viscoelastic organic polymers doped with nano-particles as its active material. This switch is a new type of FET that is compatible with large area processing with printing or photolithography, on rigid or flexible substrates and can exhibit large on-to-off conduction ratio.

Finally chapter 7 summarizes and concludes the dissertation and offers suggestions for future work to further enhance the performance of the memory and switches fabricated by using organic molecules and polymers.

## Chapter 2

### **Introduction to Flash Memory**

#### 2.1 Memory Industry and Applications

Complementary metal-oxide-semiconductor (CMOS) memories can be divided into two main categories: volatile memories that lose stored information once the power supply is switched off, and nonvolatile memories that keep stored information also when the power supply is switched off. In the past decade, memory chips with low power consumption and low cost have attracted more and more attention due to the booming market of portable electronic devices such as cellular phones and digital cameras. These applications require the memory to have ten years data retention time, so that the nonvolatile memory device has become indispensable. There are mainly four types of nonvolatile memory technology: flash memory, Ferro-electric Random Access Memory (FeRAM), Magnetic Random Access Memory (MRAM) and phase change memory. Flash memory is presently the most suitable choice for nonvolatile applications [16]. The continuous-film polysilicon-based floating-gate device has been the backbone of the nonvolatile memory (flash) market for the past decade.

The flash memory business flourished when the memory was adopted as the standard memory in cell phones, in which the memory enabled just-in-time loading of the latest program code as the last step in manufacturing, and program bugs could be fixed without taking the phone apart.

The simplicity of its device fabrication process is evident. Flash memory fabrication process is compatible with the current CMOS process and is a suitable solution for embedded memory applications.

A flash memory cell is simply a MOSFET cell, except that a poly-silicon floating gate (or Silicon Nitride charge trap layer) is sandwiched between a tunnel oxide and an inter-poly oxide to form a charge storage layer. All other nonvolatile memories require integration of new materials that are not as compatible with a conventional CMOS process. It is easier and more reliable to integrate flash memory than other nonvolatile memories with logic and analog devices in order to achieve better chip performance for wireless communication and wireless computation.

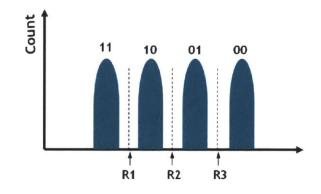

Flash memory can achieve the highest chip density since flash memory cell consists of only one transistor. A FeRAM memory cell generally consists of one transistor and one capacitor [31], while a MRAM cell needs a transistor and a magnetic tunnel junction [32]. Phase change memory was expected to be a promising nonvolatile memory; however, its memory cell consists of one resistor and a bipolar junction transistor [33]. In addition, Flash memory possesses the multi-bit per cell storage property [34]. Four distinct threshold voltage ( $V_T$ ) states can be achieved in a flash memory cell by controlling the amount of charge stored in its floating gate [10, 16].

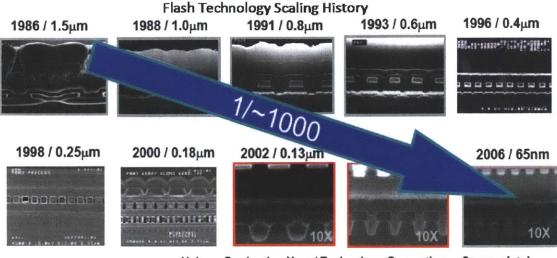

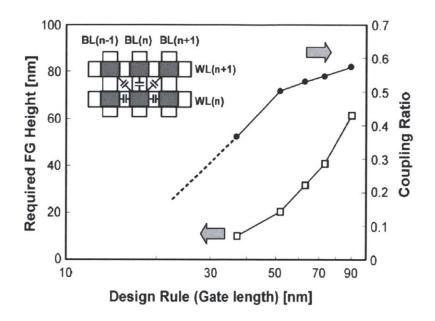

However, after years of intense growth in the Flash memory market, conventional flash memory technology appears to be reaching fundamental scaling limits [10, 12, 13]. The difficulty in scaling the tunnel oxide thickness due to leakage-current-related charge loss, reduction in gate coupling, and increase in cell-to-cell interference, necessitate modification in the design of the flash memory structures, including proposals for replacing the polysilicon floating gate by either floating traps such as silicon nitride in the SONOS technology [16, 22, 23] or floating quantum dots (QD) [14, 16]

#### 2.2 Flash Memory Structure

To have a memory cell that can commute from one state to the other and that can store the information independently of external conditions, the storing element needs to be a device whose conductivity can be changed in a nondestructive way.

One solution is to have a transistor with a threshold voltage that can change repetitively from a high to a low state, corresponding to the two states of the memory cell, i.e., the binary values

("1" and "0") of the stored bit. Cells can be "written" into either state "1" or "0" by either "programming" or "erasing" methods. One of the two states is called "programmed," the other "erased."

The threshold voltage of a MOS transistor can be written as [10]

$$V_T = K - \bar{Q}/C_{ox} \tag{2.1}$$

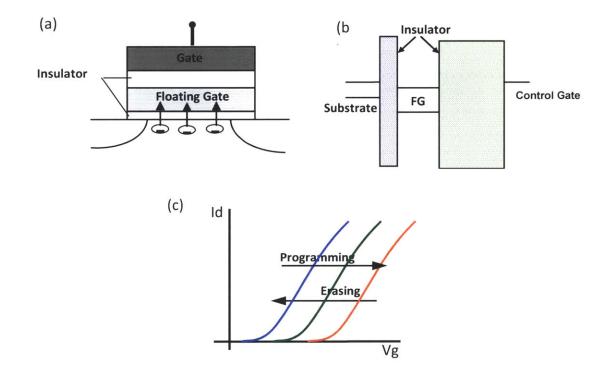

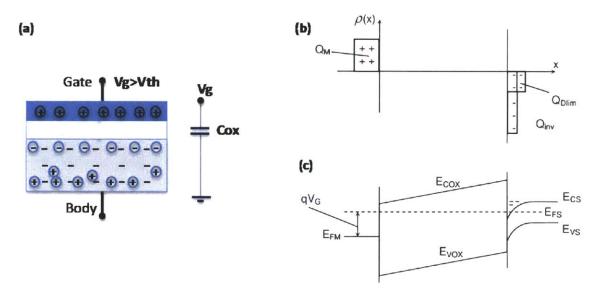

**Figure 2-1:** (a) Schematic cross section of conventional flash memory; (b) Flash memory energy band diagram; (c) Threshold voltage shift during programming and erasing.

where *K* is a constant that depends on the gate and substrate material, doping, and gate oxide thickness,  $\overline{Q}$  is the charge weighted with respect to its position in the gate oxide, and C<sub>ox</sub> is the gate oxide capacitance. As can be seen, the threshold voltage of the memory cell can be altered by changing the amount of charge present between the gate and the channel. There are many ways to obtain the threshold voltage shift. Two are the most common solutions used to store charge:

In a conductive material layer between the gate and the channel and completely surrounded by insulator. This is the floating gate (FG) device.

In traps that are present in the oxide, more precisely at the interface between two dielectric materials. The most commonly used interface is the silicon oxide/nitride interface. Devices obtained in this way are called metal-nitride-oxide-silicon (MNOS) cells.

Programming

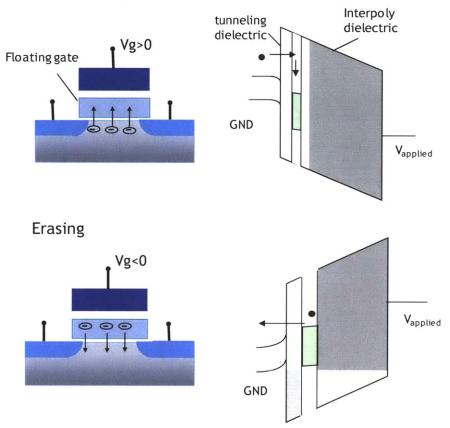

Figure 2-2: Schematic cross section and energy band diagram of conventional flash memory during programming and erasing.

The schematic cross section of a generic FG device is shown in Figure 2-1(a); the upper gate is the control gate (CG) and the lower gate, completely isolated within the gate dielectric, is the FG. The FG acts as a potential well (see Figure 2-1(b)). If a charge is forced into the well, it cannot move from there without applying an external force: the FG stores charge [1]. Usually the gate dielectric, i.e., the one between the transistor channel and the FG, is an oxide in the range of 9–10 nm and is called "tunnel oxide" since electron tunneling occurs through it. The dielectric

that separates the FG from the CG is formed by a triple layer of oxide–nitride–oxide (ONO). The ONO thickness is in the range of 15–20 nm of equivalent oxide thickness. The ONO layer as interpoly dielectric has been introduced in order to improve the tunnel oxide quality.

Stored charges on the floating-gate alter the threshold voltage of the MOSFET. The amount of charge stored on the floating gate can be controlled with biasing the terminal electrodes with voltages sufficient enough to cause tunneling of carriers in the gate-insulator from either the channel or the gate. These charges can tunnel through the gate insulator and be trapped/stored on the floating gate (programming), therefore causing a shift in the threshold voltage of the device. Appropriate biasing of the device can also be performed to cause removal of the charges that are stored on the floating gate (erasing), and to return the threshold voltage to the original uncharged state (Figure 2-2).

The data stored in a Flash cell can be determined measuring the threshold voltage of the FG MOS transistor by reading the current driven by the cell at a fixed gate bias.

## 2.3 Types of Flash Memory

Two major forms of Flash memory, NAND Flash and NOR Flash, have emerged as the dominant varieties of non-volatile semiconductor memories utilized in portable electronics devices. NAND Flash, which was designed with a very small cell size to enable a low cost-perbit of stored data, has been used primarily as a high-density data storage medium for consumer devices such as digital still cameras and USB solid-state disk drives. NOR Flash has typically been used for code storage and direct execution in portable electronics devices, such as cellular phones and PDAs.

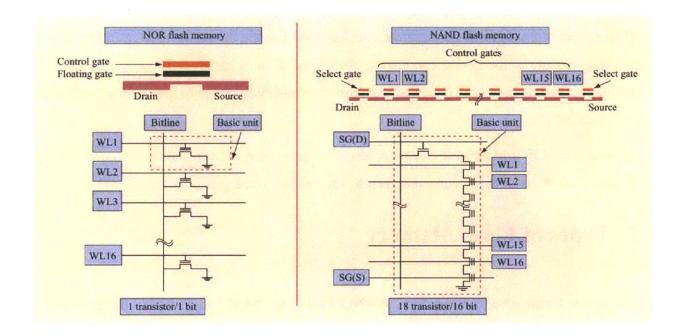

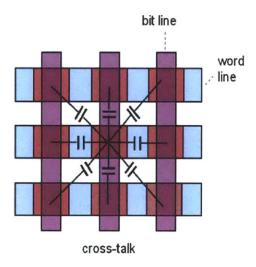

In NOR flash memory, each cell resembles a standard MOSFET, except that the cell has two gates, stacked vertically, instead of just one. Each NOR memory cell is connected to the common drain connection called a bitline and can be read from directly giving the fast read performance that is necessary for fast program execution. In order to decrease the cost of flash memory, NAND flash memory (Figure 2-3) was invented [12, 35].

In NAND flash memory, the memory cells are connected in series with 16 or 32 memory cells connected to the bitline and source line through two select transistors. [In Figure 2-3, the source

line is connected to the ground through SG(S).] Because cell contact area represents about 30% of unit cell area, this serial cell approach gives smaller cell size and lower die cost compared to NOR memory. The tradeoff is slower read performance because the read current is lower when using serial transistors. The NAND memory business flourished with the growth in popularity of digital cameras, for which NAND memory cards provided a convenient low-cost media for

**Figure 2-3:** Schematic cross-sections and circuit diagrams for NOR and NAND flash memory. In NOR memory, the basic unit is one memory transistor. For NAND memory, the basic unit is 16 memory and 2 select transistors [12]. (WL: wordline; SG(D): select gate drain; SG(S): select gate source)

picture storage. The slow read speed is not an issue for such applications. This application was followed by the ubiquitous USB (Universal Serial Bus) drives and MP3 (MPEG-1 Audio Layer 3) players. An emerging new application that will drive more growth for NAND memory is solid-state disks to replace disk drives in notebook computers. The growth of flash memory over the years was driven by the relentless memory cost reduction through Moore's Law; the price for flash memory dropped from approximately \$80,000 per gigabyte in 1987 for NOR flash to approximately \$10 per gigabyte in 2007 for NAND flash.

### 2.4 Program and erase mechanisms

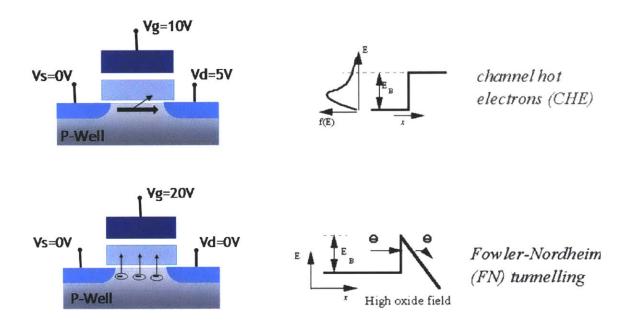

There are two main mechanisms by which charge carriers can charge and discharge the floating gate: Hot-Electron Injection and Fowler-Nordheim tunneling.

Figure 2-4: Writing mechanism in floating-gate devices [11, 36].

#### 2.4.1 Hot-Electron Injection

Hot-Electron Injection is a phenomenon by which a charge carrier in the channel gains energy from the lateral electric field, and then crosses the oxide energy barrier into the floating gate by experiencing a vertical electric field between the control gate and substrate.

An electron traveling from the source to the drain gains energy from the lateral electric field and loses energy to the lattice vibrations (acoustic and optical phonons). At low fields, this is a dynamic equilibrium condition, which holds until the field strength reaches approximately 100 kV/cm [10, 11]. For fields exceeding this value, electrons are no longer in equilibrium with the lattice, and their energy relative to the conduction band edge begins to increase. Electrons are "heated" by the high lateral electric field, and a small fraction of them have enough energy to surmount the barrier between oxide and silicon conduction band edges. For an electron to overcome this potential barrier, three conditions must hold.

- 1) Its kinetic energy has to be higher than the potential barrier.

- 2) It must be directed toward the barrier; and

- 3) The field in the oxide should be collecting it.

In general terms, the electron current density from Si to  $SiO_2$  at a point x along the channel of a MOSFET can be analytically expressed as [11]:

$$J = q \int_0^\infty v_{\perp}(x, E) f_{\perp}(x, E) g(E) P(x, E) dE)$$

(2.2)

where  $f_{\perp}(x, E)$  is the distribution of electrons that hit the interface between x and x+dx; g is the number of available electron states; P(x, E) is the injection probability; and  $v_{\perp}(x, E)$  is the electron velocity component perpendicular to the interface and directed towards it. The injected current is the combined result of a few factors: (1) the number  $(f_{\perp}, g)$  and velocity  $(v_{\perp})$  of electrons directed towards the interface; (2) the electron energy and momentum distribution; and (3) the probability of injection from Si to SiO<sub>2</sub> (P(x, E)).

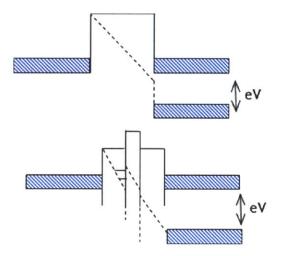

### 2.4.2 Fowler-Nordheim Tunneling

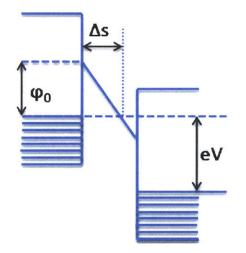

Fowler-Nordheim Tunneling is another mechanism for charge carriers to cross the oxide energy barrier by applying a strong electric field (in the range of 8–10 MV/cm) across a thin oxide. The concept of tunneling is rooted in quantum mechanics. Electrons can penetrate a forbidden region in order to tunnel from one classically allowed region (substrate) to another (floating gate). However, this phenomenon is probabilistic, depending on the source material, and the height and width of the oxide barrier. For this method only single external power supply is needed. The current density of electrons being shown in Figure 2-5 is transmitted through the trapezoidal potential barrier to the polysilicon gate is [37]:

$$J = \frac{2}{(2\pi)^3} \iiint dk_x dk_y dk_z v_x(k_x) \times D(E_x(k_x)) f_{eq}(E(k))$$

(2.3)

where

$$E(k) = \frac{\hbar^2 k_x^2}{2m} + \frac{\hbar^2 k_y^2}{2m} + \frac{\hbar^2 k_z^2}{2m} \equiv E_x(k_x) + E_y(k_y) + E_z(k_z)$$

(2.4)

is the electron energy;  $E_x$  is the associated perpendicular tunneling energy;

$$D(E_{x}) = \exp\left(-\frac{2}{\hbar}\int_{s_{1}}^{s_{2}} dx \sqrt{2m(V(x) - E_{x})}\right)$$

(2.5)

**Figure 2-5:** Rectangular potential barrier in insulating film between metal electrodes for V>  $\varphi_0/e$ .

is the transmission probability in the WKB approximation, which depends on the perpendicular tunneling energy  $E_x$ ;  $v_x = \hbar^{-1} dE_x / dk_x$  - the *x* component of the group velocity; *m* - the electron mass; and  $f_{eq}(E)$  - the equilibrium electron distribution function.

Approximating the Fermi–Dirac distribution with the step function leads for high oxide fields to the Fowler–Nordheim tunneling current [37]

$$J = \frac{2.2e^3 F^2}{8\pi h \varphi_0} \exp\left(\frac{-8\pi}{2.96 h e F} \sqrt{2m} \varphi_0^{-1.5}\right)$$

(2.6)

where  $\varphi_0$  is the barrier height and *F* the oxide field. This formula has proved very successful in describing the dependence of the FN tunneling current of *cold* electrons on oxide thickness and gate voltage, in particular for the erase operation in silicon flash memory cells.

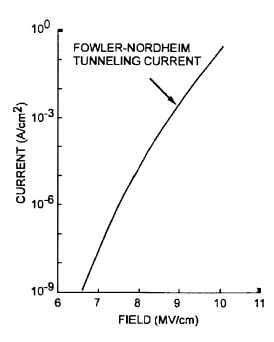

A plot of the amount of Fowler-Nordheim tunneling as a function of electric field is shown in Figure 2-6. Though the Fowler-Nordheim tunneling current can be intensified by increasing voltage or decreasing the oxide thickness, the performance and reliability needs must be balanced. The oxide cannot be made too thick as it would significantly increase the voltage and time required for charging the floating gate nor can it be made too thin as it would increase oxide defect density and ruin device reliability. In this dissertation memory behavior of organic molecules were studied using MOS structures. FN tunneling method will be used for programming and erasing the memory cells.

Figure 2-6: FN tunneling current as a function of electric field [10].

### 2.4.3 Metal Oxide Semiconductor (MOS) Capacitor

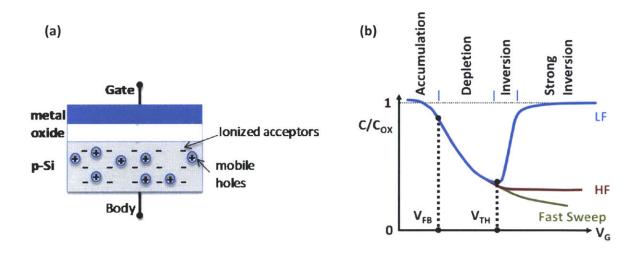

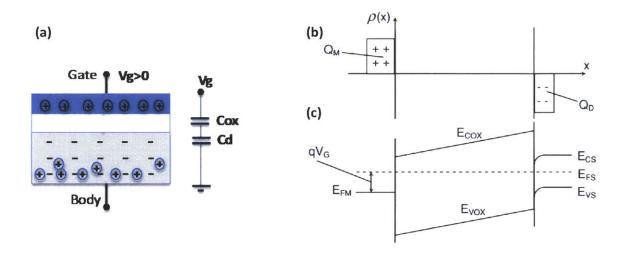

The MOS capacitor consists of an oxide film sandwiched between a P- or N-type silicon substrate and a metal plate called gate as shown in Figure 2-7.