| Title                       | Multi-frequency inversion-charge pumping for charge separation and mobility analysis in high-k/InGaAs metal-oxide-semiconductor field-effect transistors                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Author(s)                   | Djara, Vladimir; Cherkaoui, Karim; Negara, M. A.; Hurley, Paul K.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| Publication date            | 2015                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| Original citation           | Djara, V., Cherkaoui, K., Negara, M. A. and Hurley, P. K. (2015) 'Multi-frequency inversion-charge pumping for charge separation and mobility analysis in high-k/InGaAs metal-oxide-semiconductor field-effect transistors', Journal of Applied Physics, 118(20), 204107 (7pp). doi: 10.1063/1.4936313                                                                                                                                                                                                                                                                |  |  |  |  |

| Type of publication         | Article (peer-reviewed)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| Link to publisher's version | http://aip.scitation.org/doi/10.1063/1.4936313 http://dx.doi.org/10.1063/1.4936313 Access to the full text of the published version may require a subscription.                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| Rights                      | © 2015 AIP Publishing LLC. This article may be downloaded for personal use only. Any other use requires prior permission of the author and AIP Publishing. The following article appeared in Djara, V., Cherkaoui, K., Negara, M. A. and Hurley, P. K. (2015) 'Multifrequency inversion-charge pumping for charge separation and mobility analysis in high-k/InGaAs metal-oxide-semiconductor field-effect transistors', Journal of Applied Physics, 118(20), 204107 (7pp). doi: 10.1063/1.4936313 and may be found at http://aip.scitation.org/doi/10.1063/1.4936313 |  |  |  |  |

| Item downloaded from        | http://hdl.handle.net/10468/4712                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

Downloaded on 2018-08-23T20:19:51Z

## Multi-frequency inversion-charge pumping for charge separation and mobility analysis in high-k/InGaAs metal-oxide-semiconductor field-effect transistors

V. Djara, K. Cherkaoui, M. A. Negara, and P. K. Hurley

Citation: Journal of Applied Physics 118, 204107 (2015); doi: 10.1063/1.4936313

View online: http://dx.doi.org/10.1063/1.4936313

View Table of Contents: http://aip.scitation.org/toc/jap/118/20

Published by the American Institute of Physics

# Multi-frequency inversion-charge pumping for charge separation and mobility analysis in high-k/InGaAs metal-oxide-semiconductor field-effect transistors

V. Djara, K. Cherkaoui, M. A. Negara, and P. K. Hurley<sup>a)</sup> *Tyndall National Institute, University College Cork, Dyke Parade, Cork, Ireland*

(Received 9 July 2015; accepted 10 November 2015; published online 30 November 2015)

An alternative multi-frequency inversion-charge pumping (MFICP) technique was developed to directly separate the inversion charge density ( $N_{inv}$ ) from the trapped charge density in high-k/InGaAs metal-oxide-semiconductor field-effect transistors (MOSFETs). This approach relies on the fitting of the frequency response of border traps, obtained from inversion-charge pumping measurements performed over a wide range of frequencies at room temperature on a single MOSFET, using a modified charge trapping model. The obtained model yielded the capture time constant and density of border traps located at energy levels aligned with the InGaAs conduction band. Moreover, the combination of MFICP and pulsed  $I_{d}$ - $V_{g}$  measurements enabled an accurate effective mobility vs  $N_{inv}$  extraction and analysis. The data obtained using the MFICP approach are consistent with the most recent reports on high-k/InGaAs. © 2015 AIP Publishing LLC. [http://dx.doi.org/10.1063/1.4936313]

#### I. INTRODUCTION

InGaAs and related compound semiconductors have become serious candidates for replacing strained Si in future complementary metal-oxide-semiconductor device applications due to their remarkable electron mobility. In a metal-oxide-semiconductor transistor (MOSFET), the effective mobility ( $\mu_{eff}$ ) is expressed as<sup>2</sup>

$$\mu_{eff} = \frac{L}{W} \frac{I_d}{q.N_{inv}.V_{ds}},\tag{1}$$

where L/W is the channel length over width ratio,  $I_d$  is the drain current, q is the electron charge,  $N_{inv}$  is the inversioncharge density, and  $V_{ds}$  is the drain-to-source voltage. The "standard"  $\mu_{eff}$  extraction method relies on the combination of split capacitance vs voltage (C-V) and DC drain current vs gate voltage  $(I_d - V_g)$  measurements to provide the parameters  $N_{inv}$  and  $I_d/V_{ds}$ , respectively. While this method enables highly accurate mobility extraction in SiO<sub>2</sub>/Si MOSFETs, its accuracy in emerging high-k/InGaAs devices with a relatively high density of interface traps  $(D_{it})$ , combined with a high density of near-interface oxide traps or "border traps"  $(D_{bt})$ , is now questionable. In recent years, significant research efforts were dedicated to solving this issue. For instance, Ali et al. combined split C-V measurements performed over a range of temperature (T) going from 292 K to 35 K with theoretical calculations in order to extract more accurate  $N_{inv}$  and  $\mu_{eff}$  values,<sup>3</sup> while Taoka *et al.* proposed an approach combining split C-V and Hall measurements to study the impact of the traps aligned with the InGaAs conduction band on  $\mu_{eff}$ . While both methods yielded important results, access to a cryogenic probe station or a Hall measurement setup (along with gated Hall structures) is not

#### II. EXPERIMENTAL DETAILS

#### A. Process flow of Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSFETs

The InGaAs MOSFETs used in this study were fabricated using the process flow reported in Ref. 7. Briefly, the devices featured a p-In<sub>0.53</sub>Ga<sub>0.47</sub>As channel with a nominal doping of  $4 \times 10^{17}$ /cm³. A (NH<sub>4</sub>)<sub>2</sub>S surface passivation was performed before the formation of a 10-nm-thick Al<sub>2</sub>O<sub>3</sub> gate dielectric by atomic layer deposition.<sup>8</sup> The source and drain (S/D) areas were formed by ion implantation. The Pd gate and the Au/Ge/Au/Ni/Au S/D metal contacts were obtained by evaporation and lift-off. The devices received a forming gas (H<sub>2</sub>/N<sub>2</sub>) anneal to improve the gate stack and the S/D contact performance.<sup>7</sup>

#### B. Multi-frequency inversion-charge pumping method

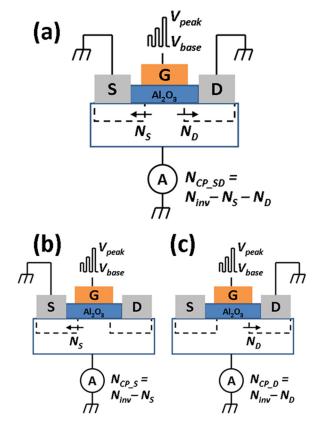

The ICP/MFICP setup shown in Fig. 1(a) is similar to that reported in Ref. 6. The S/D terminals are grounded. A square pulse train of variable amplitude increasing from a

always possible. We, therefore, developed a multi-frequency inversion-charge pumping (MFICP) technique as an alternative approach to analyze the  $\mu_{eff}$  in high-k/InGaAs MOSFETs. The MFICP technique represents an extension of the ICP approach reported by Kerber et~al. in Ref. 6 for Si devices. Compared to the aforementioned  $\mu_{eff}~vs~N_{inv}$  extraction methods for high-k/InGaAs MOSFETs,  $^{3-5}$  the MFICP provides several advantages. Indeed, the  $\mu_{eff}~vs~N_{inv}$  extraction with MFICP only requires measurements of a single MOSFET at room temperature. Moreover, the analysis of the frequency (f) response of border traps by MFICP not only enables a direct separation of the inversion charge and the trapped charge but also provides information about border traps located at energy levels aligned with the InGaAs conduction band.

a)Electronic mail: paul.hurley@tyndall.ie

FIG. 1. Schematic representations of the ICP/MFICP setup used to extract  $N_{inv}$  in long channel length ( $L>20~\mu{\rm m}$ ) high-k/InGaAs MOSFETs through measurements of (a)  $N_{CP~SD}$ , (b)  $N_{CP~S}$ , and (c)  $N_{CP~D}$ .

base voltage  $(V_{base})$ , generally set to a value close to the flatband voltage  $(V_{FB})$ , to a peak voltage  $(V_{peak})$  is applied to the gate terminal. The total pumped charge density  $(N_{CP\_SD})$  is measured on the substrate terminal.

The geometrical and trapped charge components of  $N_{CP\_SD}$  are, respectively, expressed as the first and second terms of the equation  $^{9,10}$

$$N_{CP\_SD} = \alpha.C_{inv}(V_g - V_T)/q + (D_{it} + D_{bt}.\Delta t_{bt}).\Delta E, \qquad (2)$$

where  $\alpha$  is the fraction of  $N_{inv}$  recombining in the substrate,  $C_{inv}$  is the inversion capacitance,  $V_T$  is the threshold voltage,  $\Delta t_{bt}$  is the oxide thickness over which the border traps are probed, and  $\Delta E$  is the energy interval swept by the Fermi level when  $V_g$  increases from  $V_{base}$  to  $V_{peak}$ . It is noted that, here,  $D_{it}$  refers to interface traps located at energy levels aligned with the  $In_{0.53}Ga_{0.47}As$  bandgap, while  $D_{bt}$  refers to border traps located at energy levels aligned with the  $In_{0.53}Ga_{0.47}As$  conduction band.

The ICP method applied to devices featuring low  $D_{it}$  and  $D_{bt}$ , such as SiO<sub>2</sub>/Si MOSFETs, enables a direct extraction of  $N_{inv}$  by simply maximizing the geometrical component, <sup>11</sup> through the use of long channel  $(L > 20 \,\mu\text{m})$  devices in combination with fast (10 ns) pulse rise time  $(t_r)$  and fall time  $(t_f)$ . 6 Under such conditions, a quantity  $\alpha \cdot N_{inv}$  is forced to recombine in the substrate and contribute to  $N_{CP\_SD}$ . A correction for the quantity  $(1 - \alpha).N_{inv}$ , representing the sum of the charge density lost by diffusion to the source  $(N_S)$  and to the drain  $(N_D)$ , is applied through the measurements of

$N_{CP\_S}$  [Fig. 1(b)] and  $N_{CP\_D}$  [Fig. 1(c)]. Following the measurements of  $N_{CP\_SD}$ ,  $N_{CP\_S}$ , and  $N_{CP\_D}$ , a corrected pumped charge density  $(N_{CP})$  equal to  $N_{inv}$  can be obtained using the relationship:

$$N_{CP} = N_{CP S} + N_{CP D} - N_{CP SD}. (3)$$

However, for the case of devices featuring relatively high  $D_{it}$  and  $D_{bt}$ , such as high-k/InGaAs MOSFETs, further attention needs to be dedicated to the selection of the ICP measurement parameters in order to not only maximize the geometrical component, but also minimize the trapped charge component.

In Section III C 1, we demonstrate that  $V_{base}$  can be raised in order to maintain most of the interface traps, having energy levels located within the  $In_{0.53}Ga_{0.47}As$  bandgap to be constantly occupied and, therefore, not contributing to  $N_{CP}$ . Similarly, in Section III C 2, we show that the duty cycle (D) of the pulse train applied to the gate terminal can be reduced to minimize the transient charging time  $(t_{charge})$  of border traps, maintaining most border traps constantly unoccupied and, therefore, not contributing to  $N_{CP}$ .

In our proposed MFICP approach, where ICP measurements are performed over a wide range of f at a fixed D, a modulation of the border trap response as a function of  $t_{charge} = D/f$  is observed. This enables the effective separation of the inversion charge from the trapped charge by fitting the experimental  $N_{CP}$  vs  $t_{charge}$  data using a charge trapping model that we modified to account for  $N_{inv}$  (Section III D).

#### III. RESULTS AND DISCUSSION

#### A. Interface trap density profile

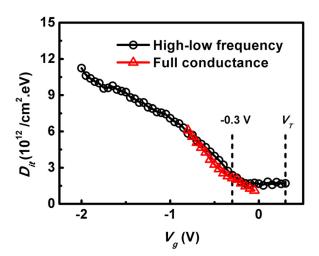

Fig. 2 shows the  $D_{it}$  vs  $V_g$  profile obtained on our fabricated Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSFET using the high  $(f=1\,\mathrm{MHz})$ -low  $(f=2\,\mathrm{kHz})$  frequency C-V method<sup>13</sup> and the full-conductance method.<sup>14</sup> It is noted that the  $D_{it}$  is intentionally plotted against  $V_g$  (not against energy) in order to identify the different  $D_{it}$  values for varying  $V_{base}$ . The  $D_{it}$

FIG. 2.  $D_{ii}$  vs  $V_g$  profile obtained using the high (f=1 MHz)-low (f=2 kHz) frequency and full-conductance methods. The  $V_T$  of 0.3 V (Fig. 3) is used to locate the In<sub>0.53</sub>Ga<sub>0.47</sub>As  $E_C$ .

$vs\ V_g$  profile presents relatively high  $D_{it}$  levels (>5.5 × 10<sup>12</sup>/cm<sup>2</sup>.eV) going towards the middle of the In<sub>0.53</sub>Ga<sub>0.47</sub>As bandgap for  $V_g$  < -0.75 V. However,  $D_{it}$  values below 2.5 × 10<sup>12</sup>/cm<sup>2</sup>.eV are observed near the In<sub>0.53</sub>Ga<sub>0.47</sub>As conduction band edge ( $E_C$ ) for  $V_g$  = -0.3 V to  $V_g$  =  $V_T$  = 0.3 V ( $V_T$  is obtained by extrapolation in the linear region of the up-trace of the single triangular pulse  $I_d$ – $V_g$  hysteresis shown in Fig. 3).

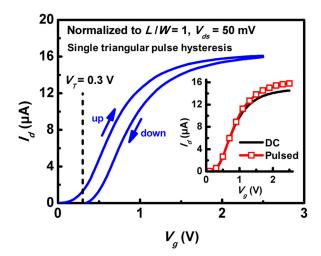

#### B. Evidence of border trap response

Recent studies have indicated the presence of border traps in high-k/InGaAs MOS structures using C-V, 15-19 charge pumping<sup>20</sup> and high-frequency transconductance<sup>21</sup> measurements. Evidence of the presence of border traps can also be observed in an  $I_d$ - $V_g$  characteristic, where it is manifest as a hysteresis loop. 22 A single triangular pulse  $I_d$ - $V_g$  hysteresis, 23 performed at  $V_{ds} = 50 \,\text{mV}$  and  $t_r = t_f = 500 \,\text{ns}$ , is shown in Fig. 3. A positive  $V_T$  shift of  $\sim 200 \,\mathrm{mV}$  is observed on the down trace, indicating electron trapping into border traps during the measurement. From Fig. 3 (inset), it is also clear that the electron trapping involves a significant  $I_d$  degradation. Indeed, the maximum  $I_d$  (at  $V_g = 2.5 \,\mathrm{V}$ ) increases from 14.5  $\mu A$  in the DC  $I_d$ - $V_g$  characteristic to 16  $\mu A$  in the pulsed  $I_{d}$ - $V_{g}$  characteristic, which represents a  $\sim$ 10% increase. This clearly indicates that a pulsed  $I_d$ – $V_g$  measurement is required to minimize  $I_d$  degradation due to border traps and extract an accurate  $\mu_{eff}$ .

### C. Inversion-charge pumping and minimization of trapped charge component

#### 1. Base voltage and interface trap response

We found that the ICP measurement configuration where  $V_{base} \approx V_{FB}$ , initially developed in Ref. 6 for a SiO<sub>2</sub>/Si interface with typical  $D_{it} < 10^{11}/\text{cm}^2.\text{eV}$  (Refs. 24 and 25), was not suitable for the studied Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSFETs due to the large  $D_{it}$  level observed towards the middle of the

FIG. 3. Single triangular pulse  $I_{d^{*}}V_{g}$  hysteresis and (inset) comparison of DC and pulsed  $I_{d^{*}}V_{g}$  characteristics. The measurements were performed at  $V_{ds} = 50 \,\mathrm{mV}$ . For the single triangular pulse  $I_{d^{*}}V_{g}$ ,  $t_{r} = t_{f} = 500 \,\mathrm{ns}$ , while for the pulsed  $I_{d^{*}}V_{g}$ ,  $t_{r} = t_{f} = 10 \,\mathrm{ns}$ , and  $f = 1 \,\mathrm{MHz}$ . A  $V_{T}$  of 0.3 V was extracted from the up-trace of the single triangular pulse  $I_{d^{*}}V_{g}$  by extrapolation in the linear region.

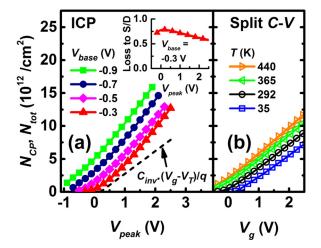

In<sub>0.53</sub>Ga<sub>0.47</sub>As bandgap (Fig. 2). Indeed, in this configuration, any interface trap with an energy level located within the semiconductor bandgap can contribute to  $N_{CP}$  and lead to an overestimation of  $N_{inv}$ . We, therefore, propose to raise  $V_{base}$  in order to maintain most of the interface traps constantly occupied during the ICP measurement and minimize the  $D_{it}$   $\Delta E$ contribution to  $N_{CP}$ . This is demonstrated in Fig. 4(a) with  $N_{CP}$  measurements obtained for  $V_{base}$  ranging from  $-0.9 \,\mathrm{V}$  to  $-0.3\,\mathrm{V}$  and corrected for the charge density lost to the S/D using (3). As  $V_{base}$  is gradually raised to -0.3 V, which corresponds to the region of the  $D_{it}$  vs  $V_g$  profile where the  $D_{it}$  is the lowest (Fig. 2), the  $N_{CP}$  vs  $V_{peak}$  curves shift downwards along the y-axis until a point where  $N_{CP}$  starts rising at  $V_{peak}$ close to  $V_T$ . This indicates that the response of the majority of the interface traps located within the In<sub>0.53</sub>Ga<sub>0.47</sub>As bandgap is removed at  $V_{base} = -0.3 \text{ V}$ .

A similar approach was used in Ref. 26, where split C-V measurements were performed at a low T of 77 K in order to "freeze" the response of the interface traps located slightly below the  $In_{0.53}Ga_{0.47}As E_C$  and extract a more accurate  $N_{inv}$ . We performed split C-V measurements over a wide range of T going from 440 K to 35 K [Fig. 4(b)] in order to verify this concept and demonstrate that varying  $V_{base}$  in an ICP measurement performed at  $T = 292 \,\mathrm{K}$  had a similar impact as varying T in a split C-V measurement. From Fig. 4(b), where the  $N_{tot}$ , which is defined here as  $N_{tot} = N_{inv} + (D_{it} + D_{bt} \cdot \Delta t_{bt}) \cdot \Delta E$ , is plotted against  $V_g$ , it is clear that the  $N_{tot}$ - $V_g$  curves exhibit a progressive reduction in  $N_{tot}$  magnitude as T reduces. The similarity between the two trends observed in Figs. 4(a) and 4(b) provides evidence to support the idea that raising  $V_{base}$  reduces the  $N_{CP}$  contribution of interface states located in the upper part of the  $In_{0.53}Ga_{0.47}As$  bandgap.

Having demonstrated the advantage of raising  $V_{base}$ , we also need to consider the issue associated with a higher  $V_{base}$ . Indeed, as  $V_{base}$  is raised towards  $V_T$ , the fraction  $(1-\alpha)$  of  $N_{inv}$  lost to the S/D increases and the correction applied to

FIG. 4. (a)  $N_{CP}$  vs  $V_{peak}$  obtained from ICP performed on a 40- $\mu$ m-channel-length device at f=1 MHz and D=50% with  $V_{base}$  ranging from -0.3 V to -0.9 V. The  $D_{it}$  contribution to  $N_{CP}$  reduces as  $V_{base}$  is raised. The curves "curl up" and deviate from the theoretical  $C_{inv}$ . $(V_g-V_t)/q$  curve. (inset) Loss to S/D  $(1-\alpha)$  vs  $V_{peak}$  obtained for  $V_{base}=-0.3$  V. (b)  $N_{tot}$  vs  $V_g$  obtained by split C-V at f=1 MHz over a range of T going from 440 K to 35 K. The  $D_{it}$  contribution to  $N_{tot}$  reduces as T is reduced.

$N_{CP}$  using (3) becomes larger. This is explained by the fact that as  $V_{base}$  increases, the barrier height of the space charge region increases, impeding the recombination of the inversion charge in the substrate and favouring its diffusion to the S/D, in agreement with Ref. 11. However, from examination of the inset of Fig. 4(a), it is evident that even with  $V_{base} = -0.3 \, \text{V}$ , the fraction  $\alpha$  of  $N_{inv}$ , which is not lost to the S/D, is still 22% or greater. Consequently, it is possible to select  $V_{base}$  to minimise the  $D_{it} \cdot \Delta E$  contribution (of interface traps at energy levels located within the  $In_{0.53}Ga_{0.47}As$  bandgap) to  $N_{CP}$  and still extract a correct  $N_{inv}$ . However, it is important to note that the remaining  $D_{it} \cdot \Delta E$  contribution to  $N_{CP}$  sets the lower limit for accurate  $N_{inv}$  extraction where  $D_{it} \cdot \Delta E$  is not negligible anymore compared to  $N_{inv}$ .

Going back to Fig. 4(a) and considering a theoretical  $C_{inv}$  of  $5.5 \times 10^{-7}$  F/cm<sup>2</sup>, obtained for the Pd/Al<sub>2</sub>O<sub>3</sub> (10 nm)/ In<sub>0.53</sub>Ga<sub>0.47</sub>As gate stack in our previous work, <sup>27</sup> we can compare the measured  $N_{CP}$ – $V_{peak}$  ( $V_{base}$  = -0.3 V) curve to a theoretical  $C_{inv}$ .( $V_g$ – $V_T$ )/q curve. From this comparison, it is clear that the  $N_{CP}$ – $V_{peak}$  curve "curls up" and significantly deviates from  $C_{inv}$ .( $V_g$ – $V_T$ )/q as  $V_{peak}$  increases. This "curling up" can be explained by the fact that the  $\Delta E$  swept by the Fermi level going from  $V_{base}$  to  $V_{peak}$  increases with  $V_{peak}$ . As a result, the  $D_{bt}$ - $\Delta t_{bt}$ - $\Delta E$  contribution to  $N_{CP}$  also increases with  $V_{peak}$ , leading to the "curling up" observed in the  $N_{CP}$ – $V_{peak}$  curves. It is noted that this assumes an increasing  $D_{bt}$ - $\Delta t_{bt}$  with  $\Delta E$ , in agreement with Refs. 4, 5, and 27.

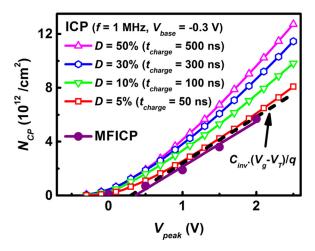

#### 2. Transient charging time and border trap response

To minimize the  $D_{bt} \cdot \Delta t_{bt} \cdot \Delta E$  contribution to  $N_{CP}$  in our ICP measurements, we propose to reduce  $t_{charge}$  by reducing D and keeping f=1 MHz. It is noted that this approach is based on the premise that, since border traps capture electrons from the inversion layer (Fig. 3), the time to charge a border trap must be larger than that required to form the inversion layer. The impact of D ( $t_{charge}$ ) on  $N_{CP}$  is presented in Fig. 5, where D ( $t_{charge}$ ) is gradually reduced from 50% (500 ns) to 5% (50 ns). The "curling up," attributed to the  $D_{bt} \cdot \Delta t_{bt} \cdot \Delta E$  contribution, gradually reduces as D reduces. At D=5%, the  $N_{CP}-V_{peak}$  curve nearly matches the theoretical  $C_{inv} \cdot (V_g-V_T)/q$  curve and the "curling up" disappears, clearly indicating that the  $D_{bt} \cdot \Delta t_{bt} \cdot \Delta E$  contribution to  $N_{CP}$  is minimized.

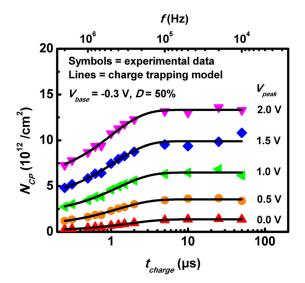

## D. Multi-frequency inversion-charge pumping for trapped charge and inversion charge separation

Fig. 6 shows MFICP measurements performed for f increasing from 10 kHz to 2 MHz with D=50%. It is noted that  $N_{CP}$  is plotted against f on the top x-axis and against  $t_{charge}$  on the bottom x-axis (as D=50%,  $t_{charge}=0.5/f$ ).  $N_{CP}$  increases as f reduces and a clear  $N_{cp}$  saturation is reached for  $f \le 100 \, \text{kHz}$  ( $t_{charge} \ge 5 \, \mu \text{s}$ ), indicating a full border trap response in that f range. In the high f region, however, no  $N_{CP}$  saturation is observed. This suggests that some border traps still respond at  $f > 2 \, \text{MHz}$ . This result is in line with the work reported in Ref. 21, where evidence of "fast" border traps responding to  $f > 1 \, \text{GHz}$  is demonstrated. Unfortunately, the

FIG. 5.  $N_{CP}$  vs  $V_{peak}$  obtained from ICP performed on a 40- $\mu$ m-channel-length device at f=1 MHz and  $V_{base}=-0.3$  V with D ( $t_{charge}$ ) varied from 50% (500 ns) to 5% (50 ns). The ICP curve at D=5% nearly matches the theoretical  $C_{inv}(V_g-V_T)/q$  curve. Note: the MFICP data obtained from Section III D are also shown to highlight the consistency between the ICP and MFICP methods.

GHz frequency range is not accessible with MFICP. Indeed, considering the model for the recombination of the electrons of the inversion layer with the holes of the *p*-type substrate

$$N_{inv}(t) = N_{inv}(0) \exp\left(-\frac{t}{\tau_e}\right),\tag{4}$$

and an electron lifetime ( $\tau_e$ ) of 30 ns for a p-In<sub>0.53</sub>Ga<sub>0.47</sub>As doping of  $4 \times 10^{17}$ /cm<sup>3</sup>, <sup>28</sup> we calculated that a channel with  $N_{inv} = 10^{11}$ /cm<sup>2</sup>,  $10^{12}$ /cm<sup>2</sup>, and  $10^{13}$ /cm<sup>2</sup> would be effectively depleted ( $N_{inv} < 10^9$ /cm<sup>2</sup>) in approximately 130 ns, 210 ns, and 270 ns, respectively. This indicates that it is not possible to perform ICP measurements at f > 2 MHz and D = 50% as the transient discharge time [ $t_{discharge} = (1 - D)/f$ ] becomes

FIG. 6.  $N_{CP}$  plotted against f on the top x-axis and against  $t_{charge} = 1/(2.f)$  on the bottom x-axis. The symbols show the experimental data obtained from the measurements performed on a 40- $\mu$ m-channel-length device with  $V_{base} = -0.3 \, \text{V}$  and D = 50%. The  $V_{peak}$  was varied from  $0 \, \text{V}$  to  $2 \, \text{V}$ . The lines represent the fitting of the data with the proposed charge trapping model (4).

too short to allow the full  $N_{inv}$  recombination, leading to an underestimation of  $N_{inv}$ . However, the use of a model to describe the variation of  $N_{CP}$  with f (or  $t_{charge}$ ) can be employed to predict  $N_{inv}$  and extract border trap distribution parameters for each value of  $V_{peak}$

$$N_{CP} = N_{inv} + D_{bt} \cdot \Delta t_{bt} \cdot \Delta E \cdot \left[1 - \exp(-(t_{charge}/\tau)^{\beta})\right], \quad (5)$$

where  $\tau$  is the capture time constant, and  $\beta$  is the distribution factor of capture cross section ( $\sigma$ ). This model is similar to the one reported in Ref. 12, but includes  $N_{inv}$  and assumes negligible  $D_{it} \Delta E$  contribution to  $N_{CP}$  owing to an appropriate  $V_{base}$  selection.

The  $\tau$ ,  $\beta$ ,  $D_{bt} \cdot \Delta t_{bt} \cdot \Delta E$ , and  $N_{inv}$  values obtained from the fitting without manual intervention of the multi-frequency  $N_{CP}$ vs  $t_{charge}$  data (Fig. 6) using (5) are summarized in Table I. Adjusted R<sup>2</sup> values ranging from 0.964 to 0.997 were obtained, indicating a good fit of the model to the experimental data. As  $V_{peak}$  increases from 0 V to 2 V, a decrease in  $\tau$  from 1.7  $\mu$ s to  $1.0 \,\mu s$  is observed, consistent with an electron distribution located closer to the Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As interface at higher  $V_{peak}$ . These  $\tau$  values are consistent with the values reported in Refs. 3, 29, and 30 for traps located at energy levels aligned with the In<sub>0.53</sub>Ga<sub>0.47</sub>As conduction band. In the charge trapping model, the distribution factor  $\beta$ , which represents the distribution width of  $\sigma$ , can range between 1.0 and 0. A  $\beta$  value of 1.0 corresponds to a discrete  $\sigma$ , while values approaching 0 indicate very wide distributions of  $\sigma$ . The fact that our experimental data are best fitted with  $\beta = 1.0$  indicates a discrete  $\sigma$ . This also suggests that the border traps are located in a plane near the Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As interface and are not distributed throughout the oxide thickness, in line with Ref. 19. Moreover, it is possible to estimate  $\sigma$  using

$$\sigma = 1/(N.v_{th}.\tau),\tag{6}$$

where N is the volume inversion density and  $v_{th}$  is the electron thermal velocity. For this demonstration,  $\sigma$  is calculated for  $V_{peak}=2\,\mathrm{V}$ , corresponding to the case where the device is in strong accumulation. Using a self-consistent Poisson-Schrödinger solver, we calculated an inversion layer thickness  $(t_{inv})$  of 14 nm for  $N_{inv}=5.7\times10^{12}/\mathrm{cm}^2$  (Table I), yielding  $N=N_{inv}/t_{inv}=4.1\times10^{18}/\mathrm{cm}^3$ . With  $N=4.1\times10^{18}/\mathrm{cm}^3$ ,  $v_{th}=5.5\times10^7\,\mathrm{cm/s}$  (Ref. 15), and  $\tau\sim1.0\,\mu\mathrm{s}$  (Table I), we obtain  $\sigma\sim5\times10^{-21}\,\mathrm{cm}^2$ . This  $\sigma$  is more than four orders of magnitude smaller than the values typically reported for interface traps in the high-k/InGaAs system. This observation is in line with Ref. 32, which brings further evidence of a charge trapping process involving tunnelling into

TABLE I. Model parameters  $\tau$ ,  $\beta$ ,  $D_{br}\Delta t_{br}\Delta E$ , and  $N_{inv}$  fitted without manual intervention over a range of  $V_{peak}$  going from 0 V to 2 V. The adjusted  $R^2$  values indicate the quality of each fit.

| V <sub>peak</sub> (V)                                               | 0     | 0.5   | 1     | 1.5   | 2     |

|---------------------------------------------------------------------|-------|-------|-------|-------|-------|

| τ (μs)                                                              | 1.7   | 1.2   | 1.2   | 1.1   | 1.0   |

| β                                                                   | 1.0   | 1.0   | 1.0   | 1.0   | 1.0   |

| $D_{bt} \cdot \Delta t_{bt} \cdot \Delta E (10^{12} / \text{cm}^2)$ | 1.4   | 2.9   | 4.6   | 6.3   | 7.8   |

| $N_{inv} (10^{12} / \text{cm}^2)$                                   | 0.1   | 0.7   | 1.9   | 3.5   | 5.7   |

| Adjusted R <sup>2</sup>                                             | 0.997 | 0.991 | 0.984 | 0.964 | 0.991 |

border traps. A distance (x) for the spatial location of the border traps relative to the  $In_{0.53}Ga_{0.47}As$  interface can be estimated using the relationship<sup>33</sup>

$$x = \lambda \ln(t/\tau),\tag{7}$$

where  $\lambda$  is the attenuation coefficient and t is the tunnelling time. Assuming a  $\lambda$  value within the typical range of  $9.8 \times 10^{-9} - 1.25 \times 10^{-8} \, \mathrm{cm}$  reported for the  $\mathrm{Al_2O_3/In_{0.53}Ga_{0.47}As}$  interface  $^{16-18,21,30}$  and considering that  $N_{CP}$  saturation is reached at  $t \sim 5 \, \mu \mathrm{s}$  (Fig. 6), we obtain a distance x of about 1.6–2.1 Å from the interface. This range of values is in agreement with other studies of border traps in the high- $k/\mathrm{InGaAs}$  system.  $^{18,21,34}$

It is noted that the discussion of the  $D_{bt} \cdot \Delta t_{bt} \cdot \Delta E$  data relies on the energy vs gate bias and trap density vs energy profiles obtained from a previous C-V study that we performed on the same set of devices as that used in this study. Moreover, since  $\Delta t_{bt}$  cannot be obtained from our ICP-based approach, a value of  $\sim 2 \,\text{Å}$  is assumed from Ref. 21. This assumption is in agreement with the extracted  $\beta$ value of 1.0 (Table I) suggesting a discrete  $\sigma$ . Therefore, considering from our previous work<sup>27</sup> that an energy range of  $\sim 0.8 \,\mathrm{eV}$  is swept when  $V_g$  goes from  $V_{base} = -0.3 \,\mathrm{V}$  to  $V_{peak} = 2 \text{ V}$  and assuming  $\Delta t_{bt} \sim 2 \text{ Å}$  (Ref. 21), a  $D_{bt} \cdot \Delta t_{bt} \cdot \Delta E$ of 7.8  $\times$  10<sup>12</sup>/cm<sup>2</sup> (Table I) equates to a  $D_{ht}$  of  $\sim$  4.9  $\times$  10<sup>20</sup>/ cm<sup>3</sup>.eV. This estimated value is comparable to the peak  $D_{bt}$ value of  $1.6 \times 10^{21}$ /cm<sup>3</sup>.eV reported in Ref. 21. Furthermore, the integration of our trap density vs energy profile across a  $\Delta E$  of  $E_C + 0.05$  eV to  $E_C + 0.35$  eV corresponding to a  $V_g$  of 0.5 V–2 V yields a trap density of  $4.4 \times 10^{12} \text{/cm}^2$ . This value is in excellent agreement with the value of  $4.9 \times 10^{12} / \text{cm}^2$ obtained by subtracting the  $D_{bt} \cdot \Delta t_{bt} \cdot \Delta E$  values obtained using the MFICP method for  $V_{peak} = 2 \text{ V}$  and 0.5 V (Table I).

This excellent agreement shows further evidence of the validity of our proposed MFICP technique for trapped charge and inversion charge separation. Moreover, the negligible  $N_{inv}$  value at  $V_{peak} = 0 \text{ V}$  is consistent with a  $V_T$  of 0.3 V (Fig. 3). As  $V_{peak}$  increases from 0.5 V to 2 V,  $N_{inv}$  increases from  $7.0 \times 10^{11}$  to  $5.7 \times 10^{12}$ /cm<sup>2</sup>. These  $N_{inv}$  values are slightly lower than those obtained using ICP with f = 1 MHzand D = 5% (Fig. 5), confirming the presence of "fast" border traps responding in less than 50 ns, in line with Ref. 21. Furthermore, it is important to note that the  $N_{inv}$  values obtained from MFICP are in excellent agreement with reported  $N_{inv}$  values obtained at the same gate overdrive using Hall measurements performed on similar Al<sub>2</sub>O<sub>3</sub>/ In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSFETs featuring sulfur passivation of the In<sub>0.53</sub>Ga<sub>0.47</sub>As interface and Al<sub>2</sub>O<sub>3</sub> thicknesses of 6 nm and 8 nm.<sup>4,5</sup>

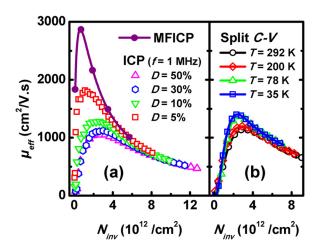

#### E. Effective mobility extraction and analysis

The effective separation of the inversion charge and the trapped charge allows for a more accurate determination of  $\mu_{eff}$ . This is shown in Fig. 7(a), where the  $\mu_{eff}$  values, extracted from the ICP (Fig. 5) and MFICP (Fig. 6) methods both combined with a pulsed  $I_{d}$ - $V_{g}$  measurement [Fig. 3 (inset)], are compared. The ICP data indicate that, as D reduces from 50% to 5%, the peak  $\mu_{eff}$  increases in

FIG. 7. (a) Comparison of  $\mu_{eff}$  vs  $N_{inv}$  extracted using the ICP (f=1 MHz, D=50%, 30%, 10%, and 5%) and MFICP methods both combined with a pulsed  $I_{d^*}V_g$  measurement. (b) Comparison of  $\mu_{eff}$  vs  $N_{inv}$  extracted from split C-V and DC  $I_{d^*}V_g$  measurements performed at T=292 K, 200 K, 78 K, and 35 K.

magnitude and its position shifts towards lower  $N_{inv}$  values. This arises from the reduction of the trapped charge component of  $N_{CP}$  with lower D, yielding a better estimation of  $N_{inv}$ . However, as MFICP enables the complete removal of the trapped charge component of  $N_{CP}$ ,  $N_{inv}$  is not overestimated and a more accurate  $\mu_{eff}$  vs  $N_{inv}$  is obtained.

The  $\mu_{eff}$  obtained with MFICP reaches 2850 cm<sup>2</sup>/V.s at  $N_{inv} = 7 \times 10^{11} \text{/cm}^2$ . It is noted that peak  $\mu_{eff}$  values ranging from 2000 to 3000 cm<sup>2</sup>/V.s were reported for high-k/ In<sub>0.53</sub>Ga<sub>0.47</sub>As devices following correction for traps aligned with the In<sub>0.53</sub>Ga<sub>0.47</sub>As conduction band.<sup>3,26,35–37</sup>A strong  $N_{inv}$  dependence is observed as  $\mu_{eff}$  rapidly drops from 2850 cm<sup>2</sup>/V.s at  $N_{inv} = 7 \times 10^{11} / \text{cm}^2$  to  $600 \text{ cm}^2 / \text{V.s}$  at  $N_{inv} = 1 \times 10^{13} \text{/cm}^2$ . This suggests a  $\mu_{eff}$  dominated by surface roughness, in agreement with Refs. 26, 35, 37, and 38. This is also confirmed by the lack of temperature dependence in the  $N_{inv} > 5 \times 10^{12} / \mathrm{cm}^2$  region of the  $\mu_{eff}$  curve [Fig. 7(b)], extracted from split C-V (f = 1 MHz) and DC  $I_d$ -V<sub>g</sub> measurements performed over a range of T going from 292 K to 35 K (not shown). However, while an increase in  $\mu_{eff}$  is observed for  $N_{inv} < 5 \times 10^{12} / \text{cm}^2$  as T reduces, consistent with Ref. 26, it is very clear that some of the trapped charge cannot be "frozen out" with low T, which confirms the presence of a temperature-independent charge trapping involving tunnelling into border Consequently, the peak  $\mu_{eff}$  extracted from low-T split C-V remains lower than that extracted with the ICP (D=5%)and MFICP methods. This brings further evidence of the relevance of our proposed MFICP approach and highlights the limitation of the split C-V technique for accurate  $\mu_{eff}$  vs  $N_{inv}$  extraction in high-k/InGaAs MOSFETs featuring relatively large  $D_{bt}$ .

#### **IV. CONCLUSIONS**

We successfully demonstrated the separation of the inversion charge and the trapped charge in high-k/InGaAs MOSFETs using our proposed MFICP technique. This approach offers the advantage of only requiring

measurements performed at room temperature on a single long-channel MOSFET. The obtained values for the border trap capture time constant, capture cross section, spatial location, and density were all in line with the most recent literature values, confirming the validity of the technique. Finally, the comparison of the  $\mu_{eff}$  vs  $N_{inv}$  extracted from the MFICP and split C-V techniques highlighted the limitation of the split C-V approach for high-k/InGaAs MOSFETs featuring relatively large  $D_{bv}$ .

#### **ACKNOWLEDGMENTS**

This work was supported by Science Foundation Ireland under the FORME Strategic Research Cluster Award No. 07/SRC/I1172F and in part by the European Commission through the project entitled "Compound Semiconductors for 3D Integration COMPOSE3" under Grant No. FP7-ICT-2013-11-619325 and the project entitled "III-V MOS" under Grant No. FP7-ICT-11-619326. The work of M.A.N. was supported by the Irish Research Council for Science, Engineering and Technology (IRCSET)-Marie Curie International Mobility Fellowship in Science, Engineering and Technology. The help from Mr. Dan O'Connell, Mrs. Carmel Murphy, Dr. Éamon O'Connor, and Dr. Ian M. Povey for the sample preparation and the support from Mr. John MacHale for the cryogenic probe station operation are gratefully acknowledged.

<sup>1</sup>J. A. del Alamo, Nature **479**, 317 (2011).

<sup>2</sup>K. Romanjek, F. Andrieux, T. Ernst, and G. Ghibaudo, IEEE Electron Device Lett. **25**, 583 (2004).

<sup>3</sup>A. Ali, H. Madan, S. Koveshnikov, S. Oktyabrsky, R. Kambhampati, T. Heeg, D. Schlom, and S. Datta, IEEE Trans. Electron Devices **57**, 742 (2010).

<sup>4</sup>N. Taoka, M. Yokoyama, S. H. Kim, R. Suzuki, R. Iida, S. Lee, T. Hoshii, W. Jevasuwan, T. Maeda, T. Yasuda, O. Ichikawa, N. Fukuhara, M. Hata, M. Takenaka, and S. Takagi, IEEE Int. Electron Devices Meet., Tech. Dig. **2011**, 27.2.1.

<sup>5</sup>N. Taoka, M. Yokoyama, S. H. Kim, R. Suzuki, S. Lee, R. Iida, T. Hoshii, W. Jevasuwan, T. Maeda, T. Yasuda, O. Ichikawa, N. Fukuhara, M. Hata, M. Takenaka, and S. Takagi, IEEE Trans. Device Mater. Reliab. 13, 456 (2013).

<sup>6</sup>A. Kerber, E. Cartier, L.-A. Ragnarsson, M. Rosmeulen, L. Pantisano, R. Degraeve, Y. Kim, and G. Groeseneken, in *VLSI Technical Digest*, 2003, p. 159.

<sup>7</sup>V. Djara, K. Cherkaoui, M. Schmidt, S. Monaghan, É. O'Connor, I. Povey, D. O'Connell, M. Pemble, and P. K. Hurley, IEEE Trans. Electron Devices **59**, 1084 (2012).

8É. O'Connor, B. Brennan, V. Djara, K. Cherkaoui, S. Monaghan, S. B. Newcomb, R. Contreras, M. Milojevic, G. Hughes, M. E. Pemble, R. M. Wallace, and P. K. Hurley, J. Appl. Phys. 109, 024101 (2011).

<sup>9</sup>G. Groeseneken, H. E. Maes, N. Beltran, and R. F. De Keersmaecker, IEEE Trans. Electron Devices **31**, 42 (1984).

<sup>10</sup>Y. Son, S. Park, T. Kang, B. Oh, and H. Shin, IEEE Trans. Electron Devices **58**, 2752 (2011).

<sup>11</sup>G. Van den Bosch, G. Groeseneken, and H. E. Maes, IEEE Electron Device Lett. 14, 107 (1993).

<sup>12</sup>S. Zafar, A. Callegari, E. Gusev, and M. V. Fischetti, J. Appl. Phys. 93, 9298 (2003).

<sup>13</sup>R. Castagné and A. Vapaille, Surf. Sci. **28**, 157 (1971).

<sup>14</sup>K. Martens, C. O. Chui, G. Brammertz, B. De Jaeger, D. Kuzum, M. Meuris, M. M. Heyns, T. Krishnamohan, K. Saraswat, H. Maes, and G. Groeseneken, IEEE Trans. Electron Devices 55, 547 (2008).

<sup>15</sup>G. Brammertz, A. Alian, D.-C. Lin, M. Meuris, M. Caymax, and W. E. Wang, IEEE Trans. Electron Devices 58, 3890 (2011).

<sup>16</sup>Y. Yuan, L. Wang, B. Yu, B. Shin, J. Ahn, P. C. McIntyre, P. Asbeck, M. J. W. Rodwell, and Y. Taur, IEEE Electron Device Lett. 32, 485 (2011).

- <sup>17</sup>H.-P. Chen, Y. Yuan, B. Yu, J. Ahn, P. C. McIntyre, P. M. Asbeck, M. J. W. Rodwell, and Y. Taur, IEEE Trans. Electron Devices 59, 2383 (2012).

- <sup>18</sup>Y. Yuan, B. Yu, J. Ahn, P. C. McIntyre, P. M. Asbeck, M. J. W. Rodwell, and Y. Taur, IEEE Trans. Electron Devices 59, 2100 (2012).

- <sup>19</sup>J. Lin, Y. Y. Gomeniuk, S. Monaghan, I. M. Povey, K. Cherkaoui, É. O'Connor, M. Power, and P. K. Hurley, J. Appl. Phys. 114, 144105

- <sup>20</sup>M. E. Ramón, T. Akyol, D. Shahrjerdi, C. D. Young, J. Cheng, L. F. Register, and S. K. Banerjee, Appl. Phys. Lett. 102, 022104 (2013).

- <sup>21</sup>S. Johansson, M. Berg, K.-M. Persson, and E. Lind, IEEE Trans. Electron Devices 60, 776 (2013).

- <sup>22</sup>R. Degraeve, A. Kerber, E. Cartier, L. Pantisano, and G. Groeseneken, in International Semiconductor Device Research Symposium (ISDRS), 2003,

- p. 322. <sup>23</sup>A. Kerber, E. Cartier, L. Pantisano, M. Rosmeulen, R. Degraeve, T. Kauerauf, G. Groeseneken, H. E. Maes, and U. Schwalke, in IEEE International Reliability Physics Symposium (IRPS), 2003, p. 41.

- <sup>24</sup>A. Kerber, E. Cartier, L. Pantisano, R. Degraeve, T. Kauerauf, Y. Kim, A. Hou, G. Groeseneken, H. Maes, and U. Schwalke, IEEE Electron Device Lett. 24, 87 (2003).

- <sup>25</sup>D. Bauza, Solid-State Electron. **47**, 1677 (2003).

- <sup>26</sup>C. L. Hinkle, A. M. Sonnet, R. A. Chapman, and E. M. Vogel, IEEE Electron Device Lett. 30, 316 (2009).

- <sup>27</sup>V. Djara, T. P. O'Regan, K. Cherkaoui, M. Schmidt, S. Monaghan, É. O'Connor, I. M. Povey, D. O'Connell, M. E. Pemble, and P. K. Hurley, Microelectron. Eng. 109, 182 (2013).

- <sup>28</sup>R. K. Ahrenkiel, R. Ellingson, S. Johnston, and M. Wanlass, Appl. Phys. Lett. 72, 3470 (1998).

- <sup>29</sup>D. Lin, A. Alian, S. Gupta, B. Yang, E. Bury, S. Sioncke, R. Degraeve, M. L. Toledano, R. Krom, P. Favia, H. Bender, M. Caymax, K. C. Saraswat, N. Collaert, and A. Thean, IEEE Int. Electron Devices Meet., Tech. Dig. 2012, 28.3.1.

- <sup>30</sup>R. V. Galatage, D. M. Zhernokletov, H. Dong, B. Brennan, C. L. Hinkle, R. M. Wallace, and E. M. Vogel, J. Appl. Phys. 116, 014504 (2014).

- <sup>31</sup>W. Wang, J. Deng, J. C. M. Hwang, Y. Xuan, Y. Wu, and P. D. Ye, Appl. Phys. Lett. 96, 072102 (2010).

- <sup>32</sup>E. J. Kim, L. Wang, P. M. Asbeck, K. C. Saraswat, and P. C. McIntyre, Appl. Phys. Lett. 96, 012906 (2010).

- <sup>33</sup>F. Heiman and G. Warfield, IEEE Trans. Electron Devices 12, 167

- <sup>34</sup>A. Vais, H.-C. Lin, C. Dou, K. Martens, T. Ivanov, Q. Xie, F. Tang, M. Givens, J. Maes, N. Collaert, J.-P. Raskin, K. DeMeyer, and A. Thean, Appl. Phys. Lett. 107, 053504 (2015).

- <sup>35</sup>M. A. Negara, V. Djara, T. O'Regan, K. Cherkaoui, M. Burke, Y. Gomeniuk, M. Schmidt, É. O'Connor, I. Povey, A. Quinn, and P. K. Hurley, Solid-State Electron. 88, 37 (2013).

- <sup>36</sup>Y. Xuan, Y. Q. Wu, H. C. Lin, T. Shen, and P. D. Ye, IEEE Electron Device Lett. 28, 935 (2007).

- <sup>37</sup>T. P. O'Regan, M. V. Fischetti, B. Sorée, S. Jin, W. Magnus, and M. Meuris, J. Appl. Phys. 108, 103705 (2010).

- <sup>38</sup>W. Wang, J. Hwang, Y. Xuan, and P. Ye, IEEE Trans. Electron Devices **58**, 1972 (2011).