# LOW ENERGY SOLUTIONS FOR MULTI– AND TRIPLE–LEVEL CELL NON-VOLATILE MEMORIES

by

# Ali Alsuwaiyan

B.Sc. in Computer Engineering, King Fahd University, 1998M.Sc. in Computer Engineering, King Fahd University, 2002

Submitted to the Graduate Faculty of the Swanson School of Engineering in partial fulfillment of the requirements for the degree of

# **Doctor of Philosophy**

University of Pittsburgh

2017

#### UNIVERSITY OF PITTSBURGH

#### SWANSON SCHOOL OF ENGINEERING

This dissertation was presented

by

Ali Alsuwaiyan

It was defended on

May 11, 2017

and approved by

Kartik Mohanram, PhD, Associate Professor

Department of Electrical and Computer Engineering, University of Pittsburgh

Hai (Helen) Li, PhD, Associate Professor

Department of Electrical and Computer Engineering, Duke University

Zhi-Hong Mao, PhD,

Department of Electrical and Computer Engineering, University of Pittsburgh

Natasa Miskov-Zivanov, PhD, Assistant Professor

Department of Electrical and Computer Engineering, University of Pittsburgh

Youtao Zhang, PhD, Associate Professor

Computer Science Department, University of Pittsburgh

Dissertation Director: Kartik Mohanram, PhD, Associate Professor

Department of Electrical and Computer Engineering, University of Pittsburgh

Copyright © by Ali Alsuwaiyan 2017

# LOW ENERGY SOLUTIONS FOR MULTI– AND TRIPLE–LEVEL CELL NON-VOLATILE MEMORIES

Ali Alsuwaiyan, PhD

University of Pittsburgh, 2017

Due to the high refresh power and scalability issues of DRAM, non-volatile memories (NVM) such as phase change memory (PCM) and resistive RAM (RRAM) are being actively investigated as viable replacements of DRAM. However, although these NVMs are more scalable than DRAM, they have shortcomings such as higher write energy and lower endurance. Further, the increased capacity of multi- and triple-level cells (MLC/TLC) in these NVM technologies comes at the cost of even higher write energies and lower endurance attributed to the MLC/TLC program-and-verify (P&V) techniques.

This dissertation makes the following contributions to address the high write energy associated with MLC/TLC NVMs. First, we describe MFNW, a Flip-N-Write encoding that effectively reduces the write energy and improves the endurance of MLC NVMs. MFNW encodes an MLC/TLC word into a number of codewords and selects the one resulting in lowest write energy. Second, we present another encoding solution that is based on perfect knowledge frequent value encoding (FVE). This encoding technique leverages machine learning to cluster a set of general-purpose applications according to their frequency profiles and generates a dedicated offline FVE for every cluster to maximize energy reduction across a broad spectrum of applications. Whereas the proposed encodings are used as an add-on layer on top of the MLC/TLC P&V solutions, the third contribution is a low latency, low energy P&V (L<sup>3</sup>EP) approach for MLC/TLC PCM. The primary motivation of L<sup>3</sup>EP is to fix the problem from its origin by crafting a higher speed programming algorithm. A reduction in write latency implies a reduction in write energy as well as an improvement in cell endurance.

Directions for future research include the integration and evaluation of a software-based hybrid encoding mechanism for MLC/TLC NVMs; this is a page-level encoding that employs a DRAM cache for coding/decoding purposes. The main challenges include how the cache block replacement algorithm can easily access the page-level auxiliary cells to encode the cache block correctly. In summary, this work presents multiple solutions to address major challenges of MLC/TLC NVMs, including write latency, write energy, and cell endurance.

### TABLE OF CONTENTS

| 1.0 | <b>INTRODUCTION</b>                              |

|-----|--------------------------------------------------|

|     | 1.1 Contributions                                |

|     | 1.1.1 MFNW: An MLC/TLC Flip-N-Write Architecture |

|     | 1.1.2 Frequent Value Encoding                    |

|     | 1.1.3 $L^{3}EP$                                  |

|     | 1.2 Thesis Organization                          |

| 2.0 | BACKGROUND                                       |

|     | 2.1 Basics of NVMs                               |

|     | 2.2 Review of Encoding Solutions                 |

|     | 2.3 P&V Related Background                       |

| 3.0 | MFNW: AN MLC/TLC FLIP-N-WRITE ARCHITECTURE       |

|     | 3.1 Contributions                                |

|     | 3.1.1 MLC FNW (MFNW)                             |

|     | 3.1.2 Cell Hamming Distance (CHD) MFNW           |

|     | 3.1.3 Energy Hamming Distance (EHD) MFNW         |

|     | 3.1.4 TFNW: TLC Flip-N-Write                     |

|     | 3.1.5 Further Energy Reductions                  |

|     | 3.1.6 Endurance Evaluation                       |

|     | 3.2 Evaluation and Results                       |

|     | 3.3 Conclusions                                  |

|     | 3.4 Appendix                                     |

| <b>4.0</b> | AN OFFLINE FREQUENT VALUE ENCODING FOR ENERGY-EFFICIENT                  |    |

|------------|--------------------------------------------------------------------------|----|

|            | MLC/TLC NON-VOLATILE MEMORIES                                            | 47 |

|            | 4.1 Contributions                                                        | 49 |

|            | 4.1.1 Memory Trace Clustering                                            | 50 |

|            | 4.1.2 Code Generation                                                    | 51 |

|            | 4.1.3 Hardware Realization                                               | 53 |

|            | 4.2 Evaluation and Results                                               | 55 |

|            | 4.3 Conclusions                                                          | 61 |

| 5.0        | L <sup>3</sup> EP: A LOW LATENCY, LOW ENERGY PROGRAM-AND-VERIFY APPROACE | 62 |

|            | 5.1 Contributions                                                        | 63 |

|            | 5.1.1 L <sup>3</sup> EP                                                  | 63 |

|            | 5.1.1.1 L <sup>3</sup> EP amorphization regression model                 | 64 |

|            | 5.1.1.2 L <sup>3</sup> EP crystallization                                | 67 |

|            | 5.1.2 Parameter Optimization                                             | 68 |

|            | 5.2 Results                                                              | 70 |

|            | 5.2.1 Cell-Level Evaluation                                              | 70 |

|            | 5.2.2 Full System Simulation                                             | 80 |

|            | 5.2.3 Hardware overhead                                                  | 86 |

|            | 5.3 Conclusions                                                          | 89 |

| 6.0        | FUTURE PLAN                                                              | 90 |

| BIB        | BLIOGRAPHY                                                               | 94 |

### LIST OF TABLES

| 3.1 | Write energies for MLC states                         | 28 |

|-----|-------------------------------------------------------|----|

| 3.2 | Write energies for TLC states                         | 29 |

| 3.3 | Memory traces for different SPEC CPU2006 benchmarks   | 35 |

| 4.1 | MLC/TLC memory line organization and NVM overhead     | 55 |

| 4.2 | Estimation of ROM overhead of the proposed FVE scheme | 56 |

| 5.1 | Goodness of fits                                      | 65 |

| 5.2 | PCM cell and access device parameters                 | 71 |

| 5.3 | Full system specifications                            | 83 |

| 5.4 | Workloads specifications                              | 84 |

| 5.5 | MPKI for various workloads                            | 84 |

| 6.1 | Resistance bounds of some TLC states                  | 92 |

### LIST OF FIGURES

| 2.1  | An illustration of SLC FNW                                 | 10 |

|------|------------------------------------------------------------|----|

| 2.2  | Effect of aggregating incompatible frequency profiles      | 12 |

| 2.3  | SCUP flowchart                                             | 16 |

| 2.4  | PIDP flowchart                                             | 16 |

| 2.5  | AOP flowchart                                              | 17 |

| 3.1  | Illustration of CHD MFNW                                   | 24 |

| 3.2  | Accuracy of the proposed model (Eq. 3.2)                   | 27 |

| 3.3  | CHD vs EHD MFNW                                            | 29 |

| 3.4  | Reusing the components of MFNW to construct MFNW2.         | 31 |

| 3.5  | The effect of different transformation on energy reduction | 32 |

| 3.6  | MFNW energy consumption                                    | 36 |

| 3.7  | Number of writes broken down by MLC states                 | 37 |

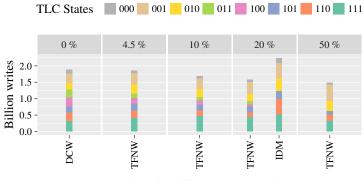

| 3.8  | TNFW energy consumption                                    | 38 |

| 3.9  | Number of writes broken down by TLC states                 | 38 |

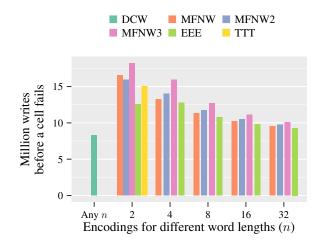

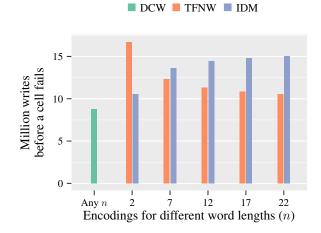

| 3.10 | MFNW endurance                                             | 39 |

| 3.11 | TFNW endurance                                             | 40 |

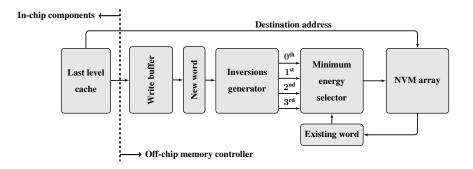

| 3.12 | MFNW write path                                            | 40 |

| 3.13 | Inversion index                                            | 43 |

| 4.1  | Memory word organization for the proposed FVE scheme       | 50 |

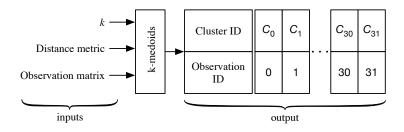

| 4.2  | Output of <i>k</i> -medoids clustering algorithm           | 52 |

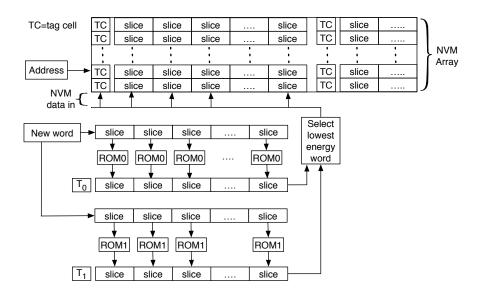

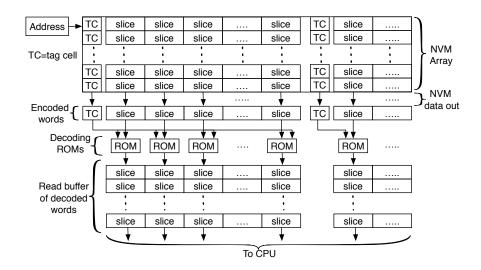

| 4.3  | Encoding path of the proposed FVE scheme                   | 54 |

| 4.4  | Encoding path of the proposed FVE scheme                   | 54 |

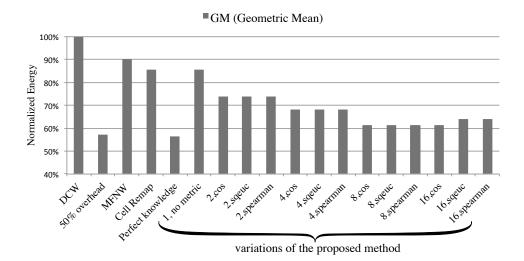

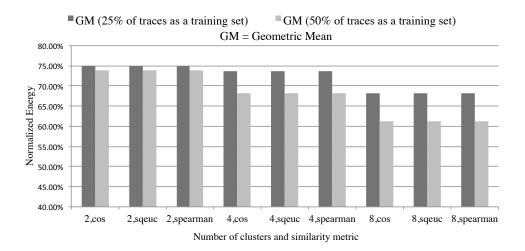

| 4.5  | MLC energy consumption results of the proposed FVE scheme                         | 57 |

|------|-----------------------------------------------------------------------------------|----|

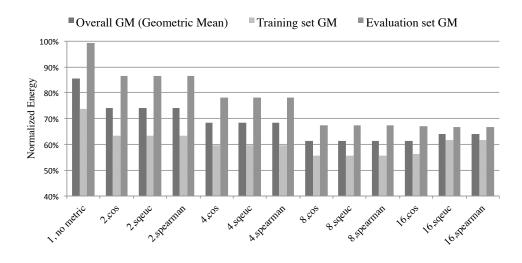

| 4.6  | MLC training and evaluation sets energy consumptions                              | 58 |

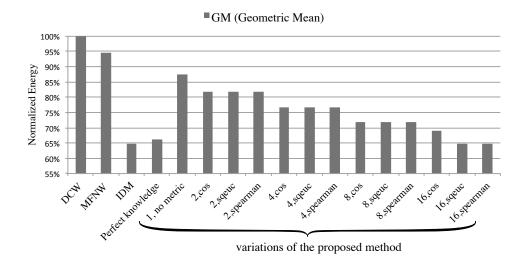

| 4.7  | TLC energy consumption results of the proposed FVE scheme                         | 59 |

| 4.8  | TLC training and evaluation sets energy consumptions                              | 59 |

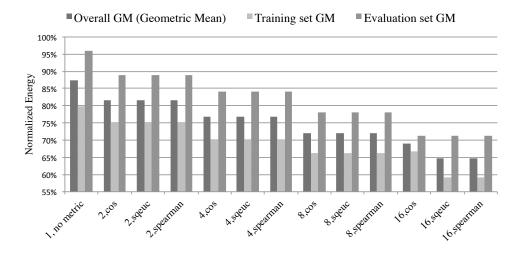

| 4.9  | Evaluating the robustness of the proposed FVE scheme for MLC                      | 60 |

| 4.10 | Evaluating the robustness of the proposed FVE scheme for MLC                      | 60 |

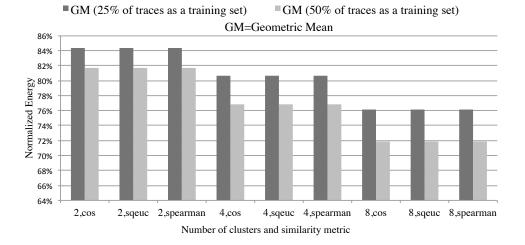

| 5.1  | $L^{3}EP$ flowchart                                                               | 64 |

| 5.2  | $L^{3}EP$ amorphization based on Example 1                                        | 66 |

| 5.3  | $L^{3}EP$ crystallization based on Example 2                                      | 67 |

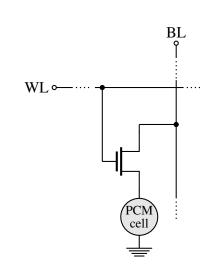

| 5.4  | 1T1R PCM cell                                                                     | 71 |

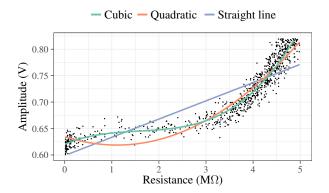

| 5.5  | Resistance/voltage regression analysis                                            | 73 |

| 5.6  | Resistances histograms                                                            | 73 |

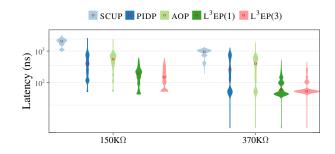

| 5.7  | Cell-level write latencies                                                        | 73 |

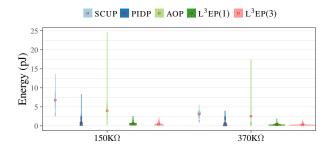

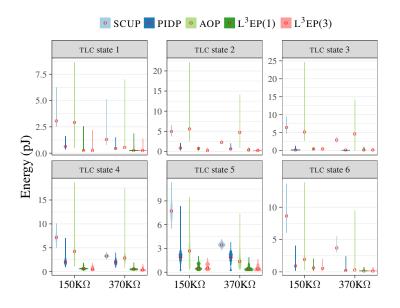

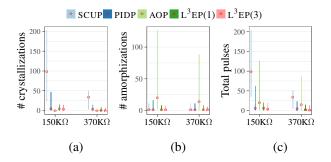

| 5.8  | Cell-level write energies by TLC state                                            | 74 |

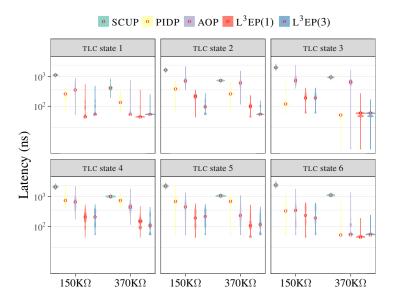

| 5.9  | Cell-level write latencies by TLC state for PIDP, $L^{3}EP(1)$ , and $L^{3}EP(3)$ | 74 |

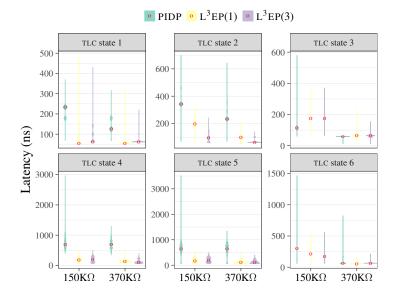

| 5.10 | Cell-level write energies                                                         | 75 |

| 5.11 | Cell-level write energies by TLC state                                            | 75 |

| 5.12 | Cell-level write energies by TLC state for PIDP, $L^{3}EP(1)$ , and $L^{3}EP(3)$  | 76 |

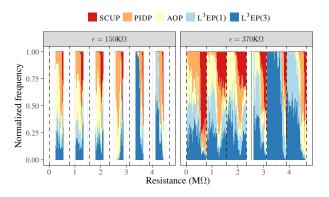

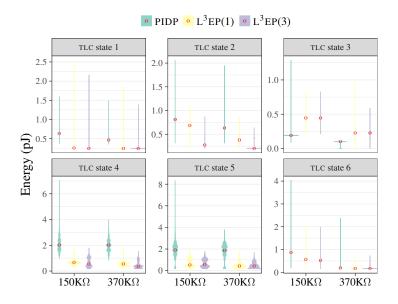

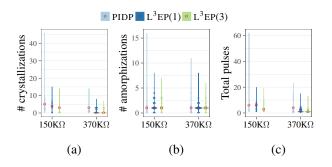

| 5.13 | Distributions of different pulse types for various P&V approaches                 | 76 |

| 5.14 | Distributions of different pulse types for PIDP, $L^3EP(1)$ , and $L^3EP(3)$      | 77 |

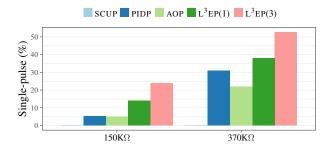

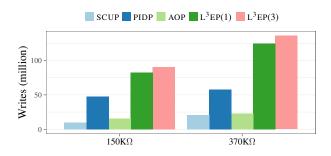

| 5.15 | MC Iterations converging in one pulse                                             | 77 |

| 5.16 | Endurance of various P&V approaches                                               | 77 |

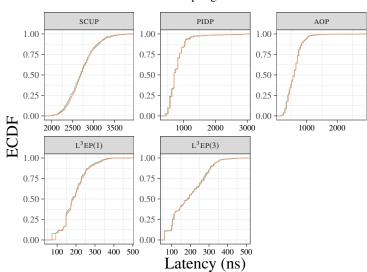

| 5.17 | Comparison of the ECDFs                                                           | 83 |

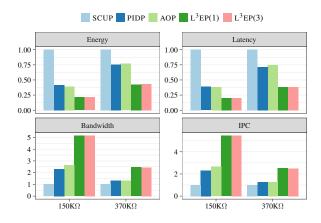

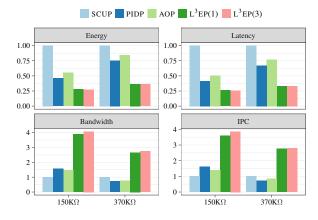

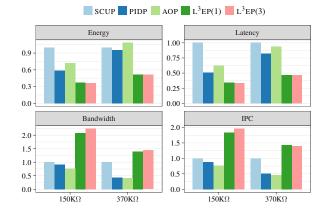

| 5.18 | Performance metrics for Case (i) simulation setup                                 | 85 |

| 5.19 | Performance metrics for Case (ii) simulation setup                                | 86 |

| 5.20 | Performance metrics for Case (iii) simulation setup                               | 87 |

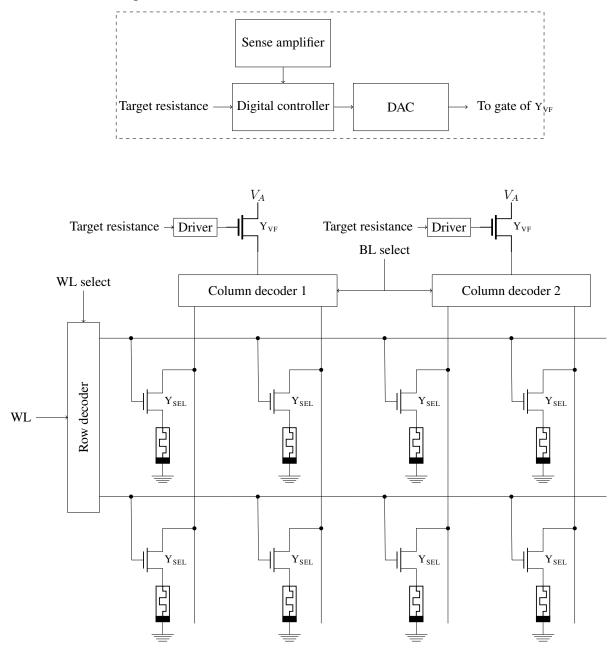

| 5.21 | An example PCM array with two L3EP drivers                                        | 88 |

#### **1.0 INTRODUCTION**

The performance of a computer system heavily depends on the memory subsystem, especially DRAM. Multicore CPUs and parallel processing enable another performance-boosting dimension; however, this performance is bottlenecked by DRAM scalability issue. The issue is due to the fact that DRAM stores bits using capacitors, and DRAM industry faces difficulties in down-scaling DRAM capacitors below 22 nm, due to considerable static and dynamic power requirements [ITRS 2011]. Whereas ideas have been proposed to mitigate this scalability issue of DRAM, e.g., [Mutlu 2013, Liu *et al.* 2012], these ideas only defer the inevitable fact that pure DRAM-based computer systems are going to hit the memory wall.

The continuous demand for higher performance systems has led to extensive research to find a more scalable memory technology, e.g., phase change memory (PCM) [Lee *et al.* 2009] and resistive RAM (RRAM) [Baek *et al.* 2004]. In comparison to DRAM, these technologies are resistance-based, in which logic values correspond to the value of the resistance of the cell. This property makes them more scalable, have an extended data retention time (i.e., non-volatility), and consume only negligible static power.

Even though PCM and RRAM are more scalable than DRAM, they have their own shortcomings too. First, they require higher read latencies and energies than traditional DRAM. Second, they require much higher write latencies and energies in comparison to DRAM. Third, they suffer from a limited cell endurance. These shortcomings must be addressed to make PCM and RRAM viable replacements for DRAM.

Being resistance-based memories, and due to the huge gap between on- and off-resistances, these NVMs can be utilized to store more than one logical bit in one physical cell. This is referred to multi/triple-level cell (MLC/TLC) NVMs in the literature [Nirschl *et al.* 2007, Kang *et al.* 2008, Xu *et al.* 2013]. In this work, we assume that MLC refers to a physical cell that can store 2

logical bits, and TLC refers a cell that can store 3 logical bits. While MLC/TLC enable realizing density and cost advantages, they also aggravate the problems of these NVM technologies, namely, energy, latency, and endurance.

Data encoding solutions (e.g. [Li and Mohanram 2014, Dgien *et al.* 2014, Mirhoseini *et al.* 2012]) try to reduce write energy in NVM technologies. They also implicitly improve NVM endurance [Wang *et al.* 2011], and (in some cases) improve access latency [Niu *et al.* 2013]. Frequent value encoding (FVE) was originally introduced to encode data and address buses [Yang and Gupta 2002, Yang *et al.* 2004, Suresh *et al.* 2009]. FVE can achieve high reductions in NVM write energy by mapping frequent values (words) into low energy codewords. Recently, FVE has been proposed to encode SLC memory words in PCM [Sun *et al.* 2011]. The authors investigated both static (offline) encoding and dynamic (online) encoding. They report that although offline encoding (originally introduced in [Yang and Gupta 2002] by the name "find-once for a given program") achieves higher energy reductions on average, it requires support from compilers and operating system, and therefore, it is infeasible. On the other hand, online encoding provides good energy savings, but requires a non-trivial online profiling effort and therefore affects the overall system performance.

#### **1.1 CONTRIBUTIONS**

This work presents three main ideas to mitigate the shortcomings of NVMs:

- 1. We present an MLC/TLC version of the Flip-N-Write encoding referred to as MFNW [Alsuwaiyan and Mohanram 2015] with the main objective of reducing write energy.

- 2. We introduce an MLC/TLC version of the FVE encoding that employs machine learning to find perfect codes [Alsuwaiyan and Mohanram 2016] to reduce write energy.

- 3. We propose low latency, low energy program-and-verify (P&V) approach, referred to as L<sup>3</sup>EP, that simultaneously improves MLC/TLC PCM endurance and significantly reduces its write latency and energy in comparison to state-of-the-art P&V for MLC/TLC PCM.

The following subsections present high level summaries of these ideas and break them down by finer grain contributions.

#### 1.1.1 MFNW: An MLC/TLC Flip-N-Write Architecture

The first idea introduces a Flip-N-Write algorithm that is explicitly tailored for MLC NVMs (MFNW). To the best of our knowledge, this is the first work that generalizes the original Flip-N-Write (FNW) algorithm for MLC NVMs. The key idea is the use of cell inversions in place of bit flipping to evaluate encoded forms of the new word for energy reduction.

Below is a break down of the contributions related to MFNW:

- We introduce and investigate two possible variations of the MFNW algorithm: cell Hamming distance (CHD) MFNW and energy Hamming distance (EHD) MFNW. We show that EHD MFNW is more effective in write energy reduction (Section 3.1.3).

- We develop an approximate probabilistic model to facilitate the theoretical analysis of MFNW. This includes the derivation of a closed form expression for the expected number of cell writes in CHD MFNW (Eq. 3.2 in Section 3.1.2). This expression helps determining the optimal word length that maximizes write energy reduction subject to memory overhead constraints. Simulation results show that the closed form expression incurs a negligible error of 1.4% for the chosen sample of word lengths.

- We introduce and evaluate TFNW, the TLC version of MFNW, for TLC NVMs (Section 3.1.4).

- We derive MFNW2 and MFNW3 to further reduce write energy beyond MFNW (Section 3.1.5).

- We propose a cost-aware endurance evaluation that accurately models MFNW/TNFW effects on NVM lifetime in comparison to state-of-the-art MLC/TLC solutions (Section 3.1.6).

**Evaluation:** Even though MFNW and TFNW are independent of the choice of NVM technology, we evaluate them for the two-bits-per-cell MLC PCM prototype and the three-bits-per-cell TLC RRAM proposed in [Bedeschi *et al.* 2009] and [Xu *et al.* 2013], respectively. We estimate the hardware and delay overheads required to implement MFNW and TFNW for these prototypes. Also, we compare the endurance and average write energy of MFNW with state-of-the-art MLC PCM encoding solutions: data comparison write (DCW) [Yang *et al.* 2007], the energy efficient encoding (EEE) in [Wang *et al.* 2011], and the two-to-three (TTT) encoding in [Mirhoseini *et al.*

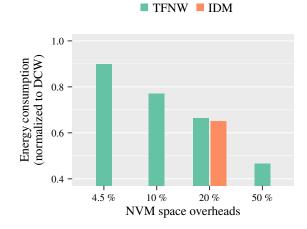

2015]. The same comparison is also carried out for TLC RRAM between TFNW and incomplete data mapping (IDM) encoding [Niu *et al.* 2013].

**Results:** We evaluate MFNW for both MLC PCM and TLC RRAM. MLC PCM results indicate that MFNW achieves up to 39% energy saving over DCW; with MFNW3, the energy saving can be as much as 47% over DCW. Using the proposed endurance evaluation, MFNW, without using any wear-leveling or error-correction techniques, can prolong memory lifetime by up to 100% in comparison to DCW. For TLC RRAM results, TFNW achieves up to 53% energy saving over DCW and, without using any wear-leveling or error-correction techniques, it is capable of extending the lifetime of RRAM NVM by up to 87% in comparison to DCW. Detailed findings and comparisons with state-of-the-art encoding solutions are presented in Section 3.2.

#### 1.1.2 Frequent Value Encoding

The second idea presents an offline frequent value encoding (FVE) for MLC/TLC NVMs that achieves an average write energy reduction approaching, and sometimes exceeding, that of optimal offline encoding [Yang and Gupta 2002]. The proposed method, which does not require compiler or operating system support, is based on finding multiple optimal FVEs. Each FVE is derived by aggregating the data frequency profiles of a group of compatible applications. To the best of our knowledge, this is the first work that presents a feasible version of an offline FVE approaching the average energy reductions of optimal offline FVE.

Below is a break down of the contributions related to the proposed FVE solution:

- We describe the use of k-medoids algorithm [Park and Jun 2009] to cluster a set of generalpurpose benchmark applications (SPEC CPU2006 [SPEC CPU 2006]) into k groups, in which each group contains compatible set of applications. The applications are represented as an observation matrix consisting of rows of feature sets that are essential inputs to the k-medoids algorithm (Section 4.1.1).

- We process the output of the *k*-medoids algorithm to produce offline, low overhead, energyefficient FVEs. The objective is to reach the write energy of optimal offline FVE while avoiding its disadvantages (Section 4.1.2). The proposed codec (coder/decoder) architecture uses read-

only memories (ROMs) that are known to consume low power/energy in comparison to lookup tables (LUTs) and content-addressable memories (CAMs) (Section 4.1.3).

**Evaluation:** For a realistic evaluation of the proposed FVE solution, we divide the set of benchmark applications into training and evaluation sets. The training set is used to derive the k offline FVE mappings, which are then used to encode the applications in the evaluation set. The energy saving of our solution across the evaluation set is an accurate indicator of its quality against other new applications that are not considered in this work. However, the training set should accurately model the class of applications to be expected. For example, in this work, the training set models a broad set of general-purpose applications (SPEC benchmarks).

**Results:** We evaluate the proposed FVE solution for both MLC PCM and TLC RRAM. MLC PCM results indicate that average write energy is only 5% more than that of the optimal offline FVE. The result is even better in the TLC RRAM case, where the average write energy of the proposed technique is 1% less than that of the optimal offline FVE. In comparison to the write energies of the MLC and TLC DCW [Yang et al. 2007], the proposed solution achieves 39% and 35% energy savings, respectively, while the memory overhead in both cases for our solution does not exceed 3.5%. We report the results of our proposed solution for different values of k (the number of clusters), and for some values, our method results in average write energy that is only 4% more than that of the state-of-the-art MLC PCM TTT encoding in [Mirhoseini et al. 2015]. However, the big difference is that TTT requires 50% NVM overhead ( $16 \times$  more than ours) for the case study presented in that paper. While the 50% overhead of TTT can be reduced significantly, we argue that the reduction will result in exponentially larger sizes of LUTs than the sizes of our codec ROMs. For TLC RRAM, our method results in the same average write energy as IDM [Niu et al. 2013]. However, IDM has a memory overhead of 20%, i.e.,  $5.7 \times$  more than the proposed work. Detailed findings and comparisons with state-of-the-art encoding solutions are presented in Section 4.2.

#### 1.1.3 $L^{3}EP$

Whereas encoding schemes try to alleviate the side effects of P&V approaches, our third idea is a low latency, low energy (L<sup>3</sup>EP) P&V approach for MLC/TLC PCM. L<sup>3</sup>EP simultaneously reduces the write latency and energy, and improves the endurance of PCM cells.

Below is a break down of the contributions related to  $L^3EP$ :

- L<sup>3</sup>EP utilizes a multiple linear regression model to reach the target TLC state in just one (at most five) pulse(s) for 53% (>95%) of our comprehensive Monte Carlo (MC) simulations.

- L<sup>3</sup>EP also accelerates the naturally slow PCM crystallization process by packing crystallization pulses separated by short idle periods, and augmenting them with a single verify step. L<sup>3</sup>EP thus avoids unnecessary P&V verification steps resulting in faster crystallization over state-ofthe-art P&V approaches.

- We describe a comprehensive framework to compute critical L<sup>3</sup>EP P&V-related parameters for multiple technology nodes (Section 5.1.2). The framework uses a series of MC simulations and optimizations imposing bounds on those parameters for the target technology node. Although this work focuses on TLC PCM, it can also be applied to MLC PCM through appropriate write margin and resistance ranges parameterization, as explained in Section 5.1.2.

**Evaluation:** We compare L<sup>3</sup>EP to three state-of-the-art TLC PCM P&V approaches: (i) staircase up programming (SCUP) [Bedeschi *et al.* 2009], (ii) proportional-integral-derivative programming (PIDP) [Papandreou *et al.* 2011], and (iii) dual-pulse programming [He *et al.* 2014] (an amorphization-only P&V approach referred to as AOP henceforth). The comparisons are performed at both the cell-level as well as full system level.

**Results:** Results at the cell-level indicate that  $L^{3}EP$  can reduce the mean latency (energy) by 2.4– 15× (1.9–12.2×) in comparison to SCUP, PIDP, and AOP. Moreover,  $L^{3}EP$  reduces the worst case latency (energy) by 2.8–9.1× (2.1–11.4×) in comparison to SCUP, PIDP, and AOP. Despite this significant improvement in the programming latency, energy, and endurance of TLC PCM, the hardware overhead of  $L^{3}EP$  is comparable to SCUP, PIDP, and AOP.

Full system simulation results indicate that the average access latency and total energy of  $L^3EP$  are 2.1–8.3× and 1.6–3.7× lower, respectively, in comparison to SCUP, PIDP, and AOP. Further-

more, the IPC and memory bandwidth of  $L^3EP$  are  $1.6-5\times$  and  $1.6-4.6\times$  higher, respectively, in comparison to SCUP, PIDP, and AOP. Detailed findings and comparisons with state-of-the-art P&V solutions are presented in Section 5.2.

#### **1.2 THESIS ORGANIZATION**

The rest of this document is organized as follows. Chapter 2 covers basic concepts of NVMs and related encoding and P&V solutions for MLC/TLC NVMs. Chapter 3 presents the theory and results of the proposed MFNW encoding solution. Chapter 4 introduces our proposed FVE solution for MLC/TLC NVMs. L<sup>3</sup>EP is presented in Chapter 5. Finally, directions for future research are summarized in Chapter 6.

#### 2.0 BACKGROUND

This chapter is divided into three sections. The first two sections cover background material related to the proposed MFNW and FVE schemes. The third section is background material for the proposed TLC program-and-verify (P&V) approach, and it overviews concepts related to MLC/TLC P&V approaches of MLC/TLC PCM.

#### 2.1 BASICS OF NVMS

A PCM cell is made of chalcogenide material which has two states, amorphous and crystalline corresponding with high and low resistances, respectively. To program logic 0 in a PCM cell, current is applied to heat the cell above its melting point followed by a quick cool down. Programming logic 1 is similar, but the target heating temperature is lower, and the rate of cooling is slower; as a result programming logic 1 takes more time [Lee *et al.* 2008, Kang *et al.* 2011].

An RRAM cell is composed of three layers: two metal electrode layers surrounding a transition metal-oxide layer (MOL). The MOL can be switched between high and low resistance states by applying set and reset voltages, respectively. The change in the state of the MOL is a result of forming and deforming the conductive filaments (CF). When Oxygen holes line up from the top to the bottom electrode, a CF is formed, and current can pass through the cell, resulting in a low resistance MOL. Applying a reset voltage disrupts the CF and results in a high resistance MOL [Wong *et al.* 2012].

While these NVM technologies offer extended data retention times, high scalability, and very low static power consumption, they suffer from shorter lifetime, high cell programming energy, and high read/write latencies in comparison to DRAM. For example, STT-RAM requires about  $10 \times$  more energy than DRAM per write access [Chang *et al.* 2013]. These problems are worse in MLC NVMs, where a memory cell stores more than one logical bit.

**Multi-level cell NVM:** While every physical cell in SLC NVMs stores one logical bit of information, a physical cell in MLC NVMs can store more than one logical bit (typically 2 and 3). Each level in a multi-level cell encodes a state, and  $2^m$  states can be encoded using *m* bits per cell. Program-and-verify (P&V) [Bedeschi *et al.* 2009] is commonly used to encode MLC states in PCM and RRAM. To program a cell to a specific state, P&V loops through a program phase followed by verify phase until the target state is reached. The all–0 and all–1 states are the easiest to program in terms of write energy. The further a state from these boundary states, the more P&V loops are required, i.e., the write energy of these non-terminal states is higher. In other words, write energy peaks as we get closer to the middle state. Due to the high variability of the manufacturing of PCM and RRAM arrays, the number of iterations required to program a certain state is unknown, and programming happens slowly and gradually until we are within some acceptable tolerance of the destination state.

#### 2.2 **REVIEW OF ENCODING SOLUTIONS**

**Data comparison write (DCW) [Yang et al. 2007]:** DCW is also referred to as read-modifywrite, and it is the simplest way to avoid unnecessary bit writes in NVMs. Whenever there is a new word to be written to memory, DCW only writes the bits that are different. For  $2^m$ -state MLC memory, assuming each state has  $2^{-m}$  probability of occurrence, a write event has a probability of  $1-2^{-m}$ . It follows from the Binomial distribution theorem that the expected number of cell writes in DCW is  $n \cdot (1-2^{-m})$ , where *n* is the number of cells per word.

**Flip-N-Write:** FNW for SLC memories encodes data with the objective of minimizing the number of bit writes. Each memory word is associated with a tag bit, which is 0 if the word is stored as-is, or 1 if the word is stored in bit-wise complemented form. When a write request arrives at the memory controller, FNW writes the new word as-is if the Hamming distance between the new and old words is not greater than n/2, where n is the number of bits per word (excluding the tag bit).

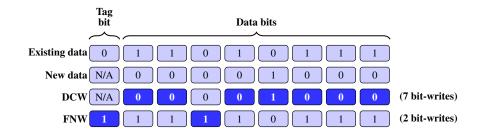

Figure 2.1: For the shown existing and new data, DCW results in 7 bit-writes, whereas FNW, results in only 2 bit-writes. Bit-writes are indicated with darker-color backgrounds.

If the Hamming distance is greater than n/2, FNW writes the new word in bit-wise complemented form. While it can be easily shown that the peak number of bit-writes in FNW cannot exceed [n/2], the expected number of bit-writes, as reported in [Cho and Lee 2009], is

$$\frac{1}{2^{n+1}} \left( \sum_{k=0}^{n/2} k \binom{n+1}{k} + \sum_{k=n/2+1}^{n+1} (n+1-k) \binom{n+1}{k} \right)$$

Fig. 2.1 illustrates the potential advantage of FNW over DCW. While DCW results in 7 bit-writes, FNW uses the complemented version of the new word and results in only 2 bit-writes (71% improvement).

FNW interestingly alleviates all three problems of NVMs simultaneously. First, since it reduces the average number of bit writes per memory word, it reduces the average energy consumption per word. Second, the reduction of the expected number of bit writes per word, as well as bounding the peak number of bit writes per word, definitely improves memory endurance and prolongs lifetime, since the probability of writing to the same memory cell is reduced. Third, improving the write latency is a direct result of the upper bound on the number of bit writes per word, implying that we can write at least two words at a time without violating the energy consumption limits in modern NVM memory module controllers [Yue and Zhu 2012]. For these reasons, we chose to design and implement an MLC version of FNW, believing that it will help alleviate the problems in MLC NVMs as well.

FlipMin [Jacobvitz *et al.* 2013] is a variation of SLC FNW that utilizes coset coding to generate more encoded versions of the new word and reduce the number of bit flips. This enables FlipMin to achieve more energy reduction than FNW at the cost of k overhead bits in comparison to one

bit overhead for FNW. FlipMin is a generalization of FNW, and it behaves identical to FNW when k = 1.

PRES [Seyedzadeh *et al.* 2015] is another coset based write minimization scheme that encodes the new word into a set of random codewords, which outperforms both FNW and FlipMin. The authors demonstrate (by simulation and mathematically) that random codewords result in less number of flips in comparison to FNW and FlipMin. Therefore, they derive a reversible pseudo-random encoding scheme and prove its randomness by random code tests. PRES has the same NVM overhead as FlipMin.

CAFO [Maddah *et al.* 2015] is another variation of SLC FNW that slices the new word into a 2-dimensional  $r \times c$  matrix and performs row- and column-wise bit flipping operations. It aims at minimizing the write cost, e.g., write energy and read reliability in PCM and spin-transfer torque random access memory (STT-RAM), respectively. CAFO achieves more write cost reduction than FNW. This is due to using a heuristic to identify unnecessary flips that is usually overlooked in FNW. Also, incurring more NVM overhead in comparison to FNW helps achieving further cost reduction. The excess overhead of CAFO in comparison to FNW is  $\min(r, c)$  bits.

**Offline frequent value encoding (FVE) [Yang and Gupta 2002]:** Motivated by the fact that most computer applications have high data locality, FVE encodes frequent values such that they are assigned to the least energy codewords. It has been reported that these frequent values may account for 32% of all the values written to memory by a specific application [Yang *et al.* 2004]. Consider an example where an application has only four possible values: A, B, C, and D:

| Value       | А  | В   | С   | D  |

|-------------|----|-----|-----|----|

| Frequency   | 20 | 5   | 10  | 4  |

| Energy (pJ) | 36 | 307 | 547 | 20 |

In this table, the 1<sup>st</sup> row is the possible value, 2<sup>nd</sup> is the corresponding frequency of occurrence of that value, and 3<sup>rd</sup> is the corresponding write energy for each value. Therefore, the total energy consumed by this application is 7,805 pJ. The following value-codeword assignment:

reduces the total energy to 4,483 pJ, i.e., 43%. The assignment ranks the values in decreasing frequencies and codewords in increasing energies, and assigns values with high frequency to code-

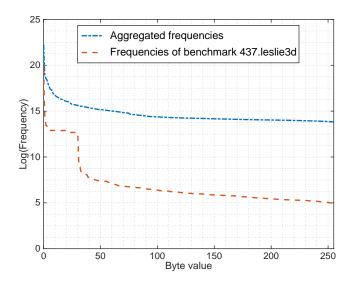

Figure 2.2: In this plot, the x-axis is all the possible values (bytes) and the y-axis is the frequency of the corresponding value in logarithmic scale. Clearly, the frequency profile of benchmark 437.leslie3d exhibits good skew that supports the locality of frequent values. But aggregating the frequency profiles of 32 benchmarks results in a relatively flat plot, suggesting that more than 98% of the values are almost equally likely.

words with low energy in the order of the ranking. For example, A has the highest frequency and D has the lowest energy, we assign value A the codeword D. This optimal offline code assignment will only be good if used for this specific application (or a similar one), and therefore it is referred to as *optimal perfect knowledge* assignment, i.e., find-once for a given program [Yang and Gupta 2002]. Henceforth, we simply refer to this method as the perfect knowledge method.

In practice, if we have more than one application, we aggregate their frequency profiles and generate a combined code assignment resulting in lower energy. However, combining frequencies of incompatible applications may eliminate skew that is essential to achieve high energy reductions, as illustrated in Fig. 2.2. The plots show (1) the aggregate frequency plot of 32 distinct benchmark applications (28 SPEC CPU2006 [SPEC CPU 2006] and four Splash-2 [Arnold *et al.* 1992]) and (2) the frequency plot of the leslie3d benchmark. Even though most offline frequency profiles of individual applications are skewed in favor of FVE, aggregating frequency profiles may eliminate skew and plateaus the graph for almost 98% of possible values. This is in comparison to the individual frequency plot of the benchmark leslie3d, in which the last elbow in the plot appears after 23% of possible values, implying high energy reduction.

Most applications have skewed frequency profiles in favor of perfect knowledge FVE. A primary motivation for this work is the careful aggregation of the frequency profiles of applications to derive multiple encodings, in which each encoding is still a result of a skewed aggregate frequency profile.

The authors in [Sun *et al.* 2011] evaluated perfect knowledge FVE on SLC PCM. While they reported that average write energy is greatly reduced, perfect knowledge FVE requires profiling support during the compilation process, implying a long compilation time for most applications. Another disadvantage of perfect knowledge FVE is that it requires operating system support, since for every application, we need to store the code assignment specific to that application in its executable. Perfect knowledge FVE is therefore expensive in practice.

On the other hand, online profiling occurs during application execution, e.g., [Sun *et al.* 2011]. Frequent values are identified on the fly and may also be replaced by other more frequent values. Although online profiling provides adaptive write energy reduction, it requires significant hardware and may affect overall system performance.

**Encoding solutions for MLC/TLC NVMs:** Besides DCW, FNW, FlipMin, PRES, and CAFO, many data encoding solutions have been proposed for SLC NVMs, e.g. [Li and Mohanram 2014, Dgien *et al.* 2014, Mirhoseini *et al.* 2012, Sun *et al.* 2011, Cho and Lee 2009]. Most of SLC encoding solutions can be readily applied to MLC/TLC NVMs with minor and sometimes no changes. In the following few paragraphs, we summarize the main ideas of some encoding solutions that have been designed specifically for MLC/TLC NVMs.

Zero-value-based morphable PCM (ZM-PCM) [Arjomand *et al.* 2011] is an MLC PCM main memory architecture design that is based on and motivated by the observation that the zero value frequently occurs in PARSEC-2 benchmarks. Driven by this motivation, ZM-PCM encodes these zero-valued MLC cells into SLC resistance levels, implying improved latency, energy, and lifetime. The key element is the use of morphable cells, in which the number of logical bits per physical cell can range from 1 to n (in practice, n cannot exceed six under the utilized P&V algorithm). Therefore, ZM-PCM requires additional memory overhead to track the number of logical bits stored in each physical cell.

In [Wang *et al.* 2011], a cell-level mapping has been proposed to reduce write energy in MLC PCM. The idea is to use a set of six mappings, in which one mapping type is chosen to be applied

to a PCM line at a time, depending on the statistics of the states of the cells in that line. The objective of these mappings is to reduce the number of high power state (HPS) cells and increase the low power state cells (LPS). The mapping type of a PCM line is tracked by using a tag value composed of two cells. A cell state will only contribute to the line statistics if it results in a write operation under DCW. In Section 3.2, we refer to this encoding as the energy efficient encoding (EEE).

Write truncation (WT) [Jiang *et al.* 2012b] dynamically identifies the PCM cells that require more P&V iterations than other cells in the memory line, and truncates their last several iterations to match a preset maximum number of iterations. The objective is to finalize the PCM write early, and therefore improve latency and reduce write energy. WT is integrated with an error correction code (ECC) to recover truncation errors. The same reference proposes "form switch" (FS) to mitigates the additional storage overhead required by ECC. FS utilizes frequent pattern compression (FPC) [Alameldeen and Wood 2004] to reduce storage overhead requirement. Moreover, FS will store a PCM line in SLC format if it can be compressed to half its size or less. This implies shorter access latency and better write endurance.

Elastic RESET (ER) [Jiang *et al.* 2012a] proposes to use only 3 states of the 4-state MLC PCM to reduce MLC reset current, and therefore reduce write energy and improve endurance. ER first compresses the memory line using FPC, and an encoding scheme is chosen based on the the compression ratio. If the compression ratio is 50% or less, data is stored in SLC form [Arjomand *et al.* 2011]. If the ratio is between 50% and 75%, fraction encoding is employed, in which three logical bits are mapped into two physical cells. If the ratio is more than 75%, the cells are stored in regular MLC form. Two SLC bits are associated with every PCM line to distinguish these cases during decoding.

Incomplete data mapping (IDM) [Niu *et al.* 2013] has been proposed to encode TLC RRAM. In IDM, a TLC memory line is converted into another form, in which the cells are 6-state cells. The purpose of this conversion is to eliminate the two high energy and latency states. This encoding is achieved by mapping every chunk of 5 logical bits in the memory line into 6 logical bits (two physical cells), while restricting the use of encoded states to the lowest six states (i.e., the lowest with respect to the state write energy). IDM reduces both write energy and latency, but incurs a memory overhead of 20%. In [Mirhoseini *et al.* 2015], an encoding scheme has been proposed for MLC PCM. This method assigns (n + 1)-cell codeword to *n*-cell word. The word may be any value in the range from 0 to  $4^n - 1$ . The  $4^n$  corresponding codewords are selected from the range from 0 to  $4^{n+1} - 1$  such that the number of intermediate high-energy states (01 and 10) is minimized. An example code-assignment table is given in [Mirhoseini *et al.* 2015] for the case of n = 2. For this code-assignment, the expected write energy reduction is about 40%. However, this is at the cost of 50% memory overhead. As *n* increases, we expect more saving in energy; however, the code-assignment table grows exponentially with *n*. We compare MFNW with this encoding scheme for the case n = 2, assuming the same NVM overhead for MFNW. In our comparison charts, we refer to the case of n = 2 as two-to-three (TTT) encoding.

In [Palangappa and Mohanram 2016], a compression-expansion (CompEx) coding has been proposed. CompEx combines compression and expansion coding to realize energy reduction in MLC/TLC NVMs. The authors evaluated CompEx using both frequent pattern compression (FPC) [Alameldeen and Wood 2004] and base-delta-immediate ( $B\Delta I$ ) compression [Pekhimenko *et al.* 2012]. The compression step is followed by an expansion step to avoid writing high energy states.

#### 2.3 P&V RELATED BACKGROUND

This section covers relevant concepts and provides an overview of state-of-the-art P&V solutions for MLC/TLC PCM.

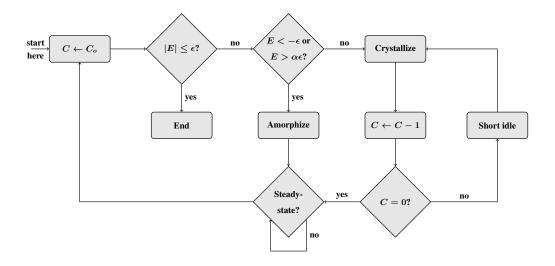

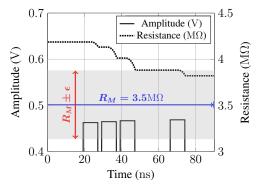

Multi–/Triple–level cell (MLC/TLC): An MLC (TLC) can store two (three) logical bits corresponding to four (eight) distinct MLC (TLC) states. The encoding of MLC/TLC states is achieved by controlling the resistance level of the PCM cell, i.e., each MLC/TLC state has its own unique resistance range that does not overlap with other states. However, instead of maintaining lower and upper bounds of resistance ranges for every MLC/TLC state, it is more efficient to assign a midpoint resistance ( $R_{M_i}$ ) of the resistance range corresponding to the *i*<sup>th</sup> MLC/TLC state, and a write margin,  $\epsilon$ , to define a mapping from a PCM cell resistance, R, to an MLC/TLC state. In other words, a PCM cell is assigned to the *i*<sup>th</sup> MLC/TLC state if  $|R_{M_i} - R| \leq \epsilon$ .

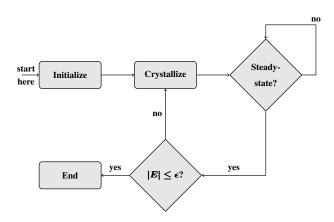

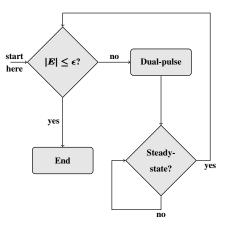

Figure 2.3: In SCUP P&V [Bedeschi *et al.* 2009], SCUP first initializes the cell to the amorphous state. Next, SCUP issues a partial crystallization pulse to slightly lower the resistance, waits for the steady-state resistance, and verifies if the programming error (|E|) is within the write margin ( $\epsilon$ ). If so, SCUP stops, otherwise it repeats the process until the target resistance is reached ( $|E| \le \epsilon$ ).

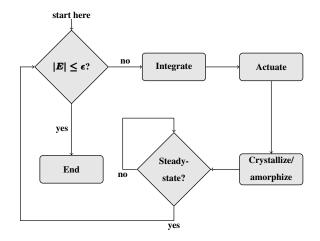

Figure 2.4: In PIDP P&V [Papandreou *et al.* 2011], PIDP examines if  $|E| \leq \epsilon$  and stops if true. Otherwise, it integrates the error signal, converts it into a control command (actuation), and issues either a crystallization or amorphization pulse, depending on the outcome of the actuation. Next, it waits for the steady-state resistance and repeats this process until  $|E| \leq \epsilon$ .

Figure 2.5: In AOP P&V [He *et al.* 2014], AOP examines if  $|E| \le \epsilon$  and stops if true. Otherwise, based on the error, AOP guesses the amplitude of the first dual-pulse using a simple linear model. Next, it waits for the steady-state resistance and repeats this process until  $|E| \le \epsilon$ . Subsequent amplitudes of the dual-pulses are slight increments (or decrements) of the previous amplitude.

**PCM P&V strategies:** The two P&V strategies are crystallization-based and amorphizationbased. In the crystallization-based strategy, the cell is initialized to the highest resistance state using a full RESET pulse. The PCM resistance is then gradually reduced by applying short crystallization pulses with increasing amplitudes, until the target MLC/TLC state is reached. In the amorphization-based strategy, the cell is initialized to the lowest resistance state using a full SET pulse. The PCM resistance is then gradually increased by applying short amorphization pulses with increasing amplitudes, until the target MLC/TLC state is reached. The key difference between the two strategies is the amplitude range of the pulses, i.e., crystallization pulses have smaller amplitudes than amorphization pulses [Burr *et al.* 2010, Braga *et al.* 2010, Bedeschi *et al.* 2009, He *et al.* 2014].

**PCM model:** Our proposed P&V approach ( $L^{3}EP$ ) leverages an accurate state-of-the-art compact model for a PCM cell [Xu *et al.* 2012] to support a comprehensive analysis of the effects of manufacturing variability on write latency and energy in both the crystallization-based and amorphization-based strategies. This device-level model can capture the underlying physical mechanisms of phase change and the dependence on material/structure parameters. The physical nature of this model further helps incorporate variability and reliability issues in the analysis. Note that  $L^{3}EP$  uses this model primarily to simulate the phase change behavior of the PCM cell;

readout operations are modeled by the maximum duration of the PCM cell readout. This tradeoff is essential for an accurate modeling of phase change to simulate the various P&V approaches. In this work, when a P&V approach requires sampling the PCM cell resistance, we assume that the sampling time is  $\leq 10$  ns [Burr *et al.* 2010].

State-of-the-art P&V: There are three state-of-the-art P&V approaches: staircase up programming (SCUP) [Bedeschi *et al.* 2009], proportional-integral-derivative programming (PIDP) [Papandreou *et al.* 2011], and amorphization-only P&V (AOP) [He *et al.* 2014]. Note that we exclude the pulse-tail slope-tuning P&V [Nirschl *et al.* 2007] from our comparisons, since it has a longer latency due to the accumulation of the long tails of its programming pulses. Fig. 2.3 shows the flowchart of SCUP. SCUP starts by applying a full RESET pulse causing the phase change material (Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub>, or GST for short) to transform to the full amorphous state. This is followed by successive P&V iterations that incrementally crystallize the GST until the absolute value of the programming error, |E|, is  $\leq \epsilon$ , the predefined write margin. The amplitude of the programming pulse starts from the voltage causing the lowest crystallization temperature. In each iteration, the amplitude is incremented by a fixed  $\Delta V$ . Although larger values of  $\Delta V$  result in faster programming, they also affect programming reliability, since SCUP uses a crystallization-based P&V strategy with only one programming direction. In practice,  $\Delta V$  can be optimized using Monte Carlo (MC) simulations.

Whereas SCUP updates the pulse amplitude in fixed increments independently of the programming error, PIDP updates the pulse amplitude dynamically in response to a summarized history of the programming error. PIDP achieves this by using an integrator to accumulate error over time. Fig. 2.4 shows the flowchart of PIDP. The programming loop starts with a verification step, which samples the PCM cell resistance (R) and calculates the error  $E = R - R_M$ , where  $R_M$  is the midpoint resistance of the target TLC state. If  $|E| \le \epsilon$ , PIDP stops programming. If  $|E| > \epsilon$ , PIDP proceeds to the "Integrate" step to sum the error and compute a control command, which is then converted to a pulse amplitude in the "Actuate" step. Subsequently, the programming pulse is issued during the "Crystallize/amorphize" step. Note that PIDP idles until the steady-state resistance is reached and then returns to the verification step to begin a new loop.

In contrast to SCUP and PIDP, which utilize crystallization pulses, the authors in [He *et al.* 2014] describe an amorphization-only P&V (AOP) technique to reach any cell resistance level

by the application of a dual-pulse instead of just a single pulse on every iteration. The authors report that the heat accumulation effect between double pulses with a narrow interval is primarily responsible for the high controllability of the cell resistance. In AOP, any cell resistance level can be reached by controlling three parameters of the dual-pulse: pulse amplitude (V), width (W), and interval (T). In this work, AOP is integrated into a P&V loop by controlling V, while keeping W and T constant. Fig. 2.5 shows the flowchart of AOP. Similar to PIDP, the loop starts with a verification step, which samples the PCM cell resistance (R) and calculates the error  $E = R - R_M$ . If  $|E| \le \epsilon$ , the target TLC state is reached. If  $|E| > \epsilon$ , AOP predicts V of the first dual-pulse using a simple linear predictor. A dual-pulse of amplitude V is then issued during the "Dual-pulse" step. Finally, AOP waits for the steady-state resistance and then returns to the verification step for a new iteration. From the second iteration onward, AOP updates V in fixed increments or decrements according to the sign of E.

#### 3.0 MFNW: AN MLC/TLC FLIP-N-WRITE ARCHITECTURE

Flip-N-Write (FNW), originally introduced as "bus-invert coding" in [Stan and Burleson 1995], has been proposed to encode single-level-cell (SLC) memory words in PCM [Cho and Lee 2009]. It has the appeal to simultaneously realize improvements in write energy, endurance, and latency. To write a memory word to a given destination address, FNW tracks the number of bit-writes required to overwrite the old word using the new word (i) as-is and (ii) in bit-wise complemented form. FNW chooses the option that results in minimum bit-writes to reduce the write energy per word. For decoding, FNW tracks the chosen alternative using a tag bit that is associated with each memory word. In addition to reducing energy, in the long run, FNW also improves memory endurance since it also reduces the number of bit-writes. Note that FNW has been applied to SLC PCM, where each memory cell stores a single logical bit. In contrast, in MLC NVMs, a single cell can store more than one logical bit realizing density and cost advantages [Nirschl *et al.* 2007, Kang *et al.* 2008, Xu *et al.* 2013]. The increase in the storage capacity per cell comes at the cost of increased programming energy, read latency, as well as lower endurance in comparison to SLC NVMs. Therefore, there is a strong motivation to develop data encoding and wear-leveling techniques for MLC NVMs [Wang *et al.* 2011, Niu *et al.* 2013, Wen *et al.* 2014].

The contributions in this chapter are as follows. First, we introduce MFNW, a Flip-N-Write algorithm explicitly tailored for MLC NVMs (Section 3.1.1). To the best of our knowledge, this is the first work that generalizes the original FNW algorithm for MLC NVMs. The key idea is the use of cell inversions in place of bit flipping to evaluate encoded forms of the new word for energy reduction. Second, we introduce and investigate two possible variations of the MFNW algorithm: cell Hamming distance (CHD) MFNW and energy Hamming distance (EHD) MFNW. We show that EHD MFNW is more effective in write energy reduction (Section 3.1.3). Third, we develop an approximate probabilistic model to facilitate the theoretical analysis of MFNW.

This includes the derivation of a closed form expression for the expected number of cell writes in CHD MFNW (Eq. 3.2 in Section 3.1.2) . This expression is important because it helps determining the optimal word length that maximizes write energy reduction subject to memory overhead constraints. Simulation results show that the closed form expression incurs a negligible error of 1.4% for the chosen sample of word lengths. Fourth, we introduce and evaluate TFNW, the TLC version of MFNW, for TLC NVMs (Section 3.1.4). Fifth, we propose MFNW2 and MFNW3 that can further reduce energy consumption beyond MFNW (Section 3.1.5). Finally, we introduce a cost-aware endurance evaluation methodology that we use to evaluate MFNW/TNFW effects on NVM endurance in comparison to state-of-the-art MLC/TLC solutions (Section 3.1.6).

Even though MFNW and TFNW are independent of the choice of NVM technology, we evaluate them for the two-bits-per-cell MLC PCM prototype and the three-bits-per-cell TLC RRAM proposed in [Bedeschi *et al.* 2009] and [Xu *et al.* 2013], respectively. We estimate the hardware and delay overheads required to implement MFNW and TFNW for these prototypes. Also, we compare the endurance and average write energy of MFNW with state-of-the-art MLC PCM encoding solutions: data comparison write (DCW) [Yang *et al.* 2007], the energy efficient encoding (EEE) in [Wang *et al.* 2011], and the two-to-three (TTT) encoding in [Mirhoseini *et al.* 2015]. The same comparison is also carried out for TLC RRAM between TFNW and incomplete data mapping (IDM) encoding [Niu *et al.* 2013].

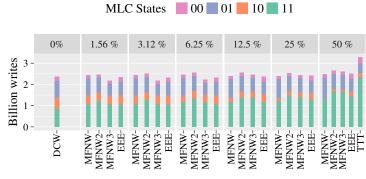

MLC PCM results indicate that MFNW achieves up to 39% energy saving over DCW; with MFNW3, the energy saving can be as much as 47% over DCW. Using the proposed endurance evaluation, MFNW, without using any wear-leveling or error-correction techniques, can prolong memory lifetime by up to 100% in comparison to DCW. For TLC RRAM results, TFNW achieves up to 53% energy saving over DCW and, without using any wear-leveling or error-correction techniques, it is capable of extending the lifetime of RRAM NVM by up to 87% in comparison to DCW. Detailed findings and comparisons with state-of-the-art encoding solutions are presented in section 3.2.

In summary, MFNW3 results in lower write energy, longer endurance than state-of-the-art MLC NVM encodings. On the other hand, whereas TFNW provides a 25% reduction in the number of cell writes over IDM, it only results in comparable energy and endurance to IDM. Intuitively, cell write reduction should improve both energy and endurance; however, in contrast to TFNW,

IDM completely avoids cell writes to the high energy TLC states (States 3 and 4), resulting in the two approaches having comparable energy and endurance.

This chapter is organized as follows. Section 3.1 and 3.2 present the contributions and evaluation results, respectively. Section 3.3 summarizes our findings and concludes the chapter. Finally, Section 3.4 is a supplementary section that lists and proves some observations about MFNW and TFNW.

#### 3.1 CONTRIBUTIONS

This section starts with a high level overview of MFNW, followed by a discussion of the two MFNW modes: CHD and EHD. This is followed by a theoretical analysis to derive a closed-form expression for the expected number of cell writes of CHD MFNW. This expression is then used to derive an upper bound for the expected energy consumption of EHD MFNW. Additionally, we introduce the TLC version of FNW (TFNW) and the other variations of MFNW, which allow further energy reductions (MFNW2 and MFNW3). The section concludes by describing our proposed endurance model that we assume during memory lifetime simulation.

#### 3.1.1 MLC FNW (MFNW)

We begin with the definitions that are necessary to present MFNW. We define the *replication* operator  $\{n\{a\}\}$  as in Verilog: replicate the binary string a, n times. For example,  $\{4\{01\}\}$  is the binary string 01010101. We also borrow the *concatenation* operator from Verilog, i.e.,  $\{01, 1100\} = 011100$ . Further, we define the  $i^{\text{th}}$  cell inversion of a multi level cell c as  $i \oplus c$ , where  $\oplus$  is the bit-wise XOR operator, assuming that i and c have the same number of bits. For example, if c = 01, then the  $0^{\text{th}}$  inversion of c is  $00 \oplus 01 = 01$ ; the  $1^{\text{st}}$  inversion is  $01 \oplus 01 = 00$ , and so on. Note that the number of possible cell inversions of c is  $2^m$ , where m is the width of c in bits.

**Inversion operator:** Assume that the MLC is *m*-bit wide, *i* is a single cell, and *a* is *n*-cell wide. We define the *i*<sup>th</sup> inversion of *a* as  $\{i, \{n\{i\}\} \oplus a\}$ . Note the use of both replication and concatenation operators in this definition. Also, note that the *i*<sup>th</sup> inversion of *a* can be defined equivalently as

*i* concatenated with the *i*<sup>th</sup> cell inversions of every cell in *a*, starting with the most significant cell. Clearly, the number of possible inversions for *a* is  $2^m$ . To illustrate the inversion operator, assume MLC NVM, where every cell is 2-bit wide. If a = 001110, then the  $0^{th}$  inversion of  $a = \{00, 000000 \oplus 001110\} = 00001110; 1^{st}$  inversion of *a* is 01011011, and so on. Note if *i* is one bit, the  $0^{th}$  inversion of *a* is *a* and the  $1^{st}$  inversion of *a* is  $\overline{a}$ , i.e., the 1's complement of *a*.

**MFNW write:** With this definition of inversion operator, we can generalize the bit-flipping in SLC FNW to cell-inversion in MFNW as follows. Suppose the memory controller receives a write request, with a new word  $W_2$  to replace an old word  $W_1$ . Without loss of generality, let us assume that the old word is already fetched from the NVM array into the controller. This means that the old word is 1 cell wider than the new word, because it contains the tag cell. MFNW generates all possible cell inversions of  $W_2$ , and computes the distance between these inversions and the old word  $W_1$ . The *closest* inversion is chosen to overwrite  $W_1$ . Algorithm 1 outlines these steps in an algorithmic manner.

| Α | lgori | thm | 1: | MFNW |

|---|-------|-----|----|------|

|---|-------|-----|----|------|

input :  $W_1$ : existing data,  $W_2$ : tag-less data to write, n: number of bits/cell, n: number of cells/word effect : An inversion of  $W_2$  written at address A, which is the address of  $W_1$

1. Compute the  $i^{\text{th}}$  inversion of  $W_2, W_{2,i} = \{i, \{n\{i\}\} \oplus W_2\}$ , for  $0 \le i < 2^n$ .

2. Find k such that the Hamming distance between  $W_1$  and  $W_{2,k}$  is minimum.

3. Write the closest inversion  $(W_{2,k})$  at address A

The algorithm needs to know the number of bits per cell and the number of cells per word excluding the tag cell. These two parameters are constants while the dynamic parts of input parameters are the old word (including the tag cell) and the new tagless word. The interpretation of the *closest* inversion to the old word can mean the closest with respect to CHD or EHD. We define and illustrate both distance metrics in sub-sections 3.1.2 and 3.1.3.

**MFNW read:** When the CPU needs to read a memory location, the MFNW memory controller must decode the memory word at that address to recover the original tagless word. This is done by bit-wise-XORing the word with its tag cell replicated n times, assuming the memory word length (without the tag cell) is n cells. For example, assuming an MLC NVM, if the {tag, word} is {01, 110011}, then the decoded tagless word is {010101  $\oplus$  110011} = 100110. This implies that the latency of the MFNW read data path is minimally affected by this simple XOR operation.

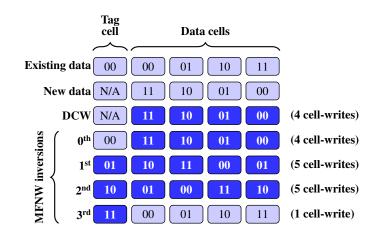

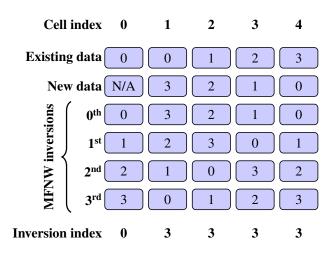

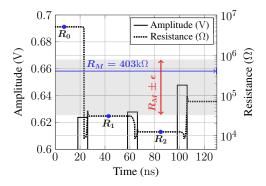

Figure 3.1: For the shown existing and new data, DCW results in 4 cell writes. CHD MFNW chooses to write the 3<sup>rd</sup> inversion of the new data, since it results in the minimum number of cell writes (1) among all other inversions. Note that cell-writes are indicated with darker-color backgrounds.

#### 3.1.2 Cell Hamming Distance (CHD) MFNW

We define the cell Hamming distance (CHD) between two words  $W_1$  and  $W_2$  as the number of cells in which the two words differ from each other. For example, in MLC memory, if  $W_1 = 2130_4$  and  $W_2 = 2121_4$ , the CHD is 2. Note that  $CHD(W_1, W_2) = CHD(W_2, W_1)$ , i.e., the CHD is symmetric.

Before analyzing CHD MFNW, we provide a simple example which illustrates the potential of CHD MFNW in comparison to DCW. Fig. 3.1 shows an existing word that is to be replaced by a new word. Note that each cell is bounded in a square for readability purposes. Also note that DCW does not require a tag cell and it is therefore ignored, resulting in 4 cell writes (0% saving). CHD MFNW examines all possible inversions and picks the 3<sup>rd</sup>, since it results in the minimum number of cell writes (1). Note that this 1 cell write implies 4 'no-write' operations. We emphasize this because in our analysis, we count the average number of 'no-writes' and deduct it from the total number of cells per word (including the tag cell) to obtain the average number of cell writes. Therefore, in the following discussion, we use *the number of no-cell-writes*, or alternatively, *the number of no-writes* to refer to the number of cases where MFNW does not overwrite a cell during a write.

**Probabilistic model for CHD MFNW**: In the following, we develop a probabilistic model for CHD MFNW. The objective is to derive the expected number of cell writes. Without loss of

generality, this derivation assumes MLC NVM. Given a {tag,word}, note that the least significant bit (LSB) of the tag cell controls the inversion of all the LSBs in the remaining cells in the word. Similarly, the most significant bit (MSB) of the tag cell controls the inversion of all the MSBs in the remaining cells in the word. Therefore, we can partition {tag,word} into two strings of bits: The first (second) string is composed of the LSB (MSB) bits of the tag and other cells in the word. For example, {00,000111} can be partitioned into two bit strings {0,001} and {0,011}. We refer to the first (second) bit string as the first (second) partition of a {tag,word}. Note that each one of these two partitions can be interpreted as a separate and independent instance of SLC FNW. Therefore, we wish to find the number of cell writes such that each of the two partitions has no more than  $\lceil n/2 \rceil$  bit writes, which is consistent with the peak bit-write result for SLC FNW. Each trial of this 'compound' experiment has two possible outcomes: either 'cell-write' or 'no-cell-write', and a 'cell-write' occurs whenever a bit-write occurs in at least one partition.

Let Y be the random variable indicating the number of 'no-cell-write' outcomes. Let  $X_1$  and  $X_2$  be the random variables indicating the number of 'no-bit-write' events in the first and the second partitions of the word, respectively. Let  $m = \lceil n/2 \rceil$ . Then, the expected number of 'no-cell-write' events, denoted by  $\overline{S}$ , is

$$\overline{S} = \mathbf{E}\left[Y \mid (X_1 > m) \cap (X_2 > m) \cap (Y \ge l)\right]$$

Using probability theory, this expands to

$$\overline{S} = \sum_{k=0}^{n+1} k \frac{\mathsf{P}((Y=k) \cap (X_1 > m) \cap (X_2 > m) \cap (Y \ge l))}{\mathsf{P}((X_1 > m) \cap (X_2 > m) \cap (Y \ge l))}$$

(3.1)

Note that Y is constrained with a lower bound l. Setting l = 0 deactivates this lower bound. Observation 3.4.1 in section 3.4 proves that this lower bound equals  $1 + \lfloor n/4 \rfloor$  for the MLC case.

To determine the probabilities in Eq. 3.1, consider the number of ways in which the event  $((Y = k) \cap (X_1 = c_1) \cap (X_2 = c_2) \cap (Y \ge l))$  occurs, for some constants  $k, c_1, c_2$ , and l. Imagine the two partitions of the word are of length n+1 (including the tag bits). We perform SLC FNW on both partition, and observe the parallel outcomes of this exercise, i.e., four possibilities { NN, NW, WN, WW }, where N denotes a no-bit-write event and W denotes a bit-write event. A cell write event occurs at position i if at least one of the partitions results in W event at the same position. A no-cell-write occurs at cell position i when both partitions result in event N at bit position i.

Clearly, the sample space can be partitioned into two events: no-cell-write (NN) and cell write (not NN) events. Therefore, the number of ways in which Y = k is simply  $\binom{n+1}{k}$ , as long as  $k \ge l$ , and 0 otherwise. Assuming that  $c_1, c_2 > k$ , the number of ways in which  $X_1 = c_1$  is  $\binom{n+1-k}{c_1-k}$ , and this corresponds to the cases where we have NW outcomes only, since NN events were already counted in  $\binom{n+1}{k}$ .

The number of ways in which  $X_2 = c_2$  corresponds to the number of WN outcomes only, since the NN were already counted in  $\binom{n+1}{k}$ , i.e.,  $\binom{n+1-k-(c_1-k)}{c_2-k}$  or  $\binom{n+1-c_1}{c_2-k}$ . Therefore, the number of ways in which  $((Y = k) \cap (X_1 = c_1) \cap (X_2 = c_2) \cap (Y \ge l))$  event occurs is

$$\left\{ \begin{array}{cc} 0 & k < l \\ {\binom{n+1}{k}\binom{n+1-k}{c_1-k}\binom{n+1-c_1}{c_2-k}} & \text{otherwise} \end{array} \right.$$

Dividing the above by  $4^{n+1}$ , which is the size of the sample space, gives us the probability of such event. Therefore, the probability of the event  $((Y = k) \cap (X_1 > m) \cap (X_2 > m) \cap (Y \ge l))$ , which shows up in the numerator of Eq. 3.1, is expanded as the summation of the probabilities as follows:

$$\begin{cases} 0 & k < l \\ \frac{1}{4^{n+1}} \sum_{\forall (c_1, c_2) > m} \binom{n+1}{k} \binom{n+1-k}{c_1-k} \binom{n+1-c_1}{c_2-k} & \text{otherwise} \end{cases}$$

and the denominator of Eq. 3.1 is

$$\frac{1}{4^{n+1}} \sum_{c_3 \ge l, (c_1, c_2) > m} \binom{n+1}{c_3} \binom{n+1-c_3}{c_1-c_3} \binom{n+1-c_1}{c_2-c_3}$$

Substituting these quantities into Eq. 3.1, we obtain the expected number of 'no-cell-write' events:

$$\overline{S} = \sum_{k=l}^{n+1} \frac{k \sum_{\forall (c_1, c_2) > m} \binom{n+1}{k} \binom{n+1-k}{c_1-k} \binom{n+1-c_1}{c_2-k}}{\sum_{c_3 \ge l, (c_1, c_2) > m} \binom{n+1}{c_3} \binom{n+1-c_3}{c_1-c_3} \binom{n+1-c_1}{c_2-c_3}}$$

Note that the denominator is completely independent of k, and therefore may be placed outside the summation over k. Also, the expected number of 'cell-writes',  $\overline{W}$ , is

$$\overline{W} = n + 1 - \overline{S} \tag{3.2}$$

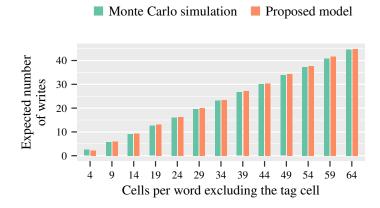

To evaluate the accuracy of this approximation, we computed the average number of cell writes numerically using Monte Carlo simulation for some values of n and compared the result with

Figure 3.2: The expected number of cell writes using Monte Carlo simulation in comparison to the proposed model (Eq. 3.2).

Eq. 3.2 in Fig. 3.2. The geometric mean error is less than 1.5% and the error itself can be as low as 0.4%.

Finally, the expected write energy of CHD MFNW is  $\overline{W} \times \overline{e}$ , where  $\overline{e}$  is the average energy over all cell states. This is true by symmetry, since the number of cell writes does not influence which cell states are written, but assumes all cell states have equal probability of occurrence. The average energy saving as a result of using CHD MFNW normalized to DCW is  $1 - \frac{4\overline{W}}{3n}$ .

#### 3.1.3 Energy Hamming Distance (EHD) MFNW

We define the energy Hamming distance (EHD) between two words  $W_1$  and  $W_2$  as the energy required to write the cells of  $W_2$  that are different from  $W_1$ . For example, for MLC NVMs, if  $W_1 = 2130_4$  and  $W_2 = 2121_4$ , the EHD is the energy required to write state 2 plus the energy required to write state 1. Note that  $EHD(W_1, W_2) \neq EHD(W_2, W_1)$  except when  $W_1 = W_2$ , unlike CHD MFNW. Clearly, write energies are technology-dependent, and therefore, without loss of generality, we base our discussion on the write energies of the MLC PCM prototype design proposed in [Bedeschi *et al.* 2009]. For this prototype, the energy in our example is 547+307=854 pJ. Table 3.1 lists cell states against their average energies as reported in the same reference.

Note that it is not necessarily true that reducing the number of cell writes leads to a reduction in write energy. Fig. 3.3 shows a real memory write scenario extracted from memory traces of

| MLC state | Energy (pJ) |  |  |

|-----------|-------------|--|--|

| 00        | 36          |  |  |

| 01        | 307         |  |  |

| 10        | 547         |  |  |

| 11        | 20          |  |  |

Table 3.1: Average write energies for the four MLC states of the PCM prototype [Bedeschi et al. 2009]

the 'perlbench' SPEC CPU2006 benchmark [SPEC CPU 2006]. In this example, we observe that the minimum number of cell writes, i.e., 5 writes, occurs at the 2<sup>nd</sup> inversion. This is the preferred choice of CHD MFNW. On the other hand, we see that this choice leads to the highest write energy among all other inversions. The least write energy occurs if we choose 3<sup>rd</sup> inversion, which results in 9 cell writes. This example clearly illustrates and motivates the necessity of EHD MFNW, which essentially chooses the inversion that results in the minimum cell write energy, regardless of the number of cell writes.

For this reason, we implement EHD MFNW, since our objective is to lower the write energy. Although this may increase the expected number of cell writes per word, it reduces the probability of programming a high energy state into a specific cell. In other words, it makes low energy states more likely to occur than high energy states. This implies that the programming effort is lowered in general, and therefore the expected lifetime of memory cells is also increased.

Unlike CHD MFNW, the analysis of the EHD MFNW is more involved. In addition to knowing if a cell write occurred, we also need to know which state has been written. In other words, we need to know the expected number of times each state was written. However, we can simplify this analysis by deriving an upper bound on the expected write energy per word. This upper bound is given by  $\overline{W} \times \overline{e}$ , where  $\overline{W}$  is defined in Eq. 3.2 and  $\overline{e}$  is the average energy over all cell states. Our results that the empirical averages of EHD MFNW write energy can be 16% lower than this bound.

Figure 3.3: For the new and existing data above, CHD MFNW picks the 2<sup>nd</sup> inversion, resulting in minimum cell Hamming distance (but the highest energy too). EHD MFNW picks the 3<sup>rd</sup> inversion, since it results in minimum energy, regardless of cell distance.

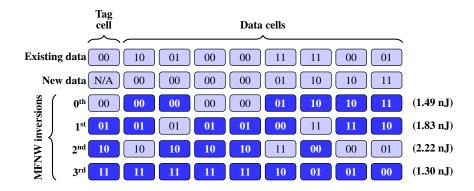

# 3.1.4 TFNW: TLC Flip-N-Write

MFNW can be extended to TLC NVMs, referred to as TFNW in this work. Since a TLC can have eight states, eight inversions are generated during a memory write, and the one consuming the least energy will be selected to replace the old NVM content. We adopt an EHD-based TFNW, since the write energy consumption of the CHD version is also bounded by the EHD TFNW, as in the MLC case. Henceforth, we refer to EHD TFNW as TFNW. Evaluation of TFNW is based on the 8-state TLC RRAM prototype in [Xu *et al.* 2013]. The state-energy pairs of this prototype are shown in Table 3.2.

| TLC state | Energy (pJ) |

|-----------|-------------|

| 000       | 2           |

| 001       | 6.7         |

| 010       | 19.3        |

| 011       | 35.1        |

| 100       | 35.6        |

| 101       | 19.6        |

| 110       | 8.5         |

| 111       | 1.5         |

Table 3.2: Average write energies for the eight TLC states of the RRAM prototype [Xu et al. 2013]

To illustrate TFNW, consider an example with n = 2, i.e., the number of cells per word, excluding the tag cell, is 2. Also, assume the old content is  $023_8$ . Note that we use base 8 (octal) to represent the words and inversions in this example. Also, in the old content, the leftmost digit is the tag (0). Consider the case where the old content as to be replaced with the new content  $13_8$ . The first step is to calculate all the inversions of the new content:

- The  $0^{\text{th}}$  inversion is  $013_8$ ,

- $1^{\text{st}}$  inversion is  $102_8$ ,

- $2^{nd}$  inversion is  $231_8$ ,

- $3^{rd}$  inversion is  $320_8$ ,

- $4^{\text{th}}$  inversion is  $457_8$ ,

- $5^{\text{th}}$  inversion is  $546_8$ ,

- $6^{\text{th}}$  inversion is  $675_8$ , and

- $7^{\text{th}}$  inversion is  $764_8$ .

The energies of the inversions as ordered above are: 6.7, 28, 61.1, 37.1, 56.7, 63.7, 29.6, and 45.6 pJ, respectively. Clearly, the 0<sup>th</sup> inversion is selected for replacing the old content, since it results in the lowest write energy.

## 3.1.5 Further Energy Reductions

One way to achieve more energy reduction is to reduce n, i.e., the number of cells per word, excluding the tag cell. In this manner, the maximum energy reduction is achieved when n = 2, where MFNW completely avoids writing the highest energy MLC state 10 and TFNW avoids writing the highest energy TLC states 011 and 100 ( for a proof of this statement, refer to observations 3.4.2 and 3.4.3 in Section 3.4). This implies an average of 47% and 40% write energy reductions in the MLC and TLC cases, respectively, due to high energy state avoidance. However, this is at the cost of 50% NVM overhead.

We can achieve higher energy reductions without this high NVM overhead. Recall that MFNW generates four inversions and selects the inversion with the minimal write energy for writing into NVM. We can achieve further write energy reductions by increasing the number of generated inversions, provided that extra NVM and controller overheads are tolerable. One can easily see

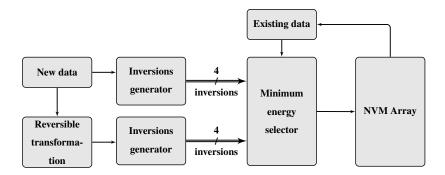

Figure 3.4: Reusing the components of MFNW to construct MFNW2.

that the maximum number of cell-level mappings is 24 in the MLC case. One approach to generate a subset of the 24 possible mappings is to utilize a lookup-table. Alternately, it is possible to reuse the components of MFNW architecture to construct more inversions as follows. Before the inversions are generated, reversible transformation(s) of the new word can be used to generate the four inversions of the original word and another four inversions of the transformed version(s) of the new word. This results in a total of 4(1 + T) inversions (mappings), where T is the number of reversible inversions. This widens the search and increases the chances of finding a lower energy inversion. But it also implies the usage of two tag cells, one to track the selected inversions (MFNW tag cell), and another to track the selected transformation. A practical value of T is  $\leq 3$ , and T = 3results in 16 mappings. In this work, we evaluated T = 1 and T = 3, since they both result in mappings that are a power of 2. We refer to MFNW with T = 1 as MFNW2, and with T = 3 as MFNW3. Fig. 3.4 shows how MFNW2 can be constructed by reusing the components of MFNW: two inversions generators and a minimum energy selector. The internals of the inversions generator and minimum energy selector blocks are described in Section 3.2 along with the discussion of the hardware and delay overhead of MFNW.

Although many reversible mappings are possible, the primary factor in determining the expected energy reduction is the number of evaluated inversions. The choice of a certain mapping over another has only little influence on the resultant energy reduction. To demonstrate this case, we show the result of a Monte Carlo (MC) simulation for T = 1 and T = 3 and observe the change in energy reduction as a result of changing the mapping. Although many reversible map-

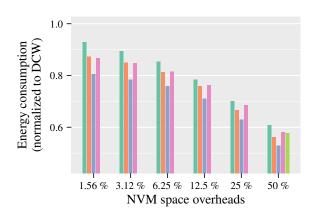

Figure 3.5: The effect of choosing a transform over the other on energy consumption. Here, R,  $S_1$ , and  $S_2$  denote bitwise rotation, swapping MLC states 10 and 11, and swapping MLC states 01 and 11, respectively. All the bars are normalized to MFNW energy consumption.