## **Durham E-Theses**

# Effect of wearout processes on the critical timing parameters and reliability of CMOS bistable circuits

Das, A.G. Man Mohan

#### How to cite:

### Use policy

The full-text may be used and/or reproduced, and given to third parties in any format or medium, without prior permission or charge, for personal research or study, educational, or not-for-profit purposes provided that:

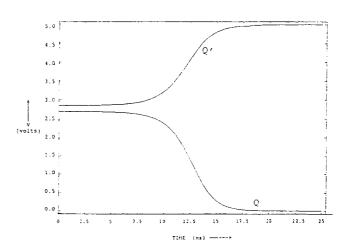

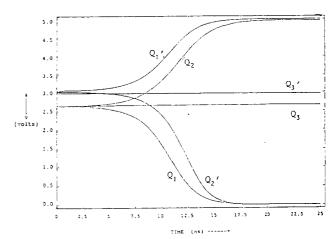

- a full bibliographic reference is made to the original source

- a link is made to the metadata record in Durham E-Theses

- the full-text is not changed in any way

The full-text must not be sold in any format or medium without the formal permission of the copyright holders.

Please consult the full Durham E-Theses policy for further details.

### **Abstract**

The objective of the research presented in this thesis was to investigate the effects of wearout processes on the performance and reliability of CMOS bistable circuits. The main wearout process affecting reliability of submicron MOS devices was identified as hot-carrier stress (and the resulting degradation in circuit performance). The effect of hot-carrier degradation on the resolving time leading to metastability of the bistable circuits also have been investigated.

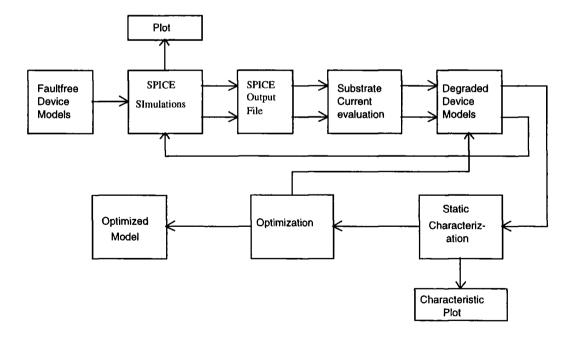

Hot-carrier degradation was identified as a major reliability concern for CMOS bistable circuits designed using submicron technologies. The major hot-carrier effects are the impact ionisation of hot-carriers in the channel of a MOS device and the resulting substrate current and gate current generation. The substrate current has been used as the monitor for the hot-carrier stress and have developed a substrate current model based on existing models that have been extended to incorporate additional effects for submicron devices. The optimisation of the substrate current model led to the development of degradation and life-time models. These are presented in the thesis.

A number of bistable circuits designed using 0.7 micron CMOS technology design rules were selected for the substrate current model analysis. The circuits were simulated using a set of optimised SPICE model parameters and the stress factors on each device was evaluated using the substrate current model implemented as a post processor to the SPICE simulation.

Model parameters for each device in the bistable were degraded according to the stress experienced and simulated again to determine the degradation in characteristic timing parameters for a predetermined stress period. A comparative study of the effect of degradation on characteristic timing parameters for a number of latch circuits was carried out. The life-times of the bistables were determined using the life-time model. The bistable circuits were found to enter a metastable state under critical timing conditions. The effect of hot-carrier stress induced degradation on the metastable state operation of the bistables were analysed.

Based on the analysis of the hot-carrier degradation effects on the latch circuits, techniques are suggested to reduce hot-carrier stress and to improve circuit life-time. Modifications for improving hot-carrier reliability were incorporated into all the bistable circuits which were re-simulated to determine the improvement in life-time and reliability of the circuits under hot-carrier stress. The improved circuits were degraded based on the new stress factors and the degradation effects on the critical timing parameters evaluated and these were compared with those before the modifications. The improvements in the life-time and the reliability of the selected bistable circuits were quantified. It has been demonstrated that the hot-carrier reliability for all the selected bistable circuits can be improved by design techniques to reduce the stress on identified critically stressed devices.

# University of Durham

The copyright of this thesis belongs to the author.

Readers must sign their name below to show that they undertake

- 1) to acknowledge any use made of it, or any quotation from it, in any work of their own.

- 2) not to publish (or in the case of a Music thesis perform) any part of the work without obtaining the consent of the author (or his representatives after his death) during the period of copyright.

- 3) not, under any circumstances, to leave it unattended, and to return it to a member of the library staff before leaving the library.

| signature and permanent address | date ·      |

|---------------------------------|-------------|

|                                 |             |

|                                 |             |

|                                 | ·           |

| ·                               |             |

|                                 |             |

|                                 |             |

|                                 |             |

|                                 |             |

|                                 |             |

|                                 |             |

|                                 | <del></del> |

| /                               |             |

|                                 |             |

|                                 |             |

|                                 |             |

|                                 |             |

|                                 |             |

|                                 |             |

| •                               | <del></del> |

|                                 |             |

|                                 |             |

|                                 |             |

|                                 |             |

# Effect of Wearout Processes on the Critical Timing Parameters and Reliability of CMOS Bistable Circuits

### A.G. Man Mohan Das

The copyright of this thesis rests with the author. No quotation from it should be published without the written consent of the author and information derived from it should be acknowledged.

This thesis is submitted to the University of Durham in candidature for the degree of Doctor of Philosophy

School of Engineering and Computer Science

University of Durham

1997

### Declaration

The material contained within this thesis is the sole work of the author and has not been submitted previously for a degree in this or any other University.

## Statement of Copyright

The copyright of this thesis rests with the author. No quotation from it should be published without his prior written consent and information derived from it should be acknowledged.

### Acknowledgements

I would like to thank my supervisor, Dr. Simon Johnson, for his constructive criticism and careful reading of this thesis. I would also like to thank Dr. Martin Morant for his inspiring guidance during the first few years of my research work.

I am thankful to my wife, Renuka, for her encouragement and support for my research work. I also appreciate the concern and understanding of my son Gopimohan and daughter Sunayana during my many trips to Durham for the research work.

## Contents

| Cha  | apter 1                                                   |      |

|------|-----------------------------------------------------------|------|

| Intı | roduction                                                 | 1    |

|      | Objectives of the research                                |      |

|      | The need for the research                                 |      |

|      | Outline of this thesis                                    |      |

| Cha  | apter 2                                                   |      |

| We   | earout Processes in CMOS and Reliability of VLSI Circuits | .5   |

| 2.1  | Terminology                                               | .6   |

| 2.2  | A Review of Wearout Processes                             | 10   |

| 2.3  | Distinction Between Catastrophic & Parametric Faults      | 12   |

|      | Parametric Faults Identified for Investigation            |      |

|      | Chapter Summary                                           |      |

| Ch   | apter 3                                                   |      |

| Mo   | odelling Hot carrier degradation effects                  | . 16 |

|      | Hot-Carriers: A Review                                    |      |

|      | 3.1.1 Generation of hot carriers and substrate current    | 17   |

| 3.2  | Hot carrier degradation mechanisms                        | 18   |

|      | 3.2.1 Multiplication and oxide charging                   |      |

|      | 3.2.2 Carrier temperature and mobility degradation        |      |

|      | 3.2.3 Gate current generation                             |      |

| 3.3  | Substrate current modelling                               | . 24 |

|      | 3.3.1 Existing substrate current models                   | 26   |

|      | 3.3.1.1 Sakurai model                                     | . 26 |

|      | 3.3.1.2 Hu model                                          | 27   |

|      | 3.3.1.3 HSPICE model                                      | 28   |

|      | 3.3.1.4 BSIM model                                        |      |

|      | 3.3.1.5 Philips model                                     |      |

|      | 3.3.2 Optimised substrate current model                   |      |

|      | 3.3.2.1 Optimisation procedure                            |      |

|      | 3.3.2.2 Optimised final model                             |      |

| 34   | Degradation modelling                                     | .35  |

| 3.4.1 Parametric degradation                                        | 36              |

|---------------------------------------------------------------------|-----------------|

| 3.4.2 Existing degradation models                                   | 38              |

| 3.4.2.1 BERT model                                                  | 38              |

| 3.4.2.2 Leblebici model                                             | 40              |

| 3.4.2.3 HOTRON model                                                | 41              |

| 3.4.2.4 RELY model                                                  | 42              |

| 3.4.2.5 PRESS degradation model                                     | 43              |

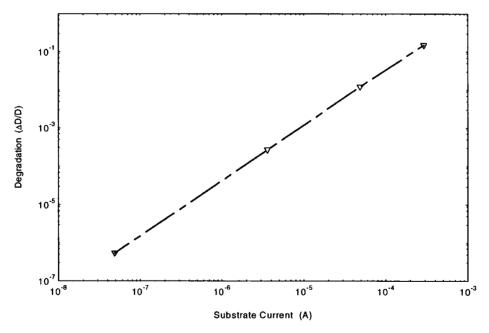

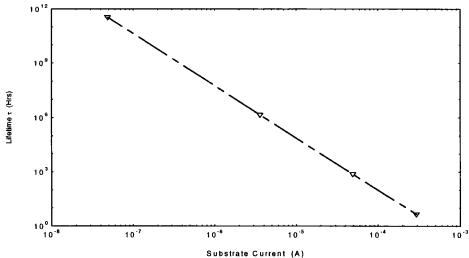

| 3.4.3 Optimised degradation model                                   |                 |

| 3.5 Characterisation of degradation effects                         |                 |

| 3.5.1 Characterisation simulation results                           |                 |

| 3.6 Chapter summary                                                 | 50              |

| •                                                                   |                 |

| Chapter 4                                                           |                 |

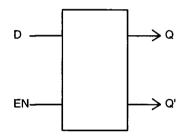

| The Analysis of CMOS Bistable Circuits                              | 52              |

| 4.1 Bistable circuits: Terminology                                  | 53              |

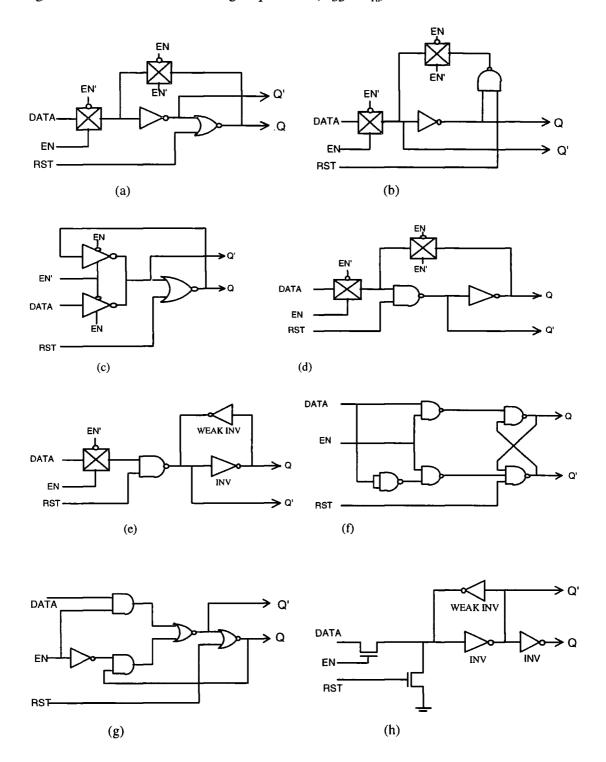

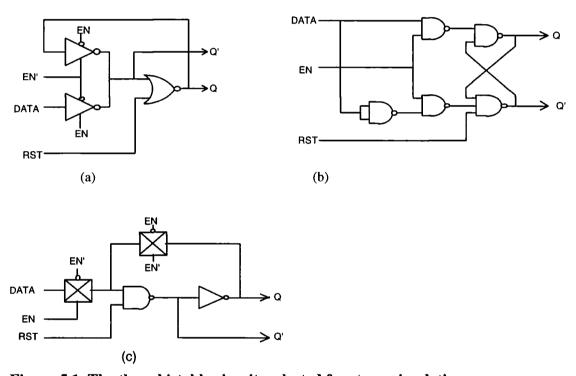

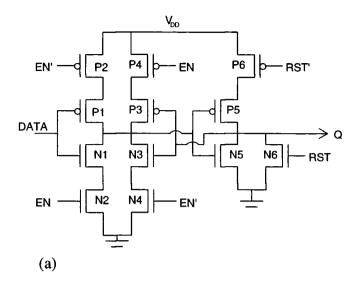

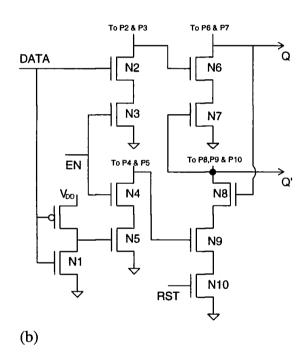

| 4.2 Design of transparent latches                                   |                 |

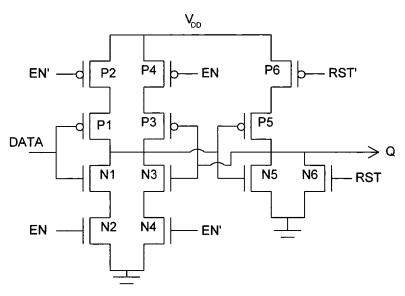

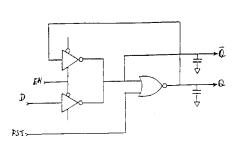

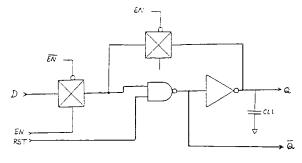

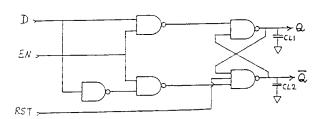

| 4.2.1 Design of D-type latch with reset                             |                 |

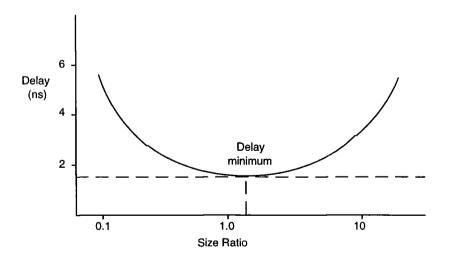

| 4.2.2 Optimised CMOS D-latch Design                                 |                 |

| 4.3 Standardisation of inputs and outputs for simulation            |                 |

| 4.3.1 Parameters                                                    |                 |

| 4.3.2 Standard conditions for input and output                      | 62              |

| 4.3.3 Types of circuits                                             | 62              |

| 4.4 Standardisation of SPICE parameters for MOS devices             |                 |

| 4.4.1 MOS Level 1 model                                             |                 |

| 4.4.2 MOS level 2 model                                             | 65              |

| 4.4.3 MOS level 3 model                                             |                 |

| 4.4.4 Optimisation of model parameters                              | 68              |

| 4.5 Simulation of latch circuits                                    |                 |

| 4.5.1 Simulation environment                                        | 70              |

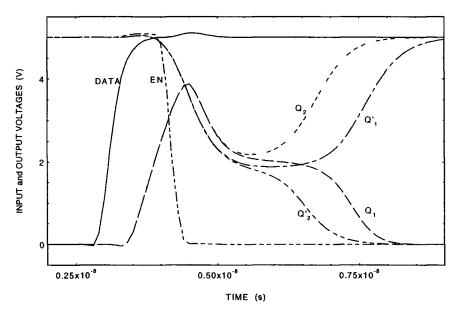

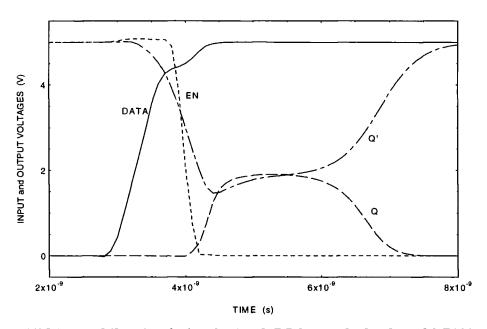

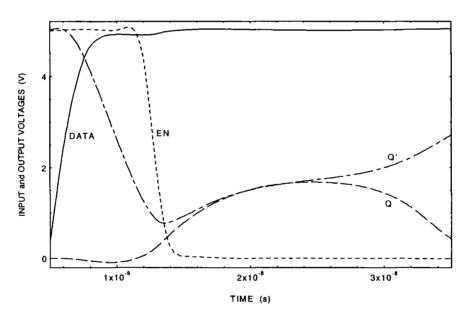

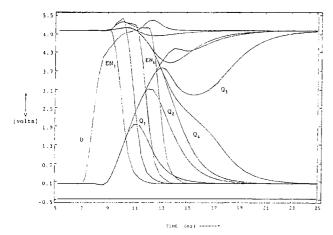

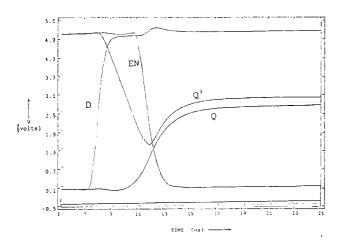

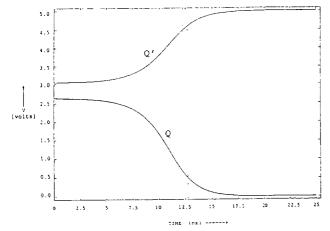

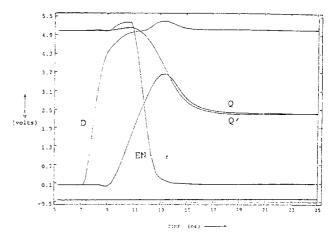

| 4.5.2 Fault-free simulations of D-latches                           | 71              |

| 4.6 Simulation results and selection of 3 latch circuits            |                 |

| 4.6.1 Analysis of simulation results                                |                 |

| 4.6.2 Fault-free simulations of 1 Micron Latch circuits             |                 |

| 4.6.3 Simulation results for 0.7 micron design                      | 77              |

| 4.7 Chapter summary                                                 |                 |

| Chapter 5                                                           |                 |

| <b></b>                                                             |                 |

| Hot-carrier Degradation simulations of CMOS bistable circu          | aits <b>7</b> 9 |

| 5.1 Modelling Degradation Effects in Bistables                      |                 |

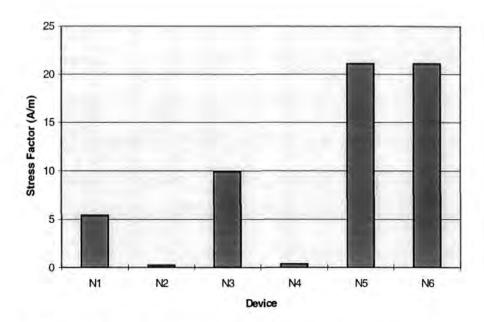

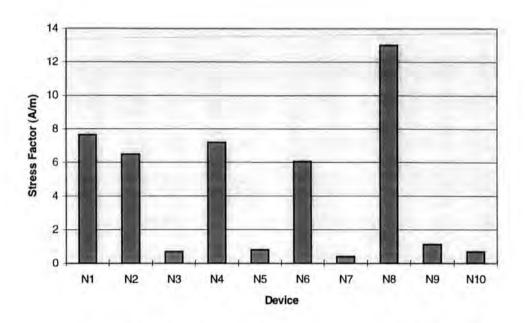

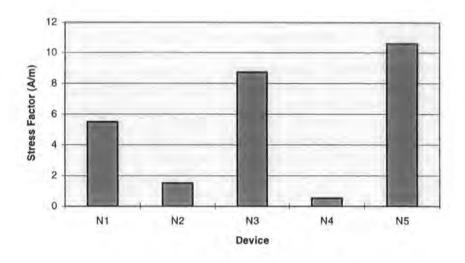

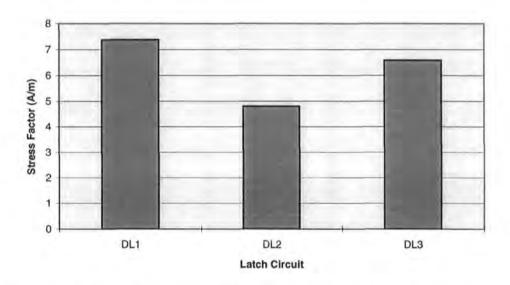

| 5.2 Relative effects of stress on each device in the latch circuits |                 |

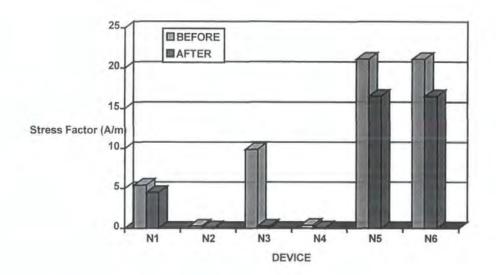

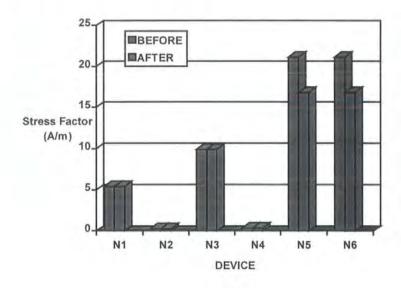

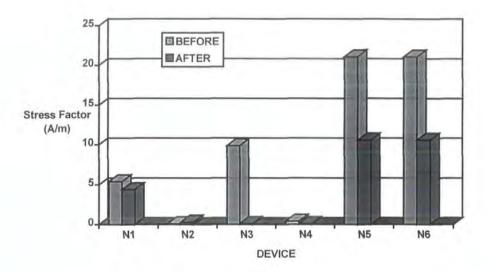

| 5.2.1 Effect of stress on Latch DL1                                 |                 |

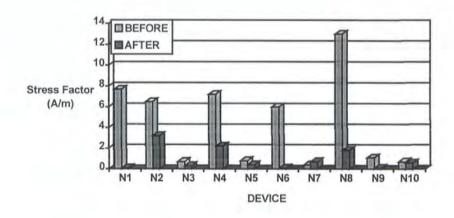

| 5.2.2 Effect of stress on latch DL2                                 |                 |

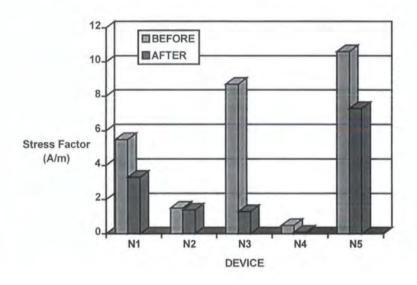

| 5.2.3 Effect of stress on latch DL3                                 |                 |

| 5.3 Degradation simulations                                         |                 |

| 5.3.1 AC Degradation Model                                          | 89              |

| 5.3.2 Characterisation of degradation effects under ac stress                                                                                                     | . 89                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| 5.3.3 Effects of uniform degradation of all devices in the latch                                                                                                  |                                               |

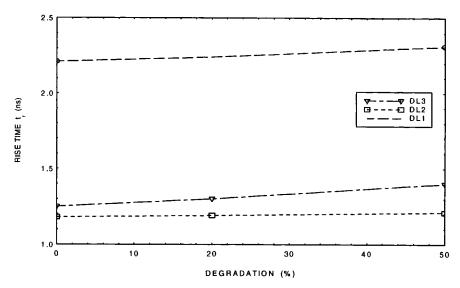

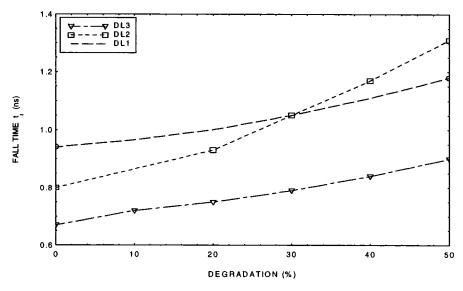

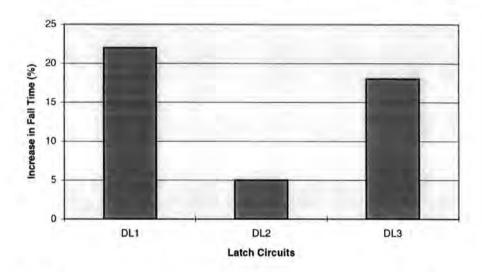

| 5.3.4 Effect of degradation on rise and fall times                                                                                                                |                                               |

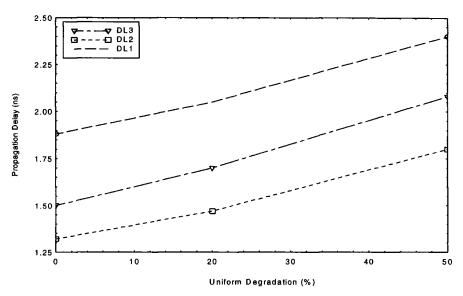

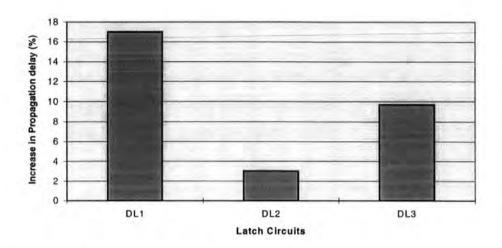

| 5.3.5 Effects of degradation on propagation delays                                                                                                                |                                               |

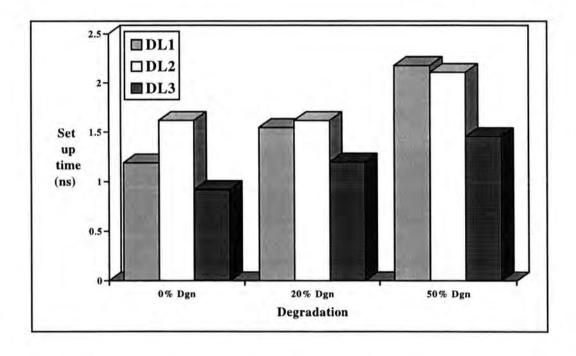

| 5.3.6 Effects of degradation on set-up & hold times                                                                                                               |                                               |

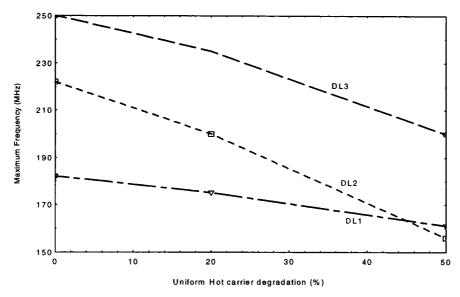

| 5.3.7 Effects of degradation on min. pulse width and max. frequency                                                                                               |                                               |

| 5.4 Relative susceptibility of different bistables to degradation                                                                                                 |                                               |

| 5.5 Chapter summary                                                                                                                                               |                                               |

| 5.5 Chapter Summary                                                                                                                                               | 101                                           |

| Chanton 6                                                                                                                                                         |                                               |

| Chapter 6                                                                                                                                                         |                                               |

|                                                                                                                                                                   |                                               |

| Metastability Behaviour and Reliability of Bistable circuits                                                                                                      | 103                                           |

| 6.1 What is Metastability?                                                                                                                                        | 103                                           |

| 6.2 A review of metastability in bistables                                                                                                                        | 105                                           |

| 6.3 Metastability resolving time                                                                                                                                  | 108                                           |

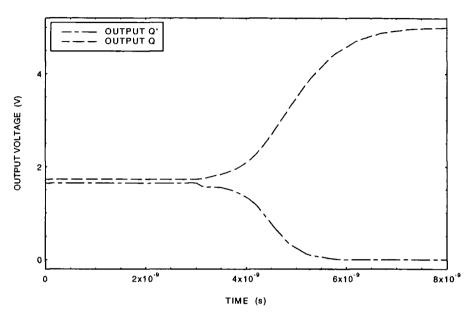

| 6.4 Metastability Simulations                                                                                                                                     |                                               |

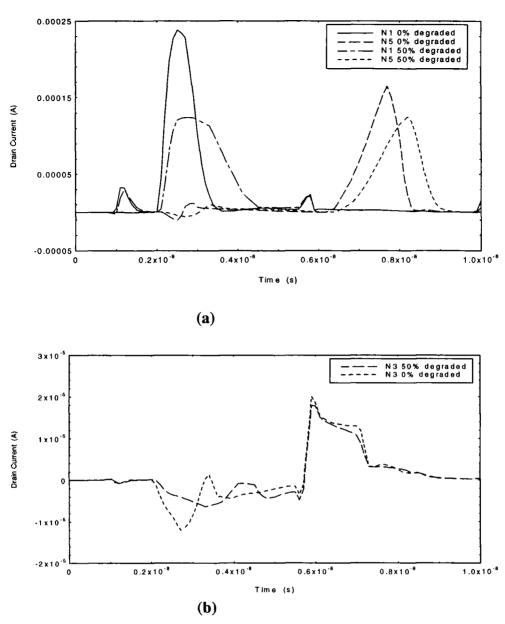

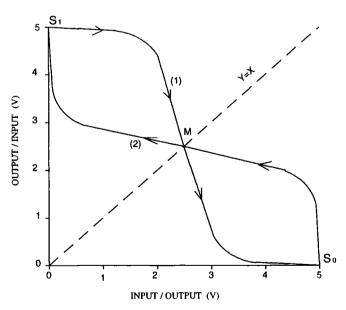

| 6.5 Effects of hot carrier degradation on metastability                                                                                                           |                                               |

| 6.5.1 Variation of resolving time with ABSTOL                                                                                                                     |                                               |

| 6.5.2 Effects of threshold voltage variation on metastability                                                                                                     |                                               |

| 6.6 Chapter summary                                                                                                                                               |                                               |

| 0.0 Chapter Summary                                                                                                                                               | 120                                           |

| Chapter 7                                                                                                                                                         |                                               |

| Chapter 7                                                                                                                                                         |                                               |

|                                                                                                                                                                   |                                               |

| Design Techniques for Reducing the Effects of the Degradation                                                                                                     | 1S                                            |

| and Improve Life-time                                                                                                                                             | 125                                           |

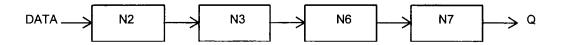

| 7.1 Techniques for Reducing the Stress on Circuit DL1                                                                                                             | .125                                          |

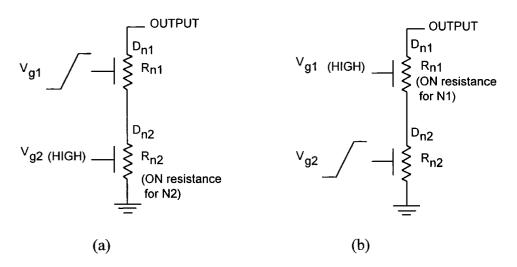

| 7.1.1 Stress Reduction for N1 and N3                                                                                                                              |                                               |

| 7.1.2 Stress Reduction for N5 and N6                                                                                                                              | . 129                                         |

| 7.1.3 Final Improved Design for DL1                                                                                                                               | 130                                           |

| 7.2 Techniques for Reducing the Stress on DL2                                                                                                                     |                                               |

| 7.2.1 Stress Reduction for N1                                                                                                                                     |                                               |

| 7.2.2 Improvements for Devices N2 and N3                                                                                                                          |                                               |

| 7.2.3 Improvements for N4 and N5                                                                                                                                  |                                               |

| 7.2.4 Improved Design for N6 and N7                                                                                                                               |                                               |

| 7.2.5 Improvements for N8                                                                                                                                         |                                               |

| 7.2.3 Implovements for ivo                                                                                                                                        |                                               |

| 7.2.6 Evaluation of the Improvements                                                                                                                              |                                               |

| 7.2.6 Evaluation of the Improvements                                                                                                                              | .134                                          |

| 7.3 Improvements for Latch Circuit DL3                                                                                                                            | .134                                          |

| 7.3 Improvements for Latch Circuit DL3                                                                                                                            | 134<br>136<br>136                             |

| 7.3 Improvements for Latch Circuit DL3                                                                                                                            | 134<br>136<br>136<br>136                      |

| 7.3 Improvements for Latch Circuit DL3                                                                                                                            | 134<br>136<br>136<br>137                      |

| 7.3 Improvements for Latch Circuit DL3. 7.3.1 Stress Reduction for N3. 7.3.2 Improvements for N5. 7.3.3 Improvements for N1. 7.3.4 Simulation of Improved Design. | 134<br>136<br>136<br>136<br>137               |

| 7.3 Improvements for Latch Circuit DL3                                                                                                                            | 134<br>136<br>136<br>137<br>137               |

| 7.3 Improvements for Latch Circuit DL3                                                                                                                            | 134<br>136<br>136<br>137<br>137<br>138        |

| 7.3 Improvements for Latch Circuit DL3                                                                                                                            | 134<br>136<br>136<br>137<br>137<br>138<br>140 |

| Chapter 8                                                                                  |

|--------------------------------------------------------------------------------------------|

| Quantitative Analysis of the results and the Reliability                                   |

| Improvements in the Selected Bistables143                                                  |

| 8.1 Reduction in Stress Factor                                                             |

| 8.2 Improvements in Life-Time                                                              |

| 8.3 Reliability Improvements                                                               |

| 8.4 Effect on Performance of the Latch Circuits                                            |

| 8.4.1 Transition Times                                                                     |

| 8.4.2 Propagation Delay                                                                    |

| 8.4.3 Operating Speed                                                                      |

| 8.4.4 Critical Window for Metastability                                                    |

| 8.5 Conclusions and Chapter Summary                                                        |

| Chapter 9                                                                                  |

| Summary and Conclusions                                                                    |

| 9.1 A Summary of the Thesis                                                                |

| 9.2 Conclusions of the Thesis                                                              |

| 9.2.1 Design Rules for Hot-Carrier Reliability.1599.3 Recommendations for Further Work.161 |

| 9.4 General Conclusions                                                                    |

| APPENDICES                                                                                 |

| Appendix A: Transistor dimensions for 3 micron CMOS design165                              |

| Appendix B: SPICE device model parameters                                                  |

| Appendix C: Circuit and input file for transistor characteristics172                       |

| Appendix D: CMOS Technologies                                                              |

| Appendix E: Device dimensions for CMOS design                                              |

| Appendix F: MATHCAD program                                                                |

| Appendix G: Publications                                                                   |

| 1. The Effect of Hot-Carrier Degradation on CMOS                                           |

| Bistable operation, ISSDT'95, 15-17 November 1995,                                         |

| Kruger National Park, South Africa                                                         |

| 2. Simulating Metastable State Operation in CMOS                                           |

| Flip-flops, ICSDT'96, 13-17 May 1996, Obninsk, Russia18                                    |

| References 194                                                                             |

# Chapter 1

### INTRODUCTION

As integrated circuit processing has advanced in recent years, the reliability of sub micron Complementary Metal Oxide Semiconductor (CMOS) bistables has been critically affected. One cause of this is timing errors introduced by wearout processes as a result of process tolerances and device degradation during normal operational life of the circuit. Increased semiconductor complexity and reduced feature sizes for devices have emphasised the need for greater understanding of the physical processes affecting the reliability of Very Large Scale Integrated (VLSI) circuits. For sub-micron devices, variations in their parameters due to fabrication tolerances and limited process control become larger on a percentage basis [1.1]

The two major failure classifications affecting the reliability of VLSI circuits are catastrophic failures and wearout failures. Catastrophic failures such as junction breakdowns, oxide breakdown and electrostatic discharge initiated breakdowns have been thoroughly investigated by many researchers. Wearout failures due to hot-carrier effects have become a major issue for submicron devices. Research has been going on for many years and have gained a very good understanding of the physical processes leading to the generation of hot-carriers in a MOS device and the damaging effects it can cause. But the degradation effects of hot-carriers on the various characteristic timing parameters of digital VLSI circuits have not been fully understood mainly because of the cumulative effects of time dependant degradation on individual devices in a large integrated circuit are difficult to assess. Furthermore, in comparison with combinational circuits, bistable circuits have been relatively neglected by many researchers. This may be due to the effects of positive feedback which can compensate for defects in many cases making the circuit less susceptible and preventing fault detection. The scaling of MOS transistors to submicron dimensions has caused degradation mechanisms to become a significant problem which needs to be addressed as a matter of priority.

CMOS has emerged as the dominant technology for VLSI digital circuits. In VLSI and ULSI systems, the low power and high packing density afforded by advanced CMOS process is vital. The increased circuit complexity was made possible by shrinking device geometry using scaled down MOS devices. Because the operating voltage is not scaled down proportional to the device geometry reduction, the electric fields in the channel of the devices have increased dis-proportionately. The high fields in the channel of MOS devices led to the phenomenon of hot-carriers giving rise to a number of problems in the channel, oxide layers and the depletion regions. Hot carriers can cause degradation in device characteristics and the overall reliability

of the circuit is affected. Hot-carrier degradation occurs in the field and so it is not very easy to assess the impact on reliability of the VLSI circuits at the design and testing phase unless field testing data is made available. In this context, it is important to consider the hot-carrier induced changes in electrical variables and the effects of these on the timing parameters of important VLSI circuit elements such as bistables. This information can be used to design a reliable bistable which when incorporated into a VLSI circuit will enhance the overall reliability of the circuit.

### 1.1 Objectives of the research

The main objective of the research was to establish the effects of CMOS wearout processes (not catastrophic failures) on the reliability of representative bistable circuits. One of the main factors affecting the reliability which is metastability in the bistables and the conditions which cause changes in the metastable behaviour of the bistable and hence eventual failure of the circuit have been investigated. Solutions to the problems caused by wearout have also been investigated. Device design techniques for reducing the effects of wearout processes on the timing performance of bistables have been proposed at the end of the thesis.

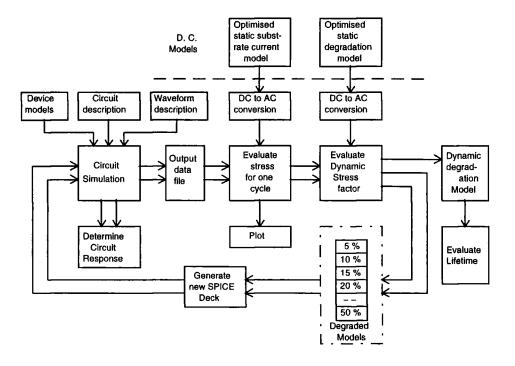

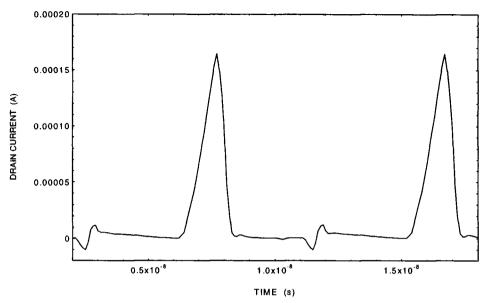

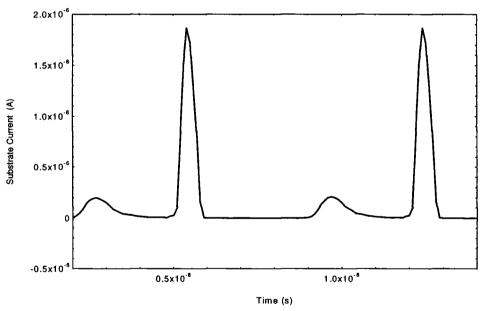

In this thesis we describe the hot carrier induced damage mechanisms and how to model the effects of degradation on MOS devices on the characteristic timing performance of bistable circuits designed using standard CMOS technology. All the identified known degradation effects due to hot-carriers have been incorporated into the hot-carrier degradation model which is based on a substrate current model to monitor stress levels on all the devices in a bistable circuit. Available data from other researchers have been used to characterise the degradation effects on the electrical parameters of the devices. AC degradation models were generated from dynamic stress simulations of the bistables and by processing the time varying current and voltage wave forms employing quasi-static analysis. Identified SPICE device model parameters have been used to incorporate the degradation effects and subsequent circuit simulations using degraded SPICE models were used to establish the timing performance degradation in the bistable circuits. Comparison of various forms of bistables simulated under identical conditions led to the identification of circuit forms which are less susceptible to hot carrier effects. Effects of hot carrier degradation on metastability behaviour has been investigated and bistable circuits which have better resistance to metastability have been identified. An understanding of the circuit configurations and stress levels leading to hot-carrier degradations led to proposals for circuit designs with improved reliability. The detailed analysis of the selected circuits simulated using the proposed design improvements have been used to quantify the reliability improvements in the cases under analysis.

### 1.2 The need for the research

The development of submicron CMOS technology has introduced a number of new factors into the reliability equation. The intrinsic wearout failure mechanisms such as hot carrier degradations are becoming an important factor in VLSI circuits. Wearout processes occur in all CMOS circuits although the time to failure may vary greatly. Manufacture of VLSI circuits now is based upon accurate simulation and estimation of the reliability of the circuit. Hence we need an accurate model to predict the stress levels on the various devices in a circuit under normal operating conditions.

Unfortunately for sub micron VLSI circuits, the reliability implications due to wearout processes such as hot carrier effects and electromigration have not been fully investigated and assessed before manufacture. Much time and cost could be saved if one is able to make a prediction of the reliability of the VLSI at the design phase. Reliability simulation offers an opportunity to uncover potential reliability hazards present in designs. The effectiveness of the reliability simulator is determined by the quality of the models employed and the time required for the simulations. It is possible to use accelerated testing or time steps to reduce the time for simulation for the wearout processes to progress provided that the acceleration factors are known and that the increased stress conditions are not going to introduce any other wearout mechanisms that are not present during normal operating conditions. The wearout processes leading to the eventual failure of bistable circuits have not been fully investigated yet and so it was necessary to develop a simulation model for the analysis of degradation effects on critical timing parameters of various forms of bistables. Unlike catastrophic failures, wearout degradations generate timing errors and an eventual failure of the bistable. Bistable elements are one of the basic building blocks of VLSI circuits and so the reliability of bistables are very important.

### 1.3 Outline of this Thesis

Following this introduction, a review of wearout processes in bistable circuits designed using CMOS technology is presented in chapter 2. The common terms used in reliability engineering and failure analysis have been defined. The basic distinction between the two major failure mechanisms, catastrophic and wearout faults, are discussed and the parametric faults to be investigated are identified.

In chapter three, we review the hot carrier generation and the degradation mechanisms in MOS devices. A new substrate current model has been developed which will be used to

monitor stress levels on MOS devices in a circuit. Using the substrate current model and employing characterisation techniques, a static degradation model has been proposed to monitor the effects of hot carrier stress.

Chapter four deals with the analysis and optimisation of a range of CMOS bistable circuits. The timing parameters are analysed using fault-free simulations and an optimisation procedure is used to select the most appropriate circuits for further analysis. The selected bistable circuits were redesigned using 1 micron and 0.7 micron device technologies and simulated to determine the fault-free delays.

In chapter five, hot-carrier degradation in bistable circuits is addressed. Using the static substrate current model and employing dynamic simulations, we have developed a dynamic stress model for the bistable. The modelling of the stress and the effects of hot-carrier degradation led to the evaluation of timing degradation in the selected bistable circuits. A comparative study of the hot carrier degradation effects on the selected bistable circuits is presented and the circuits having best performance identified.

Metastabe behaviour and its impact on the reliability of bistable circuits are considered in chapter six. Metastability simulations of the selected bistable circuits revealed the susceptibility to this condition and the metastable resistance as well as metastable window are defined and described. The effects of parametric variations including hot-carrier degradations on critical timing parameters leading to metastability on the bistable circuits are also addressed.

Design techniques for reducing stress and the effects of the degradation considered in chapter five and six are discussed in chapter seven. Improvements in the life-time of the bistables as a result of the design improvements are also considered. The characteristic timing parameters for the latch circuits are evaluated after the design modifications. The changes in metastability resolving time due to hot-carrier degradation was evaluated and analysed.

A qualitative analysis of the simulation results and the reliability improvements in the selected bistables has been considered in chapter eight. Improvements in reliable operating lifetime of the circuits have been analysed, compared and quantified. The overall effect of design improvements on the characteristic timing parameters have been assessed. Chapter nine deals with the conclusions and some suggestions on future direction for research work. A few design rules for reducing the hot-carrier degradations and hence how to improve the reliability of the bistable circuits have been suggested.

# Chapter 2

# Wearout Processes in CMOS and Reliability of VLSI Circuits

Reliability standards for VLSI are becoming more stringent with a required failure rate of one failure per 10<sup>8</sup> devices per hour [2.1]. The improvement in reliability can only be achieved by the interaction of the design engineer and the process engineer in order to remove process and design related problems. It has been reported in the literature [2.1]-[2.4] that the key failure mechanisms in VLSI circuits are related to hot-carrier damage, electromigration, radiation effects, electrostatic discharge and time-dependent dielectric breakdown and in many cases the failure arises because of manufacturing defects.

The observed failure rate of electronic components in VLSI circuits can be considered to be made up of intrinsic and extrinsic failure rates. According to Campbell [2.5], the intrinsic failure rate is dependant on the physical processes inherent within the device. This leads to wearout during normal operation which has long time scales and so does not contribute significantly to the failure rate during the useful life of a component. Takeda [2.1] has reported that increased VLSI reliability has been achieved by improving device and circuit structures for overcoming hot-carrier effects, dielectric breakdown and stress effects and will require close control of every process condition including gas purification and contamination of impurities in the wafer. The damaging effects of degradations no longer can be predicted by fault analysis based on the simple fault models developed by many researchers. Common fault models are the stuck-at, stuck-closed and the stuck-open fault models and the reader may refer to any of the following references [2.6]-[2.11].

Technological evolution and reliability engineering influence each other. Reliability engineering is a branch of human knowledge that has the aim of describing, predicting and improving the behaviour over time of components and systems. Failure analysis is the study of each individual anomaly with the aim of determining the dynamics of the physiochemical mechanism responsible for it and locating the cause, outside or inside the component [2.12]. The techniques of investigation applied to failure analysis have been applied to the study of new devices with the aim both of knowing the process and trying to identify eventual weak points present in the new device; and extracting information that will improve the reliability. Failure analysis carried out intensively, implemented with its methodology of observation and analysis and the development of a new branch of physics have exercised a decisive role in the evolution of the semiconductor failure technology.

In this thesis, it is postulated that all the devices in a VLSI circuit do not receive the same amount of electrical and environmental stress. For submicron devices in a VLSI circuit, the major concerns are wearout mechanisms, which lead to degradation in the circuit performance due to overstress in critical devices, and eventual failure. The effects of such over-stress and the gradual degradation of circuit delays have not been fully investigated in the case of latches and flip-flops in CMOS VLSI circuits. Bistables are critical circuits and hot-carriers are a major reliability hazard and can give rise to reduced performance of the IC. The proposed method to investigate this problem is to evaluate the extent of stress and to determine the eventual degradation of key circuit parameters on critical devices in a range of bistable circuits. Once this is established, methods to reduce the stress and hence to improve the reliability of the VLSI circuit will be identified.

### 2.1 Terminology

Some of the common terms used in this thesis are defined below, based on a survey of literature [2.12]-[2.16]:

**Wearout:** gradual degradation or deterioration of the specified characteristics of the main population of non defective devices which may lead to an eventual failure which ideally will occur a considerable time after manufacture. Doyle [2.16] defines wearout as the process of attrition that results in an increase of hazard rate with increasing age.

**Hazard rate:** The rate of change of the number of items that have failed at a particular time divided by the number surviving.

**Degradation:** deterioration in the characteristic parameter(s) of a device or circuit.

**Reliability:** is a characteristic of a device or circuit expressed by the probability that the item will perform its required function under specified conditions for a stated interval of time.

Reliability,

$$R(t) = \exp(-t/\tau)$$

--- (2.1)

where  $\tau$  is the life-time of the device.

Fault: unacceptable discrepancy between actual performance and its expected performance.

Failure: termination of the ability to perform a required function due to presence of a fault

1 FIT: 1 failure per 109 device hour.

Failure Mechanism: is the physical, chemical or other process that result in failure.

Failure mode: the effect by which a failure is observed.

Stress: Any influence to which an item is exposed to at a certain instant.

**Life-Time** ( $\tau$ ): is the expected (reliable) operating period of the device.

Mean time between failure (MTBF): is the mean of all time periods over an infinite length of time for which the device has functioned correctly before failing.

Failure rate: the probability of failure in unit time of a component which is still working satisfactorily.

Failure rate,

$$Z(t) = \frac{\text{Number failing per unit time at instant t}}{\text{Number surviving at instant t}} --- (2.2)$$

For a constant failure rate,  $Z(t) = \lambda$ , and so the constant failure rate is the number failing per unit time.

If we assume that the reliability to be 100% at t = 0, then R(0) = 1 and  $R(t) = \exp(-\lambda t)$

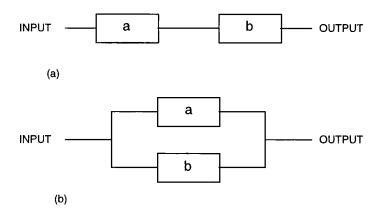

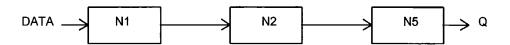

For a system consisting of two sub systems in series as shown, the failure rate for the system [2.20],

$$\lambda_{\text{system}} = \lambda_{\text{a}} + \lambda_{\text{b}}$$

--- (2.3)

and the system reliability is,

$$R_{\text{system}} = \exp \left[ -(\lambda_a + \lambda_b) t \right] \qquad --- (2.4)$$

For a system made up of two identical sub systems in parallel, the reliability for the sub systems are,

$$R_a = R_b = \exp(-\lambda t) \qquad ---(2.5)$$

and the system reliability (for a parallel system) is [2.20],

$$R_{\text{system}} = 1 - (1 - R_a) (1 - R_b)$$

--- (2.6)

Figure 2.1 (a) Series and (b) parallel models for reliability evaluation

Substituting equation 2.5 into equation 2.6 for the identical sub systems,

$$R_{\text{system}} = 2 \exp(-\lambda t) - \exp(-2\lambda t) \qquad --- (2.7)$$

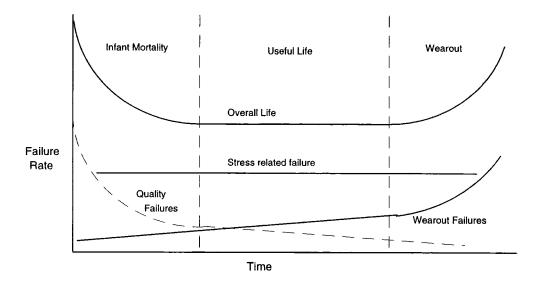

A common graphical interpretation of the failure rate known as the bathtub curve [2.13], [2.16] is shown in figure 2.2. The overall life characteristic curve (thick line) is a plot of failure rate versus time and can be divided into three regions, the infant mortality region, useful life and wearout phase. This curve can be further defined by the three failure components as shown in the bottom part of the figure. Stress related failure shown as a thin horizontal line is a constant failure rate and the wearout phase only starts later in life and starts to increase with age.

Figure 2.2 The bathtub curve

Accelerated Tests: The principle is to apply stress to a limited quantity of devices, under bias or environmental conditions above the normal ratings, to speed up the failure mechanisms that would occur in actual operating conditions and then extrapolate the behaviour observed on one lot to an entire population.

**Screening:** The principle of screening is to submit the entire population to low intensity stress with the aim of inducing failure only in the devices that are already weak and without damaging those that are strong.

Screening or burn-in testing has greatly reduced the failure rate in the field, since it identifies and allows elimination of early failures.

**Arrhenius'** Law: Temperature is one of the environmental stress that most often accelerates the degradation in semiconductor devices. A mathematical model of failure rate at raised temperature is,

$$\lambda(T) = \lambda(T_0) \exp\left[\frac{E_a}{k} \left(\frac{1}{T_0} - \frac{1}{T}\right)\right] \qquad ---- (2.8)$$

where T: temperature in Kelvin,  $T_0$ : reference temperature in Kelvin,  $\lambda(T)$ : failure rate at temperature T,  $E_a$ : activation energy for failure mechanism in electron-volt and k: Boltzmann's constant. The activation energy is often used to characterise a failure mechanism.

### 2.2 A Review of Wearout Processes

As opposed to catastrophic failures, wearout processes in VLSI circuits are very difficult to predict and, therefore more difficult to model. The physical mechanism of the wearout processes can vary from one process technology to another as well as from device/design technology point of view. MOS devices designed using sub micron technology design rules are expected to wearout faster because of factors such as increased current density and raised operating temperature.

Wearout mechanisms in VLSI circuits can be classified as operational if they require the external application of a voltage to the chip and as environmental if they do not. Examples of environmental wearout are corrosion, surface ionic inversion and diffusion, while examples of operational wearout are electromigration, hot-carrier degradation and charge injection. Not all wearout processes may lead to failure of the circuit. Failure mechanisms in MOS VLSI circuits are either process-related or timerelated. Some devices wearout faster when operated normally due to defects introduced during processing [2.4]. Burn-in tests can identify most of the weak devices due to this type of wearout mechanism. Takeda [2.1] has reported that wearout processes such as hot-carrier degradation, dielectric breakdown and degradation in the aluminium used as interconnect are responsible for time-dependant failures which are shown to affect the reliability of sub-micron VLSI circuits. According to another researcher [2.14], timedependant wearout mechanisms leading to failure may give rise to abnormally high and low ohmic resistance in the interconnect layers, high resistance contact windows, excessive drain/source-substrate reverse leakage currents, large threshold voltage shifts, transconductance degradations, gate-oxide breakdowns, excessive sub-threshold leakage currents and device width and length variations.

Reviewing the literature in the field [2.3], [2.12]-[2.18] suggests the following list of wearout processes which may lead to an eventual failure:

(a) Electromigration: Electromigration is a clear example of a wearout mechanism which can lead to failure. If the current density is sufficiently high in the aluminium tracks on the semiconductor surface, the continuous impact of electrons on the Al grains cause the grains to move in the direction of electron flow [2.3]. A void is created at one end of the track while metal accumulates at the other end. Failure can occur due to an open circuit of the track at a thin region or due to short circuit with another track where the Al grains pile up.

- (b) Hot-carrier degradation: The current sub micron MOS transistors used in VLSI circuits are susceptible to damage due to hot-carrier degradation. MOS transistors have two main characteristics, threshold voltage and transconductance. Any small change in one of these parameters can alter the performance of a circuit. If charge carriers are introduced into the gate dielectric then the threshold voltage will be changed and the transconductance will be degraded. Electrons may be injected into the gate oxide of an NMOS transistor when a hot electron in the channel collides with the crystal lattice generating electron-hole pairs which are attracted to the interface due to the lateral electric field. The electrons must have higher energy to surmount the silicon-silicon dioxide barrier. As device feature sizes are reduced, a corresponding reduction in thickness of the oxide dielectric layers are also made, which increases electric field strengths significantly. Hot electrons are injected from the channel into the oxide layer mainly in the avalanche plasma region near the drain [2.1]-[2.4].

- (c) Oxide breakdown: Oxide breakdown is another wearout process which can lead to a gradual increase in gate to channel leakage current and an eventual short circuit from gate to channel. If an electron injected into the gate oxide has sufficient energy, it will produce electron-hole pairs by impact ionisation. The electrons created are collected by the gate and give rise to a small gate current in the case of an NMOS transistor. The holes are trapped in the gate oxide making it more positive and so encouraging more impact ionisation of hot electrons from the channel and an eventual breakdown of the oxide layer [2.1].

- (d) Corrosion: Another metalisation related problem is that of aluminium corrosion due to galvanic or electrolytic action [2.1]. Galvanic corrosion may occur due to the bonding of gold wires to aluminium pads producing corrosion at the junction. The intermetallic compounds formed between the gold and aluminium can produce bond embrittlement or voiding, leading to bond breakages and open circuits. Electrolytic decay occurs due to impurities in the overglass used to protect the IC surface from contamination. If chlorine is present with a small amount of moisture then the aluminium can be attacked, forming aluminium hydroxide and eventually producing an open circuit. This effect is increased by high electric field between conductors.

| Failure mode     | Definition                        | Effect                              |

|------------------|-----------------------------------|-------------------------------------|

| Internal short   | Short from metal to metal or      | Circuit malfunction or failure      |

|                  | diffusion region or polysilicon   |                                     |

| Internal open    | Open circuit in the metal or wire | Circuit malfunction or failure      |

|                  | bond or contact                   |                                     |

| Parametric shift | Variation of gain or other        | Marginal performance or             |

|                  | electrical parameter              | temperature sensitivity             |

| Junction         | Leakage current across p-n        | Malfunction and increased current   |

| leakage          | junctions                         |                                     |

| Threshold shift  | Shift in turn-on voltage          | Increased propagation delay,        |

|                  |                                   | random logic malfunction            |

| Oxide            | Charges and traps in oxide        | increased propagation delay         |

| damage           | and interface                     |                                     |

| Seal integrity   | Ingress of ambient air, moisture  | Effects ranging from degradation to |

|                  | and/or contaminants               | complete malfunction                |

Table 2.1 Failure modes in semiconductor devices.

A summary of principal failure modes for semiconductor devices is given in table 2.1 [2.16].

# 2.3 Distinction between catastrophic and parametric faults

Catastrophic faults are those leading to a complete and sudden or obvious malfunction of the device or circuit. Examples of catastrophic failures are those due to electrostatic discharge, short circuits and open circuits due to process induced faults and many of the stresses (voltage and mechanical) induced failures, leading to complete destruction of a semiconductor junction or a metal track. Gross defects such as missing bond, large mask misalignment, wrong ion implantation dose etc. produces catastrophic failures [2.14]. The effect of catastrophic faults on a circuit can be normally detected at the outputs using a few simple tests and so these are well researched and understood even though new types of failure mechanisms may arise as device dimensions are further scaled or when new process technologies are implemented.

Parametric faults are quite different from catastrophic faults in that they may not give rise to a hard failure of the device or circuit and may take a relatively long period of time to manifest even though the mechanisms responsible for the fault already exist. Such a fault may have to be detected indirectly because the present fault detecting algorithms are unable to detect it directly since it lies dormant in a device and can only develop into a fault after a period of time in field use. A literature survey [2.14], [2.17] shows that a number of wearout mechanisms in CMOS may not cause hard failures of a device. These are:

- (i) gradual increase in resistance of a metal track due to electromigration,

- (ii) a change in the dielectric properties of gate oxide due to charges injected into it,

- (iii) threshold voltage shift,

- (iv) transconductance degradation,

- (v) excessive subthreshold leakage current,

- (vi) excessive drain/source-substrate reverse leakage current and

- (vii) Device width and length variation due to inter diffusion or corrosion.

These are classified as wearout mechanisms leading to parametric faults. Functional level and logic level simulators do not have the models necessary to specify the above set of faults [2.14]. Faults resulting from process induced or intrinsic defect induced wearout [2.4] are easily detected using accelerated tests therefore are not classified as parametric faults. Parametric faults can be detected by the potential of a device to develop the fault when it is operated in a circuit under certain conditions such as increased stress during active life of the device. Hence tests must be devised to detect increased stress on a device in a circuit environment. Electrical, mechanical or environmental overstress can give rise to prolonged wearout leading to parametric faults. An increase in the time it takes for a specific sequence of tests to propagate through a defective circuit is a parametric fault called *delay fault* [2.8]. Hot-carrier degradation and electromigration are two examples of parametric degradation mechanisms.

### 2.4 Parametric faults identified for investigation

Not all parametric faults in CMOS circuits lead to catastrophic failures. There is a significant amount of literature dealing with fault analysis in CMOS for catastrophic faults. Wearout was not considered as a problem for semiconductor devices until submicron devices became the standard in VLSI and ULSI circuits in the 1990s. It was reported by Christiansen [2.15] that since semiconductor devices have no wearout mechanism, the late-life end of the *bathtub* in the life characteristic curve is missing! Doyle [2.16] also stated that wearout failures are not a factor with semiconductors whose life characteristic curves tend to be flat after the early failure period. But these suggestions are incorrect for submicron devices as these devices degrade faster and have wearout mechanisms not encountered in normal devices of larger dimensions. Takeda [3.21] stated that the influence of scaling down device dimensions on hot-carrier generation can be fatal for submicron devices. Researchers [3.7-3.10] also found evidence of wearout mechanisms for MOS logic circuits designed using submicron devices that are not normally found in 2- and 3- micron device technologies.

Hot-carrier degradations have been investigated for several decades by many researchers and have become a major constraint on submicron MOS devices as the degradation effects set in at a much faster rate. The degradations in device parameters are more or less understood. The effects of hot-carrier degradations on combinational circuits under normal static operation also have been investigated. But the research into the degradation effects due to hot-carriers on the timing and propagation through sequential circuits has not been fully investigated yet.

The parametric faults which are identified for investigation in this thesis are the **hot-carrier** induced degradation effects and the effect of the degradation on the **metastability** of the CMOS bistable circuits. Modelling of hot-carrier degradation will be discussed in the next chapter. Hot-carrier degradation simulations will be presented in chapter 5 and metastability simulations will be considered in chapter 6. Improvements in circuit designs to reduce hot-carrier degradations are considered in chapters 7 and 8.

### 2.5 Chapter summary

The wearout processes affecting the reliability of VLSI circuits have been reviewed. Reliability in VLSI circuits has been increasing with improved processing technology and due to the fact that there exists a greater understanding of the physical mechanisms responsible for the failures. Failure physics has been applied for the identification of mechanisms responsible for wearout processes leading to circuit failure and hence affecting the reliability of VLSI circuits. The common terms used in reliability engineering and failure analysis have been defined. For submicron devices, hot-carrier degradations were identified as a major reliability problem that needs to be addressed as a matter of priority.

# Chapter 3

# Modelling hot-carrier degradation effects

The wearout processes affecting the reliability of VLSI circuits have been considered in chapter 2. The dominant degradation mechanisms in submicron devices have been identified as hot-carrier degradations and the effect of degradation on metastability of CMOS bistables.

Reliability research involves the following sequence of steps:

- (i) characterising the effect contributing to reliability problems,

- (ii) mathematical modelling of the effects,

- (iii) incorporating the model into a CAD package and

- (iv) using these tools to optimise the design.

Understanding the physical principles of various degradation mechanisms and their effect on circuit behaviour is essential for successful modelling of the effects and hence improving the reliability through the optimisation procedure. Many of the degradation effects in CMOS VLSI circuits cannot be successfully modelled by the gate-level stuck-at, stuck-closed or stuck-open models. Degradation effects due to hot-carriers and metastability behaviour in CMOS circuits fall into this category.

In this chapter, we will review the present understanding of the physical mechanisms leading to hot-carrier generation and the effect of these on MOS device model parameters. We will also examine some of the existing mathematical models used for simulating hot-carrier degradation effects on MOS devices. We will present an improved model which takes into consideration additional effects which have been ignored by previous models. As the degradations in devices progress in a circuit environment, the main difficulty in quantifying the degradations was to identify a parameter which can be used as a monitor. Many researchers have suggested different

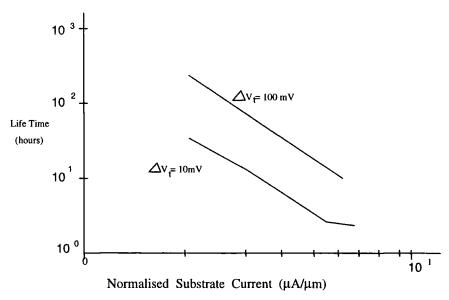

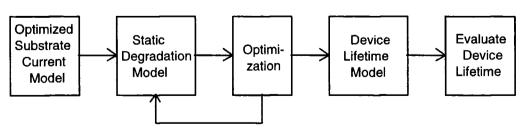

techniques for this and have defined *device lifetime* using the shift in this parameter as a guideline. We have made use of a modified model based on substrate current as a monitor to predict the lifetime of the device.

### 3.1 Hot-carriers: a review

Research into hot-carrier generation and degradation in CMOS devices has been carried out by many researchers. The investigation of hot electrons in solids was initiated by Landau and collaborators in the mid-nineteen-thirties [3.1]. Experimental understanding of electron transport and acceleration in vacuum tubes led to similar studies in solids under the action of electric and magnetic fields. Frohlich introduced the idea of field-dependent electron temperature and the concept of a hot-electron in 1947 [3.2]. In 1951 Shockley postulated [3.3] that the characteristic temperature (average energy) of electrons in a solid is proportional to the electric field strength based on his early work on electron conduction in germanium and silicon. According to the *Lucky electron model*, electrons acquiring a kinetic energy greater than 1.5 eV may initiate ionisation by collision with lattice atoms in the solid [3.4]. At a typical field strength of 105 V/cm the electrons will gain sufficient energy for impact-ionisation giving rise to carrier pairs and phonon emission.

### 3.1.1 Generation of hot-carriers and substrate current

A MOSFET is a voltage controlled device. The current through the device can be expressed as a function of the MOSFET terminal voltages and the device (geometrical) parameters using the Gradual Channel Approximation (GCA). In GCA it is assumed that the transverse electric field (gate to channel field) is much greater than the longitudinal field (along drain to source) [3.5]. The current in a MOSFET is intended to flow between the source and the drain. Currents to the substrate and the gate, and from one device to another, are prevented by potential barriers between different regions of the device. As device dimensions shrink, it becomes harder to maintain large potential barriers between adjacent regions and tunnelling currents may flow as the barrier decreases. The decreasing barriers give rise to reduced radii of curvature of depletion regions and localised regions of very high field are formed. For sub-micron devices, the GCA is not valid since the longitudinal field is now comparable to the transverse field. The two-dimensional potential results in degradation

of the sub threshold behaviour, dependence of the threshold voltage on channel length and biasing voltages and failure of current saturation due to punch-through.

As the longitudinal field is increased, the channel mobility becomes field-dependent and eventually velocity saturation of the carriers occurs. When the field is increased further, carrier multiplication near the drain occurs, leading to substrate current and parasitic bipolar action. The generation of substrate current will be discussed in more detail in the next section. The high field also causes *hot-carrier* injection into the oxide leading to oxide charging and subsequent threshold voltage shift and transconductance degradation [3.5]. Hot-carriers are electrons or holes in the channel and pinch-off regions of a short channel MOSFET which have gained sufficient energy from the high lateral electric fields in the channel to cause their energy distribution to greatly exceed that which would be expected if they were in equilibrium with the lattice [3.6]. The generation of these hot-carriers can be the cause of reliability problems and there are a number of factors which can influence the generation of hot-carriers. Many effects not encompassed in the simple theory of FETs are collectively known as *short channel effects* and these limit the scaling of FETs.

The research into hot-carrier degradation has been gaining momentum during the last fifteen years and much understanding has been gained in recent years. However there is still some controversy and debate about the nature of degradation and the physical processes involved, mainly because of the limitations in the conventional techniques used to monitor carrier injection and device degradation. We will now take a closer look at the physical processes which bring about the degradation and their effects on the device parameters. This will help us to model the hot-carrier degradations for circuit simulation studies.

### 3.2 Hot-carrier degradation mechanisms

The degradation mechanisms and the overall effect on the device parameters will now be discussed in detail. The reliability and the life-time of the devices are estimated using characterisation of the hot-carrier mechanisms and simulations of the degradation effects. In the case of an nMOS transistor, with a positive voltage on the gate, inversion of the p-region between the drain and the source occurs, forming an n-type conduction channel extending from drain n<sup>+</sup> region to source n<sup>+</sup> region. A potential

applied on the drain with respect to the source sets up a longitudinal field along the channel causing the electrons to be swept across from the source to the drain. The longitudinal field has a pronounced peak in the vicinity of the substrate-drain junction at the  $Si\text{-}SiO_2$  interface [3.6-3.8]. The electrons in the channel absorb energy and can become *heated* because of the interaction between them. Some of the hot electrons with energies higher than 1.5 eV generate electron-hole pairs by impact ionisation. The electrons generated contribute to added current ( $I_D$ ) and the holes travel towards the source. Some of these holes are repelled away from the interface and they are attracted by the low substrate potential [3.31]. This causes a substrate current of the order of micro amperes at a value of  $V_{DS}$  of 5 V or more. The substrate current generated can be used as a monitor for hot-carrier generation in the transistor [3.8].

If the drain voltage is higher than 5 V, some electrons can gain energy of 3 eV or more so that they can overcome the energy barrier of 3.1 eV between silicon and oxide and may be trapped or form interface states, generally damaging the dielectric properties of the oxide [3.6], [3.8]. For even higher fields, holes generated due to impact ionisation can overcome their barrier of 4.8 eV into the valence band of the SiO<sub>2</sub> and be injected into the oxide. Holes can cause greater damage inside the oxide than the electrons although, fortunately, there are fewer high energy holes than hot electrons so that the degradation is relatively insignificant at normal operating voltages.

In order to understand the physical mechanism of the hot-carrier degradation in MOS devices, several MOSFET parameters have been commonly used as a measure of the damage. These are  $\Delta I_{DS}/I_{DS}$ ,  $\Delta g_m/g_m$ ,  $\Delta I_{DS}-V_{GS}$  curves, the change of sub threshold slope S,  $\Delta V_T$  with  $V_T$  defined at a constant current level etc. Variations in  $V_T$ ,  $\mu$ ,  $g_m$  etc. can be characterised using these curves. Many experimental techniques such as *charge pumping* (CP) and *floating gate* (FG) were employed by many researchers [3.6], [3.32],[3.42] to characterise the hot-carrier effects.

### 3.2.1 Multiplication and oxide charging

As the injection of hot-carriers into the gate oxide is the driving force of the degradation in MOSFETs, the process of generation of hot-carriers will be examined in detail. In a long-channel MOS transistor, when the drain voltage becomes sufficiently high, a weak avalanche occurs within the pinch-off region. From the avalanche plasma,

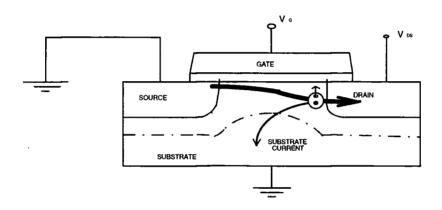

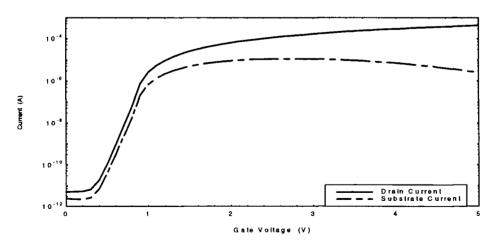

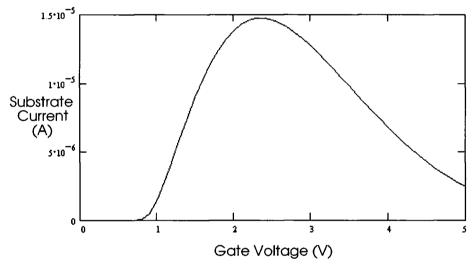

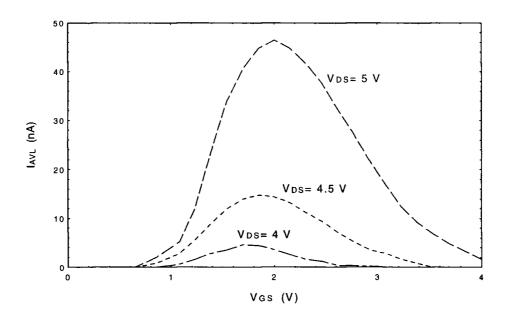

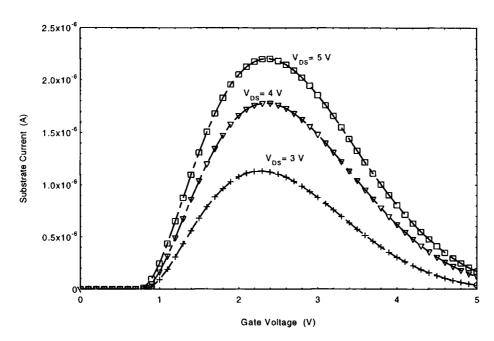

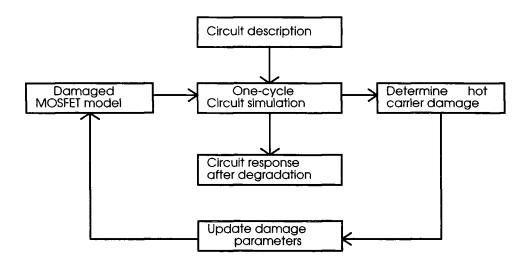

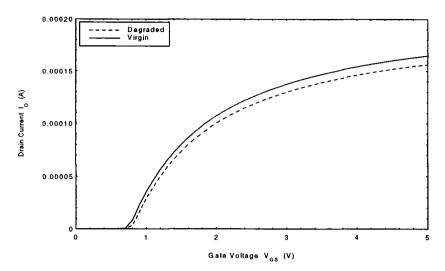

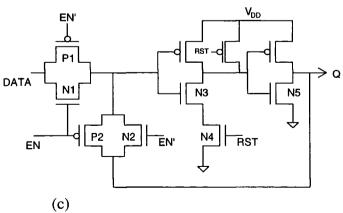

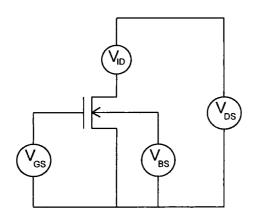

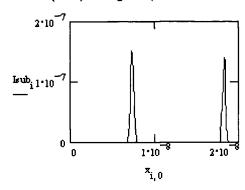

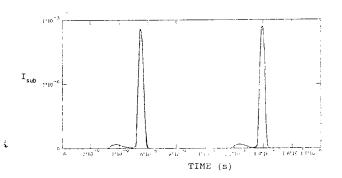

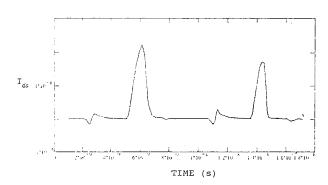

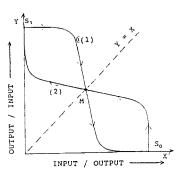

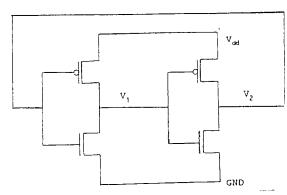

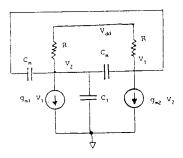

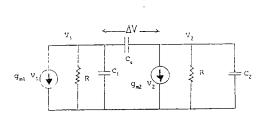

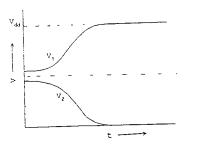

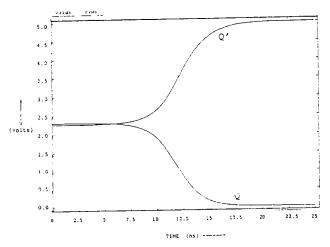

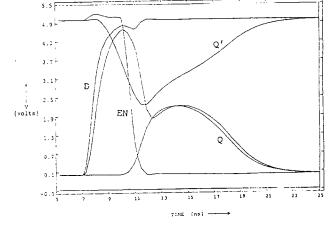

the generated electrons enter the drain and the generated holes are collected by the substrate terminal and constitute a substrate current. A schematic diagram [3.9] showing the generation of substrate current in an nMOS transistor is shown in figure 3.1. The substrate current  $I_{SUB}$  plotted as a function of the gate voltage using equation (3.1) for a long-channel transistor is shown in figure 3.2. The drain current for the device is also shown and it covers the region from sub-threshold to linear and then to saturation. The substrate current increases first with  $V_{GS}$ , reaches a maximum, then decreases.

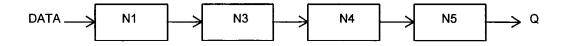

Figure 3.1 Cross section of an nMOS transistor showing substrate current generation

Figure 3.2 Drain current and substrate current versus gate voltage for an nMOS transistor (W=1  $\mu$ m, L=0.8  $\mu$ m, V<sub>DS</sub> = 5 V, Process: EC/3 (see appendix D))

The maximum in IsuB characteristic can be explained as follows. Assuming that the impact ionisation occurs uniformly in the pinch-off region, the substrate current can be written as, [3.5]

$$I_{SUB} = I_{D}.\gamma.\Delta L \qquad --- (3.1)$$

where  $\gamma$  is the ionisation coefficient, the number of electron-hole pairs generated per unit distance; and  $\Delta L$  is the length of the pinch-off region. For a given  $V_{DS}$ , as  $V_{GS}$  increases, both  $I_D$  and  $V_{DS.SAT}$  increase. When  $V_{DS.SAT}$  increases, the lateral field ( $V_{DS} - V_{DS.SAT}$ )/L decreases, causing a reduction of  $\gamma$ . Thus we have two conflicting factors. The initial increase of IsuB is caused by the increase of drain current with  $V_{GS}$ , and at larger  $V_{GS}$  the decrease of  $I_{SUB}$  is due to the decrease of  $\gamma$ . Maximum  $I_{SUB}$  occurs where the two factors balance.

For short-channel devices, the additional effect is caused by the avalanche-generated hole current. As the source-drain separation is reduced, some hole current can flow to the source. If the drain voltage is low, most of the hole current flows out at the substrate terminal; the substrate current behaves similarly to that shown in fig. 3.2. However when the drain voltage is large, a substantial hole current can flow to the source and the product of the current and substrate resistance can become large enough (> 0.6V) to forward-bias the source-substrate junction, causing electron injection into the substrate. This injection leads to a parasitic n-p-n (source-substrate-drain) bipolar transistor action [3.5]

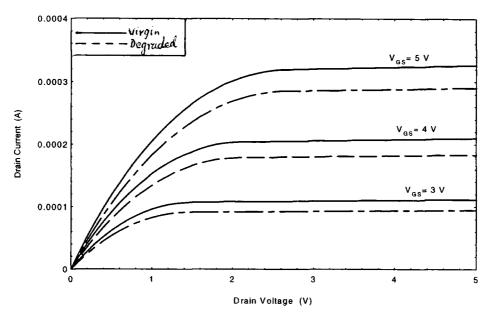

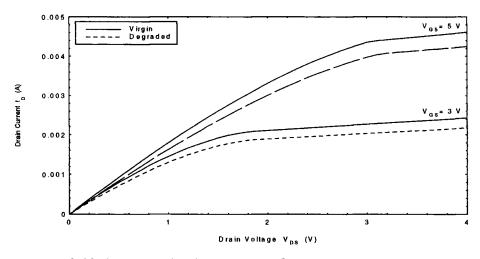

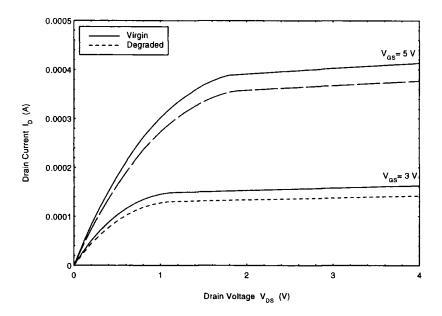

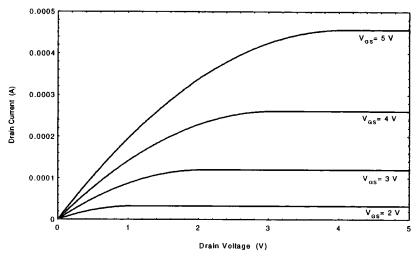

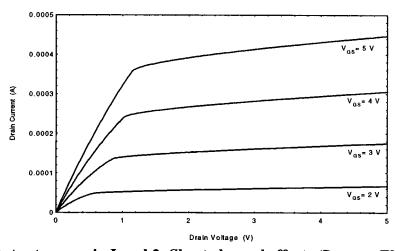

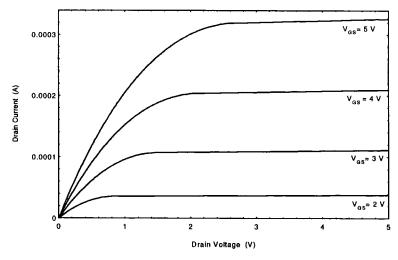

As the field along the channel becomes high, it is possible for some hot-carriers in the inversion layer to gain sufficient energy to surmount the Si-SiO<sub>2</sub> energy barrier (3.1 eV) and be injected into the gate oxide. Hot electrons can therefore be injected from the avalanche plasma formed near the drain region. Thermally generated carriers can also be injected into the oxide due to a large transverse field in the bulk semiconductor. The effects of the injected hot electrons on the  $I_{DS}$  -  $V_{DS}$  characteristics are shown in figure 3.3. Note the reduction in drain current after stress. The transconductance becomes smaller because of reduced channel mobility [3.5] and the sub threshold current becomes larger because of the increased interface trap density. An increase in threshold voltage also can be observed on a  $I_D$  -  $V_{GS}$  curves for the device.

Long-term operation of the device is seriously affected by oxide charging,

because the charging continues to increase with time during device operation. As a result of this cumulative degradation, oxide charging limits the maximum voltage levels that can be applied for a device to have a specified lifetime [3.10], [3.11]. As the channel length is reduced, different mechanisms limit the maximum drain voltage.

Figure 3.3 Degradation in drain current due to hot-carrier stress (Device: N 4/3 (see appendix: E) Process: EM/3)

### 3.2.2 Carrier temperature and mobility degradation

At low electric fields the drift velocity in a semiconductor is proportional to the electric field and the proportionality constant is called the mobility  $\mu$ , which is independent of the electric field. When the fields are sufficiently large, non-linearities in mobility and saturation of drift velocity are observed. At still larger fields, impact ionisation occurs.

As the electric field increases, the average energy of the carriers also increases and they acquire more energy than they have at thermal equilibrium. The effective temperature  $T_e$  at high field is higher than the lattice temperature  $T_e$  and is given by [3.5],

$$\frac{T_e}{T} = \frac{1}{2} \left\{ 1 + \left[ 1 + \frac{3}{8} \pi \left( \frac{\mu_0 \varepsilon}{C_s} \right)^{1/2} \right] \right\} \qquad --- (3.2)$$

and the drift velocity is given by,

$$v_{d} = \mu_{0} \varepsilon \sqrt{T/T_{e}} \qquad --- (3.3)$$

where  $\mu_o$  is the low field mobility,  $\varepsilon$  is the electric field and  $C_s$  is the velocity of sound in the semiconductor. When  $\mu_o \varepsilon$  is comparable to  $C_s$  (low fields),

$$T_{e} \approx T \left[ 1 + \frac{3\pi}{32} \left( \frac{\mu_{0} \varepsilon}{C_{s}} \right)^{2} \right] \qquad --- (3.4)$$

and

$$v_d \approx \mu_0 \varepsilon \left[ 1 + \frac{3\pi}{64} \left( \frac{\mu_0 \varepsilon}{C_s} \right)^2 \right]$$

--- (3.5)

When the field increases to  $\mu_0 \varepsilon \approx \frac{8}{3} C_s$ , the carrier temperature  $T_e$  is double that for

low field and the mobility drops by 30% [3.5]. Finally at sufficiently high fields, the drift velocity approaches a saturation velocity,

$$v_s = \sqrt{\frac{8E_p}{3\pi m_0}} \sim 107 \text{ cm/s}$$

--- (3.6)

where E<sub>p</sub> is the optical-phonon energy. At very high fields, the carriers gain enough energy so that they can excite electron-hole pairs by impact ionisation. The electron-hole pair generation rate G is [3.5],

$$G = \gamma_n \cdot n \cdot v_n + \gamma_p \cdot p \cdot v_p \qquad --- (3.7)$$

where  $\gamma_n$  and  $\gamma_p$  are electron and hole ionisation coefficients respectively.

The ionisation rate is given by

$$\gamma(\varepsilon) = \frac{q\varepsilon}{E_I} \exp \left[ -\frac{\varepsilon_I}{\left( 1 + \frac{\varepsilon}{\varepsilon_p} \right) + \varepsilon_{kl}} \right] \qquad --- (3.8)$$

where  $E_I$  is high field effective ionisation energy,  $\varepsilon_{kt}$ ,  $\varepsilon_p$  &  $\varepsilon_I$  are threshold fields for carriers to overcome the deceleration effects of thermal, optical phonon and ionisation scattering respectively. For Si the value of  $E_I$  is 3.6 eV for electrons and 5.0 eV for holes. The impact ionisation is temperature dependent.

### 3.2.3 Gate current generation

A small gate current is generated due to channel hot-carriers, either channel electrons or avalanch generated holes, that possess sufficient energy to surmount the Si-

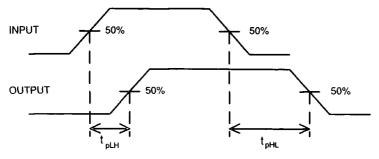

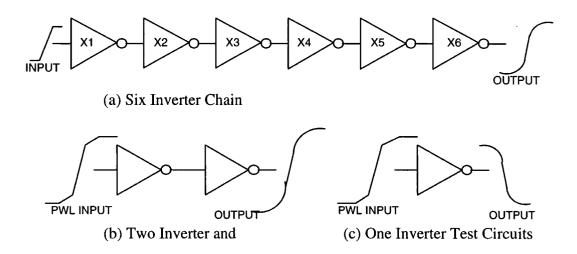

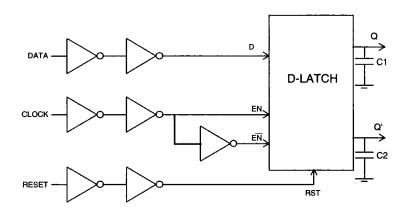

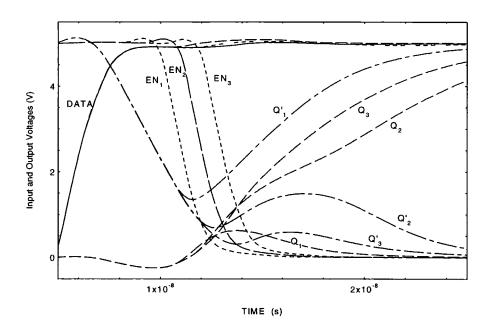

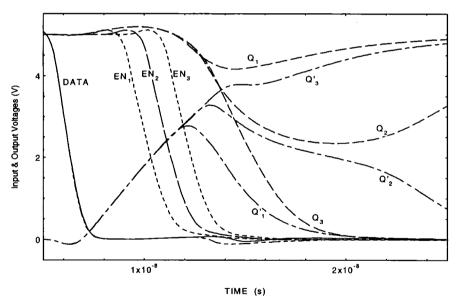

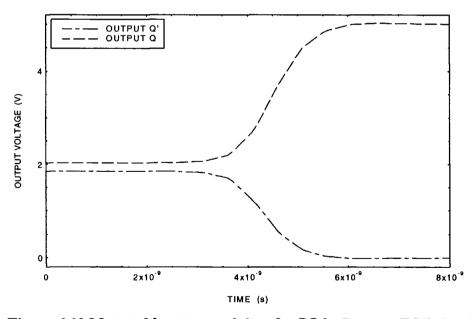

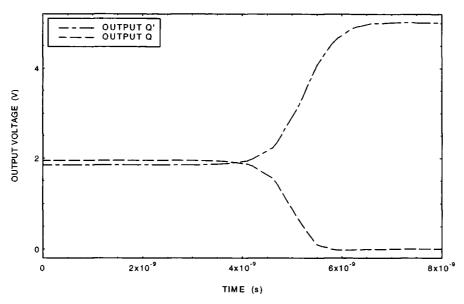

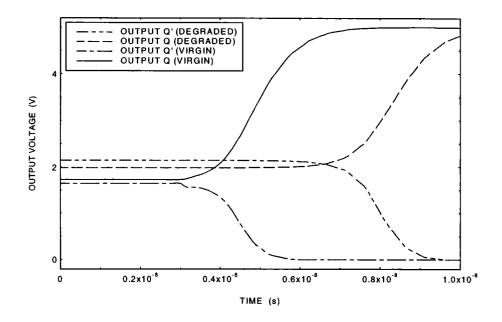

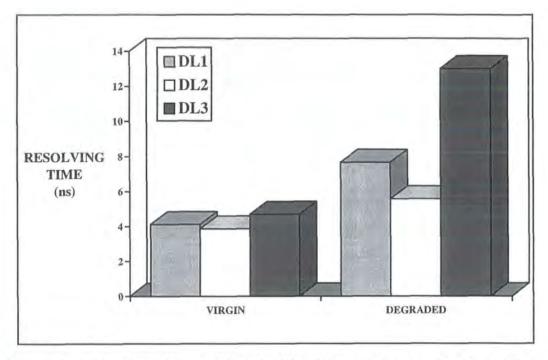

SiO<sub>2</sub> barrier [3.12]. The barriers for electrons and holes emitted to the gate are 3.1 eV and 4.1 eV, respectively. The two common models for gate current are the *lucky-electron model* [3.4] and the *electron-temperature model* [3.5]. In the lucky-electron model, the probability of an electron suffering a collision would determine the energy distribution of carriers generated. The *lucky-electrons* simply escape energy loss events and gains energy from the applied fields; while the electron-temperature model applies the theory of thermionic emission of *hot* electrons into the oxide from the channel if the electron temperature T<sub>e</sub> is not in equilibrium with the lattice. For the present technology devices, the gate current generated is insignificant and may not produce excessive leakage current. The gate current generation will not be considered in detail in this thesis and the reader is requested to refer any one of the many authors [3.6], [3.12] on this topic.