# **Durham E-Theses**

# $Algorithms \ and \ VLSI \ architectures \ for \ parametric \\ additive \ synthesis$

Spanier, Jonathan Robert

#### How to cite:

Spanier, Jonathan Robert (1999) Algorithms and VLSI architectures for parametric additive synthesis, Durham theses, Durham University. Available at Durham E-Theses Online: http://etheses.dur.ac.uk/4536/

#### Use policy

The full-text may be used and/or reproduced, and given to third parties in any format or medium, without prior permission or charge, for personal research or study, educational, or not-for-profit purposes provided that:

- a full bibliographic reference is made to the original source

- a link is made to the metadata record in Durham E-Theses

- the full-text is not changed in any way

The full-text must not be sold in any format or medium without the formal permission of the copyright holders.

Please consult the full Durham E-Theses policy for further details.

# THE UNIVERSITY OF DURHAM

SCHOOL OF ENGINEERING

# Algorithms and VLSI Architectures for Parametric Additive Synthesis

Jonathan Robert Spanier

19 JUL 2000

A THESIS SUBMITTED IN PARTIAL FUL-FILLMENT OF THE REQUIREMENTS OF THE COUNCIL OF THE UNIVERSITY OF DURHAM FOR THE DEGREE OF DOCTOR OF PHILOSO-PHY (PH.D.).

MAY 1999

The copyright of this thesis rests with the author. No quotation from it should be published without the written consent of the author and information derived from it should be acknowledged.

# Algorithms and VLSI Architectures for Parametric Additive Synthesis Jonathan Robert Spanier Ph.D. 1999

## Abstract

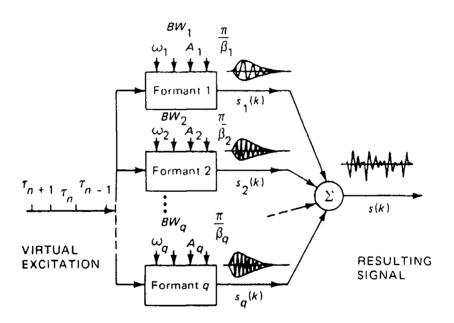

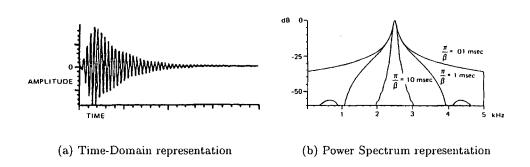

A parametric additive synthesis approach to sound synthesis is advantageous as it can model sounds in a large scale manner, unlike the classical sinusoidal additive based synthesis paradigms. It is known that a large body of naturally occurring sounds are resonant in character and thus fit the concept well. This thesis is concerned with the computational optimisation of a super class of formant synthesis which extends the sinusoidal parameters with a spread parameter known as bandwidth. Here a modified formant algorithm is introduced which can be traced back to work done at IRCAM, Paris.

When impulse driven, a filter based approach to modelling a formant limits the computational work-load. It is assumed that the filter's coefficients are fixed at initialisation, thus avoiding interpolation which can cause the filter to become chaotic. A filter which is more complex than a second order section is required.

Temporal resolution of an impulse generator is achieved by using a two stage polyphase decimator which drives many filterbanks. Each filterbank describes one formant and is composed of sub-elements which allow variation of the formant's parameters. A resource manager is discussed to overcome the possibility of all sub-banks operating in unison. All filterbanks for one voice are connected in series to the impulse generator and their outputs are summed and scaled accordingly.

An explorative study of number systems for DSP algorithms and their architectures is investigated. I invented a new theoretical mechanism for multi-level logic based DSP. Its aims are to reduce the number of transistors and to increase their functionality.

A review of synthesis algorithms and VLSI architectures are discussed in a case study between a filter based bit-serial and a CORDIC based sinusoidal generator. They are both of similar size, but the latter is always guaranteed to be stable.

# **Declaration**

I hereby declare that this thesis is a record of work undertaken by myself, that it has not been the subject of any previous appplication for a degree, and that all sources of information have been duly acknowledged.

Jonathan Robert Spanier, May 1999

Forathan Spane

## © Copyright 1999, Jonathan Robert Spanier

The copyright of this thesis rests with the author. No quotation from it should be published without the written consent of the copyright owner, and information derived from it should be acknowledged.

# Acknowledgments

I would like to take this opportunity to thank both my supervisors, Professor Alan Purvis and Dr. Simon Johnson for the encouragement and support they provided over the course of study.

The financial assistance provided by the University of Durham Studentship and the Royal Academy of Engineering International Travel Grant Scheme is gratefully acknowledged.

I would like to thank Mike Ellison of the University IT Computing Service for helping me to operate the Cadence Design Integration tools. My thanks go to members of the electronics workshop and to the departmental computing support; especially to Peter Friend, Ian Hutchinson, Peter Baxendale and Trevor Nancarrow for their advice and assistance in electronic and computing problems. Special thanks go to Matthew Jubb and John Glover for enlightening me in the joys of UNIX system administration and running Linux.

I am indebted to my fellow postgraduates, especially to Steve Robinson, Martin Bradley and the rest of the Telecoms Networks Research Group. I would like to thank my colleagues in the Digital and Optical Signal Processing Group and the VLSI Research Group for the informative discussions we had over the three years. I would like to acknowledge the LATEX community for providing such a useful and worthwhile typesetting package.

Special thanks also go to Austin Cassidy, Dr. Roger Woods and Dr. Saeed Vaseghi of The Queen's University of Belfast for providing UNIX support, portable computers and for all their encouragement.

Finally I would like to thank my parents for providing steadfast support throughout all my endeavours and to give special thanks to my mother, who tirelessly proof read this thesis despite not understanding any of the technical aspects.

# Contents

| Li | st of | Figure | es                                         | v    |

|----|-------|--------|--------------------------------------------|------|

| Li | st of | Tables | 3                                          | vii  |

| Li | st of | Abbre  | eviations                                  | viii |

| 1  | Bac   | kgrour | nd and Structure                           | 1    |

|    | 1.1   | Introd | uction                                     | 1    |

|    | 1.2   | Aims o | of this Thesis                             | 2    |

|    | 1.3   | Summ   | ary of Thesis                              | 3    |

| 2  | Intr  | oducti | ion to Synthesis methods                   | 5    |

|    | 2.1   | Subtra | active Synthesis                           | 6    |

|    |       | 2.1.1  | The Digital Controlled Oscillator          | 7    |

|    |       | 2.1.2  | The Digital Controlled Amplifier           | 10   |

|    |       | 2.1.3  | The Digital Controlled Filter              | 11   |

|    | 2.2   | Additi | ive Synthesis                              | 12   |

|    |       | 2.2.1  | Time-Multiplexed Wavetable Oscillators     | 13   |

|    |       | 2.2.2  | Inverse FFT-based Oscillators              | 14   |

|    |       | 2.2.3  | Multirate Additive Oscillators             | 14   |

|    | 2.3   | Freque | ency Modulation                            | 15   |

|    | 2.4   | Data l | Reduction for Synthesis                    | 16   |

|    | 2.5   | Waveg  | guide Modelling                            | 17   |

|    | 2.6   | Speech | h Modelling                                | 18   |

|    |       | 2.6.1  | Time-Domain Modelling                      | 18   |

|    |       | 2.6.2  | Spectral Modelling                         | 19   |

|    |       |        | 2.6.2.1 VOSIM                              | 20   |

|    |       |        | 2.6.2.2 Parallel/Cascade Formant Synthesis | 21   |

|    |       |        | 2.6.2.3 Forme d'Onde Formantique           | 24   |

|    | 2.7   | Summ   | nary                                       | 25   |

| 3 | Number Systems for VLSI Processing Elements |         |                                                               | 27 |

|---|---------------------------------------------|---------|---------------------------------------------------------------|----|

|   | 3.1                                         | Introd  | uction to Number Systems                                      | 27 |

|   | 3.2                                         | Conve   | ntional Radix Number System                                   | 30 |

|   |                                             | 3.2.1   | Weighted Number Systems                                       | 30 |

|   |                                             | 3.2.2   | Sign-Magnitude Representation                                 | 31 |

|   |                                             | 3.2.3   | Diminished-Radix Complement Representation                    | 31 |

|   |                                             | 3.2.4   | Radix Complement Representation                               | 32 |

|   |                                             | 3.2.5   | Properties of Sign-Magnitude, r-1's and r's Complement        |    |

|   |                                             |         | Numbers                                                       | 32 |

|   | 3.3                                         | The S   | igned-Digit Number System                                     | 33 |

|   |                                             | 3.3.1   | Definition of Signed-Digit Numbers                            | 33 |

|   |                                             | 3.3.2   | Conversion Between The Conventional Radix-r Number and        |    |

|   |                                             |         | its SD Form                                                   | 34 |

|   |                                             |         | 3.3.2.1 Conversion from Conventional to SD Systems            | 34 |

|   |                                             |         | 3.3.2.2 Conversion from SD to Conventional Systems            | 35 |

|   | 3.4                                         | The R   | esidue Number System                                          | 35 |

|   |                                             | 3.4.1   | The Multiplicative Inverse                                    | 36 |

|   |                                             |         | 3.4.1.1 Euler's Formula                                       | 37 |

|   |                                             | 3.4.2   | Residue to Decimal Conversion                                 | 37 |

|   |                                             |         | 3.4.2.1 Mixed-Radix Method                                    | 37 |

|   |                                             |         | 3.4.2.2 Chinese Remainder Theorem                             | 38 |

|   |                                             | 3.4.3   | The Quadratic Residue Number System                           | 38 |

|   |                                             |         | 3.4.3.1 Conversion To Complex Quadratic Residue Number        |    |

|   |                                             |         | System                                                        | 38 |

|   |                                             |         | 3.4.3.2 Conversion Back To Conventional Number System .       | 39 |

|   | 3.5                                         | Additi  | ion Elements                                                  | 40 |

|   |                                             | 3.5.1   | Conventional Binary Addition and Subtraction                  | 40 |

|   |                                             | 3.5.2   | Signed Digit Addition and Subtraction                         | 41 |

|   |                                             |         | 3.5.2.1 The Algorithm.                                        | 41 |

|   | 3.6                                         | Array   | Multiplication Techniques                                     | 44 |

|   |                                             | 3.6.1   | Cellular Array Multipliers Conclusions                        | 46 |

|   | 3.7                                         | Canon   | nical Multiplier Recoding                                     | 47 |

|   |                                             | 3.7.1   | Introduction to Multiplication String Recoding Algorithms .   | 47 |

|   |                                             | 3.7.2   | Canonical Signed-Digit Multiplier Recoding                    | 48 |

|   |                                             | 3.7.3   | Canonical Recoding Algorithm                                  | 48 |

|   |                                             | 3.7.4   | The Booth's Multiplier Algorithm                              | 49 |

|   |                                             | 3.7.5   | Efficiency of Multiplier Algorithms and Design Alternatives . | 50 |

|   | 3.8                                         | Summ    | nary                                                          | 51 |

| 4 | VL                                          | SI Tecl | hnologies and Applications                                    | 53 |

|   | 4.1                                         | Novel   | VLSI Technologies                                             | 54 |

|   | 4.2                                         | Curre   | nt-Mode Logic                                                 | 55 |

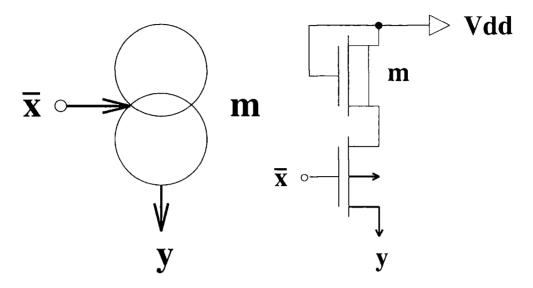

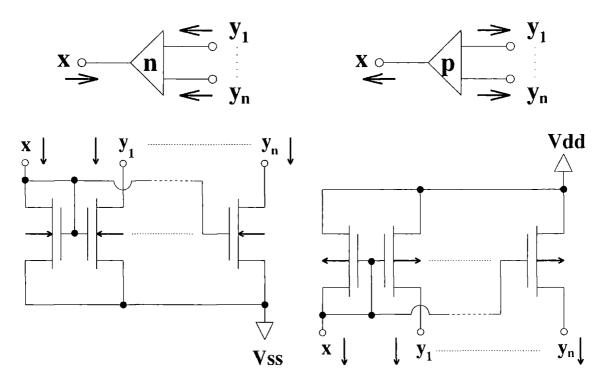

|   |                                             | 4.2.1   | Current Source                                                | 56 |

|   |                                             | 4.2.2   | Current Mirror                                                | 57 |

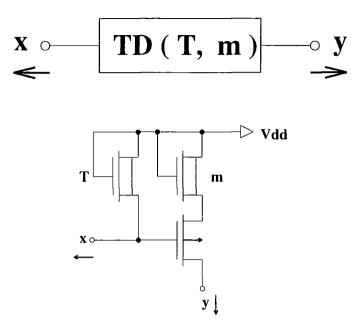

|   |                                             | 4.2.3   | Threshold Detector                                            | 58 |

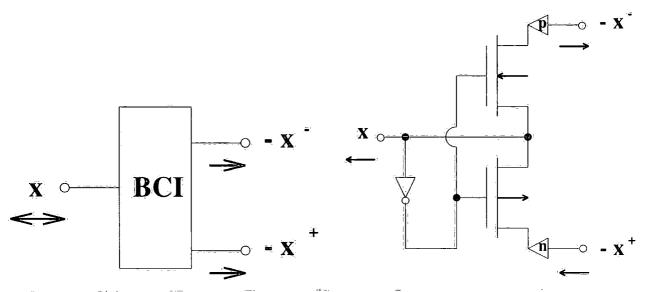

|   |                                             | 4.2.4   | Bidirectional current input circuit                           | 58 |

|   |                                             |         |                                                               |    |

|   |     | 4.2.5   | Module VLSI Scaling                                    |      |    | 60        |

|---|-----|---------|--------------------------------------------------------|------|----|-----------|

|   | 4.3 | Negati  | ve Differential Resistance                             |      |    | 60        |

|   | 4.4 | Voltage | e-Mode Multiple-Valued Logic                           |      |    | 62        |

|   |     | 4.4.1   | Operational Amplifier Approach                         |      |    | 62        |

|   |     | 4.4.2   | Neuron MOSFET Approach                                 |      |    | 62        |

|   | 4.5 | DAD I   | Logic                                                  |      |    | 63        |

|   |     | 4.5.1   | Mathematical Theory behind DAD Logic                   |      |    | 66        |

|   |     | 4.5.2   | Harmonic Oscillator                                    |      |    | 67        |

|   |     | 4.5.3   | Bipolar Level System                                   |      |    | 68        |

|   |     | 4.5.4   | Value Determination through Approximation              |      |    | 70        |

|   |     |         | 4.5.4.1 Analogue Eigenvalue Methods                    |      |    | 70        |

|   |     |         | 4.5.4.2 The Shooting Method                            |      |    | 71        |

|   |     |         | 4.5.4.3 The Pruess Method                              |      |    | 74        |

|   |     |         | 4.5.4.4 Important Issues regarding Eigenvalue Determin | nati | on | 77        |

|   | 4.6 | Summ    | ary                                                    |      |    | 77        |

|   |     |         | ·                                                      |      |    |           |

| 5 |     | -       | irements for synthesis                                 |      |    | <b>79</b> |

|   | 5.1 |         | Systems Design                                         |      |    | 79<br>~~  |

|   |     | 5.1.1   | Multiplier Constraints                                 |      |    | 79        |

|   |     | 5.1.2   | MAC Constraints                                        |      |    | 80        |

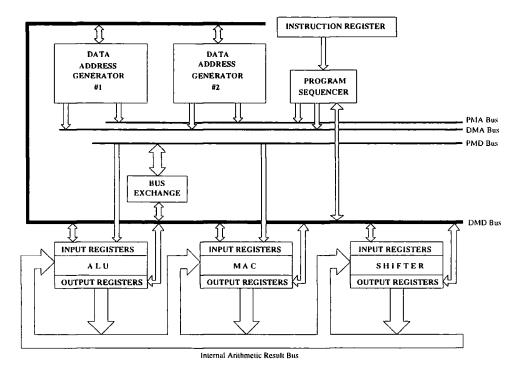

|   |     | 5.1.3   | ALU Constraints                                        |      |    | 81        |

|   |     | 5.1.4   | Data Address Generator                                 |      |    | 81        |

|   |     | 5.1.5   | Program Sequencer                                      |      |    | 81        |

|   |     | 5.1.6   | Memory                                                 |      |    | 82        |

|   |     | 5.1.7   | Architecture Summary                                   |      |    | 82        |

|   | 5.2 | -       | ath length criteria                                    |      |    | 83        |

|   |     | 5.2.1   | Overflow and underflow reduction                       |      |    | 83        |

|   |     | 5.2.2   | Truncation, Rounding and Unbiased Rounding             |      |    | 84        |

|   |     | 5.2.3   | Saturation Arithmetic                                  |      |    | 85        |

|   |     | 5.2.4   | Other noise problems                                   |      |    | 85        |

|   | 5.3 |         | based Sine Generator                                   |      |    | 86        |

|   |     | 5.3.1   | Filter Structure                                       |      |    | 87        |

|   |     | 5.3.2   | Multiplier Design                                      |      | •  | 88        |

|   |     | 5.3.3   | Accumulator Design                                     |      |    | 90        |

|   |     | 5.3.4   | Filter Design                                          |      |    | 90        |

|   | 5.4 |         | CORDIC Sine Generator                                  |      |    | 91        |

|   |     | 5.4.1   | Derivation for Circular Mode                           |      |    | 91        |

|   |     | 5.4.2   | The CORDIC Algorithm                                   |      |    | 92        |

|   |     | 5.4.3   | CORDIC Sine Algorithm                                  |      |    | 94        |

|   |     | 5.4.4   | Design of the CORDIC sine Generator                    |      |    | 95        |

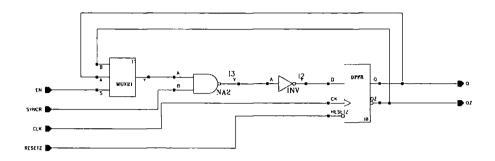

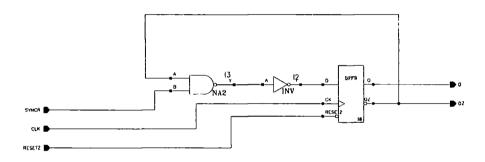

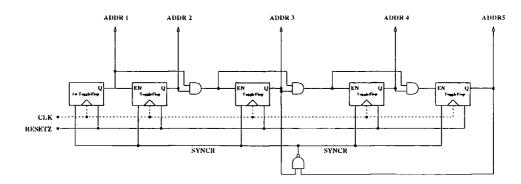

|   |     | 5.4.5   | Sequencer Design                                       |      |    | 98        |

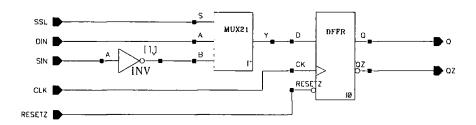

|   |     | 5.4.6   | ROM Design                                             |      |    | 100       |

|   |     | 5.4.7   | CORDIC register Design                                 |      |    | 102       |

|   |     | 5.4.8   | Adder Design                                           |      |    | 103       |

|   |     | 5.4.9   | Construction and Testing                               |      |    | 103       |

|   | 5.5 | Comp    | parisons between Sinusoidal Generators                 |      |    | 108       |

| 6 |      | aying Sinusoidal Additive Synthesis                                | 110 |

|---|------|--------------------------------------------------------------------|-----|

|   | 6.1  | Analysis of a Second Order Filter Structure                        | 111 |

|   | 6.2  | Analysis of the FOF technique                                      |     |

|   |      | 6.2.1 Implementation Approaches to the FOF wavefunction            |     |

|   |      | · •                                                                | 115 |

|   |      | 6.2.3 Filter Based FOF Synthesis                                   | 117 |

|   |      | 6.2.4 Full Hanning Window FOF envelope                             | 120 |

|   |      | 6.2.5 FOF filter structure with oscillation                        | 122 |

|   |      | 6.2.6 Miscellaneous Wavefunction Designs                           | 124 |

|   | 6.3  | Approaches to formant synthesis                                    | 125 |

| 7 | Para | ametric Additive Synthesis Implementation                          | 127 |

|   | 7.1  | Optimisation of the filter $t^2e^{-\alpha t}\sin(\omega_0 t)$      | 128 |

|   |      | 7.1.1 Analysis of the Transversal Element of the Filter Topology . | 128 |

|   |      | 7.1.2 Transversal Filter Structure                                 | 129 |

|   |      | 7.1.3 IIR Filter Structure                                         | 130 |

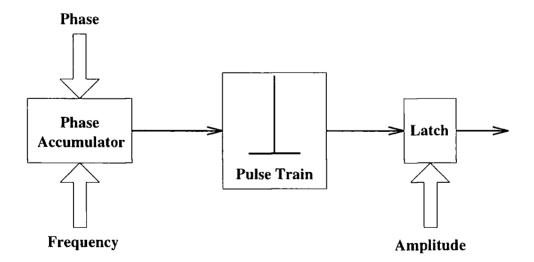

|   | 7.2  | Source Excitation Driver                                           | 131 |

|   |      | 7.2.1 Discrete Summation Formulas for Impulse Generation           | 133 |

|   |      | 7.2.2 Impulse generation using Decimation                          | 134 |

|   |      | 7.2.2.1 The Decimator Structure                                    | 134 |

|   |      | 7.2.2.2 Decimator Design                                           | 135 |

|   |      | 7.2.2.3 Reduced Coefficient Storage Design                         | 137 |

|   | 7.3  | Synthesiser Structure                                              | 138 |

|   | 1.0  | 7.3.1 The importance of Phase in Audio                             |     |

|   |      | 7.3.2 Parallel Formant Model                                       | 139 |

|   |      |                                                                    |     |

| 8 | Alge | orithm Scheduling and Miscellaneous Topics                         | 143 |

|   | 8.1  | Algorithm Scheduling                                               | 143 |

|   |      | 8.1.1 Controller Algorithm Overview                                | 144 |

|   |      | 8.1.2 Filterbank Scheduler Controller                              | 145 |

|   |      | 8.1.3 Number of Filters required                                   | 146 |

|   | 8.2  | Miscellaneous Topics                                               | 147 |

|   |      | 8.2.1 Envelope Generation                                          | 147 |

|   |      | 8.2.2 Subtractive Synthesis Extensions                             | 148 |

|   |      | 8.2.3 Synthesis by Rule                                            | 149 |

|   | 8.3  | User Interface Design                                              | 150 |

|   | 8.4  | Hardware/Software Segmentation                                     | 151 |

| 9 | Con  | clusions and Further Work                                          | 153 |

|   | 9.1  | Conclusions                                                        | 153 |

|   | 9.2  | Further Work                                                       | 156 |

| A | The  | Laplace to Z Transform Algorithm                                   | 158 |

# List of Figures

| 2.1 | Simplified Subtractive Voice Architecture                            |

|-----|----------------------------------------------------------------------|

| 2.2 | Block Diagram of a Wavetable Oscillator                              |

| 2.3 | Second Order Digital Filter                                          |

| 2.4 | LPC Synthesiser                                                      |

| 2.5 | Typical VOSIM waveform                                               |

| 2.6 | Block Diagram of Serial-parallel formant synthesiser                 |

| 2.7 | FOF synthesiser topology                                             |

| 2.8 | Properties of the FOF wavefunction                                   |

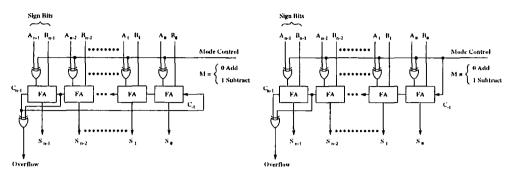

| 3.1 | Block Diagrams of ripple carry adders for conventional binary arith- |

|     | metic                                                                |

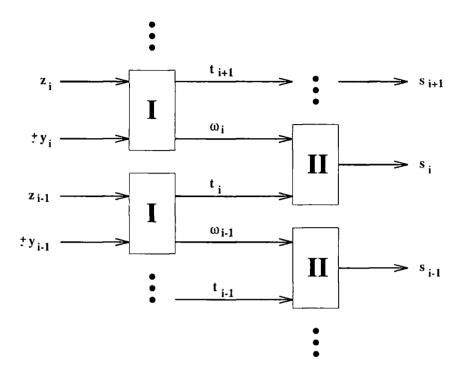

| 3.2 | Block Diagram of Part of the SD adder/subtractor                     |

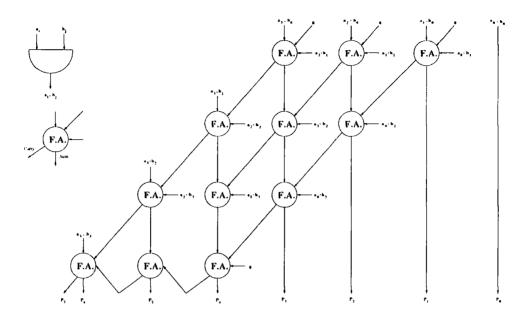

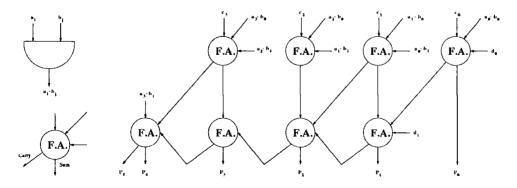

| 3.3 | The Structure of a 4x4 NMM                                           |

| 3.4 | The Structure of a 4x2 AMM                                           |

| 4.1 | Current Source Circuit Symbol and Schematic                          |

| 4.2 | Current Mirror Circuit Symbols and Schematics                        |

| 4.3 | Threshold Detector Circuit Symbol and Schematic                      |

| 4.4 | Bidirectional Current Input Circuit Symbol and Schematic 59          |

| 4.5 | Bidirectional Current Input I-V characteristics                      |

| 4.6 | Block Diagrams of Negative differential Resistance 61                |

| 4.7 | Schematic representation of a neuron MOS transistor                  |

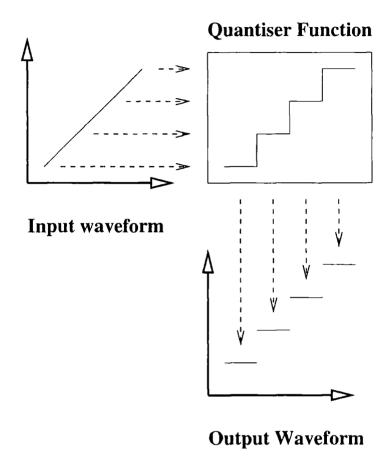

| 4.8 | Functional Diagram of DAD Logic Quantiser Operation 65               |

| 4.9 | Stationary state solutions for the Harmonic Oscillator Potential 68  |

| 5.1 | A Simplified Structure of a DSP Processor                            |

| 5.2 | Block Diagram of the IIR Sinusoidal Generator                        |

| 5.3 | Schematic Diagram of the 5 level Booth Multiplier Module 89          |

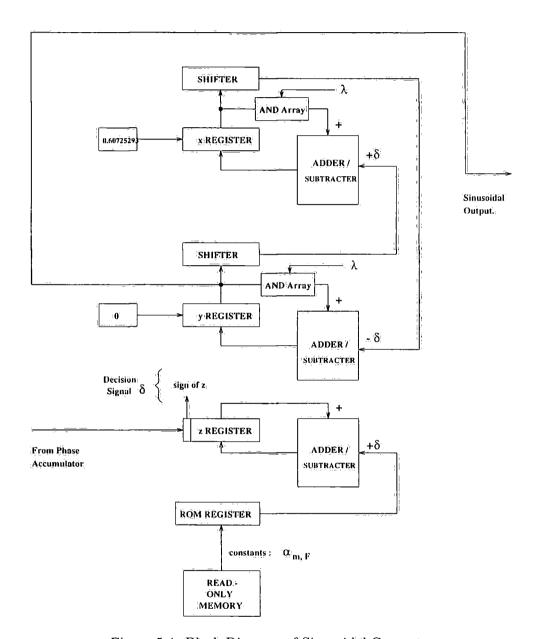

| 5.4 | Block Diagram of Sinusoidal Generator                                |

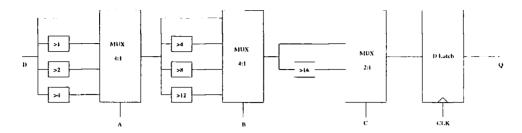

| 5.5 | Block Diagram of the Barrel Shifter                                  |

| 5.6 | Schematic Diagram of a T flip-flop                                   |

| 5.7 | Schematic Diagram of first T flip-flop for mod counting 99           |

| 5.8 | Schematic Diagram of a modulo 21 counter                             |

| 5.9  | Schematic Diagram of a Synchronous Reset Flip-Flop                                    | 103  |

|------|---------------------------------------------------------------------------------------|------|

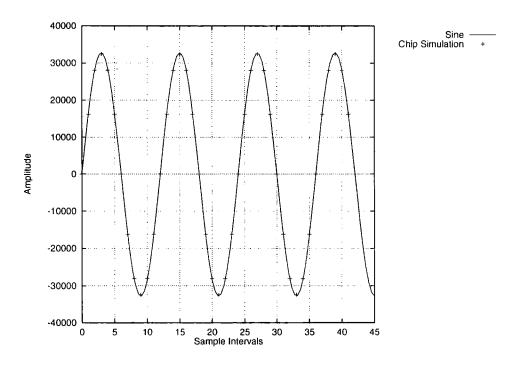

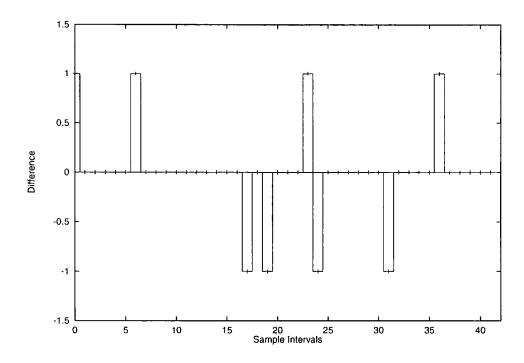

| 5.10 | Comparison between Sine Function and CORDIC Simulation                                | 105  |

| 5.11 | Error Difference between Sine Function and CORDIC Simulation                          | 106  |

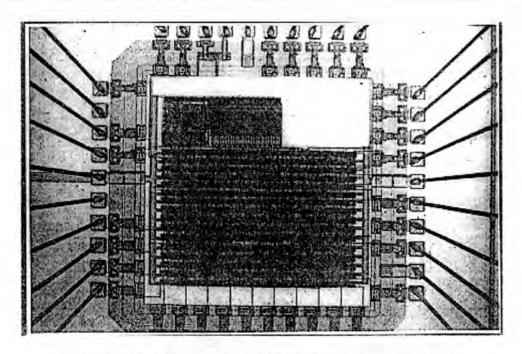

| 5.12 | Photomicrograph of the CORDIC Cosine Chip                                             | 108  |

| 6.1  | The FOF Wavefunction                                                                  | 112  |

| 6.2  | Power Spectrum of the FOF Wavefunction                                                | 114  |

| 6.3  | Simplified CSOUND FOF Implementation                                                  | 116  |

| 6.4  | Time domain behaviour of FOF envelope generator                                       | 118  |

| 6.5  | Zero-Pole plot of the FOF envelope generator                                          | 119  |

| 6.6  | Heterodyned version of the FOF Algorithm                                              | 120  |

| 6.7  | Time domain and z-plane responses to Full Hanning FOF                                 | 121  |

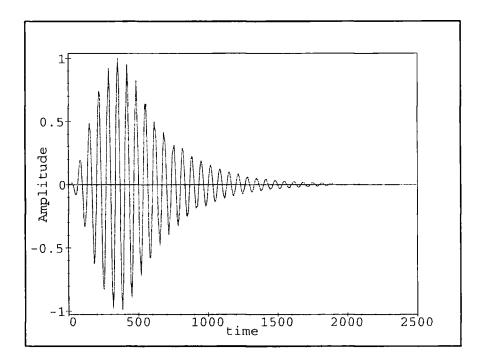

| 6.8  | Time Domain response of the $t^2e^{-\alpha t}\sin(\omega_0 t)$ wavefunction           | 123  |

| 6.9  | z-plane response to $t^2e^{-\alpha t}\sin(\omega_0 t)$ wavefunction                   | 123  |

| 6.10 | Magnitude and Phase Spectra for the $t^2e^{-\alpha t}\sin(\omega_0 t)$ wavefunction . | 124  |

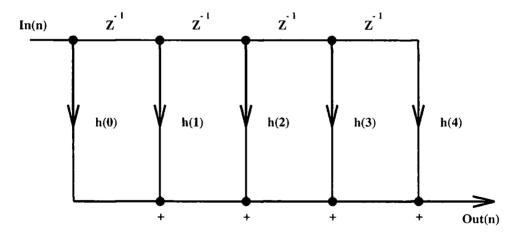

| 7.1  | Flowgraph of Direct Form FIR Filter Structure                                         | 129  |

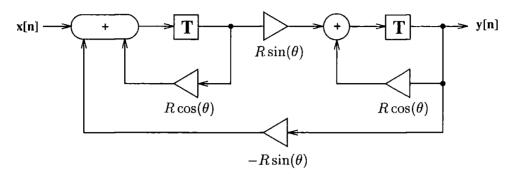

| 7.2  | Second Order Coupled IIR filter Form                                                  | 131  |

| 7.3  | Simple Impulse Generator Schematic                                                    | 131  |

| 7.4  | Amplitude vs Frequency for the sinc function                                          | 132  |

| 7.5  | Reduced Dynamic Memory Storage Polyphase Filter                                       | 136  |

| 7.6  | Block Diagram of $t^2 e^{-\alpha t} \sin(\omega t)$ based formant synthesiser         | 140  |

| 8.1  | Block Diagram of the controller for idle/running status                               | 145  |

| 8.2  | Block Diagram of Resource Filter Allocation                                           | 146  |

| Q 2  | Schamatic of a Ripolar Envelope Caparator                                             | 1/10 |

# List of Tables

| 3.1 | Multiples of the multiplicand to be added after scanning a triplet of multiplier bits in an overlapped pairwise scanning system | 48  |

|-----|---------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.2 | The Booth Multiplier Radix-2 String Recoding Algorithm                                                                          | 4   |

| 5.1 | Input-Output Functions for CORDIC Modes                                                                                         | 9:  |

| 5.2 | CORDIC Sine Chip Input-Output Connections                                                                                       | 100 |

| 5.3 | Current Consumption of CORDIC Sine Chip                                                                                         | 107 |

| 6.1 | Comparisons between Formant Filter Topologies                                                                                   | 120 |

| 8.1 | Decision Table for Bipolar Envelope Ramp Generator                                                                              | 148 |

# List of Abbreviations

| ADSR                 | Attack Decay Sustain Release                        |

|----------------------|-----------------------------------------------------|

| AES                  | Audio Engineering Society                           |

| ALU                  | Arithmetic Logic Unit                               |

| AM                   | Amplitude Modulation                                |

| ASIC                 | Application Specific Integrated<br>Circuit          |

| CCRMA                | Center for Computer Research in Music and Acoustics |

| CMOS                 | Complementary Metal-Oxide<br>Silicon                |

| CORDIC               | COrdinate Rotation DIgital<br>Computer              |

| DAC                  | Digital Analogue Converter                          |

| DCA                  | Digital Controlled Amplifier                        |

| DCF                  | Digital Controlled Filter                           |

| DCO                  | Digital Controlled Oscillator                       |

| DFT                  | Discrete Fourier Transform                          |

| DIL                  | Dual In Line                                        |

| DSP                  | Digital Signal Processor                            |

| ES2                  | European Silicon Structures                         |

| $\operatorname{FFT}$ | Fast Fourier Transform                              |

| FIFO   | First In First Out                                            |

|--------|---------------------------------------------------------------|

| FIR    | Finite Impulse Response                                       |

| FM     | Frequency Modulation                                          |

| FOF    | Forme d'Onde Formantique                                      |

| FPGA   | Field Programmable Gate Array                                 |

| HP     | Hewlett Packard                                               |

| IEEE   | The Institite of Electrical and Electronic Engineers          |

| IIR    | Infinite Impulse Response                                     |

| IMEC   | Inter-Universitair Micro-Elektronica<br>Centrum               |

| IRCAM  | Institut de Recherche et Co-<br>ordination Acoustique/Musique |

| LPC    | Linear Predictive Coding                                      |

| MAC    | Multiply-Accumulate unit                                      |

| MIDI   | Musical Instruments Digital Interface                         |

| MOSFET | Metal-Oxide Silicon Field Effect Transistor                   |

| MVL    | Multiple-Valued Logic                                         |

| NDR    | Negative Differential Resistance                              |

| RNS    | Residue Number System                                         |

| ROM    | Read Only Memory                                              |

| SD     | Signed Digit                                                  |

| SHARC  | Super Harvard ARchitecture<br>Computer                        |

| SQUID  | Superconducting QUantum Interference Device                   |

| STL    | Simulation and Test Language                                  |

TTLTransistor Transistor Logic

VHSIC Hardware Description Language VHDL

Very Large Scale Integration or Integrated circuits VLSI

VOcal SIMulation VOSIM

# CHAPTER 1

# Background and Structure

#### 1.1 Introduction

Since the dawn of time, mankind has used materials from the Earth to mould into instruments to hit, pluck, stroke or blow. Over the aeons, man has harnessed new developments in Science and Technology to transform or create new tones and new playing techniques. Initially, these came through material science, as in the tones created from different types of wood and varnish. Now, in the 20th century the ubiquitous silicon chip has taken the limelight.

Man uses VLSI technology either to make a facsimile of an instrument by modelling the instruments' properties or to create new ones which require new performance criteria to control them. Research into this field requires a multidisciplinary approach utilising the skills of musicians, physicists and computer scientists.

At the dawn of the millennium, musicians now have a plethora of different synthesis tools to generate unique sounds, but the commercialisation of these algorithms has been relegated to software implementation. Most manufactures have only implemented the easy algorithms, such as wavetable, subtractive and Frequency Modulation synthesis. They are becoming reluctant to spend any more man years and money on ASIC design, which will never repay their initial investment due to its small customer base. However, most manufactures have jumped onto the multimedia concept. This leaves musicians with a quandary on whether to buy similar hardware instruments or to go down the software extensibility route. The latter approach seems good value due to its upgradability, but this assumes that computational resources are fixed. In reality, algorithms consume valuable computation

thus slowing down the synthesis engine to near or below real time. It is difficult for musicians, who normally rely on their tactile and auditory responses, to respond in the same way to purely acoustically based sounds.

### 1.2 Aims of this Thesis

This thesis looks at the mapping of a parametric additive synthesis technique to a specialised hardware implementation, in order to discover an optimal implementable approach built around a recursive filter with the minimum number of arithmetic and storage operations. The parametric additive synthesis technique is simply a formant based model which reduces the number of parameters needed to model a sound, and is applicable because most instruments resonate. The alternative method would be a sinusoidal based additive synthesis which has an explosion of controllable parameters and would be difficult to implement.

The standard approach to digital CMOS design has been shown to be effective in reducing design times predominantly because digital is easier to work with than analogue. In this thesis, I explore different forms of digital structures by increasing the number of encodings per wire. To this end, current mode CMOS logic and negative differential resistance devices are discussed. My novel theoretical approach uses a constant number of transistors to generate many discrete levels. This is closer to the behaviour of negative differential devices and should consume less power.

A comparison between a bit-serial sinusoidal generator and a CORDIC parallel based sinusoidal generator is made, and they are found to be of comparable size. However, despite taking 21 clock cycles to generate a sinusoid, the CORDIC version is always stable. The IIR filter coefficients sets the frequency of oscillation and is sensitive to the pole quantisation of its transfer function. This form takes 25 clock cycles to perform one filter operation, with both adders and multipliers operating in parallel.

The standard FOF wavefunction approach is very greedy on memory and arithmetic resources. A filter based approach overcomes this problem. The filter structure chosen has 4 zeros in complex conjugate form on the real axis and 3 poles in complex conjugate pair form. This is radically different to any other FOF form.

Octaviation can be performed by using two phase accumulators plus an adder. This forms an idealised impulse generator running at a high sampling rate. The impulses are decimated to a lower sampling rate, using an optimal two stage decimator. Using polyphase filters and FIR symmetry, a novel coefficient storage reduction scheme is proposed.

The filters are controlled by an allocation system which utilises decrementing counters and a linked list scheduler. The need for synthesis rules, envelope generation, subtractive synthesis modules and intuitive user interface will all be highlighted.

# 1.3 Summary of Thesis

The structure of this thesis is as follows:

Chapter 2 presents a review of common audio synthesis techniques for music generation. It highlights the subtractive synthesis approach based on modular components progressing through to sinusoidal additive synthesis. The remainder of the chapter looks briefly at physical modelling and speech inspired synthesis techniques based on formant modelling.

Chapter 3 examines the multitude of approaches to number representation and the effect of these on numerical computation. Both of these are of paramount importance in VLSI DSP design and implementation as they enable designers to meet the performance criteria of the chosen algorithm. Conventional and redundant number representations are discussed and their merits in addition and multiplication are highlighted. Finally, array and Booth recoded multipliers are discussed.

Chapter 4 discusses different material structures for DSP, highlighting multivalued logic architectures using current mode logic and voltage-mode logic paradigms. Multivalued logic, based on negative differential resistance based devices, plus a new concept which I have invented, are also presented.

Chapter 5 expands on Chapter 3 and deals with hardware implementation requirements necessary for audio synthesis and discusses wordlength issues caused by addition and multiplication. These increases in wordlength can be minimised using truncation or rounding schemes. Problems caused by noise are also addressed. The rest of the chapter then applies this knowledge to a comparison of two sinusoidal oscillators implemented using either a bit-serial filter or a CORDIC based algorithm.

Chapter 6 examines a formant based synthesis technique by modelling the time-domain impulse response of a second order filter. This creates a damped sinusoid having no attack and the problem is overcome by looking at the FOF methodology. The method is then discussed in terms of implementational metrics. Implementation of this structure is then approximated by various filter topologies and some unusual waveform generators are highlighted.

Chapter 7 chooses from Chapter 6 one filter topology with an elegant structure and its implementation is discussed. The driver to this filter is designed and optimised.

Chapter 8 addresses scheduling of the filters and synthesis structures to enable easy use of the technique. Rules to enable realistic simulation of singing voices are discussed as are other approaches to enhance the sonic capabilities of the synthesis model. The chapter ends with details of how the algorithm would be partitioned between hardware and software.

Chapter 9 describes the conclusions reached in this work, and suggestions for further research in this topic are discussed.

Appendix A discusses the mathematical derivation of the Laplace to Z transform.

# CHAPTER 2

# Introduction to Synthesis methods

Audio synthesis techniques provide a valuable playground in which to explore the route from algorithm design to a full-custom VLSI architecture. This thesis will concentrate on the synthesis of musical tones. This field has benefited from the cross-fertilisation of ideas from engineers to musicians and evolved from original work at Bell Telephone Laboratories. The work at Bell Telephone Laboratories was originally in speech compression, but in the 1960's Max Mathews created the first digital software generating musical tones known as MUSIC IV [82, 114]. The first commercially available digital music synthesiser was introduced by Yamaha in the early eighties. This instrument was based on research by John Chowning [11] of Stanford University, which used the FM synthesis technique. Before the advent of the DX series of synthesisers by Yamaha, musicians were using analogue based subtractive synthesisers of Moog, ARP and others [137]. The digital approach provided repeatability of sounds because the technology was not dependent on temperature drifting of components as was found in the analogue systems. The FM algorithm also provided musicians with bright, clean sounding timbres that were unique. However, musicians now prefer the analogue systems because they provide warm sounding timbres caused by their imperfections. Musical instrument manufacturers began to explore newer techniques in order to give the musicians better control over the sounds.

All the early digital synthesisers relied upon custom VLSI architectures to provide

the computational power necessary to generate multiple voices in real-time and to make the instruments affordable. Nowadays, with new general purpose DSP chips designed for sustained computation, manufacturers choose the programmable (software) and hardware approach. We have gone full-circle, from off-line compiler based software synthesis to real-time synthesis engines like the new CSOUND, based around the Analog Devices floating point SHARC DSP chip [138]. Does this mean that a thesis on VLSI and synthesis algorithms is worthwhile? I think so because software based engines require hardware which can support the computations which must be computed within a sample interval and so require powerful new VLSI designs. The other approach is the full-custom ASIC design which has a payoff when the number of units sold is very large. However, the latter approach requires a longer gestation period. The ASIC approach is of value for sample-rate converters [2] and mobile phones. For the music market this approach is becoming less attractive. But optimising the algorithms will make software use the available hardware resources more effectively.

This chapter will review the current synthesis techniques available today and highlight their possible hardware configurations.

# 2.1 Subtractive Synthesis

In 1964 Robert Moog constructed a transistor-based analogue voltage controlled oscillator, and presented a paper on it at the sixteenth annual convention of the AES [82]. Over a period of rapid growth, engineers realised the need for other functions to emulate instruments and make new tones. New voltage controlled functions were provided in the form of Voltage Controlled Filters and Amplifiers. The subtractive synthesis technique uses filtering to change the harmonic structure of the input which is normally of a rich harmonic content, for example, the sawtooth waveform.

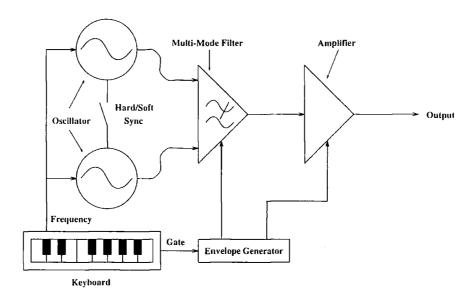

Figure 2.1: Simplified Subtractive Voice Architecture

An example of a typical single voice, dual oscillator subtractive synthesiser is shown in figure 2.1. The keyboard generates two control signals; the gate which is an on/off signal indicating the duration of the note and a signal proportional to the frequency of the note value. The gate signal drives the DCF and/or DCA via an envelope generator. The two oscillators (DCO) can either be controlled separately or chained together, thus providing a richer evolving sound. These oscillators in analogue synthesisers produce a range of waveforms, most notably, Sinusoidal, Triangular, Pulse and Sawtooth. In the digital equivalent, the musician has an infinite choice of waveform. Incidentally, modern day samplers are basically subtractive synthesisers with oscillators having user definable waveforms.

The next three sub sections will concentrate on digital hardware to implement the DCO, DCA and DCF modules in a subtractive synthesiser.

#### 2.1.1 The Digital Controlled Oscillator

There are many different ways of generating an oscillator; either filter based [31, 53] or by wavetable lookup. This sub-section will discuss the wavetable based approach to oscillator generation. Essentially, wavetable based oscillators are counters being incremented by a variable representing frequency of oscillation. The output from the counter is used as an address for a ROM containing a discrete-time version of the analogue waveform. The counter can be thought of as a periodic ramp waveform, hence each ramp count is transformed by *looking up* in a table. The contents of the table (ROM) can be any shape the musician likes, not simply a sinusoid. The only

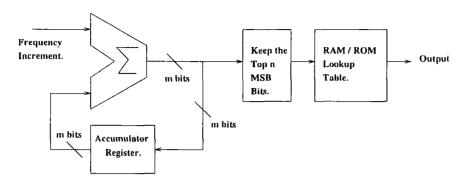

Figure 2.2: Block Diagram of a Wavetable Oscillator

proviso being that the waveform in ROM is single-cycled; so the counter provides the means of generating repetitive cycles of the waveform.

There are two types of wavetable lookup oscillators [10], one is the variable-rate form which drives the counter, ROM and the output conversion elements. This approach provides high-fidelity but is very expensive in terms of hardware. Due to the variable-rate nature, the approach cannot be multiplexed and is thus unsuitable for VLSI implementation. The other type is known as the fixed sample-rate oscillator which is also known as the phase-accumulator oscillator. A block diagram of this oscillator is shown in figure 2.2.

The phase-accumulator oscillator contains the phase angle increment and phase angle registers. The phase angle register holds the instantaneous phase of the waveform. Each clock interval, the phase angle contents are added by the phase angle increment and when the output of the adder overflows, the adder performs a modulo operation. This operation naturally occurs when the phase angle is greater than  $2^m-1$ , and m is the number of bits in the adder. The clock signal is generated via a crystal for stability. This technique requires interpolation when the sample falls between two storage locations. Failure to correct for this non-integer sample will manifest itself as audio distortion. In figure 2.2 we have a truncating oscillator, the m-n bits can be thought of a fractional part, used if necessary for interpolation. In silicon, interpolating oscillators increase the chip real-estate and hence requires thought to whether the expense is justified. However, this oscillator is suitable for VLSI implementation because the adder can be time-division multiplexed, providing many oscillators. Multiple registers are required, but in VLSI the adder consumes more space. By providing a system clock which is k times the sampling rate and logic which can operate at this speed, k oscillators can be generated at the sample rate.

The frequency of the waveform, f given the phase angle increment, I is

$$f = f_s \frac{I}{L}$$

where  $f_s$  is the sampling rate and L is the table length. What is now required is the number of bits in the adder to provide sufficient resolution for musical applications. Using the method as presented in Snell's paper [127] the size of the adder is given by equation 2.1

$$b = 1 + 3.32 \log_{10} \left( \frac{F_{\text{max}}}{F_{\text{min}}} + 1 \right) \tag{2.1}$$

Where  $F_{\rm max}$  is the maximum desirable frequency of any sinusoidal component and  $F_{\rm min}$  is the minimum step or change in frequency. Due to work done by many scientists the values for these parameters are 20 kHz and 0.03 Hz respectively. Substituting into equation 2.1 gives an adder word length of 21 bits. This is the minimum required resolution necessary for musical purposes. If  $F_{\rm max}$  is a power of two, then the true frequency of the oscillator can be read directly from the phase angle increment without using any extra hardware/software, providing a direct human readable value.

An expression which relates b to the minimum interval the oscillator can be tuned to, requires knowledge of the non-linear equally tempered musical scale. The minimum interval is normally expressed in cents and a cent is 1/1200 of an octave. One octave is a doubling/halving by a factor of two. The minimum interval (or tuning accuracy) about a particular note frequency F is given below.

$$C_{\min} = 3986.31 \log_{10} \left( \frac{F_{\max}}{F(2^{b-1} - 1)} + 1 \right)$$

(2.2)

It can be shown that various values for F,  $F_{\text{max}}$  and b give non-linear values for  $C_{\min}$  by using equation 2.2. Therefore to achieve adequate resolution across the entire audio spectrum, the designer must choose a value for b which provides better than 1 cent tuning resolution at the *lowest* frequency the oscillator will run at.

As mentioned earlier, this type of wavetable lookup generates distortion if the sample value in the phase accumulator is not integer, i.e. a non zero fractional part. Thus the correct sample required is in between two memory locations. What is required is a mathematical expression that predicts the noise as a function of the size of table. An empirical result was discovered by Moore [94] and the Signal-to-Noise ratio was found to be 6(k-2) dB for a truncating oscillator and 6(k-1) dB for rounded (to nearest integer) oscillators. The k and k+1 being the bits of precision in the oscillator (not including the sign bit) for each result respectively. It is also assumed

that the table has  $2^k$  entries. So, if we do not want interpolated wavetables, the designer must choose a larger wavetable to reduce the noise generated by the lookup process. Moore also found that for sinusoidal interpolation there needs to be 2(k-1) bits of precision (excluding the sign bit) in a table of  $2^k$  entries to provide a SNR of 6l dB. The interpolation formulae for sinusoidal interpolation can be as follows: take I, the integer part and f, the fractional part of the phase angle respectively.

$$sin(I + f) = sintable[I] + f(sintable[I + 1] - sintable[I])$$

An alternative form using the approximation  $\sin(x) \approx x$  for small x expressed in radians is

$$sin(I + f) \approx sintable[I] + f costable[I]$$

So far, the analysis has not taken into account the simplifications that can be made for symmetrical waveforms like sinusoids. Since a sine function is symmetrical about 180° and the first quarter cycle is symmetrical about 90° storage space can be reduced by a factor of 4. The savings in memory as the table length increases make this approach very attractive.

For the 180° approach, the designer will implement half the table size and the sign bit would control a two's complement inverter, to convert the positive table value to its negative. The designer would normally need to add one to this result to actually implement two's complement, but this can be assumed to be negligible.

In the 90° reduced table method, the most significant two bits are used to decide on whether to complement and/or scan the table. The most significant is the sign bit as usual. The next bit determines the negation of the address for the table and thus performs backward scanning. The remaining bits are the address for the ROM table lookup. If the penultimate most significant bit is non-zero, this will alter the address bits to the ROM by two's complementing them. However if the address bits are zero at the same time as this control bit is active (1), the phase angle is either 90° or 270° exactly and the complement would give an incorrect address for zero. This special case is overcome by substituting the maximum address instead, and is accomplished by oring the carry bit of the two's complementer with the address bits.

# 2.1.2 The Digital Controlled Amplifier

The DCA is nothing more than a multiplier. However, for the VLSI designer, the choice becomes tricky because the larger the wordlength the more area is used (in

parallel multiplier circuits). The observant reader might wonder if a floating point multiply would be beneficial. Unfortunately, for commercial uses, a multiplier of this type is excessively expensive in terms of design time and floor space. It is worth noting that floating point multipliers actually truncate the mantissa part, just like integer based multipliers, primarily to reduce the number of bits to wire. This can be shown clearly by the following analysis. Say, the musician wants to multiply a 16 bit number by an 8 bit amplitude envelope, the multiplier would need to have 16 + 8 = 24 bits output. However, if this multiplier is going to be used again, the designer would need to provide sufficient headroom, otherwise saturation and an incorrect answer will result.

# 2.1.3 The Digital Controlled Filter

The DCF provides gross modification of the harmonic structure of the input by either boosting or attenuating user specifiable frequencies. This module is the most expensive to implement in silicon because filtering in the discrete-time domain requires numerical operations and storage elements operating at the sample rate. In analogue synthesisers, the filter is relatively simple to implement because the arithmetic calculations are implemented directly using active and passive electronic components [139]. In the digital domain, the designer must choose on the arithmetic format for the computations and then construct the operators accordingly.

There are many different types of digital filters, where their topologies influence ease of implementation and accuracy. In this introductory chapter the second order state variable digital filter will be used as a case study.

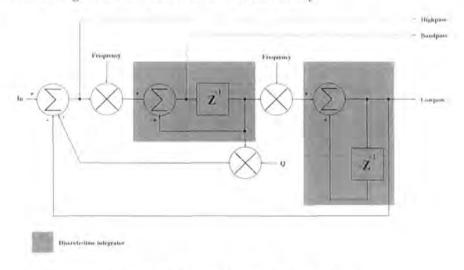

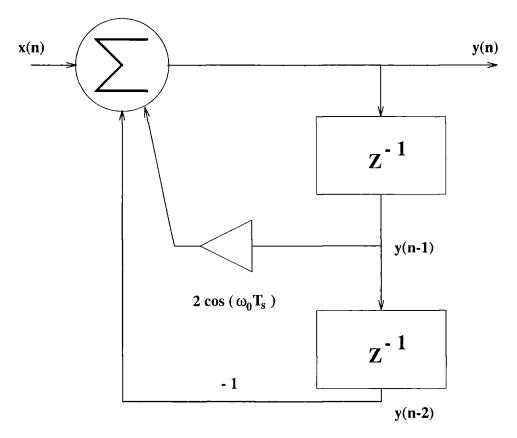

Figure 2.3: Second Order Digital Filter

As shown in figure 2.3 the digital filter is quite complicated as it has addition, multiplication and delay  $(z^{-1})$  elements. This filter is composed of three elements; a mixer/adder and two integrators in cascade. This filter has a -12 dB/octave roll-off in each of the output modes (lowpass, highpass and bandpass). The frequency parameter is defined as  $2\sin(\frac{\pi F}{f_s})$  and the Q (Quality factor) or bandwidth parameter is bw/f, where bw is the bandwidth and f is the desired frequency cut-off for the high and lowpass modes of the filter. This filter topology has the main advantage that the two variables, frequency and Q are independent. Note that the Q factor in the diagram is actually the reciprocal of the real Q factor.

As mentioned earlier in section 2.1.1 it is possible to implement an oscillator using filters. To implement a decaying oscillator, the first frequency parameter is multiplied by -1 and the first adder is modified to have no input and the other inputs are transformed into add operators. To implement a sinusoidal oscillator, the user sets infinite Q; hence the Q parameter, as shown in the diagram, becomes zero. A final note, for constant ring time oscillation, set Q to zero, set zero input and replace the feedback connection of the first integrator by a factor being  $-\exp(\frac{1}{F_sD})$  and D is the time taken for the oscillation to decay to 37% of its value  $^1$ .

In chapter 5 the complexities of digital filter implementations will be discussed in terms of the addition, multiplication and delay VLSI primitives. There are two main approaches to implementing these filters in ASICs; either by using bit-serial or bit-parallel techniques. The latter uses more floor space and therefore is more expensive to manufacture.

# 2.2 Additive Synthesis

Additive synthesis is a technique whereby complex waveforms can be decomposed into simpler waveforms (normally sinusoidal) and regenerated by adding the components together. Any waveform can be decomposed into a sum of simpler waveforms provided that the components belong to an orthogonal basis. In the simplest case the components are  $\sin(x)$  and  $\cos(x)$ . An orthogonal basis function means the  $\sin(x)$  is  $90^{\circ}$  out of phase compared to  $\cos(x)$ . Mathematically, a set of functions  $\{f_n(x)\}_{n=1}^{\infty}$  is said to be an orthogonal system with respect to the non-negative weight function w(x) on the interval [a, b] if

$$\int_{a}^{b} f_{m}(x) f_{n}(x) w(x) dx = 0, \qquad \text{whenever } m \neq n$$

<sup>&</sup>lt;sup>1</sup>The amplitude falls to 8.7 dB

The technique was pioneered by the physicist Joseph Fourier during his research on heat flow and the results were published widely, especially in "Théorie Analytique de la Chaleur" (Analytical Theory of Heat) in 1822. The Fourier series is defined as follows:

Let f be a piecewise continuous function on the interval [-T, T]. Then the Fourier series of f is the trigonometric series

$$f(x) \sim \frac{a_0}{2} + \sum_{n=1}^{\infty} \{a_n \cos(\frac{n\pi x}{T}) + b_n \sin(\frac{n\pi x}{T})\}$$

(2.3)

The coefficients  $a_n$ 's and  $b_n$ 's are given by the following formulas

$$a_n = \frac{1}{T} \int_{-T}^{T} f(x) \cos(\frac{n\pi x}{T}) dx \qquad n = 0, 1, 2, \dots$$

(2.4)

$$b_n = \frac{1}{T} \int_{-T}^{T} f(x) \sin(\frac{n\pi x}{T}) dx \qquad n = 1, 2, 3, \dots$$

(2.5)

In equation 2.3, the continuous time form has been used. In the digital domain, the Fourier series becomes periodic due to the sampling process and integrals become summations. Also, calculations of the coefficients in equations 2.4, 2.5 are simplified by using complex arithmetic. All the DFT does is to correlate the data with sinusoids to *see* how much of a particular harmonic is contained within the signal. Once the harmonics are found, resynthesis of the signal can be performed by using equation 2.3.

A relative to sinusoidal additive synthesis uses what are known as wavelets. A wavelet is a time-domain and frequency-domain limited function. In [38], Guillemain and Kronland-Martinet discuss the relationships of acoustical signals in terms of wavelets. This modern area of additive synthesis has advantages in signal reconstruction (resynthesis) due to its resemblance with multirate DSP techniques. However, formant based synthesis techniques do have many similarities with this approach and to a musician these are much more intuitive to use.

There are three methods to implement sinusoid additive synthesis. They are timedivision multiplexed fixed sample-rate wavetable oscillators, inverse FFT and multirate additive synthesis.

#### 2.2.1 Time-Multiplexed Wavetable Oscillators

This approach is the logical extension of a fixed sample-rate, wavetable oscillator, whereby inserting registers at key locations allow the hardware to perform multiple oscillator lookups by utilising pipelining in the adder and ROM output stages. The

works by [10, 58, 86, 127] utilise this concept. All the oscillators run at the highest sample-rate and the maximum number of oscillators that they are capable of is about 256. The oscillators are then multiplied by an amplitude factor and summed together.

An extension to this scheme reduces the data requirements, by storing the sinusoid as a piecewise linear function with interpolation. To overcome certain limitations caused by the straight-line segment approximation, Gaussian noise is injected into the audio stream to mask the audible artefacts. The storage requirements are just 65 elements compared with 65536 in a normal lookup table oscillator without symmetry logic. A chip implementing 127 sinusoid oscillators using  $1\mu$ m CMOS technology in an area of 27mm<sup>2</sup> was created by workers at Sheffield University [47].

Another method will be discussed in chapter 5, which is based on the CORDIC iteration algorithm. This technique improves on the previous memory reduction algorithm by almost 70 %

#### 2.2.2 Inverse FFT-based Oscillators

This technique utilises the Fast Fourier Transform to generate a complex waveform from the amplitude and phases of the individual harmonics. It is only feasible because there are algorithms which perform the DFT very quickly by noting symmetry caused by the discrete-time nature of the signals and the sample length.

The technique uses the overlap-add methodology because the FFT is a periodic function and the signal is time varying. The actual approach uses the short-time FFT. The number of oscillators the musician requires imparts directly on the computational cost and delay before hearing the signal. If the algorithm is based on a 1024 point radix-2 FFT, any frequencies which are not integer multiples of the data length will require interpolation.

This system can be built purely in software [34] and will eventually be commercialised.

#### 2.2.3 Multirate Additive Oscillators

This approach partitions the oscillators in a tree which depends on the maximum oscillator frequency within a particular sub-band. The oscillators are based on the table lookup scheme *but* their sample clocks are not operating at a fixed sample-rate, rather they operate on factors of the output sampling-rate. This approach optimises resolution of the oscillators and efficiency by noting the hierarchical nature of music [104].

The oscillators in each sub-bank will have different frequency resolutions and the frequency control word in the phase accumulator will need some conversion algorithm for the benefit of the musician. The oscillators operating at the lowest frequency will be up-sampled in stages until they have been up-sampled to the audio sampling rate. At each sub-bank the oscillators running at that frequency are added and up-sampled up through the tree.

The system will require clever scheduling techniques and sophisticated user interfaces to operate [107, 108]. It has the potential of generating thousands of sinusoids using current ASIC design methodologies.

# 2.3 Frequency Modulation

FM synthesis uses standard wavetable hardware as described earlier in this thesis. Its application to musical tone synthesis can be traced back to John Chowning in 1973 [11]. He used the technique to generate audio spectra where both carrier and modulating frequencies are in the audio band. Thus the side-bands generated by the process appears in the audio band and these form the spectrum. This technique was sold to Yamaha and the first digital synthesiser, known as the DX7, was born.

In FM, the instantaneous frequency of the carrier wave is varied by the modulating wave. The rate at which the carrier varies is the frequency of the modulating wave. The variation of the carrier, known as the peak frequency deviation, is proportional to the amplitude of the modulating wave. The equation describing the process, having a carrier frequency, c, modulation frequency, m and peak deviation, d is shown in equation 2.6

$$e = A\sin(2\pi ct + \frac{d}{m}\sin(2\pi mt))$$

(2.6)

When  $I=\frac{d}{m}$  is zero, there is no modulation. When I is greater than zero, sidebands appear above and below the carrier and are separated by m Hz. The larger I, the modulation index, the more sidebands appear and the carrier amplitude reduces. The amplitudes of the carrier and sidebands are determined by Bessel functions of the first kind. These functions naturally arise from problems having circular symmetry.

The total bandwidth of the signal generated by FM is approximately 2 (d+m) Hz. The sidebands can be derived from the expansion of equation 2.6, where  $J_n(I)$  is the n'th order Bessel function.

$$e = A\{J_0(I)\sin(2\pi ct) + J_1(I)[\sin(2\pi t(c+m)) - \sin(2\pi t(c-m))] + J_2(I)[\sin(2\pi t(c+2m)) + \sin(2\pi t(c-2m))] + J_3(I)[\sin(2\pi t(c+3m)) - \sin(2\pi t(c-3m))] + \cdots \}$$

It can be seen that by varying few parameters, a rich time-varying spectrum can be produced. Chowning has been able to make quite realistic analogs of trumpets, violins and singing voices using this non-intuitive method.

FM synthesis can use non-sinusoidal carrier and/or modulation waves to produce a richer spectrum. The only caveat being the bandwidth must not exceed the audio bandwidth, otherwise aliasing will result.

# 2.4 Data Reduction for Synthesis

In this section, I will briefly discuss techniques used to reduce the number of parameters to describe timbres. This is of paramount importance in all synthesis engines because of finite computational resources. So it is important to know how much data is necessary to produce high quality audio synthesis of sound.

This aspect of sound synthesis is really beyond the scope of this thesis, as it is concerned with the analysis of sampled sound into its harmonic structure. These results are subjected to further analysis to reduce the parameters necessary so that on resynthesis a close facsimile to the original can be generated.

There are various approaches to this transformation and all are dependent on clustering of data into regions of similarity and the condensing of these areas into a reduced parameter space. Two important methods are known as Principal Component Analysis and Group Additive Synthesis. Principal Component Analysis is a statistical technique used to recast a correlated matrix of data into a set of orthonormal basis vectors subject to the minimisation of the sum of the mean-square differences between the original and reconstructed data sets. In [118], Sandell and Martens described this approach for additive synthesis of sound and reported that nearly identical resynthesis to original tones for cello, trombone and clarinet can be generated with a 40 - 70 % data reduction. In Group Additive Synthesis [101], a more complex analysis is involved which is NP-complete and thus intractable.

However, the data can be reduced by using methods derived from Computer Science research for amplitude envelopes. This scheme is still under active exploration and ongoing research.

In [46], different optimization methods were applied to piecewise-linear envelopes in order to reduce the data needed to describe timbres. Horner and Beauchamp used gradient search and genetic algorithm techniques and found that genetic algorithms were the best but were computationally expensive for real-time analysis/synthesis systems. The use of shared breakpoint times for harmonic amplitude envelopes enabled additive synthesis to be mapped onto wavetable interpolation schemes. However, the authors do not mention what synthesis engine should be used. In addition to this, work has been undertaken to apply a reduced data set to various synthesis models [45] for the Trumpet, Tenor voice and Chinese Pipa tones. But these require a great deal of human intuition to work efficiently. In my view this is because the data set was designed for one particular synthesis technique; therefore a model of the parameter relationships between these two methods would be required.

In this section, I have shown that some analysis would be required to provide synthesis techniques in order to model and use instrument timbres which already exist in the physical world. However, for new timbres and effects, the assumptions which can be applied to data reduction methods no longer apply. In this regime unusual audio textures can be produced by using reduced parameter spaces.

# 2.5 Waveguide Modelling

This method tries to model the physical world by solving partial differential equations using digital techniques. Thus digital waveguides are used. These are the discrete-time equivalents to transmission lines having two 'arms' providing the forward and backward propagating wave solutions to a pipe. Oscillators [124] can be made.

The primary aim of this technique is the concept that by modelling the real world the articulation of the digital simulations will provide realistic timbres and smooth parameter updates. However, this is normally offset by the man-machine user interface being different to the instrument being modelled and thus an interface model must be designed.

Currently, most waveguide based synthesis systems are monophonic because of the enormous memory and arithmetic operations required to perform the synthesis. A good introduction on this subject can be found in [126].

# 2.6 Speech Modelling

The most interesting of all the synthesis methods are the ones which are based on human speech emulation. The human voice is acknowledged as being the most versatile of all sound producing instruments and is capable of producing drum and wind instrument imitations, as well as ventriloquists and impersonators. The quest for speech synthesis has been man's goal for many centuries. Mankind's fascination for talking machines was first encountered in Ancient Greek mythology and more recently in Cervantes' "Don Quixote". The following quote sums up man's interest in speech synthesis:-

"The invention of a talking machine, and its operation in accordance with a well-considered plan, would be one of the boldest schemes to occur to the human intellect"

Wolfgang Von Kempelen (1971)

In this section time-domain (LPC) and spectrum (Formant synthesis including FOF) synthesis methods will be studied. Incidentally, waveguide modelling has been used in speech production [76], and is normally known as articulatory synthesis.

Instead of modelling the physical processes which produce speech, these approaches model the signal itself. This overcomes the limitations of modelling a system which is often non-linear and complex; thus simplifications and assumptions are made which result in poor emulation of the signal. However, these methods are abstract in construction, having no physically meaningful parameters and requiring complex rules to account for every perceptible nuance of the signal.

However, these engines are easy to construct and are found in many appliances including GSM phones, speech synthesisers and audio coding for broadcast. It is quite common to find that analysis of instrument's mechanics in terms of the audio signal is easier to investigate than their physical behaviour.

#### 2.6.1 Time-Domain Modelling

This approach models the sample nature of the signal rather than the frequency components. In the literature there is some confusion as to what time-domain modelling refers to. I am assuming that this technique models the amplitude fluctuations as a function of time.

The aim of this technique is to model the signal to a linear all-pole IIR filter having the transfer function shown in equation 2.7.

$$H(z) = \frac{G}{1 + \sum_{k=1}^{p} a_p(k)z^{-k}}$$

(2.7)

Where p is the number of poles in the filter, G is the filter gain and  $\{a_p(k)\}$  are the parameters that determine the poles. Taking a short segment of the audio signal of about 20 ms and using linear prediction the coefficients  $a_p(k)$  can be determined. We model equation 2.7 by its inverse, which is a FIR filter. The analysis process works out the error between the FIR filter and the signal and minimises the sum of the squared errors and the residual signal which cannot be modelled by the filter is stored as the residual.

To reconstruct the signal, the parameters are inserted into an all-pole IIR filter and the residual signal is idealised by a noise source. Vowel sounds can be modelled by driving the filter with a periodic impulse train with a period equal to the pitch.

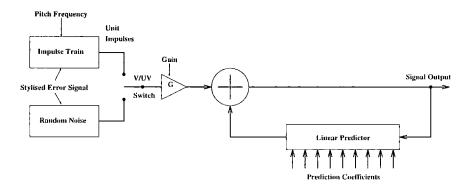

Figure 2.4: LPC Synthesiser

A schematic diagram of a LPC synthesiser is shown in figure 2.4 and by using lattice all-pole filters, the coefficients can be quantised to a few bits without loss of precision. Consequently, cheap and commercially viable systems can be made, e.g. Texas Instruments Speak and Spell. However, for music, the user requires greater precision. This difference can be traced back to speech coding for transmission over low bandwidth lines.

#### 2.6.2 Spectral Modelling

In the previous sub-section the signal was approximated by modelling the timevarying signal in the time domain. Here, the signal is modelled via its frequency components. Most physical instruments, including the human voice, are composed of a cavity in which standing waves are set up. The air in these cavities thus resonates. In the speech and music fields these resonances are collectively known as formants. This technique finds some known filter which can resonate and uses a parallel or cascade connection of them to generate a harmonically rich spectrum.

The VOSIM, parallel/cascade formant and FOF synthesisers will be discussed in the next sub-sections.

#### 2.6.2.1 VOSIM

The VOSIM technique was designed to create a simulation of vocal sounds and hence was called VOcal SIMulation. It was created and developed by Werner Kaegi in 1973.

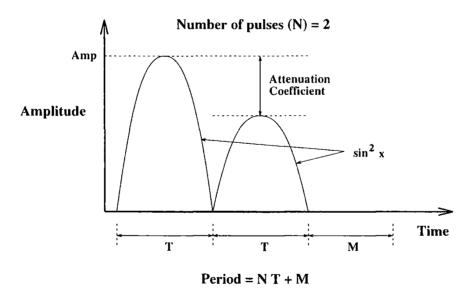

VOSIM uses a simple waveform controlled by three parameters and periodically repeated at the desired fundamental frequency. It consists of a series of  $\sin^2(x)$  pulses having a pulse-width of T, followed by a delay M. There is a decay parameter, b which is the factor by which each pulse height is reduced with respect to the preceeding pulse. The first pulse has unit amplitude. The last parameter is the number of pulses in each period. It can be clearly seen from diagram 2.5 that the period can be varied by altering M. A rigorous analysis of the waveform in both time and frequency domains can be found in [135].

Figure 2.5: Typical VOSIM waveform

To generate format-like regions in the frequency domain, the musician will require two or more VOSIM oscillators. Each oscillator models a formant. The output of all the oscillators is summed to produce the desired effect. One major draw-back to the technique is that it is only useful in producing tones with variable pitch but stationary spectra.

The beauty of this technique is manifest in the hardware. Each VOSIM oscillator can be computed using a slightly modified wavetable oscillator. The first pulse is generated by setting the amplitude factor to unity and scanning the table pointer forwards, thus reading the pulse at a rate dependent on the pulse-width parameter. Once the pulse has been read, the amplitude factor is multiplied by the decay parameter and the table pointer is reset and allowed to scan through the table as before. If all the pulses are generated, the wavetable oscillator will output zeros for M seconds.

#### 2.6.2.2 Parallel/Cascade Formant Synthesis

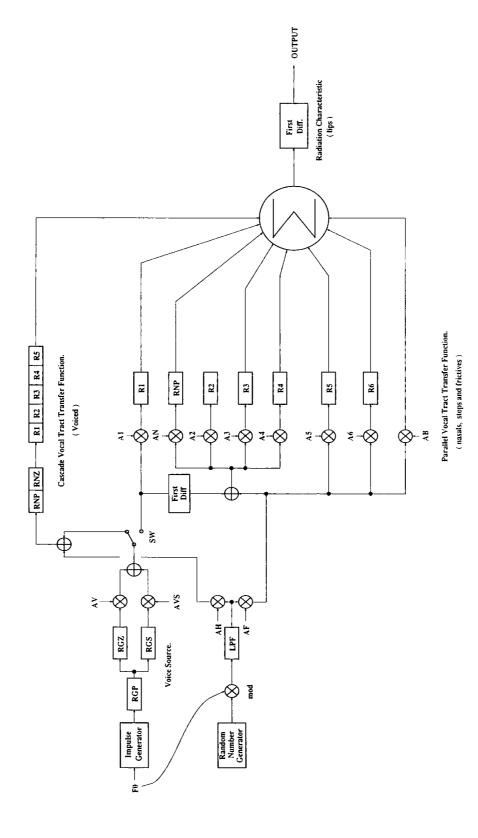

The formant synthesiser uses three to five second order low pass filters, each having variable amplitude, bandwidth and frequency controls. These filters are either connected in serial (cascade) form or parallel form. They are driven like LPC with an idealised pulse train and/or noise source. The former configuration is suitable for non-nasal voiced sounds and the latter is superior for nasals, fricatives and stops. The cascade form models the vocal tract without nasal coupling and thus is a closer model to the human voice. The parallel form is an abstract model.

In the serial form, if a small number of resonant filters is to be used, then a correcting function is required. Ideally, this depends on the number of formants and their frequencies, but can be approximated by a fixed network [76]. The advantage of the serial approach is that the formant amplitudes are predictable from the knowledge of the formant frequencies and bandwidths.

However, the parallel form has greater flexibility and control as all three parameters are directly controllable. This creates two problems. Firstly, the user has yet another parameter to control; in a musical context this might be desirable to aid novel, non-physical based timbres. The second problem is potentially more serious. The phase cancellation at frequencies between two resonances may cause zeros in the frequency response when the parallel formant filters are summed together. This can be explained by considering the sum of two second-order bandpass filter functions in the continuous domain <sup>2</sup>.

$$\frac{s}{s^2 + \beta_1 s + \omega_1^2} + \frac{s}{s^2 + \beta_2 s + \omega_2^2} = \frac{s(2s^2 + s(\beta_1 + \beta_2) + \omega_1^2 + \omega_2^2)}{(s^2 + \beta_1 s + \omega_1^2)(s^2 + \beta_2 s + \omega_2^2)}$$

(2.8)

<sup>&</sup>lt;sup>2</sup>The equation in the discrete time form is similar, except the parameters are trigonometric and exponential functions.

It can be seen that the numerator term of equation 2.8 will have complex conjugate roots between the two pole frequencies  $\omega_1$  and  $\omega_2$ . This will produce a deep minima, which can be removed by alternating the signs for each formant filter.

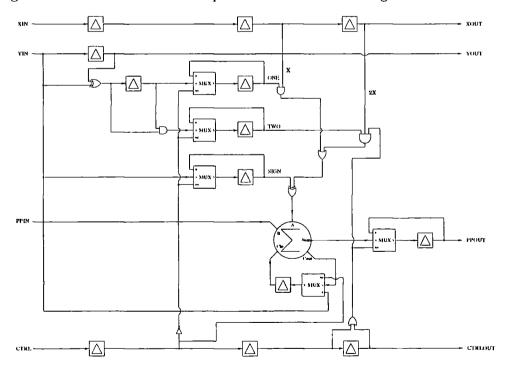

A general parallel/series hybrid formant synthesiser [69] is shown in figure 2.6. F0 is the pitch and AV, AVS, AH, AF, AB and A1 to A6 are amplitude factors. RGS, RNP and R1 to R6 are resonators and RGZ and RNZ are anti-resonators having variable bandwidth and frequency.

The synthesiser as shown in figure 2.6 can be simplified to a standard parallel structure and the formant filters can be factorised into common terms, this would reduce the arithmetic and storage costs.

Figure 2.6: Block Diagram of Serial-parallel formant synthesiser. (After Klatt (1980) [69])

#### 2.6.2.3 Forme d'Onde Formantique

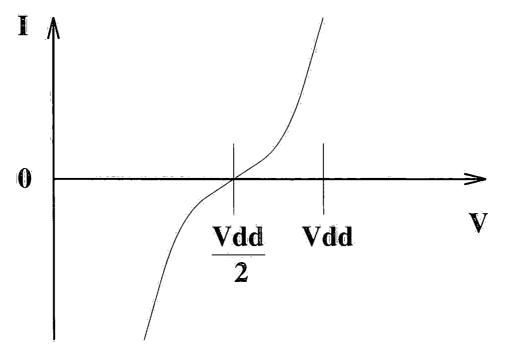

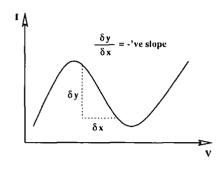

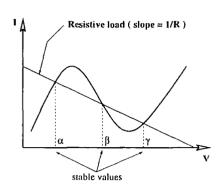

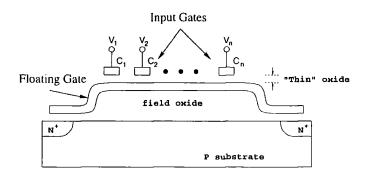

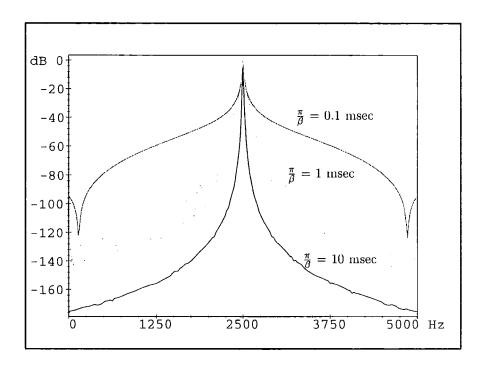

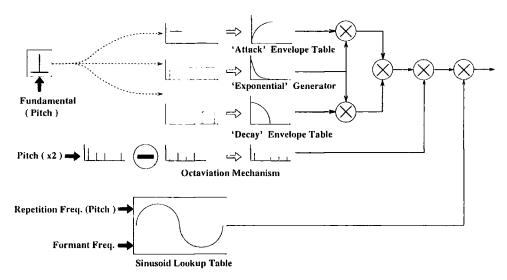

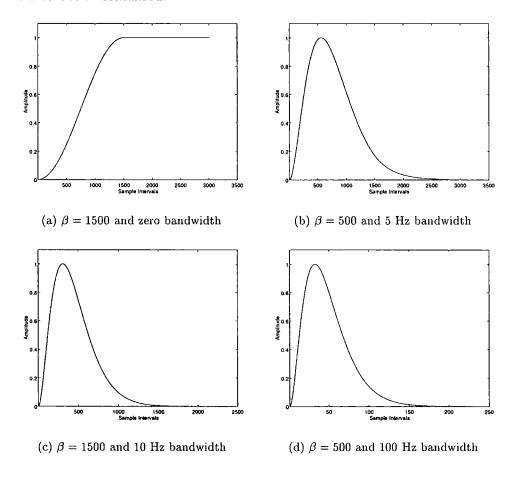

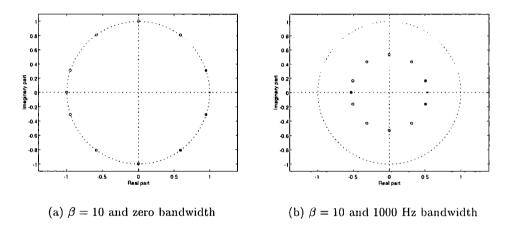

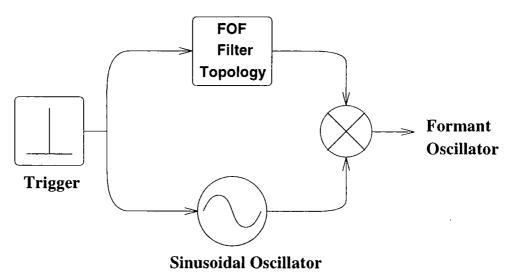

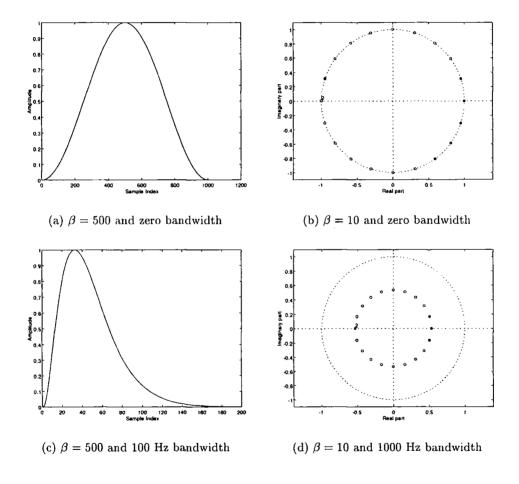

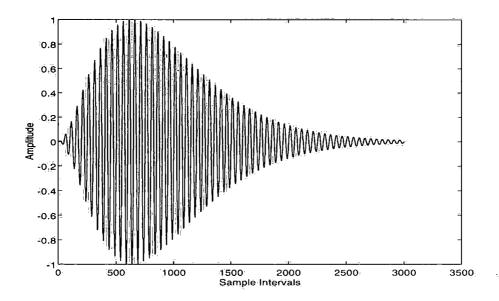

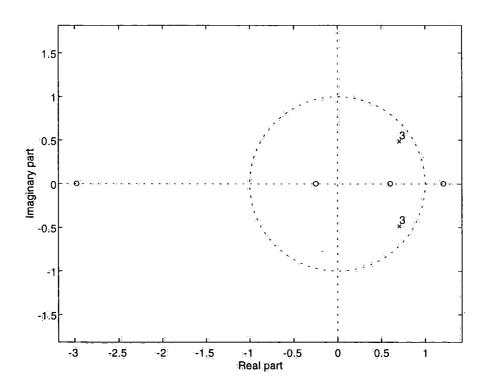

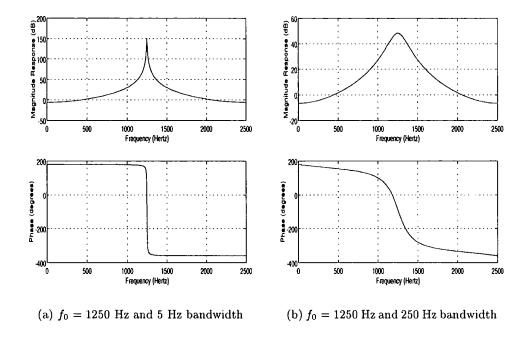

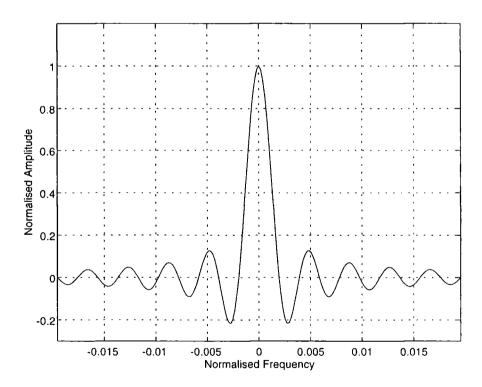

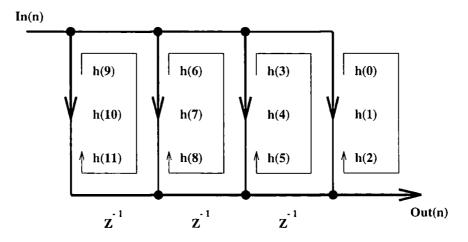

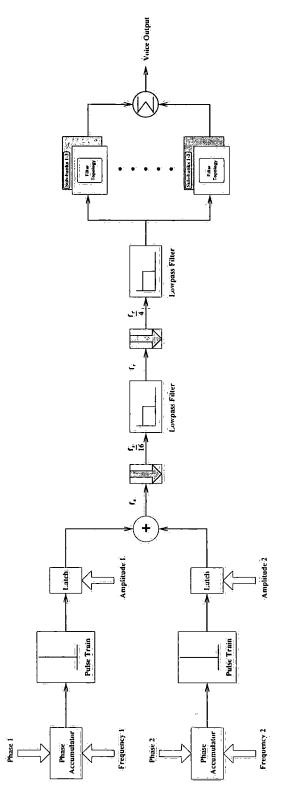

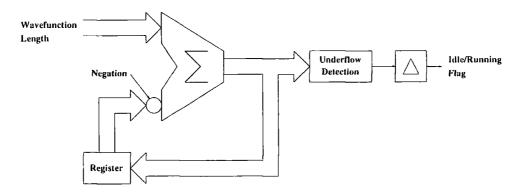

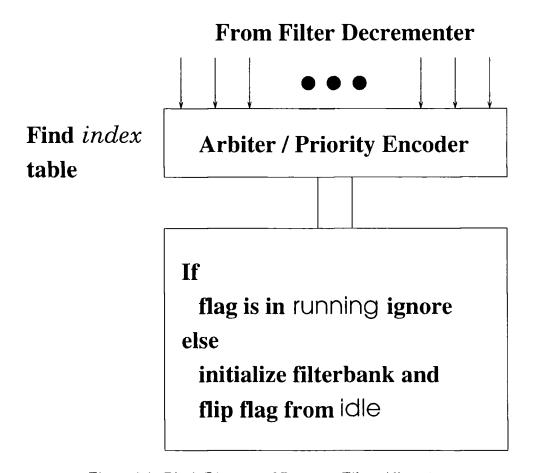

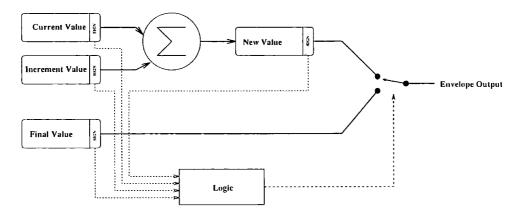

FOF was developed by Xavier Rodet in 1978 and a control program known as CHANT allowed musicians to generate excellent renditions of singing voices, providing the musicians composed at IRCAM in Paris, France. Later in the development of the system, cymbals, drums and string based instruments were emulated.