# PARITY-BASED ERROR DETECTION WITH RECOMPUTATION FOR FAULT-TOLERANT SPACEBORNE COMPUTING

# **GÖKÇE AYDOS**

GÖRSCHWIN FEY

Advisor

UNIVERSITY OF BREMEN Faculty of Mathematics and Computer Science

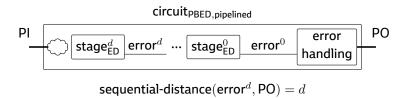

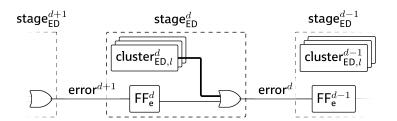

REVIEWERS

Görschwin Fey — University of Bremen

Jaan Raik — Talinn University of Technology

COLLOQUIUM

10th August 2017

Further information and experimental data used in this work can be found at https://aydos.de/diss

### Abstract

In radiation environment (e.g., space, nuclear reactor), electronics can fail due to bitflips in the flipflops of integrated circuits. A common solution is to triplicate the flipflops and connect their outputs to a voter. If one of the three bits is flipped, then the voter outputs the majority value and tolerates the error. This method is called triple modular redundancy (TMR).

TMR can cause about 300% area redundancy. An alternative way is error detection with on-demand recomputation, where the recomputation is done by repeating the failed processing request to the processing circuit. The computation is done in consecutive transactions, which we call transaction-based processing.

We implemented and evaluated the aforementioned alternative approach using parity checking on the Microsemi ProASIC3 FPGA, which is often used in space applications. The results show that parity-based error detection with our system recovery approach can save up to 54% of the area overhead that would be caused by the TMR, and achieve in most circuits slightly better timing results than TMR on ProASIC3. This area saving can be the key for fitting the application to a space-constrained chip.

### Zusammenfassung

In einer Strahlungsumgebung wie im All oder in der Nähe eines Atomreaktors können elektronische Geräte durch Bitkipper in den Flipflops integrierter Schaltungen ausfallen. Eine gängige Methode gegen die Bitkipper ist triple modular redundancy (TMR), bei der jedes Flipflop der Schaltung dreifach instanziiert wird und die Ausgänge der Flipflops zu einem Voter angeschlossen werden. Falls eins von den drei Bits gekippt wird, dann gibt der Voter den Majoritätswert aus und toleriert somit diesen Fehler.

TMR kann etwa 300% Flächenaufwand verursachen. Eine alternative Methode ist Fehlerdetektion mit anschließender Neuverarbeitung der letzten Daten. Die Neuverarbeitung der Daten wird durch die Wiederholung der letzten Datenverarbeitungsanfrage zur Schaltung realisiert. Die Verarbeitung der Daten erfolgt durch nacheinanderfolgende Transaktionen und diese Art von Datenverarbeitung nennen wir transaktions-basierte Datenverarbeitung in dieser Arbeit.

Wir haben die obenerwähnte Methode implementiert und bewertet, wobei wir als Fehlerdetektionsmethode Paritätsprüfung eingesetzt haben. Die Bewertung erfolgte auf dem FPGA Microsemi ProASIC3, das bei Avionikanwendungen sehr verbreitet ist. Die Ergebnisse zeigen, dass unsere Methode bis zu 54% des Flächenaufwands einsparen kann, der sonst vom TMR verursacht wäre. Andererseits kann unsere Methode in den meisten Schaltungen etwas besseres Timing als TMR erzielen. Die Flächeneinsparung könnte maßgeblich für die Implementierung einer Anwendung auf einer begrenzen Chipfläche sein.

# **Contents**

| 1 | Intr          | oductio                                  | on Control of the Con | 1  |  |  |

|---|---------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|

|   | 1.1           | cation on a processing architecture      | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |  |  |

|   |               | 1.1.1                                    | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3  |  |  |

|   |               | 1.1.2                                    | FPGA Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3  |  |  |

|   |               | 1.1.3                                    | Communication Protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4  |  |  |

|   |               | 1.1.4                                    | Hardening                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5  |  |  |

|   | 1.2           | Next o                                   | chapters and background work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6  |  |  |

| 2 | Preliminaries |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |  |

|   | 2.1           | Conce                                    | epts of dependable computing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 9  |  |  |

|   |               | 2.1.1                                    | Systems and threats to dependability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 10 |  |  |

|   |               | 2.1.2                                    | Means for dependability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 15 |  |  |

|   |               | 2.1.3                                    | Fault tolerance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 16 |  |  |

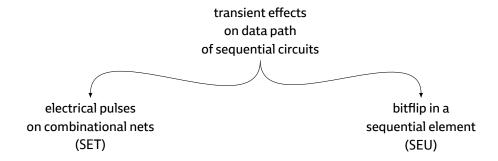

|   | 2.2           | Transient effects on sequential circuits |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |  |

|   | 2.3           | Fault r                                  | model used in this work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 20 |  |  |

|   | 2.4           | Fault t                                  | tolerance techniques against SEUs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 22 |  |  |

|   |               | 2.4.1                                    | Fabrication process level techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 23 |  |  |

|   |               | 2.4.2                                    | Chip layout level techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 24 |  |  |

|   |               | 2.4.3                                    | Logic level techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 25 |  |  |

|   |               | 2.4.4                                    | Triple modular redundancy on logic level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 26 |  |  |

|   |               | 2.4.5                                    | Architecture level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 28 |  |  |

|   |               | 2.4.6                                    | Software level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 28 |  |  |

|   |               | 2.4.7                                    | Algorithm level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 29 |  |  |

|   | 2.5           | FPGA:                                    | s used in mission-critical applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 29 |  |  |

|   | 2.6           | Microsemi ProASIC3 FPGA                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |  |

|   | 2.7           | Error detection-based fault tolerance    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |  |

| 3 | Rela          | ited wo                                  | ork                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 35 |  |  |

|   | 3.1           | Error                                    | detection by duplicated instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 35 |  |  |

|   | 3.2           | Limitations of software-based techniques |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |  |

|   | 3.3           |                                          | layer exploration for architecting resilience                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 41 |  |  |

|   |               | 3.3.1                                    | General discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 41 |  |  |

|   |               | 3.3.2                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 43 |  |  |

### **CONTENTS**

| 4  | Pari  | ty-based error detection                 | 45         |

|----|-------|------------------------------------------|------------|

|    | 4.1   | Concept                                  | 45         |

|    | 4.2   | Analytical evaluation                    | 48         |

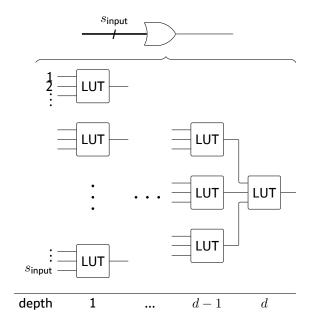

|    |       | 4.2.1 Prerequisites                      | 48         |

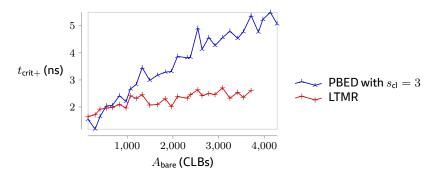

|    |       | 4.2.2 Critical path delay                | 49         |

|    |       | 4.2.3 Circuit area overhead              | 53         |

|    |       | 4.2.4 Multiple bit error susceptibility  | 56         |

|    | 4.3   | Experimental evaluation                  | 58         |

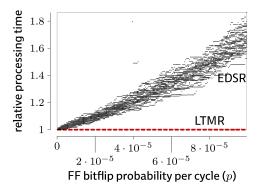

|    |       | 4.3.1 Finite state machine (FSM) circuit | 59         |

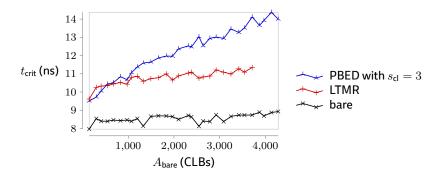

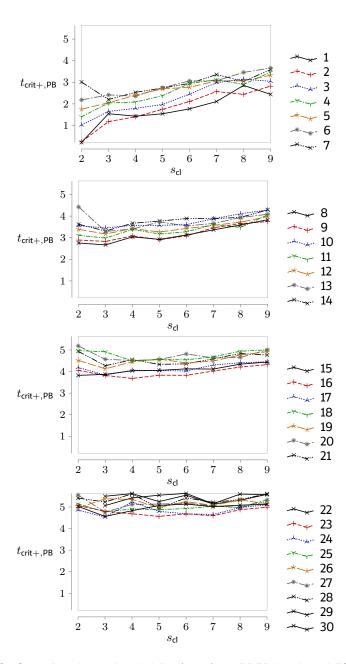

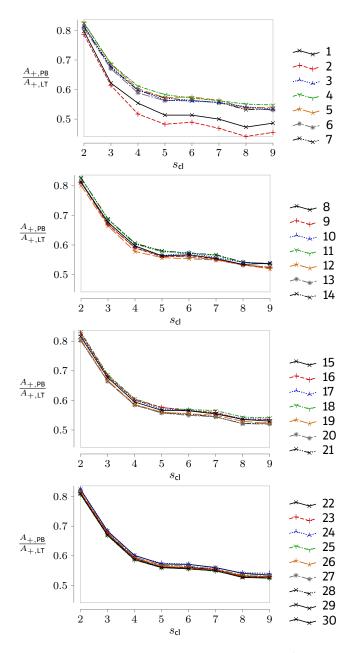

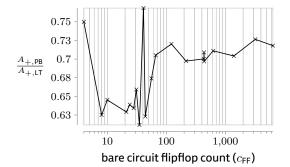

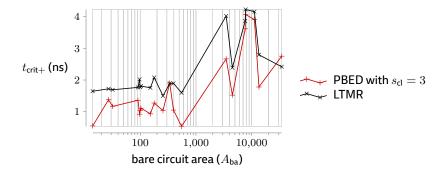

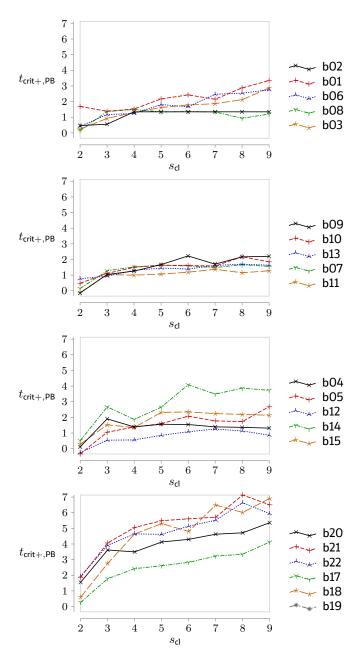

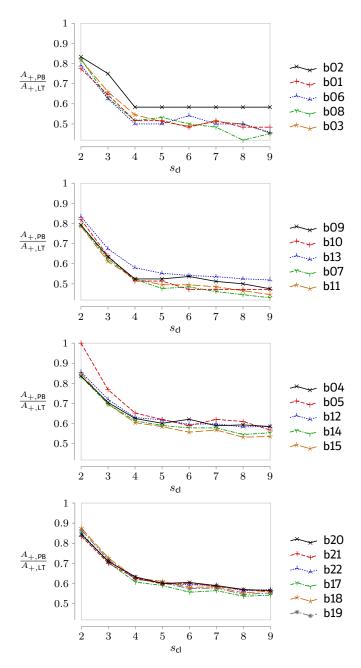

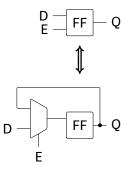

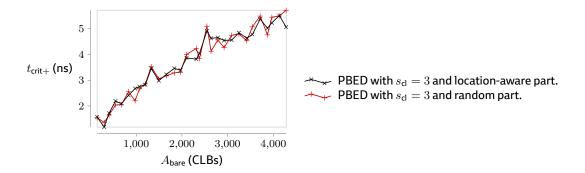

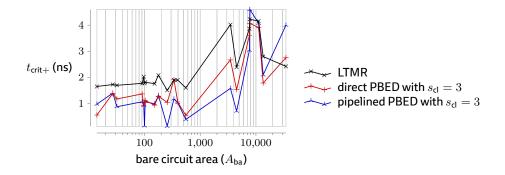

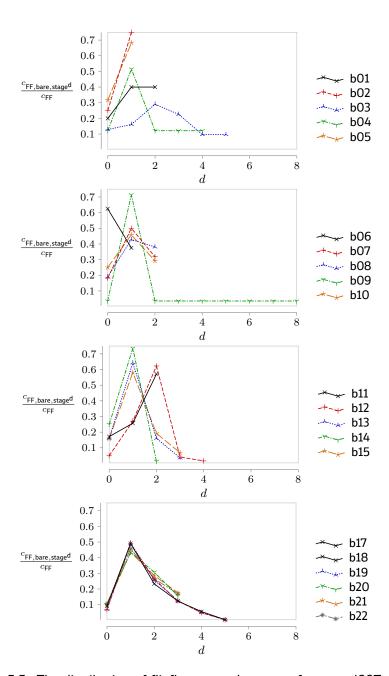

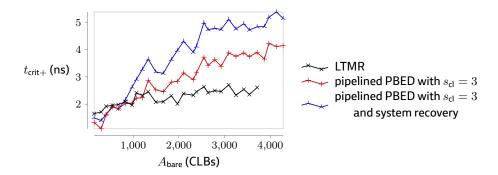

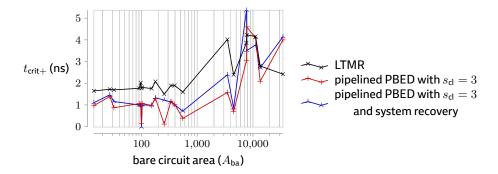

|    |       | 4.3.2 199T circuits                      | 66         |

|    | 4.4   | Automatic application                    | 76         |

| 5  | Pipe  | elined cluster error signal reduction    | 83         |

|    | 5.1   | Concept                                  | 83         |

|    | 5.2   | Experimental evaluation                  | 84         |

|    |       | 5.2.1 Finite state machine (FSM) circuit | 85         |

|    |       | 5.2.2 199T circuits                      | 87         |

|    | 5.3   | Automatic application                    | 90         |

| 6  | Tran  | nsaction-based processing & recovery     | 93         |

| •  | 6.1   | Recovery in the target circuit           | 93         |

|    | 0.1   | 6.1.1 Circuit isolation                  | 94         |

|    |       | 6.1.2 Circuit reset                      | 96         |

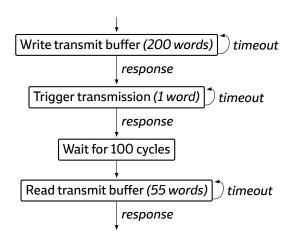

|    | 6.2   | Transaction-based processing             | 97         |

|    | 0.2   | 6.2.1 Concept                            | 97         |

|    |       | 6.2.2 Fault tolerance analysis           | 99         |

|    | 6.3   | <u> </u>                                 | 100        |

|    | 0.5   | •                                        | 101        |

|    |       |                                          | 104        |

|    |       |                                          | 106        |

|    | 6.4   | 3 , 3                                    | 107        |

|    | 0.4   |                                          | 107<br>107 |

|    |       | 3 3                                      | 109        |

| 7  | Con   | clusion                                  | 111        |

|    |       |                                          |            |

| Ac | knov  | vledgments and statutory declaration     | 113        |

| Re | ferer | nces                                     | 114        |

# **Chapter 1**

# Introduction

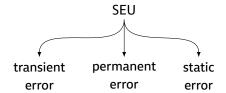

Electronics for airborne and space systems, called avionics, must often be protected from ionizing radiation in and coming from space. In the absence of a shield like the magnetic field of the earth, high energy particles can traverse through the digital circuit fabric and cause bitflips in the flipflops of a circuit.

Also terrestrial computing systems at sea level are exposed to some amount of radiation, but the probability that a bit in a flipflop is flipped is relatively low compared to higher attitudes in atmosphere or space. Still, as more bits can be stored on the same chip area, the computing systems at sea level also show signs of bitflips.

Where some of the induced bitflips can vanish unnoticed by the computing system, some bitflips can lead to a restart or freeze of a system. This is not an issue if a personal computer restarts, but this should not happen with a critical system like a server which tracks financial transactions or a computer, which guides a space vehicle. Such systems must be dependable and be able to tolerate possible threats in their working environment, e.g., component failure due to aging or high energy particles present in space striking through system components.

Dependable computers often use modular redundancy against component failures. Modular redundancy means that a module is present many times that failure of a module can be tolerated by switching to the redundant modules. If the effect of a threat is permanent, i.e., a component cannot be used after a failure, then a system with n equal components can tolerate up to n-1 component failures.

In contrast, if a threat is only temporary, e.g., by recovering a failed component by a restart, there is no need to include many redundant modules. A well-known fault tolerance approach against temporary module failures is the *triple modular redundancy (TMR)*, which provides a straightforward error detection and recovery approach by triplicating a module and connecting the modules to a voter entity, and the voter entity selects the trusted output. For instance, a majority voter outputs *yes* if two of the modules output *yes* and one *no* by trusting the majority. Consequently, TMR can tolerate a failure of a single module and enables the continuation of the service. Still, while one module is in failure, module recovery

must be initiated to avoid a failure of the system (consisting of these three modules), because a second module failure will cause a system failure.

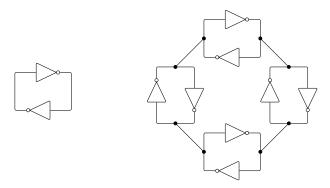

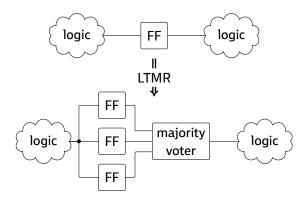

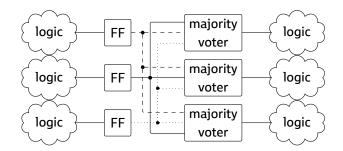

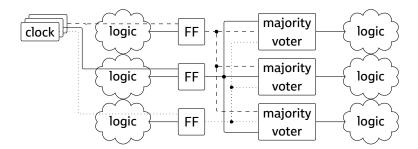

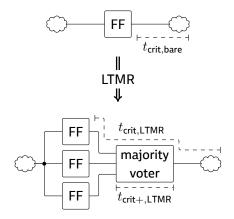

The idea of TMR can also be applied on components of avionics. Digital sequential circuits which are part of avionics also often implement TMR. If TMR is implemented solely on the flipflops, it is called *local TMR (LTMR)*. In LTMR, for every application flipflop in the circuit two redundant flipflops are created, which store the same bit as the application flipflop. The outputs of these three flipflops are then connected to a majority voter.

The LTMR approach has the advantage of built-in error detection and recovery: If a flipflop bit is flipped during a clock cycle, then this bit error is masked by the voter. In the next cycle, the flipped flipflop will be overwritten with the correct bit coming from the combinatorics, leading to the recovery from the erroneous state of the flipflop.

LTMR can be easily applied on a circuit and is often applied using commercial available software tools. Unfortunately, LTMR comes at a significant cost of additional space for redundant flipflops. Additionally, redundant flipflops can also account for excess power consumption.

On space- and power-constrained applications, an alternative is to apply an error detection approach instead of LTMR, because error detection generally incurs less resources than error correction.

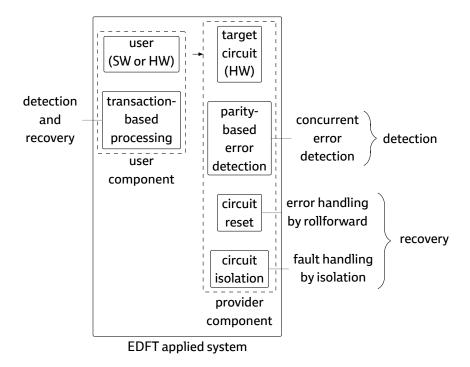

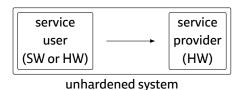

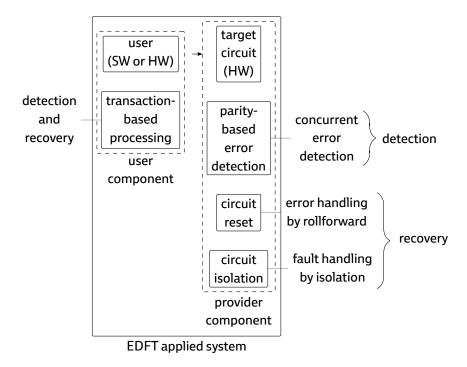

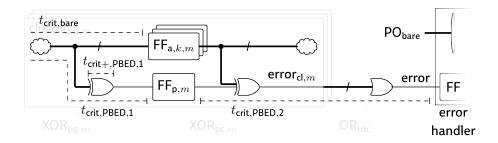

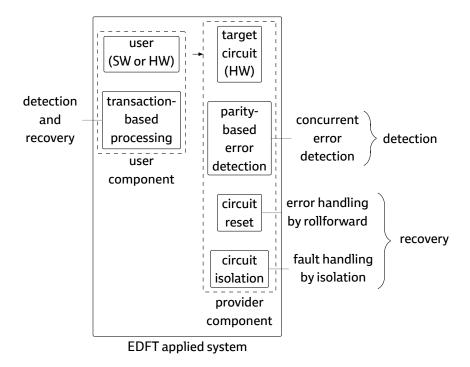

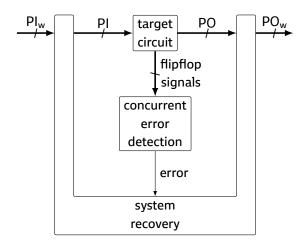

A circuit which implements error detection can only flag an error, but cannot correct erroneous data, or recover itself from an erroneous state. In this situation, this circuit can be recovered externally from the failure state by another system component and the last processing request to this circuit can be retried. In this work, we propose this approach, and call it *error detection-based fault tolerance* and will be abbreviated as *EDFT*.

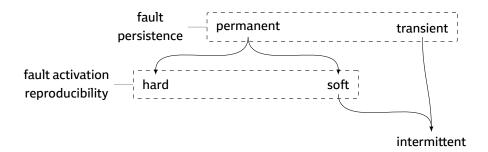

In chronological order, EDFT involves the following actions:

- the detection of the error

- system recovery on the circuit using isolation and error handling

- error detection and system recovery on the user application retrying the last processing request to the circuit

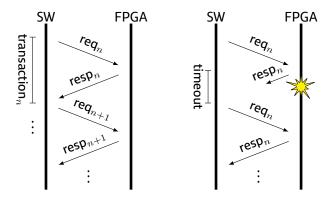

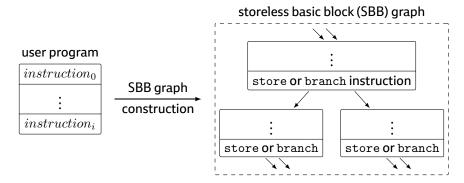

The last action can be carried out by a request and response-based processing protocol between two systems. In this work, this processing technique is called *transaction-based processing*.

The three actions of EDFT can be implemented by different approaches. To evaluate EDFT in detail and compare to the state of the art, not only generic specifications but also concrete implementation of EDFT's components are needed. In the next section, we will present a data processing architecture, on which EDFT can be applied. With the help of this example architecture, we will describe the EDFT's components more in detail and then evaluate EDFT by using the concrete implementations.

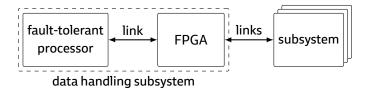

Figure 1.1: Overview of the reference processing architecture. Processor communicates with other subsystems through the FPGA.

### 1.1 Application on a processing architecture

In this section, we describe a reference model of an on-board data handling unit (OBDH) for satellites [Tre+14]. Using this example architecture we will briefly explain in the following section how EDFT is implemented. The detailed implementation will be discussed in the following chapters. Moreover, this particular implementation will also be used for comparing EDFT with state of the art in the following chapters.

First, we describe an overview of the system, then the target circuit, and finally the communication protocol between the processor and the circuit.

### 1.1.1 Overview

Figure 1.1 shows an overview of the architecture. The OBDH subsystem comprises of two main processing modules: a processor and an FPGA. The processor runs the mission software, which involves communicating with different subsystems on-board of the space system. The communication is done through the FPGA, which acts as an interface component and implements the various communication interfaces needed by the subsystems (e.g., UART, CAN). We assume that the processor, the communication line between the processor and the FPGA, and the subsystems are sufficiently protected against soft errors.

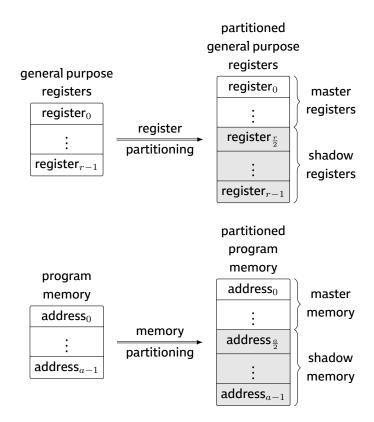

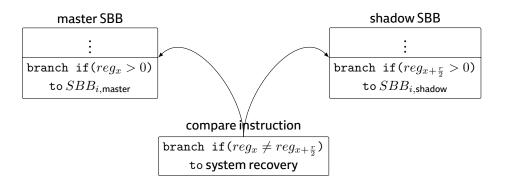

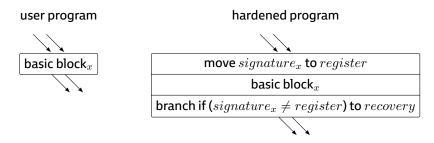

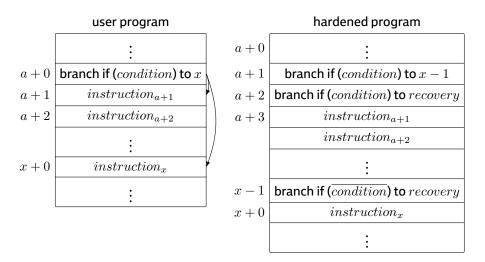

### 1.1.2 FPGA Design

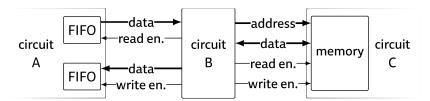

From the processor point of view, the FPGA is a remote memory bus, where the implemented link interfaces are memory-mapped. The processor utilizes these interface modules by reading and writing the respective memory areas.

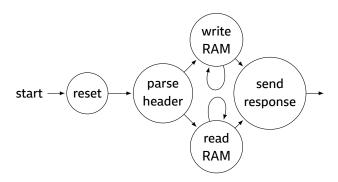

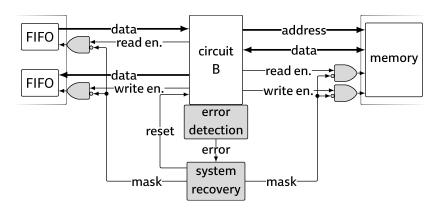

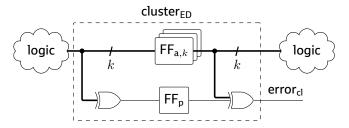

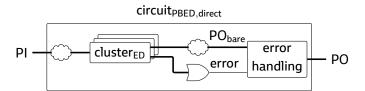

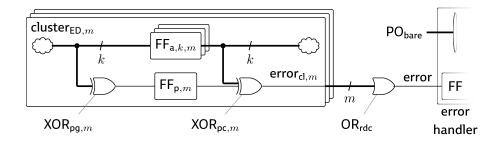

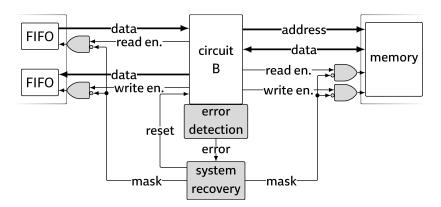

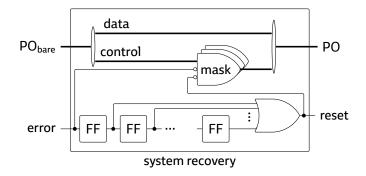

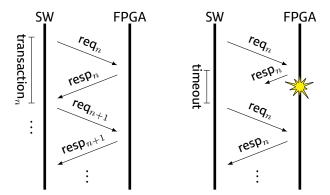

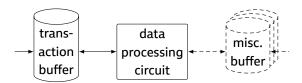

The simplified FPGA model consists of three functional blocks: sequential circuits A, B, and C as shown in figure 1.2. Circuit A serves the memory access requests from the processor to circuit B, which issues memory accesses on circuit C and finally returns the data to the processor using the FIFO interface of circuit A. In figure 1.3, circuit B is described as a finite state machine (FSM). Circuit B reads the memory access request packets sent by the processor from the FIFO and transforms them in memory accesses for circuit C. Circuit C with a memory block inside resembles the memory-mapped interfaces. The memories transfer one word per

Figure 1.2: Excerpt from the FPGA design. Circuit B must be hardened by design. Other circuits are immune to soft errors.