### Development of Readout Electronics for the ATLAS Tile Calorimeter at the HL-LHC

Departamento de Ingeniería Electrónica Programa de doctorado en Ingeniería Electrónica

> TESIS DOCTORAL Fernando Carrió Argos

> > DIRECTOR

Dr. Alberto Valero Biot

Valencia, mayo 2017

A dissertation submitted to the University of València for the degree of Doctor of Philosophy.

### Declaration

This dissertation is the result of my own work, except where explicit reference is make to the work of others. It has not been submitted for another qualification to this or any other university.

Fernando Carrió Argos

# Acknowledgements

Many people contributed to the success of this thesis and I would like to thank all of them.

First of all, I would like to express my gratitude to my advisor Dr. Alberto Valero for the guidance and suggestions offered during all these years at IFIC and CERN. He was always accessible and willing to help me even during one of the most important periods of his life (congratulations on your baby).

Thanks to my friends and colleagues from the IFIC TileCal group: Luca, Juan, Damián, Leonor, Sergi, Yesenia, Pedro, and Paco. You are an incredible teamwork that makes this group feels like family. Also my acknowledgment to the professors Antonio Ferrer, Victoria Castillo and Emilio Higón for all the support and advice, especially during my first months at CERN. I would like to thank all of you for giving me the opportunity of collaborating in this fascinating project.

Most probably, this period was not as hard as it should thanks to my friends from the University of Valencia and IFIC: David, Javier Navarro, Ramón, Gesssamí, Xavier and Javier Collado. Thank you so much for the coffees and conversations which saved me in the worst moments.

Of course, all this work could not have been possible without the hard work of a great community: the TileCal collaboration. I want to thank Christian Bohm, Steffen Muschter and Eduardo Valdés from the Stockholm University for the time discussing about firmware, clock domains and remote programming. Mark Oreglia, Kelby Anderson and Fukun Tang from the University of Chicago, thank you for sharing your invaluable experience with readout electronics and hardware. Special thanks to Alexander Paramonov from Argonne National Laboratory for the fruitful discussions during the coffees at the testbeam and

#### ACKNOWLEDGEMENTS

for all the support during the writing of this document. I am also grateful to Giulio Usai from University of Texas for being an excellent leader in the projects in which we worked together. I hope we can continue discussing for a long time in the increasingly longer upgrade meetings.

I would also like to thank Carlos Solans, Júlio Viera and Pablo Moreno with whom I shared most of my time working in the MobiDICK project at CERN.

I am grateful to Manoel Barros and Diego Barrientos for the endless discussions about technical details about digital electronics and printed circuit board design. I learn a lot from you!

Finalmente, me gustaría agradecer a mi familia y a Anna por el apoyo incondicional que me han dado durante estos años y, en especial, durante los últimos meses de esta tesis. Sin ellos esta tesis no sería posible.

A todos vosotros: ¡MUCHAS GRACIAS!

### Preface

The Large Hadron Collider (LHC) is one of largest particle accelerators in the world. It has been used to explore energy frontier physics since 2010, with a collaboration composed of more than 7,000 scientists from 60 different countries. After a major upgrade that will occur in the 2020s, the LHC will become the High Luminosity LHC (HL-LHC). The HL-LHC will increase the instantaneous luminosity by a factor 5 compared to the LHC. The integrated luminosity of the HL-LHC program will be 10 times the integrated luminosity of LHC.

The R&D HL-LHC efforts involve a large community in Europe, but also in the US and Japan. The design of the HL-LHC and the consequent upgrade of the experiments at the HL-LHC represents an exceptional technological challenge. New accelerator technologies are under development such as superconducting magnets and cavities and high-throughput electronics to receive and process the extraordinary amount of data generated by the experiments. In addition, the new readout and trigger architecture planned for the ATLAS in the HL-LHC requires a complete redesign of the front-end and back-end electronics systems to cope with the new requirements in radiation levels, data bandwidth and clocking distribution.

This thesis is focused on the development of readout electronics for the ATLAS experiment at the HL-LHC, particularly in the design of the Tile Preprocessor (TilePPr) prototype envisaged for the readout of the Tile Calorimeter and communication with the ATLAS trigger system.

Chapters 1 and 2 present an introduction to the LHC and HL-LHC experiments, followed by an extensive review of the Tile Calorimeter and the plans for the ATLAS Phase II Upgrade for the HL-LHC.

#### PREFACE

The TilePPr prototype hardware design is fully described in Chapter 3, followed by the result of signal integrity simulations that confirmed the correct design of the PCB. At the end of the chapter some experimental results obtained during the initial tests with the first prototypes are presented.

Chapter 4 describes all the firmware developments implemented for the operation of the Demonstrator module in the TilePPr prototype and in the DaughterBoard. This chapter includes a detailed description of all the firmware blocks designed for the front-end and back-end electronics, focusing in the development of high-speed data links with fixed and deterministic latency.

Chapter 5 presents the development of FPGA-based circuits for the precise measurement of phase differences between clocks. A phase measurement circuit, called OSUS, based on oversampling techniques is discussed. The experimental results with the OSUS circuit obtained from its implementation in the TilePPr prototype are presented here. The OSUS circuit permits the synchronization of the Demonstrator module and the LHC clock, as well as the monitoring of the phase stability of clocks with a precision of about 30  $ps_{RMS}$ .

Chapter 6 includes a description of the testbeam setup and some experimental physics results obtained. During these testbeam campaigns the TilePPr prototype was the main readout system in the back-end electronics operating the Demonstrator module.

Finally, the conclusions and future plans for this work are given at the end of this document.

# Contents

| 1 | $Th\epsilon$ | e Large | e Hadron Collider                                                                     | 1    |

|---|--------------|---------|---------------------------------------------------------------------------------------|------|

|   | 1.1          | Introd  | uction                                                                                | 1    |

|   |              | 1.1.1   | LHC experiments                                                                       | 2    |

|   | 1.2          | The A   | TLAS experiment                                                                       | 3    |

|   |              | 1.2.1   | Trigger and Data AcQuisition system $\hfill \ldots \ldots \ldots$ .                   | 5    |

|   | 1.3          | The T   | 'ile Calorimeter                                                                      | 6    |

|   |              | 1.3.1   | Optics                                                                                | 7    |

|   |              | 1.3.2   | Front-end electronics                                                                 | 8    |

|   |              | 1.3.3   | Back-end electronics $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 13   |

|   | 1.4          | Data f  | flow of the TileCal readout chain $\ldots \ldots \ldots \ldots \ldots \ldots$         | 15   |

| • |              |         |                                                                                       | 1 17 |

| 2 |              |         | pgrades for HL-LHC                                                                    | 17   |

|   | 2.1          | TDAG    | architecture                                                                          | 18   |

|   | 2.2          | Tile C  | alorimeter Upgrade                                                                    | 20   |

|   |              | 2.2.1   | Front-end electronics                                                                 | 22   |

|   |              | 2.2.2   | Power supplies                                                                        | 30   |

|   |              | 2.2.3   | Back-end electronics                                                                  | 33   |

| • | ъ            | •       |                                                                                       | 07   |

| 3 |              | -       | the TilePPr prototype                                                                 | 37   |

|   | 3.1          | -       | ications of the TilePPr prototype                                                     | 37   |

|   | 3.2          | Comp    | onents and functionality                                                              | 38   |

|   |              | 3.2.1   | Field Programmable Gate Arrays                                                        | 39   |

|   |              | 3.2.2   | TTC receiver block                                                                    | 45   |

|   |              | 3.2.3   | Clocking unit                                                                         | 46   |

|   |              | 3.2.4   | Configuration                                                                         | 47   |

|   |      | 3.2.5   | Power distribution                                                                                                                                | 18 |

|---|------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   |      | 3.2.6   | Other components                                                                                                                                  | 51 |

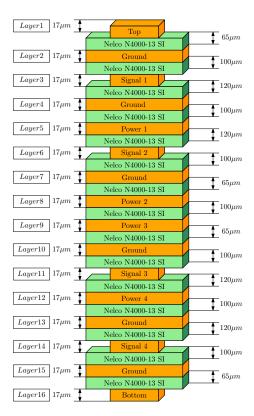

|   | 3.3  | Physic  | cal design and PCB layout                                                                                                                         | 52 |

|   |      | 3.3.1   | Stack-up                                                                                                                                          | 53 |

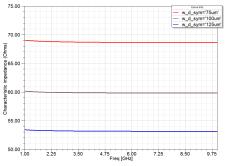

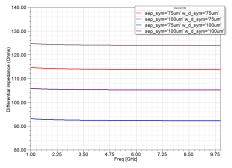

|   |      | 3.3.2   | Signal integrity studies                                                                                                                          | 54 |

|   |      | 3.3.3   | IR drops                                                                                                                                          | 35 |

|   | 3.4  | Post-la | ayout simulations $\ldots \ldots $                                                 | 37 |

|   |      | 3.4.1   | Insertion and return losses                                                                                                                       | 67 |

|   | 3.5  | Chara   | cterization tests                                                                                                                                 | 71 |

|   |      | 3.5.1   | Introduction to jitter                                                                                                                            | 72 |

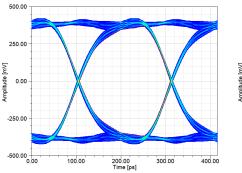

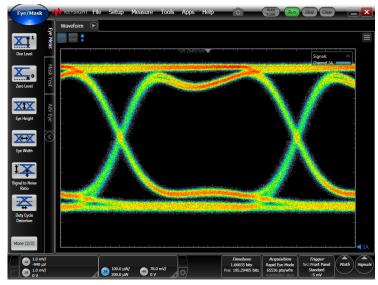

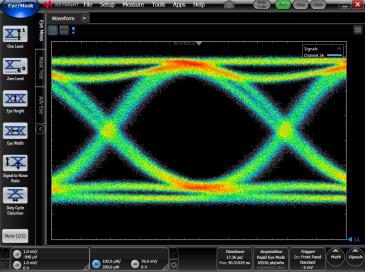

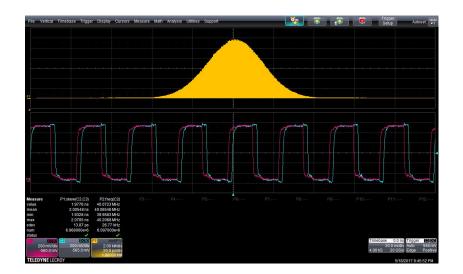

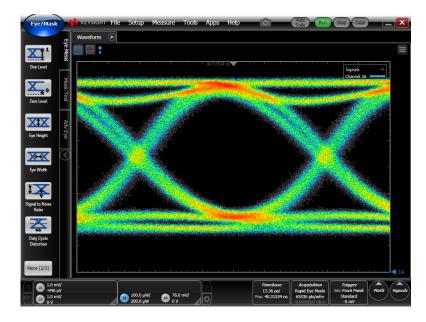

|   |      | 3.5.2   | Eye diagrams                                                                                                                                      | 74 |

| 4 | Inte | gratio  | on of the TilePPr in the Demonstrator 7                                                                                                           | 9  |

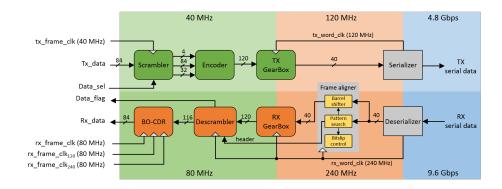

|   | 4.1  | GBT ]   | protocol                                                                                                                                          | 80 |

|   | 4.2  | Tile G  | BT-FPGA IP core                                                                                                                                   | 33 |

|   |      | 4.2.1   | Front-end Tile GBT links                                                                                                                          | 84 |

|   |      | 4.2.2   | Back-end Tile GBT links                                                                                                                           | 36 |

|   | 4.3  | Data f  | format                                                                                                                                            | 91 |

|   |      | 4.3.1   | Downlink data format                                                                                                                              | 92 |

|   |      | 4.3.2   | Uplink data format                                                                                                                                | 93 |

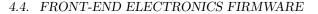

|   | 4.4  | Front-  | end electronics firmware                                                                                                                          | 94 |

|   |      | 4.4.1   | Data Packer                                                                                                                                       | 94 |

|   |      | 4.4.2   | MainBoard Interface module                                                                                                                        | 96 |

|   |      | 4.4.3   | Charge Injection System block                                                                                                                     | 98 |

|   |      | 4.4.4   | Integrator block                                                                                                                                  | 99 |

|   |      | 4.4.5   | GBTx configuration module                                                                                                                         | 99 |

|   |      | 4.4.6   | Monitoring block                                                                                                                                  | )0 |

|   |      | 4.4.7   | DCS module $\ldots \ldots \ldots$ | )0 |

|   |      | 4.4.8   | ADC block                                                                                                                                         | )1 |

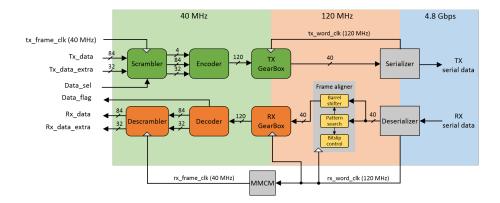

|   | 4.5  | Back-   | end electronics firmware                                                                                                                          | )4 |

|   |      | 4.5.1   | IPbus                                                                                                                                             | )4 |

|   |      | 4.5.2   | Link Controller                                                                                                                                   | )5 |

|   |      | 4.5.3   | Encoder                                                                                                                                           | )5 |

|   |      | 4.5.4   | DCS FSM                                                                                                                                           | )6 |

#### CONTENTS

|   |      | 4.5.5   | TTC module                                                                                              | 107  |

|---|------|---------|---------------------------------------------------------------------------------------------------------|------|

|   |      | 4.5.6   | Decoder                                                                                                 | 108  |

|   |      | 4.5.7   | Integrator Readout block                                                                                | 109  |

|   |      | 4.5.8   | $Pipeline \ module \ \ \ldots $ | 109  |

|   |      | 4.5.9   | Readout interfaces                                                                                      | 111  |

|   |      | 4.5.10  | Latency block                                                                                           | 113  |

|   | 4.6  | Data p  | bath delays and latency measurements                                                                    | 114  |

|   |      | 4.6.1   | Digital path latency measurements                                                                       | 114  |

|   |      | 4.6.2   | ADC interface path latency $\ldots \ldots \ldots \ldots \ldots$                                         | 117  |

| 5 | Clo  | ck dist | ribution in the Tile Calorimeter                                                                        | 121  |

|   | 5.1  | Currer  | nt clock distribution architecture                                                                      | 122  |

|   | 5.2  | Clock   | distribution architecture in the HL-LHC                                                                 | 123  |

|   |      | 5.2.1   | Synchronization of the Demonstrator module                                                              | 123  |

|   | 5.3  | DMTI    | D method                                                                                                | 125  |

|   |      | 5.3.1   | Digital approximation of the DMTD method $\ldots \ldots \ldots$                                         | 127  |

|   | 5.4  | OverSa  | ampling to UnderSampling method                                                                         | 131  |

|   |      | 5.4.1   | Performance of the OSUS circuit $\ldots \ldots \ldots \ldots \ldots$                                    | 133  |

|   | 5.5  | Impler  | nentation of the OSUS circuit                                                                           | 138  |

|   |      | 5.5.1   | Synchronization of the Demonstrator with the TTC system                                                 | n139 |

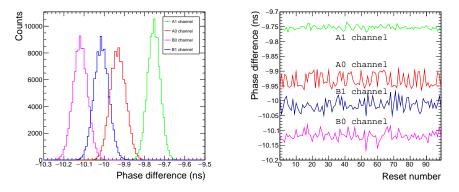

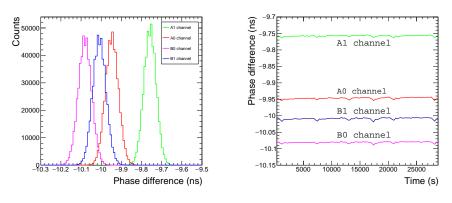

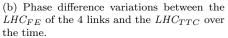

|   |      | 5.5.2   | Studies on clock stability $\ldots \ldots \ldots \ldots \ldots \ldots$                                  | 143  |

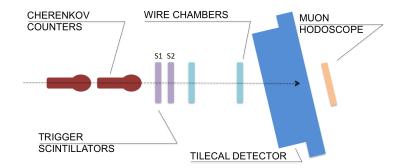

| 6 | Test | tbeam   | setup and results                                                                                       | 147  |

|   | 6.1  | Introd  | uction                                                                                                  | 147  |

|   | 6.2  | Testbe  | am setup                                                                                                | 148  |

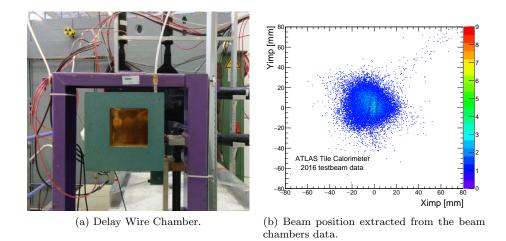

|   |      | 6.2.1   | Beam elements                                                                                           | 150  |

|   | 6.3  | Clock   | distribution                                                                                            | 152  |

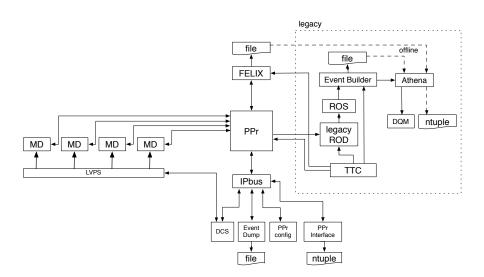

|   | 6.4  | Data a  | acquisition                                                                                             | 153  |

|   | 6.5  | Calibr  | ation systems                                                                                           | 156  |

|   |      | 6.5.1   | Pedestal and linearity runs                                                                             | 156  |

|   |      | 6.5.2   | Charge Injection System                                                                                 | 158  |

|   |      | 6.5.3   | Cesium scans                                                                                            | 159  |

|   | 6.6  | Demor   | nstrator physics program                                                                                | 161  |

|   |      | 6.6.1   | Data quality                                                                                            | 161  |

|    |                     | 6.6.2  | Offline data analysis                                  | 164 |

|----|---------------------|--------|--------------------------------------------------------|-----|

| 7  | Con                 | clusio | ns                                                     | 169 |

| 8  | $\mathbf{Res}$      | umen   |                                                        | 173 |

|    | 8.1                 | Introd | ucción                                                 | 173 |

|    |                     | 8.1.1  | Experimento ATLAS                                      | 174 |

|    |                     | 8.1.2  | Calorímetro Hadrónico TileCal                          | 176 |

|    |                     | 8.1.3  | Mejoras del experimento ATLAS y el High Luminosity LHC | 177 |

|    |                     | 8.1.4  | Proyecto Demonstrator                                  | 178 |

|    | 8.2                 | Protot | ipo TilePPr                                            | 180 |

|    | 8.3                 | Objeti | vos                                                    | 183 |

|    | 8.4                 | Metod  | ología                                                 | 184 |

|    | 8.5                 | Conclu | usiones                                                | 187 |

| Li | st of               | Acron  | yms                                                    | 191 |

| Bi | bliog               | graphy |                                                        | 195 |

| Li | List of Figures 202 |        |                                                        |     |

| Li | st of               | Tables | 5                                                      | 209 |

### Chapter 1

## The Large Hadron Collider

#### 1.1 Introduction

The Large Hadron Collider (LHC) [1] is the world's largest and most powerful particle accelerator. It is installed and operated at the European Organization of Nuclear Research (CERN) in a circular tunnel of 27 km and 100 m underground, crossing the border of France and Switzerland, close to Geneva. The LHC is composed of super-conducting magnets designed to collide proton beams at a center-of-mass energy of  $\sqrt{s} = 14$  TeV, delivering an instantaneous luminosity of  $\mathcal{L} = 1 \times 10^{34} \,\mathrm{cm}^{-2} \mathrm{s}^{-1}$ .

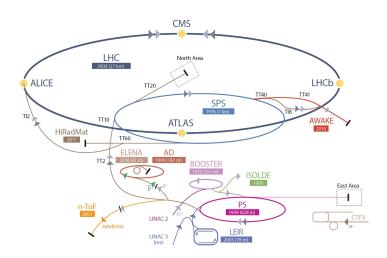

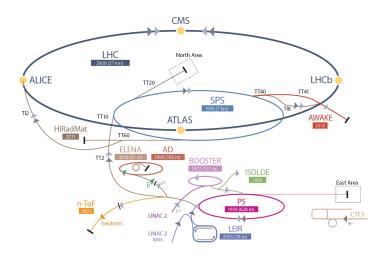

The LHC is the last stage of a series of accelerators increasing the energy of the proton beams. Figure 1.1 shows a diagram of the CERN's accelerator complex and how they are interconnected. Linac2 and PS Booster compose the first stages of the accelerator complex where the proton beam reaches an energy of 1.4 GeV. Then, the beam is injected into the Proton Synchrotron (PS) which accelerates the beam up to 25 GeV. The Super Proton Synchrotron (SPS) receives the protons from the PS and accelerates them to 450 GeV before injecting them into the LHC. Finally, in the LHC proton beams are accelerated to their maximum energy in two separated beam pipes where beams travel in opposite directions before colliding.

Figure 1.1: The CERN's accelerator complex.

#### 1.1.1 LHC experiments

Seven experiments installed around the LHC analyze the particles produced in the collisions. The LHC collides the proton beams at four interaction points around the accelerator ring corresponding to the location of the main experiments: ATLAS (A Toroidal LHC ApparatuS) [2], CMS (Compact Muon Solenoid) [3], ALICE (A Large Ion Collider Experiment) [4] and LHCb (Large Hadron Collider beauty) [5].

The two largest experiments, ATLAS and CMS, are multi-purpose experiments located in opposite sides of the LHC ring. ATLAS and CMS were designed and optimized to measure the properties of the strong and electroweak forces with high precision at the TeV scale, and studying new physics beyond the Standard Model. In 2012, both experiments announced the discovery of the Higgs boson [6] with a mass around 125 GeV. The LHCb studies B-physics and the CP violation whereas ALICE experiment investigates the quark-gluon plasma through heavy ion collisions.

The other three experiments in the LHC are much smaller in size. The TOTEM (TOTAl Elastic and diffractive cross-section Measurement) [7] experiment is near the CMS detector and performs high-precision measurements of the proton size and the LHC luminosity. The LHCf (LHC forward) [8] is located near the ATLAS detector and studies the particle generation in the forward re-

gion of collision as a simulation of cosmic rays in laboratory conditions. The last experiment approved by the LHC is the MoEDAL (Monopole and Exotics Detector at the LHC) [9]. The MoEDAL is installed in the walls of the LHCb cavern and searches directly for the magnet monopole.

#### **1.2** The ATLAS experiment

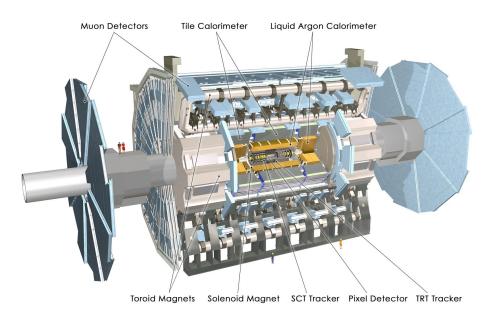

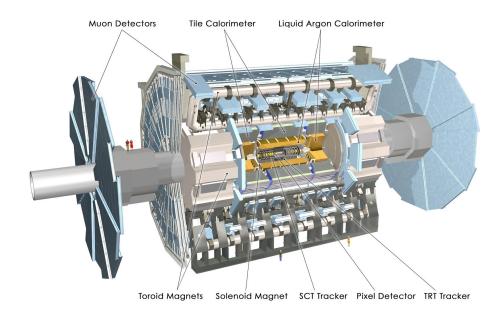

The ATLAS experiment [2] is a general-purpose detector designed to study the products of p-p collisions at the LHC. The ATLAS detector is the largest detector in the LHC and is about 45 meters long, more than 25 meters high, and has an overall weight of approximately 7,000 tons.

Figure 1.2: The ATLAS experiment.

The two proton beams collide at the center of the ATLAS detector producing particles in all directions. The ATLAS experiment is composed of different subdetectors to measure the different type of particles emerged from the collisions: the Inner Detector (ID), electromagnetic and hadronic calorimeter systems and the Muon Spectrometer (MS).

Built around the beam pipe, the ID is located at the inner part of ATLAS. It was designed for tracking and vertexing by the measurement of the trajectories of the charged particles generated in the collisions. A solenoidal magnet surrounds the ID generating a magnetic field of 2 Tesla which bends the trajectories of the charged particles. The curvature of the trajectories is used for the calculation of the particle momentum. Surrounding the ID, the Liquid Argon (LAr) and the Tile (TileCal) calorimeters measure the deposited energy and reconstruct the direction of different types of particles. The outermost layer of the ATLAS is composed of the MS and a toroid magnet, where a muon tracking system measures the trajectories of the muons beyond the calorimeters. Three superconducting air-core toroid magnets surrounding the ATLAS detector generate a field of 0.5 Tesla in average to bend the trajectory of charged particles.

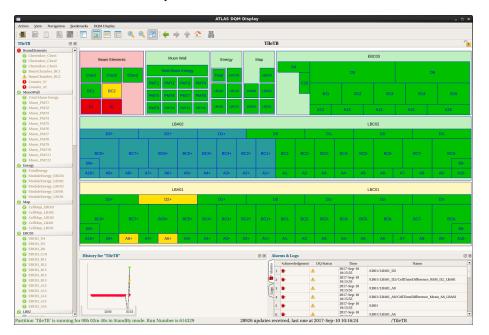

The ATLAS detector provides high precision measurements of different types of particles and processes.

The design requirements of the ATLAS detector include the following aspects:

- Very good electromagnetic calorimetry for electron and photon separation and measurement, complemented by a full coverage hadronic calorimetry for accurate jet and missing transverse energy  $(E_T^{miss})$  measurements.

- High-precision muon measurements, with the capability to guarantee accurate measurements at the highest luminosity using the external muon spectrometer alone.

- Efficient tracking at high luminosity for high- $p_T$  lepton-momentum measurements, electron and photon identification,  $\tau$  -lepton and heavy-flavour identification, and full event reconstruction capability at low luminosity.

- Triggering and measurement of particles at low- $p_T$ , providing high efficiencies for most physics processes of interest at LHC.

- Large acceptance in pseudorapidity (η) with almost full azimuthal angle

(φ) coverage. The azimuthal angle is measured around the beam axis,

while the pseudorapidity is measured with respect to the plane perpendicular to the beam line and derived from the polar angle (θ):

$$\eta = -\ln\left(\tan\left(\frac{\theta}{2}\right)\right) \tag{1.1}$$

#### 1.2.1 Trigger and Data AcQuisition system

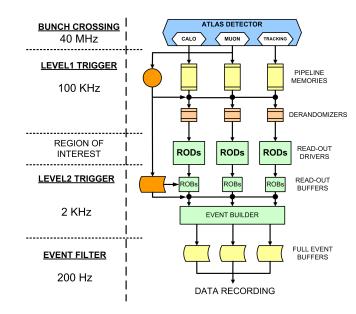

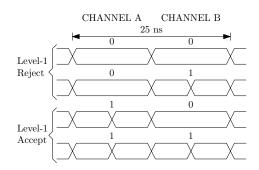

The current ATLAS trigger system [10] is composed of 3 levels of event selection. While the Level 1 (L1) trigger system is completely based on custom hardware designed for the ATLAS detector, the Level 2 (L2) and the Event Filter (EF) levels are largely based on Commercial Off-The-Shelf (COTS) components. Each trigger level refines the event selection that the previous level provided, thus reducing the trigger rate. A schema of the ATLAS Trigger and Data AcQuisition (TDAQ) system is shown in Figure 1.3.

Figure 1.3: ATLAS trigger and data acquisition system.

The L1 decision is based on reduced-granularity information provided by the Resistive Plate Chambers (RPC) and Thin-Gap Chambers (TGC) for high  $p_T$  muons, and by the calorimeters for electromagnetic clusters, jets,  $\tau$ -leptons,  $E_T^{miss}$  and large  $E_T$ . The L1 trigger reduces the event rate from 40 MHz to a maximum of 100 kHz on average. The L1 decision must arrive to the readout electronics in less than 2.5  $\mu$ s, meanwhile the front-end electronics keeps the events in pipeline memories.

The L2 trigger decision is based on Regions of Interest (RoI). The RoIs are regions of the detector where the L1 has identified possible trigger objects within the event with full-granularity and full-precision. The RoI are stored in the Read Out Buffers (ROBs) until the L2 trigger system process them. The L2 trigger system uses the ROIs information on coordinates, energy and type of signature to reduce the amount of data and reduces the event rate below 3.5 kHz, with an average event processing time of approximately 40 ms.

In the final trigger decision level the Event Filter (EF) process the complete events built in the Event Builder (EB) system and the events selected are permanent stored in the CERN computer center for further physics analysis. Although the EF was initially designed to reduce the output to about 200 Hz, during the Run 1 (2010-2012) the trigger event output was 800 Hz.

In addition, the Data AcQuisition (DAQ) system provides infrastructure for the configuration, control and monitoring of the ATLAS detector, while the Detector Control System (DCS) supervises the detector services, such as power supplies or gas systems.

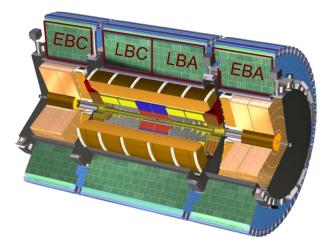

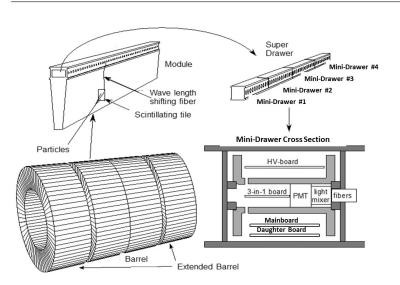

#### **1.3** The Tile Calorimeter

The Tile Calorimeter detector [2] [11] is a sampling calorimeter which uses steel as absorber and scintillator tiles as active medium. It covers the region,  $|\eta| < 1.7$ , behind the liquid argon electromagnetic calorimeter. TileCal is divided into a central Long Barrel, 5.6 meters in length, and two Extended Barrels, 2.6 meters in length. The radial depth of TileCal is approximately 7.4  $\lambda$  (interaction lengths). Each barrel is azimuthally divided into 64 wedges of size  $\Delta \phi \sim 0.1$ , made of steel plates and scintillator tiles, with a total weight of 2,600 metric tons for the complete detector.

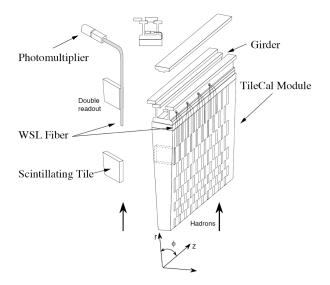

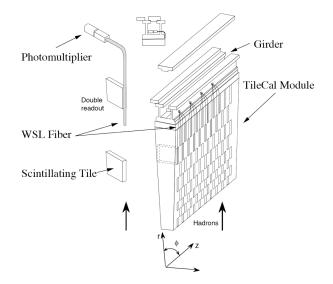

The combination of the orientation of the scintillator tiles radially and normal to the beam axis with wavelength-shifting (WLS) fiber readout on the tile edges, allows for almost seamless azimuthal calorimeter coverage. The WLS fibers are grouped into bundles defining 5,182 calorimetric cells. The fiber bundles are read out by 9,852 PhotoMultiplier Tubes (PMTs) providing an approximate projective geometry in pseudorapidity. There is a gap region between the long and the extended barrel which is instrumented with special cells. The frontend electronics and readout optics are highly integrated within the mechanical structure of TileCal. The PMTs and all the readout electronics are housed on aluminum units, called super-drawers, located at the outermost part of TileCal. The front-end electronics also provide analogue sums of channels from cells with the same  $\eta$  coordinate, forming trigger towers which are the basis for the L1 trigger processing. The low-voltage power supplies of the front-end electronics are mounted in an external steel box at one of the sides of the super-drawer which contains the connections for power and other services. For the calibration systems, the calorimeter is equipped with a laser system, a Charge Injection System (CIS) and a <sup>137</sup>Cs radioactive source which are employed to calibrate the detector response to the electromagnetic scale with a high precision. The structure of the TileCal modules is depicted in Figure 1.4.

Figure 1.4: Structure of a TileCal module and main components.

#### 1.3.1 Optics

The TileCal active medium is composed of scintillating tiles of eleven different sizes [12] of 3 mm thickness and with radial lengths ranging from 97 mm to 187 mm and azimuthal lengths ranging from 200 mm to 400 mm, where different size of the tiles corresponds to different depth in radius. Ionizing particles crossing the tiles induce the production of ultraviolet scintillation light in the polystyrene base material of the tiles and this light is subsequently converted to visible light by wavelength shifting.

The tiles are surrounded by a plastic sleeve to protect the tile and improve the scintillation light yield due to its high reflectivity of 95%. In addition, the plastic sleeve contains a mask pattern to reduce the optical non-uniformity of the tiles to a level below 5% for the sum of signals of both sides of the tile. The WLS fibers are attached to the tile edges to collect the light produced in the scintillators and shift its wavelength to a longer one. Each WLS fiber collects light from tiles and routes it to the PMTs inserted into the super-drawers.

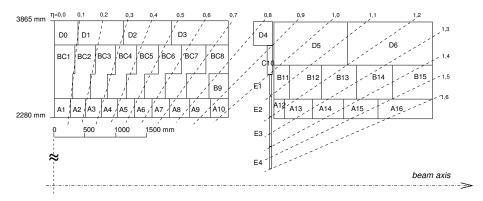

The WLS fibers are grouped together in bundles and coupled to the PMTs. The fiber grouping defines a three-dimensional cell structure to form three radial sampling depths, approximately 1.5, 4.1 and 1.8  $\lambda$  thick at  $\eta = 0$ . These cells have dimensions  $\Delta \eta \times \Delta \phi = 0.1 \times 0.1$  in the first two layers and 0.2  $\times$  0.1 in the last layer. The depth and  $\eta$ -segmentation of the barrel and extended barrel modules are shown in Figure 1.5. Each tile is read out by two different PMTs providing redundancy and sufficient information to partially equalize signals produced by particles crossing the calorimeter at different positions.

Figure 1.5: Segmentation in depth and  $\eta$  of the TileCal modules for half of a long barrel (left) and for an extended (right) barrel. TileCal cell distribution is symmetric respect to the interaction point at the origin.

#### **1.3.2** Front-end electronics

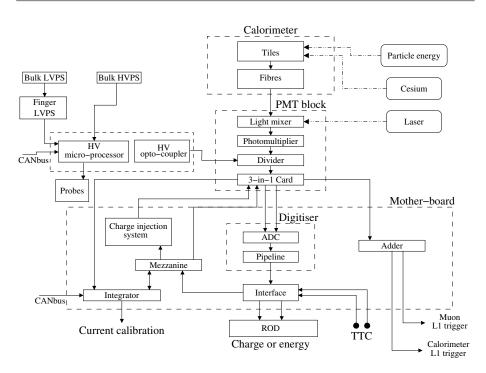

The Long Barrel and Extended Barrels are subdivided in four partitions (EBA, LBA, LBC and EBC) as depicted in Figure 1.6. Each partition is contains 64 super-drawers for a total of 256 super-drawers. The front-end electronics [13] and readout components are housed inside the super-drawers, while the rest

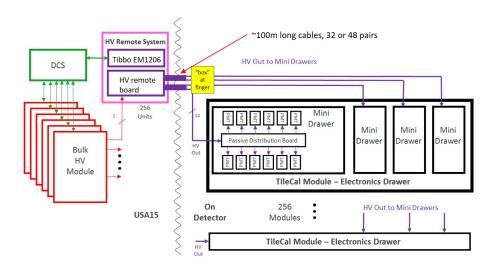

of the trigger and readout electronics are located off detector in the ATLAS counting rooms (USA15). Figure 1.7 depicts a block diagram of the TileCal electronics.

Figure 1.6: Tile Calorimeter partitions. EBA and EBC partitions correspond to the Extended Barrels and LBA and LBC partitions to the central Long Barrel.

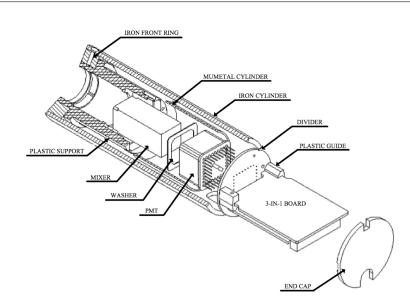

#### Photomultiplier block

The PMT block is the key element in the readout chain as they measure the light produced by the scintillating tiles. It is composed of a mechanical structure made of steel cylinder and mu-metal shield for magnetic shielding and contains a light mixer, a PMT, a high voltage divider and the 3-in-1 card (Figure 1.8). The light mixer mixes the light from the readout fibers to ensure uniform illumination of the photo-cathode. The PMT blocks are inserted into the aluminum structure of the super-drawers, ensuring an accurate placement of the light mixer and WLS fiber bundle for each tile. The main components of a PMT block are the following:

Photomultipliers: the PMT converts the light signal from the fiber bundles into an electric charge. The Hamamatsu R5900 PMT was selected to read out the tiles. This PMT has a compact size with of 28 × 28 × 28 mm<sup>3</sup> and has a dynode structure with 8 amplification stages.

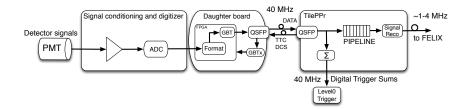

Figure 1.7: Block diagram of the TileCal electronics.

- Light mixers: since the PMT response depends over the photocathode surface position illuminated, a light mixer is used for mixing the light coming from all the fibers in the bundle, so that there is no correlation between the position of the fiber and the area of the photocathode receiving the light.

- Magnetic shielding: The mu-metal and iron magnetic shielding in the PMT must prevent residual fields from the ATLAS solenoid and toroids that could cause gain variations. It should provide a protection up to 500 Gauss magnetic fields in any direction.

- HV dividers: the primary purpose of the divider is to partition the high voltage between the dynodes of the PMT. The High Voltage (HV) divider also serves as a socket to allow the connection of the PMT to the front-end electronics without any interconnecting wires. This design minimizes the capacitance between the PMT and the electronics, which is important to reduce noise and unreliable connections.

Figure 1.8: Scheme of the PMT block.

• 3-in-1 cards: these boards provide a high and a low gain shaped pulse for the digitizer boards, the charge injection calibration system and slow integration of the PMT signals for monitoring and calibration.

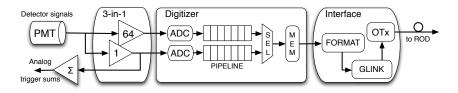

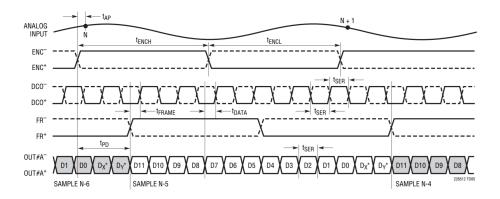

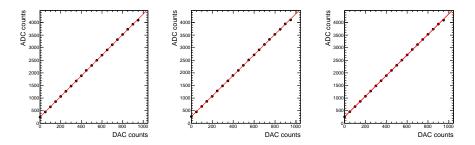

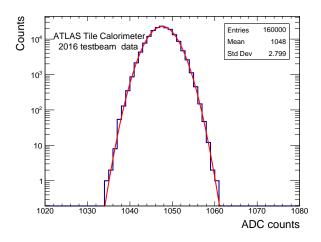

#### Digitizer system

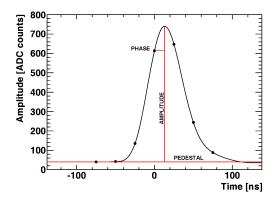

The 3-in-1 cards amplify and shape the PMT signals generating two output signals, high and low gain with a gain ratio of 64. High and low gain signals are transmitted to the Digitizer boards, where they are digitized every 25 ns by 10bit Analog-to-Digital Converters (ADC). The Digitizer board is equipped with two depth-configurable pipeline memories in the TileDMU ASIC [14] which store the digitized data until the reception of a L1 accept signal (L1A). Each TileDMU ASIC receives the digitized data from three channels, this is six channels per Digitizer board. Upon the reception of a L1A signal, a data frame containing up to 16 samples is copied into the derandomizer buffers in the Interface board for its transmission to the ROD system in the back-end electronics. In order to reduce the total data bandwidth during the normal operation only one of the two gains, and only 7 samples are read out. The sampling clock is provided by the TTCrx ASIC [15] and can be adjusted collectively for all ADC in a Digitizer board in steps of 106 ps. The phase adjustment of the clock is necessary to ensure that the central sample is near the pulse peak. The motherboard also contains an analog part to provide a voltage reference to the ADCs and two 8-bit Digital-to-Analog Converters (DAC) that provide a pedestal for the AC-coupled inputs. Each super-drawer of the LB contains up to 8 digitizer boards whereas the EB modules contains 6 digitizer boards.

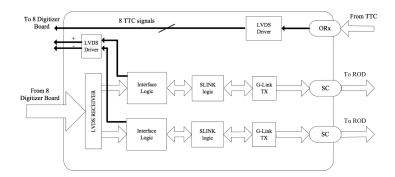

#### Interface board

The Interface board [16] is the digital link with the back-end electronics system. Each module hosts one Interface board which receives and distributes the TTC signals to the electronics, collects and formats data from the digitizer boards, and transmits the digitized data via an optical link to the ROD system. The Interface board implements a redundant readout system with two output fibers to reduce possible errors due to single event upset, though, at a given time, only one of the two fibers is connected to the ROD system. Figure 1.9 shows a block diagram of the Interface board.

Figure 1.9: Block diagram of the functional blocks and data flow of the Interface board.

#### Adder board

The adder boards receive the analog signals from up to six 3-in-1 cards composing a trigger tower and perform an analog sum. Two analog sum results are sent to the L1 trigger system. The first analog sum comprises the sum of all the cells, while the second one only contains the last layer cell.

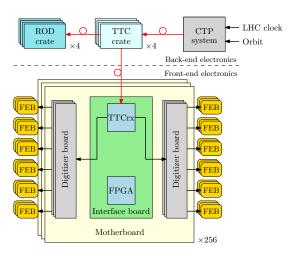

#### **1.3.3** Back-end electronics

The back-end electronics system is installed in the counting rooms of the cavern (USA15), located 70 meters away from the detector and contains two different sub-systems: the Read Out driver (ROD) system and the Trigger, Timing and Control (TTC) system [17]. The back-end electronics is organized in four partitions, each one dedicated to the readout of the Long and Extended Barrels. These units are physically split into different crates: a 6U Versa Module Eurocard (VME) TTC crate and a 9U VME ROD crate.

#### Read Out Driver

The Read Out Driver [18] is the core element of the back-end electronics receiving data from 8 super-drawers through optical links. A total of 32 RODs, divided in four VME crates, one per barrel, are needed to read out the Tile Calorimeter, this is eight RODs per rack. The ROD module is composed of a ROD motherboard and four Processing Units (PU), each populated with two commercial Digital Signal Processor (DSP) chips that process the data before its transmission to the ATLAS DAQ system.

In addition, one Trigger and Busy Module (TBM) is installed per ROD crate. This 9U VME module receives and distributes the TTC signals from the local TTC system to the RODs, and also gathers the busy signals from eight RODs to provide a combined busy signal to the ROD Busy module.

#### Trigger, Timing and Control

The back-end TTC system is installed in four VME crates. Each TTC partition contains a series of VME boards to handle the TTC information in the different subsystems.

- Local Trigger Processor (LTP): the LTP receives the TTC signals from the Central Trigger Processor (CTP) and distributes them to the TTCvi module.

- LTP Interface (LTPI): the LTPI communicates multiple LTP modules with the CTP.

- TTC VME Bus Interface (TTCvi): the TTCvi provides the A and B channel signals to the TTCex for its encoding and distribution to the front-end electronics.

- TTC Emitter (TTCex): the TTCex converts the commands received from the TTCvi to optical signals.

- TTC Optical Coupler (TTCoc): the TTCoc fans out the optical signals up top 320 different destinations.

- ROD Busy module: this module monitors the busy signal, and produces the OR operation of the 16 busy input lines.

Other TileCal-specific modules are also present in the TTC crate, which are primary used for calibration purposes but also receive or handle TTC information.

- Shaft module: it controls the calibration trigger requests. It is primary used to share the calibration request during physics runs.

- TTC Receiver in PCIe Mezzanine Card (TTCpr) module: the TTCpr provides TTC information to the TDAQ software for the calibration runs. This board is attached into the Single Board Computer (SBC) of the TTC crate.

- Laser Read Out Driver: this module provides information from the Laser calibration system to the TDAQ software and distributes TTC signals to the Laser system.

The TTC rack location was chosen to minimize the length of the TTC fibers to the front-end crates and the associated contribution to the trigger latency, understood as the time difference between the bunch crossing identification (BCID) and the arrival time of the L1A signal to the front-end electronics system. In addition, the programmable delay lines of the calibration boards are configured to reproduce the timing of signals generated by particles originated from the interaction point.

#### 1.4 Data flow of the TileCal readout chain

The complete readout process is shown in Figure 1.10. It starts collecting the light generated by particles crossing the TileCal scintillating tiles, and then routing it to the PMTs through WLS fibers. The PMTs convert the light into an electrical analog pulse which is shaped and amplified by the 3-in-1 cards, distributing two copies of the analog signal with a ratio of 1:64. The analog PMT signals are transmitted to the digitizers boards where the signals are digitized at the LHC frequency and stored in the configurable-depth pipeline memories of the TileDMU. In parallel to this operation, the low gain analog signals are summed in groups of five and the result is sent to the L1 trigger system.

Figure 1.10: Block diagram of TileCal readout chain.

In the L1 trigger system, the CTP transmits the L1A signal through the TTC network via the LTP to the front-end electronics requesting the selected events at a mean rate of 100 kHz. When the front-end electronics receives the L1A signal, the TileDMU transmits the samples corresponding to the requested BCID to the Interface board. Then, the Interface board builds up a data fragment containing the samples from all channels in the super-drawer and transmit it to ROD system in the back-end electronics system. The data flow rate is controlled using a busy feedback signal from the back-end electronics to the CTP. The busy signal is generated by the RODs modules when the input buffers are full. This signal is transmitted to the TBM and ROD busy module which distributes it to the CTP, informing that it is not possible to accept new events.

### Chapter 2

# ATLAS Upgrades for HL-LHC

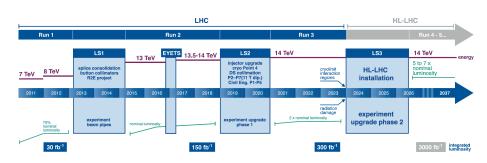

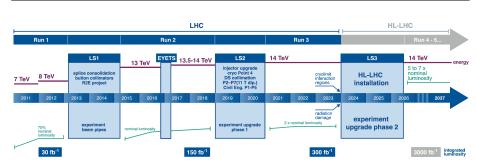

The High Luminosity upgrade of the Large Hadron Collider (HL-LHC) [19] is planned for the Long Shutdown 3 (LS3) period from 2024 to 2026. The HL-LHC will provide a nominal instantaneous luminosity of  $\mathcal{L} = 7.5 \times 10^{34} \text{ cm}^{-2} \text{s}^{-1}$ , 7.5 times the initial design luminosity, with an average of 200 inelastic collisions per bunch crossing. The HL-LHC will deliver an integrated luminosity of  $300-350 \text{ fb}^{-1}$  per year with the goal of  $4000 \text{ fb}^{-1}$  by 2035, about 10 times the integrated luminosity reached with the LHC. The central activity at the HL-LHC will be the measurement of the properties of the recently discovered Higgs boson and, in particular, the studies of the Higgs coupling to the different fermions and bosons, as well as the precise measurement of the trilinear Higgs self-coupling through the observation of di-Higgs production. The HL-LHC will produce high statistics data that will permit the study in detail of the Standard Model and physics Beyond the Standard Model. A temporal overview of the plans for the LHC evolution towards the HL-LHC is given in Figure 2.1.

The complete upgrade of the ATLAS detector [20] is planned in three different phases corresponding to the three long shutdown periods. After LS3, the ATLAS Phase II Upgrade will prepare the different sub-detectors for the HL-LHC luminosity conditions. The pile-up of events per beam crossing in ATLAS will increase from 20 to 200, requiring a finer granularity for the detectors and

#### CHAPTER 2. ATLAS UPGRADES FOR HL-LHC

Figure 2.1: LHC plan for the next ten years, with a series of shutdowns with dedicated upgrades and increase of energy and luminosity.

a new TDAQ architecture able to handle the trigger rates and the amount of generated data. Moreover, the increment of the luminosity will require a new front-end electronics system more tolerant to radiation.

Some detectors, such as the Inner Detector, the LAr Forward Calorimeter and the Forward Muon Wheels will be more affected by the radiation and will require the complete replacement of the current detector and electronics. This is not the case for the calorimeters and muon chambers, where there is no necessity of replacing their structures and active materials. Only an upgrade of the frontend and back-end electronics systems is required in order to cope with the new radiation levels and data bandwidth.

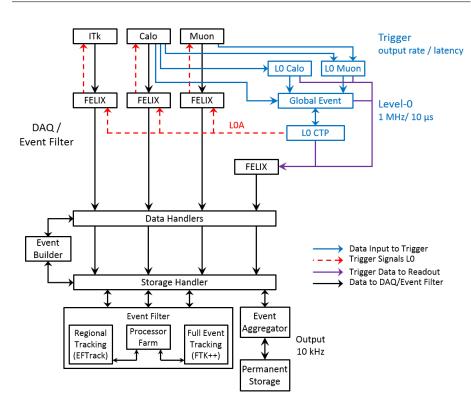

#### 2.1 TDAQ architecture

The TDAQ system will be completely redesigned for the HL-LHC to address the performance requirements in combination with the increased trigger rates and data volumes. The proposed TDAQ for the HL-LHC [21] consists of a single-level hardware trigger stage, called Level-0 (L0) trigger system, and a software system called Event Filter (EF). Figure 2.2 presents a block diagram of the single-level TDAQ architecture for the HL-LHC.

The L0 trigger system receives the information from the LAr and TileCal detectors, and the muon system reducing the trigger rate from 40 MHz to 1 MHz by the application of hardware-based algorithms.

The calorimeters provide coarse granularity data to the L0Calo system to identify electron, tau and jet candidates, and to calculate  $E_T^{miss}$ . In parallel,

Figure 2.2: Block diagram of the single-level architecture envisaged for the TDAQ at the HL-LHC [21].

the L0Muon system receives data from all muon subsystems and from the most external cells of TileCal to identify muons. It also receives information from the Monitoring Drift Tubes (MDT) and RPCs to improve the muon trigger coverage.

The L0Calo and L0Muon systems provide trigger objects with reconstructed energies and spatial locations to the Global Event which combines them into higher level signatures. These signatures are then passed to the Level-0 Central Trigger Processor (L0CTP) which makes the Level-0 decision (LA0) based on several parameters.

Related to the readout path, all detectors transmit the data to a common readout system called Front-End LInk eXchange (FELIX) [22]. This system is used to transmit selected detector data to Level-0 trigger system using low latency point-to-point connections and also to interface the detector electronics with the DCS and TTC systems. The FELIX system sends the event data to the Data Handlers where data is reformatted and then buffered into the Storage Handler before being transmitted to the EF for the application of the last trigger algorithms. The Storage Handler buffers the event data while the EF is processing the events between fills. In the last stage of the trigger architecture, the EF makes the final trigger decision using software algorithms at a rate of 10 kHz.

The TDAQ collaboration is also considering a second option: an architecture with two hardware levels (Level-0 and Level-1), where the L0 trigger rate reaches 4 MHz and the Level-1 (L1) trigger system implements more complex algorithms reducing the event rate to 800 kHz.

In order to fulfill the latency requirements imposed by the new TDAQ system and adding a margin for future developments, the detectors will implement large pipeline memories to store  $10 \,\mu$ s of data for Level-0 and  $35 \,\mu$ s for Level-1 (in the case of a L0/L1 trigger architecture). The latency, trigger and data rates between the detector readout and the trigger systems for both architecture options are summarized in Table 2.1.

|                                   | L0 schema           | L0/L1 schema                          |

|-----------------------------------|---------------------|---------------------------------------|

| L0/L1 trigger rate                | $4\mathrm{MHz}$     | $4 \mathrm{MHz}$ / $800 \mathrm{kHz}$ |

| L0/L1 latency                     | $10\mu{ m s}$       | $10\mu{ m s}~/~35\mu{ m s}$           |

| Data rate to L0Calo and L0Muon    | $40.08\mathrm{MHz}$ | $40.08\mathrm{MHz}$                   |

| Latency data to L0Calo and L0Muon | $1.7\mu{ m s}$      | $1.7\mu{ m s}$                        |

| Data rate to FELIX                | $1\mathrm{MHz}$     | $800\mathrm{kHz}$                     |

| Latency data to FELIX             | $10\mu{ m s}$       | $35\mu{ m s}$                         |

Table 2.1: Trigger parameters and readout data rates for the two proposed TDAQ architectures.

#### 2.2 Tile Calorimeter Upgrade

The motivation for the upgrade of the Tile Calorimeter is to fulfill the new requirements set by the HL-LHC. The complete replacement of the readout electronics is foreseen for the Phase II Upgrade [20] in order to meet the increased radiation tolerance requirements and to be compatible with the TDAQ architecture, providing more precise and higher granularity information to the trigger systems.

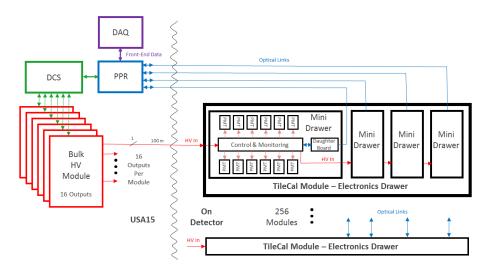

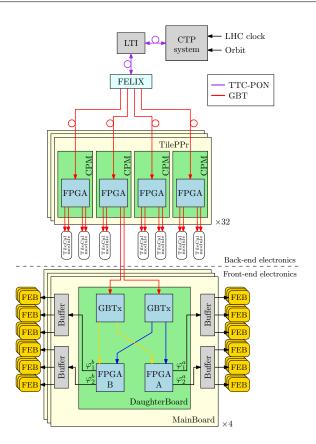

In the proposed TDAQ architecture the back-end electronics system will readout the detector and transmit pre-processed data from cells to the trigger system at the LHC frequency. In parallel to the data processing for the trigger system, the data samples will be stored in pipeline memories until the reception of a Level-0/Level-1 acceptance signal. A block diagram of the upgraded readout architecture is shown in Figure 2.3.

Figure 2.3: Block diagram of the TileCal readout architecture for the Phase II Upgrade.

The new TDAQ architecture requires a considerable increase in bandwidth and number of links between the front-end and back-end electronics systems, in addition to the use of high-speed links between the back-end electronics and trigger systems. While with the current system the detector is read out through 256 optical links with a bandwidth of 800 Mbps for each link, the new readout architecture requires 4096 optical links (including redundancy) transmitting at 9.6 Gbps per link.

Table 2.2 summarizes the main features of the current and the Phase II Upgrade readout systems.

| Downlinks                | Current          | Phase II              |

|--------------------------|------------------|-----------------------|

| Nbr. of links            | 256              | 2048                  |

| Link bandwidth           | 80 Mbps (TTC)    | 4.8 Gbps              |

| Uplinks                  | Current          | Phase II              |

| Nbr. of links            | 256              | 4096                  |

| Link bandwidth           | $800 { m ~Mbps}$ | $9.6 { m ~Gbps}$      |

| Nbr. of readout boards   | 32 (ROD)         | 32 (TilePPr)          |

| Nbr. of crates           | 4 (VME)          | 4 (ATCA)              |

| BW to DAQ per module     | 3.2  Gbps (ROS)  | 40 Gbps (FELIX)       |

| BW to Trigger per module | Analog           | $\sim 500 { m ~Gbps}$ |

Table 2.2: Comparison between the current and Phase II readout systems.

#### The Demonstrator module

In parallel with the developments of the readout electronics for the HL-LHC, the Demonstrator project aims to evaluate and qualify the upgraded trigger and readout electronics before the complete replacement of the electronics after the Phase II Upgrade.

A Demonstrator module containing the upgraded front-end electronics was developed in the framework of the project. It combines the Phase II readout electronics with the legacy analog interface for the L1 trigger system since the full digital trigger system will not be installed before the Phase II Upgrade. In the back-end electronics, a Tile Preprocessor (TilePPr) prototype will read out and operate the Demonstrator module. The TilePPr will store the samples in pipeline memories and transmit L1 selected data to the ROD modules keeping backward compatibility with the current DAQ system. The Demonstrator module will replace one of the super-drawers into the ATLAS experiment. The installation of the Demonstrator module into the ATLAS experiment is foreseen during one of the short LHC shutdowns planned for the Run 2.

#### 2.2.1 Front-end electronics

The front-end electronics comprise the set of electronic equipment, boards and devices dedicated to the data readout and operation of the PMTs which are hosted in the TileCal modules. The electronics will be housed inside four aluminum structures per module, called minidrawers, placed in the outermost part of the detector. The mechanical design of the super-drawers has been modified to organize the front-end electronics in four independent modules improving the access and serviceability, and reducing the impact of the single point failures. Figure 2.4 shows the mechanical structure of the TileCal detector and how the super-drawers have been organized in minidrawers.

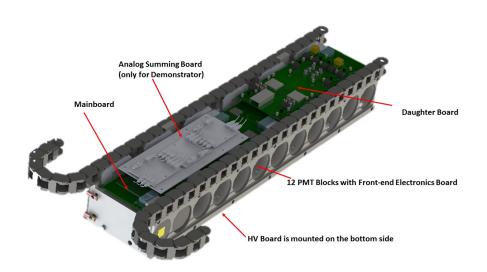

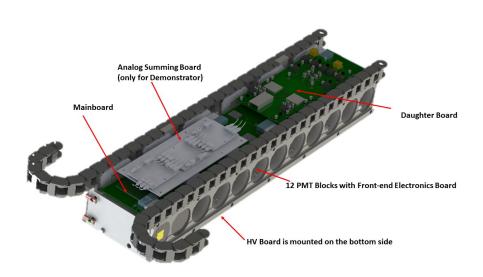

As is shown in Figure 2.5, each minidrawer houses up to 12 PMTs together with its corresponding Front-End Boards (FEB), one High Voltage board to distribute power to the PMTs, one MainBoard (MB) which receives the PMT signals and one DaughterBoard (DB) which interfaces with the back-end electronics.

#### 2.2. TILE CALORIMETER UPGRADE

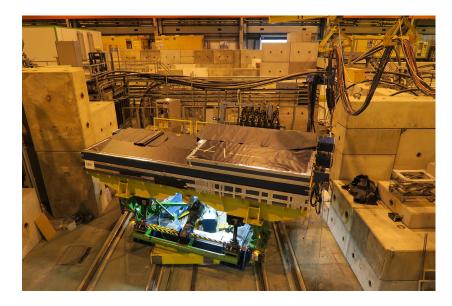

Figure 2.4: Picture of the TileCal modules and the minidrawers.

#### **DaughterBoard**

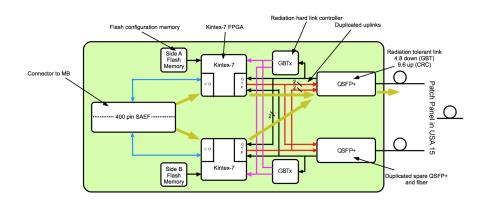

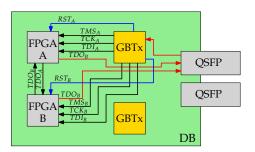

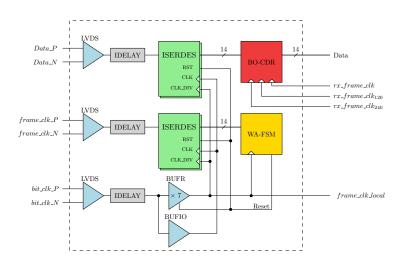

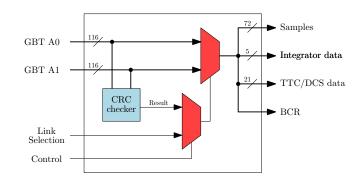

The DaughterBoard [23] provides a high-speed communication path between the front-end electronics and the TilePPr modules in the counting rooms (USA15). In the upgrade electronics, the DBs will be responsible for the reception and execution of configuration commands for the front-end electronics, as well as for collecting and transmitting the digitized signal from the PMTs to the TilePPr. In addition, the DBs will distribute the recovered LHC clock to the FEBs for the digitization of the PMT signals. Figure 2.6 depicts a block diagram with the main components of the DaughterBoard.

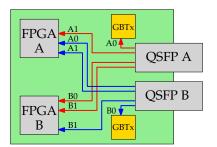

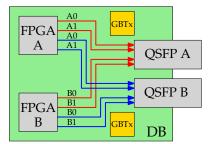

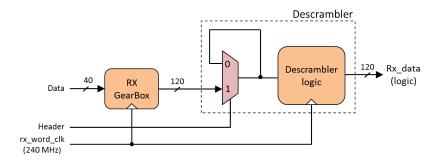

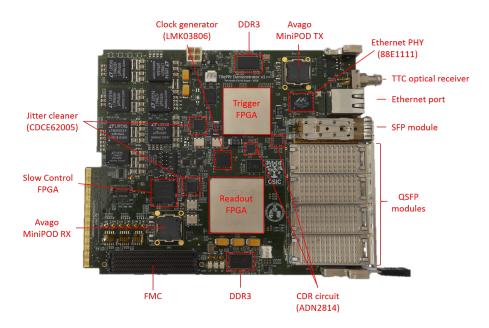

The DaughterBoard version 4 (Figure 2.7) was used during the 2015-2017 testbeam periods and will be integrated into the Demonstrator module. The DB version 4 fulfills all the requirements of the HL-LHC and is compatible with the three FEB options that will be presented in next sections. The DB was designed in two independent halves, corresponding to A and B sides, where each half serves 6 PMTs on one side of the minidrawer. The DB is populated with two Xilinx Kintex 7 Field Programmable Gate Arrays (FPGA) connected to two Quad Small Form-factor Pluggable (QSFP) modules. These connections provide a redundant high-speed communication with the back-end electronics.

Figure 2.5: Detailed drawing of the minidrawer indicating the position of the different parts of the front-end electronics.

Each side of the DB includes one GBTx [24] chip per side which recovers the LHC clock and distributes it to the FPGA for the operation of the front-end electronics and communication with the back-end electronics. In addition, the GBTx also provides remote reset and configuration capabilities. Both FPGAs are connected to the GBTx through LVDS buffers forming two independent JTAG chains. The JTAG chain is closed transmitting the TDO signal to the back-end electronics using the FPGA not being programmed, and therefore only one FPGA can be programmed at a time. Although during the normal operation of the module the FPGAs will be configured from the on-board flash memories, the remote programming enables the possibility of programming the FPGAs if the flash memory is damaged or updating the firmware version in the flash memories.

A DB is connected to a MainBoard through a 400-pin FMC connector. This connector provides a high-speed path to receive the PMT digitized data and to configure and operate the FEBs. Related to the power distribution, each side of the DB is individually powered with 10 V from the MainBoard.

Different techniques will be implemented in the FPGA to prevent errors due to Single Event Upsets (SEU) or Multi Event Upsets (MEU). One of these techniques is the memory scrubbing where the FPGA configuration memory

Figure 2.6: Block diagram of the DaughterBoard.

Figure 2.7: Picture of the DaughterBoard version 4.

is continuously checked and corrected if possible. For those cases where the memory integrity cannot be recovered the DB will be remotely reset or reprogrammed. Moreover, the Triple Modular Redundancy (TMR) will be implemented in firmware to reduce the likelihood of data errors due to SEU or MEU.

#### MainBoard

The MainBoard [25] controls the FEBs and also provides a high-speed path to transmit digitized PMT signals to the DaughterBoard. Depending on the FEB option the MainBoard could also include circuitry to digitize the signals coming from the FEBs. In this thesis, the MainBoard for the 3-in-1 option is covered in detail since it is used in the Demonstrator module.

#### 3-in-1 front-end boards

The upgraded 3-in-1 FEB [26] is a revised version of the current FEB installed in ATLAS. This new FEB is composed of COTS components. It features dynamic range of 17 bits, better linearity and lower noise than the previous version. Functionality of the FEB includes: the fast signal processing chain, the slow signal processing chain and the calibration circuitry. Figure 2.8 shows a picture of the upgraded 3-in-1 card.

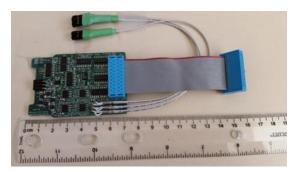

Figure 2.8: A 3-in-1 card designed for the HL-LHC.

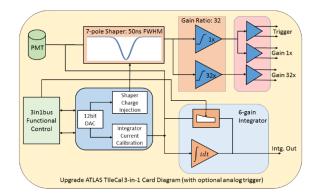

Figure 2.9 presents a block diagram of the functional blocks of the 3-in-1 card. The fast signal processing chain includes a 7-pole passive LC shaper to transform a PMT pulse into a wider pulse. The wide pulse is amplified with two clamping amplifiers with a gain ratios of 1 and 32, providing the so-called high and low gain signals. The amplified signals are routed to MainBoard where they are digitized with on-board dual-channel 12-bit ADCs. The slow signal processing chain includes a 6-gain programmable slow integrator. It is used to monitor the average PMT currents for Cesium detector calibration, and monitoring of instantaneous luminosity. The precise charge injection circuit is connected to the shaper. Charge injection procedure is used to calibrate each readout channel and response of the amplifiers and ADCs, as well as the integrator circuit.

The 3-in-1 card was selected for the Demonstrator module since it is backwardcompatible with the present analog trigger. A 3-in-1 card can provide analog signal to the L1 calorimeter trigger system (L1Calo). If inserted into the AT-LAS detector before the HL-LHC upgrade, the Demonstrator will provide analog trigger sums to the L1Calo system.

Figure 2.9: Functionality of 3-in-1 card for the upgrade of the TileCal detector.

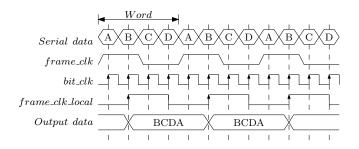

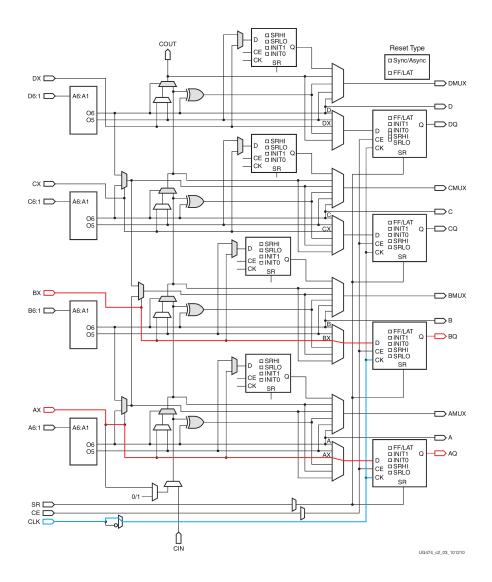

The 3-in-1 MainBoard circuit (Figure 2.10) is divided in four sections each controlled by an Altera Cyclone IV FPGA. A section contains the required circuitry to control and read out three PMTs for a total of twelve PMTs per MainBoard. Each FPGA controls three dual-channel ADCs for digitizing the PMT signals at 40 Msps, six DACs for control the bias voltage levels applied to the ADC inputs and three ADCs for sampling the integrators at 50 kSps. All the control and data lines are routed to the DaughterBoard via the FMC connector. The Cyclone FPGAs are accessed from the DaughterBoard via an SPI interface, while digitized PMT signals are sent directly from the ADCs to the DaughterBoard using LVDS lines at 560 Mbps. Also two I<sup>2</sup>C buses (one per side) are dedicated for the read out of the integrator ADCs.

Figure 2.10: Picture of both sides of the MainBoard for the 3-in-1 FEB option.

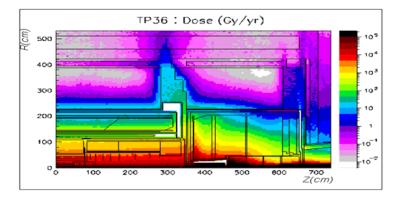

In the same way as the DaughterBoard, this MainBoard is divided in two halves called A and B sides. Each side has its own power distribution, where the Schottky diodes connecting both sides prevent power failures in case of malfunctioning of one of the fLVPS bricks. Even if one side of a minidrawer fails completely, all PMTs on the opposite side can still be read out. The steel structure of the TileCal modules acts as a good radiation shield, where the end of the module close to the patch panel is exposed to a higher rate of radiation. A simulated map of the radiation dose for the ATLAS is shown in Figure 2.11. Based on this map, the voltage regulators and FPGAs were placed where the radiation is lower.

Figure 2.11: Simulated radiation dose in ATLAS after  $100 \text{ fb}^{-1}$ , being  $1/40^{\text{th}}$  of the total integrated luminosity expected for the HL-LHC [27].

#### QIE FEB

The core of the second FEB design is a Charge (Q) Integrator and Encoder (QIE) chip [28]. This custom ASIC digitizes the analog PMT signals with a constant resolution and no dead-time, covering a dynamic range of about 18 bits. In opposition to the other two FEB designs, the QIE does not perform any pulse shaping, but integrates the PMT current for every tick of the LHC clock so pileup-related noise is reduced.

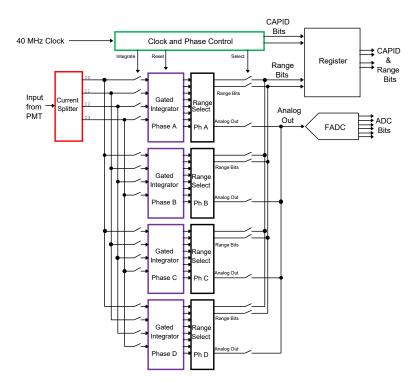

Figure 2.12 depicts a block diagram of the main blocks of the QIE. The first stage of the QIE consists of a current splitter dividing the PMT current into fixed fractions. Then the output of the splitter is time-multiplexed between four gated integrators at 40 MHz and digitized with a flash ADC. The total acquisition time of the QIE corresponds to a latency of four clock cycles due to its pipelined operation. In addition, the QIE includes a fixed-threshold Time to Digital Converter (TDC) which is used to measure the time position of rising edge of the PMT pulses. The QIE FEB includes a calibration circuitry to calibrate the system with a Cesium source and current injection. The QIE outputs data through 8 LVDS outputs at 80 Mbps which constitutes of a 9-bit floating point word for the digitized charge, 2 bits to identify the gated integrator, and 5 bits for the TDC data.

Figure 2.12: Block diagram describing the operation of the main modules of the QIE chip [27].

The QIE MainBoard is the least complex of the three types of MainBoards. It handles point-to-point LVDS signals for controlling purposes and to read out the QIE FEBs. Due to the limited number of pins in the FMC connector of the DaughterBoard v4, the MainBoard includes CPLDs to multiplex the SPI bus between the DB and the FEBs required for the control of the FEBs.

#### FATALIC FEB

The third FEB design relies on an ASIC called the Front end for ATLAS TileCal Integrated Circuit (FATALIC) [29]. FATALIC includes a multi-gain current conveyor which splits the input signal into three ranges with different gains (1, 8, 64) covering the full dynamic range of the PMT signal. Each current conveyor output is followed by a shaper and the readout chain is completed with a 12-bit ADC operating at 40 Msps. The FATALIC chips transmit two gains: the internal logic performs the auto-selection between high and low gain while the medium gain is always transmitted. In addition, FATALIC also includes a slow integrator circuit to measure the minimum bias current of the PMT during the operation and to calibrate the detector with a Cesium source. The circuitry for the CIS calibration is located in the FEBs.

The FATALIC MainBoard is based on the 3-in-1 MainBoard including four Altera Cyclone IV. Each FPGA is associated to three channels and serializes the parallel data provided by the FATALIC FEBs, transmitting the result to the DaughterBoard through the FMC connector. In addition, the MainBoard also provides the clock to the FEBs, and interfaces with the DaughterBoard to receive the configuration commands.

#### 2.2.2 Power supplies

#### Low Voltage Power Distribution

The low voltage power is distributed to the front-end electronics using a threestage power distribution system. The upgraded low voltage schema is largely based on the current version, due to the reliable operations of the current power supplies.

The 200 V power supplies installed in USA15 racks distribute power to the finger Low Voltage Power Supplies (fLVPS) [30] [31] located in the extreme end of each module. Each fLVPS includes 8 buck converters designed with COTS components, called bricks, to deliver 10 V to the MainBoards and Daughter-Boards. Each minidrawer is powered with two bricks for double-redundancy, using the OR-diode circuit in the MainBoard. Extra effort has been made to make the fLVPS bricks radiation-tolerant with special focus on SEU. The fLVPS bricks are controlled and monitor through the DCS system.

The Point Of Load (POL) regulators of the front-end electronics comprise the third stage of the LV power distribution system. The POL regulators convert 10 V to the required voltage for the different electronic components. The POL regulators were selected to provide low-noise and were qualified for the operation with the TileCal radiation levels.

#### High Voltage Power Distribution System

The High Voltage Power distribution System (HVPS) controls and monitors the voltages applied to the almost 10,000 PMTs via the DCS system. The TileCal community is developing two different approaches for the high voltage distribution: the HV remote [32] and the HV internal [27]. Both approaches have in common that the high voltage power supplies are placed away from the detector in USA15. The difference is the location of the high voltage regulation and control circuits.

#### HV remote

In this approach, the control and monitoring electronics will be located away from the detector, in USA15, and each PMT will receive high voltage independently via two long wires. Individual wires will be combined into cables. This implementation is shown in Figure 2.13.

Figure 2.13: Block diagram of the remote HV power distribution system [27].

The high voltage control circuit of the remote HVPS is an improved version of the currently used HVPS during Runs 1 and 2. The first version is capable of delivering HV to groups of 12 channels corresponding to an entire minidrawer where each channel could be controlled individually.

Continuing with the developments of the HV remote system, the local electronics boards used to control and monitor voltages will be replaced with commercial computers that interface with the HV remote system through Ethernet. The second version of the HV remote system will be able to provide high voltage to 24 channels per high HV board, for a total of 512 boards for the complete detector.

One of the advantages of the HV remote system is that no radiation tolerant electronics is needed and the access to the HV boards for maintenance will be easy since the electronics will be located in USA15. The disadvantage is that the system needs almost 10,000 long wires.

#### HV internal

The HV internal system implements a different schema where the high voltage is sent directly to each module through a common high voltage cable. In the front-end electronics, each DaughterBoard is connected to one HVOpto board that regulates and monitors the voltage applied to 12 PMTs. Figure 2.14 shows a block diagram of the HV internal system.

Figure 2.14: Block diagram of the internal HV power distribution system [27].

The HV bulk power supply in the counting rooms provides high voltage to four minidrawers in parallel through a single coaxial cable. The core of the HV Opto board is a Maxim Integrated MAX1329 chip which features 16 multiplexed analog inputs connected to an ADC, 2 DACs and GPIOs. The DCS system sets the high voltage individually for each PMT by transmitting commands to the DaughterBoards through the TilePPrs. The DaughterBoards receive and store the applied voltages digitized by the ADC of the MAX1329 chip. The MAX1329 chips are read out through an SPI interface. The DaughterBoards collect the monitoring data and transfers it to the DCS system through the TilePPr.

The advantage of the HV internal option is the reduction in the number of high voltage cables (where only one per four minidrawers is needed), at the expense of a more difficult maintenance of the HV system due to the limited access to the detector.

#### Active dividers

The passive HV dividers employed to distribute the high voltage to the PMT dynodes were redesigned to fulfill the HL-LHC requirements. The legacy HV dividers are implemented with a resistive network that provides non-linearities below the 1% with the small anode currents generated with the current luminosity. The new HV dividers [33] were designed with active components (transistors) to provide a constant gain independently of the anode current at the HL-LHC where the anode currents will be larger for some cells due to the higher pulse rates.

#### 2.2.3 Back-end electronics

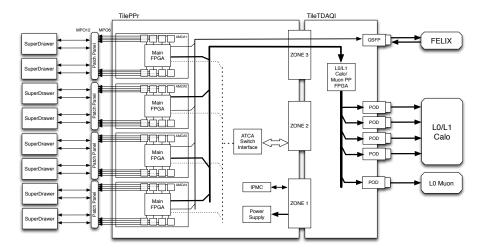

The upgraded back-end electronics system will be, as the current version, located in USA15 racks, 70 meters away from the detector. The Phase II Tile back-end electronics consist of two different systems: the Tile PreProcessor modules and the Trigger and DAQ interface (TDAQi) boards. The Tile back-end electronics system is based on the Advanced Telecommunications Computing Architecture (ATCA) specifications [34]. The ATCA framework provides a commercially and standardized platform for high-speed serial interconnects on the backplane supporting different I/O interfaces.

#### **Tile PreProcessor module**

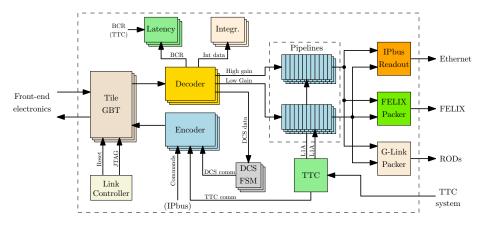

The Tile PreProcessors [35] will be first and main element in the back-end electronics. It will be responsible for the reception and processing of the digital data coming from the TileCal modules. They will also distribute the DCS and TTC information for synchronization with the LHC clock to the front-end electronics.

The TilePPr modules will transmit selected data, integrator data and DCS information to the FELIX system. It will also provide reconstructed energy and time per cell to the TDAQi boards. On the other hand, the FELIX system will transmit the LHC clock, TTC commands and DCS configuration to the TilePPr modules to distribute it to the on-detector electronics.

The TilePPr module will be designed as a full size ATCA blade following the ATCA specifications, where the interfaces with the other ATCA boards in the same shelves will be achieved through three backplane connectors in locations called Zone 1 to 3.

- Zone 1 connector provides slow control paths for the shelf management and the power connection.

- Zone 2 connector routes the different data paths between the TilePPr module and the different ATCA blades connected in the same shelf.

- Zone 3 connector provides high-speed point-to-point connections to QSFP connectors in the TDAQi to communicate with the FELIX system and to the PreProcessing Trigger (PPT) FPGA.

The TilePPr module will be composed of an ATCA carrier board with four Advanced Mezzanine Card (AMC) [36] slots to host the Compact Processing Modules (CPM). The ATCA carrier will provide power to the CPMs, as well as, the basic interfaces for the communication with other systems through the backplane.

The CPMs will be designed with a single AMC form factor and will be populated with one FPGA and high-speed optical modules to implement all the required functionalities. The FPGA and optical modules will be selected to provide the CPM with the capability to read out and operate up to 8 minidrawers (two of the current TileCal modules). Therefore 32 TilePPr modules will be required for the complete readout of the TileCal detector.

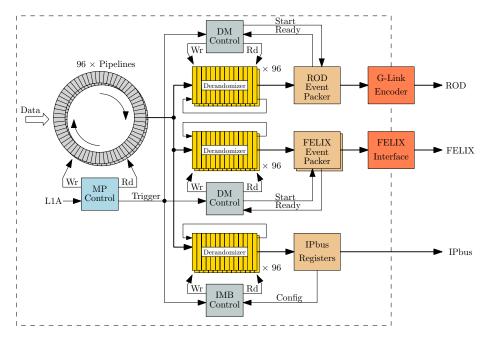

During the operation, the TilePPr modules will distribute LHC clock, TTC commands and DCS configuration to the front-end electronics. Furthermore, the CPM FPGAs in the TilePPr module will compute the reconstructed energy and time per cell and bunch crossing, transmitting them to the TDAQi board. At the same time, the CPM FPGAs will store the received samples in pipelined memories until the reception of a L0/L1 acceptance signal. When this happens, the selected data will be extracted from the memories, formatted and transmitted to the FELIX system. Figure 2.15 presents a block diagram of the TilePPr and TDAQi boards for the Phase II Upgrade.

Figure 2.15: Block diagram of the final TilePPr and TDAQi designs.

#### Tile PreProcessor prototype

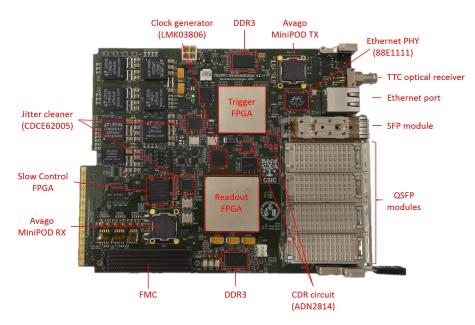

The TilePPr prototype is the first iteration of the final TilePPr module. It is the main element of the back-end electronics system in the Demonstrator project, providing compatibility with the upgraded front-end electronics system and the current DAQ system. It is capable of operating up to four minidrawers (one complete TileCal module), and therefore represents one eighth of the final design.

The first prototype includes all the components required to receive and process data from the Demonstrator module, as well as to decode and distribute TTC signals to the front-end electronics for configuration and synchronization with the LHC clock. It also interfaces with the DCS system to control and monitor the high voltage distribution to the PMTs.

Furthermore, this prototype serves as a testbench for the development of trigger pre-processing algorithms that will be implemented in the TDAQi board after its installation in the HL-LHC.

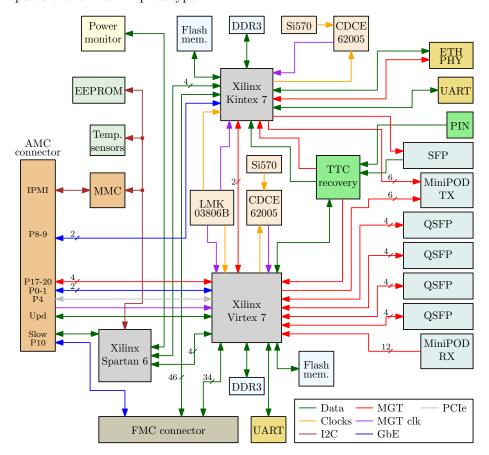

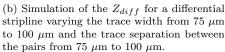

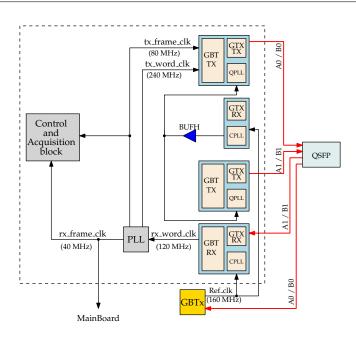

The core processing of the TilePPr prototype relies on two high-performance FPGAs connected to four QSFP optical modules. The TilePPr prototype was designed as a double mid-size AMC board that can be operated in an ATCA carrier or in a  $\mu$ TCA shelf. Chapter 3 is devoted to the TilePPr prototype design, describing it in detail, and Chapters 4 and 5 cover the integration and operation of the TilePPr within the Demonstrator module.

#### Trigger and DAQ interface

The Trigger and DAQ interface [37] board will be the interface between the TilePPr module and the ATLAS TDAQ system. The TDAQi will be designed as an ATCA Rear Transition Module (RTM) [38] and will be powered and operated from the TilePPr module through the Zone 3 connectors.

The PPT FPGA in the TDAQi will compute trigger objects with different granularity and energy resolution with the data provided by the TilePPr modules. The trigger data will be transmitted to the trigger systems through the optical links using a protocol with low, fixed and deterministic latency. In addition, the TDAQi will provide a point-to-point path between the TilePPr module and the FELIX system through a QSFP module placed in the TDAQi board.

## Chapter 3

# Design of the TilePPr prototype

The TilePPr will be the first element and the main readout component of the back-end electronics in the Tile Calorimeter after the Phase II Upgrade. It will also provide the sampling clock and the configuration to the front-end electronics. This chapter gives a detailed description of the design of the TilePPr prototype for the Demonstrator project. The system requirements, component selection, PCB layout design and hardware test verifications are covered in this chapter.

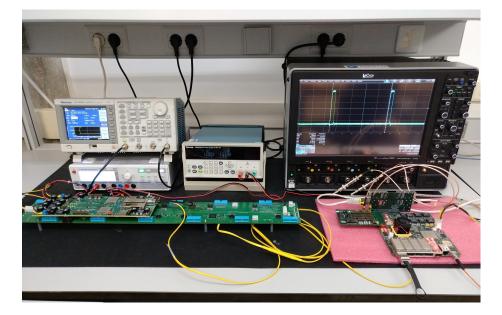

## 3.1 Specifications of the TilePPr prototype

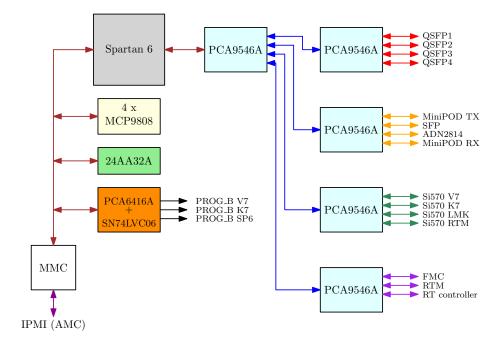

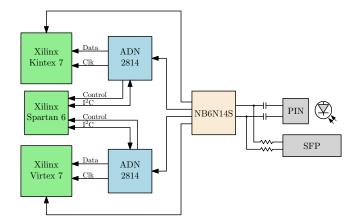

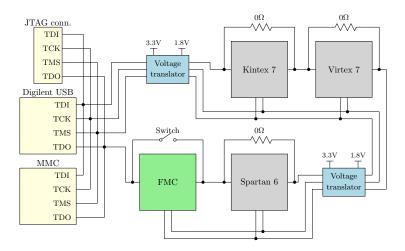

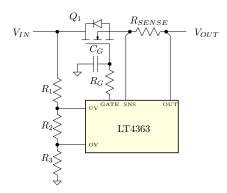

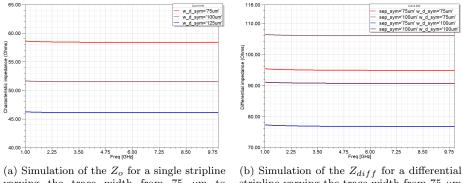

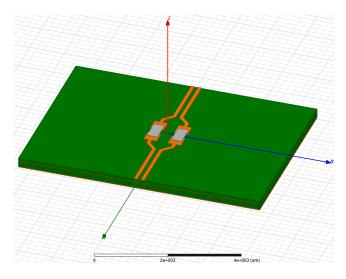

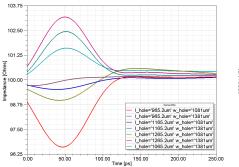

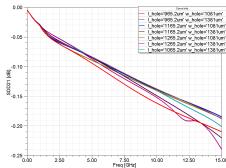

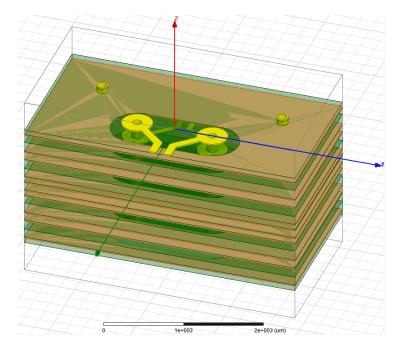

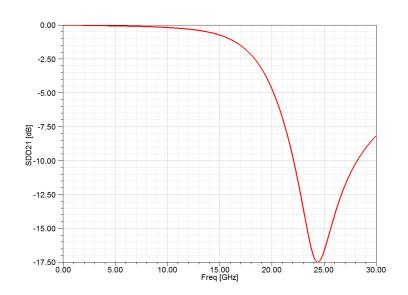

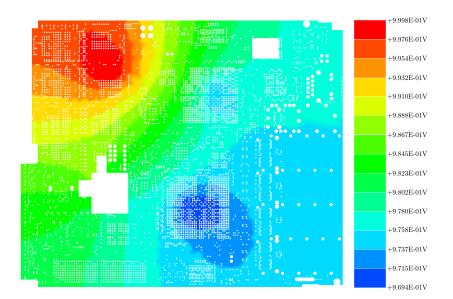

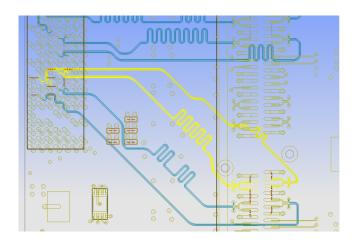

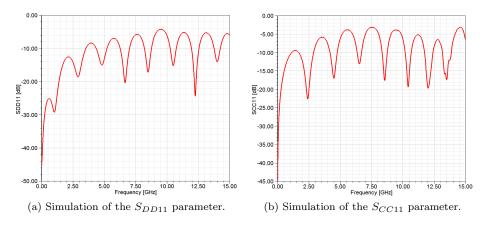

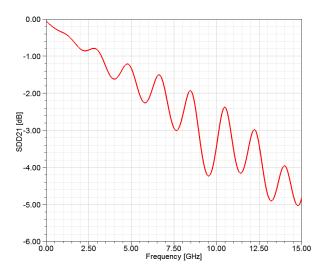

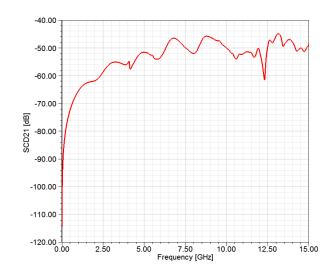

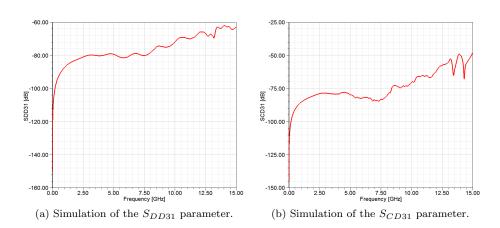

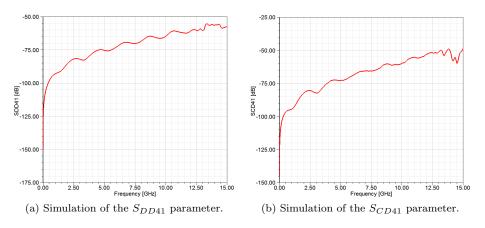

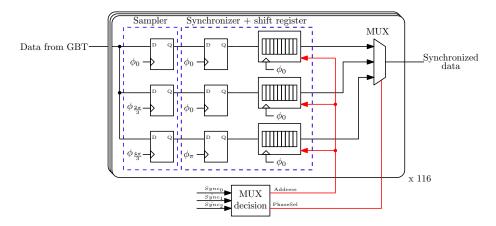

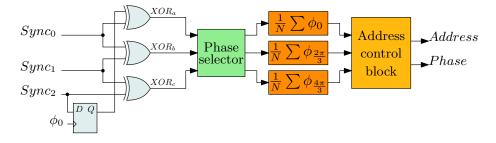

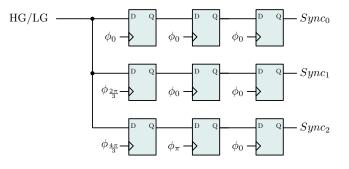

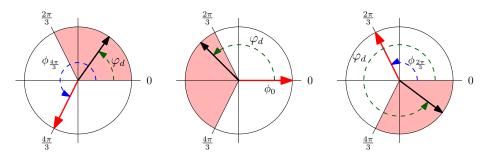

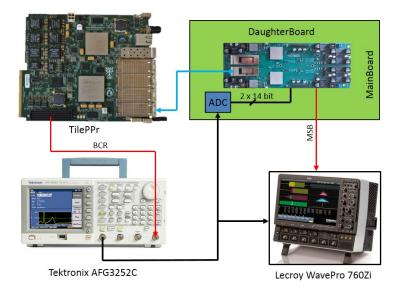

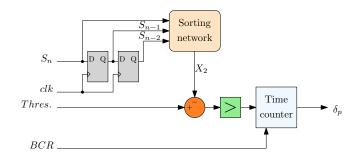

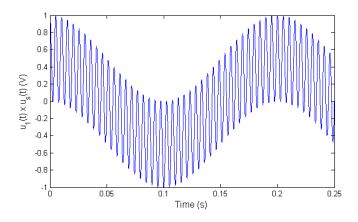

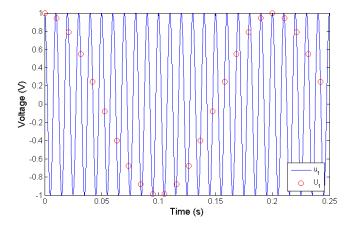

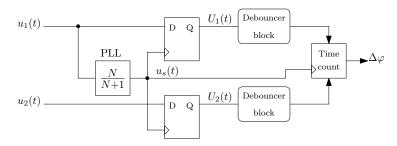

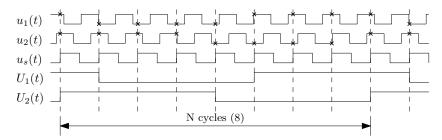

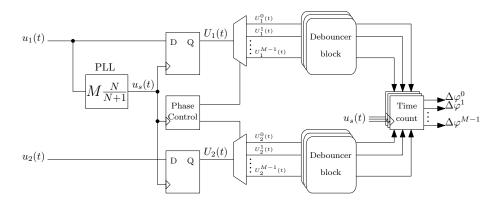

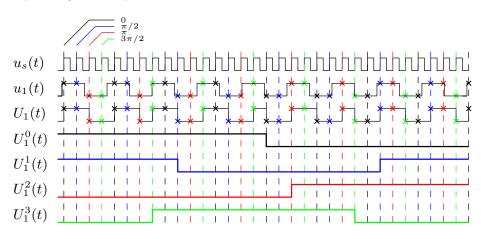

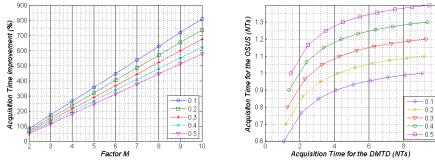

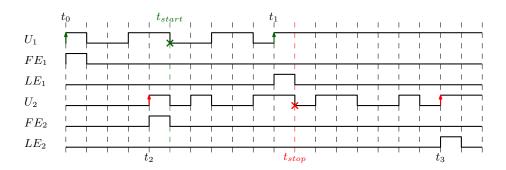

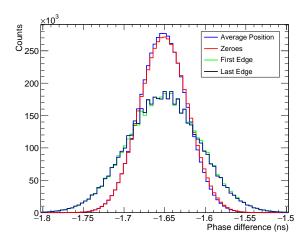

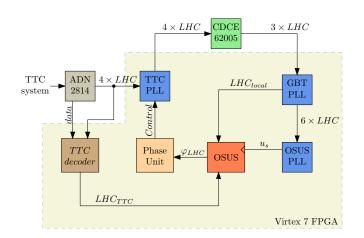

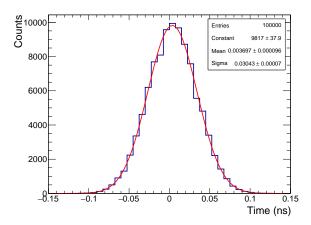

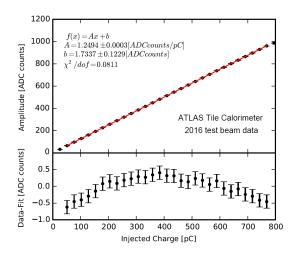

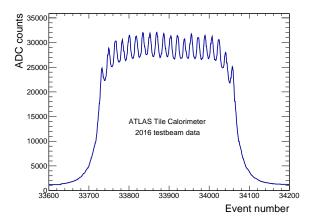

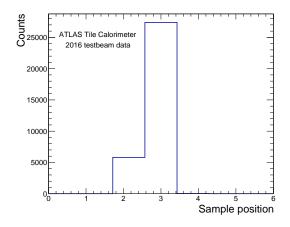

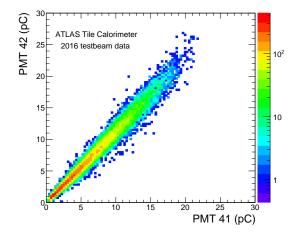

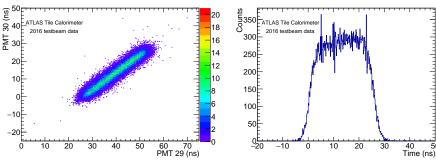

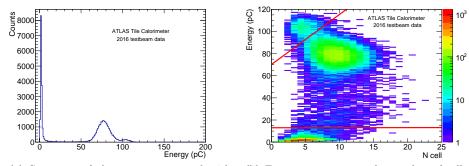

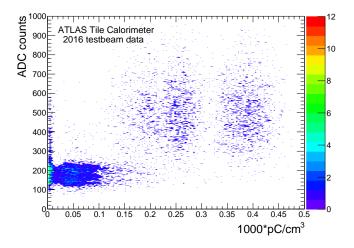

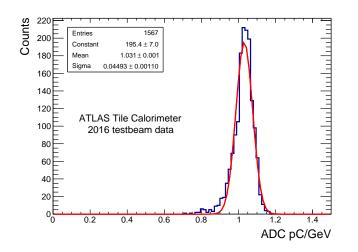

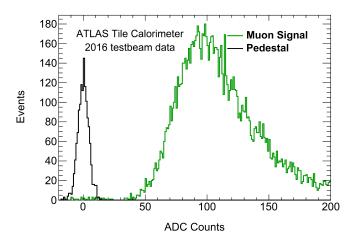

The core of this thesis is the design of the first prototype of the TilePPr for the HL-LHC. The designed prototype is a key element in the Demonstrator project that aims to validate the proposed readout architecture for the Phase II Upgrade, as has already been discussed in Chapter 2.