University of Latvia Faculty of Computing

Uldis Locans

# Future Processor Hardware Architectures for the Benefit of Precise Particle Accelerator Modeling

Doctoral Thesis Field: Computer Science Subfield: Programming languages and systems

> Scientific advisors Dr.sc.comp., prof. Guntis Barzdins Dr. Andreas Adelmann (PSI) Dr. Andreas Suter (PSI)

> > Riga, 2017

# Acknowledgements

I would like to thank my supervisors prof. Dr. Guntis Barzdins, Dr. Andreas Adelmann and Dr. Andreas Sutter for their support and guidance during this work.

I thank the co-authors Jannis Fischer, Werner Lustermann, Gunther Dissertori, Quilin Wang, Xu Xaisheng and Lukas Stingelin for their help and expertise during our interesting collaborations.

I thank my colleagues at PSI AMAS and LEM groups - it has been a real pleasure working and collaborating with all of you.

Many thanks go to my parents, family and friends for their continuous help and support trough-out this time.

This work was carried out in Paul Scherrer Institut during years 2014-2017 as a collaboration between Accelerator Modeling and Advanced Simulations (AMAS) group and Low-Energy Muon (LEM) group.

This study was financially supported by AMAS and LEM groups at PSI, as well as by Prof. Peter Arbenz group at ETH Zurich and Prof. Gunther Dissertori group at ETH Zurich.

This work was in part supported by the Latvian State research program SOPHIS

# Abstract

Emerging processor architectures such as graphical processing units (GPUs) and Intel Many Integrated Cores (MICs) provide a huge performance potential for high performance computing. However developing software that uses these hardware accelerators introduces additional challenges for the developer. These challenges may include exposing increased parallelism, handling different hardware designs, and using multiple development frameworks in order to utilize devices from different vendors.

During this work the Dynamic Kernel Scheduler (DKS) was developed, to provide a software layer between the host application and hardware accelerators. DKS handles the communication between the host and the device, schedules task execution, and provides a library of built-in algorithms. Algorithms available in the DKS library will be written in CUDA, OpenCL, and OpenMP. Depending on the available hardware, the DKS can select the appropriate implementation of the algorithm.

The author used DKS to enable co-processor usage in applications such as OPAL (Object-oriented Particle Accelerator Library), musrfit and PET (Positron Emission Tomography) Image reconstruction application. These applications are developed at Paul Scherrer Institut, and ETH Zurich for particle accelerator modeling and experimental data analysis, and used by the world wide user community. The achieved results show that substantial speedups in application execution times can be achieved using co-processors compared to CPUs and with the help of DKS the process of integrating new processors in existing applications is simplified and more maintainable. The potential of the new hardware architectures is further demonstrated by porting to CUDA application for multibunch tracking (mbtrack) developed at SOLEIL (French national synchrotron facility). This application is used at PSI for the detailed study of coupled bunch instabilities and transient beam-loading. By using the computational power of GPUs the necessary simulations can be executed on the GPU instead of a larger computing cluster that would be required otherwise.

**Keywords:** Hardware acceleration, GPU computing, Intel MIC, CUDA, OpenCL, OpenMP

# Contents

| $\mathbf{C}$ | onter  | nts                                                                  | iv   |

|--------------|--------|----------------------------------------------------------------------|------|

| Li           | ist of | Figures                                                              | viii |

| Li           | ist of | Tables                                                               | xi   |

| N            | omer   | nclature                                                             | xi   |

| 1            | Intr   | roduction                                                            | 1    |

|              | 1.1    | Research background and motivation                                   | 1    |

|              | 1.2    | Novelty of the work                                                  | 2    |

|              | 1.3    | Thesis and research questions                                        | 4    |

|              | 1.4    | Research methodology                                                 | 5    |

|              | 1.5    | The aim and tasks of the research                                    | 5    |

|              | 1.6    | Main results of the thesis and approbation of the results $\ldots$ . | 6    |

|              | 1.7    | Publications of the research results                                 | 7    |

|              | 1.8    | Outline of the thesis                                                | 9    |

| <b>2</b>     | Fut    | ure hardware architectures                                           | 11   |

|              | 2.1    | GPU Accelerated Computing                                            | 11   |

|              |        | 2.1.1 GPU Architecture                                               | 11   |

|              |        | 2.1.2 CUDA                                                           | 12   |

|              |        | 2.1.3 OpenCL                                                         | 14   |

|              | 2.2    | Intel Many Integrated Cores                                          | 15   |

|              |        | 2.2.1 Intel MIC architecture                                         | 15   |

|              |        | 2.2.2 OpenMP and vectorization                                       | 16   |

|          |     | 2.2.3   | OpenCL                                                                                           | 17 |

|----------|-----|---------|--------------------------------------------------------------------------------------------------|----|

|          | 2.3 | Hardw   | vare accelerators                                                                                | 18 |

|          |     | 2.3.1   | Hardware accelerators used during this work $\hdots$                                             | 18 |

| 3        | Dyı | namic I | Kernel Scheduler                                                                                 | 19 |

|          | 3.1 | Accele  | erator libraries                                                                                 | 19 |

|          |     | 3.1.1   | ArrayFire                                                                                        | 19 |

|          |     | 3.1.2   | Thrust $\ldots$ | 20 |

|          |     | 3.1.3   | Boost.compute                                                                                    | 22 |

|          |     | 3.1.4   | VexCL                                                                                            | 23 |

|          |     | 3.1.5   | ViennaCL                                                                                         | 24 |

|          |     | 3.1.6   | Other libraries                                                                                  | 24 |

|          | 3.2 | DKS o   | concept and architecture                                                                         | 25 |

|          | 3.3 | DKS a   | algorithm library                                                                                | 28 |

|          |     | 3.3.1   | DKS Base                                                                                         | 29 |

|          |     | 3.3.2   | DKS and OPAL                                                                                     | 30 |

|          |     | 3.3.3   | DKS and Musrfit                                                                                  | 31 |

|          |     | 3.3.4   | DKS and PET Image Reconstruction                                                                 | 31 |

|          | 3.4 | DKS a   | auto-tuning                                                                                      | 32 |

|          |     | 3.4.1   | Auto-tuning concept                                                                              | 32 |

|          |     | 3.4.2   | DKS and auto-tuning                                                                              | 33 |

| <b>4</b> | OP. | AL      |                                                                                                  | 35 |

|          | 4.1 | OPAL    | and DKS $\ldots$                                                                                 | 35 |

|          | 4.2 | FFT I   | Poisson solver                                                                                   | 36 |

|          |     | 4.2.1   | FFT Based Particle-Mesh Solver                                                                   | 36 |

|          |     | 4.2.2   | FFT-based Convolutions                                                                           | 36 |

|          | 4.3 | FFT I   | Poisson solver and DKS                                                                           | 37 |

|          |     | 4.3.1   | CUDA Implementation of the Poisson Solver in DKS                                                 | 38 |

|          |     | 4.3.2   | OpenMP Implementation of the Poisson Solver in DKS                                               | 39 |

|          |     | 4.3.3   | Integration of DKS in OPAL                                                                       | 40 |

|          |     | 4.3.4   | Performance Results                                                                              | 40 |

|          | 4.4 | Partic  | le matter interaction                                                                            | 41 |

|     | 4.4.2                                                                                                                                                     | Coulomb Scattering                                                                                                                                                                                                                                                               | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |                                                                                                                                                           |                                                                                                                                                                                                                                                                                  | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     | 4.4.3                                                                                                                                                     | Large Angle Rutherford Scattering                                                                                                                                                                                                                                                | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     | 4.4.4                                                                                                                                                     | OPAL implementation                                                                                                                                                                                                                                                              | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     | 4.4.5                                                                                                                                                     | Particle drift via time integration                                                                                                                                                                                                                                              | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4.5 | Partic                                                                                                                                                    | ele matter interaction and DKS                                                                                                                                                                                                                                                   | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     | 4.5.1                                                                                                                                                     | The DKS Implementation of the Particle Matter Interac-                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     |                                                                                                                                                           | tion Model                                                                                                                                                                                                                                                                       | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     | 4.5.2                                                                                                                                                     | Particle matter interaction on the GPU                                                                                                                                                                                                                                           | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     | 4.5.3                                                                                                                                                     | Particle matter interaction on the MIC                                                                                                                                                                                                                                           | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     | 4.5.4                                                                                                                                                     | Integrating DKS in OPAL                                                                                                                                                                                                                                                          | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4.6 | Perfor                                                                                                                                                    | mance Results                                                                                                                                                                                                                                                                    | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Mu  | $\operatorname{srfit}$                                                                                                                                    |                                                                                                                                                                                                                                                                                  | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5.1 | Musrf                                                                                                                                                     | it and DKS                                                                                                                                                                                                                                                                       | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

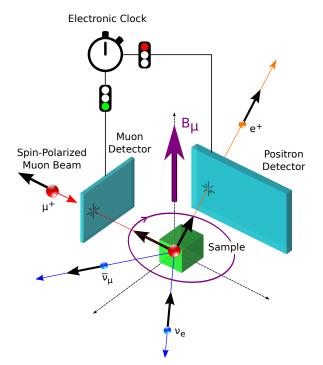

| 5.2 | Proble                                                                                                                                                    | em description                                                                                                                                                                                                                                                                   | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5.3 |                                                                                                                                                           |                                                                                                                                                                                                                                                                                  | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5.4 |                                                                                                                                                           |                                                                                                                                                                                                                                                                                  | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5.5 | Musrf                                                                                                                                                     | it speedups with GPUs                                                                                                                                                                                                                                                            | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| PE  | Г Imag                                                                                                                                                    | ge reconstruction and analysis                                                                                                                                                                                                                                                   | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6.1 |                                                                                                                                                           |                                                                                                                                                                                                                                                                                  | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     | 6.1.1                                                                                                                                                     |                                                                                                                                                                                                                                                                                  | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     | 6.1.2                                                                                                                                                     | Image analysis                                                                                                                                                                                                                                                                   | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6.2 | GPU                                                                                                                                                       |                                                                                                                                                                                                                                                                                  | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     | 6.2.1                                                                                                                                                     | Forward and backward projections                                                                                                                                                                                                                                                 | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

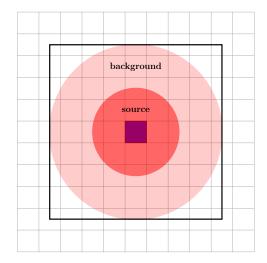

|     | 6.2.2                                                                                                                                                     | Source and background calculation                                                                                                                                                                                                                                                | 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6.3 | Result                                                                                                                                                    | $\operatorname{ts}$                                                                                                                                                                                                                                                              | 79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Mu  | lti-bur                                                                                                                                                   | och tracking code - mbtrack                                                                                                                                                                                                                                                      | 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     |                                                                                                                                                           | -                                                                                                                                                                                                                                                                                | 84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     |                                                                                                                                                           |                                                                                                                                                                                                                                                                                  | 84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     | 7.1.2                                                                                                                                                     | Limitations of mbtrack MPI version                                                                                                                                                                                                                                               | 84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     |                                                                                                                                                           |                                                                                                                                                                                                                                                                                  | 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     | <ul> <li>4.6</li> <li>Mu:</li> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> <li>PE7</li> <li>6.1</li> <li>6.2</li> <li>6.3</li> </ul> | 4.5 Partic<br>4.5.1<br>4.5.2<br>4.5.3<br>4.5.4<br>4.6 Perfor<br>Musrfit<br>5.1 Musrfit<br>5.2 Proble<br>5.3 $\chi^2$ and<br>5.4 User of<br>5.5 Musrfit<br>PET Imag<br>6.1 PET 1<br>6.1.1<br>6.1.2<br>6.2 GPU 1<br>6.2.1<br>6.2.2<br>6.3 Result<br>Multi-bur<br>7.1 MBTI<br>7.1.1 | 4.4.5       Particle drift via time integration         4.5       Particle matter interaction and DKS         4.5.1       The DKS Implementation of the Particle Matter Interaction Model         4.5.2       Particle matter interaction on the GPU         4.5.3       Particle matter interaction on the MIC         4.5.4       Integrating DKS in OPAL         4.6       Performance Results         5.1       Musrfit         5.2       Problem description         5.3 $\chi^2$ and MLH kernels on GPU         5.4       User defined kernels         5.5       Musrfit speedups with GPUs         5.4       Intege reconstruction basics         6.1.1       Image analysis         6.2       GPU kernels for PET image reconstruction and analysis         6.2.1       Forward and backward projections         6.2.2       Source and background calculation         6.3       Results         6.3       Results         7.1       Collective effects in synchrotrons |

|    | 7.2           | GPU    | acceleration of MBTRACK                                                 | 86 |  |

|----|---------------|--------|-------------------------------------------------------------------------|----|--|

|    |               | 7.2.1  | mbtrack CUDA                                                            | 86 |  |

|    |               | 7.2.2  | GPU memory management                                                   | 86 |  |

|    |               | 7.2.3  | The basic single particle transformations $\ldots \ldots \ldots \ldots$ | 87 |  |

|    |               | 7.2.4  | Geometric ring impedance                                                | 89 |  |

|    |               | 7.2.5  | Statistics calculations                                                 | 93 |  |

|    | 7.3           | Result | ts                                                                      | 94 |  |

|    |               | 7.3.1  | Verification of the mbtrack-cuda                                        | 94 |  |

|    |               | 7.3.2  | Performance of the mbtrack-cuda                                         | 95 |  |

| 8  | Con           | clusio | ns                                                                      | 97 |  |

| Re | References 99 |        |                                                                         |    |  |

# List of Figures

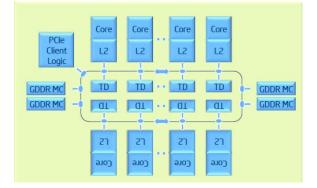

| 2.1 | Intel MIC micro-architecture                                       | 16 |

|-----|--------------------------------------------------------------------|----|

| 3.1 | Approximating pi on the device using ArrayFire                     | 20 |

| 3.2 | A Thrust program for sorting data on the GPU $\ldots$              | 21 |

| 3.3 | Example of Boost.Compute library                                   | 22 |

| 3.4 | Example of VexCL vector operations                                 | 23 |

| 3.1 | ViennaCL architecture                                              | 24 |

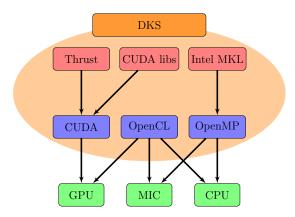

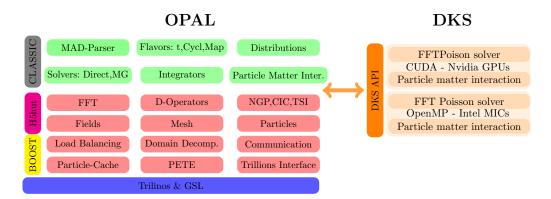

| 3.2 | The Dynamic Kernel Scheduler                                       | 25 |

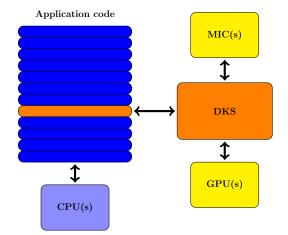

| 3.3 | The Dynamic Kernel Scheduler concept                               | 26 |

| 3.5 | Example of DKS usage for FFT                                       | 27 |

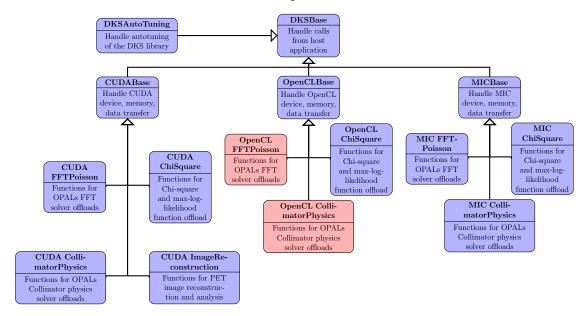

| 3.4 | Architecture of the Dynamic Kernel Scheduler. The nodes shown      |    |

|     | in red are planned in the future versions of DKS, in case other    |    |

|     | vendor GPU support is required.                                    | 28 |

| 3.6 | Example of setup of auto-tuning test                               | 33 |

| 4.1 | The OPAL software structure and connection to DKS $\ldots$ .       | 35 |

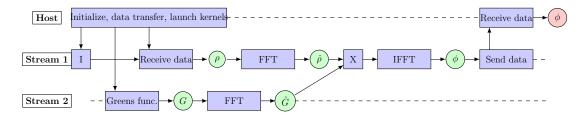

| 4.2 | FFT-Poisson solver sequence diagram                                | 38 |

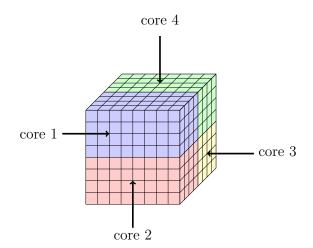

| 4.3 | FFT-Poisson 2D domain decomposition                                | 39 |

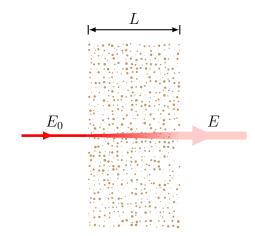

| 4.4 | Particle matter interaction. With the final energy $E < E_0$ and   |    |

|     | larger momenta spread due to Coulomb scattering and the large      |    |

|     | angle Rutherford scattering                                        | 42 |

| 4.1 | Struct to store one particle                                       | 45 |

| 4.2 | Loop trough the particles, calculate energy loss, Coulomb scatter- |    |

|     | ing and large angle Rutherford scattering for each particle        | 46 |

| 4.3 | Calculate energy loss for a particle using Bethe-Bloch equation    | 47 |

#### LIST OF FIGURES

| 4.4  | Move dead particles to the end of the list and erase                  | 48 |  |

|------|-----------------------------------------------------------------------|----|--|

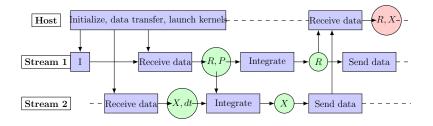

| 4.5  | Integration sequence diagrams                                         |    |  |

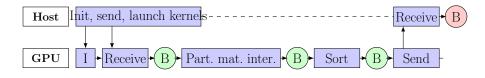

| 4.6  | Particle in matter sequence diagrams, where B denotes particle        |    |  |

|      | bunch                                                                 | 50 |  |

| 4.5  | Data structure for storing particles that are in the material on the  |    |  |

|      | GPU                                                                   | 50 |  |

| 4.6  | CUDA kernel for MC simulation.                                        | 52 |  |

| 4.7  | Sorting of the particles on the GPU.                                  | 53 |  |

| 4.8  | Data structure for storing particles that are in the material on the  |    |  |

|      | MIC                                                                   | 53 |  |

| 4.9  | Vectorization of checkHit and particle drift if it leaves material    | 54 |  |

| 4.10 | Vectorization of energy loss calculations                             | 55 |  |

| 4.11 | Vectorization of coulomb scattering                                   | 56 |  |

| 4.12 | Vectorization of Rutherford, P1, P2 and P3 are temporary arrays       |    |  |

|      | of size MIC_WIDTH with pregenerated random values                     | 57 |  |

| 4.13 | Initializing DKS for particle matter interaction in OPAL              | 57 |  |

| 4.14 | Integrating DKS in OPAL for particle matter interaction simulations.  | 58 |  |

| 5.1  | Schematic of a time differential $\mu$ SR experiment                  | 62 |  |

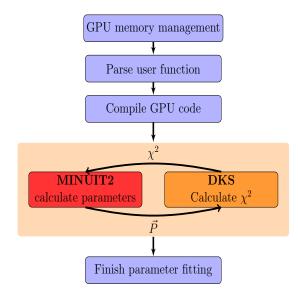

| 5.2  | Flow diagram of parameter fitting with MUSRFIT using MINUIT2          |    |  |

|      | and DKS                                                               | 65 |  |

| 5.1  | CUDA examples of predefined functions that can be used to create      |    |  |

|      | the user function.                                                    | 67 |  |

| 5.2  | Example of parsed user defined function ready for compilation         | 67 |  |

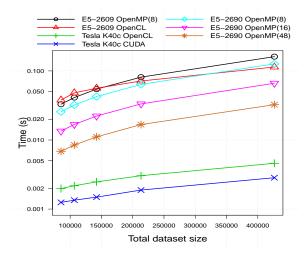

| 5.3  | Parameter fitting with $\chi^2$ function running on the GPU. The time |    |  |

|      | is shown for the execution of one iteration of the minimize com-      |    |  |

|      | mand of Minuit2                                                       | 69 |  |

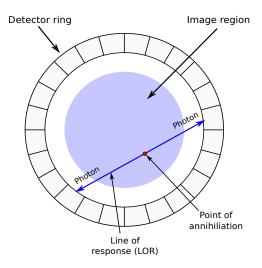

| 6.1  | PET imaging basic principles.                                         | 72 |  |

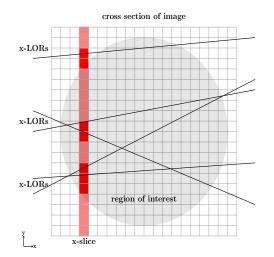

| 6.2  | Cross section of the image showing LORs, with predominant di-         |    |  |

|      | rection in the x plane, and a slice of the image along this direction |    |  |

|      | being processed                                                       | 77 |  |

| 6.1  | Example code of DKS interface integrated in the host application      |    |  |

|      | for image reconstruction.                                             | 78 |  |

| 6.3 | 2D representation of sphere placement at the voxel position for                              |    |

|-----|----------------------------------------------------------------------------------------------|----|

|     | source and background calculation                                                            | 79 |

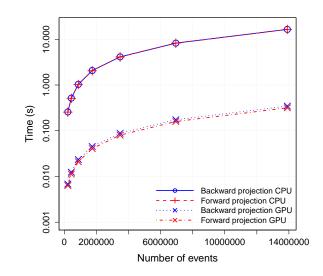

| 6.4 | Execution time for forward and backward projections. Run on In-                              |    |

|     | $\mathrm{tel}(\mathbf{R})$ Xeon(R) CPU E5-2690 v3 and Nvidia Tesla K40c $\ \ldots\ \ldots$ . | 81 |

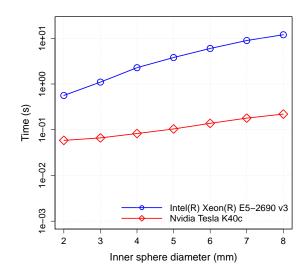

| 6.5 | Calculation of source and background values with different sphere                            |    |

|     | diameters                                                                                    | 82 |

| 7.1 | Allocate the arrays for the data structures                                                  | 87 |

| 7.2 | Kernel to apply wake potential effect to particles in a bunch                                | 93 |

|     |                                                                                              |    |

# List of Tables

| 2.1        | Specifications of used hardware accelerators                                                                                        | 18 |

|------------|-------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1        | Main class functions to interact with device $\ldots \ldots \ldots \ldots \ldots$                                                   | 30 |

| 4.1<br>4.2 | FFT Poisson Solver results       OPAL degrader results                                                                              |    |

| 5.1        | Parameter fitting with $\chi^2$ function running on the GPU. The given time is for the execution of the minimize command of Minuit2 | 68 |

| 6.1        | Performance of image reconstruction and analysis example                                                                            | 80 |

| 7.1        | Comparison of mbtrack-mpi and mbtrack-cuda on 8 core machine with 1 Nvidia Tesla K40c GPU for the first test simulation             | 95 |

| 7.2        | Comparison of mbtrack-mpi and mbtrack-cuda on 8 core machine with 1 Nvidia Tesla K40c GPU for the second test simulation            | 96 |

# Chapter 1

# Introduction

### 1.1 Research background and motivation

In recent years hardware accelerators have become increasingly popular within scientific computing. Based on the Top500 list from November 2016 [1], 86 of the top 500 supercomputers in the world are accelerator based. This includes two of the top three systems on the list: Tianhe-2 which uses Intel Xeon Phi coprocessors and Titan which uses NVIDIA K20x GPUs. GPU usage for general purpose computing has become even more important, due to the gaming industry. Almost every computer is now equipped with a GPU, but if the application is not exploiting the GPU, it is not using all the available computational power of the system. The main benefit of these new devices is the performance potential they provide. The GPUs and also Intel MICs are designed to execute massively parallel workload very efficiently when compared to CPUs, which are designed for serial task execution. Taking advantage of the these resources can substantially increase the performance of an application.

Despite the growing popularity of these devices, developing software that can take advantage of hardware accelerators can become a challenging task, especially for large existing applications. Each hardware accelerator has its own architecture and memory hierarchy which must be taken into account to gain the maximum performance out of the device. In addition to hardware differences, there are also varying methods to program these devices. NVIDIA provides the CUDA [2] toolkit for its GPUs, both AMD and NVIDIA support the OpenCL [3] framework, and Intel allows usage of standard tools and languages to program Intel MIC processor [4], but parallelization and vectorization of the code is needed to gain the best performance. There are also OpenACC [5] and OpenMP 4.0 [6] standards that allow the targeting of hardware accelerators by expressing parallelism through compiler directives.

In this work, the Dynamic Kernel Scheduler (DKS) is presented which provides a slim software layer between the host application and the hardware accelerators. DKS separates the accelerator and framework specific code from the host application and provides a simple interface that can be implemented in the host application to offload tasks to the accelerator. DKS provides functions to handle communication and data transfer between host and device, as well as a library of functions written in CUDA, OpenCL, and OpenMP that allow the targeting of different hardware accelerators.

The ability of DKS to have implementations using different frameworks and libraries, and switch between them from the host application allows the targeting of hardware accelerators of different types and fine tuning of the code to gain the maximum performance from each device. This approach also provides more portability and software investment protection for the host application. In case a hardware architecture is no longer available, a new architecture or development framework emerges, only DKS needs to be updated.

# 1.2 Novelty of the work

With the increasing popularity of hardware accelerators there have been many attempts to ease the development of applications that exploit these devices. These attempts range from creation of cross-platform standards, use of compiler directives, device specific libraries and high level APIs that allow the creation of GPU/MIC code.

The OpenCL standard [3] gives the opportunity to create a cross-platform code, but while the code is guaranteed to execute on the device, as long as it supports OpenCL, the performance portability is not guaranteed. This means that different implementations of the same algorithm might be necessary to gain the best performance from the device. In addition device specific frameworks such as CUDA and CUDA libraries for Nvidia devices, or OpenMP, vectorization and MKL libraries for Intel devices, provide advantages over OpenCL in performance and ease of development. For this reason use of only OpenCL as a device language may not be the best option in each case.

The OpenMP standard starting with version 4.0 provides the support to offload the code to the target device [7]. This would allow the creation of GPU/MIC code using OpenMP pragmas, an approach similar as used with OpenACC [5]. Unfortunately compiler support for creating device codes using OpenMP4.0 or OpenACC is limited and for this reason creating device code that would run on all the devices and platforms is not yet a feasible task.

In order to help with the code development for the GPUs, Nvidia provides a set of GPU accelerated libraries with the CUDA toolkit [8]. These libraries can be easily incorporated in the host applications to offload tasks to the device. Similar approach can be used on Intel MIC where Intel Math Kernel Library (Intel MKL) is available [9].

Several parallel vector libraries, such as Thrust [10], ArrayFire [11] and Boost-Compute [12], are available that implement parallel versions of algorithms from C++ standard template libraries. These libraries provide a collection of functions such as scan, sort, and reduce, which can be combined to implement complex algorithms.

There have also been attempts to create higher level APIs and abstractions to ease the creation of the GPU code [13, 14, 15]. These attempts focus on creating a more generic way of expressing the parallelism needed for the GPU code, that is later translated to CUDA or OpenCL kernels.

The DKS API does not aim to replace or replicate these efforts but rather provide a confined layer where all of these approaches can be used. Developer provided libraries together with hand tuned kernels provide the ability to create fast, optimized algorithms for each hardware accelerator. DKS algorithms for Nvidia graphics cards use handwritten CUDA kernels complemented by cuFFT, cuBLAS, cuRand and Thrust libraries, while the algorithms to target Intel MIC use OpenMP complemented by Intel's Math Kernel Library (MKL). OpenCL is used to target devices from other vendors, which in this work were AMD GPUs. With DKS all of these approaches can be combined to create fast and optimized device code for each device, while keeping the changes to integrate these devices in the host application minimal.

As can be seen, there is no universal and effective solution to include different hardware accelerators in existing applications - for this reason many domain specific solutions are developed, for example TensorFlow and Torch libraries for deep learning applications, ArrayFire, Thrust and Boost.Compute for vector and matrix operations, and also DKS library, developed by the author, for physics simulations.

### **1.3** Thesis and research questions

During this work the following thesis have been proposed:

- With the use of hardware accelerators it is possible to significantly speed up the performance if physics simulation applications.

- It is possible to develop a universal library (DKS), that would allow to effectively integrate devices with different architectures in the existing physics simulation tools.

The research questions studied during this work is how to effectively develop the needed algorithms for these parallel architectures and how to develop the DKS library. DKS library needs to provide a common interface so that the application could communicate with different hardware accelerators un execute tasks on these devices. At the same time library needs to provide the best possible implementation of the algorithms for different architectures. This library needs to be easily extendable, so that other algorithms needed in the future or needed for different applications could be easily added. DKS library also needs to be extendable with different hardware accelerator support, so in the future new devices could be added without changing the interface used in the host application.

### 1.4 Research methodology

During this work both theoretical analysis and practical research methods were used.

Theoretical studies were used to analyze existing physics simulation tool and the algorithms used in these applications as well as attempts to use hardware accelerators in similar simulation application optimization. Additionally existing hardware accelerator libraries were analyzed to develop a concept for DKS architecture.

The practical implementation of the thesis is the development of DKS library which was also successfully integrated in multiple physics simulation and experimental data analysis applications. Additionally benchmark tests were performed to study the benefits that these devices can provide for simulation applications.

### 1.5 The aim and tasks of the research

The main objective of the thesis was to integrate new processor technologies such as GPUs and Intel MICs to speed up existing particle accelerator simulation software, such as OPAL and mbtrack, software for experimental data analysis such as musrfit, and PET image reconstruction.

To take advantage of the new processor architectures, algorithms that will be executed on these devices, need to be rewritten using the supported programming languages such as CUDA, OpenCL and OpenMP. To achieve the optimal performance from each device the algorithms also need to be constructed with the device architecture in mind.

To facilitate the integration of the device specific algorithms in large existing applications, DKS was developed which allows to separate all the device specific code from the host application. With the help of DKS it is possible to create device code using multiple different frameworks to target different devices and integrate this code in the host application with one simple interface. This simplifies the process of supporting multiple co-processors for the host application. DKS also eases the process of developing, maintaining and optimizing the device code.

The auto tuning framework for DKS is developed to allow DKS to execute the

GPU code with best possible launch parameters. This allows DKS to adapt to different hardware environments since GPU hardware resources, such as available memory, available cores and registers per core, vary between different devices and influence how the code should be launched for best performance.

# 1.6 Main results of the thesis and approbation of the results

The main result of the thesis is universal DKS library, developed by the author, that eases the integration of hardware accelerators in existing physics simulation applications. During this work DKS was used to add the option to offload the compute intensive parts of the simulations to GPU and Intel MIC for various physics simulation codes, developed and used at PSI and ETH Zurich. These codes include:

- OPAL a framework for general particle accelerator simulations

- musrfit a framework to analyze muSR data

- PET Image reconstruction and analysis software

- mbtrack multibunch tracking code

DKS library was developed to be easily extendable un reusable in other applications. This library can also be extended to support other hardware accelerators.

DKS was integrated in OPAL (Object-oriented Parallel Accelerator Library) which is an open source C++ framework for general particle accelerator simulations. For acceleration of OPAL simulations using GPUs and Intel MIC devices CUDA and OpenMP implementations were created for FFT based Poisson solver and for Monte Carlo simulations of particle matter interactions. These algorithms are the ones of the most time consuming parts in some of the most widely run simulations using OPAL - ring cyclotron simulations and degrader simulations.

DKS was used in musrfit - a framework for muSR data analysis, to enable almost real time data analysis of experimental data. In musrfit parameter fitting using  $\chi^2$  and log-max likelihood minimization was offloaded to the GPUs to speed up data analysis of muSR experiments. CUDA and OpenCL was used in DKS to create the necessary GPU algorithms and the performance was tested using various GPUs from different vendors. The results show that almost real-time data analysis performance can be achieved with a single GPU. This allows to perform the data analysis simultaneously with the experiments, guiding the experimenter to optimize the measuring program.

Using DKS and CUDA a PET image reconstruction and analysis software was optimized to allow compute intensive parts of the code to run on Nvidia GPUs. With the help of GPUs it was demonstrated that the execution time of PET image reconstruction can be decreased significantly, bringing the project closer to its goal of real time image reconstruction.

Multibunch tracking code mbtrack developed at SOLEIL (French national synchrotron facility) and used at PSI to study multibunch instabilities was ported to CUDA. This allows the code to execute on Nvidias GPUs. The results show a substantial improvement in computing time for single bunch simulations compared to CPU version. The main benefit of GPU version for multibunch simulations is the ability to run the large simulations required at PSI without the need of a computing cluster, which was required for the original version.

OPAL, must and mbtrack applications accelerated by GPUs are used at PSI for particle matter interaction simulations (OPAL), studies of multi bunch instabilities for SLS-2 upgrade proposal (mbtrack) and for  $\mu$ SR experimental data analysis (must in PET image reconstruction program was used as a prototype at ETH Zurich to demonstrate the potential of GPU acceleration and could be used in the future in order to achieve real time image reconstruction.

### **1.7** Publications of the research results

The list of publications by the author includes 2 papers submitted to journal "Computer Physics Communications" and three papers in the conference proceedings (ICAP2015, IPAC2017 and  $\mu$ SR2017). In all three papers the author of the dissertation was the main author of the publication and responsible for the design of the algorithms for parallel architectures in DKS, the GPU/MIC code development, verification and benchmark tests.

Andreas Adelmann, Uldis Locans, Andreas Suter, The Dynamic Kernel Scheduler – Part 1, Computer Physics Communications, Volume 207, October 2016,