PhD-FSTC-2017-43 The Faculty of Sciences, Technology and Communication

## DISSERTATION

#### Defence held on 21/07/2017 in Luxembourg to obtain the degree of

### DOCTEUR DE L'UNIVERSITÉ DU LUXEMBOURG EN INFORMATIQUE

by

CHUNHUI WANG Born on 11 April 1987 in Harbin (Heilongjiang, China)

## AUTOMATED REQUIREMENTS-DRIVEN TESTING OF EMBEDDED SYSTEMS BASED ON USE CASE SPECIFICATIONS AND TIMED AUTOMATA

#### DISSERTATION DEFENSE COMMITTEE

PROF. DR. ING. LIONEL BRIAND, Dissertation Supervisor *University of Luxembourg*

DR. MEHRDAD SABETZADEH, Chairman *University of Luxembourg*

DR. SHIVA NEJATI, Deputy Chairman *University of Luxembourg*

PROF. DR.BRUNO LEGEARD, Member Université de Franche-Comté

DR. GIOVANNI DENARO, Member Università degli Studi di Milano

DR. FABRIZIO PASTORE, Advisory Member University of Luxembourg

#### Abstract

The complexity of embedded software in safety-critical domains, such as automotive and avionics, has significantly increased over the years. For most embedded systems, standards require system testing to explicitly demonstrate that the software meets its functional and safety requirements. In these domains, system test cases are often manually derived from functional requirements in natural language plus other design artefacts, like UML statecharts. The definition of system test cases is therefore time-consuming and error-prone, especially given the quickly rising complexity of embedded systems.

The benefits of automatic test generation are widely acknowledged today but existing approaches often require behavioural models that tend to be complex and expensive to produce, and are thus often not part of development practice.

The work proposed in this dissertation focusses on the automated generation of test cases for testing the compliance between software and its functional and timing requirements. This dissertation is inspired by contexts where functional and timing requirements are expressed by means of use case specifications and timing automata, respectively. This is the development context of our industrial partner, IEE, an automotive company located in Luxembourg, who provided the case study used to validate the approach and tool described in this dissertation.

This dissertation presents five main contributions: (1) A set of guidelines for the definition of functional and timing requirements to enable the automated generation of system test cases. (2) A technique for the automated generation of functional test cases from requirements elicited in the form of use case specifications following a prescribed template and natural-language restrictions. (3) A technique that reuses the automatically generated functional test cases to generate timeliness test cases from minimal models of the timing requirements of the system. (4) A technique for the automated generation of oracles for non-deterministic systems whose specifications are expressed by means of timed automata. In the context of this dissertation, automated oracles for non-deterministic systems are necessary to evaluate the results of the generated timeliness test cases. (5) The evaluation of the applicability and effectiveness of the proposed guidelines and techniques on an industrial case study, a representative automotive embedded system developed by IEE.

## Acknowledgements

First and foremost I would like to extend my sincere gratitude to my supervisor Professor Lionel Briand and co-supervisor Fabrizio Pastore. Without their patient guidance, the goal would not have been attained as smoothly, nor would the road have been as pleasant.

The research presented in this thesis was conducted under the collaboration between academia and industry. I would like to thank everyone who involved in this project that trying to improve the testing process in IEE S.A. for their commitment and patience, in particular, Thierry Stephany, Marcel Stolzenbach and David Wiseman.

I am grateful to the members of my defence committee: Mehrdad Sabetzadeh, Shiva Nejati, Bruno Legeard, and Giovanni Denaro for their insightful suggestions and remarks. I would like to additionally thank Prof. Bruno Legeard, and Dr. Giovanni Denaro for taking the time to travel to Luxembourg to attend my defence, despite their busy schedules.

I would like to also express my great thanks to all the friends that I have made in the tiny Grand Duchy of Luxembourg for the memorable moments that we have had. More specifically, I would like to thank all my colleagues in the Software Verification and Validation Lab for creating an inspiring and welcoming working environment.

Last but not least I would like to thank my parents in China for always supporting and believing in me. Without their support, this dissertation would not have been possible.

Chunhui WANG At University of Luxembourg On July 2017

## Contents

| C  | onten   | ts                                                                             | V      |

|----|---------|--------------------------------------------------------------------------------|--------|

| Li | st of ] | Figures                                                                        | viii   |

| Li | st of ' | Tables                                                                         | xi     |

| A  | crony   | ms                                                                             | xiii   |

| 1  |         | oduction                                                                       | 1      |

|    | 1.1     |                                                                                | 1      |

|    | 1.2     | Research Contributions                                                         | 2      |

|    | 1.3     | Organisation of the Dissertation                                               | 4      |

| 2  | _       | uirement Analysis Guidelines for the Automated Generation of Functional and    |        |

|    |         | eliness Test Cases                                                             | 5      |

|    | 2.1     | Case Study System                                                              | 6      |

|    | 2.2     | 2.1.1 Testing of BodySense                                                     | 6      |

|    | 2.2     | Eliciting Functional Requirements                                              | 7<br>7 |

|    |         | <ul><li>2.2.1 Eliciting Use Cases with RUCM</li></ul>                          | 9      |

|    | 2.3     | Modelling Timing Requirements                                                  | 10     |

|    | 2.5     | 2.3.1 Modelling the Timing Properties of Domain Entities                       | 10     |

|    |         | 2.3.2 Modelling the Timing Properties of Domain Enddes                         | 12     |

| 3  | Aut     | omatic Generation of System Test Cases from Use Case Specifications            | 15     |

|    | 3.1     | Motivation                                                                     | 16     |

|    | 3.2     | Overview of the Approach                                                       | 17     |

|    | 3.3     | NLP Pipeline for UMTG                                                          | 18     |

|    | 3.4     | Evaluation of the Model Completeness                                           | 20     |

|    | 3.5     | Identification of Constraints                                                  | 21     |

|    | 3.6     | Generation of the Use Case Test Model                                          | 21     |

|    | 3.7     | Generation of Scenarios and Test Inputs                                        | 23     |

|    | 3.8     | Generation of Test Cases                                                       | 26     |

|    | 3.9     | Empirical Evaluation                                                           | 28     |

|    |         | 3.9.1 RQ1. Is the modelling and analysis effort required by UMTG acceptable in | 29     |

|    |         | an industrial context?                                                         | 29     |

|   |       | 3.9.2    | RQ2. Is UMTG effective in generating test cases that cover the requirements         |    |

|---|-------|----------|-------------------------------------------------------------------------------------|----|

|   |       |          | captured by use case specifications?                                                | 30 |

|   |       | 3.9.3    | RQ3. Does UMTG scale?                                                               | 30 |

|   |       | 3.9.4    | Threats to Validity                                                                 | 31 |

|   | 3.10  | Conclu   | usion                                                                               | 32 |

| 4 | Syste | em Test  | ting of Timing Requirements based on Use Cases and Timed Automata                   | 33 |

|   | 4.1   | Limita   | tions of Test Generation Based on Timed Automata                                    | 34 |

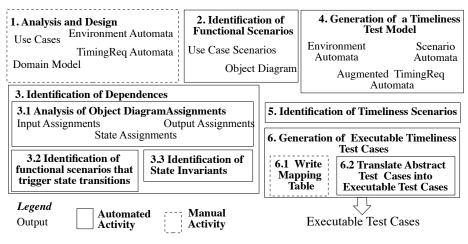

|   | 4.2   | Autom    | ated Testing with TAUC                                                              | 35 |

|   | 4.3   | Overvi   | ew of TAUC                                                                          | 36 |

|   | 4.4   | Identif  | ication of dependencies                                                             | 37 |

|   |       | 4.4.1    | Analysis of attributes in object diagrams                                           | 38 |

|   |       | 4.4.2    | Identification of functional scenarios that trigger state transitions               | 39 |

|   |       | 4.4.3    | Identification of state invariants                                                  | 40 |

|   | 4.5   | Genera   | ation of the Timeliness Test Model                                                  | 40 |

|   | 4.6   | Identif  | ication of Timeliness Scenarios                                                     | 42 |

|   | 4.7   | Genera   | ation of Executable Test Cases                                                      | 44 |

|   | 4.8   | Empiri   | cal evaluation                                                                      | 46 |

|   |       | 4.8.1    | RQ1. Is TAUC effective in generating test cases able to detect faults that affect   |    |

|   |       |          | software timeliness?                                                                | 46 |

|   |       | 4.8.2    | RQ2. Is the modelling and analysis effort required by TAUC acceptable in an         |    |

|   |       |          | industrial context?                                                                 | 48 |

|   |       | 4.8.3    | Threats to Validity                                                                 | 48 |

|   | 4.9   | Conclu   | ision                                                                               | 49 |

| 5 | Orac  | cles for | Testing Software Timeliness with Uncertainty                                        | 51 |

|   | 5.1   | Model    | ling of Test Cases                                                                  | 53 |

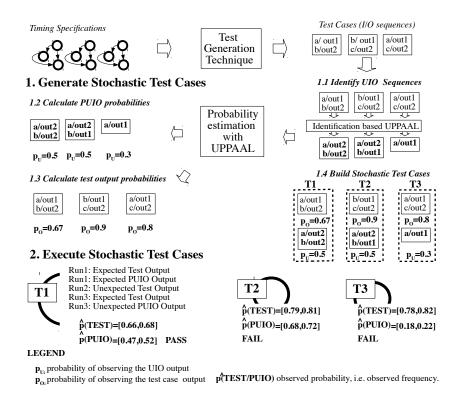

|   | 5.2   | Testing  | g with UIO Sequences                                                                | 54 |

|   |       | 5.2.1    | Generation of UIO sequences from TAs                                                | 55 |

|   |       | 5.2.2    | Consequences of uncertainty                                                         | 57 |

|   | 5.3   |          | <i>TUIOS</i> approach                                                               | 59 |

|   |       | 5.3.1    | An Overview                                                                         | 59 |

|   |       | 5.3.2    | Probability Estimation with UPPAAL                                                  | 60 |

|   |       | 5.3.3    | Generating Stochastic Test Cases                                                    | 60 |

|   |       | 5.3.4    | Building PUIO Sequences                                                             | 63 |

|   |       | 5.3.5    | Identifying Test Case Probabilities and Building Stochastic Test Cases              | 64 |

|   |       | 5.3.6    | Test Execution                                                                      | 64 |

|   | 5.4   | Empiri   | cal Evaluation                                                                      | 66 |

|   |       | 5.4.1    | RQ1. How does <i>STUIOS</i> compare with a simpler and less expensive alternative?  | 66 |

|   |       | 5.4.2    | RQ2. Does <i>STUIOS</i> generate oracles that are effective in the presence of time |    |

|   |       |          | uncertainty?                                                                        | 67 |

|   |       | 5.4.3    | RQ3. Can STUIOS negatively impact the efficiency of the testing process?            | 68 |

|   |       | 5.4.4    | Threats to Validity                                                                 | 69 |

|   |       |          | 5.4.4.1 Internal threats                                                            | 69 |

|   |       |          | 5.4.4.2 External threats                                                            | 69 |

|   | 5.5   | Conclu   | isions                                                                              | 70 |

| 6   | Related Work6.1Generation of Functional System Test Cases6.2Automated testing of software timeliness6.3Definition of oracles for systems charachterized by time uncertainty | <b>71</b><br>71<br>72<br>73                   |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| 7   | Conclusions and Future Work           7.1         Summary         Summary           7.2         Future Work         Summary                                                 | <b>75</b><br>75<br>76                         |

| Lis | st of Papers                                                                                                                                                                | 77                                            |

| Bil | bliography                                                                                                                                                                  | 79                                            |

| A   | Tool Suite Description         A.1       UMTG Toolset                                                                                                                       | <b>87</b><br>87<br>89<br>91<br>91<br>92<br>93 |

# **List of Figures**

| 2.1<br>2.2 | Partial domain model for <i>BodySense</i>                                                          | 10       |

|------------|----------------------------------------------------------------------------------------------------|----------|

| 2.2        | Edges are labelled by the triple guard (green), action (light blue), and update (blue)             | 11       |

| 2.3        | Environment automata for <i>BodySense</i>                                                          | 13       |

| 3.1        | Overview of the UMTG Approach                                                                      | 18       |

| 3.2        | NLP pipeline applied to extract the behaviour of a Use Case                                        | 19       |

| 3.3        | Part of the transducer that identifies constraints                                                 | 19       |

| 3.4        | Tags associated with the use case step in Lines 6 of Table 2.2                                     | 20       |

| 3.5        | Portion of the domain model for <i>BodySense</i>                                                   | 20       |

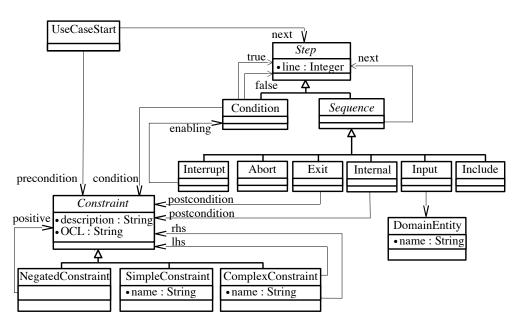

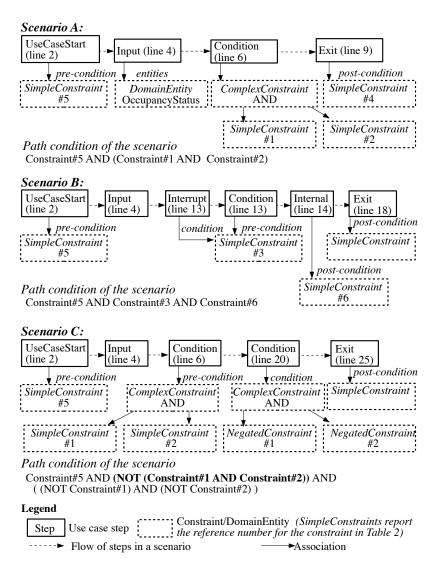

| 3.6        | Metamodel for the Use Case Testing Model                                                           | 22       |

| 3.7        | The Use Case Testing Model derived from the Use Case in Table 4.1                                  | 23       |

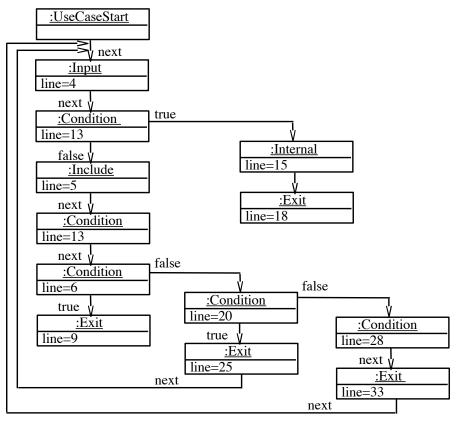

| 3.8        | GenerateInputs: the Test Generation Algorithm adopted in UMTG                                      | 24<br>26 |

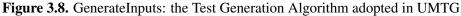

| 3.9        | Three scenarios built by UMTG for the use case in Table 2.2                                        | 20<br>28 |

| 3.10       | Activities performed by OWITO to generate the test case in Table 5.5                               | 20       |

| 4.1        | Automaton that captures how TemperatureErrors are qualified and dequalified in <i>BodySense</i> .  |          |

|            | This is the same automaton shown in Figure 2.2. Edges are labelled by the triple guard             |          |

|            | (green), action (light blue), and update (blue).                                                   | 34       |

| 4.2        | Steps of TAUC.                                                                                     | 37       |

| 4.3        | Model of a functional scenario that covers the Alternative Flow 2.2 in Table 4.1                   | 38       |

| 4.4        | Object diagram generated by UMTG to satisfy the path condition that covers the scenario            |          |

|            | in Figure 4.3                                                                                      | 39       |

| 4.5        | Assignments required to exercise the scenario in Figure 4.3                                        | 39       |

| 4.6        | Automaton for the Scenario in Figure 4.3                                                           | 41       |

| 4.7        | Augmented Timing Requirements Automaton derived from the automaton in Figure 4.1.                  | 42       |

| 4.8        | Alignment of two Timeliness Scenarios                                                              | 44       |

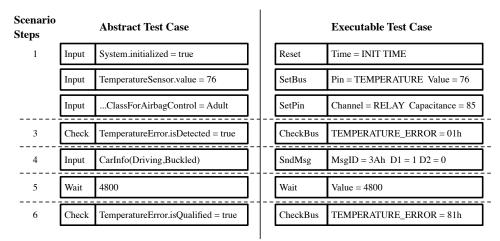

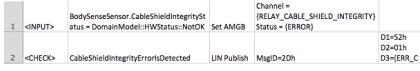

| 4.9        | (a) Abstract Test Case generated from Timeliness Scenario 2, and (b) Executable Timeli-            |          |

|            | ness Test Case.                                                                                    | 45       |

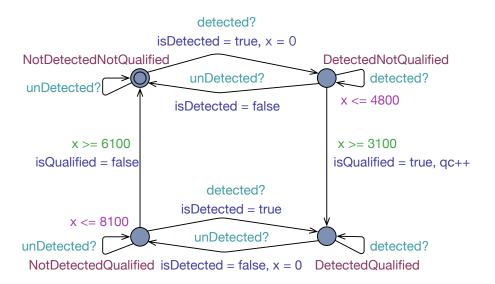

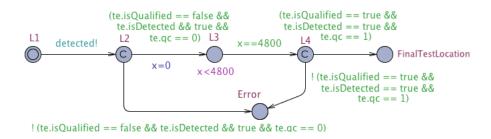

| 5.1        | Automaton that captures how temperature errors are qualified and dequalified in <i>BodySense</i> . | 54       |

| 5.2        | A Test Case that checks if TemperatureErrors are qualified on time.                                | 54       |

| 5.3        | Automaton that shows a possible transition fault in the implementation of Figure 5.1.              | 55       |

| 5.4        | UIO sequence that characterises state DetectedQualified after the execution of the test            |          |

|            | case in Figure 5.2.                                                                                | 56       |

| 5.5        | Test case of Figure 5.2 including the UIO sequence in Figure 5.4.                                  | 56       |

| 5.6        | Test case that verifies the qualification of a temperature error that appears for a short time.    | 58       |

| 5.7<br>5.8<br>5.9<br>5.10 | An overview of the <i>STUIOS</i> approach                                                | 59<br>61<br>62<br>64 |

|---------------------------|------------------------------------------------------------------------------------------|----------------------|

| A.1                       | UMTG architecture (grey boxes show third party components, black boxes UMTG components   |                      |

|                           | with nested components)                                                                  | 87                   |

| A.2                       | Menus provided by the UMTG plug-ins                                                      | 88                   |

| A.3                       | Example of an Abstract (left) and a corresponding Executable (right) Test Case Generated |                      |

|                           | by UMTG                                                                                  | 88                   |

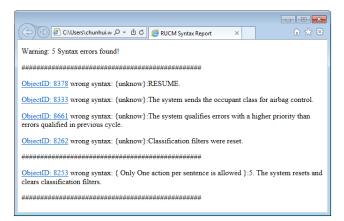

| A.4                       | RCUM Syntax Report                                                                       | 89                   |

| A.5                       | Consistency Check Report                                                                 | 89                   |

| A.6                       | List of OCL Constraints                                                                  | 90                   |

| A.7                       | Mapping table                                                                            | 90                   |

| A.8                       | Traceability Links Generated for a Test Case.                                            | 90                   |

| A.9                       | Portion of a Mapping Table                                                               | 91                   |

|                           | Description of taucGen.jar                                                               | 92                   |

|                           | Description of muta.jar                                                                  | 92                   |

|                           | Description of vmodels.jar                                                               | 93                   |

|                           | Description of verifier.jar                                                              | 93                   |

## **List of Tables**

| 2.1 | An example test case for <i>BodySense</i>                               | 6  |

|-----|-------------------------------------------------------------------------|----|

| 2.2 | Use Case Identify Initial Occupancy Status of a Seat                    | 8  |

| 3.1 | An example test case for <i>BodySense</i>                               | 16 |

| 3.2 | Some constraints for the use case 'Identify Occupancy Status of a Seat' | 21 |

| 3.3 | A generated test case for <i>BodySense</i>                              | 27 |

| 3.4 | Mapping table for <i>BodySense</i> (excerpt)                            | 27 |

| 3.5 | Results obtained with the case study                                    | 29 |

| 3.6 | Results obtained for RQ2                                                | 30 |

| 3.7 | Results obtained for RQ3                                                | 31 |

| 4.1 | BodySense Use Cases                                                     | 35 |

| 4.2 | Mapping Table for <i>BodySense</i>                                      | 46 |

| 4.3 | Fault Coverage Measured Against 323 Faulty Versions.                    | 47 |

## Acronyms

API Application Programming Interface.

**CTL** Computation Tree Logic.

**DXL** Door eXtension Language.

EFSM Extended Finite State Machine.

FSM Finite State Machine.

**ISO** International Organization for Standardization.

LIN Local Interconnect Network.

**NLP** Natural Language Processing.

**OCL** Object Constraint Language. **OMG** Object Management Group.

PUIO Probabilistic UIO sequences.

**RFS** Reference Flow Step.**RQ** Research Question.**RUCM** Restricted Use Case Modelling.

SMC Statistical Model Checking.STUIOS Stochastic Testing with Unique Input Output sequences.SUT System Under Test.

TAUC Test generation combining timed Automata and Use Case specifications.

UCS Use Case Specification.

UCTM Use Case Test Model.

UIO Unique Input Output sequence.

UML Unified Modelling Language.

UMTG Use case Modelling for system Tests Generation.

XMI XML Metadata Interchange.

# Chapter 1 Introduction

### 1.1 Context

The complexity of embedded software in safety-critical domains, such as automotive and avionics, has significantly increased over the years. When testing critical systems in the automotive domain, similar to other application domains, rigorous testing processes conforming to established industry standards such as ISO 26262 [ISO, 2011] must be employed. Such standards mandate the level of rigour required for software testing, with the level of rigour increasing as the potential for the system to lead to loss of life increases. Even for systems that are deemed to have a relatively low probability of causing loss of life, ISO 26262 effectively mandates stringent requirement-based testing. In practice, this entails constructing system test cases that can be traced to high-level system requirements.

In current industrial practice, system test cases are often derived manually by the software engineers who read functional requirements written in natural language plus other software specification artefacts, for example timed automata or UML statecharts capturing the timing requirements of the system. The definition of system test cases is therefore time-consuming and error-prone, especially so given the quickly rising complexity of embedded systems in safety-critical domains.

This dissertation focusses on software development contexts where functional and timing requirements are expressed by means of use case specifications and timed automata, respectively. This is the development context of our industrial partner, IEE, an automotive company who provided the case study used to validate the techniques described in this dissertation, which is BodySense, an airbag control system. The specific development context considered in this dissertation has influenced the definition of the research problem addressed, and the identification of the solutions proposed. More specifically, this dissertation focuses on the problem of automatically generating test cases that verify the compliance of the system with both its functional requirements, i.e. *functional test cases*, and its timing requirements, i.e., *timeliness test cases*. We use the term software timeliness to indicate the ability of the software to satisfy timing constraints. We focus on functional and timeliness test cases because for companies developing embedded automotive systems like IEE, testing the compliance of the system with functional and timing requirements is of crucial importance for ensuring proper system behavior and safety. For an airbag control system, for example, the timely identification of error conditions and the proper execution of the consequent error management activities is necessary to guarantee the safety of the passengers of the car. The benefits of automatic test case generation are widely acknowledged today and there are many proposed approaches in the literature [Escalona et al., 2011]. However most of the existing test automation approaches require very detailed behavioural models of the system in order to generate executable test cases. Usually, such detailed system models are expensive to produce, and their cost cannot be justified if they are used only for testing but not for other development activities. In case engineers decide to rely upon less detailed and high-level models, then they have to face the challenge that these models can be used only to generate abstract test cases. Abstract test cases can be concretized into executable test cases by means of test adaptation or test transformation approaches [Utting and Legeard, 2006], but the cost, however, for transforming an abstract test case into an executable test case is not negligible. The solutions proposed in this dissertation have been derived by the idea, inspired by our industrial partner, that a test generation technique can be successfully adopted in an industrial context if the additional information (e.g., models) required to enable test case generation is kept minimal.

Many approaches for the generation of functional test cases require that system specifications are captured as UML behavioural models such as activity diagrams [Linzhang et al., 2004], statecharts [Ryser and Glinz, 1999], and sequence diagrams [Nebut et al., 2006]. In modern industrial systems, these behavioural models tend to be complex and expensive if they are to be precise and complete enough to support test automation, and are thus often not part of development practice. To minimize the costs of modelling in this dissertation we propose solutions that exploit, to the maximum extent, the information available in common analysis and design artefacts, produced for other purposes such as contractual agreements with customers, to automate test case generation.

Concerning the testing of timing requirements, most of the existing techniques require that the timing constraints of the system are modelled by means of Timed Automata [Hessel et al., 2008, En-Nouaary et al., 2002, Aboutrab et al., 2013, En-Nouaary and Hamou-Lhadj, 2008] or UML state-charts [Mücke and Huhn, 2004]. However, to limit modelling effort, our observation is that software engineers derive very high level models that capture only the state transitions controlled by timing constraints. These models are thus used only to generate abstract test cases, which, as indicated above, lead to non-negligible additional costs if they are used to generate executable test cases. To automate the generation of executable test cases while keeping the modelling of timing requirements simple and high level, in this dissertation we define solutions that exploit the information available in use case specifications.

### **1.2 Research Contributions**

In this dissertation, we address the problem of automatically generating functional and timeliness test cases from requirement specifications in contexts where development is use case-driven and additional modelling effort required for testing purposes must be kept to a minimum. To this end, we propose a set of guidelines for eliciting test-ready functional and timing requirements and a set of approaches that (1) generate functional test cases from requirements elicited by means of use case specifications, (2) combine the generated functional test cases with timing specifications to test timing requirements, (3) rely upon a stochastic solution to deal with the problem of building reliable oracles in the presence of partial state visibility and non-determinism. More precisely, we provide the following contributions: 1. A set of practical guidelines (realistic modelling) for the definition of test-ready functional and timing requirements. These guidelines include the adoption of a structured and analysable form of use case specifications, i.e., Restricted Use Case Modeling (RUCM) [Yue et al., 2013], and the adoption of Timed Automata [Alur and Dill, 1994] for eliciting timing requirements. RUCM is based on a template with restriction rules, enabling the automated extraction of behavioral information by reducing imprecision and incompleteness in use cases. Timed Automata are one of the formalisms usually adopted for the specification of the timing behaviour of the system.

The proposed guidelines have been described in two conference papers [Wang et al., 2015, Wang et al., 2017] and are discussed in Chapter 2.

2. A technique for generating executable system test cases by exploiting the behavioural information implicitly described in use case specifications. We named this technique Use Case Modelling for System Tests Generation (UMTG). UMTG requires a domain model of the system, which enables the definition of constraints that are used by UMTG to generate test data and oracles. UMTG avoids behavioral modelling by applying Natural Language Processing (NLP) to use case specifications expressed using RUCM. UMTG employs NLP to build Use Case Test Models (UCTMs) from RUCM specifications. A UCTM captures the control flow implicitly described in the RUCM specification. During NLP, a list of textual descriptions of pre, post and guard conditions in use cases is extracted. The software engineer further manually reformulates these textual descriptions using constraints written using the Object Constraint Language (OCL) [OMG, 2004] based on the domain model. UMTG combines UCTMs with the OCL constraints to enable automated test generation via constraint solving.

This contribution has been published in a conference paper [Wang et al., 2015] and is discussed in Chapter 3.

3. A technique for automatically generating executable test cases targeting software timeliness. We named the technique *Test Generation combining Timed Automata and Use Case Specifications (TAUC)*. TAUC works by processing use case specifications and models of the timing requirements of the system elicited using timed automata to build the detailed models necessary to generate executable test cases. In this way, TAUC prevents software engineers from designing very detailed timed automata when use case specifications are available. In addition, TAUC automatically builds test suites that exercise the functionality regulated by timing requirements by optimising diversity among test inputs, thus increasing the probability of identifying problems dependent on specific input sequences.

This contribution has been published in a conference paper [Wang et al., 2017] and is discussed in Chapter 4.

4. A technique to automate the generation of effective oracles for timeliness test cases derived from timed automata in the presence of non-deterministic behaviour. We named the technique *Stochastic Testing with Unique Input Output Sequences (STUIOS)*. STUIOS addresses the problem of generating oracles in the presence of non-deterministic behaviour. As main components of STUIOS, we introduce the concepts of *stochastic test cases* and *probabilistic UIO sequences (PUIO sequences)*. A PUIO sequence is an input-output sequence with an associated probability of observing the given output sequence in response to the inputs. The underlying idea is that probabilistic UIO sequences enable fault detection by determining if the output sequences observed through testing are unlikely, based on multiple executions of the same test cases. Stochastic test cases extend the same idea to the entire test case. A stochastic test case specifies the expected probability of observing a specific output sequence after a given test input sequence; in addition, it includes a PUIO sequence that is used to check if the test execution brings the system to the expected state.

This contribution has been submitted and is under review. It is discussed in Chapter 5.

### **1.3** Organisation of the Dissertation

**Chapter 2** describes a set of analysis and design guidelines that enable the adoption of the techniques proposed in this dissertation. We take advantage of the example models presented in this chapter also to provide an overview of *BodySense*, the case study system provided by IEE.

Chapter 3 describes UMTG along with the empirical results achieved with *BodySense*.

Chapter 4 describes TAUC along with the empirical results achieved with *BodySense*.

Chapter 5 describes STUIOS along with the empirical results achieved with *BodySense*.

Chapter 6 discusses related work.

Chapter 7 summarises the contributions of this dissertation and discusses perspectives on future work.

**Appendix A** provides a description of the software tools that were developed to support the proposed approaches and run empirical studies.

## Chapter 2

## **Requirement Analysis Guidelines for the Automated Generation of Functional and Timeliness Test Cases**

This dissertation presents a set of techniques that automate the generation of functional and timeliness test cases by relying upon the availability of analysis and design artefacts produced according to specific guidelines. The availability of these analysis and design artefacts is a precondition for the adoption of the techniques proposed in this dissertation. We intentionally rely upon artefacts that are commonly produced in industrial practice and that are realistic in terms of what can be expected from development engineers of embedded systems when explicit requirements and traceability between requirements and test cases are required. The industrial environment where our case study took place matches this description and helped us clarify our working assumptions.

In this chapter, we thus summarize the activities that should be performed by software engineers during analysis and design to produce the design artefacts processed by the techniques proposed in the dissertation. We propose two sets of guidelines: (1) functional requirements, and (2) timing requirements.

To give concrete examples of requirements defined according to the proposed guidelines we rely upon the analysis artefacts produced for *BodySense*, the case study system used to evaluate the techniques proposed in this dissertation. For this reason, this chapter presents also a brief overview of the *BodySense* system.

This Chapter proceeds as follows. Section 2.1 overviews the characteristics of *BodySense*, the case study system used to evaluate the techniques proposed in this dissertation. *BodySense* specifications are used to ease the description of the methodology itself. Section 2.2 describes the activities required to elicit functional requirements. Section 2.3 describes the activities that must be performed to elicit timing requirements.

### 2.1 Case Study System

*BodySense* is a capacitive sensing system supporting airbag suppression for child restraint systems in vehicles. Infant-only suppression, in combination with low-risk airbag deployment technology, is the most widely accepted safety strategy to fulfil the advanced airbag requirements of the FMVSS 208 regulation issued by the National Highway Traffic Safety Administration (NHTSA) in the U.S.

*BodySense* is able to distinguish between child restraint systems (class 1) and passengers in the front seat (class 2), suppressing airbag deployment in the first situation in case of a collision. The system also supports the seat belt reminder function and can generate an *airbag off* sign. Moreover, *BodySense* offers reliable classification regardless of seat belt tension, occupant position, weight or height. *BodySense* monitors a car seat for occupancy and classifies the occupant by using a sensor in the passenger seat. By measuring the change in the electrical field between an electrode and the vehicle body, *BodySense* is able to provide a robust classification between passengers and child restraint systems.

#### 2.1.1 Testing of BodySense

*BodySense* is already in production and presents several critical functional and timing requirements that IEE engineers must verify in compliance with the ISO-26262 safety automotive standard [ISO, 2011].

*BodySense* is developed on a real-time operating system named MicroC/OS [Micrium Embedded Software, 2016] by using IBM Rational Rhapsody [IBM Rhapsody, 2017], a well-known modelling tool, for automated code generation in the C programming language. The system communicates with other components in the vehicle via LIN protocol. CANoe [Vector, 2017] is the software used for system testing, which simulates the sending of messages through the standard automotive LIN protocol.

To satisfy the requirements imposed by ISO-26262, IEE engineers must prove that each requirement has been tested and, to this end, traceability between software requirements and test cases is maintained. The tool adopted to keep traces of requirements and test cases is IBM Doors [IBM Doors, 2017], a requirements management tool, which is used by IEE engineers to both trace software requirements and the system test cases.

| Line | Operation                     | Inputs/Expectations |

|------|-------------------------------|---------------------|

| 1    | Reset power and wait          |                     |

| 2    | ResetPower                    | Time=INIT_TIME      |

| 3    | Set occupant status - Adult   |                     |

| 4    | SetBus                        | Channel = RELAY     |

|      |                               | Capacitance = 85    |

| 5    | Check SeatBeltReminder status |                     |

|      | is Occupied and AirBagControl |                     |

|      | status is Occupied            |                     |

| 6    | ReadAndCheckBus               | D0=OCCUPIED         |

|      |                               | D1=OCCUPIED         |

Table 2.1. An example test case for BodySense

Table 2.1 gives a simplified version of a real test case for *BodySense*. The *BodySense* system test cases are stored in IBM Doors and include both high-level operation descriptions, i.e., informal descriptions of the operations to be performed on the system, and the concrete test driver operations that should be executed during testing. Lines 1, 3, and 5 provide high-level operation descriptions. These lines are followed by the name of the functions that should be executed by the test driver along with the corresponding input/output values. For instance, Line 4 invokes the function *SetBus* with a value indicating that the test driver should simulate the presence of an adult on the seat (for simplicity assume that the field sensor positioned on a seat sends the value 85 on the bus when an adult is seated).

### 2.2 Eliciting Functional Requirements

We assume that software engineers elicit requirements by means of use case specifications, and define domain models of the system by relying upon UML class diagrams. Use case specifications and domain models are common in requirements engineering practice [Larman, 2002], such as in IEE, the partner's organization in our research.

Further, we expect that use case specifications to be elicited according to a use case modelling approach named RUCM [Yue et al., 2013]. Previous work has shown that RUCM is usable and beneficial with respect to making use case specifications less ambiguous and more amenable to precise analysis and design. In addition to this, we stress that one of the results of the research work presented in this dissertation consists in the delivery of the RUCM method to our industrial partner, IEE. The software engineers at IEE have in fact started eliciting the requirements for their products by following the RUCM guidelines.

#### 2.2.1 Eliciting Use Cases with RUCM

Restricted Use Case Modelling (RUCM) is a use case modelling approach [Yue et al., 2013] which is composed of a use case template that merges several aspects of existing templates and a set of well-defined restrictions to the use of natural language for documenting UCSs. RUCM aims to both reduce ambiguity and facilitate automated processing of textual requirements by mean of natural language processing.

The use case template of RUCM contains fields similar to those encountered in standard use case templates [Cockburn, 2000, Bittner, 2002, Phalp et al., 2007]. Table 2.2 shows a simplified version of the use case '*Identify Initial Occupancy Status of a Seat*' of *BodySense* written according to the RUCM rules.

Use case specifications written according to RUCM contain one basic flow (i.e., description of the main success scenario) and one or multiple alternative flows. The basic flow in Table 2.2 describes the main successful path that satisfies stakeholder interests. It contains a sequence of steps and a postcondition (Lines 3-10). A step can be one of the following interactions: an actor sends a request and/or data to the system (Line 4); the system validates a request and/or data (Line 6); the system replies to an actor with a result (Line 7); the system alters its internal state (Line 14).

Alternative flows describe other scenarios, both success and failure. An alternative flow always depends on a condition in a specific step of the basic flow. In RUCM, there are three types of alter-

#### Table 2.2. Use Case Identify Initial Occupancy Status of a Seat

| 1  | Precondition                                                                                                              |

|----|---------------------------------------------------------------------------------------------------------------------------|

| 2  | The system has been initialized                                                                                           |

| 3  | 1.1 Basic Flow                                                                                                            |

| 4  | 1. The seat SENDS occupancy status TO the system.                                                                         |

| 5  | 2. INCLUDE USE CASE Classify occupancy status.                                                                            |

| 6  | 3. The system VALIDATES THAT the occupant class for airbag control is valid and the occupant class for seat belt          |

|    | reminder is valid.                                                                                                        |

| 7  | 4. The system SENDS the occupant class for airbag control TO AirbagControlUnit.                                           |

| 8  | 5. The system SENDS the occupant class for seat belt reminder TO SeatBeltControlUnit.                                     |

| 10 | Postcondition: The occupant class for airbag control and the occupant class for seat belt reminder have been sent.        |

| 11 | 1.2 Bounded Alternative Flow                                                                                              |

| 12 | RFS 2-3                                                                                                                   |

| 13 | 1. IF voltage error is detected THEN                                                                                      |

| 14 | 2. The system resets classification filters.                                                                              |

| 15 |                                                                                                                           |

| 16 | 4. RESUME STEP 1.                                                                                                         |

| 17 | Postcondition: Classification filters have been reset.                                                                    |

| 18 | 1.3 Specific Alternative Flow                                                                                             |

| 19 |                                                                                                                           |

| 20 | 1. IF the occupant class for airbag control is not valid and the occupant class for seat belt reminder is not valid THEN  |

| 21 | 2. The system SENDS the previous occupant class for airbag control TO AirbagControlUnit.                                  |

| 22 | 3. The system SENDS the previous occupant class for seat belt reminder TO SeatBeltControlUnit.                            |

| 23 |                                                                                                                           |

| 24 | 4. ENDIF                                                                                                                  |

| 25 | Postcondition: The previous occupant classes for airbag control and seat belt reminder has been sent to AirbagControlUnit |

|    | and to SeatBeltControlUnit respectively.                                                                                  |

| 26 |                                                                                                                           |

| 27 |                                                                                                                           |

| 28 | 1. IF the occupant class for seat belt reminder is not valid THEN                                                         |

| 29 |                                                                                                                           |

| 30 |                                                                                                                           |

| 31 |                                                                                                                           |

| 32 |                                                                                                                           |

Postcondition: The occupant class for airbag control has been sent to AirbagControlUnit and the previous occupant class 33 for seat belt reminder has been sent to SeatBeltControlUnit.

native flows: *specific*, *bounded* and *global*. A specific alternative flow refers to a step in the basic flow (Lines 19 and 27). A bounded alternative flow refers to more than one step in the basic flow (Line 12) while a global alternative flow refers to any step in the basic flow. For specific and bounded alternative flows, the keyword 'RFS' is used to refer to one or more reference flow steps (Lines 12, 19 and 27).

RUCM includes 26 rules that both restrict the use of natural language (16 rules) and enforce the use of keywords for specifying control structures (10 rules). Most of the rules in the former category (11 rules) aim to reduce ambiguity in use case specifications, while the latter category aims to facilitate the automated processing of the text written in use case specifications.

The keywords defined by RUCM specify conditional logic sentences (IF-THEN-ELSE-ELSEIF-ENDIF), concurrency sentences (MEANWHILE), condition checking sentences (VALIDATES THAT), and iteration sentences (DO-UNTIL). These keywords limit ambiguities in use case specifications. Keywords ABORT and RESUME STEP are used to describe an exceptional exit action and where an alternative flow merges back in its reference flow, respectively. An alternative flow ends either with ABORT or RESUME STEP, which means that the last step of the alternative flow should clearly specify whether the flow returns back to the reference flow and where (using keywords RESUME

STEP followed by a returning step number) or terminates (using keyword ABORT).

Some of the RUCM keywords are shown in the use case in Table 2.2. For example, the keyword '*INCLUDE USE CASE*' in Line 5 indicates the inclusion of other use cases.

The keyword '*VALIDATES THAT*' (Line 6) indicates a condition that must be true to proceed to the next step, otherwise an alternative flow is taken. In Table 2.2, the system proceeds to Step 4 (Line 7) only if the occupant classes for the airbag control and the seat belt reminder are valid (Line 6).

#### **Extensions to RUCM**

As result of our research, we have introduced three main extensions to the original RUCM template, described in the following.

According to the original RUCM template, bounded and global alternative flows begin with the keyword '*IF* .. *THEN*' for the guard condition under which the alternative flow is taken (Line 13). Instead specific alternative flows do not begin with the keyword '*IF* .. *THEN*' since a guard condition is already indicated in its reference flow step (Line 6). We have extended the RUCM template to handle the case in which composite conditions need to be further refined in multiple alternative flows. This is the case for Table 2.2 in which multiple alternative flows are considered to be executed (Lines 12, 19, and 27) when the condition in the reference flow step (Line 6) evaluates to false. This case was originally not covered by RUCM. Therefore, we suggest to use the '*IF* .. *THEN*' keyword also in specific alternative flows (Lines 20 and 28). The alternative flows are evaluated in the order they appear in the use case.

We have also introduced two other extensions to RUCM regarding the adoption of 'IF' conditions and the way input/output messages are expressed. More specifically we have decided to follow the guidelines that suggest not to use multiple branches within the same use case path [Larman, 2002], thus enforcing the adoption of 'IF' conditions only as a mean to specify guard conditions for alternative flows.

Also, we introduced the keyword 'SENDS .. TO' as an RUCM extension for the system-actor interactions. The keyword eases automatic identification of steps for these interactions. According to our experience, in embedded systems the system-actor interactions are always specified in terms of messages. For instance, Step 1 in Table 2.2 (Line 4) indicates an input message from the seat to the system while Step 4 (Line 7) contains an output message from the system to the airbag. Additional keywords can be defined for other systems.

#### 2.2.2 Domain Modelling

We expect that a domain model of the system is produced by relying upon UML class diagrams according to standard software engineering practice. In particular, we expect that the names appearing in entities and attributes of the domain model are consistent with the names appearing in the use case specifications. This practice is enforced by the test case generation technique presented in Chapter 3.

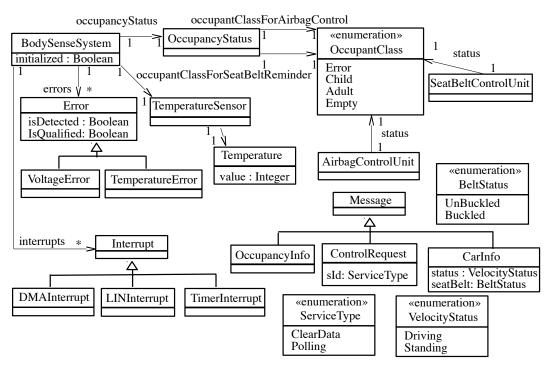

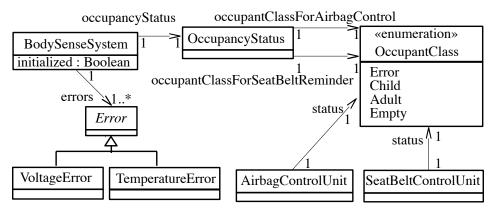

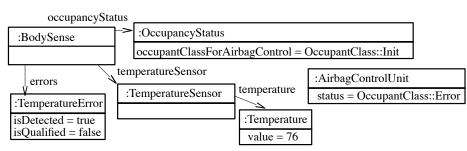

Figure 2.1 shows a portion of the domain model for *BodySense*. There are three car components: *BodySenseSystem*, *AirbagControlUnit*, *SeatBeltControlUnit*. *BodySenseSystem* periodically provides

Figure 2.1. Partial domain model for *BodySense*

the classified occupancy status to the *AirbagControlUnit* and *SeatBeltControlUnit*. *BodySenseSystem* is connected to a temperature sensor which measures the environment temperature.

Figure 2.1 shows that the system must be able to deal with multiple types of errors. The cardinality in the association between *BodySenseSystem* and *Error* shows that zero or multiple errors can be detected in case the corresponding detection condition is satisfied. For example, if the environment temperature goes beyond a certain range, a temperate error will be detected.

Communication between *BodySenseSystem* and other car components, such as *AirbagControlUnit* or *SeatBeltControlUnit*, are via messages sending through the communication bus. For example, the message *OccupancyInfo* and *CarInfo* contain the data of occupancy status and seatbelt status required by *AirbagControlUnit* and *SeatBeltControlUnit*. Engineers (and mechanicians) can request the execution of a service by sending a *ControlRequest* message through the communication bus. For instance, the engineer can send a request for clearing the error data stored in the system by sending a *ControlRequest* message with a *ServiceId* (sId) of type *ClearData*.

*BodySense* also works with several types of interrupts (we show only two in this picture). For example, when sensor data is updated a *DMAInterrupt* is triggered, while when messages arrive on the communication bus a *LINInterrupt* is triggered.

## 2.3 Modelling Timing Requirements

In this dissertation, we assume that the timing requirements of a system are modelled using Communicating Timed Automata [Alur and Dill, 1994]. Timed automata are one of the formalisms commonly used to model timing properties of systems, along with UML statecharts [Larman, 2002]. In this dissertation, we rely upon the former primarily because of the availability of tools that enable model based test generation and analysis of the timing properties. An example of this category of tools is the UPPAAL model checker [Bengtsson et al., 1995], which is one of the components integrated with our toolset. Approaches for translating UML statecharts into Timed Automata can be used when needed [David et al., 2002].

A timed automaton is a tuple (L, l0, C, A, V, E, I), where L is a set of locations,  $l0 \in L$  is the initial location, C is a set of clocks, A is a set of actions, V is a set of state variables, E is a set of edges between locations. I is a set of invariants assigned to locations. Each edge may have an action, a guard and a set of updates. Updates are expressed in form of assignments that can reset clocks or state variables. Each location might be associated with a state invariant that constrains clocks or state variables.

With communicating timed automata, the state of the system is captured by the values of state variables and the set of active locations across all the automata. Actions are used to synchronize different automata. Each action is expressed with the notation *event*? or *event*?. The notation *event*! indicates that the event is sent when the edge is fired, while the notation *event*? indicates that the edge is fired only if this event has been received from another automaton.

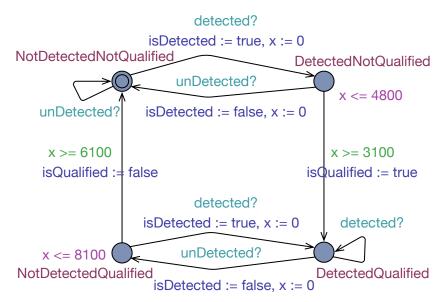

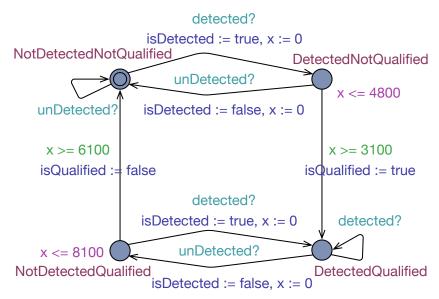

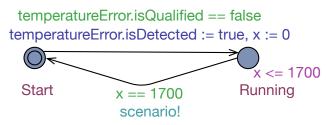

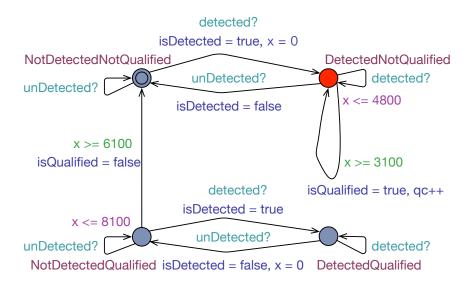

**Figure 2.2.** Automaton that captures how TemperatureErrors are qualified and dequalified in *BodySense*. Edges are labelled by the triple guard (green), action (light blue), and update (blue).

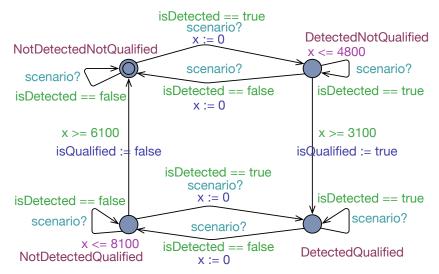

Figure 2.2 shows a timed automaton that captures the timing properties concerning the qualification of temperature errors. The variable x is a clock variable, while *isDetected* and *isQualified* are two state variables. The edge that connects locations *NotDetectedNotQualified* and *DetectedNotQualified* can be fired only when the event *detected*, which indicates that a temperature error has been detected, has been received by the automaton. The location *DetectedNotQualified* has an invariant that indicates that the clock variable x must be below 4800 ms when the location is active. The guard condition on the edge between the location *DetectedNotQualified* and *DetectedQualified* indicates that this edge cannot be fired if the clock x is below 3100. In effect, the edge between locations *DetectedNotQualified* and *DetectedQualified* and *DetectedQualified* and *a value* between 3100 and 4800. TAs are usually modeled this way (i.e., by including time ranges) in practice, to allow for timing uncertainties, since software engineers cannot predict/control with abso-

lute precision when operations start/end when software is running on the actual deployment platform. In Chapter 5 we discuss the problems caused by this uncertainty in the timing specifications of the system.

In general, we expect that software engineers use timed automata to capture both the timing properties of the entities of the domain model and the properties of the environment. The following paragraphs provide additional details for these two cases.

#### **2.3.1** Modelling the Timing Properties of Domain Entities

The identification of timing requirements is a manual activity. We expect that software engineers define a timed automaton for each entity in the domain model that features one or more timing constraints. In the rest of the dissertation, we use the term *timing requirements automata* to refer to timed automata used to model the timing properties of domain entities.

State variables appearing in the timed automata have counterparts in the domain model. More specifically, we expect that each state variable is also an attribute of the entity modelled by the timed automaton. Figure 2.2 shows the automaton that captures the timing constraints related to the entity *TemperatureError*. The variables *isDetected* and *isQualified* are two attributes of the entity *TemperatureError* and, therefore, the assignments to the state variables *isDetected* and *isQualified* capture changes to the state of the entity *TemperatureError*.

Events in the network of timed automata are used both to synchronize with different timed automata, and to indicate the processing of an input or the generation of an output. We have observed that in practice, software engineers may also use events to avoid details that are unnecessary to describe timing requirements, i.e. details about the functional operations that trigger certain state transitions. In fact, software engineers may produce timed automata with edges synchronized with events that stand for the execution of one or several specific functional scenarios. These events are not generated by any other automata of the system; we call these events *scenario events*, since they are expected to be generated as a result of the completion of a functional scenario.

To enable automated generation of timeliness test cases we constrain the adoption of scenario events by requiring that scenario events always lead to updates of state variables (the scenario event *detected* in Figure 2.2, for example, updates the state variable *isDetected*). Proper updating of state variables is required since it is the analysis of such updates that enables one of the techniques proposed in this dissertation, TAUC, to identify dependencies between use case specifications and timed automata (see Chapter 4).

Chapter 4.4 shows how TAUC automatically detects *scenario events* without requiring additional information from software engineers. Our modelling approach allows software engineers to follow usual design practices with reasonably small timed automata models.

#### 2.3.2 Modelling the Timing Properties of the Environment

Environment automata are used to capture the arrival frequency of inputs, including interrupts or messages. This information is necessary to avoid the generation of invalid test cases, e.g. test cases that send inputs with a frequency not supported by the system bus.

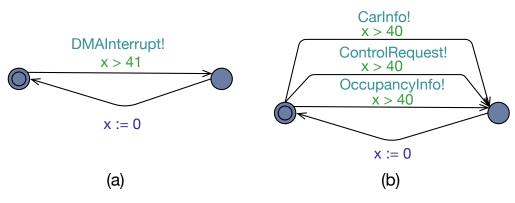

Figure 2.3. Environment automata for BodySense

We model the arrival of inputs by means of events. The event names must match entity names used in the domain model. Figure 2.3 shows two environment automata of *BodySense* that capture timing characteristics of interrupts and messages, respectively. For example, the minimal interarrival time of DMA interrupts is 41 milliseconds (a), while messages' minimal interarrival time is 40 milliseconds (b).

## Chapter 3

## **Automatic Generation of System Test Cases from Use Case Specifications**

In this chapter, we present *Use Case Modelling for System Tests Generation (UMTG)*, an approach for the generation of executable functional test cases. UMTG requires use case specifications written according to RUCM and a domain model of the system, which enables the definition of constraints that are used by UMTG to generate test data and oracles. In addition, the approach includes a specification refinement activity during which engineers are asked to provide constraints, referring to the domain model, defined with the Object Constraint Language (OCL) [OMG, 2004]. OCL is the natural choice when defining high-level constraints on class diagrams. The constraints are used to generate test data via constraint solving [Ali et al., 2013].

UMTG employs NLP to build *Use Case Test Models (UCTM)* from RUCM specifications. UCTMs capture the control flow implicitly described in the RUCM specification. During NLP, a list of textual descriptions of pre, post and guard conditions in use cases is extracted. The software engineer further manually reformulates these textual descriptions using OCL constraints based on the domain model, iteratively refining the latter when required. Our approach combines UCTMs with the OCL constraints to enable automated test generation. As a final step, it automatically generates system test cases with test inputs and outputs from UCTMs via constraint solving [Ali et al., 2013].

To summarise, the contributions of this chapter are:

- UMTG, an approach for the automatic generation of executable system test cases from use case specifications and a domain model, without resorting to behavioral modelling;

- an NLP technique generating test models (UCTMs) from use case specifications expressed with RUCM;

- an algorithm combining UCTMs and constraint solving to automatically generate test inputs;

- a demonstration of the feasibility of the approach based on an industrial case study in the automotive domain.

This chapter is structured as follows. Section 3.1 introduces the challenges that need to be tackled in order to design an automated test generation approach for embedded systems. In Section 3.2, we provide an overview of UMTG. In Section 3.3 we present the NLP pipeline in our approach. In Sections 3.4 to 3.8, we detail the automated activities in UMTG. In Section 3.9, we present our empirical evaluation.

## 3.1 Motivation

This section provides details about the challenges that need to be tackled in order to automate the generation of functional test cases in the context of an embedded system.

To illustrate the problem we introduce a simplified version of a test case for a scenario of the use case '*Identify initial occupancy status of a seat*' for *BodySense* in Table 3.1. Lines 1, 3, and 5 provide high-level operation descriptions, i.e., informal descriptions of the operations to be performed on the system. These lines are followed by the name of the functions that should be executed by the test driver along with the corresponding input/output values. For instance, Line 4 invokes the function *SetBus* with a value indicating that the test driver should simulate the presence of an adult on the seat (for simplicity assume that the field sensor positioned on a seat sends the value 85 on the bus when an adult is seated).

| Line No. | Operation                                 | Inputs/Expectations |

|----------|-------------------------------------------|---------------------|

| 1        | Reset power and wait                      |                     |

| 2        | ResetPower                                | Time=INIT_TIME      |

| 3        | Set occupant status - Adult               |                     |

| 4        | SetBus                                    | Channel = RELAY     |

|          |                                           | Capacitance = 85    |

| 5        | Check SeatBeltReminder status is Occupied |                     |

|          | and AirBagControl status is Occupied      |                     |

| 6        | ReadAndCheckBus                           | D0=OCCUPIED         |

|          |                                           | D1=OCCUPIED         |

Table 3.1. An example test case for BodySense

The exhaustive test cases needed to validate a safety-critical embedded system are difficult both to derive and maintain as requirements are changing. For instance, the real test case from which we derived the simplified test case in Table 3.1, includes 30 test steps, around 50 variable assignments, and 15 references to other specifications providing further explanations about the inputs. The effort required to specify test cases for the whole *BodySense* is overwhelming. A test suite exercising all use case scenarios would include more than 400 such test cases. Without automated test case generation, such testing activity remains not only expensive but also infeasible under typical time constraints.

Within the context of testing safety-critical embedded software system such as *BodySense*, we identify three challenges that need to be considered for the automatic generation of system test cases from functional requirements:

*Feasible Modelling.* Most of the existing automatic system test generation approaches are modelbased and rely upon behavioural models such as sequence or activity diagrams. In complex industrial systems, behavioural models that are precise enough to enable test automation are quite complex that their specification cost is prohibitive and the task is often perceived as overwhelming by engineers. To evaluate the applicability of behavioral modelling on *BodySense*, we asked the IEE software engineers to specify system sequence diagrams corresponding to the use cases of *BodySense*. For example, the system sequence diagram for the use case '*Identify initial occupancy status of a seat*', includes 74 messages, 19 nested blocks, and 24 references to other system sequence diagrams that had to be derived. This was clearly considered too complex for software engineers and required significant help from the authors of this paper, and many iterations and meetings. Note that this is a relatively simple use case compared to what can be found in other, more complex systems at IEE, and that, therefore, our conclusion was that behavioural modelling was not a practical option for test automation.

*Test Data Generation.* Without behavioral modelling, most approaches mainly exploit NL requirements specifications in which it is hard to extract test data for executable test cases. Test cases derived in such a way that requires significant manual intervention. For instance, even the simplified test case in Table 3.1 has 50 variable assignments to be manually entered as test input. Automatically generating test data, and not just abstract test scenarios, is therefore important.

**Deployment of the Software under Test.** Execution of test cases for a system like *BodySense* entails the deployment of software under test on the target environment. To speed up software testing, test case execution is typically automated through test scripts invoking test driver functions. These functions simulate sensor inputs and computational results receiving from a communication bus. Any test generation approach should generate appropriate functions and test data in a processable format for the test driver. For instance, the test drivers in *BodySense* need to invoke driver functions (e.g., *SetBus*) to simulate occupancy on a seat.

### **3.2** Overview of the Approach

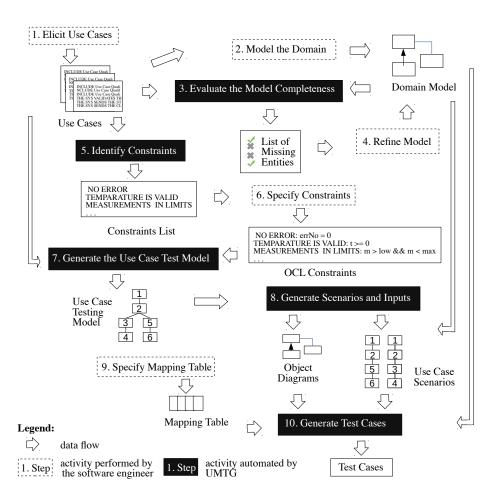

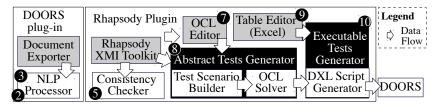

Figure 3.1 shows the main steps of the approach. The goal of UMTG is to address the challenges given in Section 3.1. In UMTG, behavioral information and high-level operation descriptions are generated from use cases (*the first challenge*), test inputs are generated through constraint solving (*the second challenge*), while test driver functions corresponding to informal descriptions and oracles implementing the postconditions of the use case scenarios are generated through mapping tables provided by the software engineer (*the third challenge*).

The software engineer elicits requirements with RUCM (Step 1). The domain model is manually created as a UML class diagram (Step 2). UMTG automatically checks if the domain model includes all entities mentioned in the use cases (Step 3) and tool support is provided to guide engineers in completing the domain model. NLP is used to extract domain entities from the use cases. Missing entities are shown to the software engineer who refines the domain model (Step 4). Steps 3 and 4 are iterative: the domain model is refined until it is complete.

Once the domain model is completed, textual descriptions of pre, post and guard conditions in the use cases are automatically extracted (Step 5) to be reformulated as OCL constraints by engineers (Step 6). UMTG further processes the use cases with the OCL constraints to generate a Use Case Test Model for each use case (Step 7). A generated test model is a directed graph that explicitly captures the implicit behavioural information in the corresponding use case.

UMTG relies on constraint solving for OCL constraints that are attached to the nodes of the test models. The goal is to generate test inputs associated with use case scenarios (Step 8). We use the term use case scenario for a sequence of use case steps that start with a use case precondition and ends with a postcondition of either a basic or alternative flow. Test inputs cover all paths in the testing model and therefore cover all possible use case scenarios.

The software engineer provides a mapping table that maps high-level operation descriptions and

Figure 3.1. Overview of the UMTG Approach

test inputs to the concrete driver functions and inputs that should be executed by test cases (Step 9). Executable test cases are automatically generated through the mapping table (Step 10). If the test infrastructure and hardware drivers change in the course of the system lifespan, then only the mapping table needs to change.

The rest of the chapter provides a detailed description of each step of UMTG shown in Figure 3.1, except Steps 1 and 2 already introduced in Chapter 2.2.

## 3.3 NLP Pipeline for UMTG

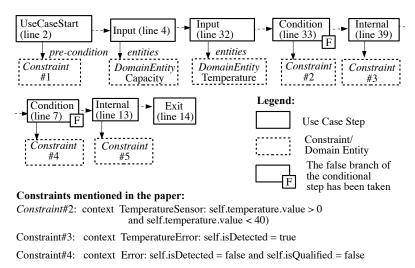

Three UMTG steps in Figure 3.1, 'evaluate the model completeness', 'identify constraints', and 'generate the use case test model', are supported by an NLP application to extract behavioral information from RUCM use cases.

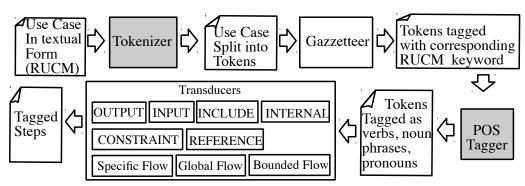

The NLP application in UMTG is based on the GATE workbench [Cunningham et al., 2002], an open source NLP framework, and implements the analysis pipeline in Figure 3.2. The pipeline includes both default NLP components (grey) and components configured to process RUCM use cases (white). The *Tokenizer* splits the use cases into tokens. The *Gazetteer* identifies the RUCM keywords. The *POS Tagger* tags tokens according to their nature: *verb*, *noun*, and *pronoun*. The

Figure 3.2. NLP pipeline applied to extract the behaviour of a Use Case

pipeline is terminated by a set of *transducers* that tag block of words to distinguish the kinds of RUCM steps: output, input, include, and internal operations. The pipeline has also *transducers* to distinguish specific, bounded and global alternative flows, plus reference blocks, and constraints part of guard and post conditions.

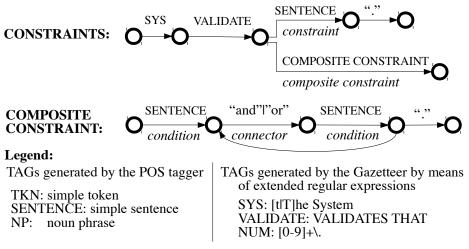

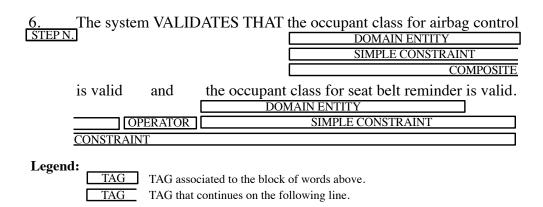

Figure 3.3 gives an example transducer for constraints. Capital names on the arrows correspond to the transducer's inputs, i.e., tags previously identified by either the POS tagger, the gazzetteer or other transducers. Italic names show the tags associated with the transducer to the words corresponding to the transducer input. Figure 3.4 gives the tags associated with the use case step in Line 6 of Table 2.2 after the execution of the transducer in Figure 3.3. In Figure 3.4, multiple tags are associated with the same block of words: the clause '*the occupant class for airbag control is valid*' is tagged both as a *simple constraint* and as a part of a *composite constraint*.

Figure 3.3. Part of the transducer that identifies constraints

Figure 3.4. Tags associated with the use case step in Lines 6 of Table 2.2

### **3.4** Evaluation of the Model Completeness

UMTG automatically evaluates the model completeness (Step 3 in Figure 3.1) by identifying missing domain entities. This is done by checking correspondences between the domain entities identified by the NLP application and the entities in the domain model. Please recall that we assume naming conventions for the use cases and domain model<sup>1</sup>.

Figure 3.5. Portion of the domain model for BodySense

Sometimes domain entities identified in a use case are not modelled as classes but as attributes. Figure 3.5 shows a simplified portion of the domain model for *BodySense* where the domain entities 'occupant class for airbag control' and 'occupant class for seat belt reminder' are modelled as attributes of the class OccupancyStatus. UMTG follows a simple yet effective solution to check class and attribute names. For each domain entity identified through NLP, UMTG generates an entity name by removing all white spaces and by putting all first letters following white spaces in capital. For instance, the domain entity 'occupant class for airbag control' becomes 'OccupantClassForAirbag-Control'. UMTG checks generated entity names in the domain model. If the entity name appears either as a class name or as an attribute name, the entity is considered present, otherwise it is considered missing.

<sup>&</sup>lt;sup>1</sup>The precise identification of correspondences between the domain entities in the use cases and the entities in the domain model in the presence of inconsistent name usage can be tackled by syntactic and semantic similarity checking algorithms but it is not in the scope of this dissertation.

| # | Condition in the Use Case        | Corresponding OCL Constraint                                                                         |

|---|----------------------------------|------------------------------------------------------------------------------------------------------|

| 1 | the occupant class for airbag    | BodySenseSystem.allInstances()                                                                       |

|   | control is valid                 | $\rightarrow$ forAll(b b.occupancyStatus.occupantClassForAirbagControl $<>$ OccupantClass :: Error)  |

| 2 | the occupant class for seat belt | BodySenseSystem.allInstances()                                                                       |

|   | reminder is valid                | $\rightarrow$ forAll(b]b.occupancyStatus.occupantClassForSeatBeltReminder <> OccupantClass :: Error) |

| 3 | voltage error is detected        | Error.allInstances()                                                                                 |

|   | voltage error is detected        | $\rightarrow$ select(e e.oclIsKindOf(VoltageError)) $\rightarrow$ forAll(v v.valid = true)           |

| 4 | the occupant classes for airbag  | $AirbagControlUnit.allInstances() \rightarrow forAll(a a.status = a.bodySense.occupancyStatus$       |

|   | control and seat belt reminder   | .occupantClassForAirbagControl) AND SeatBeltControlUnit.allInstances()                               |

|   | have been sent                   | $\rightarrow$ forAll(s s.status = s.bodySense.occupancyStatus.occupantClassForSeatBeltReminder)      |

| 5 | The system has been initialized  | $BodySenseSystem.allInstances() \rightarrow forAll(b b.initialized = true)$                          |

| 6 | The system resets classification | $BodySenseSystem.allInstances() \rightarrow forAll(b b.occupancyStatus.occupant$                     |

|   | filters                          | ClassForSeatBeltReminder = null AND b.occupancyStatus.occupantClassForAirbagControl = null)          |

Table 3.2. Some constraints for the use case 'Identify Occupancy Status of a Seat'.

## **3.5** Identification of Constraints