## Fast determination of instability in a non-linear Clock and Data Recovery circuit

Marijn Verbeke<sup>1</sup>, Pieter Rombouts <sup>2</sup>, Arno Vyncke<sup>1</sup>, Johan Bauwelinck<sup>1</sup>, and Guy Torfs<sup>1</sup> <sup>1</sup>INTEC design, Ghent University – iMinds – IMEC <sup>2</sup> CAS – ELIS, Ghent University

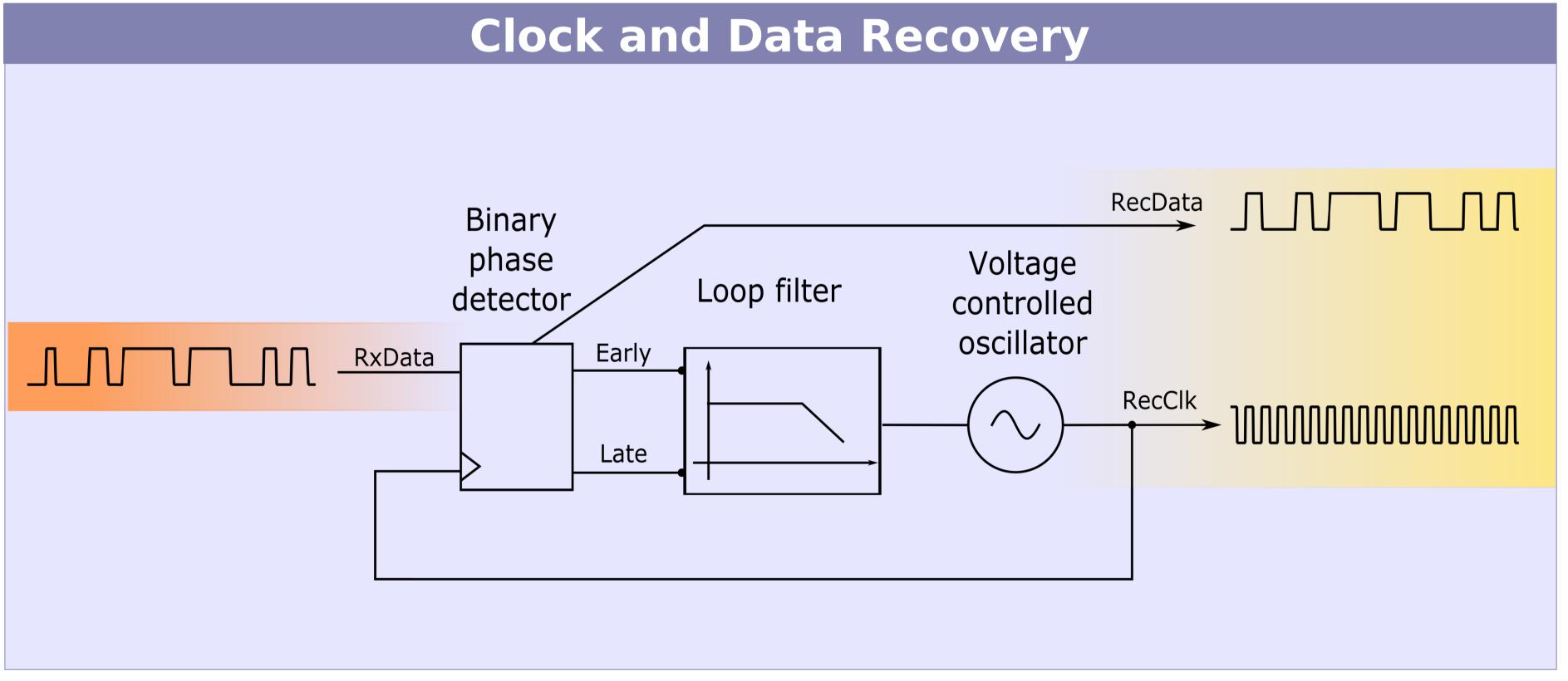

## Why Clock and Data Recovery circuits are indispensable **Transmitter** Clock Transmitted Data Received Data Receiver: CDR Recovered Clock Recovered Data

- High-speed serial data streams are sent without an accompanying clock signal

- Unwanted effects of long interconnections and other stress factors on the communication link distort the transmitted data signal

- The receiver recreates a clock (timing signal information) from the received data signal

- Using the recovered clock, the digital data is extracted from the detoriated signal and can be further processed

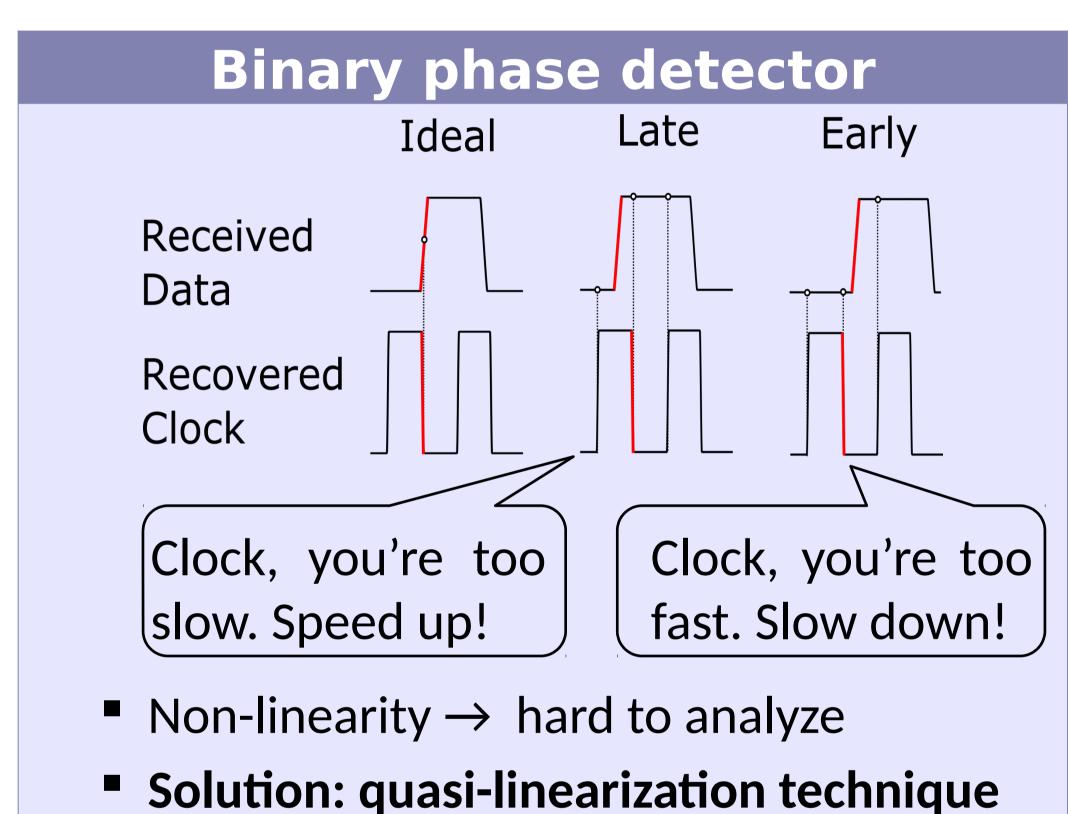

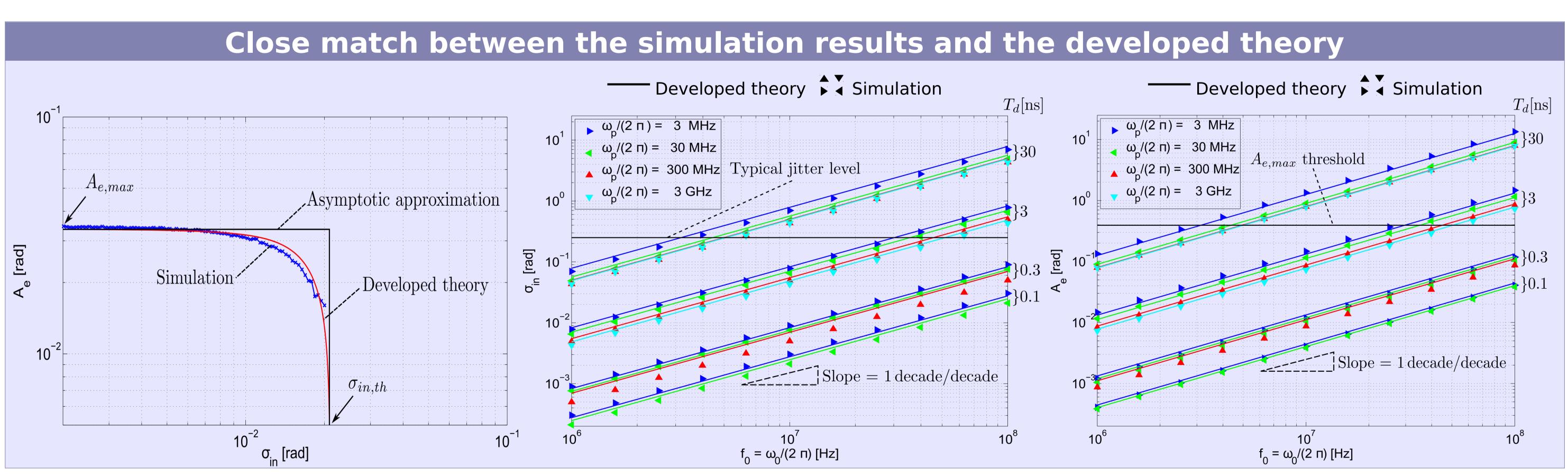

## Fast determination of instability

- Stability = essential property of the system

- New method is 1000x faster than brute-force simulation

- Further analytical approximations lead to simple equations for a quick check!

$$A_{e,max} \approx \frac{8 \, \alpha}{\pi^2} \, T_d \, \omega_0$$

$$\sigma_{in,th} \approx \frac{1}{2} \sqrt{\frac{\pi}{2}} A_{e,max}$$

## Acknowledgements

This work was supported by the Agency for Innovation by Science and Technology in Flanders (IWT) and the EU FP7 DISCUS Project.