## HARDWARE ARCHITECTURE FOR SEMANTIC COMPARISON

A Dissertation

by

## SUNEIL MOHAN

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

May 2012

Major Subject: Computer Engineering

## HARDWARE ARCHITECTURE FOR SEMANTIC COMPARISON

## A Dissertation

by

## SUNEIL MOHAN

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

## Approved by:

Chair of Committee, Rabi N. Mahapatra Committee Members, Riccardo Bettati

Deepa Kundur

Duncan M. Walker

Head of Department, Duncan M. Walker

May 2012

Major Subject: Computer Engineering

#### ABSTRACT

Hardware Architecture for Semantic Comparison. (May 2012) Suneil Mohan, B.E, Anna University, Chennai, India Chair of Advisory Committee: Dr. Rabi N. Mahapatra

Semantic Routed Networks provide a superior infrastructure for complex search engines. In a Semantic Routed Network (SRN), the routers are the critical component and they perform semantic comparison as their key computation. As the amount of information available on the Internet grows, the speed and efficiency with which information can be retrieved to the user becomes important. Most current search engines scale to meet the growing demand by deploying large data centers with general purpose computers that consume many megawatts of power. Reducing the power consumption of these data centers while providing better performance, will help reduce the costs of operation significantly.

Performing operations in parallel is a key optimization step for better performance on general purpose CPUs. Current techniques for parallelization include architectures that are multi-core and have multiple thread handling capabilities. These coarse grained approaches have considerable resource management overhead and provide only sub-linear speedup.

This dissertation proposes techniques towards a highly parallel, power efficient architecture that performs semantic comparisons as its core activity. Hardware-centric parallel algorithms have been developed to populate the required data structures followed by computation of semantic similarity. The performance of the proposed design is further enhanced using a pipelined architecture. The proposed algorithms were also implemented on two contemporary platforms such as the Nvidia CUDA and an FPGA for performance comparison. In order to validate the designs, a seman-

tic benchmark was also been created. It has been shown that a dedicated semantic comparator delivers significantly better performance compared to other platforms.

Results show that the proposed hardware semantic comparison architecture delivers a speedup performance of up to  $10^5$  while reducing power consumption by 80% compared to traditional computing platforms. Future research directions including better power optimization, architecting the complete semantic router and using the semantic benchmark for SRN research are also discussed.

# DEDICATION

To my parents

#### ACKNOWLEDGMENTS

Completing my PhD and writing this dissertation would not have been possible without the guidance, help and support of many individuals who in their unique ways helped me through my time in graduate school. It is a pleasure to be able to convey my gratitude to you all. Forgive me, if due to an extremely unfortunate oversight, I miss someone.

First and foremost, my utmost gratitude and thanks are due to my advisor Dr. Rabi Mahapatra. Without his valuable guidance, support and advice, none of this would have been possible. He has been my advisor, mentor and role model throughout my time here at Texas A & M.

I gratefully acknowledge the contributions of my advisory committee members Dr. Hank Walker, Dr. Riccardo Bettati and Dr. Deepa Kundur for their valuable feedback and guidance at critical points that enabled the successful completion of my research and my PhD.

I would not have been here if it had not been for my family. Thank to my parents for their support, prayers and advice in immeasurable quantities. To my extended family who believed that I could 'do it' even when I had serious doubts about the whole grad school endeavor, thank you for believing in me. I appreciate you listening to me rant and supporting me in so many ways over the years.

Many thanks go to my present and former colleagues at the Embedded Systems and Codesign Group including Aalap, Nikhil, Suman, Ron, Jason & Jagannath. You have helped me in everything from debugging code to proof reading papers to sharing in my joys and sorrows through graduate school.

I've been fortunate to have a close group of friends who have been there for me in more ways than I can individually list: Thank you Parikshith, Swetha, Kymberleigh, Swati, Vinodh, Lilian, Emily, Amy, Ram, Siva, Ayan, Nur, Suresh & Arun . You've been there for me when I needed someone to talk to and given me much needed

support and encouragement. I cannot thank you all enough. A special thank you to Parikshith for being an amazing house-mate who was always there to support me, listen to me rant, be a role model and not drive me up the wall. As I heard horror stories about other people's weird house-mates, I was always grateful that we had a calm setup. To the members of the Phorum, I thank you for your everlasting support and encouragement through some of the toughest times.

The staff of the Department of Computer Science and Engineering deserve a special thank you. Thank you Dave, Jeremy, Tony and the rest of CSG for helping me with computers and related technical support. Thank you Adrienne and Lindsay for answering patiently the many questions that I've posed to you over the years. Thank you Tina, Marilyn, Sybil, Lisa and the rest of the Advising, Accounting and Administrative staff of the department for helping me with various issues. Thank you Bruce for handling the logistics including packages, keys and other facility management issues that I've approached you with. Thank you all for answering the many hundreds of questions that I must have asked each of you personally over time.

Thank you Dr. Mahapatra, Dr. Hurley, Dr. Walker, Dr. Bettati and Dr. Sarin for having me as your Teaching Assistant over the many semesters. It was an incredible experience that I would not trade for another. Thank you also to my students from the various classes. You guys taught me a whole lot and introduced me to the American undergraduate culture in a way that would not have been possible otherwise.

Finally, I would like to thank the many more people who have contributed towards my ability to reach this stage in my education. I would like to thank you and apologize for not being able to name you individually as I would have liked to; you did play an important role in my ability to complete my PhD.

## NOMENCLATURE

API Application Programming Interface

BF Bloom Filter

CAM Content Addressable Memory

CPU Central Processing Unit

CUDA Compute Unified Device Architecture

DFF D Flip Flop

FPGA Field Programmable Gate Array

NIH National Institute of Health

$P_{false+ve}$  Probability of False Positive

RAM Random Access Memory

SoC System On Chip

SIMD Single Instruction Multiple Data

SRN Semantic Routed Network

TF-IDF Term Frequency - Inverse Document Frequency

UMLS Unified Medical Language System

# TABLE OF CONTENTS

| Pa                                                                                                                                                                                                                                                                                                                                                                                                                                                  | age                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| ABSTRACT                                                                                                                                                                                                                                                                                                                                                                                                                                            | iii                  |

| DEDICATION                                                                                                                                                                                                                                                                                                                                                                                                                                          | V                    |

| ACKNOWLEDGMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                     | vi                   |

| NOMENCLATURE                                                                                                                                                                                                                                                                                                                                                                                                                                        | viii                 |

| TABLE OF CONTENTS                                                                                                                                                                                                                                                                                                                                                                                                                                   | ix                   |

| LIST OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                      | xii                  |

| LIST OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                     | xiii                 |

| 1. INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                    |

| 2. BACKGROUND AND RELATED WORK                                                                                                                                                                                                                                                                                                                                                                                                                      | 7                    |

| 2.1 Semantic Routed Networks  2.2 Semantic Routed Networks  2.2.1 Overview  2.2.2 Methods and Techniques Involved in SRN  2.2.3 Application of SRN to Search Engines  2.3 Vector Based Semantic Comparison  2.4 Challenge in Dot Product Computation  2.5 Bloom Filter Basics  2.5.1 Element Insertion  2.5.2 Membership Testing  2.6 FNV Algorithm  2.6.1 Overview  2.6.2 Algorithm & Relevant Parameters  2.6.3 Standard Values of Key Parameters |                      |

| 3. OVERVIEW OF SEMANTIC COMPARISON                                                                                                                                                                                                                                                                                                                                                                                                                  | 22                   |

| 3.1 Semantic Descriptor                                                                                                                                                                                                                                                                                                                                                                                                                             | 22<br>24<br>26<br>26 |

|    |            |                                                                                                                    | Page            |

|----|------------|--------------------------------------------------------------------------------------------------------------------|-----------------|

| 4. | CR         | EATION OF REQUIRED DATA STRUCTURES                                                                                 | 29              |

|    | 4.1<br>4.2 | Description of the Data Structures                                                                                 |                 |

|    | 4.3        | 4.2.1 Consolidation of Bloom Filters                                                                               | $\frac{32}{32}$ |

|    | 1.0        | 4.3.1 Analysis of Hash functions Used for BF Index Generation                                                      |                 |

|    |            | 4.3.2 Power Draw by Stages-A & B                                                                                   |                 |

| 5. | СО         | MPUTATION OF COSINE SIMILARITY                                                                                     | 37              |

|    | 5.1        | Introduction                                                                                                       | 37              |

|    | 5.2        | Overview of the Parallel Algorithm                                                                                 | 38              |

|    | 5.3        | Overview of Hardware Implementation                                                                                | 38              |

|    | 5.4        | Common Vector Identification                                                                                       | 39              |

|    | 5.5        | Extraction of Coefficients                                                                                         | 40              |

|    | 5.6        | Multiplication and Summation                                                                                       | 41              |

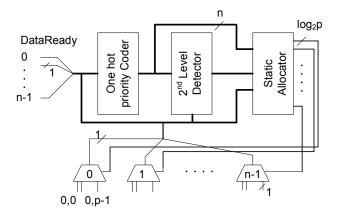

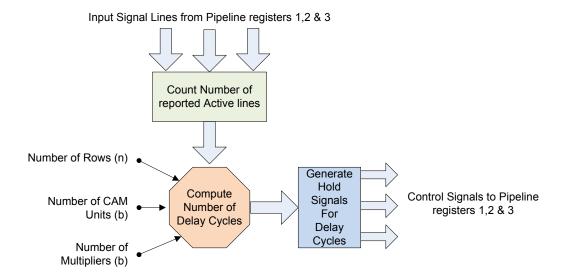

|    | 5.7        | Scheduling Logic                                                                                                   | 42<br>44        |

|    |            | 5.7.1 Design of the Scheduler                                                                                      | 45              |

|    |            | 5.7.3 Design & Operation of Global Allocator                                                                       | 46              |

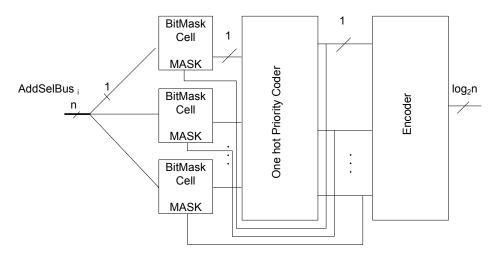

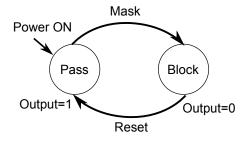

|    |            | 5.7.4 Design & Operation of Address Selector                                                                       | 47              |

|    | 5.8        | Timing Analysis                                                                                                    | 48              |

|    |            | 5.8.1 Overall Timing Analysis                                                                                      | 49              |

|    | 5.9        | Power Figures                                                                                                      | 50              |

|    | 5.10       |                                                                                                                    | 50              |

|    |            | 5.10.1 Comparison with Server Class Processor                                                                      | 50              |

|    |            | 5.10.2 Power Consumption per Functional Block                                                                      | 53              |

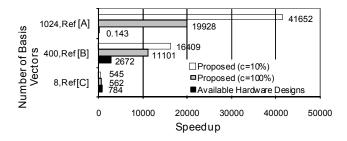

|    |            | 5.10.3 Comparison with Other Hardware Designs                                                                      | 54              |

|    |            | 5.10.4 Overall Execution Time                                                                                      | 55              |

|    |            | 5.10.5 Variation of Number of Basis Vectors                                                                        | 56              |

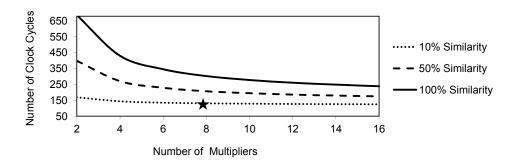

|    |            | 5.10.6 Variation in Speedup with Similarity                                                                        | 56              |

|    |            | 5.10.7 Variation in Timing due to Number of CAM Units 5.10.8 Variation in Timing due to Number of Multiplier Units | 57<br>57        |

| 6. |            | ERFORMANCE ENHANCEMENTS AND ALTERNATIVE IMPLE-<br>NTATIONS                                                         | 59              |

|    | 6.1        | Pipelining                                                                                                         | 59              |

|    |            | 6.1.1 Implementation                                                                                               | 59              |

|    |            | 6.1.2 Operation                                                                                                    | 61              |

|    |            | 6.1.3 Results                                                                                                      | 62              |

|    |                          |                                | Page                                               |

|----|--------------------------|--------------------------------|----------------------------------------------------|

|    | 6.2                      | CUDA Implementation            | 63<br>63<br>64<br>65<br>67<br>68<br>69<br>70<br>72 |

|    | 0.3                      | FPGA Implementation            | 78                                                 |

| 7. | CR                       | EATION OF A SEMANTIC BENCHMARK | 81                                                 |

|    | 7.1<br>7.2<br>7.3<br>7.4 | Need for a Semantic Benchmark  | 82<br>82                                           |

| 8. | СО                       | NCLUSIONS AND FUTURE WORK      | 85                                                 |

|    | 8.1<br>8.2               | Future Work                    |                                                    |

| RE | EFER                     | ENCES                          | 88                                                 |

| VI | ТА                       |                                | 95                                                 |

# LIST OF TABLES

| TAI | BLE                                                                  | Page |

|-----|----------------------------------------------------------------------|------|

| 2.1 | Values of $FNV_{prime}$ for Different Sizes of $n$                   | . 21 |

| 2.2 | Values of offset_basis for Different Sizes of $n$                    | . 21 |

| 4.1 | Some Possible Variations of Hash Functions                           | . 33 |

| 4.2 | Power Draw by One Instance of the FNV module                         | . 34 |

| 4.3 | Overall Power Draw by Stages A & B                                   | . 35 |

| 5.1 | Power Figures for Computation of Cosine Similarity                   | . 50 |

| 5.2 | Superior Performance of Hardware Design                              | . 53 |

| 5.3 | Power Consumed by Each Functional Block                              | . 54 |

| 5.4 | Speedup Comparison with Other Hardware Designs                       | . 55 |

| 6.1 | Comparative Results between Pipelined and Non-Pipelined Designs $$ . | . 62 |

| 6.2 | Baseline Power Figures                                               | . 74 |

| 6.3 | Execution Times of GPU and CPU                                       | . 76 |

| 6.4 | Energy Consumption for Different Table Sizes                         | . 77 |

| 6.5 | FPGA Resource Utilization                                            | . 80 |

| 6.6 | FPGA Power Consumption                                               | . 80 |

| 7.1 | Datasets in Semantic Benchmark Suite                                 | . 84 |

# LIST OF FIGURES

| FIG | FURE                                                  | Page |

|-----|-------------------------------------------------------|------|

| 2.1 | Abstract Model of a Semantic Routed Network           | . 8  |

| 2.2 | Semantic Routing Table                                | . 10 |

| 2.3 | Routing Table Optimization                            | . 12 |

| 2.4 | Architecture of a Typical Search Engine               | . 13 |

| 2.5 | Search Engine with SRN Integrated                     | . 14 |

| 2.6 | Tensor Model of Semantic Comparison                   | . 16 |

| 2.7 | Bloom Filter: Insertion                               | . 18 |

| 2.8 | Bloom Filter: Membership Testing                      | . 18 |

| 3.1 | Concept Trees of Two Sentences                        | . 23 |

| 3.2 | Conversion of Concept Tree into Tensor Representation | . 23 |

| 3.3 | Tabular Form of Semantic Descriptor                   | . 24 |

| 3.4 | Sequence of Steps for Semantic Comparison             | . 25 |

| 3.5 | Overall Stages of Processing                          | . 27 |

| 4.1 | Stages Involved in Generating Data Structures         | . 29 |

| 4.2 | Components of Data Structure                          | . 30 |

| 4.3 | Populating the Data Structure                         | . 30 |

| 4.4 | Bloom Filter Index Generation                         | . 31 |

| 4.5 | Bloom Filter Consolidation                            | . 32 |

| 5.1 | Stages Involved in Cosine Similarity Computation      | . 37 |

| FIG  | URE                                                                                     | Page |

|------|-----------------------------------------------------------------------------------------|------|

| 5.2  | Steps of Computing Cosine Similarity                                                    | 39   |

| 5.3  | Identification of Common Basis Vectors                                                  | 40   |

| 5.4  | Extraction of Coefficients                                                              | 41   |

| 5.5  | Multiplication and Summation                                                            | 42   |

| 5.6  | Location of Scheduler-1 between Stages C & D                                            | 43   |

| 5.7  | Internal Structure of the Scheduler                                                     | 44   |

| 5.8  | Timing Diagram of the Scheduler                                                         | 45   |

| 5.9  | Details of Global Allocator                                                             | 46   |

| 5.10 | Details of Address Selector                                                             | 47   |

| 5.11 | State Diagram of BitMask Cell                                                           | 48   |

| 5.12 | Comparison of Speedup Against Other Hardware Designs                                    | 54   |

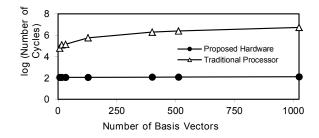

| 5.13 | Variation in Number of Clock Cycles between Proposed Hardware and Traditional Processor | 56   |

| 5.14 | Variation in Execution Time due to Number of Basis Vectors                              | 56   |

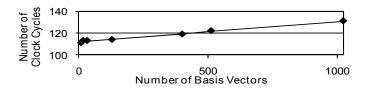

| 5.15 | Variation of Speedup with Variation in Similarity                                       | 57   |

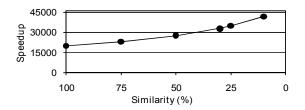

| 5.16 | Variation in Execution Time due to Number of CAM Units                                  | 57   |

| 5.17 | Variation in Execution Time due to Number of Multiplier Units                           | 58   |

| 6.1  | Overall Architecture with Pipeline Enabled                                              | 60   |

| 6.2  | Block Diagram of Pipeline Controller                                                    | 61   |

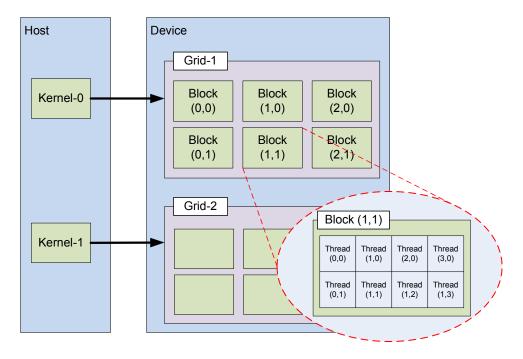

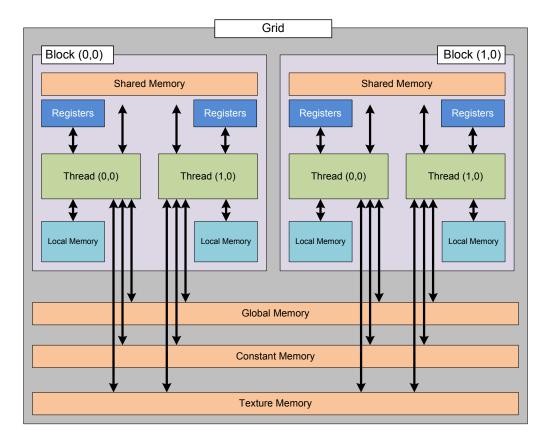

| 6.3  | CUDA Logical Layout                                                                     | 65   |

| 6.4  | CUDA Memory Model                                                                       | 66   |

| FIGU | URE                                                                 | Pa | ıge |

|------|---------------------------------------------------------------------|----|-----|

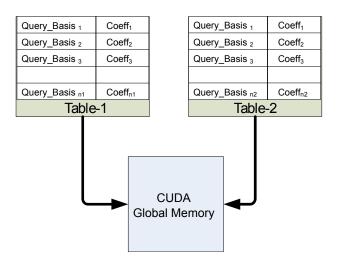

| 6.5  | Copying Tables into CUDA Memory                                     |    | 68  |

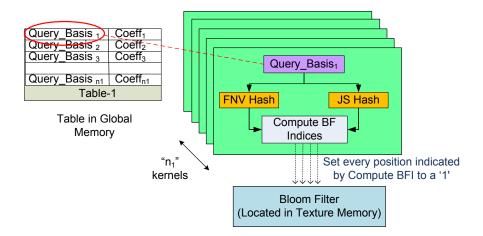

| 6.6  | Encoding Elements of Table-1 using Concurrent Kernels               |    | 69  |

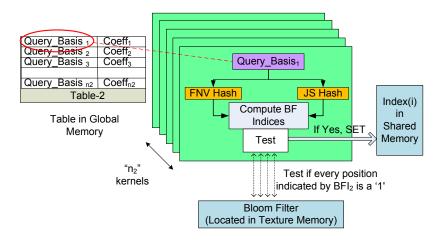

| 6.7  | Encoding Elements of Table-2 using Concurrent Kernels               |    | 70  |

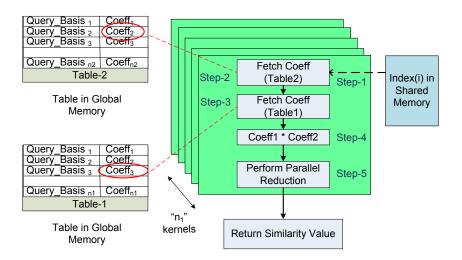

| 6.8  | Extracting Coefficients and Performing Parallel Reduction           |    | 71  |

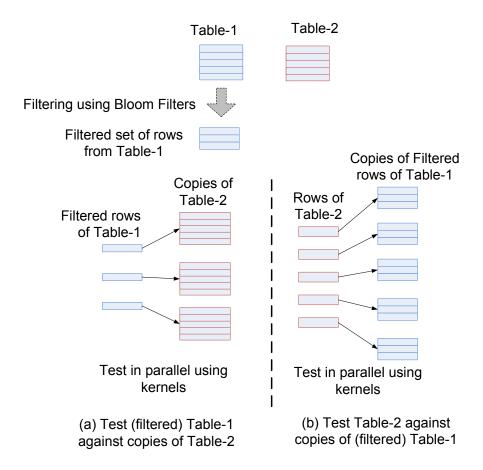

| 6.9  | Alternative Methods of Performing Extraction of Common Coefficients |    | 72  |

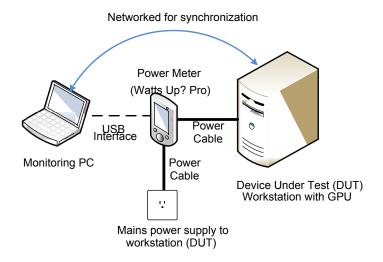

| 6.10 | Setup for Power Profiling                                           |    | 73  |

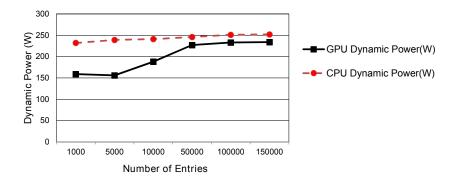

| 6.11 | Dynamic Power Consumption                                           |    | 77  |

| 6.12 | Architecture of FPGA Implementation                                 |    | 78  |

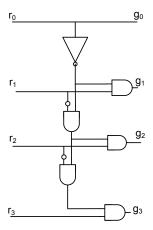

| 6.13 | Schematic of Fixed Priority Arbiter                                 |    | 79  |

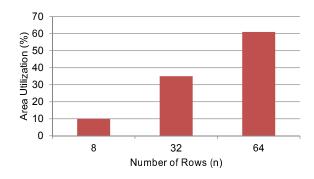

| 6.14 | Area Usage on the FPGA for Varying Number of Rows                   |    | 80  |

| 7.1  | Sample of Corpus from UMLS Semantic Network                         |    | 83  |

| 7.2  | Sample of Tensors after Processing UMLS Corpus                      |    | 83  |

#### 1. INTRODUCTION

Searching for information has become an important activity on the Internet and other information systems. At present the world wide consumption of the web search as a service is estimated to be 13 billion search queries per month and growing at 38% annually [1].

Users increasingly expect that search engines provide intelligent and relevant matches. For example, when they enter a search term such as *healthy lifestyle*; they expect that articles and web-links that cover a broad range of topics related to a *healthy lifestyle* such as *balanced diet*, exercise and *time management* be made available to them.

As the amount of information available on the web grows, there is increased demand for relevant and meaningful search results. The first search engines on the web used to perform simple keyword comparisons. This is no longer sufficient. Users are no longer satisfied with search engines returning simple keyword match documents. Indeed, returning simple keyword search results these days would result in millions and millions of search results, most of which would have no relevance to the query.

With the increase in the pervasiveness of the web, massively increasing usage and demands placed on search engines, it is not surprising that implementing a fast meaningful search service is challenging. Current search engines require a lot of processing power because of the volume of data involved. Hence, search engines such as Google and Yahoo are forced to deploy a large number of servers in data centers to service the enormous web traffic [2].

This dissertation follows the style of IEEE Transactions on Parallel and Distributed Systems.

These data centers consume a significant amount of power (Megawatts) which has become a key factor in data center planning and management [3] [4] [5]. Therefore there is a pressing need to deliver a technique that can provide high performance while balancing power usage.

Traditional search engines use common information retrieval techniques such as TF-IDF [6] to rate documents and objects on the web. These techniques rely on keyword comparisons to create a ranking on the relative importance of the object. Unfortunately, the reliance on keywords means that if the document does not contain the keyword, it would not be ranked at all. This leads to situations where the search for healthy lifestyle would probably not return a single result (object/document) that did not have the words healthy lifestyle as part of its description or in the text. In order to deliver better search results, search engines are increasingly turning to the area of semantics to understand both input queries as well as search results, so that they can match and return relevant results [7].

Semantic search techniques on the other hand, decomposes concepts and ideas into their basic concepts and compares these concepts against the known data store [8] [9]. This allows the locating and identification of related articles that may not have the same keywords in the document. Hence semantic search while performing a similar service does not rely on the same search techniques as existing search engines.

A Semantic Routed Network (SRN) proposed initially in [10] provides a superior infrastructure enabling semantic information retrival. A SRN allows search engines to operate with smaller number of servers by enabling automatic reorganization of their search indices based on content. This content reorganization and subsequent query routing requires the use of semantic routers [11]. The critical component of the SRN which determines its performance is a semantic router.

Semantic routers perform semantic comparison using a cosine similarity (dot product) computation scheme that can be elegantly parallelized [12]. By creating a power efficient hardware co-processor that performs dot product we can enable

realization of a semantic router. Cosine similarity is also the key-computation in traditional search paradigms such as TF-IDF, hence creating a power efficient hardware co-processor can help in both areas. In this dissertation we will use the terms cosine similarity and dot product interchangeably.

Performing operations in parallel is a key optimization step for better performance on general purpose CPUs. Current techniques for parallelization include architectures that are multi-core [13] and have multiple thread handling capabilities [14] [15]. These coarse grained approaches have considerable resource management overhead and provide only sub-linear speedup. In addition, these approached require new programming models with parallel compilers & libraries as supporting infrastructure. For implementing the dot product required for semantic comparison, a fine-grained approach to parallelization is more suitable. This involves a hardware/software codesign strategy involving hardware centric algorithms and mapping of the algorithm to architecture.

In this dissertation we propose techniques towards a highly parallel, power efficient architecture that performs semantic comparisons as its core activity. Hardware-centric parallel algorithms have been developed to populate the required data structures followed by computation of semantic similarity. The performance of the proposed design is further enhanced using a pipelined architecture. The proposed algorithms were also implemented on two contemporary platforms - the Nvidia CUDA [16] and an FPGA [17] for performance comparison. In order to validate the designs, a semantic benchmark was also been created. It has been shown that a dedicated semantic comparator delivers significantly better performance compared to other platforms.

Results show that the proposed low power architecture presented consumes 82% less power and demonstrates a speed-up in the order of  $10^5$  compared to a contemporary hardware design, and in the order of  $10^3$  compared to software approach for large number of basis vectors. Future research directions including better power optimiza-

tion, architecting the complete semantic router and using the semantic benchmark for SRN research are also discussed.

The key contributions of this dissertation can be summarized as follows:

- 1. Design of algorithms and data structures that are suitable for semantic comparison in a semantic router.

- 2. Design of power efficient parallel hardware architecture to perform semantic comparison.

- 3. Design of pipelined architecture for the enhancement of throughput.

- 4. Implementation on reference platforms such as the Nvidia CUDA and an FPGA for performance comparison.

- 5. Development of a semantic benchmark to create semantic traffic for validation.

The rest of this dissertation is laid out as follows. In Section- 2 we present background material and related work. We begin with a discussion on what is semantic routing and how it works. This is followed by a description of Semantic Routed Networks and the application of Semantic Routed Networks to Search. Once we have established how an SRN works and how it can be applied to Search, we discuss the methods of Vector based semantic comparison and the challenges involved. One of the key computation steps in semantic comparison is the computation of cosine similarity. This contains a challenge because of the size of the data-structure used. We present the challenge and our approach to solving this. We then proceed to explanation of a space-efficient data structure known as a Bloom Filter which we use extensively in the architecture and close out this section with an overview of the Fowler / Noll / Vo (FNV) hash algorithm which is also used.

Section 3 introduces our architecture at a high level. We present details on what semantic comparison involves, the descriptors that are used as semantic metadata and an architectural overview of the computation and the requirements and stages of computation. This section also talks about the basic steps involved in the processing and our fine-grained parallelization scheme. The semantic comparison process consists of two major steps and several sub-steps. The next two sections presents each of the major steps in detail.

Section 4 presents the first part of the computation - the architecture required to create and populate the data structures that we use in our later computational stage. We present an analysis of our approach and provide timing and power figures for the design. We explore design alternatives in creating a set of hash-values in a power and time efficient manner.

Section 5 presents the second part of the computation. In this chapter, we present the details of the architecture and highlight key optimizations and design decisions that allows us impressive speedup while remaining power efficient. We also present overall results comparing, our design and that of doing the same computation on a traditional server class processor, timing analysis and overall power figures.

In Section 6 we present performance improvements and alternative implementations. Pipelining the architecture gives us noticeable speedup without excessive power overheads. Hence we present the design of the pipelined version of the architecture and power and timing figures. We then present two alternative implementations of our basic architecture - first on an Nvidia CUDA platform and then on an FPGA. We provide performance comparisons between these platforms and the base ASIC design proposed in the earlier sections.

It is not possible to evaluate our design without a benchmark. Since, to the best of our knowledge, we are the first to explore semantic comparison, there does not exist any datasets that we can use to create the appropriate kinds of traffic. In Section 7 we present the details of a Semantic Benchmark that we created. The details of its composition and features is discussed.

Conclusions and a discussion on potential directions of future research are provided in Section 8. A overview of the various areas that were discussed in the dissertation are provided.

#### 2. BACKGROUND AND RELATED WORK

### 2.1 Semantic Routing

Semantic routing, the routing of information based on the semantics, is done by humans everyday. It is just not called Semantic Routing in daily usage. The concept of semantic routing can be illustrated using the following scenario: Alice, a first year graduate student of Microbiology wants certain details about the latest Influenza outbreak. She asks her friend Bob who is a post-doctoral researcher if he has specific information. Bob feels that his supervisor Mark is more knowledgeable on the topic, so Bob forwards Alice's request to Mark. Mark responds to Alice's questions and offers to help her. In this scenario, each person is a "semantic router", who determines the next hop based on whom they know to be the best (knowledgeable) person to handle this query. The query here is the 'request for information on the Influenza outbreak' and the best identified resource was Mark who responds to Alice with the offer to help.

#### 2.2 Semantic Routed Networks

A Semantic Routed Network (SRN) routes information on the network using the concept of semantic routing. In this section we provide a brief overview of the working and organization of the SRN, the methods used in the organization of the SRN and Search as an application.

#### 2.2.1 Overview

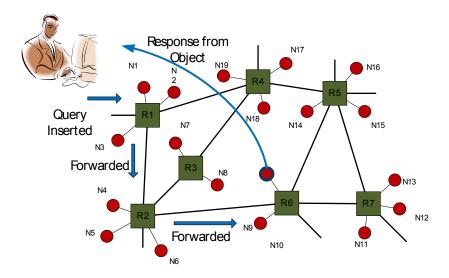

The abstract model of the SRN consists of two types of nodes: router nodes and resource object nodes as shown in Fig. 2.1. Resource nodes are the objects or resources of a network, whereas the router nodes are semantic routers [11]. Semantic

routers attach themselves (with an entry in their routing tables) to both other semantic routers as well as resources. Each router maintains a listing (routing table) of all the resources and other routers attached to itself.

When a query (request for a resource) is injected into the network, the semantic routers compare semantically the query to the entries in their routing table and route the message to the appropriate (or best match) location. The final destination (most likely the resource) would then respond to the originator of the query with the required data. An SRN would be implemented as an overlay network built on top of existing IP networks or a web-service infrastructure. Therefore the response to a query is likely to be a URI containing information about access mechanisms of the resource or relevant web-service response, depending on the type of semantic object/resource. If SOAP [18] messaging is used then semantic routers may implement a SOAP processor as well.

Fig. 2.1. Abstract Model of a Semantic Routed Network

The semantic objects may be data or services having various granularities, formats, structures, service access/delivery mechanisms. These semantic objects are annotated using *metadata* that describes the resource. This metadata can be based

on generic or upper ontologies, like Wordnet [19], Gene Ontology [20] or more specialized ontologies / standards like the Unified Medical Language System (ULMS) [21]. By "description" we mean a flat unstructured set of topics which describes a resource. The elementary metadata items that from the description are referred to as a Tags. Compound topics may be formed by collecting multiple Tags. These Tags can be harvested from the structured metadata that describes the resource. Further details of the semantic objects and the comparison scheme are given in Section . 3.1

#### 2.2.2 Methods and Techniques Involved in SRN

The SRN is implemented as a Small World Network. The Small World Network topology offers better congestion behavior and requires less number of routers to interconnect a given number of resources compared to over hierarchical topology [11]. A small world network topology is characterized by two factors: (a) Small expected path length (hop distances) and (b) Large clustering coefficient. A clustering coefficient is the probability that two nodes are connected if they have a common peer [22].

The SRN has several built-in mechanisms to ensure that the network topology is maintained as well as the routing tables of the routers contain the most updated information. Keeping the routing table updates is modeled on current networking technology i.e. BGP (Border Gateway Protocol) [23] where routers periodically exchange messages with each other giving information about resources and other routers connected to them. Once these messages are received, routing table optimization algorithms are run to update the routing table. Fig. 2.2 shows a sample of the semantic routing table layout. Each *Key* corresponds to a semantic interest of the router, and each *Destination* (per key) shows the nodes that the router knows is semantically similar to that key.

Mapping this back to our example in Section 2.1, the keys correspond to the various interests of a person, and the destinations the people/resources connected

| Keys | Destinations |     |     |     |     |

|------|--------------|-----|-----|-----|-----|

| K1   | D1           | D2  | D3  | D4  | D5  |

| K2   | D6           | D2  | D7  | D8  |     |

| K3   | D10          | D12 | D13 | D14 |     |

| K4   |              |     | D16 |     |     |

| K5   | D20          | D21 | D23 | D24 | D25 |

Fig. 2.2. Semantic Routing Table

with that interest. Bob's interests include Influenza (key) and one of the resources he knew with experience in this area was Mark (destination).

We will now briefly describe the major algorithms that help maintain the semantic routing table.

## Node Clustering Algorithm

In order to locate nodes that contain descriptions that are semantically similar to the entries in the routing tables, a semantic router, periodically sends out messages (queries) with a similarity threshold value into the network. Nodes (both resource nodes and other semantic routers) whose descriptions are semantically similar to the query (with a similarity metric greater than the threshold value) respond back to the originating router, which keeps a log of the responses. In order to keep its routing table populated, a router may periodically send out queries with lower threshold values in order to expand the range of resources that is it aware of. Resource nodes that join a network, send out similar messages advertising themselves for routers to become aware of them.

## Routing Table Optimization

There are three primary methods involved in maintaining the semantic routing table of a router. Fig. 2.3 shows the three methods.

- 1. ROUTING TABLE ENTRY EVICTION: Since the routing tables are of limited size, the routers strive to keep the quality of the entries high by evicting entries that are less similar and replacing them with entries that are semantically closer to the appropriate interest group. Fig. 2.3(a) shows D16 being considered for eviction.

- 2. Reallocation of destinations: A single key of a routing table can contain more than one destination for the key. If an entry is to be evicted (see previous method), an attempt is made to re-allocate it. This involves looking at the other keys in the table to see if it can be used for another key based on the relevance of the entry. In Fig. 2.3(b) the destination D16 is being re-allocated from key K4 to a location that is alongside K2.

- 3. Reallocation of Keys: Occasionally, a router may find that an entire row of the table needs to be re-allocated or changed. This could be due to either an entire set of resources going off-line or identification of a new more appropriate interest. If the change is due to the destinations going offline, the entries are dropped and the table is purged of that Key. In Fig. 2.3 the key K4 is now dropped since there are no new destinations and the table is compacted. If the change is due to a new key, re-allocation of the destination entries is attempted using the previous step before dropping the entry.

## 2.2.3 Application of SRN to Search Engines

Semantic Routed Networks (SRN) can be used to enable the automatic reorganization of the search-index of a distributed search engine [10]. This would allow for

| Keys | Destinations |     |     |     |     |

|------|--------------|-----|-----|-----|-----|

| K1   | D1           | D2  | D3  | D4  | D5  |

| K2   | D6           | D2  | D7  | D8  |     |

| K3   | D10          | D12 | D13 | D14 |     |

| K4   |              |     | D16 |     |     |

| K5   | D20          | D21 | D23 | D24 | D25 |

| (a)  |              |     |     |     |     |

| Keys |                     | Destinations |     |     |              |  |  |

|------|---------------------|--------------|-----|-----|--------------|--|--|

| K1   | D1                  | D2           | D3  | D4  | D5           |  |  |

| K2   | D6                  | D2           | D7  | D8( | D16          |  |  |

| K3   | D10                 | D12          | D13 | D14 | $\mathbf{F}$ |  |  |

| K4   |                     |              | _   |     |              |  |  |

| K5   | D20 D21 D23 D24 D25 |              |     |     |              |  |  |

| (b)  |                     |              |     |     |              |  |  |

| Keys | Destinations |     |     |     |     |

|------|--------------|-----|-----|-----|-----|

| K1   | D1           | D2  | D3  | D4  | D5  |

| K2   | D6           | D2  | D7  | D8  | D16 |

| K3   | D10          | D12 | D13 | D14 |     |

| K5   | D20          | D21 | D23 | D24 | D25 |

|      |              |     |     |     |     |

| (c)  |              |     |     |     |     |

Fig. 2.3. Routing Table Optimization

the reduction in the number of servers deployed by the search engine. Search engines such as Google and Bing are scrambling to provide more meaningful and relevant results without an increase in the response time (real-time search). This leads to an increased computational load per query.

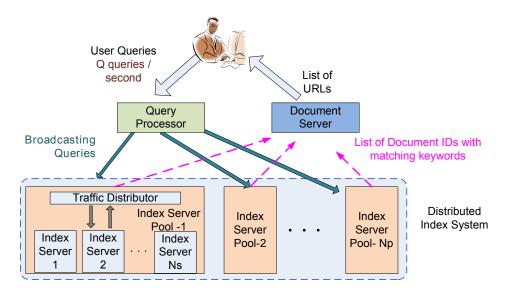

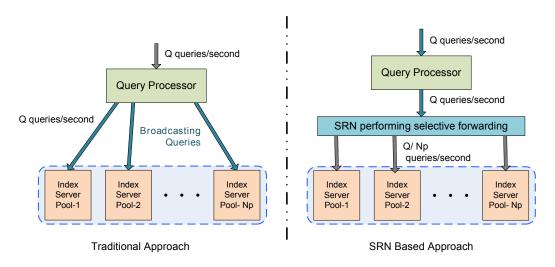

Fig. 2.4 illustrates the architecture of a typical internet search engine core [3]. It is assumed that every document indexed by a search engine is assigned a unique  $Document\ ID$ . A search engine consists of two core components (A) Index Servers and (B) Doc Servers. Users send raw queries q (at rate Q) to the front-end server. A query processor multicasts these queries to  $N_s$  Index shards (rate reduced to  $Q/N_s$ ) which constitute the index server. For a given query q, index shards return a sorted list results to the document server (a list of ID and the corresponding rank). Index shards are replicated for capacity (often across geographical locations for fault-tolerance). For example, multiple instances of the index servers form a pool as shown in Fig. 2.4. Given a set of  $Document\ IDs$  for a given query, a document processor returns the relevant (URL,snippet) which is returned to the user as a result by the front-end service.

The index is typically generated (using statistical measures like TF-IDF [6] or latent semantic dimensions [24]) with rows representing words/dimensions and several columns representing related *Document IDs* and their corresponding weights (Wi,j). The cosine similarity score is computed across the *n*-dimensions of every

index shard. The resulting similarity scores are sorted and further processed by the document servers to return to the user.

Fig. 2.4. Architecture of a Typical Search Engine

An energy efficient alternative to query broadcasting is to systematically distribute objects to the pools/shards based on the meaning of the objects, so that documents having similar content (or belonging to a similar topic) are in the same shard as shown in Fig. 2.5. Such index distribution would need a specialized network to deliver the queries to a specific pool(s)/shard(s). This arrangement will avoid unnecessary query traffic (query rate reduced to Q/Np as in Fig. 2.5) to all pools thereby allowing smaller number of servers ( $n_s \approx Ns/Np = Ns/1000 < Ns$ ) in each pool and lower power consumption. This specialized network can be elegantly implemented using a Semantic Routed Network.

This semantic routed network (SRN) consisting of multiple semantic routers [10] can be used for:

1. To selectively forward/route a (query) message to an index shard based on the meaning of the query; and

2. To automatically re-distribute index entries based on meaning of the documents/objects.

Achieving true semantic search requires a way to "represent meaning in computers" as compared to naive term-by-term comparison [6] which exists today. This question was addressed in [12] and uses Vectors to perform the semantic comparison.

New methods to represent "composite" meaning in computers have been designed and proven to be superior to TF-IDF in [12]. This enables conjunction, disambiguation & representation of "complex concepts" their synonyms and hyponyms using a Tensor-based transformation model [24]. The use of this model enables the creation of a Semantic Routed Network [10] (SRN) in the index shards of a search engine.

Fig. 2.5. Search Engine with SRN Integrated

A SRN has been proven to enable the automatic reorganization of the search-index of a distributed search engine based on the principles of a Small World Network [8]. Using this model, an incoming query q can be injected into the SRN. The SRM network then routes the query until resolved by reaching the appropriate Index Server. This implements selective unicast instead of the inefficient multicast mechanism discussed previously. Fig. 2.5 shows the reorganization of the Index shards using the principles of SRN. Results in [11] [8] show through simulation that con-

vergence to a Small World Network is possible, with bounded overhead. It is proven that query resolution is guaranteed within a maximum of 3 hops from injection on average (for a fully re-organized index).

These techniques address users need for "semantically" meaningful and relevant results without an increase in the response time (real-time search). Although an SRN has been proven to theoretically converge (in simulation), our experiments in the next Section emphasize the need for hardware in the index shards to meet the cost of a significantly larger computational load per query resolution using a Tensor model and SRN-based index server pool.

#### 2.3 Vector Based Semantic Comparison

Contemporary search engines use vector models for automatic text retrieval [6]. Each of the comparisons being performed by the computers in Fig. 2.4 performs this computation. Techniques that we described in [12] extend these vector models for more efficient semantic comparisons using tensors. Algebraically, a tensor is represented as a sum of scalar  $(w_i)$  weighted basis vectors  $(v_i)$  as shown in Fig. 2.6. The figure shows text fragments from two documents and their corresponding tensor representation (Tensors  $D^1$  &  $D^2$ ). Each basis vector denotes elementary meaning which typically is a term or a phrase (character strings) from a controlled vocabulary/dictionary or selectively picked from a text object (e.g. a sentence in Fig. 2.6) and assigned weights (scalar coefficients) depending on the model used [6].

The similarity between the meanings represented by the two vectors is given by their cosine (dot) product. The dot product of two vectors/tensors is given by the sum of products of weights of the basis vectors (having non-zero weights) that are common in both vectors. In a computer, these tensors can be represented by a table of character strings and their corresponding coefficient weights. Computing dot-product of large vectors is challenging. In the next section, we shall explain the challenge.

Text doc  $D^1$ : "The soccer player looked | Text doc  $D^2$ : "The soccer player kicked at the ball. Then he kicked it."

$$TensorD^{1} = \begin{array}{ccc} w_{soccerplayer}^{A} \overrightarrow{v}_{soccerplayer} \\ + w_{ball}^{A} \overrightarrow{v}_{ball} + w_{look}^{A} \overrightarrow{v}_{look} \\ + w_{kick}^{A} \overrightarrow{v}_{kick} \end{array} \qquad TensorD^{2} = \begin{array}{ccc} w_{soccerplayer}^{B} \overrightarrow{v}_{soccerplayer} \\ + w_{kick}^{B} \overrightarrow{v}_{kick} \\ + w_{ball}^{B} \overrightarrow{v}_{ball} \end{array}$$

the ball."

$$TensorD^{2} = w_{soccerplayer}^{B} \overrightarrow{v}_{soccerplayer} + w_{kick}^{B} \overrightarrow{v}_{kick} + w_{ball}^{B} \overrightarrow{v}_{ball}$$

$$Semantic\ Similarity < D^1, D^2 >= D^1 \cdot D^2 = w_{soccerplayer}^A w_{soccerplayer}^B \\ + w_{ball}^A w_{ball}^B + w_{kick}^A w_{kick}^B$$

Fig. 2.6. Tensor Model of Semantic Comparison

## Challenge in Dot Product Computation

Dot product is the sum of product of corresponding non-zero coefficients of two vectors. The key challenge is to pair-up the corresponding vectors to enable the appropriate multiplications. This pairing up requires that each component (basis) vector (from one of the vectors being processed) is checked for a corresponding entry in the other vector. If a corresponding entry is found, then the coefficients of the two are multiplied. If a corresponding entry is not found, this is the same as multiplying that particular coefficient by zero - a superfluous operation. This is a relatively simple task when dealing with small finite vector models (such as in Latent Semantic Indexing [24] ) since few superfluous multiplication operations does not increase the computational cost extensively. However, for vector models that deal with infinite dimensional vector space - the superfluous multiplications quickly become computationally expensive and hence need to be eliminated.

If the number of basis vectors in each vector being compared are denoted as  $n_1$ and  $n_2$ , then using the traditional computing approach, the search operation involved in dot-product takes  $n_1 \cdot log(n_2)$  or  $n_1 \cdot n_2$  computations depending on whether or not a binary search tree is created. Note that creating a binary search tree also involves sort operation on one of the vectors - which is also of the order of  $n \cdot log(n)$  where n is the size of the vector being sorted. Hence in the case of a binary search tree based approach, the order of complexity of the total computation is  $n_1 \cdot log(n_2) + n_1 \cdot log(n_1)$  (assuming that  $n_1$  is the number of rows in the table getting sorted)

In order to perform this search elegantly (with less complexity) Bloom Filters are used. Bloom filters allow one to perform this search (with a small possibility of false positives) with much less computational complexity O(1). An effective representation of composite meanings is necessary to ensure "meaningful" semantic comparison. To enable this, semantic comparison operates on an infinite dimensional vector space leading to large tensor sizes ( $\approx 10^3$ ).

We briefly describe the basic properties of the Bloom Filter that we used in the next section.

#### 2.5 Bloom Filter Basics

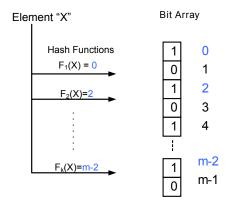

A Bloom filter (BF) is a compact representation of a set [25]. The BF consists of a large single dimensional array of m bits and a set of k hash functions and is a good candidate for performing membership tests on a set. A Bloom filter has the property that while it may present a false positive (indicate that the element is present, while it is actually not present), the BF will never have a false negative (i.e. indicate that the element is not present, when it is actually present). There are two operations that can be performed on a BF - Insertion and Membership testing. We will now briefly describe each of these operations.

#### 2.5.1 Element Insertion

To insert an element (such as a number or a text string) in this set, we hash this element to generate k different values using the k different hash functions. We use these values as bit-indices to decide which bits in the array should be set to 1 as shown in Fig. 2.7.

Fig. 2.7. Bloom Filter: Insertion

## 2.5.2 Membership Testing

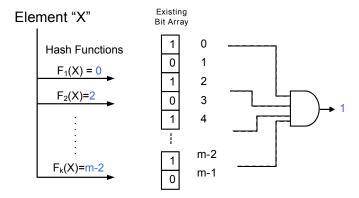

To test whether an arbitrary element is in the BF, we similarly generate k bit indices and check whether all of those bits are 1 or not. All bits being 1 indicates that the element is in the set (Fig. 2.8).

Fig. 2.8. Bloom Filter: Membership Testing

Because testing for presence is performed by looking at the bit-position values, it is possible that a bit that was set due to the insertion of one element, may be used in the testing process for testing for the presence of another element. This gives rise to the false positive rate of the Bloom Filter. However, since there is no possibility

that an element that was inserted would not have set the appropriate bit-positions, Bloom Filters will not present a false negative.

The probability of a false positive  $P_{false+ve}$  is given by:

$$P_{false+ve} = \left(1 - \left[1 - \frac{1}{n}\right]^{km}\right)^k \tag{2.1}$$

which can be simplified as

$$P_{false+ve} = \left(1 - e^{-\frac{kn}{m}}\right) \tag{2.2}$$

The probability of false positives, can be minimized by choosing large m, and optimum  $k(\approx 0.7*m/n)$ , where m is the number of bits in the BF, k is the number of independent hash functions and n is number of elements in the BF (Fig. 2.8). For example, a basic BF with m = 10240 bits, k = 7 can keep  $10^3$  elements with a small  $P_{false+ve} \approx 8 \times 10^{-3}$ , which will have a negligible effect on similarity comparison.

The basic bloom filter does not provide for deletion of an element or for the insertion of duplicate elements. However, there exists, other variations of bloom filters such as Counting Bloom Filters [26] proposed by Li et al. In [27], Bonomi et al. proposed a *d-left hash* based design that allows for a more compact (space efficient) design of counting filters.

In [28] the Chazelle et al. implemented *Bloomier Filters*, an extension to Bloom filters that allows the implementation of an associative array. The basic bloom filter approach cannot adapt to varying number of elements stored without re-creating the entire filter. This problem was addressed by [29] who proposed Scalable Bloom filters. Scalable Bloom filters are an adaptation of the classic bloom filter design, but in this case can dynamically adapt to the number of elements being stored without affecting the false positive probability.

## 2.6 FNV Algorithm

#### 2.6.1 Overview

The Fowler / Noll / Vo (FNV) hash algorithm [30] is used as the basic Hash Function in our architecture. It was chosen because of its ease of parallelization compared to more popular algorithms such as MD5 [31] or SHA2 [32]. The algorithm for the computation of the FNV hash is presented in Algorithm 1. The implementation details of this algorithm will be presented in the next chapter.

## 2.6.2 Algorithm & Relevant Parameters

## Algorithm 1 FNV Hash Algorithm (Type 1a)

```

procedure FNV-1A(data)

hash \leftarrow offset\_basis

for all octets\_of\_data do

hash \leftarrow hash \otimes octet\_of\_data

hash \leftarrow hash \times FNV_{prime}

end for

end procedure

```

The parameters of the FNV Hash of size n are:

- *hash* is an *n*-bit unsigned integer.

- The multiplication operation (denoted by  $\times$ ) is performed modulo  $2^n$ .

- The XOR operation (denoted by  $\otimes$ ) is performed on the lower octet (8 bits) of hash.

- $FNV_{prime}$  is dependent on n.

- offset\_basis is dependent on n.

## 2.6.3 Standard Values of Key Parameters

Values for  $FNV_{prime}$  and offset\_basis for different sizes of n are available at [30]. In this dissertation, the value of  $FNV_{prime}$  and offset\_basis for a size of n=64 bits is taken. Some representative values for  $FNV_{prime}$  are shown in Table- 2.1 and representative values for offset\_basis are shown in Table- 2.2

| Size of $n$ (bits) | Value of $FNV_{prime}$ |

|--------------------|------------------------|

| 32                 | $2^{24} + 2^8 + 0x93$  |

| 64                 | $2^{40} + 2^8 + 0$ xb3 |

| 128                | $2^{88} + 2^8 + 0x3b$  |

| 256                | $2^{168} + 2^8 + 0x63$ |

| Size of $n$ (bits) | Value of offset_basis                   |

|--------------------|-----------------------------------------|

| 32                 | 2166136261                              |

| 64                 | 14695981039346656037                    |

| 128                | 144066263297769815596495629667062367629 |

The value of offset\_basis is the FNV-0 hash of the following string (shown in C style notation).

''chongo <Landon Curt Noll> /\\../\\'

This text segment is the original email signature line of one of the creators of the FNV algorithm [30]

#### 3. OVERVIEW OF SEMANTIC COMPARISON

Semantic comparison as performed by a semantic router compares two objects. As explained previously in Section 2.2.1, These objects may be data or services having various granularities, formats, structures, service access/delivery mechanisms. These semantic objects are annotated using *metadata* that describes the resource. This metadata can be based on generic or upper ontologies, like Wordnet, Gene Ontology or more specialized ontologies / standards like the Unified Medical Language System (ULMS).

The metadata describing these objects, is used to create a semantic descriptor - a data structure that contains the semantic description of the object, by applying techniques such as TF-IDF onto the metadata. By comparing the semantic descriptors of two objects, we can compute the semantic similarity between the two.

# 3.1 Semantic Descriptor

A semantic descriptor can be generated in several ways. The most commonly used technique TF-IDF [6] stores a statistical product term (frequency  $\times$  inverse document frequency) for all terms in a document. In contrast [33] proposes and evaluates a weighted Concept (ontology) Tree based descriptor taking compositions into account. A concept tree is a hierarchical acyclic directed n-ary tree where the leaf nodes represent terms whereas the tree itself describes their inter-relationships within a document [34] [35]. Each term is assigned a weight which describes its relative importance. Fig. 3.1 shows two sample trees which represent two distinct "concepts" but use the same keywords (shown as leaf nodes). The intermediate notations (ex. American, man) are notional and are shown for convenience.

Associated weights for each term (coefficient values describe their relative importance) are not shown for simplicity. Concept tree building has been discussed in detail in [8] [12] and applied to test cases in [36]. It is important to note that

# The american man ate indian food {{american, man} {ate} {indian, food}} {{american, man} ate {indian, food}} {{american, man} ate {indian, food}} {{indian, man} ate {american, food}} man american food american

Fig. 3.1. Concept Trees of Two Sentences

conventional term based weighting cannot differentiate between the two statements (or their trees). A Tensor model, on the other hand, is used to decompose such concept trees into a flat data structure consisting of polyadic concept terms and their normalized coefficients without loss of the semantics contained in the original tree structure.

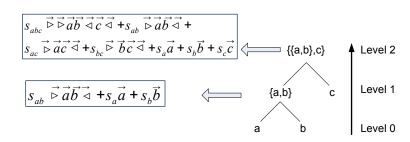

Fig. 3.2. Conversion of Concept Tree into Tensor Representation

Fig. 3.2 shows the bottom up expansion of a 3-level, 2 child concept tree. Level 0 shows leaf nodes "a" and "b". Their composition at Level 1a,b is defined by  $\triangleright ab \triangleleft$ , a and b ( $\triangleright \& \triangleleft$  are delimiters;  $s_{ab}, s_a, s_b$  are normalized weights). The final tensor representation of this concept tree is obtained at Level 2 consisting of weighted polyadic combinations of terms  $\triangleright ab \triangleleft c, \triangleright ab \triangleleft, \triangleright ac \triangleleft, \triangleright bc \triangleleft, a, b, c$  (called basis vectors) and their normalized weights. The nuances of this conversion including the process of determination of weights is detailed in [37].

The semantic descriptor created by the tensor conversion process comprises of the tensor representation as well as the associated scalar coefficient value as shown in Fig. 3.3.

| Vector ID              | Scalar Coefficient |

|------------------------|--------------------|

| Vector ID₁             | Coeff₁             |

| Vector ID <sub>2</sub> | Coeff <sub>2</sub> |

| Vector ID <sub>3</sub> | Coeff <sub>3</sub> |

| • • •                  |                    |

| Vector ID <sub>n</sub> | Coeff <sub>n</sub> |

Fig. 3.3. Tabular Form of Semantic Descriptor

## 3.2 Semantic Comparison

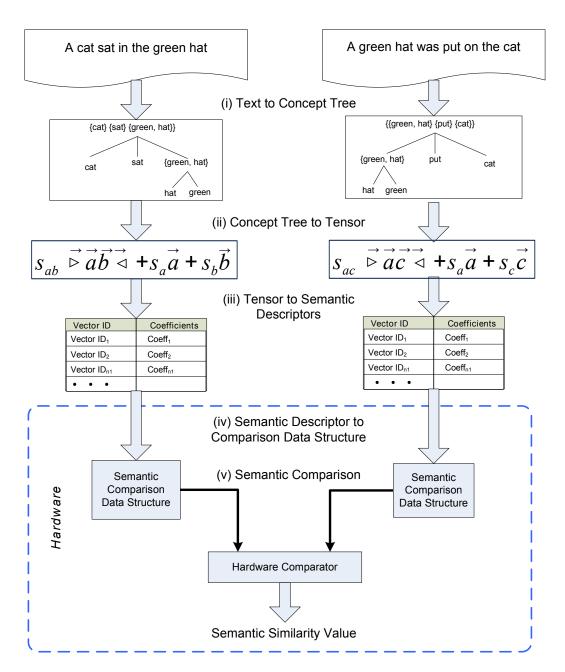

The basic comparison occurs between two descriptors D1 and D2 as follows. The task is to compute the dot-product between these two descriptors to get a numerical value for the semantic similarity. Fig. 3.4 shows the sequence of steps performed to obtain the similarity value.

The semantic comparison process begins by converting the semantic descriptors discussed above into appropriate data-structures that can be used in the computation stage. Once the conversion is complete, the computation of semantic similarity is performed using the method of cosine similarity (dot-product). For the rest of the dissertation, we will use the terms tensors and vectors interchangeably.

The major steps of computing semantic similarity are as follows

- 1. Population of Data Structure.

- (a) Computation of FNV Hash.

- (b) Population of Bloom filters.

- 2. Computation of Cosine Similarity.

Fig. 3.4. Sequence of Steps for Semantic Comparison

- (a) Identification of Common basis vectors.

- (b) Extraction of Coefficients.

- (c) Multiplication and Summation of Coefficients.

In the following sections we will discuss each of these steps in detail.

In this dissertation, we focus on Steps (iv) & Step (v) from Fig. 3.4. We presume that Step (i) (conversion of query/object to a concept tree) through Step (iii) (conversion from concept tree to descriptor) has been completed. The SRN will routes packets of data, each packet containing a semantic descriptor.

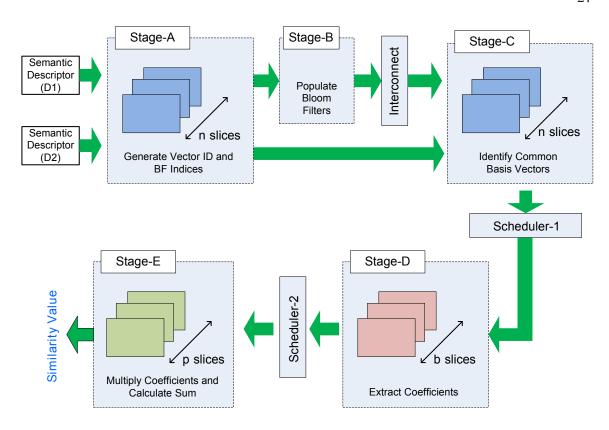

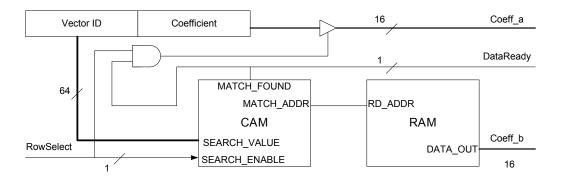

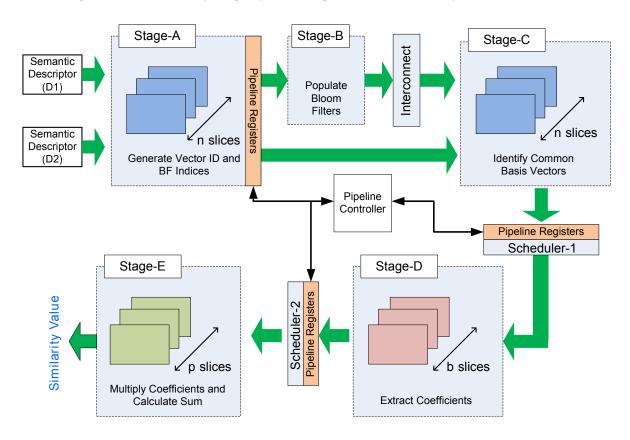

# 3.3 Architectural Overview of Semantic Comparator

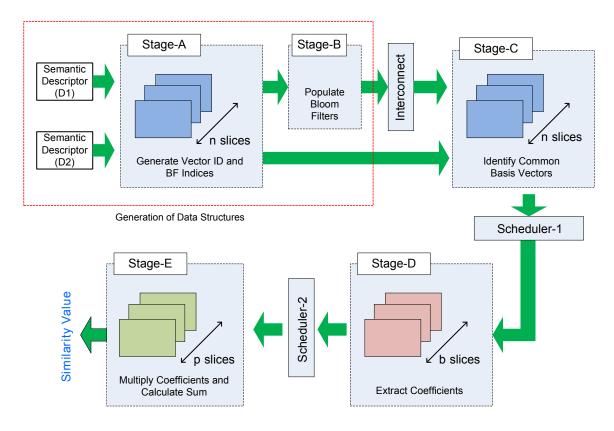

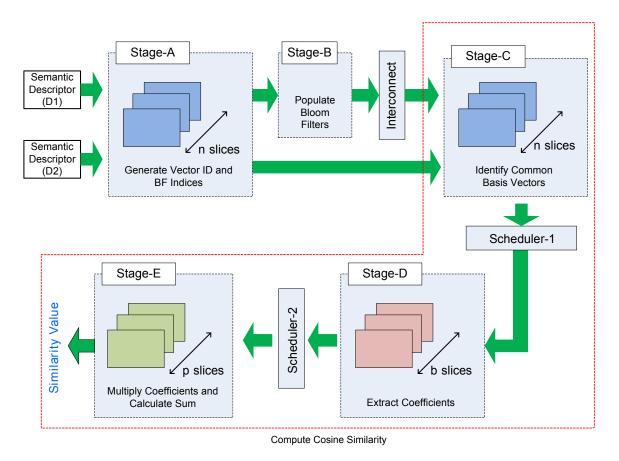

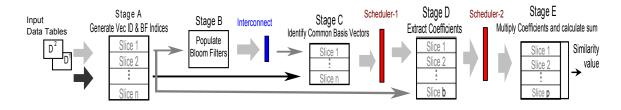

The proposed semantic processor core, has five basic stages as shown in Fig. 3.5. Stage (A) generates vector IDs and k hash values for each basis vector; Stage (B) populates the Bloom filter of descriptor D2 using the k hash values; Stage (C) identifies the common basis vectors using BF membership testing; Stage (D) extracts the matching pairs of scalar coefficients using Content Addressable Memory (CAM) modules; and Stage (E) multiplies the corresponding pairs of scalar coefficients and calculates the sum to obtain the dot product.

Each of these parallel processing instances, which can be considered as a hardware thread, is executed by each horizontal slice of each circuit stage (A to E), as shown in Fig. 3.5. There are n slices in stage A to C, and b slices in stage-D and p slices in stage-E. Stage-E also consolidates all the processing.

### 3.3.1 Working

The five stages of the semantic comparator execute the steps listed in Section 3.2. The input descriptors to be compared (D1,D2) are first converted into the respective semantic comparison data structures. This is done by hashing the input

Fig. 3.5. Overall Stages of Processing

vector IDs through a common hash function (FNV hash), and then obtaining the Bloom Filter Indices and storing them. Once both of the descriptors have been converted into the semantic comparison data structure, the actual processing of the semantic comparison begins. To begin this step, the bloom filters are consolidated into a single bloom filter and distributed to the n slices of Stage-A. Each slice of Stage-A gets one of the appropriate rows from the second data-structure. Once the Bloom filter has been consolidated, Stage-C locates the common basis vectors. This identifies which of the basis vectors in the two descriptors being compared are the same. The order of computation for Stage-C because we use n parallel stages and k indices for the bloom filter is O(k). Once the common vectors have been identified, these vectors are passed to Stage-D where the CAM blocks retrieve the

corresponding scalar coefficient values. The pairs of scalar coefficient values that need to be multiplied are then sent to Stage-E where a bank of multipliers multiply the values and feed it to an accumulator. This stage (Stage-E) is where the actual computation of dot-product (Cosine similarity) occurs. The output of Stage-E is the similarity value between the two stages. The working of each of the stages A-E is discussed in detail in the next two sections.

# 4. CREATION OF REQUIRED DATA STRUCTURES

In this section, we present the first of the two major steps (Generation of Data structures, Stages A,B in Fig. 4.1). In the next section (Section. 5) we will describe the architectural details of steps C-E.

Fig. 4.1. Stages Involved in Generating Data Structures

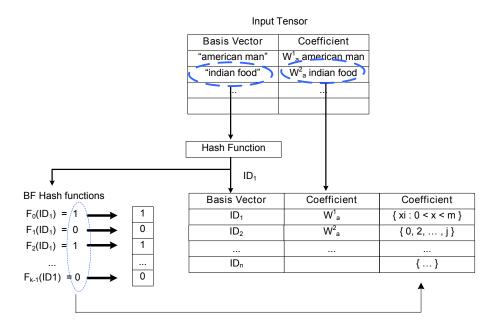

#### 4.1 Description of the Data Structures

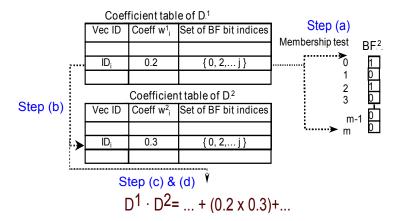

The abstract data structure required for semantic comparison has two components: (1) a Co-efficient table and (2) a large  $m \ (\approx 128K)$  bit long Bloom Filter (BF) using k(=7) hash functions [25]. The layout of the data structure is shown in Fig. 4.2 Each row of the coefficient table consists of three columns: (1) Vector ID

(e.g. "ID1" in Fig. 4.2); (2) 16 bit fixed point scalar coefficient of the corresponding basis vector (e.g.  $w_i$ ); and (3) Set of BF indices ( $x_1 : 0 \le x_i \le m$ ). The combination of the coefficient table and the bloom filter represents the vector/tensor representing the meaning of an object (text/non text document).

| Coefficient Table |                        |                       | Bloom Filter |

|-------------------|------------------------|-----------------------|--------------|

| Vec ID            | Coeff w <sup>1</sup> i | Set of BF bit indices |              |

| ID                | 0.2                    | { 0, 2, j }           | 1            |

| ID <sub>i</sub>   | 0,2                    | { 0, 2, } }           |              |

|                   |                        | •                     | Ö            |

Fig. 4.2. Components of Data Structure

A 64 or 128 bit hash of a basis vector term is generated and inserted as the Vector ID in the coefficient table as shown in Fig. 4.3. To generate a set of k BF indices, each Vector ID (or the basis vector character string) is further hashed by k hash functions and the resultant indices are stored in the third column while the corresponding bit locations are set in the BF.

Fig. 4.3. Populating the Data Structure

# 4.2 Algorithm to Populate the Data Structures

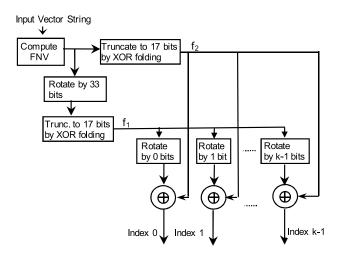

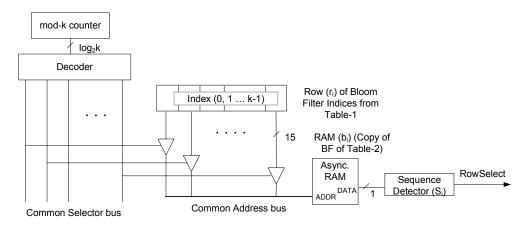

In Fig. 4.4, we present the block schematic of the architecture where the BF indices are generated. We use the FNV hash algorithm as the primary hash for the BF index generation operation. The 64 bit output of the FNV hash module is duplicated. The first copy  $(f_1)$  is directly truncated to 17 bits using XOR folding [30]. The second copy  $(f_2)$  is rotated by 33 bits and then truncated to 17 bits using XOR folding. For each BF index  $BF_i$  (where  $0 \le i \le k$ ); a copy of  $f_1$  is rotated by i bits and then XOR'd with  $f_2$ . (For example, the second BF index (index-1 in Fig. 4.4) is obtained by first rotating  $f_1$  by one-bit position and then XOR-ing this with  $f_2$ .) This enables the creation of k different index values in parallel.

Fig. 4.4. Bloom Filter Index Generation

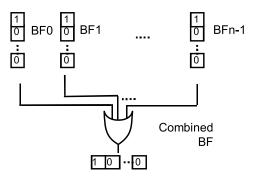

These bloom indices allow parallel setting of the corresponding bit position in a memory element, hence creating a Bloom Filter for each row. The *n* individual BFs (one per row) are then consolidated into a single BF using cascaded OR-Gates and distributed to multiple rows.

# 4.2.1 Consolidation of Bloom Filters

Since we are going to be using n copies of the circuit for Stage-C, we need to consolidate the bloom filters created in Stage-B and then distribute them to the n copies of Stage-C. The distribution is done using the Interconnect shown in Fig. 4.1. The interconnect is a simple tree network similar to the commonly accepted clock-tree implementations.

The n individual BFs (one per row) are consolidated into a single BF using cascaded OR-Gates. Fig. 4.5 shows the completely parallel architecture of doing this. It is also possible to do this in multiple-cycles by using flip-flops at intermediate stages. The use of multi-cycle allows for decreased chances of hold/setup time violations due to the longest path length.

Fig. 4.5. Bloom Filter Consolidation

# 4.3 Results

#### 4.3.1 Analysis of Hash functions Used for BF Index Generation

A Bloom Filter requires the use of k hash functions to generate k index values. The standard method of doing this is to deploy k separate hash functions for the purpose. However, deploying k hash functions in hardware is not efficient. A more efficient manner to obtain a number of hash values is to combine two hash functions

h1(x) and h2(x) in the form  $g_i(x) = h_1(x) + ih_2(x)$ . In [38], the authors show that applying this technique to Bloom Filters allows you to efficiently implement a BF without any loss in the false positive probability. In order to locate the most power efficient manner generating hash functions, we looked at several different ways of combining h1(x) and h2(x) In Table 4.1 we present some of the different ways we could combine the hash functions to get the values. In the table,  $\otimes$  represents bitwise XOR operation, \* represents a multiplication operation and + represents addition.

Table 4.1

Some Possible Variations of Hash Functions

| Method | Combination                                               | Power                 |

|--------|-----------------------------------------------------------|-----------------------|

| 1      | A + rot(B, i)                                             | $557.103~\mu { m W}$  |

| 2      | A + i * B                                                 | $88.136~\mu~{ m W}$   |

| 3      | $A + 2^i * B$                                             | $637.910 \ \mu \ W$   |

| 4      | $A \otimes i * B$                                         | $58.269 \; \mu \; W$  |

| 5      | $\mathbf{A} \otimes \mathbf{rot}(\mathbf{B}, \mathbf{i})$ | <b>61.258</b> $\mu$ W |

| 6      | $A \otimes 2^i * B$                                       | 92. 796 $\mu$ W       |

The multiplication operation (denoted by \*) can be implemented using a *shift* operation in Verilog. However, *shifting* bits, introduces Zeros into the bit positions vacated during the shift operation. Since performing an XOR operation with 0 retains its value  $(1 \otimes 0 = 1 \text{ and } 0 \otimes 0 = 0)$ , this would lead to those bit positions being deterministic (The location of the zeros are known). This leads to a sub-optimal value for the Hash function. Hence we did not choose any of the multiplication options. Thus, the most optimal choice of the options was Method-5 from the table above i.e.  $A \otimes rot(B, i)$ . This gave us the lowest power draw while retaining the randomness due to the rotation.

During the population of the data structure, the computation of the FNV hash can be done either completely in parallel or in multiple cycles. In table 4.2 we present the power and timing differences between completely parallel computation

and sequential computation. The module that generates the k hash indices is made of purely combinational logic - hence it is always a single cycle module.

# 4.3.2 Power Draw by Stages-A & B

The proposed design implemented in Verilog and simulated using ModelSim from Mentor Graphics. To obtain power results, synthesis was performed on the verified design using Design Compiler from Synopsys using components from the Design-Ware IP Library and the TSMC 90nm technology library. The memory power data was obtained using the CACTI power model [39]. The feasibility of the design is established by the synthesized power estimate, i.e. if power is within physical limits and the circuit is synthesizable, then it is feasible.

Table 4.2

Power Draw by One Instance of the FNV module

| Module                          | Power   | Num Clock Cycles |

|---------------------------------|---------|------------------|

| FNV - Parallel Implementation   | 25.3 mW | 1                |

| FNV - Sequential Implementation | 5.97 mW | 6                |

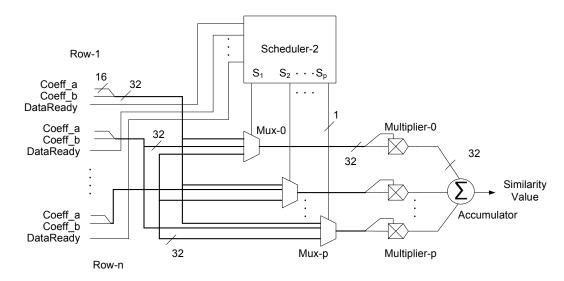

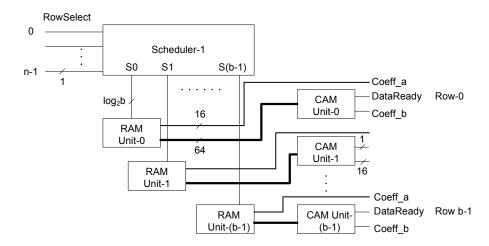

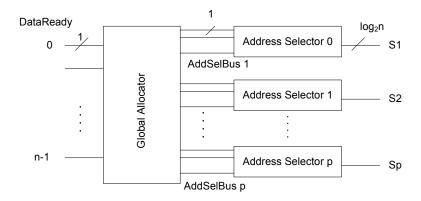

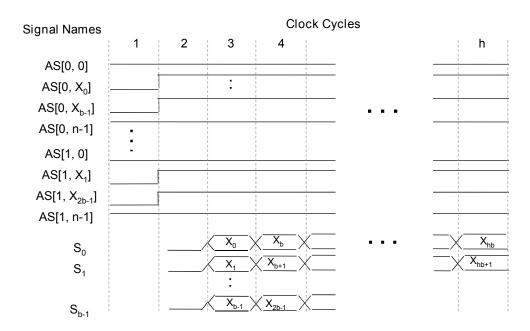

As can be seen from the data. A trade-off must be made between power and timing, depending on the performance goals. We took the sequential approach in order to keep the power draw low. However, if the power budget allows, the single-cycle approach can give a performance improvement.