# PERFORMANCE PROJECTIONS OF HPC APPLICATIONS ON CHIP MULTIPROCESSOR (CMP) BASED SYSTEMS

A Dissertation

by

SAMEH SH SHAWKY SHARKAWI

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

May 2011

Major Subject: Computer Science

# PERFORMANCE PROJECTIONS OF HPC APPLICATIONS ON CHIP MULTIPROCESSOR (CMP) BASED SYSTEMS

#### A Dissertation

by

## SAMEH SH SHAWKY SHARKAWI

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

Approved by:

Chair of Committee, Valerie Elaine Taylor

Committee Members, Nancy Amato

Vivek Sarin

R. Lee Panetta

Head of Department, Valerie Elaine Taylor

May 2011

Major Subject: Computer Science

#### **ABSTRACT**

Performance Projections of HPC Applications on

Chip Multiprocessor (CMP) Based Systems. (May 2011)

Sameh Sh Shawky Sharkawi, B.S., The American University in Cairo;

M.S., Texas A&M University

Chair of Advisory Committee: Dr. Valerie Elaine Taylor

Performance projections of High Performance Computing (HPC) applications onto various hardware platforms are important for hardware vendors and HPC users. The projections aid hardware vendors in the design of future systems and help HPC users with system procurement and application refinements. In this dissertation, we present an efficient method to project the performance of HPC applications onto Chip Multiprocessor (CMP) based systems using widely available standard benchmark data. The main advantage of this method is the use of published data about the target machine; the target machine need not be available.

With the current trend in HPC platforms shifting towards cluster systems with chip multiprocessors (CMPs), efficient and accurate performance projection becomes a challenging task. Typically, CMP-based systems are configured hierarchically, which significantly impacts the performance of HPC applications. The goal of this research is to develop an efficient method to project the performance of HPC applications onto systems that utilize CMPs. To provide for efficiency, our projection methodology is automated (projections are done using a tool) and fast (with small overhead).

Our method, called the surrogate-based workload application projection method, utilizes surrogate benchmarks to project an HPC application performance on target systems where computation component of an HPC application is projected separately from the communication component. Our methodology was validated on a variety of systems utilizing different processor and interconnect architectures with high accuracy and efficiency. The average projection error on three target systems was 11.22% with standard deviation of 1.18% for twelve HPC workloads.

# **DEDICATION**

To my mother who gives me all the love, care and support

#### **ACKNOWLEDGEMENTS**

Throughout my graduate school, there have been many people who helped and influenced me that I would like to thank; however, I have to acknowledge first that it is the grace of my Lord and Savior Jesus Christ that gave me the ability to reach where I am now. My mother, Amal, how do I ever do enough to thank you? Maybe this PhD is a start. If there is one person in this world that deserves the ultimate acknowledgement for this work, it is you. You lovingly sacrificed everything for me and never asked for anything in return except my happiness. I would also like to thank the two Monicas in my life, my sister, Monica and my fiancée, Monica; My sister for always believing in me and my judgment and my fiancée for being my motivator.

There are many people to thank in my academic life, first and foremost is my advisor and mentor, Dr. Valerie Taylor, who taught me what research really means. You always pushed me to reach perfection in all aspects of my studies and your critique and guidance will always be my guidelines in my future research. I would also like to thank Dr. Xingfu Wu and Charles Lively in my research group for all the constructive discussions and feedback. Thanks are also in order for my past research group member Dr. Ayodeji Coker.

I would like to also thank numerous people at IBM. Stephen Stevens whom I consider my Godfather at IBM, THANK YOU. You were always looking for ways to facilitate my research work and genuinely wanting to help me progress in my career. I also want to thank Don DeSota and Raj Panda for spending long hours with me to discuss research problems. The insight I gained from you both is invaluable. I also want to thank

Rajeev Indukuru, Lorena Pesantez, Joseph Robichau, Jason Cantin and Bradley Elkin for all their help and patience with my questions.

# **TABLE OF CONTENTS**

| P                                                                                                                                                                                                    | age                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| ABSTRACT                                                                                                                                                                                             | iii                                  |

| DEDICATION                                                                                                                                                                                           | V                                    |

| ACKNOWLEDGEMENTS                                                                                                                                                                                     | vi                                   |

| TABLE OF CONTENTS                                                                                                                                                                                    | viii                                 |

| LIST OF FIGURES                                                                                                                                                                                      | xi                                   |

| LIST OF TABLES                                                                                                                                                                                       | xiv                                  |

| 1. INTRODUCTION                                                                                                                                                                                      | 1                                    |

| 1.1 Performance Projection Requirements                                                                                                                                                              | 3<br>5                               |

| System                                                                                                                                                                                               |                                      |

| 1.3.1 Code Analysis  1.3.2 Simulators  1.3.3 Application Modeling                                                                                                                                    | 7<br>9                               |

| 2. PROPOSED PERFORMANCE PROJECTION SCHEME AND BACKGROUND .                                                                                                                                           | . 15                                 |

| 2.1 Performance Projection Framework 2.2 Proposed Projection Framework Challenges 2.3 Background 2.3.1 CMPs and Hierarchical System Design 2.3.2 Base System 2.3.3 Benchmarks 2.3.4 HPC Applications | . 19<br>. 19<br>. 20<br>. 23<br>. 25 |

| 3. COMPUTE COMPONENT PERFORMANCE PROJECTION                                                                                                                                                          | . 36                                 |

| 3.1 Hardware Performance Counter Metrics                                                                                                                                                             |                                      |

|                                                                   | Page |

|-------------------------------------------------------------------|------|

| 3.3 Computation Performance Projection Scheme                     | 43   |

| 3.3.1 Calculating Ranks for Metrics' Groups on Base Machine       |      |

| 3.3.2 Calculating Ranks for Metrics' Groups on Target Machine     |      |

| 3.3.3 Identifying Surrogates                                      |      |

| 3.3.4 Genetic Algorithm to Identify Surrogates                    |      |

| 3.4 Experimental Results                                          |      |

| 3.5 Related Work                                                  |      |

| 3.6 Summary                                                       |      |

| 4. COMMUNICATION COMPONENT PERFORMANCE PROJECTION                 | 64   |

| 4.1 MPI Profile                                                   | 66   |

| 4.2 Intel Benchmarks and Target Machine Parameters                | 67   |

| 4.3 Defining <i>WaitTime</i>                                      | 71   |

| 4.4 Performance Projection Scheme                                 |      |

| 4.4.1 HPC Application MPI Communication Model                     | 74   |

| 4.4.2 WaitTime Model                                              |      |

| 4.4.3 HPC Application Target System Communication Model           | 77   |

| 4.5 Experimental Results                                          | 79   |

| 4.6 Related Work                                                  | 87   |

| 4.7 Summary                                                       | 89   |

| 5. COMBINED COMPUTATION AND COMMUNICATION PERFORMANCE             |      |

| PROJECTION                                                        |      |

| 5.1 Cache Scaling Model                                           | 93   |

| 5.2 Compute Component Strong Scaling Model                        |      |

| 5.3 Combined Communication and Computation Performance Projection |      |

| Scheme                                                            |      |

| 5.4 Experimental Results                                          |      |

| 5.5 Related Work                                                  |      |

| 5.6 Summary                                                       | 117  |

| 6. SUMMARY AND FUTURE WORK                                        | 119  |

| 6.1 Summary                                                       | 119  |

| 6.2 Future Work                                                   |      |

| 6.2.1 OpenMP Communication Projection                             | 121  |

| 6.2.2 Hybrid Applications                                         | 124  |

| 6.2.3 Overall Proposed Projection Framework                       |      |

| 6.2.4 Predicting Projection Error Value                           |      |

| REFERENCES                                                        | 127  |

|      | Page |

|------|------|

| VITA | 133  |

# LIST OF FIGURES

| Page                                                                           |

|--------------------------------------------------------------------------------|

| Figure 1: Projection scheme high-level framework                               |

| Figure 2: A Nehalem processor and memory module [45], [46]                     |

| Figure 3: A Nehalem processor chip micro-photograph [45], [46]                 |

| Figure 4: An Intel Nehalem CMP node                                            |

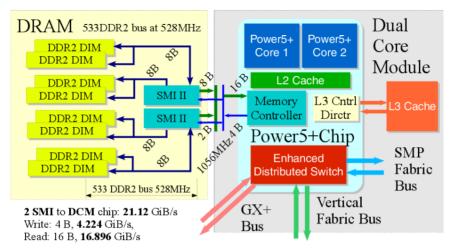

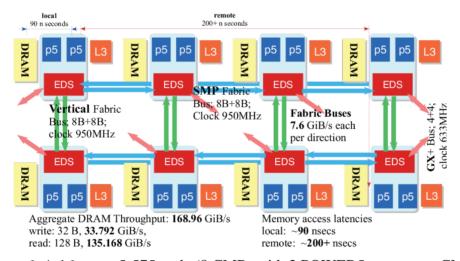

| Figure 5: Power5+ CMP and a shared 36MiB L3 cache                              |

| Figure 6: A 16-way p5-575 node (8 CMPs with 2 POWER5+ cores per CMP) 25        |

| Figure 7: Compute performance projection framework                             |

| Figure 8: Genetic tool framework                                               |

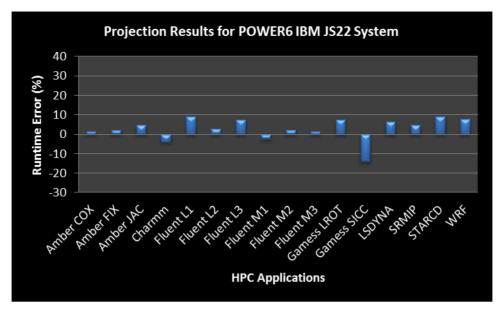

| Figure 9: Projection results for POWER6 IBM JS22 system                        |

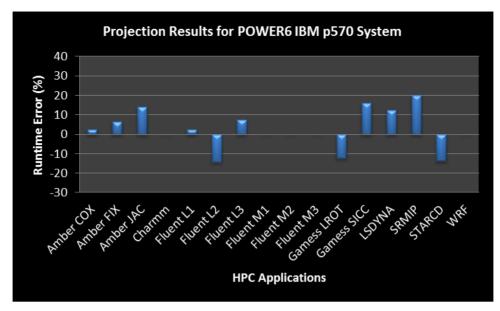

| Figure 10: Projection results for POWER6 IBM p570 system                       |

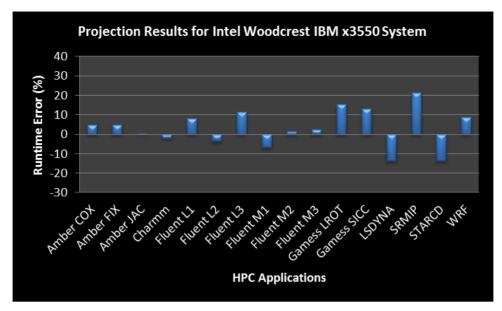

| Figure 11: Projection results for Intel Woodcrest IBM x3550 system             |

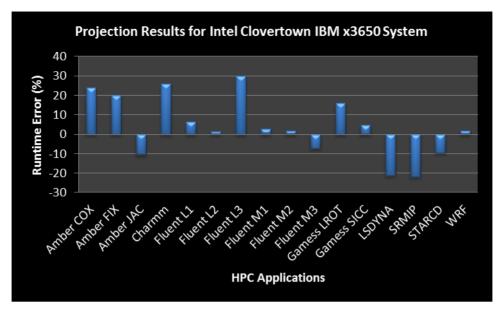

| Figure 12: Projection results for Intel Clovertown IBM x3650 system 58         |

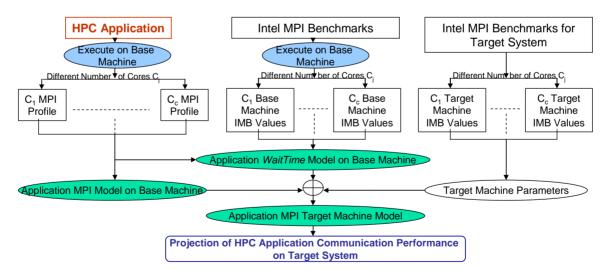

| Figure 13: Framework for MPI communication projection scheme                   |

| Figure 14: multi-Sendrecv benchmark                                            |

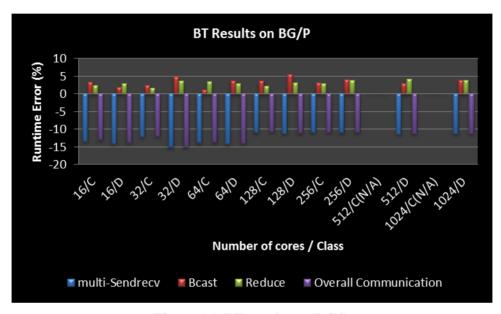

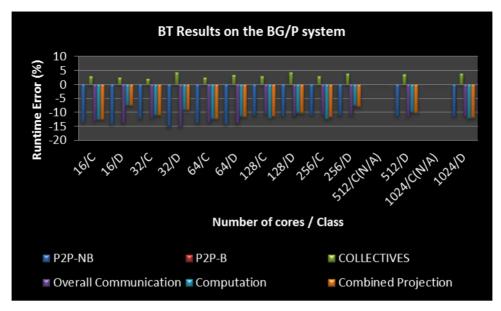

| Figure 15: BT results on BG/P                                                  |

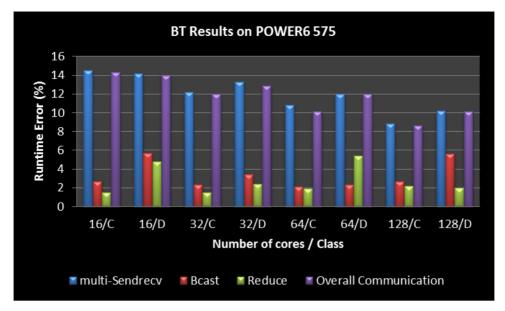

| Figure 16: BT results on POWER6 575                                            |

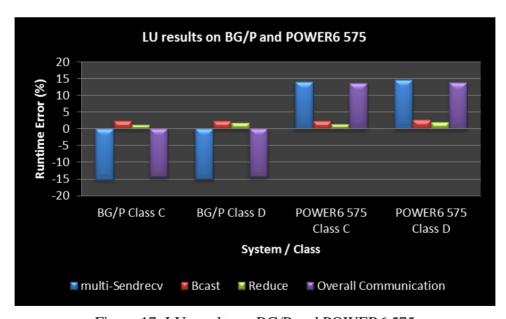

| Figure 17: LU results on BG/P and POWER6 575                                   |

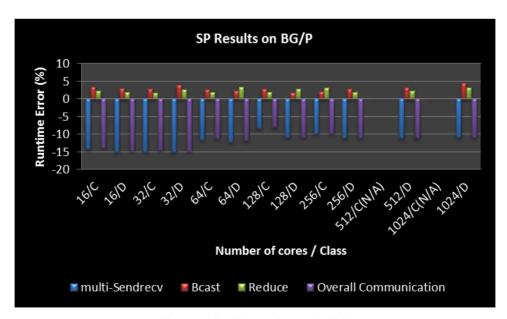

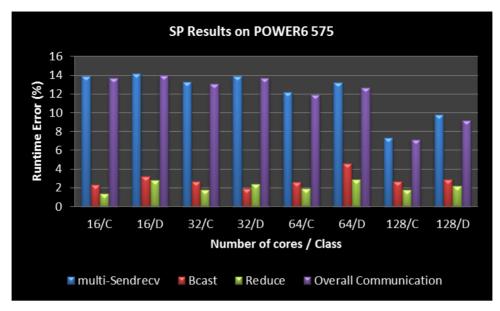

| Figure 18: SP results on BG/P                                                  |

| Figure 19: SP results on POWER6 575                                            |

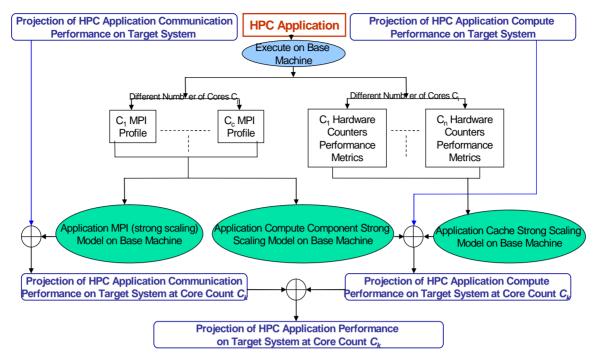

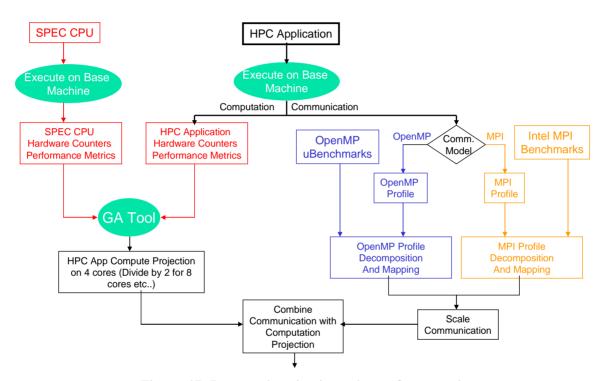

| Figure 20: Framework for combining computation and communication projection 92 |

| Page                                                                      |

|---------------------------------------------------------------------------|

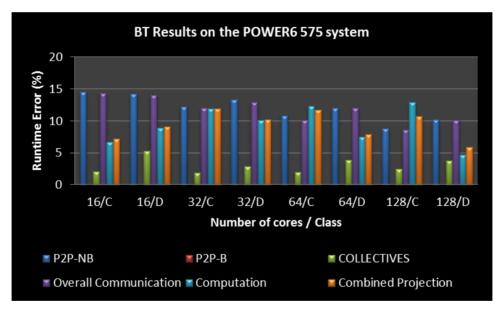

| Figure 22: BT results on the POWER6 575 system                            |

| Figure 21: BT results on the BG/P system                                  |

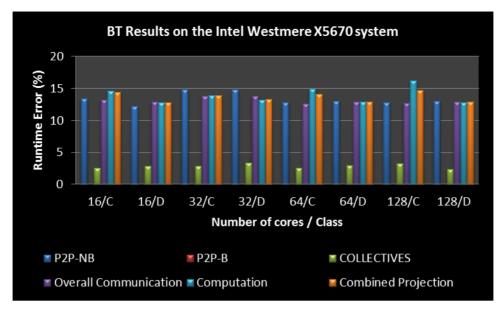

| Figure 23: BT results on the Intel Westmere X5670 system                  |

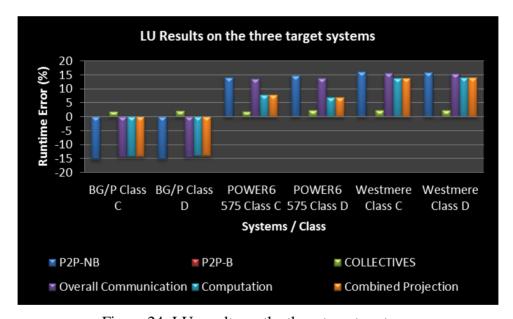

| Figure 24: LU results on the three target systems                         |

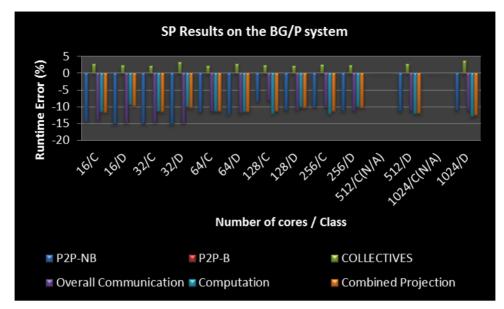

| Figure 25: SP results on the BG/P system                                  |

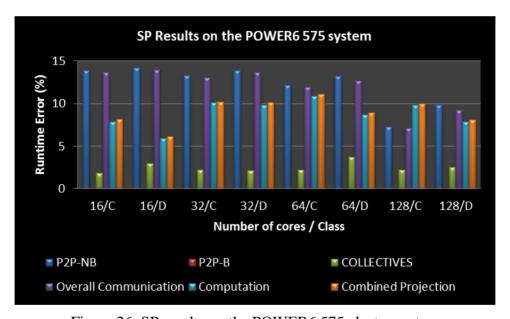

| Figure 26: SP results on the POWER6 575 cluster system                    |

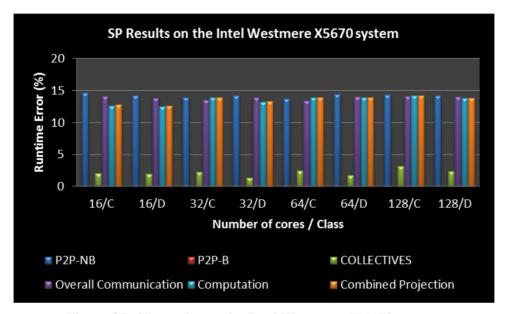

| Figure 27: SP results on the Intel Westmere X5670 system                  |

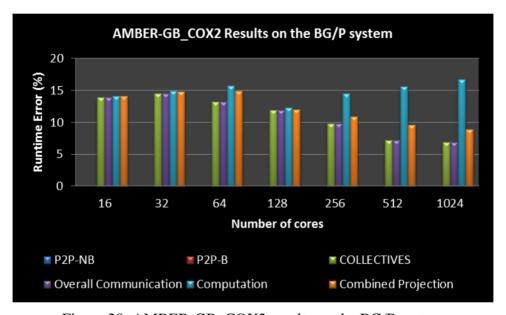

| Figure 28: AMBER-GB_COX2 results on the BG/P system                       |

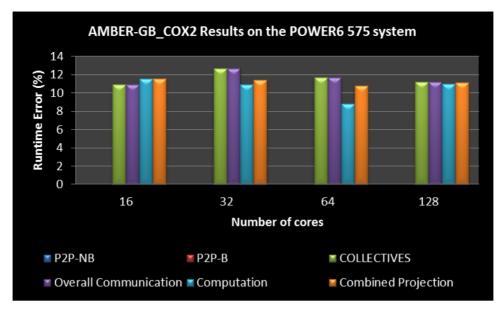

| Figure 29: AMBER-GB_COX2 results on the POWER6 575 system                 |

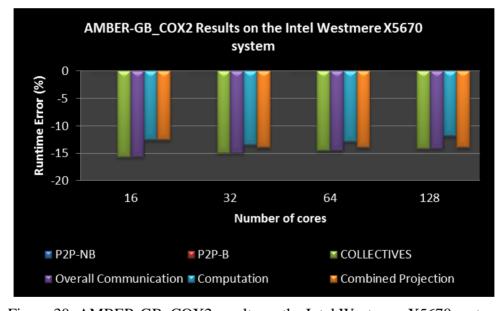

| Figure 30: AMBER-GB_COX2 results on the Intel Westmere X5670 system 105   |

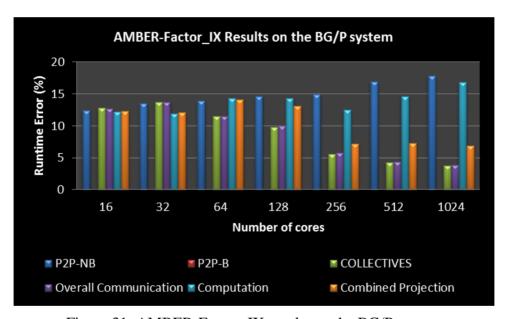

| Figure 31: AMBER-Factor_IX results on the BG/P system                     |

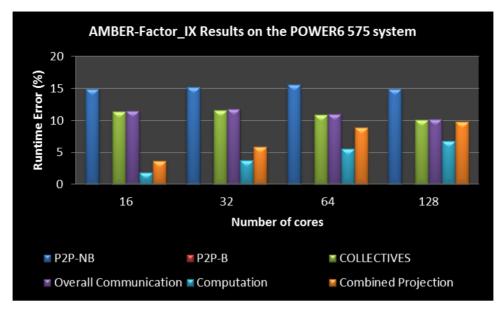

| Figure 32: AMBER-Factor_IX results on the POWER6 575 system               |

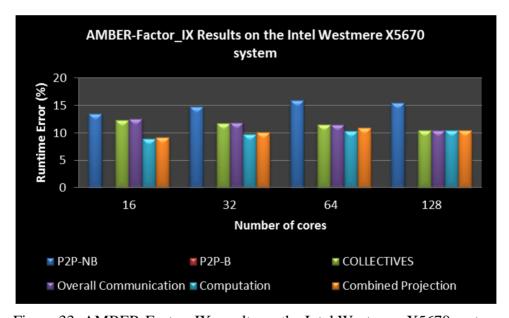

| Figure 33: AMBER-Factor_IX results on the Intel Westmere X5670 system 107 |

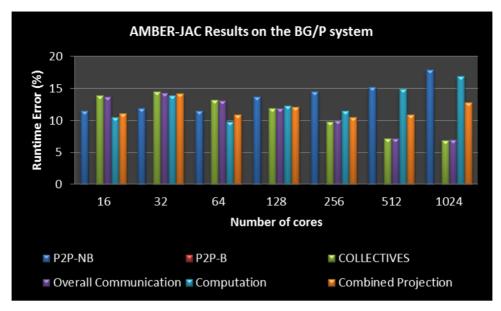

| Figure 34: AMBER-JAC results on the BG/P system                           |

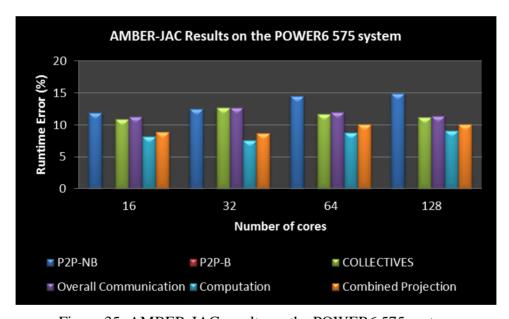

| Figure 35: AMBER-JAC results on the POWER6 575 system                     |

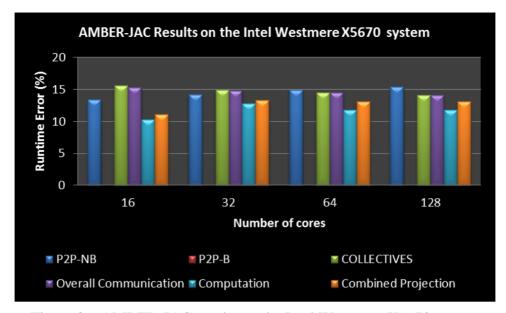

| Figure 36: AMBER-JAC results on the Intel Westmere X5670 system 109       |

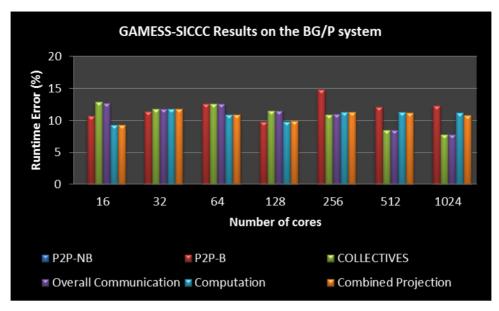

| Figure 37: GAMESS-SICCC results on the BG/P system                        |

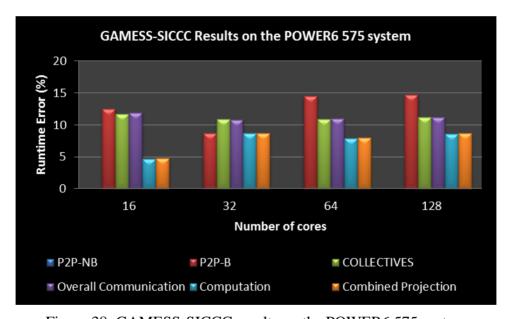

| Figure 38: GAMESS-SICCC results on the POWER6 575 system                  |

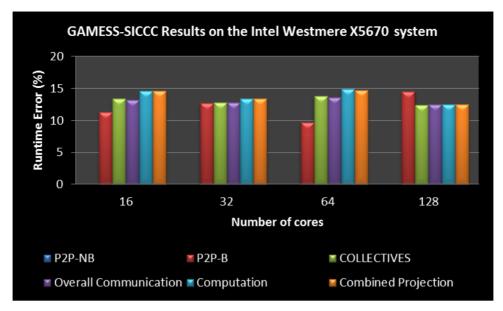

| Figure 39: GAMESS-SICCC results on the Intel Westmere X5670 system 111    |

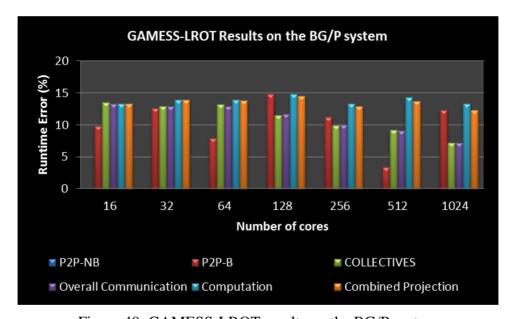

| Figure 40: GAMESS-LROT results on the BG/P system                         |

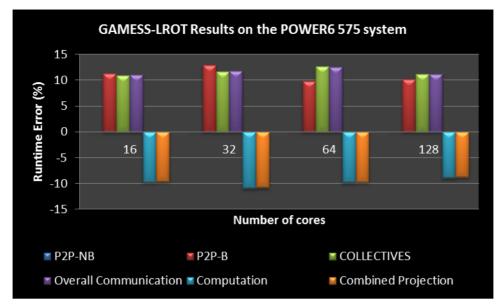

| Figure 41: GAMESS-LROT results on the POWER6 575 system                   |

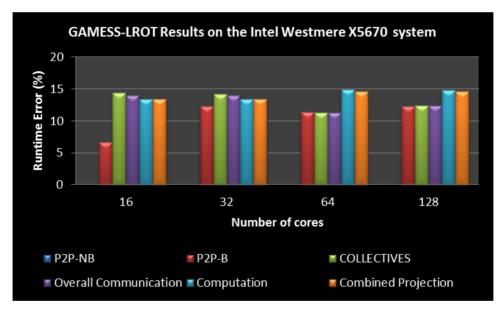

| Figure 42: GAMESS-LROT results on the Intel Westmere X5670 system         |

|                                                                  | Page |

|------------------------------------------------------------------|------|

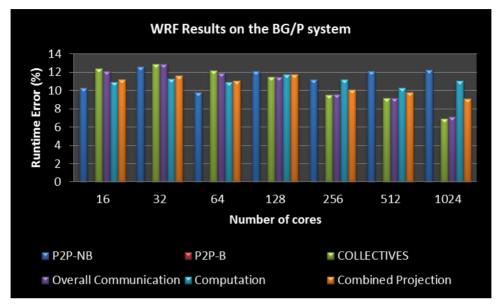

| Figure 43: WRF results on the BG/P system                        | 113  |

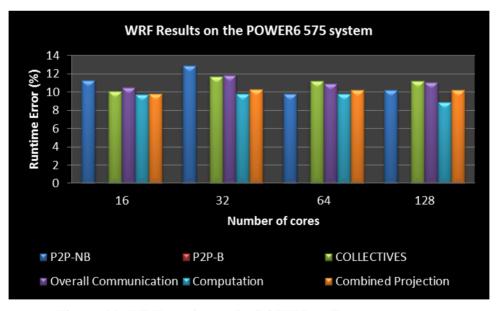

| Figure 44: WRF results on the POWER6 575 system                  | 113  |

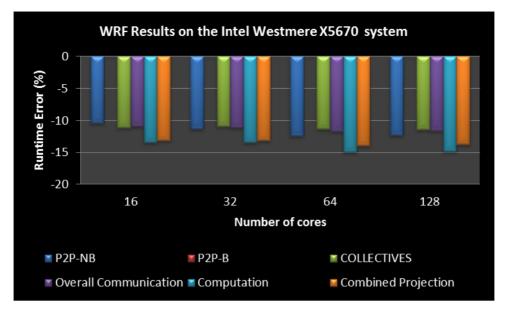

| Figure 45: WRF results on the Intel Westmere X5670 system        | 114  |

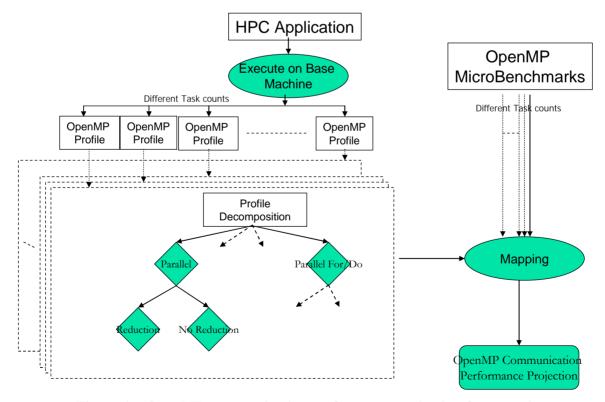

| Figure 46: OpenMP communication performance projection framework | 123  |

| Figure 47: Proposed projection scheme framework                  | 125  |

# LIST OF TABLES

|          | Pa                                                                | age |

|----------|-------------------------------------------------------------------|-----|

| Table 1  | CINT2006 benchmark suite                                          | 27  |

| Table 2  | CFP2006 benchmark suite                                           | 27  |

| Table 3  | HPC applications, their HPC areas, datasets and descriptions      | 33  |

| Table 4  | Metrics used to capture application behavior                      | 38  |

| Table 5  | Genetic Algorithm parameters                                      | 50  |

| Table 6  | Computation base system and target systems used for validation    | 52  |

| Table 7  | Surrogates for the HPC applications on POWER6 IBM JS22 system     | 54  |

| Table 8  | NAS-MZ benchmarks characteristics on base system for 16-128 tasks | 80  |

| Table 9  | Base system and the different systems used for validation         | 81  |

| Table 10 | Base system and different systems used for validation             | 97  |

| Table 11 | HPC workloads characteristics on base system for 128 tasks        | 98  |

#### 1. INTRODUCTION

Performance projections of High Performance Computing (HPC) applications onto various hardware platforms are important for hardware vendors and HPC users. The projections aid hardware vendors in the design of future systems, allowing them to compare the application performance across different existing and future systems; the projections help HPC users with system procurement and application refinements. In this dissertation, we present an efficient method to project the performance of HPC applications onto Chip Multiprocessor (CMP) based systems using widely available standard benchmark data. The main advantage of this method is the use of published data about the target machine; the target machine need not be available.

Performance projection of HPC applications allows designers of future systems to explore design trade-offs, such as in-order-execution versus out-order-execution, to develop a system that better matches the performance requirements of the HPC clients. Designers need projections because, in most cases, availability of platforms for HPC applications measurements is limited, especially for competitors' future systems. Further, simulations of such complicated applications on future systems are extremely time consuming. For HPC users, knowing in advance how applications will perform on different platforms help with selecting the best platform for procurement and execution. Further, the projections can aid in identifying areas for performance refinements.

The contributions of this dissertation to the current literature of performance projections can be summarized in the following points:

This dissertation follows the style of *IEEE Systems Journal*.

- 1. The proposed method uses publicly available benchmarks performance data for the target system in projecting the performance of HPC applications with average error rate of 11.22%. The proposed projection method does not require any access to the target system.

- 2. The projection method requires low overhead resulting from the use of one base system to characterize the properties of an HPC application and the benchmarks in combination with the publicly available benchmark data.

- 3. In this work, we model the micro-architecture of the base system and the impact of the micro-architecture on the application performance using detailed hardware counters. Modeling an application behavior independent of the micro-architecture specifications of the system it is executing on may yield inaccurate results [1].

- 4. For the communication projections, the proposed method uses MPI profiles of the HPC application instead of MPI traces resulting in very little storage requirements and eliminating the need for extensive IO during execution.

The publications resulting from this work are the following:

- S. Sharkawi, D. DeSota, R. Panda, S. Stevens, V. Taylor, X. Wu, *Using MPI Benchmarks to Project MPI Communication Performance of HPC Applications*, Submitted to ICPP 2011.

- S. Sharkawi, D. DeSota, R. Panda, R. Indukuru, S. Stevens, V. Taylor, X. Wu,

Performance Projection of HPC Applications Using SPEC CFP2006

Benchmarks, in Proceedings of IEEE IPDPS, Rome, Italy, 2009.

The remainder of this section identifies the different requirements and challenges with respect to performance projections and provides a discussion about related work. The remainder of this dissertation is organized as follows: The second Section provides an overview of the proposed performance projection scheme and presents some background on the problem. Section three describes the computation component projection method. Section four describes the communication component projection method and Section six provides the method that we use to integrate the projections of both components. The final section summarizes the overall research and presents areas of future work.

# 1.1 Performance Projection Requirements

In this dissertation, we present an efficient and accurate method for performance projection of HPC applications. An efficient performance projection method has low overhead in data collection and in the projection process [2], [3]. In addition, a performance projection method is considered accurate when projection error rate is below 20% [1].

## 1.1.1 Performance Data Requirements: HPC Application and Systems

In this dissertation, we efficiently collect performance data for the HPC applications and benchmarks on one base system. We use this performance data to characterize the micro-architectural characteristics of the base system and the impact of

the base system on the HPC application performance. In order to be efficient, the data collection process must satisfy the following requirements:

- (a) Low overhead and low cost. Acceptable low overhead is typically within 5% of the total execution time of the application [2], [3]. Also, the total size of the data collected needs to be moderate for current systems' memories and storage.

- (b) No manual intervention for recompilation and instrumentation so as to reduce the requirements on the user for the projections [4]. When instrumentation is inserted before compilation, the presence of instrumentation may inhibit optimization, in which case it will not measure the performance of optimized code; alternatively, optimization may move instrumentation, in which case the measured interval may not include all or only the code from the region of interest.

To produce accurate projections, performance data is required to have the following characteristics:

(a) Performance data needs to capture the major factors that impact the HPC application performance on the system used for execution. The measurement of time or one species of system event seldom identifies performance characteristics [1], [4]. Since HPC applications can be typically viewed as a combination of computation and communication [5], [6], the performance data should accurately represent the single core computation performance as well as the communication between the cores. From a computation perspective, each component of the processor and the memory hierarchy will

- have an impact on application performance. As for communication, each communication routine performance and characteristics need to be identified.

- (b) Raw event counts are seldom the desired metrics. Derived metrics such as cache miss ratios or cycles per floating point operation are far more useful than raw events in performance modeling [7], [8]. Also, for each application different performance metrics have different impact and this impact varies from one system to another.

# 1.1.2 Benchmarks Requirements

It is important that the benchmarks used for the projections satisfy the following requirements. First, the set of benchmarks must cover most of the performance space of HPC applications and HPC architectural characteristics. In addition, the benchmark set needs to be able to capture the micro-architectural features of the system it is testing. Second, the benchmark set needs to be a standard benchmark that is used by the industry, academia and HPC users. This allows for abundance of public data for the target systems. Even for future systems, vendors typically publicize about their systems performance using standard benchmarks. Finally, the benchmarks must be scalable to thousands of cores to allow for projections onto systems with different numbers of cores.

#### 1.2 Performance Projection Challenges

HPC systems are becoming more complex and hierarchical utilizing nodes of CMPs [9]. These systems can be configured to scale up to peta- or exa-scale systems. In

addition, CMP based systems utilize different processor architectures and interconnect schemes; thus, mapping from one base system to a target system imposes challenges described in the following subsections.

# 1.2.1 Complex and Hierarchical System Design

The hierarchical system design has a significant impact on the application performance [10]. The hierarchical design entails the sharing of resources and memory at the level of the cores. In addition, the hierarchical design involves the use of different interconnects for the different levels of the hierarchy. Thus, the projection method needs to take into account these features of the hierarchy.

#### 1.2.2 Mapping Architectural Characteristics from Base to Target System

Recall, published benchmark performance data about target system should suffice to understand the architectural characteristics of the target system in relation to the base. Typically, published benchmark data is a one metric value representing the performance of certain benchmark on a specific system [11]. This one performance metric, although represents some aspect of the system, masks many architectural characteristics of the system [1]. In order to map from the base system to the target, one needs to understand the behavior of the benchmark on the base system, the effect of the base system architecture on the benchmark performance, and the differences in the micro-architecture of the base versus that of the target system as depicted by the differences in the performance metrics of the benchmarks on the two systems.

#### 1.3 Related Work

Several techniques for performance projection have been proposed and used. Most common techniques include program modeling, code analysis, or architectural simulation. Code analysis, in addition to requiring significant expertise and abundant time, may not yield accurate performance projections due to the complexity of the hierarchical systems and applications. Performance projection using program modeling, on the other hand, needs to be a function of (at least) algorithm, implementation, compiler, operating system, underlying processor architecture, and interconnect technology to produce accurate projections. This may be impossible to achieve with the current complex systems and architectures. Architectural simulation yields extremely accurate projection results. Simulation provides the capability to observe component and system characteristics (e.g. performance and power) in order to make vital design decisions. However, simulating high-fidelity models can be very time consuming and even prohibitive when evaluating large-scale systems.

#### 1.3.1 Code Analysis

Manual source code analysis of HPC applications is a very complicated task. It is time consuming, requires high level of expertise and may lack accuracy [4]. To produce accurate projections, it is important to understand the performance characteristics of computation, communication and message passing software used for parallelization. Further, it is important to understand the interaction of the underlying architecture and interconnect with the application. All these keys require significant amount of expertise in parallel programming paradigms and techniques, parallel systems' architecture,

interconnect architecture and significant understanding of the source code of the application. Thus, manual source code analysis can be difficult and time consuming, especially with the hierarchical CMP based systems.

K"uhnemann et al in [12] proposed automatic source code analysis, which entails compile time prediction of execution time. They use *SUIF* (Stanford University Intermediate Format), which automates performance prediction of HPC applications. For each target system, a system profile is created for computation and communication. Their tool then generates a corresponding runtime function modeling the CPU execution time and the message passing overhead for the source code. This static runtime prediction lacks accuracy especially for MPI calls since collective calls can be translated differently at runtime. There are other automation tools for source code analysis [13]-[17]; however, such tools are better suited for compiler optimizations, identifying bottlenecks and code optimizations.

Miller et al in [15], [17] proposed ParaDyn tool, which uses DynInst [18] to automatically instrument the application binary. ParaDyn's goal is to automate the search for performance bottlenecks in parallel applications, not to project their performance. This is accomplished by attaching ParaDyn instrumentation manager to an application process. ParaDyn then scans the application binary image for procedures entry and exit points. Once this is done, performance metrics, such as CPU usage from the operating system and performance counter data using hardware performance counters, are collected for each procedure to identify performance bottlenecks. Further, Reed et al in [14] proposed SvPablo, which uses Pablo [13] in identifying bottlenecks. Pablo's main difference to ParaDyn is that Pablo instruments source code instead of binary.

Mellor-Crummy et al have developed HPCToolKit [16] that identifies bottlenecks without requiring any code instrumentation. HPCToolKit incorporates three components that are used in the performance analysis process. The first component, *hpcrun*, is responsible for collecting the hardware performance counters; *hpcrun* uses statistical sampling of hardware performance counters, and attributes metrics to both, the calling context and program structure. This is done using stack unwinding techniques to relate performance metrics to source code. The second component, *hpcstruct*, is responsible for analyzing the application binary to recover information about files, functions, loops etc. Finally, *hpcprof* correlates dynamic performance metrics to code structure. Again, the focus is on identifying bottlenecks, not performance predictions.

#### 1.3.2 Simulators

Simulation is often used to predict the performance of key applications to be executed on new systems. Simulation provides the capability to observe component and system characteristics (e.g. performance and power) in order to make vital design decisions. Simulating high-fidelity models, however, can be very time consuming and even prohibitive when evaluating large-scale systems. Simulations can require one to two orders of magnitude more time than the actual application. Currently, there are three major types of simulators:

Cycle-accurate node-level simulators [19]-[21]. These simulators are extremely

accurate, slow and can only simulate the node level performance of a system.

Scaling down an HPC application to fit on the simulator is nearly impossible

since these cycle accurate simulators are typically designed to simulate only the

- processor core performance. Hardware vendors use these simulators to measure their systems node level performance using industry standard benchmarks such as SPEC CPU.

- 2. Stochastic network models. These simulators are typically accurate in measuring the interconnect capabilities. They can only simulate network calls such as MPI calls; thus, they can't be used to execute a full HPC application. Typically, benchmarks such as IMB are executed on these simulators to measure the interconnect properties. Prakash and Bagrodia in [22] introduced MPI-SIM, which simulates the MPI communication library using a detailed contention model. The computation component of an application is executed on an actual processor. This limits prediction to systems using the same processor as the base machine. Also Wilmarth et al. in [23] introduced POSE, which uses a detailed network contention model to simulate the communication library only, i.e. no computation component projection.

- 3. Pseudo-accurate simulators. These simulators attempt to simulate the entire system, computation and communication, with less accuracy to reduce the simulation overhead. Zheng et al in [24] introduced BigSim, which is designed to predict performance using parallel simulation for massively large systems. In BigSim each target processor is emulated using a thread. Since each thread has a significant memory requirement to emulate a full processor, BigSim is well suited for systems that have low memory to processor ratio such as BlueGene systems. For other systems, simulations can be extremely slow. BigSim uses an optimistic approach for communication simulation, which assumes determinism in program

execution rather than an accurate contention model. In addition, BigSim uses heuristics to predict computation (not cycle-accurate). Also Susukita et al in [25] proposed macro-level simulation of communication. Mainly communication is macro simulated by replacing each MPI call by predicted runtime (compile time prediction based on target machine interconnect specification). As for computation, it is skeletonized into single processor execution. In [25], interleaved communication and computation, such as non-blocking MPI calls with computation blocks executed before the MPI call completion, cannot be accurately simulated. Other researches have proposed simulating only the critical components of an HPC application [26]. However, these simulators are not cycle-accurate.

# 1.3.3 Application Modeling

Performance projection of HPC applications using application modeling provides for a faster method than simulations. Performance projection using program modeling must incorporate algorithm, implementation, compiler, operating system, underlying processor architecture, and interconnect technology in the model to produce accurate projections. Furthermore, since the performance enhancing features of novel processing devices may be significantly different from a conventional microprocessor system, current performance modeling schemes have limited applicability on systems such as vector supercomputers and parallel systems with accelerator devices, systems with deeper memory hierarchy and different multi-core configurations. Thus, performance models

need to employ an application modeling paradigm that allows a user to develop not only "architecture aware" but also "application aware" performance models.

One approach is to build an analytical model for the application on the target platform using one of the known modeling techniques such as LogGP [27] or LogP [28]. The LogP models a parallel application based on four parameters: computational bandwidth, communication bandwidth, communication delay and efficiency of coupling of computation and communication. Since LogP was originally designed for short messages, LogGP extends the LogP model by adding the additional parameter G which reflects the bandwidth for long messages. Both the LogP and LogGP models assume a uniprocessor machine architectures where task placement effect on performance is ignored. Task placement on current SMP systems with CMP hierarchical designs has a major effect on performance specially due to the different communication protocols, shared memory or network interconnect, used by the communication library when communicating with inter vs. intra node processors. We can summarize the main advantages of this work over the LogP and LogGP models in the following points. First, LogP and LogGP models ignore the network topology and the routing algorithm. In current systems, network topologies have complicated and hierarchical designs, which have significant effect on communication performance. In our scheme, network topology effects are reflected in IMB values. Second, in our prediction methodology, support for collective communication acceleration in the hardware on the target system is captured by IMB; however, LogP and LogGP models assume that a processor will only do Send/Recv. Finally, we model *WaitTime* defined in section 4.3 which is typically due to load imbalance between computation and communication among different tasks. The LogP and LogGP don't model such WaitTime.

Blasko in [29] proposed a modeling technique that would significantly reduce the simulation time. Blasko used hierarchical modeling to analyze the program call structure. He utilized a call graph of the parallel program for the hierarchical performance analysis. In his bottom-up model, all procedures that do not contain any procedure calls are evaluated and simulated at stage one. These are the leaves of the graph. In the second stage, which concerns the callers, the callers are simulated and leaves already simulated in stage one are represented by delays. He then simulates parents all the way up to the root of the graph. This model was tightly coupled to VFCS and also doesn't accurately simulate the contention in the interconnect.

Taylor et al in [30] introduced the Prophesy system. In Prophesy, there are three program modeling techniques, curve fitting which is used to explore application scalability on the same system, parameterization which requires manual analysis of source code kernels to predict performance on target systems and kernel coupling which explores the interaction and sharing between different kernels. Clement and Quinn in [31] proposed modeling an application as a function of compiler effects, memory effects, communication overhead and floating point trends. Their work focused on projecting parallel speedup of an application rather than its performance on different systems.

Another application modeling technique achieves cross platform prediction using partial execution. Yang et al. in [2] proposed the use of partial execution of parallel applications on different systems in performance projection. They used partial execution

of application on target system to indicate its relative performance. This technique requires access to the target system.

# 2. PROPOSED PERFORMANCE PROJECTION SCHEME AND BACKGROUND

# 2.1 Performance Projection Framework

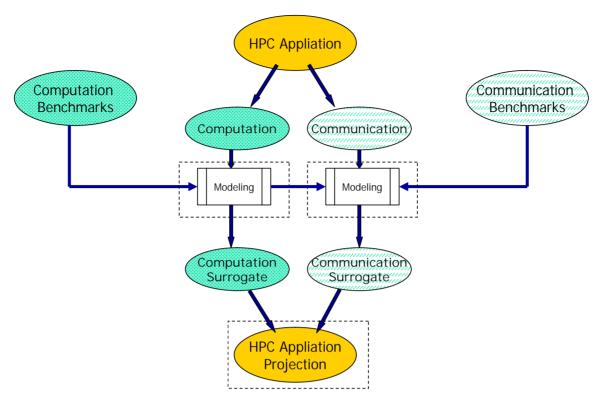

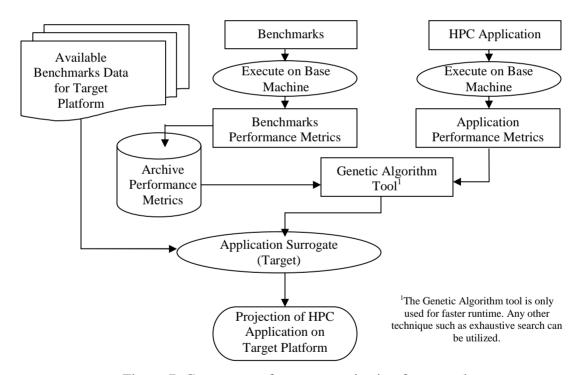

In this work we propose an efficient and accurate approach to projecting HPC applications' performance onto systems utilizing CMPs. Our method, called the surrogate-based workload application projection method, utilizes surrogate benchmarks (the surrogate is a linear equation of the appropriate benchmarks) to project an HPC application performance on target systems. Figure 1 depicts the high level framework of our projection scheme. As indicated in Figure 1, our projection scheme entails five steps:

- 1. Find the surrogate for the computation component of an HPC application.

The metrics used to identify the surrogate are described in detail in Section 3.

- 2. Use the performance data of the surrogate on the target system to project the compute performance of the HPC application on the target system.

- Find set of surrogates for the communication component of HPC application.

The metrics used to identify the set of surrogates are described in detail in Section 4.

- 4. Use the performance data of the surrogate on the target system to project the communication performance of the HPC application on the target system.

- Combine the communication and the computation performance projections to come up with the entire HPC application performance projection on the target system.

Figure 1: Projection scheme high-level framework

As indicated in Figure 1, this work encompasses modeling the HPC application as two separate components, the computation and the communication. Each component is further modeled as a combination of benchmarks. Compute performance is projected using CPU intensive benchmarks, specifically the SPEC CPU2006 suite [11], and hardware performance counter metrics; communication performance is projected using MPI benchmarks for MPI communications. The components in Figure 1 that are in dashed squares are the main focus of this research. The three main components are given below:

- a. Modeling the computation component of an HPC application

- b. Modeling the communication component of an HPC application

- c. Combining the two models to come up with an HPC application projection

We use the actual executions of surrogates on existing systems to model the HPC application as a linear function of the benchmarks. For the case of non-existing future systems, the only option is to use the simulated runtimes of the benchmarks. In addition, the complex hierarchical design of systems is accounted for in the linear function of the benchmarks. Different configurations for the benchmarks, such as binding one task per core or two tasks per core, exploit different system characteristics.

As for the communication component, we project the communication performance of HPC applications onto different systems using MPI benchmark data on the different systems as well as a base system, and the communication profile of the application on the base system. In particular, we use the Intel MPI Benchmarks (IMB) [32] as we find it the most comprehensive MPI benchmark suite. The arrow from the computation modeling to the communication modeling indicates that communication modeling partially depends on computation modeling.

The use of surrogates for performance projection of HPC applications has been proposed in [33]-[35]. The novelty of our approach in comparison to previous work that used surrogate based projections can be summarized in the following points:

## Computation Projection:

- The use of published benchmarks performance data for the target system suffices to project the performance of HPC application using only one base system.

- 2. Hardware performance counter metrics are grouped into several groups where each group has certain rank (in comparison to other metric groups) based on

the application properties and the system characteristics. Other research in the literature that used performance counter metrics and benchmarks for HPC projections do not rank metrics. In [33]-[35], all metrics have the same weight and have equal importance to the application.

- 3. Our approach incorporates available published benchmark data to model the target system in contrast to other work [26], [36], [37], [38] where access to at least one node of target system is required. Further, our approach allows for ranking the metric groups differently for each target system based on the system characteristics. The ranking of metric groups based on system characteristics provides for better projections for different architectures and systems.

- 4. Our method is independent of any benchmark suite. In this work, we used SPEC CPU2006 suite; however, adding any other benchmark suite(s) is very simple and doesn't require any change to the method.

## Communication Projection:

5. The main advantage of our method is the use of MPI profiles of the HPC application in contrast to MPI traces, which require significant storage and are very complicated, hard to understand and parse. For example, our method requires 12KB storage for the communication profile of the NAS BT benchmark [39], in contrast to 2.6 GB storage for an MPI trace of the communication behavior of the same benchmark for 128 tasks. Further, our method does not involve any simulations.

6. Another advantage is that we don't require any simulations of network events as in [5], [6], [40]. Such simulators are typically time consuming. Also creating an accurate contention model for all MPI routines [41]-[43], especially collective calls, can be extremely challenging.

## 2.2 Proposed Projection Framework Challenges

The separation of the communication and the computation components introduces some challenges and opportunities. MPI calls are reflected in the hardware performance counter metrics. To reduce the noise, we execute the HPC application using four tasks to reduce the communication. It is noted that some applications can't be executed on four tasks due to their large datasets. Also, some applications may have significant communication even with four tasks. A solution to this challenge would be to collect hardware performance counters in between MPI calls. That would require turning off counter collections during the MPI calls. However, there is a huge opportunity in this separation of computation and communication. Such separation allows for more scalability. If computation and communication were coupled, we would have to, one, find surrogates that match the application in communication and computation, two, be limited to parallel benchmarks, and, three, be limited to how scalable the benchmarks are.

## 2.3 Background

In this section, we discuss how CMP based systems are built and how their design affects the performance of HPC applications. Also, we discuss the base system that is

used throughout this research as well as its architectural characteristics. Finally, we present the benchmark suites of choice for this work that meets the requirements and challenges presented in section 1.2 as well as the HPC applications that are used for validation of our proposed method.

#### 2.3.1 CMPs and Hierarchical System Design

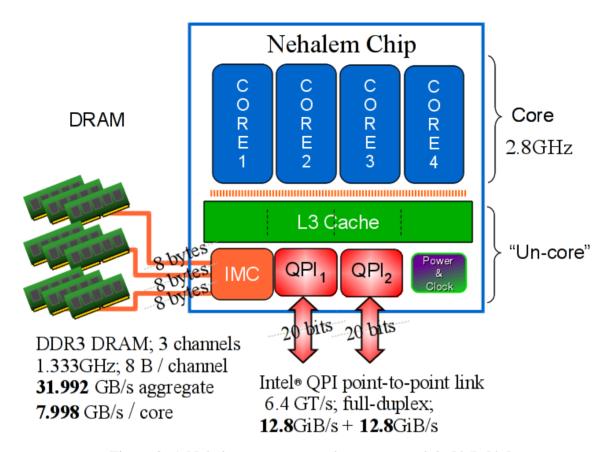

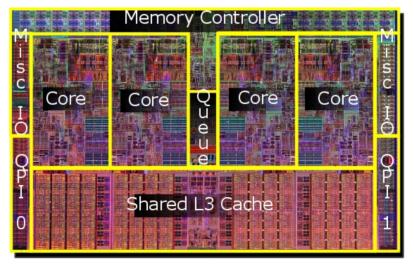

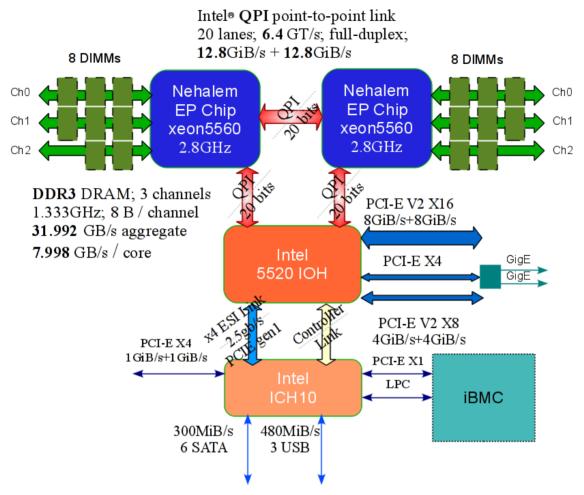

The current trend in high performance computing systems is shifting towards cluster systems with CMPs; further, the CMPs are usually configured hierarchically (e.g., multiple CMPs compose an MCM (multi-chip module), multiple MCMs compose a node, and multiple nodes compose a system). To illustrate, Figures 2 and 3 depict an Intel Nehalem CMP illustrative diagram and a Nehalem CMP chip micro-photograph, respectively. From figure 2, the Nehalem CMP has the following components: four identical compute cores, Cache Interface Unit (CIU) (switch connecting the 4 cores to the 4 L3 cache segments), level-3 (L3) cache controller and data block memory, 1 integrated memory controller (IMC) with 3 DDR3 memory channels and 2 Quick Path Interconnect (QPI) ports [44]. As indicated in the figure, the bandwidth to the main memory, 31.992 GB/s, is quite different from the bandwidth to the interconnect through the QPIs, 25.6 GiB/s ~ 27.5 GB/s. Furthermore, the bandwidth to the interconnect is affected by the geometry of the system and number of hops from source to destination.

Figure 2: A Nehalem processor and memory module [45], [46]

Figure 3: A Nehalem processor chip micro-photograph [45], [46]

Figure 4: An Intel Nehalem CMP node

As indicated in Figure 4, two CMPs are stacked together to form a CMP node. This CMP node is used a building block to build a larger cluster system connected through an interconnect switch. Typically, an interconnect switch using an InfiniBand technology will use a Fattree topology. This topology has an impact on an HPC application performance since the bandwidth and latency differ from one core to another depending on the distance between cores, number of hops, and layered switch latency.

Hierarchical system design imposes a major challenge for performance projection of HPC applications. The hierarchical design allows for sharing of resources and memory

at the lowest level involving the processing cores, L3 as in Figure 3. In addition, the hierarchical design provides for different interconnect characteristics for different levels in the hierarchy, i.e. cores on the same chip (latency of ~40 cycles), cores on different chips (~32GB/s) or cores on different nodes (~27.5GB/s). These issues must be considered in performance projection schemes of HPC applications. The application interaction with the system needs to be modeled. For example, a memory intensive application performance would be negatively impacted from memory and bandwidth sharing among cores on a CMP; however, the performance of a compute intensive application with minimal memory requirements could be greatly improved. Also, the interconnect characteristics have a major impact on HPC application performance due to the variation in bandwidth and latency among different interconnect levels as explained above. Furthermore, the architecture of interconnect between cores on the same CMP may also be different than the architecture of interconnect between CMPs on an MCM e.g. direct link vs. shared bus based. Therefore, the projection scheme has to be architecture and application aware.

### 2.3.2 Base System

The base machine used for this work is the p575 POWER5+ cluster system, TAMU Hydra. The POWER5+ chip features single-threaded and multi-threaded execution for higher performance. A single die contains two identical processor cores, each of which uses simultaneous multithreading (SMT) to support two logical threads. The result is a single dual-core POWER5+ chip that appears to be a four-way symmetric multiprocessor to the operating system. Both threads share execution units if both have

work. To the operating system, each thread executes on a logical processor. In our work, the data was collected in SMT mode, with configurations of one thread per core and two threads per core. We refer to the one thread per core configuration as Pseudo Single Thread mode (PST) and two threads per core as Simultaneous Multi Threading (SMT) mode [47].

The motivation for using PST and SMT metrics is to capture the behavioral changes in the application when running under different computing environments or with different set of resources. For example, when running an application in SMT mode, the bandwidth and cache available for each task is different than when running in PST mode. Also when the pipeline resources in the core are shared between threads, there are fewer resources available to each thread; thus, the behavior of the application is likely to change between these modes. The benchmarks that behave similarly to the HPC application under different computing conditions are a better representation for the application on different architectures.

The POWER5+ microprocessor provides Performance Monitor Unit (PMU) counters and a number of Performance Monitor Counters (PMC) to monitor and record several performance events. The POWER5+ has six PMCs per thread. The POWER5+ has 900 total events, 500 unique events, and 230 events per counter [48], [49]. We use the HPMCOUNT [50] tool on IBM systems to collect our hardware counter data. Figures 5 and 6 depict the POWER5+ CMP and the p575 node, respectively.

Figure 5: Power5+ CMP and a shared 36MiB L3 cache

Figure 6: A 16-way p5-575 node (8 CMPs with 2 POWER5+ cores per CMP)

### 2.3.3 Benchmarks

Recall from section 1.1.2 that the benchmark suites need to be an industry standard, have abundant published data, and span a majority of the performance characteristics space of HPC applications and CMP based systems. Also, to achieve scalability, we presented in section 2.1 our proposed projection method where the computation component is modeled in isolation of the communication component. Thus,

we use a suite of compute intensive benchmarks, specifically SPEC CPU2006, and a suite of communication intensive benchmarks, specifically Intel MPI Benchmarks (IMB).

(a) Compute Intensive Benchmarks: SPEC CPU2006

CPU2006 is SPEC's next-generation, industry-standardized, CPU-intensive benchmark suite, stressing a system's processor, memory subsystem and compiler [11]. SPEC designed CPU2006 to provide a comparative measure of compute-intensive performance across the widest practical range of hardware using workloads developed from real user applications.

SPEC CPU2006 focuses on compute intensive performance, which means these benchmarks emphasize the performance of: the computer processor (CPU), the memory architecture, and the compilers. It is important to remember the contribution of the latter two components. SPEC CPU performance intentionally depends on more than just the processor.

SPEC CPU2006 contains two components that focus on two different types of compute intensive performance: the CINT2006 suite measures compute-intensive integer performance, and the CFP2006 suite measures compute-intensive floating point performance. SPEC CPU2006 is not intended to stress other computer components such as networking, the operating system, graphics, or the I/O system. CINT2006 and CFP2006 are based on compute-intensive applications provided as source code. CINT2006 contains 12 benchmarks: 9 use C, and 3 use C++. The benchmarks are provided in Table 1 below. CFP2006 has 17 benchmarks: 4 use C++, 3 use C, 6 use Fortran, and 4 use a mixture of C and Fortran. The benchmarks are provided in Table 2 below.

Table 1: CINT2006 benchmark suite

| Benchmark      | Language | Area/Field                     |

|----------------|----------|--------------------------------|

| 400.perlbench  | С        | PERL Programming Language      |

| 401.bzip2      | C        | Compression                    |

| 403.gcc        | C        | C Compiler                     |

| 429.mcf        | С        | Combinatorial Optimization     |

| 445.gobmk      | С        | Artificial Intelligence: go    |

| 456.hmmer      | С        | Search Gene Sequence           |

| 458.sjeng      | С        | Artificial Intelligence: chess |

| 462.libquantum | C        | Physics: Quantum Computing     |

| 464.h264ref    | C        | Video Compression              |

| 471.omnetpp    | C++      | Discrete Event Simulation      |

| 473.astar      | C++      | Path-finding Algorithms        |

| 483.xalancbmk  | C++      | XML Processing                 |

Table 2: CFP2006 benchmark suite

| Benchmark     | Language  | Area/Field                      |

|---------------|-----------|---------------------------------|

| 410.bwaves    | Fortran   | Fluid Dynamics                  |

| 416.gamess    | Fortran   | Quantum Chemistry               |

| 433.milc      | С         | Physics: Quantum                |

|               |           | Chromodynamics                  |

| 434.zeusmp    | Fortran   | Physics/CFD                     |

| 435.gromacs   | C/Fortran | Biochemistry/Molecular Dynamics |

| 436.cactusADM | C/Fortran | Physics/General Relativity      |

| 437.leslie3d  | Fortran   | Fluid Dynamics                  |

| 444.namd      | C++       | Biology/Molecular Dynamics      |

| 447.dealII    | C++       | Finite Element Analysis         |

| 450.soplex    | C++       | Linear Programming,             |

|               |           | Optimization                    |

| 453.povray    | C++       | Image Ray-tracing               |

| 454.calculix  | C/Fortran | Structural Mechanics            |

| 459.GemsFDTD  | Fortran   | Computational Electromagnetics  |

| 465.tonto     | Fortran   | Quantum Chemistry               |

| 470.lbm       | С         | Fluid Dynamics                  |

| 481.wrf       | C/Fortran | Weather Prediction              |

| 482.sphinx3   | С         | Speech recognition              |

The SPEC CPU2006 is a benchmark suite composed of serial applications. It can be run in throughput mode with multiple instances of a workload to understand multiprocessor behavior. In parallel applications, the execution processes (threads) are distributed across different parallel computing cores. Often the dataset is divided among processors. In contrast, serial applications have one execution process working on the entire dataset. One way to account for this difference is to use throughput data for SPEC. This still leaves the issue that when the number of threads in parallel application changes the dataset per thread changes while with serial applications the working set is a constant size. When running in PST mode, we run four serial tasks of SPEC each bound to a separate core of the POWER5+ chip, thereby using two chips. In this case each task gets a dedicated CPU and L2 resources and the L3 is shared between two tasks. On the other hand, when we run in SMT mode, we run four serial tasks of SPEC each bound on a logical CPU (thread), thus using one chip. In this case two tasks share the CPU and L2 resources and the L3 is shared between four tasks. As for the HPC applications, all runs are configured as four parallel tasks each bound to a separate core on two chips in PST mode or each bound to a separate thread on one chip in SMT mode. Since both runs use four tasks, the dataset size per task remains constant on the parallel application as in the SPEC throughput runs. The effective cache size for each task changes proportionally between PST and SMT modes. Using such configurations we guarantee that the working set size per thread doesn't change from SMT mode to PST mode.

### (b) Communication Intensive Benchmarks: IMB

The idea of Intel MPI Benchmark is to provide a concise set of elementary MPI benchmark kernels. Its objective is to provide a concise set of benchmarks targeted at measuring the most important MPI functions. The IMB-MPI1 contains the benchmarks:

- *PingPong*: is the classical pattern used for measuring startup and through-put of a single message sent between two processes.

- PingPing: measures startup and throughput of single messages, with the crucial difference from PingPong that messages are obstructed by oncoming messages.

- Sendrecv: Based on MPI\_Sendrecv, the processes form a periodic communication chain. Each process sends to the right and receives from the left neighbor in the chain.

- *Exchange*: The group of processes is seen as a periodic chain, and each process exchanges data with both left and right neighbor in the chain.

- *Bcast*: A root process broadcasts X bytes to all.

- *Allgather*: Every process inputs X bytes and receives the gathered X\*(#processes) bytes.

- Allgatherv: Functionally is the same as Allgather. However, with the MPI\_Allgatherv function it shows whether MPI produces overhead due to the more complicated situation as compared to MPI\_Allgather.

- Scatter: The root process inputs X\*(#processes) bytes (X for each process); all

processes receive X bytes.

- Scatterv: The root process inputs X\*(#processes) bytes (X for each process); all

processes receive X bytes.

- *Gather*: All processes input X bytes, the root process receives X\*(#processes) bytes (X from each process).

- *Gatherv*: All processes input X bytes, the root process receives X\*(#processes) bytes (X from each process).

- Alltoall: Every process inputs X\*(#processes) bytes (X for each process) and receives X\*(#processes) bytes (X from each process).

- Alltoallv: Every process inputs X\*(#processes) bytes (X for each process) and receives X\*(#processes) bytes (X from each process).

- Reduce: Reduces a vector of length L = X/sizeof(float) float items where X is message size. The MPI data-type is MPI\_FLOAT, the MPI operation is MPI\_SUM.

- Reduce\_scatter: Reduces a vector of length L = X/sizeof(float)float items. The

MPI data-type is MPI\_FLOAT, the MPI operation is MPI\_SUM. In the scatter

phase, the L items are split as evenly as possible.

- Allreduce: Reduces a vector of length L = X/sizeof(float) float items. The MPI

data-type is MPI\_FLOAT, the MPI operation is MPI\_SUM.

- *Barrier*: MPI\_Barrier

In addition to the IMB-MPI1 (MPI1 Standard), IMB provides the extended IMB suite which includes a set of benchmarks to measure the MPI2 standard MPI functionalities. In this work, we only focus on the one sided routines of MPI from the

MPI2 standard. The remaining set of routines in the MPI2 standard is MPI-IO related which is not addressed in this dissertation. The benchmarks in the IMB-EXT are classified into three categories [32]:

- 1. Single transfer: The benchmarks in this class focus on a single data transferred between one source and one target. Single transfer IMB-EXT benchmarks only run with 2 active processes. Single transfer benchmarks, roughly speaking, are local mode. The particular pattern is purely local to the participating processes. There is no concurrency with other activities. Best case results are to be expected.

- 2. Parallel transfer: These benchmarks focus on global mode, say, patterns. The activity at a certain process is in concurrency with other processes, the benchmark timings are produced under global load. The number of participating processes is arbitrary.

- 3. Collective: This class contains benchmarks of functions that are collective in the proper MPI sense. Not only is the power of the system relevant here, but also the quality of the implementation for the corresponding higher level functions.

The benchmarks of interest in IMB-EXT that we focus on in this work are:

- *Unidir\_Put*: Benchmark for the MPI\_Put function.

- *Unidir Get*: Benchmark for the MPI Get function.

- Bidir Put: Benchmark for MPI Put, with bi-directional transfers.

- *Bidir\_Get*: Benchmark for MPI\_Get, with bi-directional transfers.

- Accumulate: Benchmark for the MPI\_Accumulate function. Reduces a vector of length L = X/sizeof(float) float items. The MPI data-type is MPI\_FLOAT, the MPI operation is MPI\_SUM.

- *Window*: Benchmark measuring the overhead of an MPI\_Win\_create / MPI\_Win\_fence / MPI\_Win\_free combination. In order to prevent the implementation from optimizations in case of an unused window, a negligible non trivial action is performed inside the window. The MPI\_Win\_fence is to properly initialize an access epoch.

# 2.3.4 HPC Applications

In this work, we used eight large-scale scientific applications and the three NAS Multi-Zone Parallel Benchmarks [39] to validate our projection method. The eight large-scale scientific applications are: AMBER [51], CHARMM [52], FLUENT [53], GAMESS [54], LS-DYNA [55], a seismic application that will be referred to as Seismic, STAR-CD [56] and WRF [57]. Some of these applications have multiple datasets totaling to 16 different workloads each having different computational and communication characteristics. Description of the applications is given in Table 3 below.

Table 3: HPC applications, their HPC areas, datasets and descriptions

| Application Name    | Category  | Datasets     | Description                       |

|---------------------|-----------|--------------|-----------------------------------|

| Amber (Assisted     | Molecular | •GB-COX2:    | A suite of programs focused on    |

| Model Building with | Dynamics  | Generalized  | molecular dynamics                |

| Energy Refinement)  |           | Born model   | simulations, particularly on      |

|                     |           | •Factor IX:  | biomolecules.                     |

|                     |           | Human Factor |                                   |

|                     |           | IX           |                                   |

|                     |           | •JAC: Joint  |                                   |

|                     |           | Amber and    |                                   |

|                     |           | CHARMM       |                                   |

| CHARMM              | Molecular | Alanine      | A molecular simulation program    |

| (Chemistry at       | Dynamics  | Dipeptide    | that focuses on the study of      |

| HARvard             |           |              | molecules of biological interest, |

| Macromolecular      |           |              | including peptides, proteins,     |

| Mechanics)          |           |              | prosthetic groups, small          |

|                     |           |              | molecule ligands, nucleic acids,  |

|                     |           |              | lipids, and carbohydrates.        |

Table 3: continued

| Category      | Datasets                                                                    | Description                                                                                                                            |  |

|---------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--|

| Computational | L1, L2, L3,                                                                 | A CFD solver for complex                                                                                                               |  |

| Fluid         | M1, M2 and                                                                  | flows ranging from                                                                                                                     |  |

| Dynamics      | M3                                                                          | incompressible (low subsonic)                                                                                                          |  |

|               |                                                                             | to mildly compressible                                                                                                                 |  |

|               |                                                                             | (transonic) to highly                                                                                                                  |  |

|               |                                                                             | compressible (supersonic and                                                                                                           |  |

|               |                                                                             | hypersonic) flows.                                                                                                                     |  |

|               |                                                                             |                                                                                                                                        |  |

| Ab Initio     | L-                                                                          | An electronic structure code                                                                                                           |  |

| Quantum       | ROTENON                                                                     | with the primary focus on ab                                                                                                           |  |

| Chemistry     | and SICCC                                                                   | initio quantum chemistry                                                                                                               |  |

|               |                                                                             | calculations.                                                                                                                          |  |

|               |                                                                             |                                                                                                                                        |  |

| Crash         | 3 Car Crash                                                                 | A general purpose transient                                                                                                            |  |

| Simulation    |                                                                             | dynamic finite element                                                                                                                 |  |

|               |                                                                             | program focused on complex                                                                                                             |  |

|               |                                                                             | real world problems.                                                                                                                   |  |

| Seismic       | N/A                                                                         | A finite-difference algorithm                                                                                                          |  |

|               |                                                                             | applied in the frequency                                                                                                               |  |

|               |                                                                             | domain focused on Seismic                                                                                                              |  |

|               |                                                                             | Migration.                                                                                                                             |  |

|               | Computational Fluid Dynamics  Ab Initio Quantum Chemistry  Crash Simulation | Computational L1, L2, L3, Fluid M1, M2 and Dynamics M3  Ab Initio L- Quantum ROTENON Chemistry and SICCC  Crash 3 Car Crash Simulation |  |

Table 3: continued

| Category      | Datasets                             | Description                                                  |

|---------------|--------------------------------------|--------------------------------------------------------------|

| Computational | Mercedes                             | A CFD code that focuses on                                   |

| Fluid         | C-Class                              | performing powerful multi-                                   |

| Dynamics      |                                      | physics (flow, thermal and                                   |

|               |                                      | stress) simulations.                                         |

| Weather       | ConUS                                | A next-generation mesoscale                                  |

| Simulation    |                                      | numerical weather prediction                                 |

|               |                                      | system designed to serve both                                |

|               |                                      | operational forecasting and                                  |

|               |                                      | atmospheric research needs.                                  |

|               |                                      |                                                              |

|               | Computational Fluid Dynamics Weather | Computational Mercedes Fluid C-Class Dynamics  Weather ConUS |

## 3. COMPUTE COMPONENT PERFORMANCE PROJECTION\*

Recall that an HPC application performance is modeled as a function of its computation and communication. The behavior of the compute component of an HPC application is represented by a set of hardware performance counter metrics. This allows for modeling the compute component without the need for simulations or the need for code analysis. We use the SPEC CPU2006 benchmark suite, described in section 2.3.3, for our possible surrogates and the IBM p575 machine, described in section 2.3.2, as the base machine.

Figure 7: Compute performance projection framework

<sup>\*</sup>Part of this section is reprinted with permission from "Performance Projection of HPC Applications Using SPEC CFP2006 Benchmarks", by Sameh Sharkawi, Don DeSota, Raj Panda, Rajeev Indukuru, Stephen Stevens, Valerie Taylor, and Xingfu Wu, in *Proc. IEEE IPDPS*, Rome, Italy, May 2009, Copyright 2009 by IEEE.

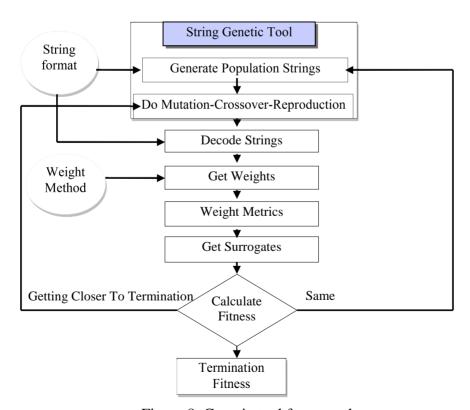

Figure 7 depicts the high level framework of our compute projection scheme. The SPEC CPU2006 benchmarks are executed once on the base machine in Simultaneous Multi Threading (SMT) mode, i.e. two threads per core, and in Single Threaded (ST) mode, i.e. one thread per core. The resultant hardware performance counter data is archived for use as needed. In addition, the HPC applications are executed once on the base machine in SMT and PST modes and the resultant hardware counter data is archived. A tool based on a Genetic Algorithm (GA) is then used to identify the "best" group of benchmarks that have similar behavior as the HPC application; this is done for each HPC application. The output of the GA is a linear equation of the group of benchmarks that best match the HPC application; this equation is given the term "surrogate". Performance data of the benchmarks that comprise the surrogate is then used to project the performance of the application onto a target machine. The target machine performance data for the surrogate is obtained from published data from actual execution or simulations (for future machines).

### 3.1 Hardware Performance Counter Metrics

We define the applications and benchmarks' behavior as a function of six groups of metrics. These six groups are:

- G<sub>1</sub> Cycles Per Instruction (CPI) Completion Cycles [49],

- G<sub>2</sub> -- CPI Stall Cycles [49],

- G<sub>3</sub> -- Floating Point Instructions [48],

- G<sub>4</sub> Data Effective to Real Address Translation (DERAT), Data Segment Lookahead Buffer (DSLB) and Data Table Lookahead Buffer (DTLB) caches miss rates [48],

- G<sub>5</sub> Data Cache Reloads and [48]

- G<sub>6</sub> Memory Bandwidth [48].

The choice of these groups of metrics is intended to characterize the application's behavior from a micro-architecture perspective. The first three groups focus on the computation behavior and the last three groups focus on the memory behavior. Group 1  $(G_1)$  shows the portion of the total CPI that was spent by the processor to complete architected instructions, while group 2  $(G_2)$  shows the portion of the total CPI that was spent in various stalling conditions. Group 3  $(G_3)$  shows the distribution of the different types of floating point instruction. Group 4  $(G_4)$  shows the miss rates for DERAT, DTLB and DSLB caches. Group 5  $(G_5)$  shows the application's memory behavior due to cache hits/misses, cache configuration, memory access patterns and memory latency while group 6  $(G_6)$  shows the application's memory bandwidth behavior. Table 4 has the detailed list of the metrics used in this work.

Table 4: Metrics used to capture application behavior

|       |                  | Metric Name      | <b>Metric Description</b>          |

|-------|------------------|------------------|------------------------------------|

| $G_1$ | m <sub>1,1</sub> | CPI_CMPL_CYC     | Completion cycles                  |

| $G_2$ | m <sub>2,1</sub> | CPI_GCT_EMPTY_IC | Pipeline Empty due to Instruction- |

|       |                  | _MISS            | Cache Miss                         |

Table 4: continued

|                   | Metric Name                               | Metric Description                          |

|-------------------|-------------------------------------------|---------------------------------------------|

| $m_{2,2}$         | CPI_GCT_EMPTY_BR                          | Pipeline Empty due to Branch                |

|                   | _MPRED                                    | MisPrediction                               |

| m <sub>2,3</sub>  | CPI_GCT_EMPTY_OTHER                       | Pipeline Empty ( Other)                     |

| m <sub>2,4</sub>  | CPI_STALL_LSU_ERAT                        | Load,Store Translation Stalls               |

|                   | _MISS                                     |                                             |

| m <sub>2,5</sub>  | CPI_STALL_LSU_REJECT                      | Load Store (Other Reject) Stalls            |

|                   | _OTHERS                                   |                                             |

| m <sub>2,6</sub>  | CPI_STALL_LSU                             | Data Cache Miss Stalls                      |

|                   | _DCACHE_MISS                              |                                             |

| m <sub>2,7</sub>  | CPI_STALL_LSU                             | Load/Store flush penalty and latency        |

|                   | _OTHERS                                   |                                             |

| m <sub>2,8</sub>  | CPI_STALL_FXU_DIV                         | Stall by any form of                        |

|                   |                                           | DIV/MTSPR/MFSPR instruction                 |

| m <sub>2,9</sub>  | CPI_STALL_FXU                             | Stall by FXU basic latency                  |

|                   | _OTHERS                                   |                                             |

| m <sub>2,10</sub> | CPI_STALL_FPU_DIV                         | Stall by any form of FDIV/FSQRT             |

|                   |                                           | instruction                                 |

| m <sub>2,11</sub> | CPI_STALL_FPU                             | Stall by FPU basic latency                  |