# A DUAL-SUPPLY BUCK CONVERTER WITH IMPROVED LIGHT-LOAD EFFICIENCY

A Thesis

by

**CHAO ZHANG**

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE

May 2011

Major Subject: Electrical Engineering

A Dual-Supply Buck Converter with Improved Light-Load Efficiency

Copyright 2011 Chao Zhang

# A DUAL-SUPPLY BUCK CONVERTER WITH IMPROVED LIGHT-LOAD EFFICIENCY

A Thesis

by

## **CHAO ZHANG**

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## MASTER OF SCIENCE

Approved by:

Chair of Committee, Edgar Sanchez-Sinencio

Committee Members, Samuel Palermo

Peng Li

Duncan M. Walker

Head of Department, Costas N. Georghiades

May 2011

Major Subject: Electrical Engineering

### ABSTRACT

A Dual-Supply Buck Converter with Improved Light-Load Efficiency. (May 2011)

Chao Zhang, B.S., Zhejiang University, China

Chair of Advisory Committee: Dr. Edgar Sanchez-Sinencio

Power consumption and device size have been placed at the primary concerns for battery-operated portable applications. Switching converters gain popularity in powering portable devices due to their high efficiency, compact sizes and high current delivery capability. However portable devices usually operate at light loads most of the time and are only required to deliver high current in very short periods, while conventional buck converter suffers from low efficiency at light load due to the switching losses that do not scale with load current. In this research, a novel technique for buck converter is proposed to reduce the switching loss by reducing the effective voltage supply at light load.

This buck converter, implemented in TSMC 0.18µm CMOS technology, operates with a input voltage of 3.3V and generates an output voltage of 0.9V, delivers a load current from 1mA to 400mA, and achieves 54% ~ 91% power efficiency. It is designed to work with a constant switching frequency of 3MHz. Without sacrificing output frequency spectrum or output ripple, an efficiency improvement of up to 20% is obtained at light load.

# DEDICATION

To my parents

#### **ACKNOWLEDGEMENTS**

I would like to express my sincere thanks to my advisor, Dr. Sanchez, who gave me the opportunity to pursue my MS degree under his guidance. I am very grateful for his professional advisement and support throughout my graduate study. I would also like to thank Dr. Samuel Palermo, Dr. Peng Li and Dr. Duncan M. Walker for severing on my committee. And thanks to Dr. Rabi N. Mahapatra for substituting for my defense.

Thanks also go to my colleagues at AMSC group for giving me valuable experience. Special thanks to Heng Zhang. Being part of her ADC project was a precious learning exercise, not only because she shared her valuable design and layout knowledge with me, but also her serious scientific attitude, professional thought, hardworking spirit has inspired me during my whole graduate life. I would like to thank my team members in buck converter project, Miguel A. Rojas-González, Joselyn Torres and Adrian Colli-Menchi, for their cooperation, great advice and making the project a great experience. I would like to thank all my other friends in AMSC group for their support and company. Studying together with them, discussion questions and sharing ideas are joyful memories for me. I also want to thank Ella and Tammy for their assistance.

Finally, I would like to express my deepest gratitude to my parents for their encouragement and unconditional love. I couldn't go this far without their support.

# TABLE OF CONTENTS

|                                                                           | Page |

|---------------------------------------------------------------------------|------|

| ABSTRACT                                                                  | iii  |

| DEDICATION                                                                | iv   |

| ACKNOWLEDGEMENTS                                                          | v    |

| LIST OF FIGURES                                                           | X    |

| LIST OF TABLES                                                            | xvi  |

| 1. INTRODUCTION                                                           | 1    |

| 1.1 Research Motivation                                                   |      |

| 1.2 Thesis Organization                                                   | 3    |

| 2. FUNDAMENTALS                                                           | 4    |

| 2.1 Introduction of Switching Converters                                  | 4    |

| 2.2 DC-DC Switching Converters                                            | 5    |

| 2.2.1 Introduction                                                        | 5    |

| 2.2.2 Comparison with Linear Regulators and Switched-Capacitor Converters | 6    |

| 2.2 Introduction of Buck and Boost Converters                             | 12   |

| 2.2.1 Basics of Buck Converter                                            | 14   |

| 2.2.2 Basics of Boost Converter                                           | 21   |

| 2.3 Open Problems in Buck Converters                                      | 24   |

| 2.3.1 High Efficiency                                                     | 24   |

| 2.3.2 Control Schemes                                                     | 26   |

| 2.3.3 Fully Integration                                                   | 27   |

| 2.3.4 Single Inductor Multiple Output                                     | 29   |

| 2.4 Light-Load Efficiency of Buck Converters                              | 29   |

| 2.4.1 Power Losses Analysis of Basic Buck Converter                       | 30   |

|                                                 | Page |

|-------------------------------------------------|------|

| 2.4.2 Light-Load Efficiency                     | 33   |

| 3. METHODS TO IMPROVE LIGHT-LOAD EFFICIENCY     | 35   |

| 3.1 Previous Methods                            | 35   |

| 3.1.1 PFM                                       | 35   |

| 3.1.2 Pulse Skipping Mode                       | 35   |

| 3.1.3 Burst Mode                                | 36   |

| 3.1.4 Mode-Hopping                              | 37   |

| 3.1.5 Gate Drive Technique                      | 38   |

| 3.1.6 Other Techniques                          | 38   |

| 3.2 Proposed Method                             | 40   |

| 3.3 Strengths and Weaknesses of Proposed Method | 43   |

| 4. SYSTEM ARCHITECTURE                          | 45   |

| 4.1 Specifications                              | 45   |

| 4.1.1 Choice of Switching Frequency             | 45   |

| 4.1.2 Output Ripple                             | 45   |

| 4.1.3 Load Regulation                           | 46   |

| 4.1.4 Specifications Summation                  | 47   |

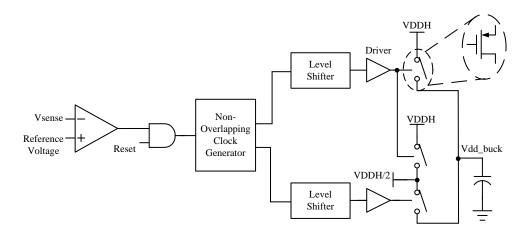

| 4.2 System Architecture                         | 48   |

| 4.3 PWM Mode and Control Method                 | 49   |

| 4.4 Current Sensing Technique                   | 57   |

| 4.5 Switched-Capacitor Converters               | 65   |

| 5. CIRCUIT IMPLEMENTAION                        | 67   |

| 5.1 Power Train                                 | 67   |

| 5.1.1 Power Stage Design                        | 68   |

| 5.1.2 Output Filter Design                      | 71   |

| 5.2 Voltage Control Loop                        | 72   |

|                                                  | Page |

|--------------------------------------------------|------|

| 5.2.1 Voltage Loop Macromodel                    | 74   |

| 5.2.2 Error Amplifier                            | 78   |

| 5.2.3 Ramp Generator                             | 80   |

| 5.2.4 Hysteresis Comparator                      | 82   |

| 5.2.5. Non-Overlapping Clock Generator           | 85   |

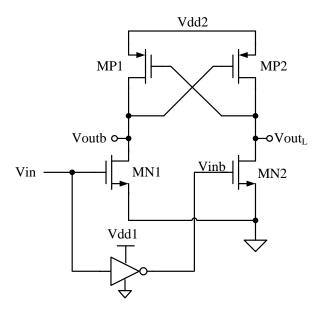

| 5.2.6 Level Shifter                              | 87   |

| 5.3 Current Sensing Loop                         | 88   |

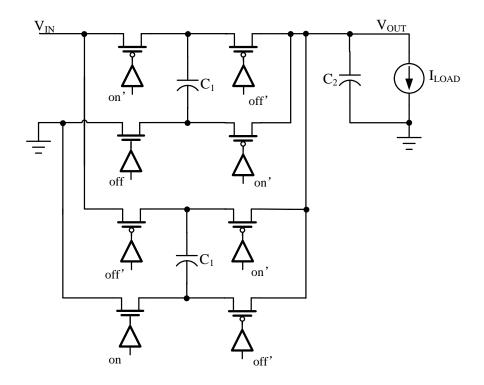

| 5.4 Switched-Capacitor Converter                 | 90   |

| 6. SIMULATION RESULTS AND COMPARISON             | 93   |

| 6.1 Simulation Results of Steady-State Condition | 94   |

| 6.1.1 I <sub>out</sub> =1mA                      | 95   |

| 6.1.2 I <sub>out</sub> =18mA                     | 97   |

| 6.1.3 I <sub>out</sub> =22.5mA                   | 98   |

| 6.1.4 I <sub>out</sub> =400mA                    | 99   |

| 6.1.3 Efficiency                                 | 100  |

| 6.2 Simulation Results of Transient Condition    | 102  |

| 6.3 Performance Summary                          | 103  |

| 6.4 Results Comparison and Discussion            | 104  |

| 7. TESTING RESULTS                               | 108  |

| 7.1 Testing Setup                                | 108  |

| 7.2 Preliminary Testing Results                  | 110  |

| 7.3 Problems Analysis                            | 111  |

| 8. CONCLUSIONS AND FUTURE WORK                   | 113  |

| 8.1 Conclusions                                  | 113  |

| 8.2 Future Work                                  | 113  |

|            | Page |

|------------|------|

| REFERENCES | 114  |

| VITA       | 126  |

# LIST OF FIGURES

|                                                                               | Page |

|-------------------------------------------------------------------------------|------|

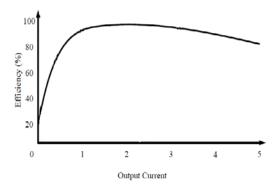

| Figure 1. Buck converter efficiency vs output current                         | 2    |

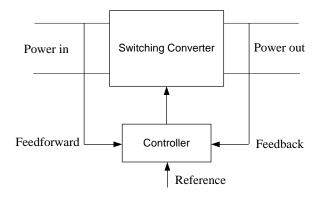

| Figure 2. Switching converter block diagram                                   | 5    |

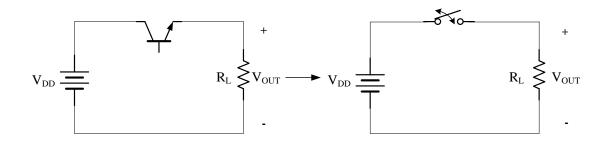

| Figure 3. A basic DC-DC switching converter                                   | 6    |

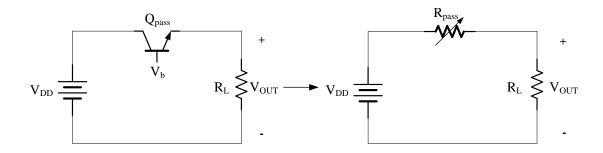

| Figure 4. A basic linear regulator                                            | 7    |

| Figure 5. Basic close loop linear regulator                                   | 8    |

| Figure 6. Typical switched-capacitor voltage divider (single phase)           | 10   |

| Figure 7. Simplified SC converter during phase φ <sub>1</sub> (mode 1)        | 10   |

| Figure 8. Simplified SC converter during phase φ <sub>2</sub> (mode 2)        | 11   |

| Figure 9. Flyback converter                                                   | 13   |

| Figure 10. Buck converter with ideal switch model                             | 14   |

| Figure 11. Voltage waveform at the switching node                             | 15   |

| Figure 12. Illustration of CCM and DCM                                        | 16   |

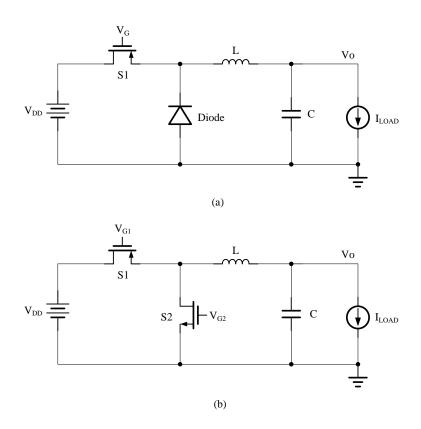

| Figure 13. (a). Asynchronous buck converter (b). Synchronous buck converter   | 17   |

| Figure 14. Inductor current goes to negative                                  | 18   |

| Figure 15. Inductor voltage $Vx$ and inductor current $i_L$ waveforms         | 19   |

| Figure 16. Gate control signals for synchronous buck converter                | 20   |

| Figure 17. Buck converter input current time domain and frequency domain      |      |

| waveform                                                                      | 21   |

| Figure 18. Buck converter with input filter (a). schematic (b). input current |      |

| waveform                                                                      | 21   |

|                                                                                     | Page |

|-------------------------------------------------------------------------------------|------|

| Figure 19. Boost converter topology                                                 | 22   |

| Figure 20. Buck converter schematic with ZVS turn-off                               | 25   |

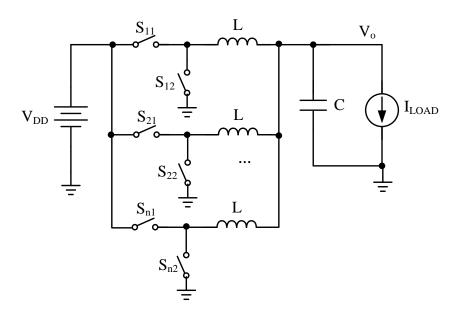

| Figure 21. Schematic of a synchronous n-phase buck converter                        | 28   |

| Figure 22. Schematic of single input multiple output buck converter                 | 29   |

| Figure 23. Circuit model for basic buck converter with parasitics                   | 30   |

| Figure 24. Output filter with parasitic resistance                                  | 33   |

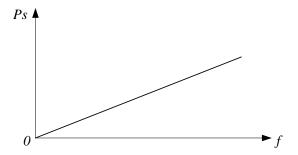

| Figure 25. Switching losses vs switching frequency                                  | 34   |

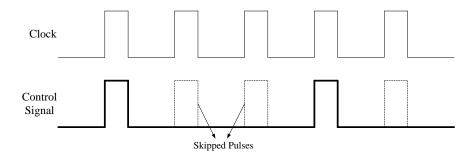

| Figure 26. Pulse skipping mode                                                      | 36   |

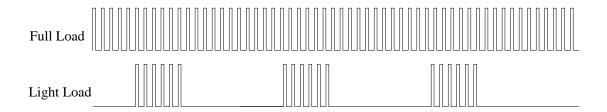

| Figure 27. Burst mode control signal at light load                                  | 37   |

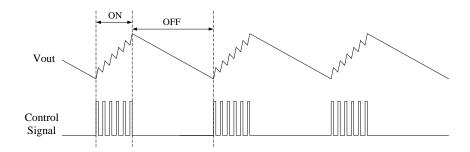

| Figure 28. Burst mode output signal                                                 | 37   |

| Figure 29. Buck converter with width controlling technique.                         | 39   |

| Figure 30. Basic idea of proposed dual-supply buck converter                        | 40   |

| Figure 31. Simplified proposed buck converter schematic under light-load condition: | :    |

| (a). $Vo < V_{DD}/2$ (b). $V_{DD}/2 < Vo < V_{DD}$                                  | 41   |

| Figure 32. Buck converter with (a) gate swing scaling technique (b) proposed dual-  |      |

| supply technique                                                                    | 44   |

| Figure 33. Load transient response                                                  | 47   |

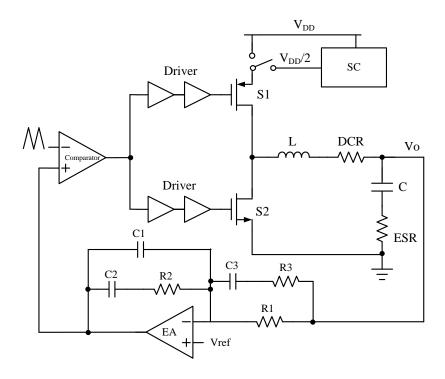

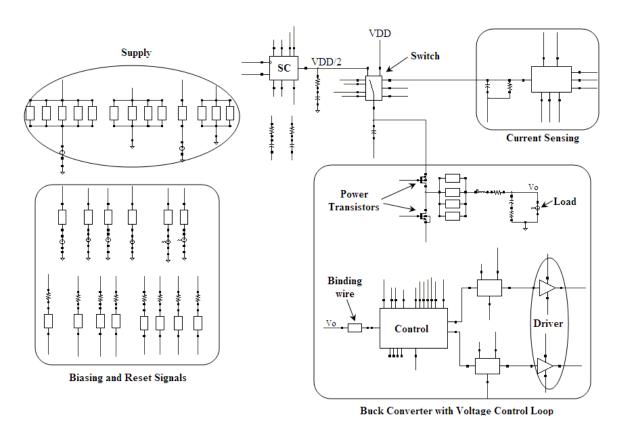

| Figure 34. System architecture of the proposed buck converter                       | 48   |

| Figure 35. Simplified buck converter schematic at (a). light load (b). medium and   |      |

| heavy load                                                                          | 48   |

| Figure 36. Voltage mode control diagram                                             | 51   |

|                                                                                  | Page |

|----------------------------------------------------------------------------------|------|

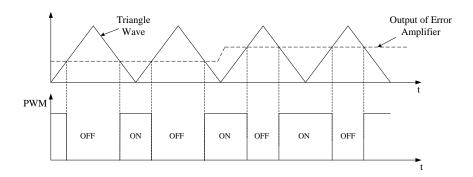

| Figure 37. PWM waveform                                                          | 51   |

| Figure 38. Output filter with parasitic resistance                               | 52   |

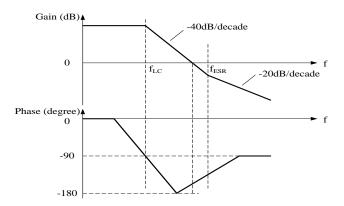

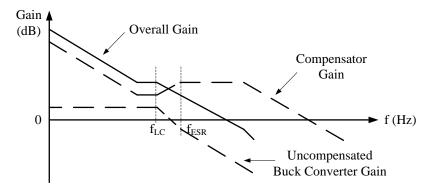

| Figure 39. Frequency response of the open loop buck converter                    | 53   |

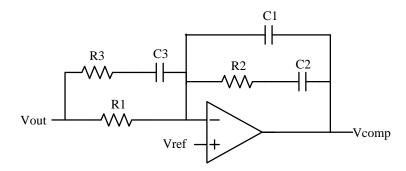

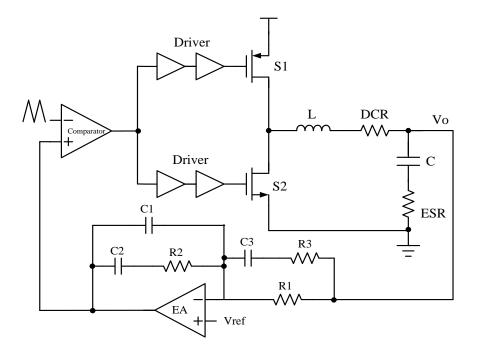

| Figure 40. Type III compensation network                                         | 54   |

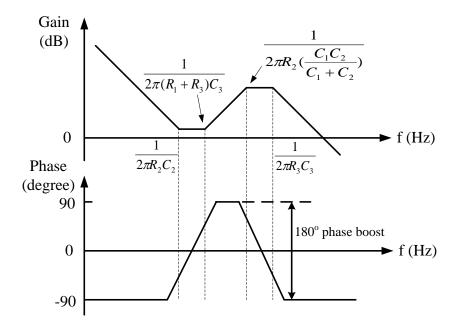

| Figure 41. Frequency response of type III compensation network                   | 55   |

| Figure 42 Close loop buck converter                                              | 56   |

| Figure 43. Frequency response after compensation                                 | 56   |

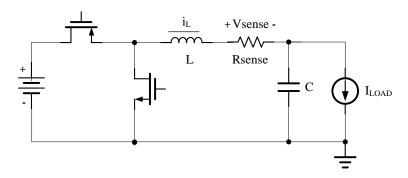

| Figure 44. Current sensing with series sense resistor                            | 57   |

| Figure 45. Current sensing with R <sub>DS</sub> of MOSFET                        | 58   |

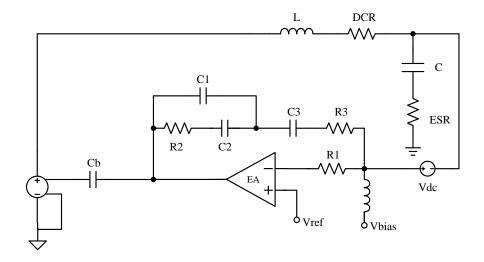

| Figure 46. Current sensing with filter                                           | 59   |

| Figure 47. Filter based average current sensing                                  | 60   |

| Figure 48. SENSEFET                                                              | 62   |

| Figure 49. A more accurate circuit using SENSEFET technology                     | 63   |

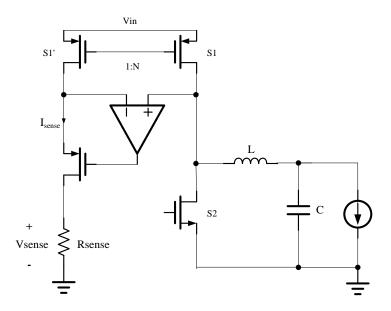

| Figure 50. Current sensing circuit used in this project                          | 64   |

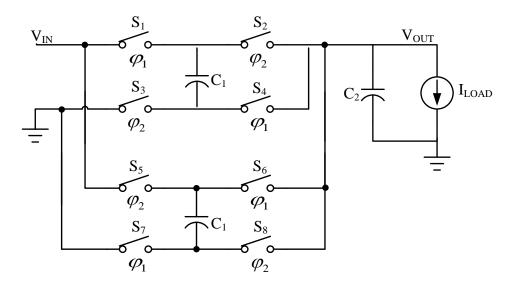

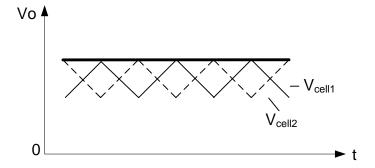

| Figure 51. Typical switched-capacitor voltage divider with interleaved operation | 65   |

| Figure 52. Output ripple cancellation with interleaved operation                 | 66   |

| Figure 53. Power chain                                                           | 68   |

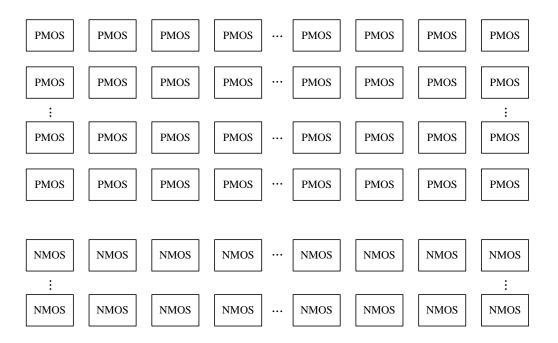

| Figure 54. Layout floorplan of power transistors                                 | 70   |

| Figure 55. Buck converter with voltage control loop                              | 73   |

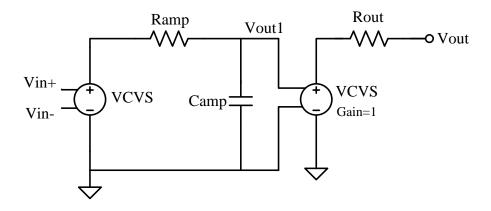

| Figure 56. Buck converter voltage loop macromodel                                | 75   |

| Figure 57. Opamp macromodel with one dominant pole                               | 75   |

|                                                                                     | Page |

|-------------------------------------------------------------------------------------|------|

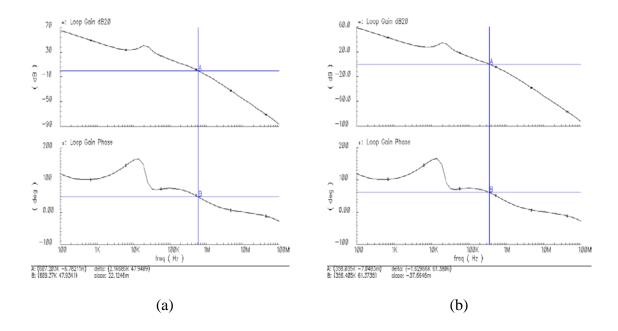

| Figure 58. AC response of the voltage control loop                                  | 76   |

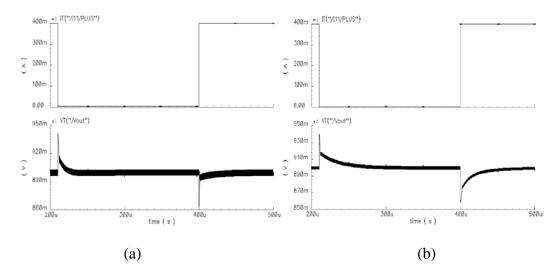

| Figure 59. Transient response of voltage control loop                               | 77   |

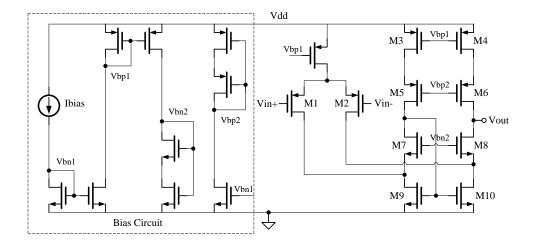

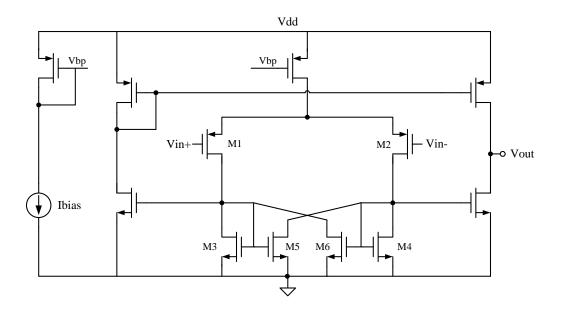

| Figure 60. Error amplifier                                                          | 79   |

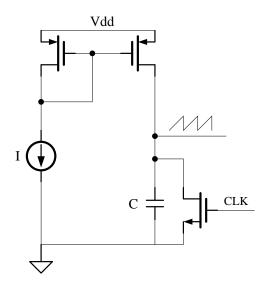

| Figure 61. Saw tooth wave generator                                                 | 80   |

| Figure 62. Triangle wave generator                                                  | 82   |

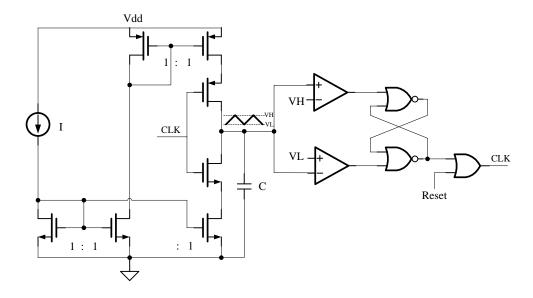

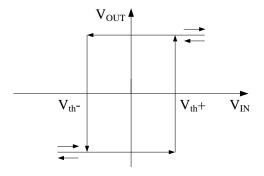

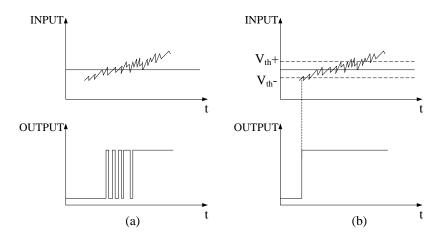

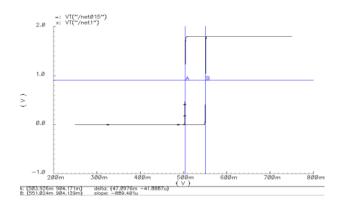

| Figure 63. Comparator transfer function curve with hysteresis                       | 83   |

| Figure 64. Comparator response to a noisy input (a).without hysteresis (b). with    |      |

| hysteresis                                                                          | 83   |

| Figure 65. Hysteresis comparator                                                    | 84   |

| Figure 66. Simulated comparator hysteresis window                                   | 85   |

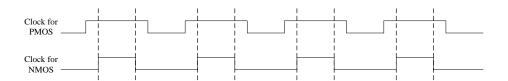

| Figure 67. Clocks for power switches                                                | 85   |

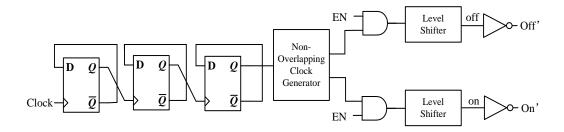

| Figure 68. Non-overlapping clock generator                                          | 86   |

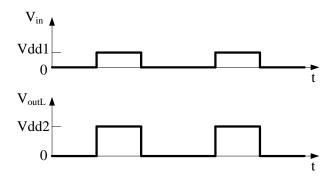

| Figure 69. Waveforms of input voltage and output voltage                            | 87   |

| Figure 70. Level shifter                                                            | 88   |

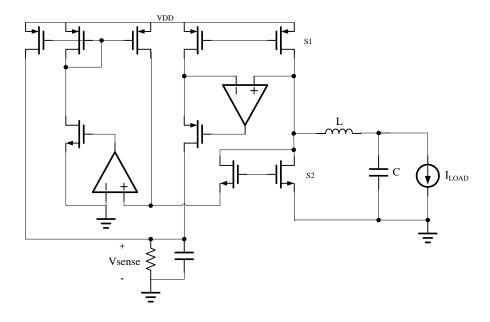

| Figure 71. Current sensing loop                                                     | 89   |

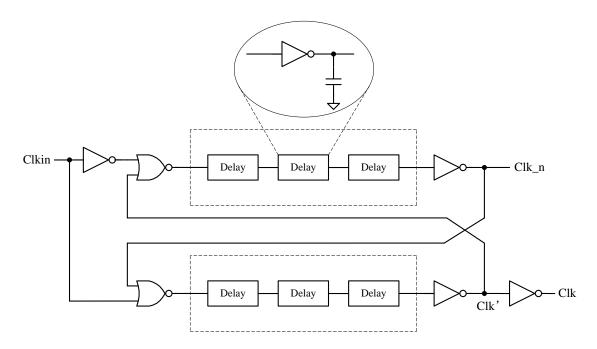

| Figure 72. Switching capacitor converter schematic                                  | 91   |

| Figure 73. Clock signals generator for switching capacitor converter                | 92   |

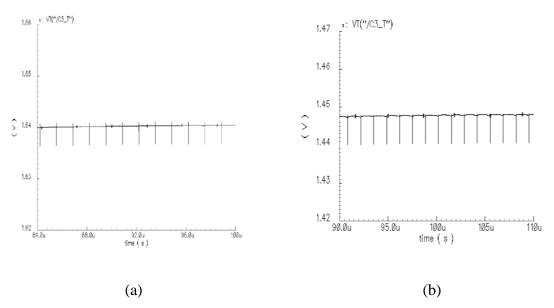

| Figure 74. SC converter output voltage waveforms (a). load current is 1mA (b). load | ad   |

| current is 20mA                                                                     | 92   |

| Figure 75. Load transient simulation setup in cadence                               | 93   |

| Figure 76. Setup change from load transient simulation to steady-state simulation   | 94   |

| Page                                                                            |

|---------------------------------------------------------------------------------|

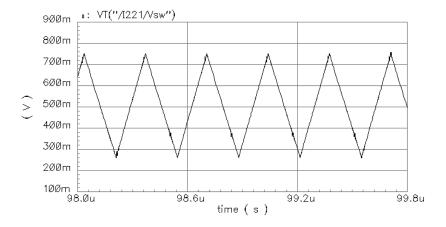

| Figure 77. Triangle wave generator output                                       |

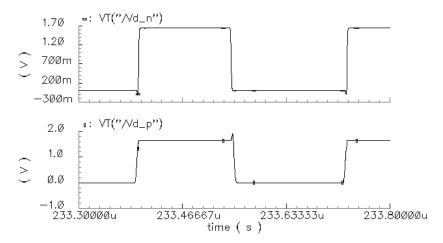

| Figure 78. PWM signals (top: for NMOS; bottom: for PMOS)                        |

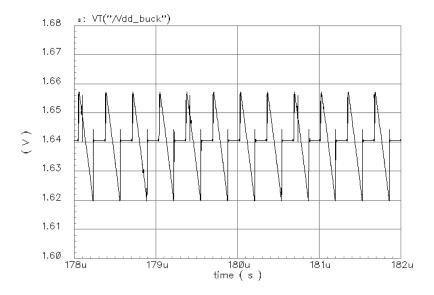

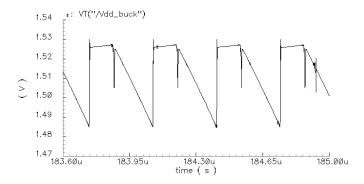

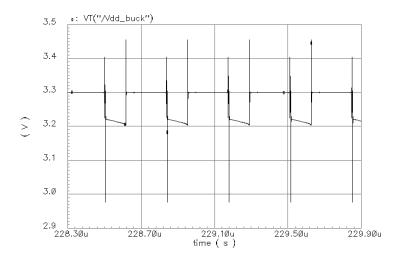

| Figure 79. Buck converter supply voltage waveform when load current is 1mA96    |

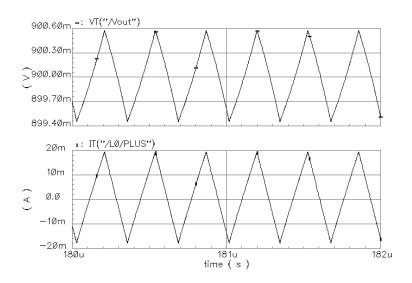

| Figure 80. Output voltage (top waveform) and inductor current (bottom waveform) |

| when load current is 1mA96                                                      |

| Figure 81. Buck converter supply voltage waveform when load current is 18mA97   |

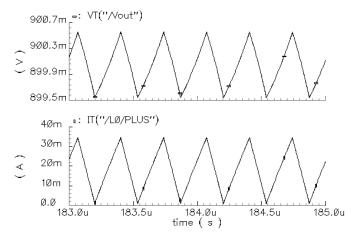

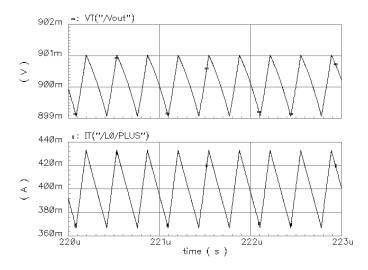

| Figure 82. Output voltage (top waveform) and inductor current (bottom waveform) |

| when load current is 18mA97                                                     |

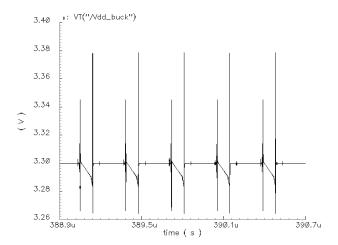

| Figure 83. Buck converter supply voltage waveform when load current is 22.5mA98 |

| Figure 84. Output voltage (top waveform) and inductor current (bottom waveform) |

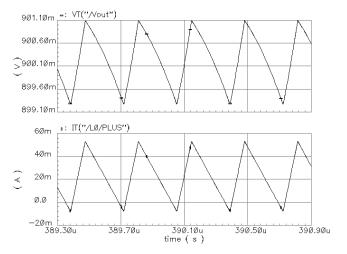

| when load current is 22.5mA98                                                   |

| Figure 85. Buck converter supply voltage waveform when load current is 400mA99  |

| Figure 86. Output voltage (top waveform) and inductor current (bottom waveform) |

| when load current is 400mA99                                                    |

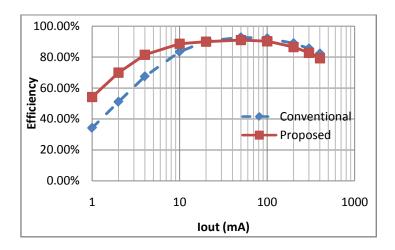

| Figure 87. Efficiency vs output current                                         |

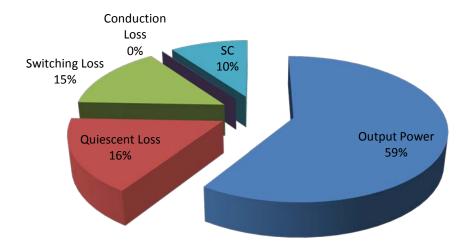

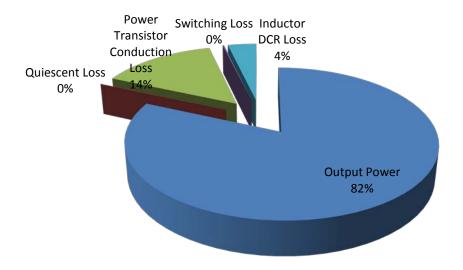

| Figure 88. Power consumption distribution chart (load current is 1mA)101        |

| Figure 89. Power consumption distribution chart (load current is 400mA)102      |

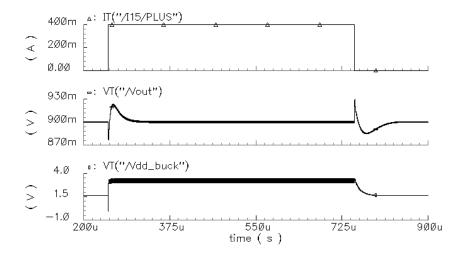

| Figure 90. Transient response of the proposed buck converter                    |

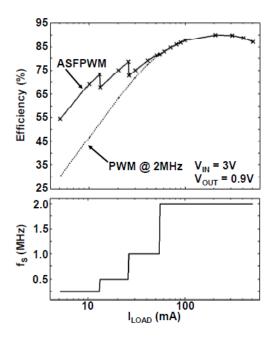

| Figure 91. Efficiency curve of [51]                                             |

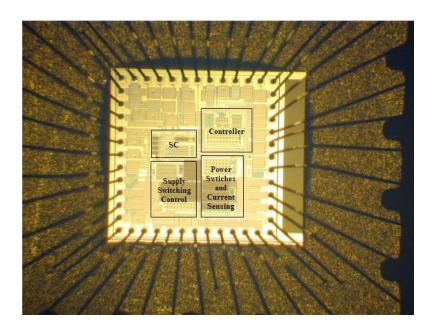

| Figure 92. Chip micrograph of buck converter                                    |

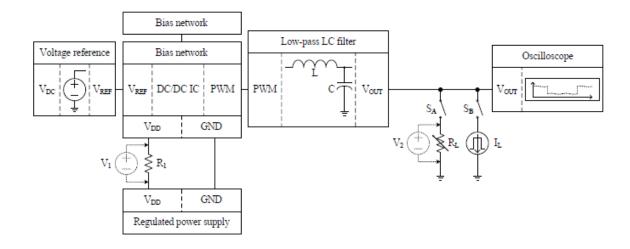

| Figure 93. Testing setup of the buck converter                                  |

|                                                                          | Page |

|--------------------------------------------------------------------------|------|

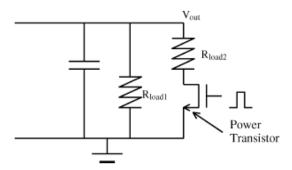

| Figure 94. Load response testing setup                                   | 109  |

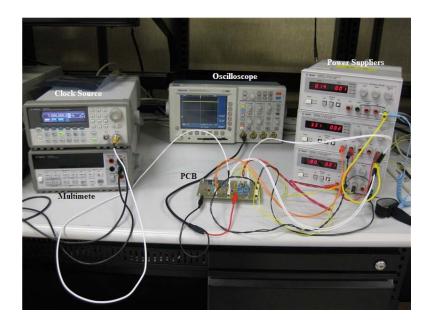

| Figure 95. Lab measurement picture                                       | 110  |

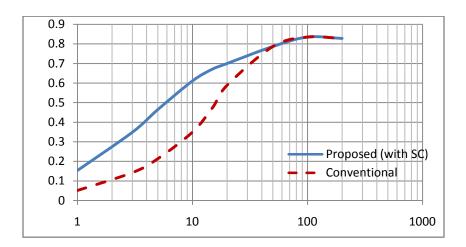

| Figure 96. Tested efficiency of both conventional and proposed converter | 111  |

# LIST OF TABLES

|                                                                                 | Page |

|---------------------------------------------------------------------------------|------|

| Table 1. Comparison between switching converter, linear regulator and switched- |      |

| capacitor converter                                                             | 12   |

| Table 2. Specifications of the proposed buck converter                          | 47   |

| Table 3. Transistor sizes of the buck converter power stage                     | 71   |

| Table 4. Output filter size                                                     | 72   |

| Table 5. Compensation components value                                          | 74   |

| Table 6. AC performance of the voltage control loop                             | 76   |

| Table 7. Load transient of conventional converter (3.3V)                        | 77   |

| Table 8. Load transient of proposed converter (1.65V)                           | 77   |

| Table 9. Performance summary of error amplifier                                 | 79   |

| Table 10. Power consumption summary (load current is 1mA)                       | 101  |

| Table 11. Power consumption summary (load current is 400mA)                     | 102  |

| Table 12. Transient performance summary of the proposed buck converter          | 103  |

| Table 13. Performance summary                                                   | 104  |

| Table 14. Comparison with previous work                                         | 105  |

| Table 15. Comparison with similar industry products                             | 107  |

### 1. INTRODUCTION

### 1.1 Research Motivation

Over the years as the portable device industry developing, different requirements are brought out such as increased battery lifetime, small size, cheap cost, and brighter, full-color displays. An ever increasing demand from power systems has placed power consumption at the primary concern. To keep up with these demands, engineers have dedicated tremendous work towards developing efficient conversion techniques. High efficiency conversion of power supplies helps to reduce power consumption for battery-operated applications, and increases the devices operating time. In addition, if the power devices dissipate a fairly large amount of power, they have to be adequately cooled by mounted on heat sinks. Thus the heat can be transferred to the surrounding air. Heat sinks and provision for cooling make the regulator bulky and large. Reduced power dissipation in the power supply will reduce the need for heat sinks and relax thermal design considerations. These benefits have resulted in the popularity of switching converters which have fairly high efficiency and compact size.

Buck converter or step-down converter is the most widely used switching converter in powering up the portable applications. The efficiency of buck converter is expressed by [1]-[3]:

$$\eta = \frac{P_{out}}{P_{in}} = \frac{V_{out} I_{out}}{V_{in} I_{in}}$$

(1.1)

This thesis follows the style of IEEE Journal of Solid State Circuits.

where  $P_{out}$  is the power output to the load,  $V_{out}$  is the output voltage,  $I_{out}$  is the load current,  $P_{in}$  is the total power supplied by the input voltage source,  $V_{in}$  is the input voltage,  $I_{in}$  is the current drawn from the supply.

Buck converters provide very high efficiency, approaching 100% as the components are made more ideal. Considering the parasitic, the efficiency of buck converters with practical components can still achieve above 80% in most of the cases. However, the efficiency is not always maximized, but varies according to the size of load. The typical efficiency curve for a conventional buck converter, which is optimized for a medium load range, is shown in Figure 1 [4]. It shows that the efficiency decreases as load becomes lighter or heavier, and especially at light load (where the load current is small), the efficiency drops to extremely low very quickly. Since the portable devices are operating in low-power standby mode or sleep mode for a majority of the time when they are on, which is in the light load region, the poor light-load efficiency can severely limit the battery lifetime. Hence improving light-load efficiency is critical for portable devices. The main objective of this work is to propose a new method to improve light-load efficiency.

Figure 1. Buck converter efficiency vs output current

# 1.2 Thesis Organization

This thesis consists of eight sections.

Section 1 presents the motivation of this project and sets objectives for the research contribution.

Section 2 introduces the fundamentals of switching converters, especially buck converter and boost converter, addresses the open problems in buck converters, and analyzes the power losses.

Section 3 overviews the light-load efficiency improving techniques existing in literature and industry, proposes a new method, and demonstrates the strengths and weaknesses of the proposed method.

Section 4 implements the proposed buck converter in TSMC 0.18um CMOS process. System architecture and system level design are described.

Section 5 covers the transistor level implementation of each building block.

Section 6 verifies the proposed idea with simulation results, and compares them with previous work.

Section 7 reveals the preliminary lab measurement results, and analyses the existing problems and possible reasons.

Section 8 summarizes this research and discusses the future work.

#### 2. FUNDAMENTALS

# 2.1 Introduction of Switching Converters

A switching converter or switch mode power converter is a power electronic system which converts one level of electrical energy into another level of electrical energy at the load, by switching action [1]. Switching converters have been in existence since the 1950s, and then became a popular choice in power supplies in the 1970s due to the emergence of modern power semiconductor devices (e.g., power MOSFET, GTR). Nowadays, the applications of switching converters are expanding quickly. The power levels encountered range from milliwatts such as in battery-operated portable equipment, to megawatts such as in variable-speed motor drives.

In general, a switching converter, as illustrated in Figure 2, contains power input and output ports, and a control block to regulate output voltage in the presence of varied input voltage and output current [2]. Switching converters can be classified into four categories according to the input and output voltage forms:

- 1) A DC-DC converter converts a DC input voltage to a regulated output voltage with a larger or smaller magnitude, and opposite polarity is possible.

- A DC-AC inverter converts DC input voltage to AC output voltage with controllable magnitude and frequency.

- 3) An AC-DC rectifier produces a DC output from an AC input.

- An AC-AC cycloconverter can be used to change the level and/or frequency of an AC signal.

Figure 2. Switching converter block diagram [2]

## 2.2 DC-DC Switching Converters

### 2.2.1 Introduction

DC-DC switching converters are very popular used as power supplies in portable electronic devices such as cellular phones, digital cameras, laptop computers etc. Often in these electronic devices, several sub-circuits with different voltage and current requirements exist. Instead of using multiple batteries, DC-DC converters are able to generate different supplies for each sub-circuit with its required voltages, currents and power ratings from a single battery source, therefore saving a lot of space. Additionally, the battery voltage drops with time. DC-DC converters offer a method to generate regulated output voltage from an unregulated DC voltage source [3], [5].

In a DC-DC switching converter, the transistor operates as an electronic switch by being completely on or completely off. In Figure 3, assuming that the switch is ideal, then the output voltage is the same as input when the switch is on, and the output is zero when the switch is off. When the switch is on, there is no voltage drop across it; when the switch is off, there is no current across it. So the power dissipated on the switch is zero.

In other words, all power is absorbed by the load, and the power efficiency is 100%. In practical circuit, there will be some losses, but the efficiency is still high. Drawbacks of switching converters include complexity, noise and electromagnetic interference (EMI).

Figure 3. A basic DC-DC switching converter

Before discussing DC-DC switching converters, it is useful to understand the motivation for an alternative to linear DC-DC converters (or linear regulators) and switched-capacitor converters.

## 2.2.2 Comparison with Linear Regulators and Switched-Capacitor Converters

## 2.2.2.1 Linear Regulators

Although there is trend that linear regulations are replacing with switching converters, linear regulators remain a basic building block used in almost every power supply design. It offers a simple, low cost solution for delivering stable, low noise DC voltage to power analog and digital circuits. Additionally, it is available in fixed and adjustable output voltage versions, and also positive and negative voltage output versions to meet different application requirement.

The linear regulator, conceptually illustrated in Figure 4 [6], operates based on active devices, such as bipolar junction transistor (BJT) or filed effect transistor (FET), working in their linear region. The active device acts as a viable resistor to maintain constant output voltage by adjusting a voltage divider network.

Figure 4. A basic linear regulator

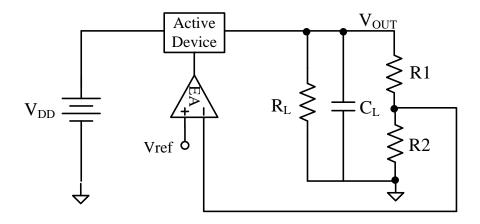

All types of linear regulators use the similar control technique to regulator the output voltage. As shown in Figure 5, the feedback loop combines a reference voltage, an error amplifier and an active device. The output voltage  $V_{OUT}$  is monitored through a resistor divider which is consisted of R1 and R2. By comparing the sensed voltage with a reference voltage to adjust the input to the active device, sufficient load current is provided to maintain constant output voltage.  $C_L$  is an external capacitor used for compensation, and  $R_L$  is the load resistor.

Figure 5. Basic close loop linear regulator

Linear regulators can be grouped into three types according to their different dropout voltages: standard regulators, low-dropout (LDO) regulators, and Quasi-LDO regulators [7]-[8]. Standard regulators use the NPN Darlington configuration for the active device, and have the highest dropout voltage. LDO regulators use one PNP transistor for the active device, and have the lowest dropout voltage. Quasi-LDO regulators use an NPN transistor and a PNP transistor as the active device, and their dropout voltages are between standard and LDOs. Lower dropout voltage usually means higher efficiency, because less power is dissipated internal. From application point of view, the standard regulator is usually best for AC-powered applications where dropout voltage is not critical compared with voltage across the regulator, and the low cost and high load current make it the ideal choice. The LDO regulator is best suited for battery-operated applications where the lower dropout voltage makes it more efficient [7].

The good thing about linear regulator is that it can provide a very low noise output voltage, which is suitable for powering noise sensitive low power analog and radio frequency circuits. But linear regulators can only output lower voltage than input. Also

they are less efficient when the voltage conversion ratio is large because the highest efficiency  $\eta_{max}$  attainable with an ideal linear regulator is given by:

$$\eta_{max} = \frac{P_{OUT}}{P_{IN}} = \frac{V_{OUT} \cdot I_{OUT}}{V_{DD} \cdot I_{IN}} = \frac{V_{OUT}}{V_{DD}}$$

(2.1)

where  $P_{IN}$  is the input power consumption,  $P_{OUT}$  is the output power consumption,  $V_{DD}$  is the regulator input voltage,  $I_{IN}$  is the input current,  $V_{OUT}$  is the regulator output voltage, and  $I_{OUT}$  is the output current, which is equal to input current  $I_{IN}$ .

While a switching converter can easily provide more than 30A of current at voltages as low as 3V, for the same voltage and current, a linear regulator would be very bulky and heavy due to the heat sinks it needed. Thus linear regulators are not normally used for large-drop high-current applications. Current trends of linear regulators include lower dropout voltages, lower operating voltages, smaller packages, and thermally efficient packages [8].

## 2.2.2.2 Switched-Capacitor Converter

A switched-capacitor converter, also called charge pump, is a kind of DC-DC converters. It uses a combination of switches and capacitors to produce an output voltage that either higher or lower than the input voltage as well as polarity reversal. SC converters are capable of high efficiencies, sometimes as high as 90% ~ 95%. They are useful for small output power applications that do not require isolation between input and output, such as LCD or white LED drivers, supplying non-volatile memory circuits (flash and electrically erasable programmable read only memories) and so on. The main advantage of the SC converters is the absence of bulk inductors and transformers, making possible a complete integration of the switching converter [1].

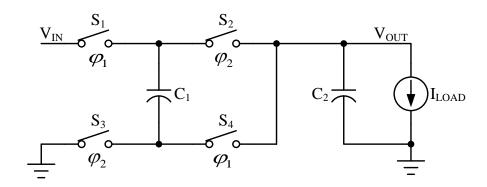

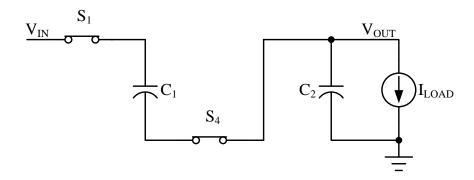

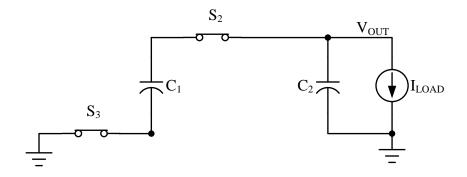

The operation of SC converter relies on periodically charging or discharging capacitors. A typical SC converter with ideal switches is shown in Figure 6 [9]. It consists of four clock-controlled switches  $S_1$  to  $S_4$ , two capacitors  $C_1$  and  $C_2$ , an input voltage source  $V_{IN}$ , and the load. During phase  $\phi_1$ , switches  $S_1$  and  $S_4$  are turned on (mode 1) out of phase with S2 and S3 for half of the period (50% duty cycle), as illustrated in Figure 7. During phase  $\phi_2$ , switches  $S_2$  and  $S_3$  are turned on (mode 2) out of phase with  $S_1$  and  $S_4$  for the other half of period, as illustrated in Figure 8. The output voltage  $V_{OUT}$  is  $V_{IN}/2$  when capacitor  $C_1$  is equal to  $C_2$ .

Figure 6. Typical switched-capacitor voltage divider (single phase)

Figure 7. Simplified SC converter during phase  $\varphi_1$  (mode 1)

Figure 8. Simplified SC converter during phase  $\varphi_2$  (mode 2)

# 2.2.2.3 Comparison

The comparison between DC-DC switching converter, linear regulator and switched-capacitor converter is summarized in Table 1. The three types of converters all have their own advantage and disadvantage. The choice between the three types is depending on applications.

Table 1. Comparison between switching converter, linear regulator and switchedcapacitor converter

|                       | Switching converter                                     | Linear regulator                   | Switched-capacitor converter                 |

|-----------------------|---------------------------------------------------------|------------------------------------|----------------------------------------------|

| Function              | Step up/down, even reversed polarity                    | Step down                          | Step up/down, even reversed polarity         |

| Voltage<br>Regulation | Good                                                    | Good                               | Poor                                         |

| Efficiency            | High                                                    | V <sub>OUT</sub> /Vin; usually low | Low                                          |

| Current Rating        | High                                                    | Low                                | Medium                                       |

| Complexity            | High, requiring inductor, capacitor and sometimes diode | Low                                | High, requiring more switches and capacitors |

| Size                  | Large                                                   | Small                              | Medium                                       |

| Ripple/Noise          | High; ripple at switching frequency                     | Low; no ripple, low noise          | High                                         |

| Total Cost            | High; mainly due to off-chip components                 | Low                                | Medium                                       |

## 2.2 Introduction of Buck and Boost Converters

DC-DC switching converter can be divided into two types, the non-isolated one and isolated one.

Non-isolated converters are simplest, including Buck converter, Boost converter, Buck-Boost converter, Cuk converter, Sepic converter, Zeta converter and so on. They have similar topologies which are consisted of two switches, inductors, capacitors and the load. By connecting these components in different ways, different voltage conversion functions can be obtained. Buck converter converts an input voltage to a lower output voltage. Boost converter converters an input voltage to a higher output voltage. Buck-

Boost converter, Cuk converter, Sepic converter and Zeta converter are all able to provide an output voltage with both higher and lower value than the input voltage, which combine the functions of buck converter and boost converter in one circuit.

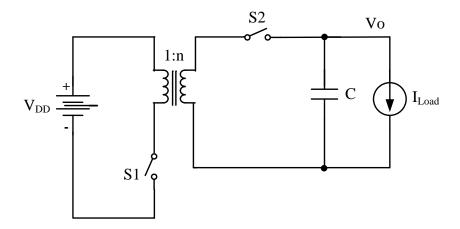

Isolated converters are bulky due to the use of transformers, but in some cases that the primary power supply operates at a relatively high voltage and/or is very noise, isolation of the load from the input supply is necessary to maintain reliable operation of the load. Common isolated converters are Flyback converter, Forward converter, Pushpull converter, Full-bridge converter, Half-bridge converter and so on. The Flyback converter is based on the Buck-Boost converter, and Forward converter is based on the Buck converter. Their conversion ratios are n times larger than the nonisolated versions, where n is the transformer turns ratio. Push-pull converter, Full-bridge converter and Half-bridge converter are converters with conversion rations of nD (for Push-pull converter and Full-bridge converter) or 0.5nD (for Half-bridge converter), where n is still the transformer turns ratio, and D is duty cycle. Figure 9 shows an example of Flyback converter with ideal switch.

Figure 9. Flyback converter

Among these varies types, Buck converter and Boost converter are the two most widely used DC-DC converters. Their basic topology and working principles will be introduced in this section.

### 2.2.1 Basics of Buck Converter

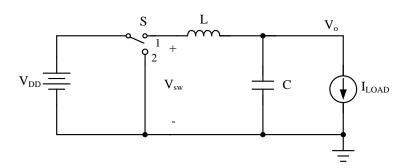

Buck converter is a step-down DC-DC switching converter, whose basic functionality is to convert an input DC voltage to a lower DC output voltage. As shown in Figure 10, it is consisted of switch S, inductor L, capacitor C, input DC voltage source  $V_{DD}$  and resistive load. The switch alternates periodically between connecting to node 1 and node 2, resulting in a square wave  $V_{sw}$ , as shown in Figure 11.  $V_{sw}$  equals to  $V_{DD}$  when the switch S is connected to voltage source, and drops to zero when S is connected to ground. The inductor and capacitor forms a low pass filter to obtain the DC component of Vx. The output voltage of buck converter  $V_o$  is expressed as:

$$V_o = D \cdot V_{DD} \tag{2.2}$$

where D is called duty cycle, and represents the fraction of time that the switch connects to source voltage. The switching frequency  $f_s$ , which equals to the inverse of the switching period  $T_s$ , generally lies in several kilo Hz to several Mega Hz.

Figure 10. Buck converter with ideal switch model

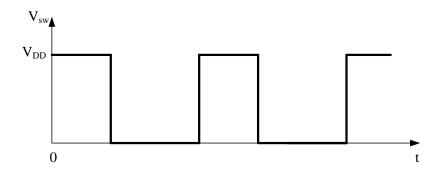

Figure 11. Voltage waveform at the switching node

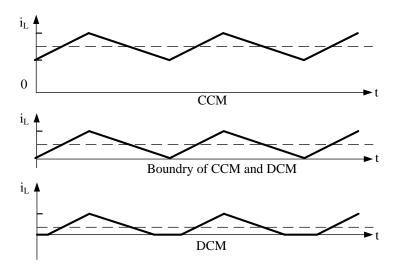

The operation of buck converters can be classified according to the continuity of the current flowing through the output inductor. If the inductor current flow is continuous of charge and discharge during a switching period, it is called Continuous Conduction Mode (CCM) operation. If the inductor current has an interval of time staying at zero during a switching period, it is called Discontinuous Conduction Mode (DCM) operation. CCM and DCM operation waveforms of inductor current are illustrated in Figure 12. The zero inductor current in DCM operation usually results from the single direction current flow characteristic of switch.

Figure 12. Illustration of CCM and DCM

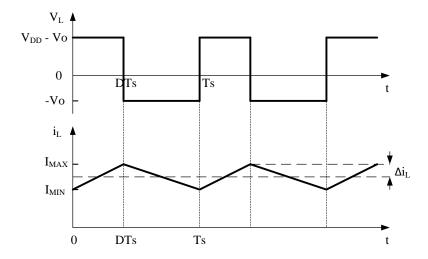

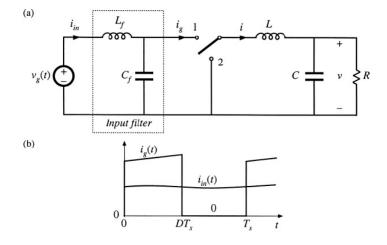

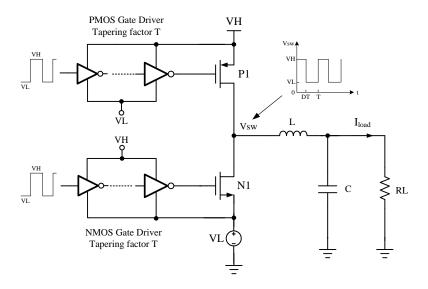

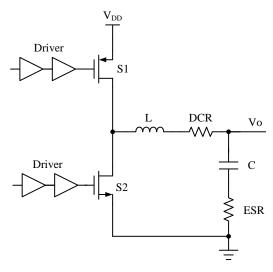

Based on different implementations of power switches in the power stage, the buck converter is classified as asynchronous and synchronous structures (Figure 13(a) and (b)). As shown in Figure 13(a), asynchronous buck converter is comprised of a PMOS transistor, a diode, an inductor and a capacitor. The diode behaves as a unidirectional switch, as the current of the diode can only flow from anode to cathode. The only difference of synchronous buck converter is the replacement of diode with MOSFET. The second MOSFET is known as a synchronous rectifier, also called a low-side MOSFET. In Figure 13(b), when S2 is on and S1 is off, current flows upward out of the drain of S2. The advantage of this configuration is that the rectifier has a much smaller voltage drop across it compared to a diode, resulting in higher efficiency. The mathematical comparison of the power loss on a diode and a MOSFET is given by

$$P_{MOS} = I_{out}^2 \cdot R_{ds} \cdot (1 - D) \tag{2.3}$$

$$P_{Diode} = I_{out} \cdot V_{Fwd} \cdot (1 - D) \tag{2.4}$$

where  $I_{out}$  is average output current,  $R_{ds}$  is the MOSFET on-resistance,  $V_{Fwd}$  is the diode forward voltage drop. Since  $V_{Fwd}$  is normally around 0.7V, and  $R_{ds}$  can be as small as several hundred milliohms, the power loss difference in low power applications can be very large. Thus, in this project, synchronous buck converter scheme is preferred.

Figure 13. (a). Asynchronous buck converter (b). Synchronous buck converter

Synchronous buck converter always operates in the CCM because the low-side MOSFET is a bi-direction switch, which allows inductor current going to negative, as shown in Figure 14. The following analysis is based on CCM operation.

Figure 14. Inductor current goes to negative

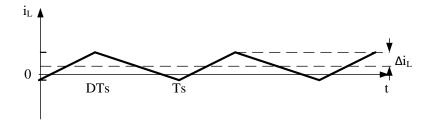

Assume the circuit is operating in CCM, steady state, and the components are ideal. For steady state operation, the analysis is based on the following two principles: the inductor current change over one period much be zero, and the capacitor voltage change over one period much be zero. The waveforms of voltage across inductor  $V_L$  and inductor current  $i_L$  are shown in Figure 15, where  $i_L$  can be obtained from:

$$V_L(t) = L\frac{di_L(t)}{dt} \tag{2.5}$$

Thus,

$$i_{L}(t) = \int \frac{V_{L}(t)}{L} dt = \begin{cases} \frac{V_{DD} - V_{o}}{L} \cdot t & 0 < t < DT_{s} \\ \frac{V_{DD} - V_{o}}{L} \cdot DT_{s} - \frac{V_{o}}{L} \cdot (t - DT_{s}) & DT_{s} < t < T_{s} \end{cases}$$

(2.6)

Figure 15. Inductor voltage Vx and inductor current  $i_L$  waveforms

The inductor peak-to-average current ripple  $\Delta i_L$  is given by:

$$\Delta i_L = \frac{I_{MAX} - I_{MIN}}{2} = \frac{V_o}{2L} (1 - D) T_s = \frac{V_{DD} - V_o}{2L f_s} \cdot D$$

(2.7)

where  $I_{MAX}$  is the maximum inductor current, and  $I_{MIN}$  is the minimum inductor current.

It is undesirable to allow  $\Delta i_L$  becoming too large. Doing so would increase the peak currents of the inductor and of the switching device, and would increase their size and cost.

In practice, the output voltage ripple cannot be kept perfectly constant with a finite capacitance. The variation in output voltage or output voltage ripple  $\Delta V_o$  is given by:

$$\Delta V_o = \frac{q}{2C} = \frac{\frac{1}{2}\Delta i_L \frac{T_S}{2}}{2C} = \frac{\Delta i_L}{8Cf_S} = \frac{(1-D)D}{16LCf_S^2} \cdot V_{DD}$$

(2.8)

where q is the charge on output capacitor.

The two MOSFETs must not be on at the same time to prevent a short circuit across the source, so a "dead time" is built into the switching control-one MOSFET is turned off before the other is turned on. The waveforms of gate control signals are illustrated in Figure 16.

Figure 16. Gate control signals for synchronous buck converter

Discontinuous mode operation is not as frequently used as continuous mode. This is because, in discontinuous mode, the circuit model becomes non-linear, increasing control complexity. It is desirable to design the buck converter to operate either in continuous mode or discontinuous mode, avoiding the change from one mode of operation into the other during normal operation, which may lead to serious stability problems [1]. But since DCM can obtain better circuit efficiency than CCM in light load, some designs employ both CCM and DCM operation. Detailed discussion will be provided in Section 3.

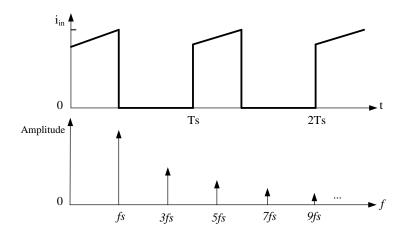

As mentioned in Section 2.1, Electronic magnetic interference (EMI) is one of the main drawbacks of the switching converter. For buck converter, EMI is caused by the pulsating current injected into the power source, as shown in Figure 17, which contains harmonics at multiples of the switching frequency. The large high-frequency current harmonics can interfere with television and radio reception, and can disrupt the operation of nearby electronic equipment. To limit EMI, an input filter can be added to attenuate

the current harmonics produced by the converter. The schematic with input filter and input current waveform is shown in Figure 18 [2].

Figure 17. Buck converter input current time domain and frequency domain waveform

Figure 18. Buck converter with input filter (a). schematic (b). input current waveform

# 2.2.2 Basics of Boost Converter

The boost converter, also known as step-up converter, is capable of providing an output voltage which is larger than the input voltage. The basic Boost converters with

ideal switch and with power MOSFET and diode as the switching components are shown in Figure 19. The key idea behind achieving a higher output voltage lies in the inductor's ability to resist changes in current. When being charged, the inductor stores energy, and when being discharged, the inductor acts as an energy source (somewhat likes a battery). The output capacitor is very large to keep the output voltage constant during steady-state.

Figure 19. Boost converter topology

(a). with ideal switch (b). with realistic components: power MOSFET and diode

Boost converter also has the synchronous topology which replaces the diode in Figure 19(b) with another power MOSFET. Synchronous boost converter is popular for high efficiency applications [10]-[12].

Similar to Buck converter, the operation of boost converter can be divided into continuous current mode and discontinuous current mode. In CCM, under steady-state condition, the input voltage  $V_{DD}$ , output voltage  $V_o$  and duty cycle of the switches D have the following relationship [1]-[2], [6]:

$$V_o = \frac{V_{DD}}{1 - D} \tag{2.9}$$

This equation shows that if the switch is always open, which means D is zero, the output will be same as input. As the duty cycle approaches one, the output goes to infinity. However, this equation is based on the assumption of ideal switch. Practical components will have losses and prevent such an occurrence.

The inductor current ripple  $\Delta i_L$  is given by:

$$\Delta i_L = \frac{I_{MAX} - I_{MIN}}{2} = \frac{\frac{V_{DD}}{L} \cdot DT_s}{2} = \frac{V_{DD}}{2Lf_s} \cdot D \tag{2.10}$$

where  $I_{MAX}$  is the maximum inductor current, and  $I_{MIN}$  is the minimum inductor current. L is the inductance of input inductor, and  $f_s$  is the switching frequency. This equation can be used to choose inductance when the spec for  $\Delta i_L$  is provided.

The voltage ripple  $\Delta V_o$  is given by:

$$\Delta V_o = \frac{\frac{I_o}{C} \cdot DT_s}{2} = \frac{\frac{V_o}{R} \cdot DT_s}{2C} = \frac{D}{2RCf_s} \cdot V_o$$

(2.11)

where  $I_o$  is the output current, R is the load resistance, and C is the output capacitance. This equation can be used to choose output capacitance when the spec for  $\Delta V_o$  is provided.

Boost converter will also operate in discontinuous current mode. In some cases, this mode is desirable for control reasons in the case of a regulated output. In DCM, the input and output relationship is given by:

$$V_o = \frac{1 + \sqrt{1 + \frac{4D_1^2}{K}}}{2} \cdot V_{DD} \tag{2.12}$$

where  $D_I$  stands for the power MOSFET duty cycle, and  $K = \frac{2L}{Rf_s}$ .

### 2.3 Open Problems in Buck Converters

As a popular used converter, tremendous effort has been dedicated to improve the performance of buck converter. The evolutionary trend in modern power supplies toward low voltage, high current, high power density, reduced volume, lower cost, and faster transient response poses new challenges for buck converter design. The recent trends and popular problems in buck converter are briefly introduced in the following section.

#### 2.3.1 High Efficiency

Efficiency is the most critical and important parameter for any power supply. A lot of work has been published in the field of improving efficiency. Since the efficiency of buck converter drops both at light load and at heavy load, the research divided into two directions depending on different applications. Applications such as battery-powered portable devices need to be designed for high efficiency over entire load ranges extended from light load to heavy load, and especially at the light load range, since they operate at this region most of the time. This project is targeting at these applications and working on improving light-load efficiency. Other applications maximize efficiency at heavy load with less concern of light-load efficiency in order to minimize the heat generated inside the converter [10]-[14].

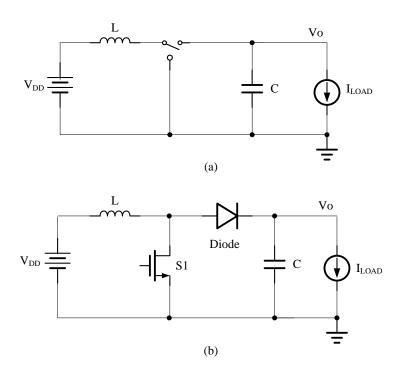

There are various kinds of techniques for improving efficiency of buck converter.

Among all these techniques, soft switching techniques, especially zero-voltage-switching

(ZVS) and zero-current-switching (ZCS) are very popular in high power applications. In ZCS technique, an inductor is placed in series with converter main switch or main diode to provide soft switching condition at switch turn-on instant. Before switch turn-off instant, an auxiliary switch is turned on and the main switch current is reduced to zero. In ZVS technique, a capacitor is placed in parallel with the main switch to provide soft switching condition for switch turn-off [15]-[17]. Figure 20 shows the example of ZVS implementation for diode turn-off transition, where *Cr* is added in parallel with the diode [2]. In this technique, soft switching condition for switch turn-on is achieved by an auxiliary switch, which discharges the snubber capacitor across the main switch. Soft-switching techniques typically increase the current and/or voltage stresses in the semiconductor devices. ZVS techniques typically increase the voltage stress of the active switches, and ZCS techniques increase current stresses. Furthermore, the auxiliary large and lossy inductor and capacitor make these techniques poor candidates for on-chip implementation applications.

Figure 20. Buck converter schematic with ZVS turn-off [2]

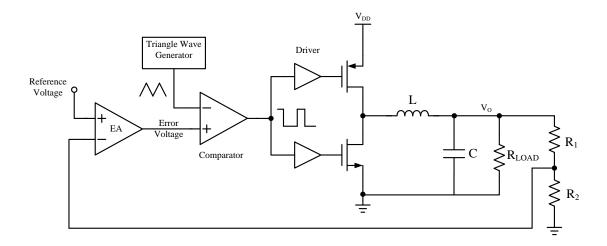

#### 2.3.2 Control Schemes

To improve the output transient response of buck converter, numerous control topologies are proposed for different applications. Faster recovery time and/or smaller voltage overshoot/undershoot, as well as simpler implementations and smaller sizes are targeted.

Traditional control techniques, such as pulse width modulation (PWM) and pulse frequency modulation (PFM), still have margin for improvement. For example, [18] propose a pseudo-Type III compensation for PWM voltage-mode buck converter, which mimics the frequency response of a Type III compensator. Type III compensator provides two zeroes and two poles by adding large value resistors and capacitors to stable the loop, which is area consuming. The pseudo-Type III compensation in [18] is able to be implemented without resistors and capacitors, thus tremendously reduces the chip area and power consumption. Hysteretic control techniques are also popular due to advantages in their simplicity, immediate response to a line/load transient and unconditional stability under all operation conditions. Their main disadvantages are switching frequency varies with design parameters, and the inductor current may go beyond the current limit of the power switches during large signal transient response [19]-[21].

Although analog controllers are still the mainstream control schemes, digital control has gained popularity recent years due to its robustness to noise, lower sensitivity to parameter variations and programmability along with its ability to implement sophisticated control schemes [22]-[23]. The main concern in digital control is how to match the dynamic performance of their analog counterparts [23]-[26]. ADC which

digitizes the error signal and digital PWM generator (DPWM) are the main building blocks and the most challenging circuits to design digital control [27]-[31].

# 2.3.3 Fully Integration

In recent years, there is a growing interest in power-supply-on-a-chip (PSoC) or power-supply-in-a-package (PSiP) for DC-DC converters. The idea of integrating all active and passive components in a switching converter would provide smaller area and lower cost, fewer connections and less parasitics, and also, it reduces losses through connections and increases reliability. The main challenge of a fully integrated buck converter is to find an effective way to integrate the output filter. Typical values for the filter inductor and filter capacitor are in the order of  $\mu H$  and  $\mu F$ , respectively, which are too large to integrate on chip.

One way to reduce the filter size is increasing the switching frequencies. The higher is the switching frequency, the smaller the physical size and component value. However, there is an upper frequency limit where either magnetic losses in the inductor or switching losses in the converter reduce efficiency to an impractical level. [32], [33] and [34] reported switching frequencies as high as 102MHz, 660MHz and 3GHz respectively to enable the integration of filter, and power losses reduction techniques are employed to achieve better efficiency.

Multiphase interleaved buck converter is another well-known solution to enable smaller filter size [35]-[39]. As shown in Figure 21, multiphase buck converter combines N stages of buck converters in parallel with a common output filter capacitor. By applying a 360°/N phase shift between the control signals of adjacent power stages, the output current ripple can be cancelled out, therefore the required output inductance is

reduce. The effective output frequency is increased to N times of the switching frequency in a single stage and a smaller capacitance is required at the output. Current sharing, current unbalance, phase interleaving, and better controller are the major concerns of multiphase buck converter [21], [38], [40]-[41].

Figure 21. Schematic of a synchronous n-phase buck converter

The reported efficiencies of fully integrated buck converters are usually around 50%, which are much lower than off-chip buck converters. However, they still have a significant improvement over linear regulators such as LDOs which are also on chip. Except high switching frequency, low Q of on-chip inductor (typically 5 to 10) is also a limiting factor for the integrated converter achieving good efficiency. In [42], in-package bondwires with and without ferrite epoxy glob cores are used as the filter inductor in buck converter, showing very high saturation current and low DCR.

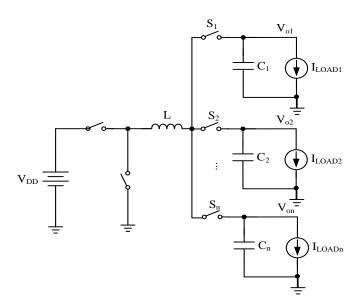

# 2.3.4 Single Inductor Multiple Output

Single inductor multiple output (SIMO) buck converter, which is shown in Figure 22, use only one inductor to generate several different voltage/current levels, thus it is a very suitable solution for power-management ICs where multiple voltage/current levels are required. Design challenges in this field include system stability, power efficiency, and cross regulation [43]-[45].

Figure 22. Schematic of single input multiple output buck converter

# 2.4 Light-Load Efficiency of Buck Converters

In order to optimize the efficiency in light load, the power loss mechanisms in the buck converter are discussed in the following sub-section.

#### 2.4.1 Power Losses Analysis of Basic Buck Converter

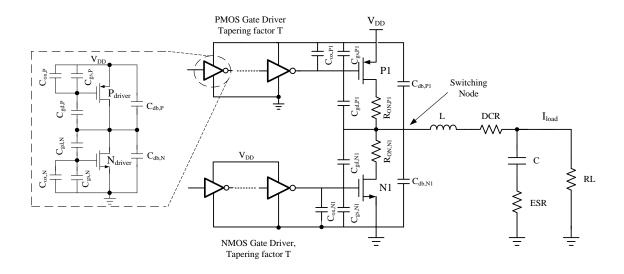

The power losses of a basic buck converter are a combination of the losses caused by the power MOSFETs, output filter, control circuits and traces. Usually the power consumption of the control circuits is very small compared to the power consumption of the power train (including the power MOSFETs, MOSFET gate drivers, and output filter). Therefore, only the power losses of the power train components are considered in the following efficiency analysis. To help with the analysis, a parasitic circuit model has been presented in Figure 23 [3], [32], [4]-[49].

Figure 23. Circuit model for basic buck converter with parasitics

### 2.4.1.1 Power Stage Related Power Losses

Power stage includes power transistors and gate drivers. The power transistors are typically large in size with high parasitics. To control the operation of the power transistors, a chain of MOSFET gate drivers are required, which are tapered with a taping

factor T. The gate driver loss and power transistors loss will be analyses separately in the following.

Assuming that the control signal applied to P1 and N1 are non-overlapping, no short-circuit current flows through P1 and N1 during transition. The short-circuit power dissipated in the gate drivers is also neglected assuming the transition times of the input signal applied at each gate drivers are smaller than the output transition time [50].

The gate drivers consist of a chain of inverters. It is well known that the power dissipation of an inverter can be written as

$$P_{inv} = f_s C_p V_{DD}^2 (2.13)$$

where  $f_s$  is the switching frequency,  $C_p$  is the parasitic capacitance,  $V_{DD}$  is the inverter supply voltage. Thus the gate drivers' loss can be expressed as

$$P_{driver} = f_s C_{driver} V_{DD}^{2} (2.14)$$

where  $C_{driver}$  is the total capacitance in driver chain, which includes transistor's gate oxide capacitor, gate-to-source/drain overlap capacitor, and drain-to-body junction capacitor. The largest portion in  $C_{driver}$  is the power transistor gate input capacitance.

The power losses of power MOSFETs in Buck converter are dominant by conduction losses and switching losses. Conduction loss is caused by the on-resistance of the transistors operating in linear region. When the MOSFET is on, it does not behave as an ideal switch with zero impedance, but it behaves as a small resistor, denoted by  $R_{on}$ . This loss can be expressed by:

$$P_c = i_{rms,P}^2 R_{on,P} + i_{rms,N}^2 R_{on,N}$$

(2.15)

$$i_{rms,P} = I_{load} \sqrt{D} (2.16)$$

$$i_{rms,P} = I_{load} \sqrt{1 - D} \tag{2.17}$$

where  $i_{rms,P}$  and  $i_{rms,N}$  are the root-mean-squared current through PMOS power transistor and NMOS power transistor respectively,  $R_{on,P}$ ,  $R_{on,N}$  denote the PMOS power transistor and NMOS power transistor on-resistance, D is duty cycle, and  $I_{load}$  is the load current. It is obvious that the conduction loss will be more significant at higher currents.

Switching losses occur as a result of the power required during the switches turn on and off. The dominant switching loss in power transistors *Ps,cap* is due to the dynamic power charging and discharging the parasitic capacitors of the switch node, which is given by:

$$P_{s,cap} = f_s C_p V_{DD}^2 (2.18)$$

where  $C_p$  is the parasitic capacitance of power switches. Figure 23 shows that the parasitic capacitors contain the gate-to-drain overlap (Miller) capacitor, drain-to-body junction capacitor, and parasitic capacitance associate with the connection of off-chip inductor, which include a bonding pad, bonding wire, pin, and board interconnect capacitance.

The total power dissipation in power stage is given by a combination of the above described losses:

$$P_{tot} = P_{drv,P} + P_{drv,N} + P_c + P_{s,cap} (2.19)$$

where  $P_{drv,P}$  and  $P_{drv,N}$  are the power dissipation of the driver circuit for PMOS power switch and NMOS power switch respectively.

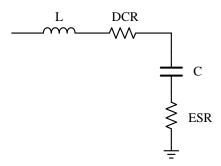

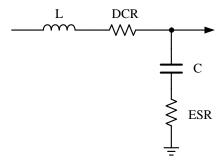

## 2.4.1.2 Output Filter Related Power Losses

Some part of the total power losses in buck converter are due to the series resistance of the filter inductor and the effective series resistance (ESR) of the filter capacitor, as

shown in Figure 24. These parasitic resistances are in the range of several hundred milliohms, and contributing to  $i^2R$  losses [5]. In this project, the output filter uses off-chip components, whose parasitics are relatively fixed, thus this part of loss can only be reduced by selecting components with lower parasitics.

Figure 24. Output filter with parasitic resistance

# 2.4.2 Light-Load Efficiency

Through the power loss analysis, we know that as load decreases, the conduction losses reduces together with the square of load current, but the switching losses are a fixed amount of power irrespective of the load size. Therefore, the rapid drop during light load condition is mainly caused by switching losses. As stated in Section 2.3.3, higher switching frequencies are preferred to reduce the off-chip inductor and capacitor sizes, which however increase the switching losses (Figure 25), and make the efficiency in light load even worse.

Figure 25. Switching losses vs switching frequency

#### 3. METHODS TO IMPROVE LIGHT-LOAD EFFICIENCY

#### 3.1 Previous Methods

Improving power efficiency of buck converters during light load becomes an essential requirement for battery-powered portable devices in order to gain power saving and extend battery life. Many techniques have been developed to mitigate this poor light-load efficiency problem. A review of several popular techniques is presented in the following.

### 3.1.1 PFM

The most frequently used method to improve light-load efficiency is to employ pulse frequency modulation (PFM) control mode [46], [51]-[59]. Since switching loss is proportional to switching frequency, by scaling down the switching frequency together with load current, PFM mode is able to reduce the switching losses, and maintains high light-load efficiency.

The main problem with PFM mode is high noise introduced by the changing switching frequencies. The varying switching frequency causes more severe EMI, making it unsuitable for noise-sensitive RF circuits in portable devices.

Usually both PFM mode and PWM mode are employed in one circuit. PFM mode is only used at light load, while at medium and heavy load, PWM mode is still preferred.

#### 3.1.2 Pulse Skipping Mode

Another prevailing method in industry is pulse skipping modulation (PSM) [60]-[62]. As shown in Figure 26, in PSM mode, control signal will skip some clock cycles as the load decreases. Consequently, the equivalent switching frequency is reduced, resulting in

increased light-load efficiency. In this mode, each pulse cycle is still synchronized by the PWM clock, thus it has better EMI characteristic. Compared to PWM and PFM mode, PSM mode also has faster response speed, but the voltage ripple is larger, and the actual switching frequency of power transistors is easy to enter the audible noise range due to skipped cycles.

Figure 26. Pulse skipping mode

#### 3.1.3 Burst Mode

Burst mode technique is also commonly used in improving light-load efficiency [63]. When configured for this mode and during light load, the converter will alternate between ON and OFF state. The control signal waveform is illustrated in Figure 27 [64]. During ON state, the controller bursts out a few pulses to maintain the charge voltage on the output capacitor. During OFF stare, it turns off the converter and goes into sleep mode with most of internal circuits shut down. Because no power is transferred during OFF stage, the output voltage begins to droop. The controller monitors the output voltage and after reaching a specified value, the converter eventually enters ON state delivering more current to replenish the output voltage. The action of switching transistors and other

unneeded portions of the converter circuit remain OFF significantly reduces power losses.

One drawback of burst mode is an additional low frequency ripple added on the output voltage during ON state, as shown in Figure 28.

Figure 27. Burst mode control signal at light load

Figure 28. Burst mode output signal

### 3.1.4 Mode-Hopping

In mode-hopping technique, the buck converter operates in both synchronous and asynchronous modes. Under medium to heavy load conditions, it operates in synchronous mode which also means in continuous conduction mode (CCM), where the inductor current does not reach or go below zero. Under light load condition, it operates in asynchronous mode or in another word discontinuous conduction mode (DCM), by

turning off the synchronous rectifier when negative inductor current is detected, to mainly reduce conduction losses [46], [61], [65]-[66]. However, conduction losses are not the dominant power loss under light load condition, thus the efficiency improvement by this technique itself is limited. In addition, the changes in the buck converter model may lead to serious regulation or stability problem. To avoid this problem, design complexity is increased.

## 3.1.5 Gate Drive Technique

This technique is more popular in literature than in industry products [32], [67]-[77]. In [32], [67]-[68], a gate drive technique was presented whereby the gate voltage swing statically reduced or dynamically scales with load current such that the gate drive loss reduces at light load. In [69]-[73], resonant gate drivers were presented in order to recover the power loss due to gate charge, which has a significant efficiency improvement in high frequency converters, but generally requires components, such as inductors, capacitors, or transformer, that increase cost and hard to be integrated in standard CMOS processes. Presented in [34], [74]-[77], gate charge recycling doesn't reduce any factor that affect the gate drive loss directly, but it involves storing a portion of the gate charge in a capacitor during discharge phase, then re-using it during charging phase. The main problem with this technique is that it only reduces the gate-drive loss, but not the switching loss due to switch the switching node.

### 3.1.6 Other Techniques

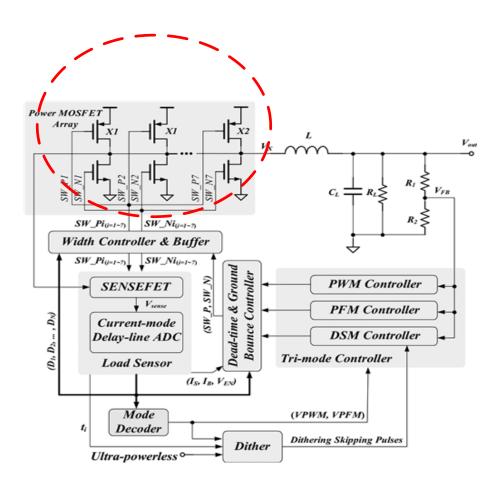

There are several other techniques to get power loss reduction at light load condition, such as width controlling technique [47], [78]-[80], dead-time controlling technique [80]-[83].

In width controlling technique, the width of power MOSFET and the size of the driver are adjusted dynamically depending on load condition to save power. Since the device parasitics generally decrease linearly with decreased gate width, the switching loss can be reduced by using smaller width at light load. Figure 29 shows an example of how the width controlling is implemented.

Figure 29. Buck converter with width controlling technique [80]

In dead-time controlling technique, since too short dead time turns power NMOS transistor on too early, leaking the energy directly to ground, not to load, while too long dead time conducts body diode of the NMOS power switch, increasing loss, optimum

dead time exists. Adjusting dead time according to the variation of load can optimize the power efficiency.

There is also technique which doesn't rely on control or active circuit variation, but increases the value of the filter inductor at light load, thereby achieving smaller inductor current ripple to reduce both conduction loss and switching loss [84].

### 3.2 Proposed Method

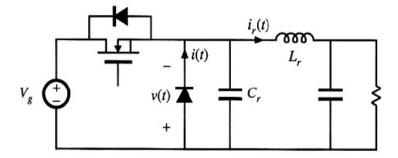

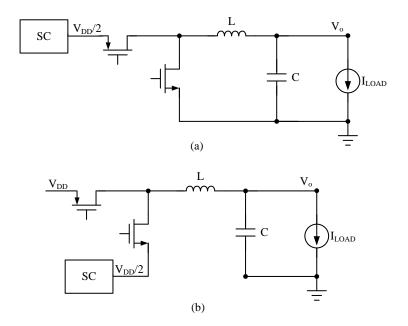

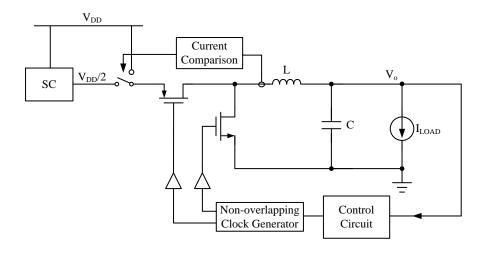

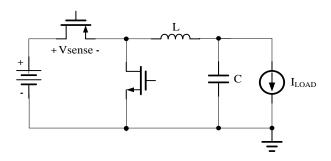

The basic idea of the proposed method is shown in Figure 30. The circuit topology is very similar with the conventional buck converter, only adds another voltage source VL between the source node of NMOS power switch and ground. We call the new topology a dual-supply buck converter.

Figure 30. Basic idea of proposed dual-supply buck converter

As shown in Figure 30, now we have two voltage sources which are denoted as VH and VL respectively. Under medium and heavy load condition, the proposed buck

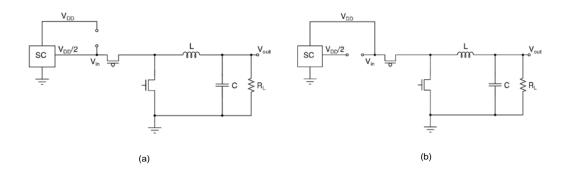

converter works exactly the same as conventional buck converter with  $VH=V_{DD}$ , and VL=0. Under light load condition, the operation of this buck converter is divided into two regions according to the output voltage:

- (a). When output voltage is smaller than  $V_{DD}/2$ , let  $VH=V_{DD}/2$ , VL=0. The switching node voltage, as well as the gate driving voltage, is switching between 0 and  $V_{DD}/2$ .

- (b). When output voltage is between  $V_{DD}/2$  to  $V_{DD}$ , let  $VH=V_{DD}$ ,  $VL=V_{DD}/2$ . The switching node voltage, as well as the gate driving voltage, is switching between  $V_{DD}/2$  and  $V_{DD}$ .

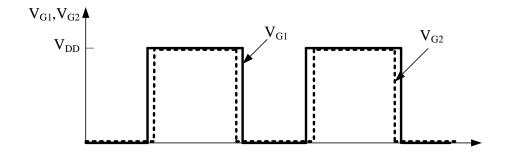

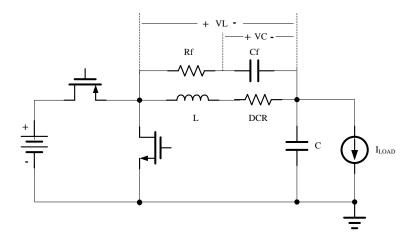

With a switched capacitor converter providing the supply voltage of  $V_{DD}/2$ , the above operation can be simply described with Figure 31.

Figure 31. Simplified proposed buck converter schematic under light-load condition: (a).  $Vo < V_{DD}/2$  (b).  $V_{DD}/2 < Vo < V_{DD}$

The reason behind adding another voltage source to improve power efficiency can be explained according to the power stage losses expression which is given by Equation (2.19). The equations of three switching losses components, including  $P_{s,cap}$ ,  $P_{drv,P}$  and  $P_{drv,N}$ , should be modified when applied for this topology:

$$P_{s,cap} = f_s C_p (VH - VL)^2$$

(3.1)

$$P_{drv,P} = f_s C_{driver,p} (VH - VL)^2$$

(3.2)

$$P_{drv,N} = f_s C_{driver,N} (VH - VL)^2$$

(3.3)

Between these three parts of switching losses,  $P_{s,cap}$  is the dominant one, since the driver size is usually much smaller than the power transistor size, resulting in a much smaller parasitic capacitance than  $C_p$ . For power transistors,  $C_p$  can easily go to pF range.

Under light load condition, switching losses are dominant. In this project, both of the two working regions (region (a) and (b)) at the light load have reduced  $V_{DD}$  to VH-VL, which equals to  $V_{DD}/2$ . Thus switching losses quadratically reduce to ½ of the original value, improving light-load efficiency. The following is an example of rough estimation of switching loss and efficiency. Assume  $C_p$  is 20pF,  $f_s$  is 1MHz, VH - VL is 1V, then the switching loss is around 20 $\mu$ W. Also assuming load current is 0.1mA, output voltage is 0.5V, and MOSFET on-resistance is 0.2ohm, the efficiency will be 71.23%. While for a conventional Buck converter, under the same condition, switching loss will be  $80\mu$ W, and efficiency will drop to 38.4%. The efficiency difference is as large as 32.83%.

Under medium and heavy load conditions, the power loss is dominant by conduction losses, which is given by Equation (2.15). In this equation, the MOSFET on-resistance  $R_{on}$  is given by:

$$R_{on} \propto \frac{1}{V_{gs} - V_{th}} = \frac{1}{VH - VL - V_{th}} \tag{3.4}$$

where  $V_{gs}$  is the voltage difference between transistor gate and source, and  $V_{th}$  is the transistor threshold voltage.

Equation (3.4) shows that smaller VH-VL is no longer good for efficiency if conduction losses dominant, because when  $V_{gs}$  reduces,  $R_{on}$  will increase, thereby deteriorating the efficiency at the medium and heavy load. To compensate for this, at the point where the buck converter with VH-VL=  $V_{DD}/2$  is about to have lower efficiency than the one with VH-VL=  $V_{DD}$ , we switch the topology to conventional buck converter, that is to let VH= $V_{DD}$ , and VL=0.

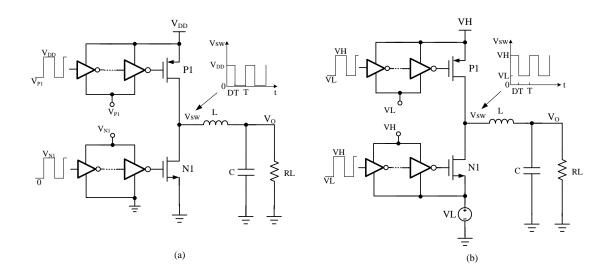

## 3.3 Strengths and Weaknesses of Proposed Method

Compared with previously discussed method, the strengths of this proposed method lie in several points. First, the efficiency at light load is improved significantly. The results showing in Section 6 and Section 7 will confirm this argument. Secondly, the switching frequency in this project keeps constant, therefore smaller noise and EMI is achieved comparing with varying switching frequency. Thirdly, PWM method is employed over the entire load range, rather than changing to other control techniques at light load, simplifying the control design. Finally, the lower supply at light load will result in both smaller output voltage ripple and smaller inductor current ripple, thus a cleaner supply is obtained.

Besides, the proposed method is similar to gate swing scaling technique. As shown in Figure 32, compared to gate swing scaling technique, the proposed method not only scales the gate voltage by two, but also reduces the swing at the switching node to half of

the original value. Thus the switching loss due to charging and discharging the switching node is decreased, and improve the efficiency in further.

Figure 32. Buck converter with (a) gate swing scaling technique (b) proposed dual-supply technique

The weaknesses of this method show in several aspects. The design is more complicated due to the additional loop and SC converter. Two different supply voltage levels exist in the circuit and increase the complexity. Additionally, due to the transition between light load and medium load, the circuit transient response becomes slower.

#### 4. SYSTEM ARCHITECTURE

# 4.1 Specifications

A buck converter with fixed input and output voltage is designed in this project with TSMC 0.18 $\mu$ m CMOS technology. The norminal supply for I/O transistors of TSMC 0.18 $\mu$ m technology, which is 3.3V, is chosen to be the input voltage. The output voltage is chosen to be 0.9V, thus the circuit is working in the first region mentioned before (VH=VDD/2, VL=0). If it operates in the second region, the circuit will be very similar, with main changes of SC circuit's output connection.

## 4.1.1 Choice of Switching Frequency

The range of switching frequency of buck converter changes from several kilo Hz to several Mega Hz. As switching frequency increases, the minimum size of the inductor to produce continuous current and the minimum size of the capacitor to limit output ripple both decrease. Therefore, high switching frequency is desirable to reduce the size of both the inductor and the capacitor. The tradeoff for using high switching frequency is the increased power loss in switches, which has been discussed in Section 2. In this project, switching frequency is chosen to be 3MHz.

### 4.1.2 Output Ripple

Output ripple is determined by the filter inductor and filter capacitor. The expression for inductor current ripple and output voltage ripple is given by Equation (2.7) and Equation (2.8) respectively. Ripple is undesired for generating a clean supply, since ripple in supply can cause clock jitter, increasing PSRR requirement for analog circuit. Filter with larger size in buck converter is able to achieve smaller the ripple, but it can

never suppress ripple to zero. Considering the trade-off between filter size (large filter means large area) and ripple amplitude, this design allows an output voltage ripple of around 1% of the average output voltage, and an inductor current ripple of around 1% of the maximum load current.

#### 4.1.3 Load Regulation

Load regulation is a very important figure-of-merit in switching converters. Load regulation is defined as the change in the output voltage corresponding to sudden change in the load from minimum current to maximum current or the opposite direction.

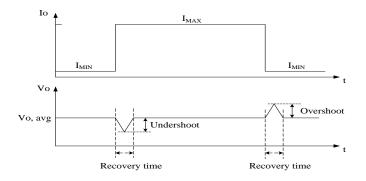

When there is a step in the load current, controller will response to the change, and adjust the duty cycle to keep constant output voltage. The transient waveform of output voltage corresponding to the sudden current change is shown in Figure 33. When load current goes from minimum to maximum, the duty cycle needs to increase to compensate for the increased conduction losses. However, the change of duty cycle needs some time, the lower duty cycle results in an output voltage undershoot. Similarly, when load current drops from maximum value to minimum value, the extra current provided by source will flow to the output capacitor, resulting in an output voltage overshoot. The output voltage recovery time is determined by the controller speed. The undershoot/overshoot voltage is given by:

$$V_{shoot} = \frac{I_{MAX} - I_{MIN}}{C} \cdot \Delta t + (I_{MAX} - I_{MIN}) \cdot ESR$$

(4.1)

where  $I_{MAX}$  is the maximum load current,  $I_{MIN}$  is the minimum load current, C is the output capacitance,  $\Delta t$  is the time that the load current changes from minimum to maximum or the other way around, and ESR is the parasitic resistance of the output capacitor.

Figure 33. Load transient response

# 4.1.4 Specifications Summation

Table 2 sums the specifications of the proposed buck converter.

Table 2. Specifications of the proposed buck converter

| Parameters       | Specs                |      |

|------------------|----------------------|------|

| Technology       | TSMC 0.18µm CMOS     |      |

| $ m V_{DD}$      | 3.3V                 |      |

| V <sub>OUT</sub> | 0.9V                 |      |

| Fs               | 3MHz                 |      |

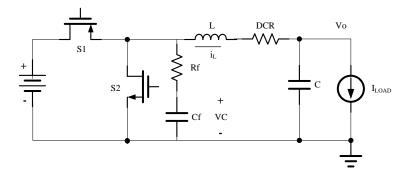

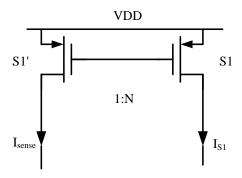

| I <sub>O</sub>   | 1mA ~ 400mA          |      |