# New MP-SoC profiling tools based on data mining techniques

Sofiane Lagraa

## ▶ To cite this version:

Sofiane Lagraa. New MP-SoC profiling tools based on data mining techniques. Artificial Intelligence [cs.AI]. Université de Grenoble, 2014. English. NNT: 2014GRENM026. tel-01548913

## HAL Id: tel-01548913

https://tel.archives-ouvertes.fr/tel-01548913

Submitted on 28 Jun 2017

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## UNIVERSITÉ DE GRENOBLE

ISBN: 978-2-11-129190-4

## **THÈSE**

Pour obtenir le grade de

## DOCTEUR DE L'UNIVERSITÉ DE GRENOBLE

Spécialité : Informatique

Arrêté ministérial 7 août 2006

Présentée par

## **Sofiane LAGRAA**

Thèse dirigée par **Frédéric PÉTROT**<sup>1</sup> et codirigée par **Alexandre TERMIER**<sup>2</sup>

préparée au sein des Laboratoires <sup>1</sup>TIMA et <sup>2</sup>LIG et de l'École Doctorale Mathématiques, Sciences et Technologies de l'Information, Informatique (MSTII)

## Nouveaux outils de profilage de MP-SoC basés sur des techniques de fouille de données

« New MPSoC profiling tools based on data mining techniques »

Thèse soutenue publiquement le **13 Juin 2014** devant le jury composé de:

#### M. Albert Cohen

Directeur de recherche INRIA, École Normale Supérieure, Examinateur

#### M. Bernard Goossens

Professeur, Université de Perpignan, Rapporteur

#### M. Pascal Poncelet

Professeur, Université Montpellier 2, Rapporteur

## M. Miguel Santana

Directeur du centre IDTEC à STMicroelectronics, STMicroelectronics - Grenoble, Examinateur

## Mme. Peggy Cellier

Maître de conférences, INSA Rennes, Examinatrice

## M. Frédéric Pétrot

Professeur, Institut Polytechnique de Grenoble, Directeur de thèse

#### M. Alexandre Termier

Maître de conférences (HDR), Université Joseph Fourier, Co-Directeur de thèse

## Abstract

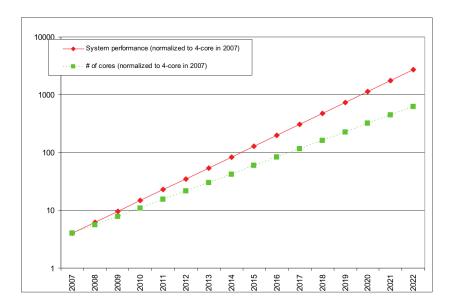

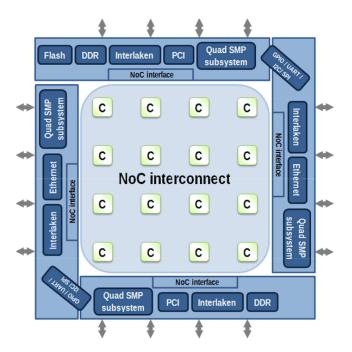

Miniaturization of electronic components has led to the introduction of complex electronic systems which are integrated onto a single chip with multiprocessors, so-called Multi-Processor System-on-Chip (MPSoC). The majority of recent embedded systems are based on massively parallel MPSoC architectures, hence the necessity of developing embedded parallel applications. Embedded parallel application design becomes more challenging: It becomes a parallel programming for non-trivial heterogeneous multiprocessors with diverse communication architectures and design constraints such as hardware cost, power, and timeliness.

A challenge faced by many developers is the profiling of embedded parallel applications so that they can scale over more and more cores. This is especially critical for embedded systems powered by MPSoC, where ever demanding applications have to run smoothly on numerous cores, each with modest power budget. Moreover, application performance does not necessarily improve as more cores are added. Application performance can be limited due to multiple bottlenecks including contention for shared resources such as caches and memory. It becomes time consuming for a developer to pinpoint in the source code the bottlenecks decreasing the performance.

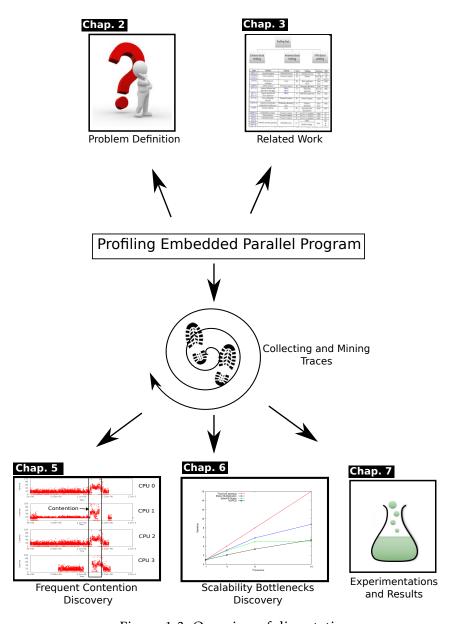

To overcome these issues, in this thesis, we propose a fully three automatic methods which detect the instructions of the code which lead to a lack of performance due to contention and scalability of processors on a chip. The methods are based on data mining techniques exploiting gigabytes of low level execution traces produced by MPSoC platforms. Our profiling approaches allow to quantify and pinpoint, automatically the bottlenecks in source code in order to aid the developers to optimize its embedded parallel application. We performed several experiments on several parallel application benchmarks. Our experiments show the accuracy of the proposed techniques, by quantifying and pinpointing the hotspot in the source code.

**Key Words** Multi-Processor System-on-Chip (MPSoC), Parallel Embedded Software, Profiling, Data Mining, Execution Traces, Contention, Scalability.

## Résumé

La miniaturisation des composants électroniques a conduit à l'introduction de systèmes électroniques complexes multiprocesseurs intégrés sur une seule puce, les *Multi-Processor System-on-Chip* (MPSoC). La majorité des systèmes embarqués à venir est basée sur des architectures avec un grand nombre de processeurs, d'où la nécessité de développer des applications parallèles embarquées. La conception et le développement d'une application parallèle embarquée est de plus en plus difficile, notamment pour les architectures multiprocesseurs hétérogènes ayant différents types de contraintes de communication et de conception, tels que le coût du matériel, la puissance et la rapidité.

Un défi à relever par les développeurs est le profilage des applications parallèles afin qu'elles puissent passer à l'échelle. Cela est particulièrement important pour les systèmes embarqués de type MPSoC, où les applications doivent fonctionner correctement sur de nombreux cœurs. En outre, la performance d'une application ne s'améliore pas forcément lorsque l'application tourne sur un nombre de cœurs encore plus grand. La performance d'une application peut être limitée en raison de multiples goulots d'étranglement, notamment la contention sur des ressources partagées telles que les caches et la mémoire. Il devient difficile et long pour un développeur de faire un profilage de l'application parallèle et d'identifier les goulots d'étranglement dans le code source qui diminuent la performance de l'application.

Pour surmonter ces problèmes, dans cette thèse, nous proposons trois méthodes automatiques qui détectent les instructions du code source conduisant à une diminution de performance due à la contention et à la croissance du nombre de processeurs sur une même puce. Les méthodes sont basées sur des techniques de fouille de données exploitant des gigaoctets de traces d'exécution de bas niveau produites par des simulateurs de plateformes MPSoC. Nos approches de profilage permettent de quantifier et de localiser automatiquement les goulots d'étranglement dans le code source afin d'aider les développeurs à optimiser leurs applications parallèles embarquées. Nous avons effectué plusieurs expériences sur plusieurs applications parallèles embarquées. Elles montrent la précision des techniques proposées, en quantifiant et localisant avec précision les lignes de code dans le code source qui induisent des ralentissements.

Mots Clès Système MultiProcesseur sur Puce (MPSoC), Logiciel Parallèle Embarqué,

## ACKNOWLEDGMENTS

Il m'est agréable à travers ces quelques lignes d'exprimer toute ma gratitude et mes remerciements envers les personnes qui m'ont aidé et m'ont soutenu tout au long de ma thèse.

Mes sincères remerciements vont à Mr Frédéric Pétrot et Mr Alexandre Termier, qui m'ont proposé ce sujet de thèse à travers lequel j'ai pu apprécier deux domaines de recherche : le data mining et les systèmes embarqués. Je les remercie pour leur confiance et leur soutien tout au long de ce projet.

J'adresse mes remerciements à Mr Albert Cohen qui m'a fait l'honneur de présider le jury de ma thèse. Je souhaite aussi remercier Mr Goossens et Mr Poncelet pour avoir accepté de rapporter mon travail de thèse. Mme Cellier et Mr Sontana pour avoir accepté d'examiner mon travail.

Je remercie mes collègues de l'équipe SLS et l'équipe HADAS respectivement au laboratoire TIMA et LIG pour leurs conseils, leur gentillesse et leur bonne humeur.

En fin, ce travail n'aurait pu avoir lieu sans le précieux soutien de ma famille.

## List of Figures

| 1.1 | Predictive evolution of number of cores in a chip and high performance    |    |

|-----|---------------------------------------------------------------------------|----|

|     | computing (source [ITR07])                                                | 2  |

| 1.2 | MPPA®-256 block diagram (source [KAL])                                    | 3  |

| 1.3 | Overview of dissertation                                                  | 6  |

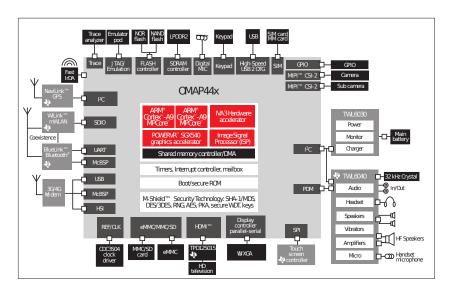

| 2.1 | Example of MPSoC platform (Source: Texas Instruments)                     | 8  |

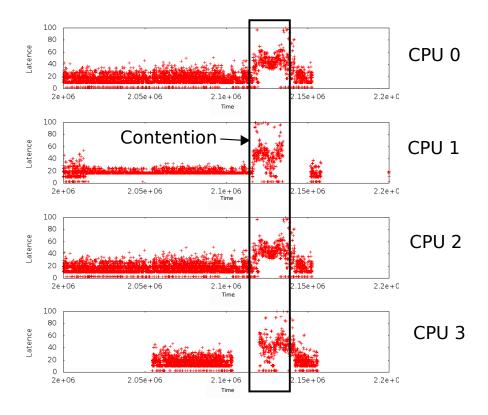

| 2.2 | Concurrent memory accesses latency versus Time across CPUs                | 12 |

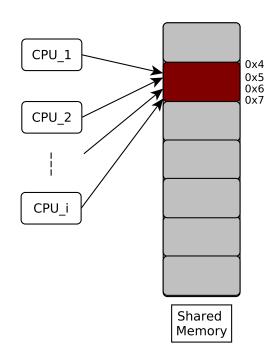

| 2.3 | Concurrent memory access by CPUs in a given time window                   | 13 |

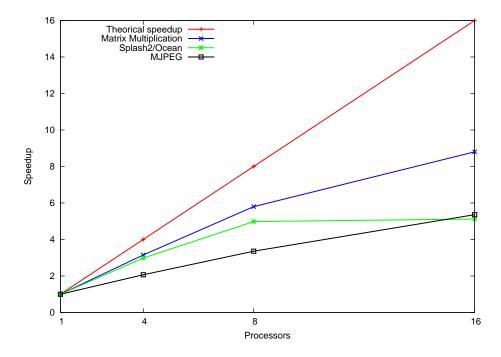

| 2.4 | Speed-up as a function of the number of processors for matrix multiplica- |    |

|     | tion, ocean (SPLASH-2) and MJPEG multi-threaded applications              | 14 |

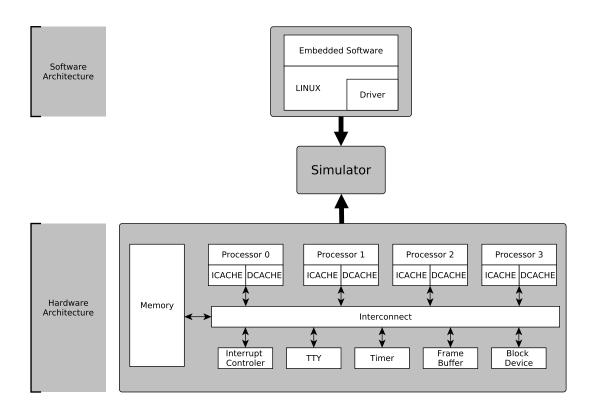

| 2.5 | Overview of the simulation of embedded software on MPSoC architecture     | 17 |

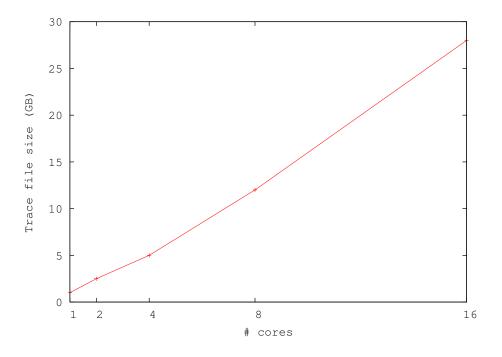

| 2.6 | Trace file size according to the number of CPUs in each MPSoC platform    | 19 |

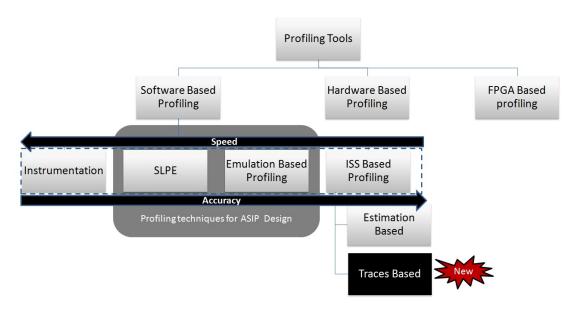

| 3.1 | Classification of Embedded Software Profiler                              | 28 |

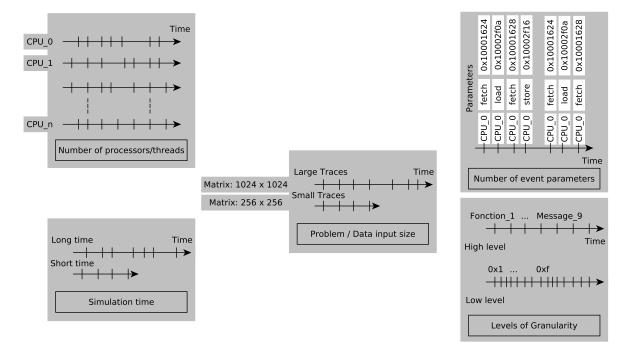

| 3.2 | Reasons for large traces                                                  | 30 |

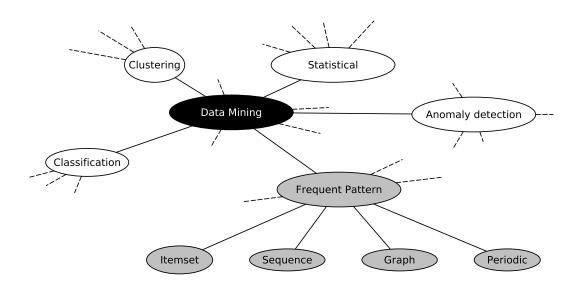

| 3.3 | Map of Data Mining domains                                                | 32 |

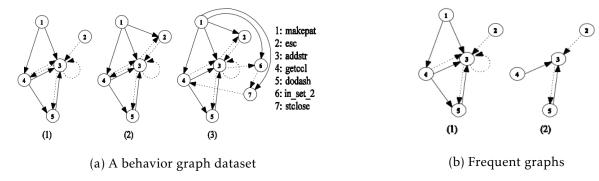

| 3.4 | A behavior graph dataset and Frequent graphs [LYY+05]                     | 34 |

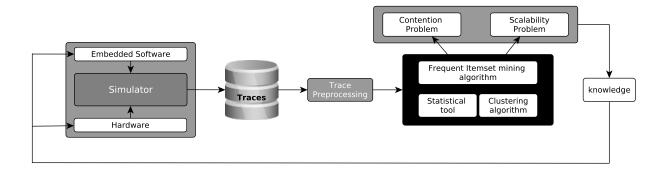

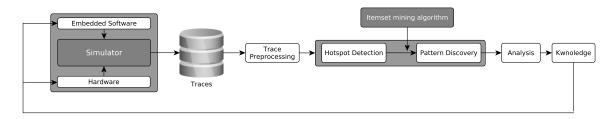

| 4.1 | Profiling Process Overview                                                | 42 |

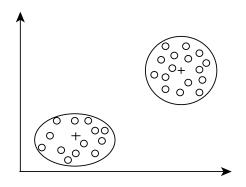

| 4.2 | Two groups or clusters of data points                                     | 45 |

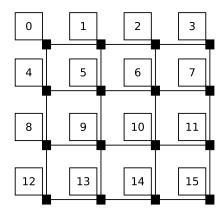

| 5.1 | Example of 4 x 4 mesh NoC                                                 | 51 |

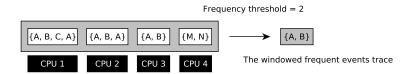

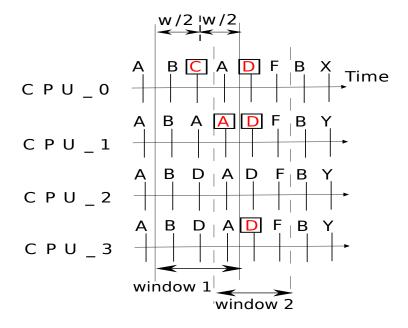

| 5.2 | The windowed frequent events trace                                        | 54 |

| 5.3 | Contention Pattern discovery methodology from execution traces in MP-     |    |

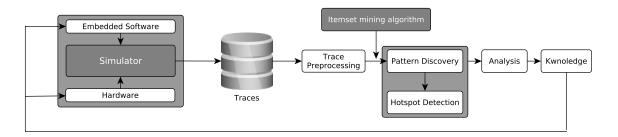

|     | SoC                                                                       | 55 |

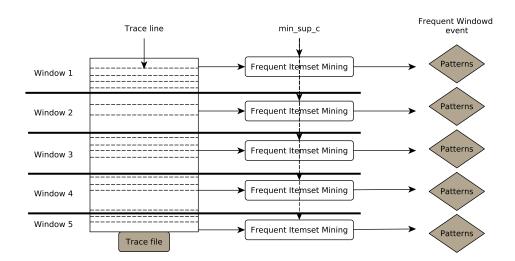

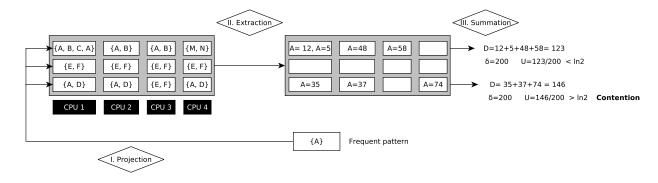

| 5.4 | Overview of Windowed frequent events trace computation                    | 56 |

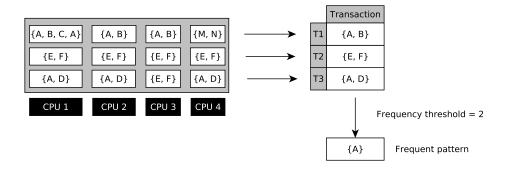

| 5.5 | Example of frequent patterns                                              | 56 |

| 5.6 | Example of hotspot detection from patterns                                | 57 |

| 5.7 | Contention Pattern discovery methodology from execution traces in MP-     |    |

|     | SoC                                                                       | 59 |

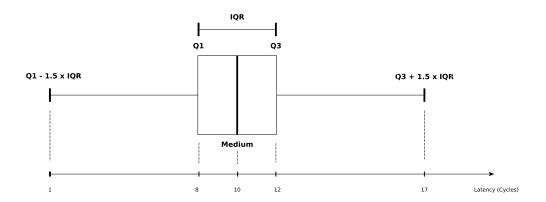

| 5.8 | Boxplot                                                                   | 60 |

| 5.9 | The windowed events trace                                                 | 61 |

|     |                                                                           |    |

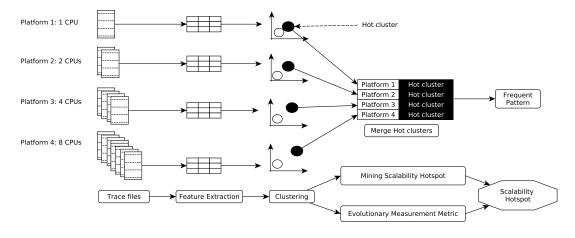

| 6.1  | Global approach for scalability hotspot in MPSoC platforms                | 70  |

|------|---------------------------------------------------------------------------|-----|

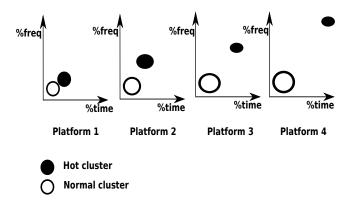

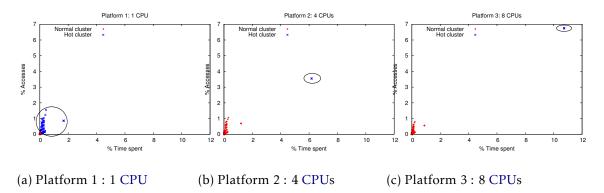

| 6.2  | Hot cluster evolution                                                     | 73  |

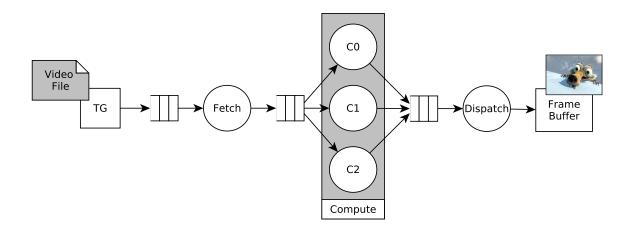

| 7.1  | MJPEG Application described with communicating tasks                      | 80  |

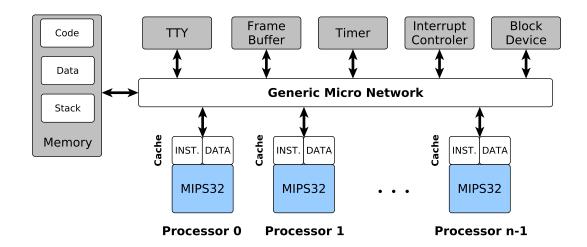

| 7.2  | Description of the used architecture                                      | 81  |

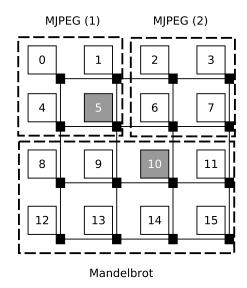

| 7.3  | Simulated platform (1)                                                    | 83  |

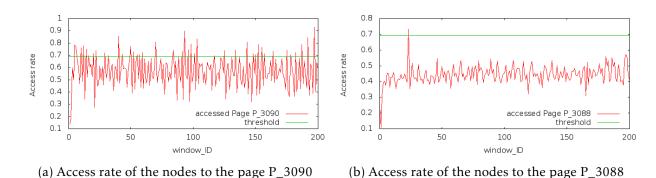

| 7.4  | Access rate of the nodes to the pages P_3090 and P_3088 running Man-      |     |

|      | delbrot application                                                       | 84  |

| 7.5  | Results Representation                                                    | 84  |

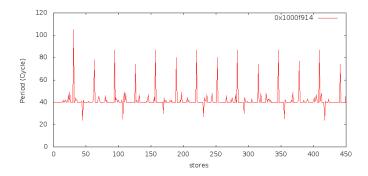

| 7.6  | Period between the successive <i>stores</i> of the address 0x1000f914     | 86  |

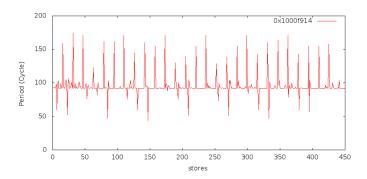

| 7.7  | New period between the successive <i>stores</i> of the address 0x1000f914 | 86  |

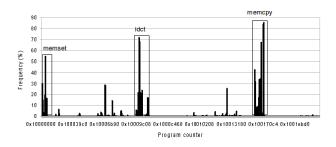

| 7.8  | Memory access frequency                                                   | 88  |

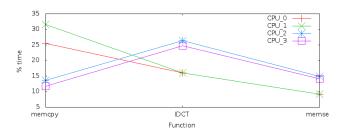

| 7.9  | Run time of <i>memcpy, idct, memset</i> in parallel application           | 88  |

| 7.10 | Scalability hotspot in assembly code for the matrix multiplication appli- |     |

|      | cation                                                                    | 90  |

| 7.11 | Visualizing the evolution of hot clusters in each multi-threaded matrix   |     |

|      | multiplication application according to platform instances                | 92  |

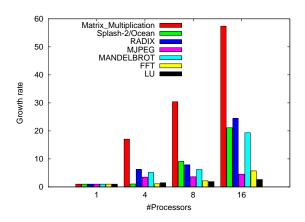

| 7.12 | Growth rate evolution over platform instances running five multi-threaded |     |

|      | applications                                                              | 92  |

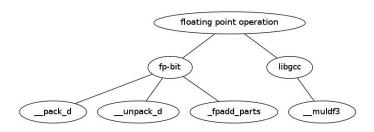

| 7.13 | InitA function of LU application                                          | 93  |

| 7.14 | Improvement of InitA function of LU application                           | 93  |

| A.1  | An example of disassembly of executable MJPEG code                        | 101 |

| B.1  | InitA function of LU application                                          | 104 |

## LIST OF TABLES

| 2.1         | Raw trace format                                                         | 18  |

|-------------|--------------------------------------------------------------------------|-----|

| 3.1         | Access memory addresses of CPUs                                          | 33  |

| 3.2         | Frequent Access memory addresses of CPUs                                 | 34  |

| 3.3         | A dataset in the context of system trace analysis [CBT+12]               | 35  |

| 3.4         | Works on program analysis using on Traces                                | 39  |

| 4.1         | Example data                                                             | 46  |

| 4.2         | Frequent itemsets                                                        | 46  |

| 5.1         | Raw trace format for NoC                                                 | 51  |

| 5.2         | Frequent Contention patterns                                             | 58  |

| 5.3         | Frequent Patterns                                                        | 63  |

| 5.4         | Comparison of contention analysis methodologies in MPSoC                 | 65  |

| 6.1         | Scalability hotspots                                                     | 75  |

| 6.2         | Comparison of Scalability Bottlenecks Detection Methodologies            | 76  |

| 7.1         | Characteristics of applications                                          | 80  |

| 7.2         | Summary of the simulation characteristics                                | 82  |

| 7.3         | Frequent patterns                                                        | 84  |

| 7.4         | Frequent patterns                                                        | 85  |

| 7.5         | Contention windows                                                       | 87  |

| 7.6         | Frequent Patterns                                                        | 88  |

| 7.7         | Scalability hotspots                                                     | 91  |

| 7.8         | Coverage of clusters in each multi-threaded application across platform  |     |

|             | instances                                                                | 95  |

| A.1         | New Raw trace format                                                     | 102 |

| B.1         | Frequent Contention Patterns in FFT Application                          | 103 |

| B.2         | Frequent Contention Patterns in Mandelbrot Application                   | 104 |

| B.3         | Data variable called by floating point functions in platform with 4 CPUs | 104 |

| <b>D.</b> 3 | Data variable called by hoating point functions in platform with 4 Cl Os | 103 |

| <b>B.4</b> | Data variable called by floating point functions in platform with 8 CPUs | 105 |

|------------|--------------------------------------------------------------------------|-----|

| B.5        | Frequent Contention Patterns in RADIX Application                        | 105 |

| B.6        | Frequent Contention Patterns in LU Application                           | 105 |

## Contents

| Αt | ostrac | ct      |                                                         | 111 |

|----|--------|---------|---------------------------------------------------------|-----|

| Ré | sume   | é       |                                                         | v   |

| A  | knov   | vledgm  | ents                                                    | vii |

| Li | st of  | Figures |                                                         | ix  |

| Li | st of  | Tables  |                                                         | xi  |

| 1  | Intr   | oductio | on                                                      | 1   |

| 2  | Prol   | blem D  | efinition                                               | 7   |

|    | 2.1    | Conte   | xt                                                      | 7   |

|    |        | 2.1.1   | MPSoC                                                   | 7   |

|    |        | 2.1.2   | Terminology                                             | 9   |

|    |        |         | 2.1.2.1 MPSoC platform                                  | 9   |

|    |        |         | 2.1.2.2 Multi-threaded programs                         | 9   |

|    |        |         | 2.1.2.3 Parallel Embedded Software                      | 9   |

|    | 2.2    | Difficu | ulties of Writing Parallel Programs for MPSoC           | 9   |

|    | 2.3    | MPSo    | C Profiling Problems                                    | 10  |

|    |        | 2.3.1   | Contention problems                                     | 11  |

|    |        | 2.3.2   | Scalability bottlenecks                                 | 13  |

|    |        | 2.3.3   | Profiling tools and Profiling tools based on Simulation | 15  |

|    | 2.4    | Execu   | tion traces                                             | 17  |

|    | 2.5    | Execu   | tion trace analysis                                     | 18  |

|    | 2.6    | Concl   | usion                                                   | 19  |

| 3  | Bacl   | kgroun  | d and Related Work                                      | 21  |

|    | 3.1    | Profili | ng Tools                                                | 21  |

|    |        | 3.1.1   | Software Based Profiling                                | 22  |

|    |        | 3.1.2   | Hardware Based Profiling                                | 24  |

|    |        |         |                                                         |     |

|   |                          | 3.1.3 FPG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | A Based Profiling                                                                                                                                                                                                                                                                           | 25                                                                   |

|---|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

|   | 3.2                      | Related Wo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | rk in Contention and Scalability Bottlenecks Discovery                                                                                                                                                                                                                                      | 25                                                                   |

|   |                          | 3.2.1 Con                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | tention Discovery                                                                                                                                                                                                                                                                           | 25                                                                   |

|   |                          | 3.2.2 Scal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ability Bottlenecks Discovery                                                                                                                                                                                                                                                               | 26                                                                   |

|   | 3.3                      | Positioning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Relative To Existing Profiling Tools                                                                                                                                                                                                                                                        | 27                                                                   |

|   | 3.4                      | Traces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                             | 28                                                                   |

|   |                          | 3.4.1 Exec                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | rution Traces Representation                                                                                                                                                                                                                                                                | 29                                                                   |

|   |                          | 3.4.2 Dea                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ing with the Large Size of Traces                                                                                                                                                                                                                                                           | 29                                                                   |

|   | 3.5                      | Multi-Threa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ided Programs Analysis based on Traces                                                                                                                                                                                                                                                      | 31                                                                   |

|   | 3.6                      | Data Minin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | g                                                                                                                                                                                                                                                                                           | 31                                                                   |

|   |                          | 3.6.1 Freq                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | uent Pattern Mining                                                                                                                                                                                                                                                                         | 32                                                                   |

|   | 3.7                      | Traces Anal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ysis Using Data Mining                                                                                                                                                                                                                                                                      | 35                                                                   |

|   |                          | 3.7.1 High                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | n level analysis                                                                                                                                                                                                                                                                            | 35                                                                   |

|   |                          | 3.7.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | .1 Software Analysis                                                                                                                                                                                                                                                                        | 35                                                                   |

|   |                          | 3.7.2 Low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | level analysis                                                                                                                                                                                                                                                                              | 37                                                                   |

|   |                          | 3.7.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2.1 Hardware Analysis                                                                                                                                                                                                                                                                       | 37                                                                   |

|   |                          | 3.7.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2.2 Software Analysis                                                                                                                                                                                                                                                                       | 37                                                                   |

|   | 3.8                      | Summary .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                             | 38                                                                   |

|   | 3.9                      | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                             | 40                                                                   |

|   |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                             |                                                                      |

| 1 | New                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | filing Tools based on Data Mining                                                                                                                                                                                                                                                           | 41                                                                   |

| 4 |                          | MPSoC Pro                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 8                                                                                                                                                                                                                                                                                           | <b>41</b><br>41                                                      |

| 4 | <b>New</b> 4.1           | w <b>MPSoC Pro</b><br>Profiling Pr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ocess Overview                                                                                                                                                                                                                                                                              | 41                                                                   |