# A multicore emulator with a profiling infrastructure for Transactional Memory on FPGA

Nehir Sönmez

Department of Computer Architecture

Universitat Politècnica de Catalunya

A thesis submitted for the degree of Doctor of Philosophy in Computer Architecture July 15, 2012 To my mother Ülkü, my father Mustafa, my brother Rüzgar (who will do much better than me) and to all my friends that I also had to leave thousands of kilometers away.

# Acknowledgements

First of all, I have to thank my compatriot Don Oriol "Beekeeper" Arcas, without whom I would still be halfway. I am also very grateful to my advisors Dr. Osman S. Ünsal and Dr. Adrián Cristal for their endless help and support and giving me the freedom to let me work on what I was interested in. I am also thankful to Gökhan Sayilar and Philipp Kirchhofer for their valuable reinforcements as loyal Beekeepers. Throughout this research, I have been very fortunate to receive indispensible help and guidance from Dr. Tim Harris, Dr. Satnam Singh, Prof. Roberto Hexsel, Prof. Arvind and Prof. Mateo Valero.

I am also indebted to all my coleagues and friends (my second family) from Barcelona Supercomputing Center for their constant help and support during this research. Thanks to, in order of appearance: Srdjan Stipic, Sasa Tomic, Ferad Zyulkyarov, Oriol Prat, Paul Carpenter, Marco Galuzzi, Cristian Perfumo, Sutirtha Sanyal, Milos Milovanovic, Vladimir Gajinov, Gokcen Kestor, Petar Radojkovic, Vladimir Subotic, Vladimir Marjanovic, Vladimir Cakarevic, Maja Etinski, Enrique Vallejo, Chinmay Kulkarni, Azam Seyedi, Vasilis Karakostas, Gulay Yalcin, Vesna Smiljkovic, Adrià Armejach, Ibrahim Hur, Nebojsa Miletic, Javier Arias, Otto Pflucker, Milovan Djuric, Milan Stanic, Timothy Hayes, Ivan Ratkovic, Nikola Markovic, Daniel Nemirovsky, Ege Akpinar, Oscar Palomar and to all those that I might have forgotten to mention here. I also have to thank Asif I. Khan, Myron King and the rest of the CSG at MIT, as well as Miquel Pericas, Roberto Gioiosa, Ruben Titos and Paolo Meloni for their help and inspiration. Finally, thanks to my family for their patience and my friends for always being my best escape from work<sup>1</sup>.

<sup>&</sup>lt;sup>1</sup>The cover image is an 8-core BeeFarm design mapped on a Virtex-5 FPGA.

## Abstract

Since the first "core mitosis" in processor market in 2005, the multicore era has implied a drastic change in computer architecture. For many decades, Moore's law [95] had dictated that processor frequencies would be doubled every 18 months, which indeed caused a thousandfold increase during this time. Due to the memory wall and the power wall both hit, in order to offer higher performance, mainstream manufacturers were forced to place multiple processors on a silicon die, whereas before Moore's law had them pushing for higher-frequency massive superpipelined cores with high single-thread performance. This new direction demands better expressiveness of thread-level parallelism (TLP) and suitable ways of providing concurrency in programming a shared-memory Chip Multiprocessor (CMP). "Multicore architectures are an inflection point in mainstream software development because they force developers to write parallel programs" [3].

To program these larger and scalable parallel architectures, easier methods and abstractions for the efficient use of parallelism are essential. Traditional mechanisms such as lock-based thread synchronization, which are tricky to use and non-composable, are becoming less likely to survive. Consequently, the use of atomic instructions in lock-free Transactional Memory (TM) is a serious candidate to being the future of concurrent programming. TM is a programming paradigm for deadlock-free execution of parallel code that provides optimistic concurrency by executing transactions atomically: in an all-or-none manner. In case of a data inconsistency, a conflict causes the transaction to be aborted without committing its changes, and restarted as if no state change had occurred.

Nowadays, TM is being seen as one of the most promising ways of the parallel programming revolution, ensuring deadlock-free transactional code segments to run atomically, saving the programmer from explicitly dealing with locks. However, how TM guarantees such as atomicity and deadlock-freedom should be provided to the programmer has been a very active research topic for the last two decades.

While TM was so actively investigated, the past decade has also seen a shift of interests from using software simulation for evaluating new research ideas, to hardware emulation and prototyping in architectural design space exploration, using programmable FPGAs (ie. reconfigurable computing). Recent advances in multicore computer architecture research were being hindered by the inadequate performance of software-based instruction set simulators which led many researchers to consider the use of FPGA-based emulation. The primary reason for using an FPGA-based simulator is to achieve a significantly faster simulation speed for multicore architecture research, compared to the performance of software instruction set simulators. A secondary reason is that a system that uses only the FPGA fabric to model a multicore processor may have a higher degree of fidelity, since no functionality is implemented by a magical software routine.

This thesis attempts to bring together these two recent topics by presenting a flexible Transactional Memory environment on a prototype that is realized on FPGA fabric. For this, we develop a 16-core MIPS-compatible shared memory CMP system with Transactional Memory support, based on the Plasma open source soft processor core [113]. We present the design and implementation of the TMbox system, which features an emulation system of up to 16 MIPS soft processor cores interconnected with a bi-directional ring bus, running at 50 MHz on a Virtex5-155t FPGA of the BEE3 prototyping platform [36]. TMbox is a completely modifiable architecture implementing the first publicly-available multicore prototype with support for Hardware-, Software- and Hybrid TM. It was written in various common design

languages, and enables modifying the complete stack, down from the ISA, through the software toolchain, up to the optimized concurrent code. With our infrastructure, fast execution and quick performance evaluation can be made possible for studies in computer architecture.

Additionally, we build the first comprehensive infrastructure to profile Hybrid TM systems, an extensive visualization environment that enables examining complete transactional executions in detail. The profiling and visualization system of the TMbox enables in depth inspection of any kind of event, either triggered by the out-of-the-way profiling hardware or by a very low overhead software routine. It creates Paraver-like [19] multi-threaded traces, which help to correctly evaluate complex parallel executions as non-disruptively as possible. It is shown to aid in (i) porting programs to appropriately make use of Hybrid TM, (ii) discovering bottlenecks such as serialization, killer transactions and repetitive aborts, as well as (iii) depicting different program phases.

The result is a fast and flexible reconfigurable multicore architecture with a very useful profiling and visualization tool that serves as an efficient feedback mechanism. Although in this thesis the focus is on TM behavior, our infrastructure can be easily modified and extended to many other directions and to other topics of interest in novel computer architecture research.

# Contents

| 1 | Intr | roducti | on                                                                                                                                             | 1  |

|---|------|---------|------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   | 1.1  | Field-I | Programmable Gate Arrays                                                                                                                       | 1  |

|   |      | 1.1.1   | Intellectual Property Cores                                                                                                                    | 3  |

|   |      | 1.1.2   | Soft and Hard IP Cores                                                                                                                         | 4  |

|   |      | 1.1.3   | FPGA use for computer architecture investigation                                                                                               | 6  |

|   |      |         | 1.1.3.1 Current Overview                                                                                                                       | 7  |

|   |      |         | 1.1.3.2 Choice of architecture                                                                                                                 | 8  |

|   | 1.2  | Transa  | actional Memory                                                                                                                                | 9  |

|   |      | 1.2.1   | Flavors of TM                                                                                                                                  | 10 |

|   | 1.3  | Thesis  | Contributions                                                                                                                                  | 12 |

| 2 | Bee  | Farm S  | $\mathbf{STM}$                                                                                                                                 | 15 |

|   | 2.1  | Introd  | $ uction \ldots \ldots$ | 16 |

|   |      | 2.1.1   | Contributions                                                                                                                                  | 16 |

|   | 2.2  | The B   | eeFarm System                                                                                                                                  | 17 |

|   |      | 2.2.1   | The Plasma soft core                                                                                                                           | 17 |

|   |      | 2.2.2   | The Honeycomb core: Extending Plasma                                                                                                           | 18 |

|   |      | 2.2.3   | The BeeFarm System Architecture                                                                                                                | 22 |

|   |      | 2.2.4   | FPGA resource utilization                                                                                                                      | 24 |

|   |      | 2.2.5   | The BeeFarm Software Stack                                                                                                                     | 27 |

|   | 2.3  | Compa   | arison with SW Simulators                                                                                                                      | 29 |

|   |      | 2.3.1   | Methodology                                                                                                                                    | 29 |

|   |      | 2.3.2   | Single Core Performance                                                                                                                        | 30 |

|   |      | 2.3.3   | Multicore Performance using STM Benchmarks                                                                                                     | 30 |

|   | 2.4  | Relate  | d Work                                                                                                                                         | 33 |

| CONTENTS |

|----------|

|          |

|   | 2.5 | 5 BeeFarm Conclusions    |                                            |    |  |  |  |  |  |

|---|-----|--------------------------|--------------------------------------------|----|--|--|--|--|--|

|   |     | 2.5.1                    | Publications                               | 37 |  |  |  |  |  |

| 3 | TM  | box                      |                                            | 38 |  |  |  |  |  |

|   | 3.1 | Introd                   | luction                                    | 39 |  |  |  |  |  |

|   |     | 3.1.1                    | Contributions                              | 39 |  |  |  |  |  |

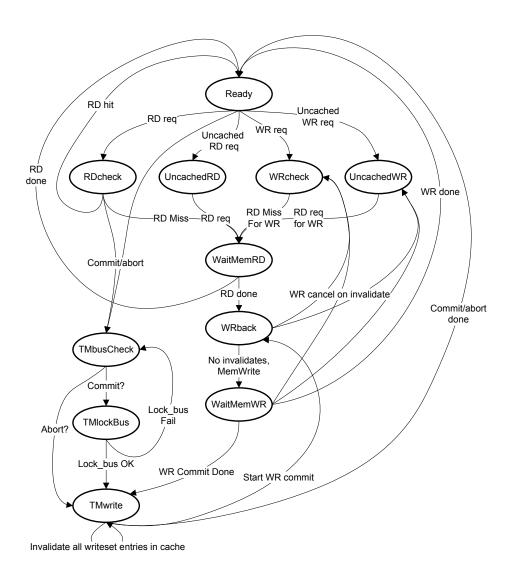

|   | 3.2 | Hybrie                   | dTM on TMbox                               | 40 |  |  |  |  |  |

|   |     | 3.2.1                    | The bi-directional ring bus                | 41 |  |  |  |  |  |

|   | 3.3 | Hybrid                   | d TM Support in TMbox                      | 43 |  |  |  |  |  |

|   |     | 3.3.1                    | Instruction Set Architecture Extensions    | 45 |  |  |  |  |  |

|   |     | 3.3.2                    | Bus Extensions                             | 46 |  |  |  |  |  |

|   |     | 3.3.3                    | Cache Extensions                           | 48 |  |  |  |  |  |

|   |     | 3.3.4                    | Area and Compilation Overheads             | 49 |  |  |  |  |  |

|   | 3.4 | Exper                    | imental Evaluation                         | 52 |  |  |  |  |  |

|   |     | 3.4.1                    | Architectural Benefits and Drawbacks       | 52 |  |  |  |  |  |

|   |     | 3.4.2                    | Experimental Results                       | 53 |  |  |  |  |  |

|   | 3.5 | Fitting                  | g inside the BEE3                          | 56 |  |  |  |  |  |

|   | 3.6 | Relate                   | Related Work                               |    |  |  |  |  |  |

|   | 3.7 | TMbo                     | ox Conclusions                             | 61 |  |  |  |  |  |

|   |     | 3.7.1                    | Publications                               | 61 |  |  |  |  |  |

| 4 | TM  | box P                    | rofiling                                   | 63 |  |  |  |  |  |

|   | 4.1 |                          | luction                                    | 64 |  |  |  |  |  |

|   |     | 4.1.1                    | -                                          | 64 |  |  |  |  |  |

|   | 4.2 | Profili                  | ing Design Objectives                      | 66 |  |  |  |  |  |

|   |     | 4.2.1                    | Network reuse                              | 67 |  |  |  |  |  |

|   | 4.3 | Profiling Infrastructure |                                            |    |  |  |  |  |  |

|   |     | 4.3.1                    | Event specification and generation         | 69 |  |  |  |  |  |

|   |     |                          | 4.3.1.1 HTM events                         | 69 |  |  |  |  |  |

|   |     |                          | 4.3.1.2 Extending the ISA with STM events  | 69 |  |  |  |  |  |

|   |     | 4.3.2                    | Event propagation on the bus               | 70 |  |  |  |  |  |

|   |     | 4.3.3                    | Transfer of events to the host             | 71 |  |  |  |  |  |

|   |     | 4.3.4                    | Post-processing and execution regeneration | 72 |  |  |  |  |  |

|   | 4.4 | Exper                    | imental Evaluation                         | 72 |  |  |  |  |  |

CONTENTS

|              |                         | 4.4.1   | Runtime     | and area overhead $\ \ldots \ \ldots \ \ldots \ \ldots \ \ldots$              | 74 |

|--------------|-------------------------|---------|-------------|-------------------------------------------------------------------------------|----|

|              |                         | 4.4.2   | Improven    | ment Opportunities                                                            | 76 |

|              |                         |         | 4.4.2.1     | Intruder-Eigenbench                                                           | 77 |

|              |                         |         | 4.4.2.2     | $\label{eq:continuity} Intruder-STAMP \ . \ . \ . \ . \ . \ . \ . \ . \ . \ $ | 78 |

|              | 4.5                     | Relate  | d Work .    |                                                                               | 82 |

|              | 4.6                     | TMbo    | x Profiling | g Conclusions                                                                 | 84 |

|              |                         | 4.6.1   | Publicati   | ons                                                                           | 85 |

| 5            | The                     | esis Co | nclusions   | 3                                                                             | 86 |

|              | 5.1                     | Experi  | ence and    | Trade-offs                                                                    | 86 |

|              | 5.2                     | Future  | Trends .    |                                                                               | 88 |

|              | 5.3                     | Thesis  | Conclusio   | ons                                                                           | 90 |

| A            | Hor                     | neycom  | b ISA       |                                                                               | 92 |

| В            | B Honeycomb Registers   |         |             |                                                                               |    |

| $\mathbf{C}$ | C List of Abbreviations |         |             |                                                                               | 97 |

# List of Figures

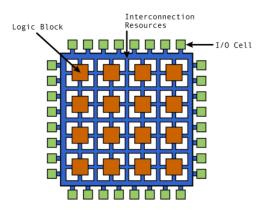

| 1.1  | A generic FPGA [140]                                                 | 2  |

|------|----------------------------------------------------------------------|----|

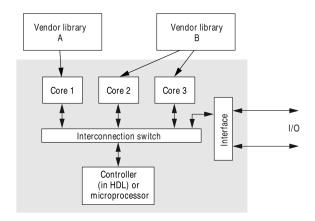

| 1.2  | Generic system-on-chip (SoC) architecture [89]                       | 4  |

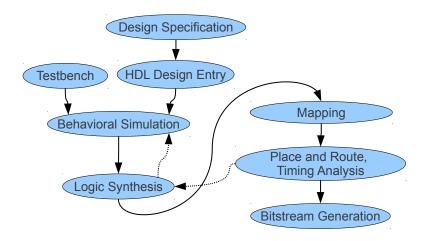

| 1.3  | FPGA Design Flow                                                     | 6  |

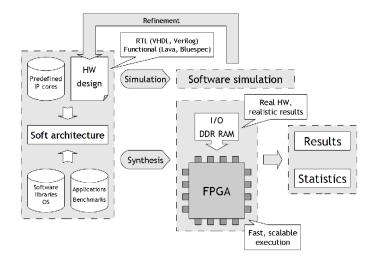

| 1.4  | An overview of FPGA emulation approach                               | 9  |

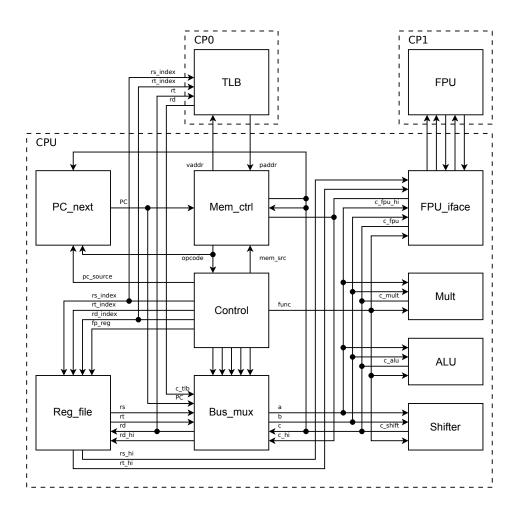

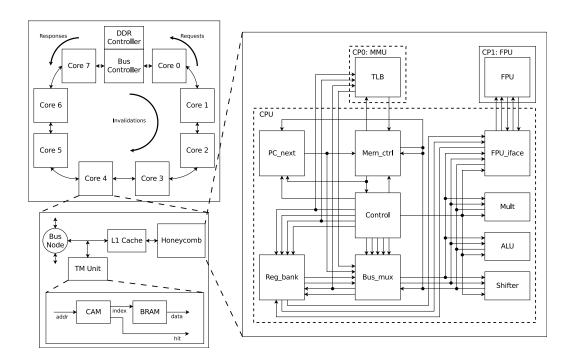

| 2.1  | The Honeycomb processor functional block diagram, with the Co-       |    |

|      | processor 0 (CP0) for virtual memory and exceptions and the Co-      |    |

|      | processor 1 (CP1) for floating point arithmetic                      | 20 |

| 2.2  | The Honeycomb pipeline                                               | 20 |

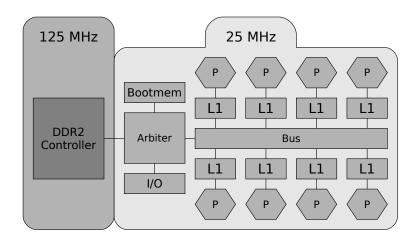

| 2.3  | The BeeFarm multiprocessor system                                    | 22 |

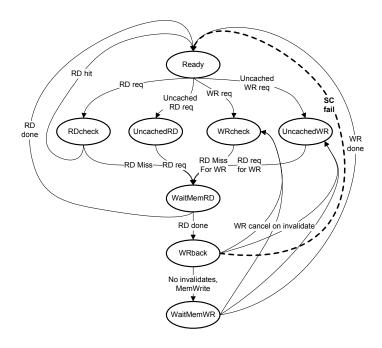

| 2.4  | Cache state diagram                                                  | 23 |

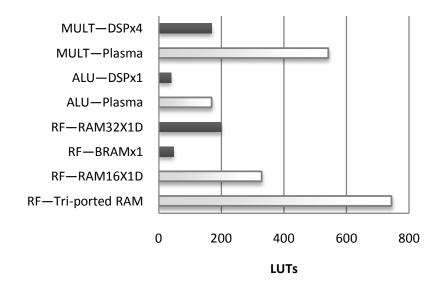

| 2.5  | Some of the available options (in 6-LUTs) to implement the Regis-    |    |

|      | ter File, the ALU and the Multiplier unit. The lighter bars indicate |    |

|      | the choices already present in the original Plasma design            | 25 |

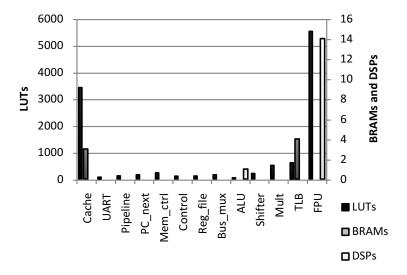

| 2.6  | LUT and BRAM usage of Honeycomb components                           | 25 |

| 2.7  | Compare and Swap using LL/SC in MIPS assembly                        | 28 |

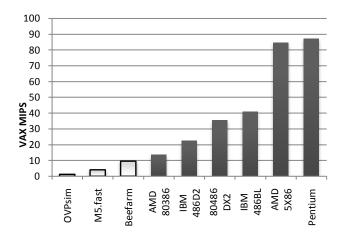

| 2.8  | Dhrystone 2.1 performance comparison of BeeFarm, M5 simulator        |    |

|      | and others.                                                          | 31 |

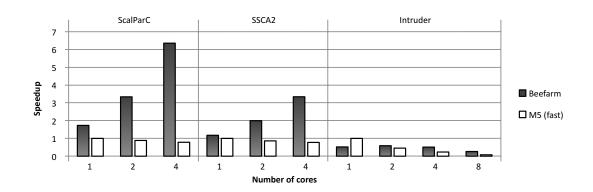

| 2.9  | BeeFarm vs M5: Speedups for ScalParC, SSCA2 and Intruder (nor-       |    |

|      | malized to single core M5 execution)                                 | 32 |

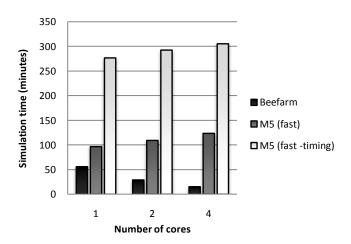

| 2.10 | BeeFarm vs M5: ScalParC simulation time                              | 33 |

| 3.1  | An 8-core TMbox infrastructure showing the ring bus, the TM          |    |

|      | Unit and the processor core                                          | 40 |

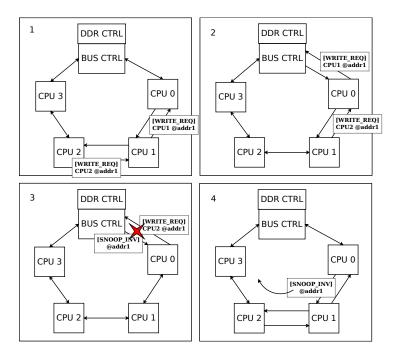

| 3.2  | An invalidation example on 4 cores                                   | 43 |

## LIST OF FIGURES

## LIST OF FIGURES

| 3.3  | TMbox MIPS assembly for atomic{a++} (NOPs and branch delay      |            |

|------|-----------------------------------------------------------------|------------|

|      | slots are not included for simplicity)                          | 46         |

| 3.4  | A commit example on 4 cores                                     | 47         |

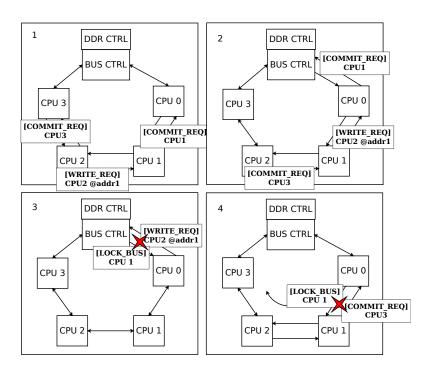

| 3.5  | Cache state diagram. Some transitions (LL/SC) are not shown for |            |

|      | visibility                                                      | 50         |

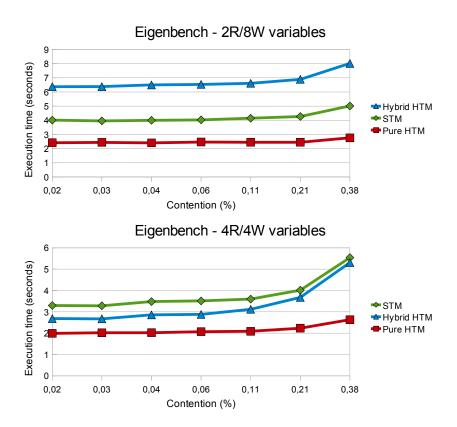

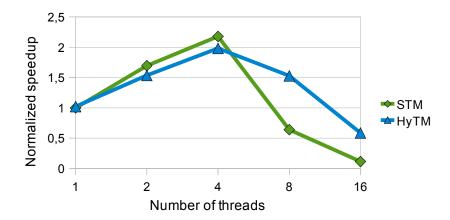

| 3.6  | Eigenbench performance on a 16 core TMbox                       | 55         |

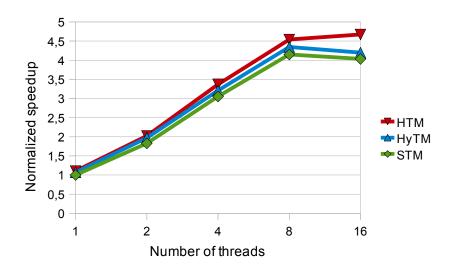

| 3.7  | SSCA2 benchmark performance on 1–16 cores                       | 55         |

| 3.8  | Intruder benchmark performance on 1–16 cores                    | 56         |

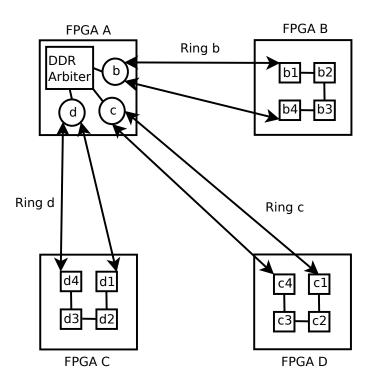

| 3.9  | A 4-FPGA setup for the BEE3                                     | 57         |

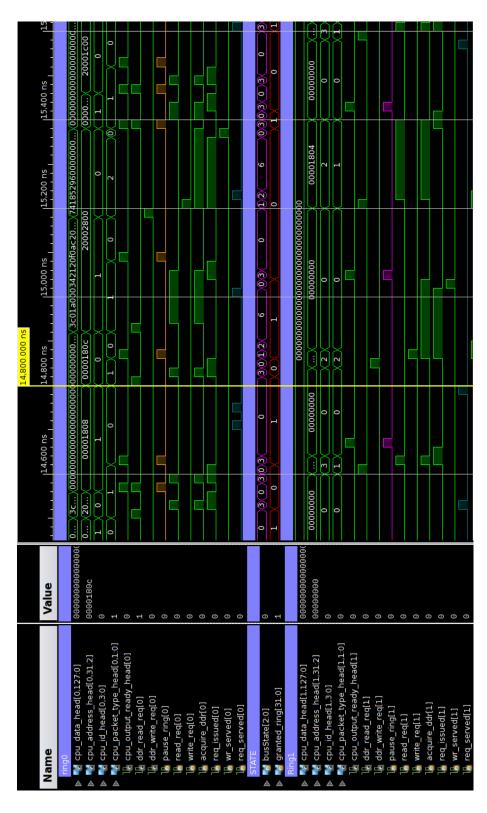

| 3.10 | A waveform simulation of a 2-ring arbiter                       | 58         |

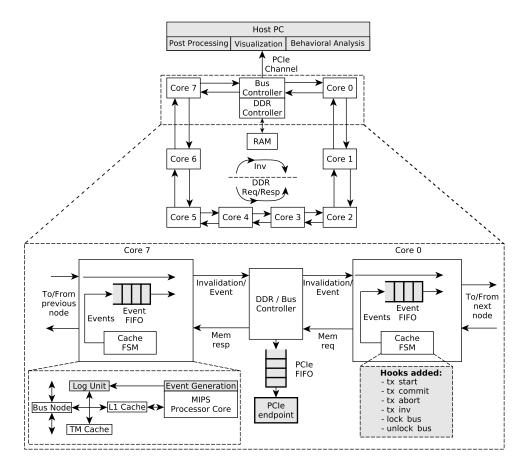

| 4.1  | An 8-core TMbox system block diagram and modifications made     |            |

|      | to enable profiling (shaded)                                    | 67         |

| 4.2  | Event format for the profiling packets                          | 68         |

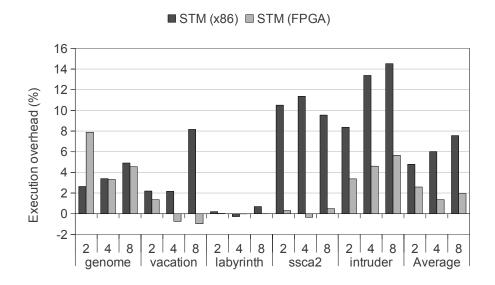

| 4.3  | Runtime overhead (%) for STM (x86) vs. STM (FPGA), in differ-   |            |

|      | ent core counts and applications. (avg. 20 runs)                | 74         |

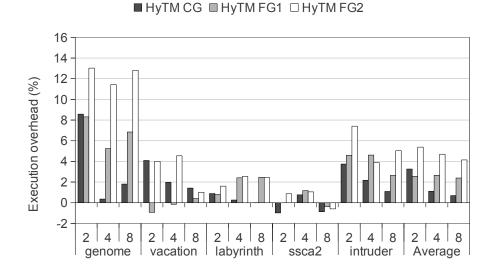

| 4.4  | Runtime overhead (%) for different Hybrid TM profiling levels,  |            |

|      | core counts and applications. (avg. 20 runs)                    | 75         |

| 4.5  | Improving Intruder-Eigenbench step by step from an STM-only     |            |

|      | version to utilize Hybrid TM appropriately                      | 77         |

| 4.6  | Example traces from the Intruder benchmark                      | <b>7</b> 9 |

# Chapter 1

# Introduction

# 1.1 Field-Programmable Gate Arrays

Field-Programmable Gate Arrays (FPGAs) are the first reconfigurable computing fabrics that were proposed half a century ago by Gerald Estrin as a "fixed-plus-variable structure computer" [41]. FPGAs are part of many of the systems and devices that we use today, such as automobiles, consumer electronics, home appliances, aircraft, or medical devices. Due to their ability to be reprogrammed, FPGAs were initially used for rapid prototyping of complex digital systems, and later on, as co-processors to speed up computations. In these implementations, compute-intensive tasks or user-defined instructions could be mapped on fabric in compile-time, [49; 50; 87; 136] or frequently used loops and tasks could get mapped on reconfigurable fabric dynamically at run-time [88].

Many researchers have often used FPGA technology to accelerate computing applications. The performance achieved by these configurable machines can be up to one or two orders of magnitude greater than general purpose processor-based counterparts. Configurable computers are proven to be the fastest in fields such as RSA decryption, DNA sequence matching, signal processing, microprocessor emulation and cryptography. Here, the fast and parallel execution on the reconfigurable chip has to compensate for the communication and transfer overheads that occur while bringing the data into the FPGA and sending it back. Generally, the more the data parallelism and the fewer the dependencies between the data, the better the performance of an FPGA implementation would be.

Figure 1.1: A generic FPGA [140].

A typical FPGA consists of an array of configurable logic blocks distributed across the entire chip in a large matrix of programmable interconnections, with programmable Input/Output (I/O) blocks at the periphery [132] (Figure 1.1). A logic block is an FPGA unit of area that includes N-input lookup tables (LUTs)<sup>1</sup> and D flip-flops. To simplify, an N-input LUT is a memory unit that, when programmed appropriately, can perform any Boolean function of up to N inputs [134], effectively emulating the logical functionality of the digital circuit. On the FPGA, configurable logic blocks (CLBs), which are made up of "slices" of LUTs are organized in an array and are used to build combinatorial and synchronous logic designs. Each CLB also has carry logic to help build fast, compact ripplecarry adders and multiplexers to help cascade multiple LUTs into larger logic structures. Each CLB element is tied to a switch matrix that accesses the general routing interconnection. Each Input/Output Block (IOB) in an FPGA offers input and output buffers and flip-flops. The programmable interconnect routes CLB/IOB output signals to other CLB/IOB inputs. It also provides low-skew clock lines that run around the FPGA, and horizontal long lines near each CLB. Although various ideas might get implemented differently by different vendors, the structures of common, non-specialized FPGAs are usually quite similar.

FPGAs are canonical examples of a configurable device. On an FPGA, all

<sup>&</sup>lt;sup>1</sup>Throughout this thesis, we utilize Xilinx terminology, since we worked with their generously donated FPGAs.

layers already exist on the chip and connections are either created or removed and the LUTs are programmed to implement the desired functionality with the aid of Computer-Aided Design (CAD) tools. The functional computation to be implemented on the hardware is defined by a set of configuration bits, generated by the CAD tools, which describes how each gate and wire (interconnect) should behave. Consequently, FPGAs can perform any computational task that fits in the machine's finite state and computational capacity that is set by its operational resources. In such, the designers themselves have the advantage of emulating an Integrated Circuit (IC) on top of a programmable chip. Although there are benefits like having a low NRE (Non-Recurring Engineering) cost and a lower time-to-market period compared to ASICs (Application-Specific Integrated Circuits), it also presents some drawbacks such as the medium-high cost per unit and slower performance than ASICs.

The term configurable is used to refer to architectures where the active circuitry can perform any of a number of different operations, but the functionality cannot be changed from cycle to cycle<sup>1</sup>. The register-rich nature of FPGA chips do not solely consist of an array of look-up tables and flip-flops, but also include on-chip RAM blocks and fast hardware DSP (Digital Signal Processing) units, making them perfect candidates for processor design.

## 1.1.1 Intellectual Property Cores

In order to keep production and development expenses as low as possible, while complying with various design constraints, embedded devices often come in the form of a System-on-Chip (SoC) in a core-based system design. A SoC is a concept that integrates the use of pre-designed, pre-verified, re-usable silicon circuitry, called Intellectual Property (IP) cores, to be used as building blocks for large and complex applications interconnected by a network-on-chip (NoC) [32] on an Integrated Circuit (IC). So, rather than developing every sub-system from scratch, the system is composed by integrating various cores with the re-use of previously deployed ones (Figure 1.2).

<sup>&</sup>lt;sup>1</sup>Although this is changing with new FPGAs that include static memories and 3D stacking technology [68].

Figure 1.2: Generic system-on-chip (SoC) architecture [89].

SoCs have altered the way commercial, off-the-shelf components are sold: as Intellectual Property (IP) cores, processor-level components with behavioral, structural, or physical descriptions, rather than actual Integrated Circuits. Examples of common IP cores range from a thousand-gate analog circuit blocks to memory controllers, peripheral devices such as MAC (Media Access Control), Ethernet, UART (Universal Asynchronous Receiver / Transmitter), or PCI (Peripheral Component Interconnect) bus controllers, to million-gate processor cores [31]. IP cores can be split into two main categories: soft and hard cores, as discussed next.

#### 1.1.2 Soft and Hard IP Cores

Although programmable logic saves development cost and time over increasingly complex ASIC designs, FPGAs have started becoming popular over the past two decades as the unit price has dropped and gate count per chip has reached numbers that allow for the implementation of more complex applications and soft cores. A soft core consists of a synthesizable HDL (Hardware Description Language) description that can be re-targeted to different semiconductor processes, rather than being a fixed part of the chip circuitry. HDLs such as VHDL (Very High Speed Integrated Circuit Hardware Description Language), Verilog, SystemC and Bluespec increase the range of options available to designers by

enabling hardware implementation with the flexibility that language-based design provides, allowing designers to implement efficient soft Intellectual Property cores.

Hard IP cores are physical descriptions that involve the implementation of a silicon-level circuit within the device fabric. A hard core includes layout and technology-dependent timing information and is ready to be included into a system. These components are products of the specific technology used, are proprietary IPs by definition, and are subject to patents and copyrights. Depending on the design constraints, the designer can use the already optimized and synthesized hard cores, or to comply with the constraints, adapt the soft (or firm) cores to specific limitations. Typical hard cores included in a modern FPGA may include DSP blocks, Block RAMs, or hard processor IPs.

Since soft cores do not target a specific technology, they are inherently more flexible in function and implementation than hard cores. On the other hand, hard core developers can afford to spend more time optimizing their implementations to be used in many designs. For a SoC that requires the highest performance in current process and design technology, a full-custom hard core is better at meeting these needs by using latches, dynamic logic, 3-state signals and custom memories. However, they are not flexible or parameterizable like soft cores and do not accept modifications and customizations.

All of the benefits and characteristics of soft IP cores are realized by soft processor cores implemented within FPGA components. Two proprietary soft processor core examples are the Xilinx Microblaze and Altera Nios II [66; 71]. Both soft processor cores are 32-bit Harvard bus architecture (separate data and instruction memories) Reduced Instruction Set Computer (RISC) systems with 32 general-purpose registers. Many open source soft processor cores, which accept modifications have also been made available, especially in the last decade [2; 47; 52; 106; 113].

The typical design flow facilitated by CAD tools includes the synthesis of the Register Transfer Level (RTL) code written in an HDL into logical gates, later its translation for the selected technology, mapping of units and their placement onto the FPGA, the routing of all signals and finally the generation of the bitstream to be loaded on the FPGA (Figure 1.3).

Figure 1.3: FPGA Design Flow

#### 1.1.3 FPGA use for computer architecture investigation

With the always-increasing frequencies of typical uni-processors, the investigation of architectural schemes have been realized by software-based microarchitectural simulators, such as Simplescalar, PTLsim, Simics or M5 [12; 114]. These sequential simulators are expressive and it's relatively easy and fast to make changes to the system in a high-level environment. However, little effort has been made to parallelize or accelerate these programs which turn out to be slow to simultaneously simulate the multiple cores of a typical multiprocessor of the current era of chip multi-cores. This has caused the computer architecture community to consider performing emulations on reconfigurable fabrics as an alternative to using software-based simulations.

The low performance of legacy architectural simulator software for investigating new generation Chip Multi-Processor (CMP) architectures has been addressed in a few ways: the development of new parallel simulators [92], parallelization efforts for sequential simulators [114], acceleration using GPUs [110], and prototype/emulation implementations on reconfigurable fabric [26; 34]. FPGAs were proven successful in accelerating simulations working in concert with a host computer [22], as well as FPGA-only multi-core MPSoC implementations [125].

#### 1.1.3.1 Current Overview

The inherent advantages of using today's FPGA systems are clear: multiple hard/soft processor cores, multi-ported SRAM blocks, high-speed DSP units, and more configurable logic cells each generation on a rapidly growing process technology. Another opportunity comes from the already-tested Intellectual Property (IP) cores. There are various open-source synthesizable Register Transfer Level (RTL) models of various x86, MIPS, PowerPC, SPARC architectures that can run at up to a hundred MHz. These models can already include detailed specifications for multi-level cache hierarchy, out-of-order issue, speculative execution, Floating Point Units (FPU), and branch prediction. These are excellent resources to start building a credible multicore system for any kind of architectural research. Furthermore, various IPs for incorporating UART, SD, Floating Point cores, Ethernet or DDR controllers are also easily accessible [104].

FPGAs can be good alternatives to implement complex computer circuitry. On-chip Block RAM (BRAM) resources on an FPGA which are optionally preinitialized or with built-in ECC can be used in many configurations, such as (i) RAM or SRAM; for implementing direct mapped or set associative on-chip instruction/data cache, cache tags, cache coherence bits, snoop tags, register file, multiple contexts, branch target caches, return address caches or branch history tables, (ii) CAM; for reservation stations, out-of-order instruction issue/retire queues or fully associative TLBs, (iii) ROM; for bootloader or lookup tables, or (iv) asynchronous FIFO; to buffer data between processors, peripherals or coprocessors[51]. BRAM capacity, which does not occupy general-purpose Look-Up Table (LUT) space or flip-flops could be used to implement debug support tables for breakpoint address/value registers, count registers or memory access history. The available dedicated on-chip DSP blocks can be cascaded to form large multipliers/dividers or FPUs. Complete architectural inspection of the memory and processor subsystems can be performed using statistics counters embedded in the FPGAs without any overhead.

Many vendors provide large FPGA programming boards and high-end FPGA prototyping boxes with preferential pricing for academia. FPGAs have already been proposed to teach computer architecture courses for simple designs as well

as for more advanced topics [52; 91; 127]. Nowadays, it is possible to prototype large architectures in a full-system environment, which allows for faster and more productive hardware research than software simulation. Over the past decade, the RAMP project has already established a well-accepted community vision and various novel FPGA architecture designs [22; 26; 34; 81; 98; 125]. It is also known that processor vendors make use of FPGAs to better investigate their new designs in a rapid way [117; 135].

#### 1.1.3.2 Choice of architecture

Although FPGA-based multiprocessor emulation has received considerable attention in the recent years, the experience and tradeoffs of building such an infrastructure from the already-available resources and IP cores has not yet been considered in depth. Indeed, most of the infrastructures developed were either (i) written from scratch using higher level HDLs, such as Bluespec [67], (ii) using hard cores such as PowerPC, or (iii) using proprietary cores such as the Microblaze [38].

One direction is to choose a well-known architecture like MIPS and enjoy the commonly-available toolchains and library support, as we demonstrate throughout this thesis. Although supporting a minimal OS might be acceptable depending on the objectives, a deeper software stack could have many advantages by providing memory protection, performing scheduling, aiding debugging, file system support, etc. Full OS support can be accomplished either by highly detailed design implementations on the FPGA, or with hybrid approaches, where the core functionality is retained in FPGA hardware and it cooperates with a nearby host computer that can serve (i) system calls and exceptions, (ii) infrequent or slow running instructions and/or (iii) I/O operations, instead of implementing everything inside the FPGA [26]. There also exist commercial simulator accelerators like Palladium and automated simulator parallelization efforts that take advantage of reconfigurable technology [108]. In this thesis, we model the entire multiprocessor system on FPGA logic (Figure 1.4).

This flexible experimental systems platform on an FPGA offers a multiprocessor System-on-Chip (SoC) implementation that: (i) can be configured to integrate

Figure 1.4: An overview of FPGA emulation approach.

various Instruction Set Architecture (ISA) extensions and hardware organizations, (ii) fit and scale well for large designs of tens of processor cores, (iii) offer high enough performance to run full benchmarks in acceptable timeframes, (iv) run at least some minimal OS and (v) must provide with credible results. The applications that run on real hardware should provide the researcher with fast, wide-ranging exploration of HW/SW options and head-to-head comparisons to determine the strade-offs between different implementations [6].

# 1.2 Transactional Memory

For the exchange of data among multiple threads, shared memory is a common and convenient IPC (Inter-Process Communication) paradigm to provide all processors with a single view of memory. However, some form of synchronization between the processes that are storing and fetching information to and from the shared memory region is required. For enforcing limits on access to a shared resource, locking is the most commonly used synchronization mechanism. Locking is simple to use, however it has many problems: Simple coarse-grained locking does not scale well, while more sophisticated fine-grained locking risks introducing deadlocks, priority inversion or data races. Many scalable libraries written using

fine-grained locks cannot be easily composed in a way that retains scalability and avoids deadlock and data races.

Some 30 years ago, Lomet proposed an idea to support atomic operations in programming languages, similar to what had already existed in database systems [86]. Nowadays, based on this idea, the proposal that has drawn the most attention for programming shared-memory CMPs has been the use of Transactional Memory (TM), an attractive paradigm for the deadlock-free execution of parallel code without using locks [64; 80; 115].

TM-based algorithms can be expected to run slower than ad-hoc non-blocking algorithms or fine-grained lock based code, but TM is as easy as using coarse-grained locks: one simply brackets the critical section that needs to be atomic! Using atomic blocks in TM simplify writing concurrent programs because when a block of code is marked, the compiler and the runtime system ensure that operations within the block appear atomic to the rest of the system [59]. TM schemes attempt to optimistically interleave and to execute all transactions in parallel. A transaction is committed if and only if any other transaction has not modified the section of the memory which its execution depended on. As a consequence, the programmer no longer needs to worry about manual locking, deadlocks, race conditions or priority inversion [60].

#### 1.2.1 Flavors of TM

The Transactional Memory approach allows programmers to specify transaction sequences that are executed atomically, by encapsulating critical sections inside the atomic{} construct. TM implementations have to ensure that all operations within the block either complete as a whole, or automatically rollback as if they were never run. The underlying TM mechanism has to automatically detect data inconsistencies and aborts and restarts one or more transactions. If there are no inconsistencies, all the side effects of a transaction have to be committed as a whole.

Transactional Memory can be implemented in dedicated hardware (HTM) [20; 96], which is fast but resource-bounded, while it might require changes to

the caches and the Instruction Set Architecture (ISA). On the other hand, Software TM (STM) [4; 44] can be flexible, run on off-the-shelf hardware, albeit at the expense of lower performance. To have the best of two worlds, there are intermediate Hybrid TM (HyTM) proposals where transactions first attempt to run on hardware, but are backed off to software when hardware resources are exceeded [33]. Another approach is Hardware-assisted STM (HaSTM), which by architectural means aims to accelerate a TM implementation that is controlled by software. By leaving the policy to software, different experimentations on contention management, deadlock and livelock avoidance, data granularity and nesting can be accomplished. HaSTM does not implement any TM semantics in hardware, but provides mechanisms that accelerate an STM, which may also have uses beyond TM.In transactional applications, a conflict occurs when two simultaneously running transactions access the same memory location and one of the accesses is a write. A TM implementation may detect conflicts either eagerly or lazily. In the eager approach, conflicts are detected immediately as soon as they occur, whereas in lazy conflict detection, they are detected at a later time of the transactional execution (e.g. at commit time).

Transactional write operations in a TM system can be buffered (lazy versioning) or done in-place (eager versioning). With buffered writes, the speculative values of the memory references are stored in a thread local buffer/cache, and only written to memory when the transaction successfully commits. With inplace writes, the TM system logs all original values for rolling back in case of an abort, and writes the speculative values to memory. Therefore, in buffered update TMs, commits are more expensive, whereas in eager update TMs, aborts tend to be more costly.

Furthermore, a TM implementation may also differ based on the granularity at which conflicts are detected. Typically TM implementations detect conflicts at word, cache line or object granularity. The choice of the granularity involves design and performance tradeoffs. Word and cache line granularity are more suitable for HTMs and non-garbage-collected low-level programming languages such as C. Per-object conflict detection is more suitable for managed STMs in object-oriented languages such as Java or C#.

Conflict resolution determines which transaction(s) are aborted at what point in the execution when a conflict is detected. Conflict resolution may follow immediately after a conflict is detected (i.e. eager conflict resolution) or at a later moment of the transactional execution (i.e. lazy conflict resolution), for instance at commit time. Once it is time to resolve the conflict, the TM system, or a contention manager [118] may choose to block the transactional execution until the other conflicting transaction commits or aborts, or delaying and assigning a back-off time for the abort. In case of a cyclical dependency between two or more waiting transactions, the TM system might choose to abort all transactions to avoid deadlock [58].

In the past two decades, there have been a flurry of proposals of different flavors of semantics and implementations, such as the first Transactional Memory system proposed in hardware (HTM) [64], that of a software-only implementation [119], hybrid approaches [33; 83], those that propose hardware conflict resolution, hardware signatures to track read and write sets, those that timestamp transactions, realize hardware-assisted TM, other hybrid mechanisms, and many more. Today, TM is still a topic of very active investigation.

## 1.3 Thesis Contributions

FPGA emulation/prototyping of multicores has been receiving a lot of research attention. Recently, FPGA emulators and prototypes of many complex architectures of various ISAs have been proposed. However, only a few of these are on research on Transactional Memory. Furthermore, only a few implement/scale to an interestingly-large number of processor cores. Additionally, the majority of these proposals are based on proprietary or hard processor cores, which imply rigid pipelines that can prevent the researcher from modifying the ISA and the microarchitecture of the system.

Therefore in this thesis, we choose a new approach: We reuse an already existing MIPS [76] processor core called Plasma [113] and we modify and extend it to build a full multiprocessor system designed for multicore research on Software-, Hardware- and Hybrid Transactional Memory. More particularly, the contributions of this thesis are made up of three parts:

- Beefarm STM: Reports on our experience of designing and building an eight core cache-coherent shared-memory multiprocessor system on FPGA called BeeFarm, to help investigate support for Software Transactional Memory [54; 96; 129]. Towards this goal, we have successfully ported an STM library and ran TM applications on the BeeFarm.

- TMbox HybridTM: Features an MPSoC built to explore trade-offs in multicore design space and to evaluate recent parallel programming proposals such as Hybrid Transactional Memory. For this work, we evaluate a 16-core Hybrid TM implementation based on the TinySTM-ASF proposal on a Virtex-5 FPGA [73] and we accelerate three benchmarks written to investigate TM trade-offs. Our flexible system, comprised of MIPS R3000 compatible cores interconnected by a ring network, is easily modifiable to study different architecture, library or Operating System extensions. TM-box is the first implementation on FPGA in the literature with support for Sofware-, Hardware- and Hybrid TM.

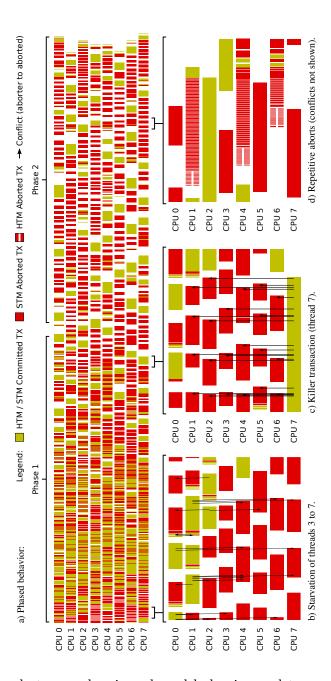

- TMbox Profiling: Multi-core prototyping additionally presents a good opportunity for establishing low overhead and detailed profiling and visualization in order to study new research topics. In this direction, we design and implement a low execution, low area overhead profiling mechanism and a visualization tool for observing Transactional Memory behaviors on FPGA. We demonstrate the usefulness of such detailed lightweight examination of SW/HW transactional behavior to appropriately port applications to Hybrid TM and to accelerate them. Thanks to its ability to rapidly run and visualize full multi-threaded benchmarks, the TMbox with profiling support can point out pathologies such as repetitive aborts, killer transactions and starvation and to depict the phased behavior in full benchmarks with very low instrumentation overheads.

In this thesis, we explain how we devised a flexible infrastructure to run and to inspect Transactional Memory systems and applications in a rapid way using reconfigurable computing technology. As a result, TMbox is the only publicly available multicore prototype with extensive support for Hardware-, Softwareand Hybrid Transactional Memory and a low overhead profiler and visualizer for analyzing extremely detailed behavior of multi-threaded transactional programs. Chapter 2 presents the design and implementation of the Beefarm STM, an initial implementation with Software TM support. Chapter 3 contains a description of the TMbox Hybrid TM implementation and Chapter 4 shows the low overhead profiling and visualization infrastructure designed for TMbox. A discussion of tradeoffs of using reconfigurable computing and future trends are in Chapter 5, as well as thesis conclusions. Appendices 1, 2 and 3 contain the list of TMbox instructions, registers, and a table of abbreviations, respectively.

The work in this thesis was highly facilitated by three other students. UPC PhD student Oriol Arcas helped in implementing the MIPS CoProcessor0, cache modifications, the software stack, the TM Unit, the profiling infrastructure, and others that are described in detail in his Master's thesis [9]. Additionally, Gokhan Sayilar (from Sabanci University, now a PhD student at UT-Austin) helped us to implement an efficient FPU for the BeeFarm. Philipp Kirchhofer from the Karlsruhe Institute of Technology implemented the HTM part of the profiling infrastructure, as well as the initial profiling data analysis software [79]. Besides the mentors Osman S. Unsal, Adrian Cristal and Mateo Valero, we received precious support from Ibrahim Hur (BSC, now at Intel) and from Satnam Singh (MSRC, now at Google), our FPGA guru.

# Chapter 2

# The BeeFarm STM platform

## Abstract

This chapter reports on our experience of designing and building an eight core cache-coherent shared-memory multiprocessor system on FPGA called BeeFarm, to help investigate support for Transactional Memory [54; 96; 129]. Towards this goal, we have ported TinySTM [44], a lightweight and efficient word-based STM library implementation in C and C++, and ran TM benchmarks on the BeeFarm. Our approach is through taking a MIPS-based open-source uniprocessor soft core, Plasma, and extending it to obtain the BeeFarm infrastructure for FPGA-based multiprocessor emulation. We discuss various design tradeoffs and we demonstrate superior scalability through experimental results compared to a traditional software instruction set simulator, the M5 [12].

## 2.1 Introduction

In this chapter, we take a popular MIPS uniprocessor core called Plasma [113] and we extend it to build a full multiprocessor system designed for multicore research for Software Transactional Memory. For this, we also provide our infrastructure with compiler tools to support a programming environment rich enough to conduct experiments on Transactional Memory workloads. An hypothesis we wish to investigate is the belief that an FPGA-based emulator for multicore systems will have better scalability compared to software-based instruction set simulators. We check this hypothesis using our flexible BeeFarm infrastructure with designs ranging from 1 to 8 cores and obtaining performance speedups of up to 8x, comparing to the M5 simulator.

#### 2.1.1 Contributions

The key contributions of this chapter are:

- A description of extending the Plasma open source processor core for implementing the Honeycomb processor.

- From the Honeycomb processor cores, building the cache coherent BeeFarm multiprocessor system on the BEE3 platform [36].

- Experimental results for three benchmarks investigating support for Transactional Memory and an analysis of the performance and scalability of software simulators versus hardware emulation/prototyping through using the BeeFarm system.

The next section explains how the Plasma core was modified to design the Honeycomb core, and later to build the BeeFarm soft multicore, and the software stack that supports running STM applications. Section 2.3 compares executions of three STM benchmarks on our platform with the M5 software simulator. Section 2.4 discusses other related research, while Section 2.5 concludes this chapter.

# 2.2 The BeeFarm System

The BeeFarm system is a bus-based multiprocessor implementation of the well-known MIPS R3000 architecture, inspired by the Plasma soft processor core [113], designed for running on the BEE3 hardware prototyping platform. Particularly, the objective is to reuse a complete and small soft processor IP core, and to be able to fit as many cache coherent cores as possible into a TM-capable multicore emulator. RISC architectures with simpler pipelines can be customized more easily and require less FPGA resources compared to a deeply-pipelined superscalar processor, so they are more appropriate to be integrated into a larger multiprocessor SoC. For this reason, using large, multithreaded soft cores like OpenSPARC (64-bit) [31] were omitted. We chose to use the Plasma in this work, mainly since (i) it is based on the popular MIPS architecture [94], (ii) it is complete and (iii) it has a relatively small area footprint on the FPGA. Using the Leon 3 (32-bit SPARC core) [1] and the miniMIPS [55] as the main processor soft IP core were the other two acceptable options with similar advantages and disadvantages.

## 2.2.1 The Plasma soft core

The synthesizable MIPS R2000-compatible soft processor core Plasma was designed for embedded systems and written in VHDL [113]. It features a configurable 2-3 stage pipeline (no hazards), a 4 KB direct-mapped L1 cache, and can address up to 64 MB of RAM. It was designed to run at a clock speed of 25 MHz, and includes UART and Ethernet cores. It also has its own real-time operating system (RTOS) with some support for tasks, semaphores, mutexes, message queues, timers, heaps etc.

In a typical ALU instruction, the program counter (PC) passes the current instruction address to the memory control unit, which fetches the 32-bit opcode from cache or from memory, when needed. Cache accesses pause the CPU and can take various cycles in case of a miss. In the next stage, the opcode received is passed to the control unit that converts it to a 60-bit control word and forwards it to the appropriate entities through a central multiplexer (bus-mux).

#### 2.2.2 The Honeycomb core: Extending Plasma

Although the original Plasma core is suitable for working with diverse research topics, it has some limitations that makes it unsuitable as the processing element of the BeeFarm system. These include the lack of virtual memory support (implemented in MIPS as the Coprocessor 0), precise exceptions and synchronization mechanisms. Furthermore, there is no support for floating point arithmetic (MIPS Coprocessor 1), multiprocessing capabilities or coherent caches.

The successor architecture to the MIPS R2000 ISA is the MIPS R3000, featuring a 5-stage pipeline and a co-processor for managing virtual memory. Later, the MIPS R4000 developed implemented a 64-bit pipeline. To be more resource efficient, we did not opt for a 64-bit datapath, however, we believe that this will be a necessity for future multicore emulators that can make use of bigger and more advanced FPGAs. Therefore, to build the Honeycomb core, we effectively upgraded the MIPS R2000-compatible Plasma to a MIPS R3000-compatible soft processor core. For enabling this, we made several changes to the Plasma soft core:

- Design and implementation of two coprocessors: CP0 that provides support for virtual memory using a Translation Lookaside Buffer (TLB), and CP1 encapsulating an FPU,

- Optimization of the cores to make better use of the resources on our Virtex-5 FPGAs, where it can run at twice the frequency (50 MHz),

- Memory architecture modifications to enable virtual memory addressing for 4 GB and caches of 8 KB,

- Implementation of extra instructions to better support exceptions and thread synchronization (load-linked and store-conditional),

- Added coherent caches and developed a parameterizable system bus that accesses off-chip RAM through a DDR2 memory controller [126],

- Development of system libraries for memory allocation, I/O and string functions, as in [123].

On the Honeycomb processor (Figure 2.1) instructions and data words are 32-bit wide, and data can be accessed in bytes, half words (2 bytes) or words (4 bytes). The processor is implemented in a 3-stage pipeline with an optional stage for data access instructions (Figure 2.2).

The Honeycomb core was designed to run on the BEE3 hardware prototyping platform which contains four Virtex5-155T FPGAs, each one with 24,320 slices of 6-LUTs, 212 BRAMs, and 128 DSP units. Four DDR2 memories are controlled by each FPGA, organized in two channels of up to 4 GB each. The DDR2 controller [126] manages one of the two channels per FPGA using a small processor called TC5 (also used in Beehive V5 [127]). It performs calibration and serves requests, and occupies a small portion (around 2%) of the Virtex5-155T FPGA. Using one controller provides sequential consistency for our multicore described in this work, since there is only one address bus, and reads are blocking and stall the processor pipeline.

A new processor model (-march=honeycomb) was added by modifying GCC and GAS (the GNU Assembler). This new ISA includes all MIPS R3000 instructions with the addition of RFE (Return from Exception), Load Linked and Store Conditional. All GNU tools (GAS, ld, objdump) were modified to work with these new instructions.

Coprocessor 0: The MMU: In order to support virtual memory, precise exceptions and operating modes, we implemented a MIPS R3000-compatible 64-entry TLB (called CP0), effectively upgrading the core from an R2000 to an R3000, which we named Honeycomb. The CP0 provides memory management and exception handling intercepting the memory control unit datapath. Each entry contains two values: The 20 highest bits of the physical address, which replace the corresponding ones in the virtual address, and the 20 highest bits of the virtual address, which are used as a matching pattern. More details can be found in [9].

There exist various approaches to implement an efficient Content Addressable Memory (CAM) on FPGAs, with configurable read/write access times, resource usage, and the technology utilized, where general-purpose LUTs or on-chip block memories can be used [16]. The use of LUT logic is inappropriate for medium and large CAMs, and the time-critical nature of this unit makes multi-cycle access

Figure 2.1: The Honeycomb processor functional block diagram, with the Coprocessor 0 (CP0) for virtual memory and exceptions and the Coprocessor 1 (CP1) for floating point arithmetic.

Figure 2.2: The Honeycomb pipeline.

inappropriate, since it must translate addresses each cycle on our design. Only the approach based on RAM blocks fitted the requirements: This unit was implemented with on-chip BRAM configured as a 64-entry CAM and a small 64-entry LUT-RAM [70]. Virtual patterns that are stored in the CAM give access to an index to the RAM that contains the physical value. It is controlled by a half-cycle shifted clock that performs the translation in the middle of the memory access stage, so it does not require a dedicated pipeline stage. This 6-bit deep by 20-bit wide CAM occupies four BRAMs and 263 LUTs.

Coprocessor 1: Double-Precision FPU: Another lack of the original Plasma is floating point arithmetic support, an integral part of a modern computing system architecture. The MIPS 3010 FPU implemented in Coprocessor 1 (CP1) can perform IEEE 754-compatible single and double precision floating point operations. It was designed using Xilinx Coregen library cores, takes up 5520 LUTs and 14 DSP units, performing FP operations and conversions in variable number of cycles (4–59). We used only 4 of the 6 integer-double-float conversion cores to save space. This optional MIPS CP1 has 32x32-bit FP registers and a parallel pipeline. The integer register file was extended to include FP registers implemented as LUT-RAM. For double precision, two registers represent the low and high part of the 64-bit number and the register file was replicated to allow 64-bit (double precision) read/write access each cycle [116].

Memory Map and ISA Extensions: We redesigned the memory subsystem that could originally only map 1 MB of RAM, to use up to 4 GB with configurable memory segments for the stack, bootloader, cache, debug registers, performance counters and memory-mapped I/O ports. Furthermore, we extended the instruction set of the Honeycomb with three extra instructions borrowed from the MIPS R4000 ISA: ERET (Exception RETurn), to implement more precise exception returns that avoid branch slot issues. We also provided with LL (Load-Linked) and SC (Store Conditional) instructions, which provide hardware support for synchronization mechanisms such as Compare and Swap (CAS) or Fetch and Add (FAA). This is essential for providing Software TM support, as we detail in Section 2.2.5.

Honeycomb's 8 KB write-through L1 cache design that supports the MSI cache coherency [63] (unified data and instructions) in 16-byte, direct-mapped

Figure 2.3: The BeeFarm multiprocessor system.

blocks. It uses 2 BRAMs for storing data and another two for the cache tags. The BRAM's dual-port access enables serving both CPU and bus requests in a single cycle. Reads and writes are blocking, and coherence is guaranteed by the snoopy cache invalidation protocol that was implemented. 2.4

# 2.2.3 The BeeFarm System Architecture

The caches designed for the BeeFarm are interconnected with a central splitbus controlled by an arbiter, as shown in Figure 2.3. The caches snoop on the system bus to invalidate entries that match the current write address, where write accesses are processed in an absolute order. This protocol can perform invalidations as soon as the writes are issued on the write FIFOs of the DDR. This serves to find an adequate balance between efficiency and resource usage. More complex caches that demand a higher resource usage would make it difficult to implement a large multiprocessor given the limited resources present on chip.

The bus arbiter implemented interfaces the FIFOs of the DDR controller, serving requests from all processors following a round-robin scheme. The boot-up code is stored in a BRAM connected to the arbiter and mapped to a configurable region of the address space. I/O ports are also mapped, and the lowest 8 KB of physical memory give access to the cache memory, becoming a useful resource

Figure 2.4: Cache state diagram.

during boot-up when the DDR is not yet initialized. Furthermore, the cache can be used as the stack thanks to the uncached execution mode of MIPS. Such direct access to cache memory is useful for debugging, letting privileged software to read and even modify the contents of the cache.

The arbiter, the bus, caches and processors can run at a quarter/fifth of the DDR frequency (25 – 31.25 MHz), the CPU's shallow pipeline being the main cause of this upper bound on the clock. Although the bus and cache frequencies could be pushed to work at 125 MHz or at an intermediate frequency, it was not desirable to decouple this subsystem from the processor, because partitioning the system in many clock domains can generate tougher timing constraints, extra use of BRAM to implement asynchronous FIFOs or extra circuitry to prepare signals that cross different clock domains. Further optimizations to the Honeycomb are certainly possible by clocking faster all special on-chip units and including such extra circuitry.

Finally, around eight Honeycomb cores (without an FPU) could form a Bee-Farm system on one Virtex5-155T FPGA, although the system bus can become a

bottleneck not only during system execution, but also when placing and routing the design.

#### 2.2.4 FPGA resource utilization

One of the objectives of the design is to fit the maximum number of cores while supporting a reasonable number of features. The components have to be designed to save the limited LUTs and conservatively use BRAMs and DSPs, both to allow for more functionality to be added later on, and to reduce the system complexity. This is necessary to keep the frequency of the clock high and thus the performance, meanwhile reducing the synthesis and place and route time. The Honeycomb core without an FPU occupies 5,712 LUTs on a Virtex-5 FPGA including the ALU, MULT/DIV and Shifter units, the coherent L1 cache, the TLB and the UART controller, a comparable size to the Microblaze core [71]. Figure 2.5 shows the LUT occupation of the CPU's components. The functional blocks on the Honeycomb can be categorized in three groups:

- Compute-intensive (DSP): Eg. ALU, MULT/DIV, Shifter, FPU. These are good candidates to take advantage of hard DSP units and in the Plasma core originally fit the third category, since the ALU is a combinatorial circuit, while the MUL/DIV/Shifter units take 32 cycles to iterate and compute. The ALU can be mapped directly onto a DSP while a MULT can be generated with Xilinx Coregen in a 35x35 multiplier, utilizing an acceptable 4 DSP and 160 LUTs. The shifter can also benefit from these 4 DSP thanks to dynamic opmodes, however, a 32-bit divider can take anywhere between 1,100 LUTs to 14 DSP units: The optimal way of combining all these operations to have a minimal design is not yet clear, and would be interesting to look into as future work.

- Memory-intensive (BRAM/LUT-RAM): Eg. Reg\_Bank, Cache, TLB. The TLB is designed in a CAM, and the cache and the cache tags in BRAMs. For the Reg\_Bank, the original Plasma design selects between instantiating 4-LUT distributed RAMs (RAM16), behaviorally describing a tri-ported RAM, or using a BRAM. The use of BRAM is inefficient since

Figure 2.5: Some of the available options (in 6-LUTs) to implement the Register File, the ALU and the Multiplier unit. The lighter bars indicate the choices already present in the original Plasma design.

Figure 2.6: LUT and BRAM usage of Honeycomb components.

it would use a tiny portion of a large structure, and the tri-ported RAM infers too many LUTs, as seen in Figure 2.5. When distributed LUT-RAM is inferred, each 6-LUT can incorporate a 32-bit register on the Virtex-5, enabling two reads and one write operation per cycle, assuming that one of the read addresses is the write address. There are a few options to enable two reads and a write to distinct addresses on each CPU cycle: (i) to do the accesses in two cycles on one register file, using one of the input addresses for reading or writing when needed, (ii) to clock the register file twice as fast and do the reads and writes separately, or (iii) to duplicate the register file to be able to do two reads and a write on distinct addresses on the same cycle. Although we currently use the third approach, our design accepts either configuration. Other groups have proposed latency insensitive circuits which save resources by accessing the register file in multiple cycles [133].

• LUT-intensive: Eg. implementing irregular case/if structures or state machines: PC\_next, Mem\_ctrl, control, bus\_mux, TLB logic, system bus and cache coherency logic. This category demands a high LUT utilization; one striking result in Figure 2.5 is that providing cache coherency occupies roughly half of the LUT resources used by the Honeycomb. Such complex state machines do not map well on reconfigurable fabric, however synthesis results show that the Honeycomb core, when a similar speed-grade Virtex-6 chip is selected, performs 43.7% faster than the Virtex-5 version, so such irregular behavioral descriptions can still be expected to perform faster as the FPGA technology advances.

Unlike the cache coherence protocol and the shared system bus that map poorly, compute-intensive units and the register bank are good matches for distributed memory that use 6-LUTs, although it is not possible to perform a 3-ported access in a single-cycle. BRAMs and DSP units must be used carefully, to better match the underlying FPGA architecture. Regular units that match a compute-and-store template rather than complex state machines must be fashioned. In general, we believe that caches are a bottleneck and a good research topic for multicore prototyping. There is little capacity for larger or multi-level

| L1 Cache Size | slice Regs | slice LUTs | BRAMs |

|---------------|------------|------------|-------|

| 4 KB          | 19         | 26         | 3     |

| 8 KB          | 40         | 47         | 4     |

| 16 KB         | 75         | 80         | 6     |

Table 2.1: Area occupied by L1 caches of different sizes

caches on our FPGA, and it would not be easy at all to provide high levels of cache associativity.

There are a total of 212 Block RAMs on our Virtex 5 FPGAs. The DDR controller utilizes 5, the Bootmem uses 2, and the TC5 tiny processor needs another 3. Figure 2.1 shows the distribution of FPGA resources for different L1 cache sizes. For supporting hardware transactions later on the next chapter, we also want to reserve BRAMs for implementing a TM cache. As a rule of thumb, we don't want to use up more than 50% of the hard FPGA units. As the number of cores go up, placement and routing would be more difficult to perform. Therefore, we choose to use caches of 8 KB each, using 4 BRAMs per core for implementing the L1 cache. The cache design is parameterizable, and accepts other configurations.

#### 2.2.5 The BeeFarm Software Stack

Since our system can not directly utilize the GNU C standard library libC and we want to avoid the complexities of running a full Linux with all system calls implemented, we developed a set of system libraries called BeeLibC for memory allocation, I/O and string functions.

Unlike the BeeFarm, many groups exercise falling back to a host machine or a nearby on-chip hard processor core to process system calls and exceptions [26; 125]. A MIPS cross-compiler with GCC 4.3.2 and Binutils 2.19 is used to compile the programs with statically linked libraries. The cores initially boot up from the read-only Bootmem that initializes the cores and the stack and then loads the RTOS kernel code into memory either from the serial port or from the SD card onto the DDR. The SD card support, which was implemented by software

```

$CAS_SC_FAIL:

$v0, 0($a0)

11

$v0, $a1, $CAS_END

bne

nop

$t0, $a2

move

$t0, 0($a0)

sc

$t0, $CAS_SC_FAIL

beqz

nop

$CAS_END:

$ra

jr

```

Figure 2.7: Compare and Swap using LL/SC in MIPS assembly

bit-banging can transfer roughly a MB of data per minute. Alternatively, an SD soft core can be incorporated for even faster data transfer. Although Ethernet might be another fast option, we deemed the additional complexity too potentially risky while developing the initial design. It might also be useful to port an RTOS with multiprocessing and threading support such as the eCos [40] or RTEMS [99] to multicore emulators. We currently let all cores initialize and wait on a barrier, which is set by CPU0. Another option that reserves the CPU0 only for I/O is also implemented.

TinySTM is an STM library that differentiates mainly by its time-based algorithm and lock-based design from other STMs, such as TL2 and Intel STM [4; 39]. It compiles and runs on 32 or 64-bit x86 architectures, using the atomic\_ops library to implement atomic operations. We modified it to support Compare and Swap (CAS) and Fetch and Add (FAA) primitives for the MIPS architecture through the use of LL/SC instructions borrowed from the MIPS R4000 architecture [25]. Figure 2.7 shows hos LL/SC instructions can be composed to form a Compare and Swap operation.

## 2.3 Comparison with SW Simulators

#### 2.3.1 Methodology

The multiprocessor system presented in this work was designed to speed up multiprocessor architecture research, to be faster, more reliable and more scalable than software-based simulators. Its primary objective is to execute real applications in less time than popular full-system simulators, although it is not possible to run as fast as the actual ASIC. Therefore our tests:

- Measure the performance of the simulator platform, NOT the performance of the system simulated. What is relevant is not the simulated processor's speed, but the time that the researcher has to wait for the results and its reliability.

- Abstract away from library or OS implementation details, so that external functions like system calls do not significantly affect the results of the benchmark.

- Can be easily ported to different architectures, avoiding architecture-specific implementations like synchronization primitives.

- Pay special attention to the scalability of the emulation, a key weakness

of software multiprocessor simulators. Our emulations are inherently not

affected by the number of processors in other ways than the usual and

expected from a reliable simulator (memory bandwidth, traffic contention,

cache protocols).

M5 [12] is a well-known and easily modifiable "full-system simulator" that can simulate an arbitrary number of Alpha processors with complex architectural details like caches and buses. We believe that despite the fact that MIPS and Alpha are distinct architectures, this can be a fair comparison to measure and compare the scalability of the software simulator and the BeeFarm multicore emulator. Both architectures are 32-bit RISC, featuring 32 registers, operate on fixed-size opcodes and the only operations that access the memory are load and store. We used a configuration that models a DEC Tsunami system with an

in-order, 5-stage pipeline Alpha 21164 CPU, with 64-entry data TLB, 48-entry instruction TLB, 2-cycle L1 cache access and 10-cycle L2 cache access times [48].

To obtain exact measurements of the execution time of the M5, we added a precise 64-bit hardware cycle counter to measure the total execution time which we compare against BeeFarm hardware counters. We executed the test in the M5 compiled with the maximum optimizations and with the minimum timing and profiling options (fast mode), and additionally for ScalParC in a slower profiling mode with timing. The compilers used to obtain the test programs for the Bee-Farm and the M5 both use GCC version 4.2, compiled with the -O2 optimization level or -O3 when possible on an Intel Xeon E5520 server with 2x quad-core processors running at 2.26 GHz with 64 GB of DDR3 RAM and 8 MB of L3 cache memory.

We use the Xilinx ISIM and the Mentor Graphics ModelSim for offline functional or post Place and Route (PnR) simulation. Real-time debugging on Xilinx chips is done with Xilinx Chipscope Pro [69], for which we apply various triggers to read our hardware debug registers. All results were obtained using 64-bit Xilinx ISE 12.2 running on RHEL5.

#### 2.3.2 Single Core Performance

The Honeycomb core, despite of its smaller cache, performs in comparable speeds to some older well-known architectures running the Dhrystone 2.1 benchmark [138], as seen on Figure 2.8. The results are in VAX MIPS, the unit of measurement of Dhrystone performance. In particular, Honeycomb has a better performance than M5 when the total execution time of the simulator (wall clock time) is compared. OVPsim is a fast simulator that is used to accelerate the development of embedded software, simulating the MIPS32 architecture [103]. Both software simulators were run on the 2x4-core server previously described.

### 2.3.3 Multicore Performance using STM Benchmarks

To test multicore performance with STM benchmarks running on the BeeFarm, we have run ScalParC, a scalable TM benchmark from RMS-TM [77], as well as

Figure 2.8: Dhrystone 2.1 performance comparison of BeeFarm, M5 simulator and others.

Intruder and SSCA2 TM benchmarks from STAMP [93], which are very commonly used for TM research. We modified ScalParC with explicit calls to use the TinySTM library. In our experiments, ScalParC was run with a dataset with 125K records, 32 attributes and 2 classes, SSCA2 was run with problem scale 13 and Intruder with 1024 flows.

The results that are normalized to the single-core M5 executions show that while the BeeFarm can scale in a near-linear way, the M5 simulator fails to scale and the performance rapidly degrades as the core counts are increased. Figure 2.9 shows that the gap opens with more cores and with only four, the BeeFarm with FPU just needs fifteen minutes to run the ScalParC benchmark, an eightfold difference. A single core ScalParC run on the BeeFarm took around 9 hours when a soft-float FP library is used [62] and a little more than an hour when an FPU is used (not shown).

The scalability of our hardware is more obvious when the abort ratio between the transactions are low and little work is repeated, so the benchmark itself is scalable. SSCA2 also benefits from the inherent parallelism of the FPGA infrastructure and the good performance of the FPU: The two-core BeeFarm takes about half of the runtime of the M5 and it shows better scalability with more cores. In this sense our FPU which takes roughly the space of a single CPU core

Figure 2.9: BeeFarm vs M5: Speedups for ScalParC, SSCA2 and Intruder (normalized to single core M5 execution).

is clearly a worthy investment for the case of this particular benchmark. Other available hardware kernels such as a quicksort core [17] would be a very useful accelerator for this particular benchmark, and such specialized cores/execution kernels could further push the advantages of multicore emulation on reconfigurable platforms.

Intruder is a very high abort rate integer-only benchmark that scales poorly, and this can be seen on both M5 and BeeFarm results. It performs worse on the BeeFarm for single processor runs, however for more than two cores, it runs faster than the M5, whose scalability again degrades rapidly. We are able to run Intruder with 8 CPUs because this design does not use the FPU.

The results of the STM benchmarks show that our system exhibits the expected behavior, scaling well with more cores and thus reducing the time that the researcher has to wait to obtain results. In other words, the simulated time and the simulation time are the same on our FPGA-based multicore emulator. The software-based simulator suffers from performance degradation when more cores are simulated and fails to scale. As seen on the Intruder example, certain configurations (eg. without an FPU) for a small number of cores could result in software simulators performing faster than FPGA devices. Mature simulators that take advantage of the superior host resources could still have advantages over FPGA emulators for simulations of a small number of cores.

Figure 2.10: BeeFarm vs M5: ScalParC simulation time.

#### 2.4 Related Work

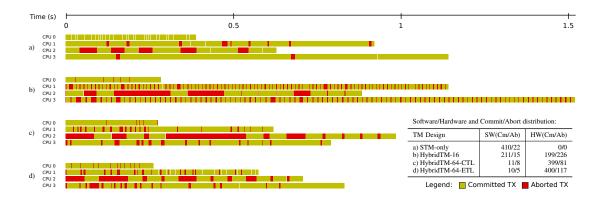

Some classic works using MIPS and FPGAs include the GARP reconfigurable array which is used as an accelerator to a MIPS processor [61], and DartMIPS an early paper on implementing the MIPS R3000 architecture on an FPGA [42]. On a similar vein, RPM features a multiprocessor design with SPARC processors coupled with cache and memory controllers that are implemented on FPGA [102].