## LOW POWER ANALOG TO DIGITAL CONVERTERS IN ADVANCED CMOS

## **TECHNOLOGY NODES**

## A Dissertation

by

## **QIYUAN LIU**

## Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

Chair of Committee, Committee Members,

Head of Department,

Jose Silva-Martinez Sebastian Hoyos Jiang Hu Jay Porter Miroslav M. Begovic

May 2017

Major Subject: Electrical Engineering

Copyright 2017 Qiyuan Liu

#### ABSTRACT

The dissertation presents system and circuit solutions to improve the power efficiency and address high-speed design issues of ADCs in advanced CMOS technologies.

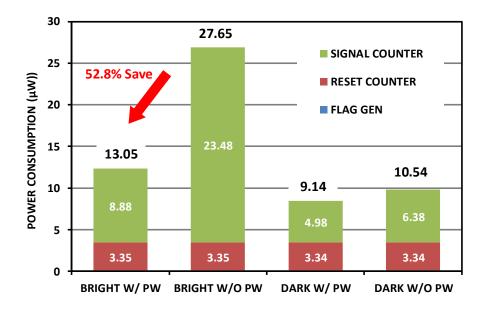

For image sensor applications, a high-performance digitizer prototype based on column-parallel single-slope ADC (SS-ADC) topology for readout of a back-illuminated 3D-stacked CMOS image sensor is presented. To address the high power consumption issue in high-speed digital counters, a passing window (PW) based hybrid counter topology is proposed. To address the high column FPN under bright illumination conditions, a double auto-zeroing (AZ) scheme is proposed. The proposed techniques are experimentally verified in a prototype chip designed and fabricated in the TSMC 40 nm low-power CMOS process. The PW technique saves 52.8% of power consumption in the hybrid digital counters. Dark/bright column fixed pattern noise (FPN) of 0.0024%/0.028% is achieved employing the proposed double AZ technique for digital correlated double sampling (CDS). A single-column digitizer consumes total power of 66.8µW and occupies an area of 5.4 µm x 610 µm.

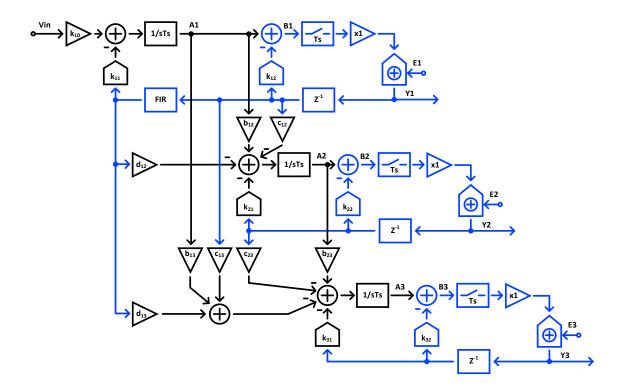

For mobile/wireless receiver applications, this dissertation presents a low-power wide-bandwidth multistage noise-shaping (MASH) continuous-time delta-sigma modulator (CT- $\Delta\Sigma$ M) employing finite impulse response (FIR) digital-to-analog converters (DACs) and encoder-embedded loop-unrolling (EELU) quantizers. The proposed MASH 1-1-1 topology is a cascade of three single-loop first-order CT- $\Delta\Sigma$ M

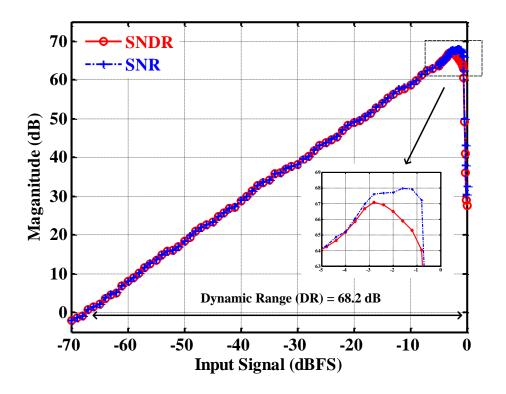

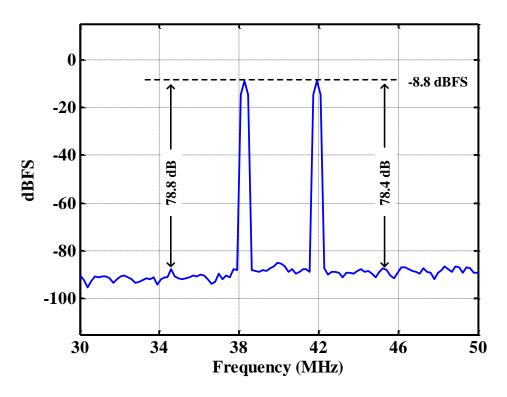

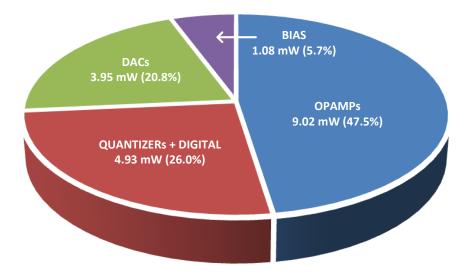

stages, each of which consists of an active-RC integrator, a current-steering DAC, and an EELU quantizer. An FIR filter in the main 1.5-bit DAC improves the modulator's jitter sensitivity performance. FIR's effect on the noise transfer function (NTF) of the modulator is compensated in the digital domain thanks to the MASH topology. Instead of employing a conventional analog direct feedback path, a 1.5-bit EELU quantizer based on multiplexing comparator outputs is proposed; this approach is suitable for highspeed operation together with power and area benefits. Fabricated in a 40-nm low-power CMOS technology, the modulator's prototype achieves a 67.3 dB of signal-to-noise and distortion ratio (SNDR), 68 dB of signal-to-noise ratio (SNR), and 68.2 dB of dynamic range (DR) within 50.5 MHz of bandwidth (BW), while consuming 19 mW of total power (P). The proposed modulator features 161.5 dB of figure-of-merit (FOM), defined as FOM = SNDR + 10 log10 (BW/P).

# DEDICATION

To my parents and Xin

#### ACKNOWLEDGEMENTS

First of all, I would like to express my sincere appreciation to my advisor, Dr. Jose Silva-Martinez. Without his guidance, my research and dissertation will not be possible. During my research and study, he is always patient and supportive when I have problems. I have learnt from him, not just limited to technical aspect, but also from his personality. He is an extremely nice person and also a wonderful friend.

I would like to thank Dr. Sebastian Hoyos, Dr. Jiang Hu, Dr. Jay Porter, and Dr. Shuguang Cui for their critical comments on my research. I would also like to thank Dr. Edgar Sanchez-Sinencio, Dr. Karman Entesari, and Dr. Samuel Palermo as instructors of my classes.

I would like to thank Alexander Edward, Carlos Briseno-Vidrios, Haoyu Qian as reliable teammates and great friends collaborating on research projects. I would like to thank my colleagues and friends at Texas A&M for their help and support. Many thanks also go to the former Analog & Mixed Signal Center (AMSC) alumni who provide many valuable suggestions and help on my career.

I would like to thank Mario Caresosa and Jun Cao for guiding me during my intern experience at Broadcom. I would like to thank Martin Kinyua and Eric G. Soenen for mentoring me during the internship at TSMC.

Last but not least, I would like to express deep appreciation to my family for their support. I cannot thank more to my parents for bringing me to the world and shaping me to who I am today.

#### CONTRIBUTORS AND FUNDING SOURCES

### Contributors

This work was supervised by a dissertation committee consisting of Professors Jose Silva-Martinez, Sebastian Hoyos, and Jiang Hu of the Department of Electrical and Computer Engineering and Professor Jay Porter of the Department of Engineering Technology and Industrial Distribution.

The work for the Section III of the dissertation was completed by the student, in collaboration with Alexander Edward, under the advisement of Dr. Jose Silva-Martinez of the Department of Electrical and Computer Engineering together with Dr. Martin Kinyua and Dr. Eric G. Soenen from TSMC Technology, Inc.

The work for the Section IV of the dissertation was completed by the student, in collaboration with Alexander Edward and Dadian Zhou, under the advisement of Dr. Jose Silva-Martinez of the Department of Electrical and Computer Engineering.

The rest part of the dissertation was completed by the student, under the advisement of Dr. Jose Silva-Martinez of the Department of Electrical and Computer Engineering.

## **Funding Sources**

Graduate study was supported by Texas Instrument Excellence Fellowship and Broadcom Corporation Fellowship.

# TABLE OF CONTENTS

| Page |

|------|

|------|

| ABSTRAC              | Τ                                                                                            | ii   |

|----------------------|----------------------------------------------------------------------------------------------|------|

| DEDICATI             | ON                                                                                           | iv   |

| ACKNOW               | LEDGEMENTS                                                                                   | v    |

| CONTRIBU             | JTORS AND FUNDING SOURCES                                                                    | vi   |

| TABLE OF             | CONTENTS                                                                                     | vii  |

| LIST OF FI           | GURES                                                                                        | ix   |

| LIST OF TA           | ABLES                                                                                        | xiii |

| I. INTROD            | UCTION                                                                                       | 1    |

| 1.1.<br>1.2.<br>1.3. | Motivation<br>Research Contribution<br>Dissertaton Organization                              | 3    |

| II. ANALO            | G-TO-DIGITAL CONVERTER TOPOLOGIES                                                            | 6    |

| 2.1.                 | Introduction                                                                                 |      |

| 2.2.                 | Nyquist ADCs                                                                                 |      |

| 2.3.                 | Oversample ADCs                                                                              |      |

| 2.4.                 | Hybrid ADCs                                                                                  |      |

| 2.5.                 | Conclusion                                                                                   | 31   |

| CMOS                 | POWER DIGITIZER FOR BACK-ILLUMINATED 3D-STACKED IMAGE SENSOR READOUT WITH PASSING WINDOW AND |      |

| DOUBI                | LE AUTO-ZEROING TECHNIQUES                                                                   | 33   |

| 3.1.                 | Introduction                                                                                 | 33   |

| 3.2.                 | Sensor Architecture                                                                          |      |

| 3.3.                 | Proposed Techniques                                                                          | 38   |

| 3.4.                 | Circuit Implementation                                                                       |      |

| 3.5.                 | Measurement Results                                                                          |      |

| 3.6.                 | Conclusion                                                                                   | 65   |

| IV. A 50-M | IHZ BW 67.3-DB SNDR MASH 1-1-1 CT $\Delta\Sigma$ MODULATOR WITH |     |

|------------|-----------------------------------------------------------------|-----|

| FIR DA     | C AND EELU QUANTIZER IN 40-NM CMOS                              | 66  |

|            |                                                                 |     |

| 4.1.       | Introduction                                                    | 66  |

| 4.2.       | Modulator Architecture                                          | 69  |

| 4.3.       | Circuit Implementation                                          | 79  |

|            | Measurement Results                                             |     |

| 4.5.       | Conclusion                                                      | 98  |

|            |                                                                 |     |

| V. CONCL   | USION                                                           | 100 |

|            |                                                                 |     |

| REFEREN    | CES                                                             | 101 |

# LIST OF FIGURES

|                                                                                                                                                                               | Page |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Fig. 1.1 Resolution and bandwidth requirements for different applications                                                                                                     | 2    |

| Fig. 2.1. Quantization noise ADC.                                                                                                                                             | 6    |

| Fig. 2.2. Sloping ADC architecture                                                                                                                                            | 7    |

| Fig. 2.3. Pulse-position modulation sloping ADC architecture (adapted from [1])                                                                                               | 8    |

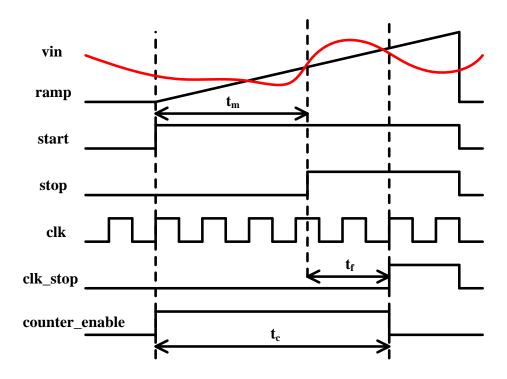

| Fig. 2.4. Pulse-position modulation sloping ADC timing scheme (adapted from [1]).                                                                                             | 9    |

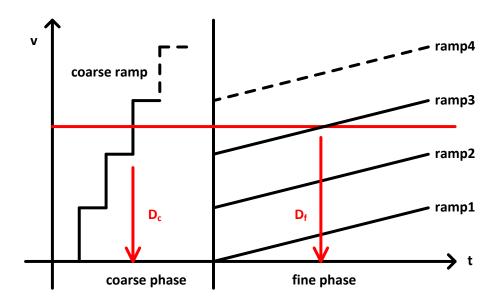

| Fig. 2.5. Multi-ramp single-slope ADC timing scheme (adapted from [2])                                                                                                        | 9    |

| Fig. 2.6. Flash ADC architecture                                                                                                                                              | 11   |

| Fig. 2.7. SAR ADC architecture.                                                                                                                                               | 12   |

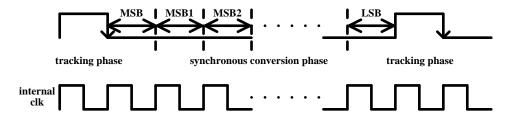

| Fig. 2.8. Synchronous conversion for SAR ADCs (adapted from [3]).                                                                                                             | 13   |

| Fig. 2.9. Asynchronous conversion for SAR ADCs (adapted from [3])                                                                                                             | 13   |

| Fig. 2.10. Monotonic capacitor switching procedure (adapted from [4])                                                                                                         | 14   |

| Fig. 2.11. Time-interleaved SAR ADC (adapted from [5]).                                                                                                                       | 15   |

| Fig. 2.12. Pipeline ADC architecture.                                                                                                                                         | 16   |

| Fig. 2.13. Time-interleaved pipeline ADC architecture (adapted from [8])                                                                                                      | 18   |

| Fig. 2.14. Delta-Sigma ADC                                                                                                                                                    | 19   |

| Fig. 2.15. Quantization noise: (a) oversample ADC; (b) delta-sigma ADC                                                                                                        | 19   |

| Fig. 2.16. Block diagram of second-order DT- $\Delta\Sigma$ M                                                                                                                 | 21   |

| Fig. 2.17. Second-order DT- $\Delta\Sigma M$ implementation                                                                                                                   | 22   |

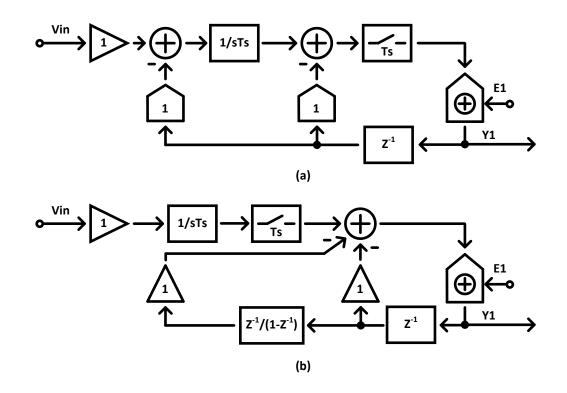

| Fig. 2.18. Block diagram of first order $CT-\Delta\Sigma M$ : (a) time-domain model; (b) linearized time-domain model splitting signal feedforward and output feedback paths. | 23   |

| Fig. 2.19. Pipelined SAR ADC (adapted from [11])                                                                                                                                                                                                                                                                                                                                                       | 25 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig. 2.20. Noise-shaping SAR using FIR and IIR filter (adapted from [12])                                                                                                                                                                                                                                                                                                                              | 26 |

| Fig. 2.21. Noise and mismatch shaping SAR with segmented DAC (adapted from [13]).                                                                                                                                                                                                                                                                                                                      | 27 |

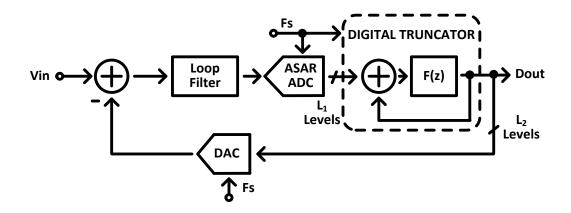

| Fig. 2.22. A-synchronous SAR based CT- $\Delta\Sigma$ M with digital delta-sigma truncator (adapted from [14]).                                                                                                                                                                                                                                                                                        | 28 |

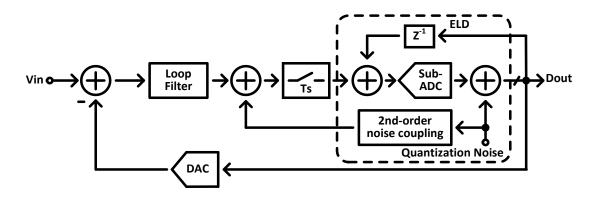

| Fig. 2.23. SAR-assisted CT- $\Delta\Sigma M$ with 2 <sup>nd</sup> -order noise shaping (adapted from [15]).                                                                                                                                                                                                                                                                                            | 28 |

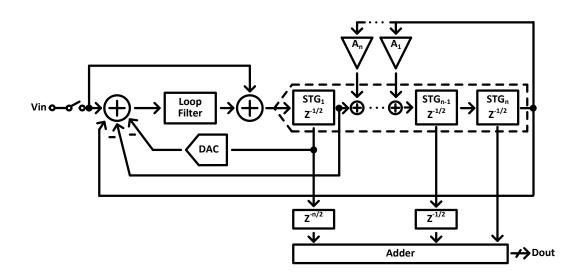

| Fig. 2.24. Hybrid delta-sigma/pipelined (HDSP) modulator (adapted from [16])                                                                                                                                                                                                                                                                                                                           | 29 |

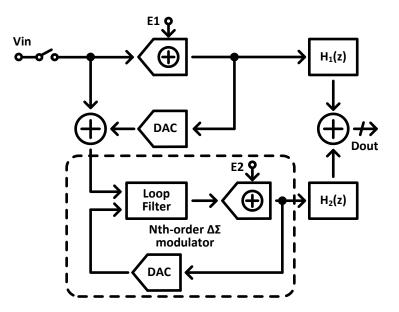

| Fig. 2.25. The 0-N MASH $\Delta\Sigma$ M concept (adapted from [17]).                                                                                                                                                                                                                                                                                                                                  | 30 |

| Fig. 2.26. The 1-0 MASH $\Delta\Sigma M$ with nonlinear memory error calibration (adapted from [18]).                                                                                                                                                                                                                                                                                                  | 31 |

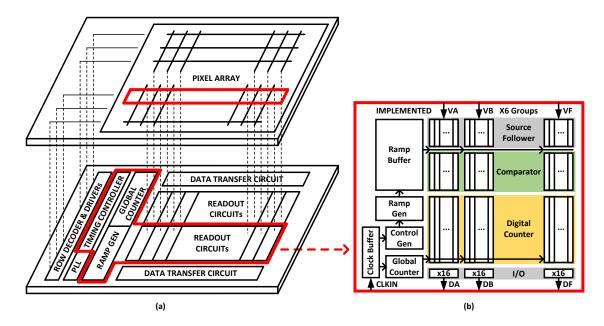

| Fig. 3.1. Block diagram of (a) 3D image sensor chip; (b) 96-column digitizer prototype.                                                                                                                                                                                                                                                                                                                | 38 |

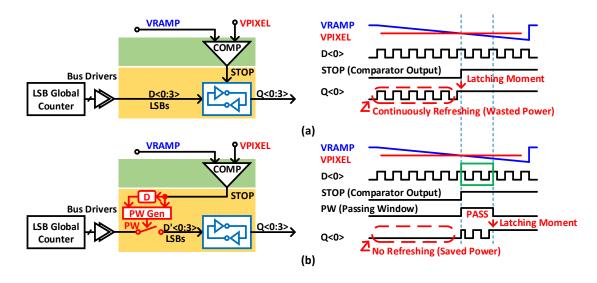

| Fig. 3.2. Global counter latching scheme: (a) without passing window; (b) with passing window.                                                                                                                                                                                                                                                                                                         | 40 |

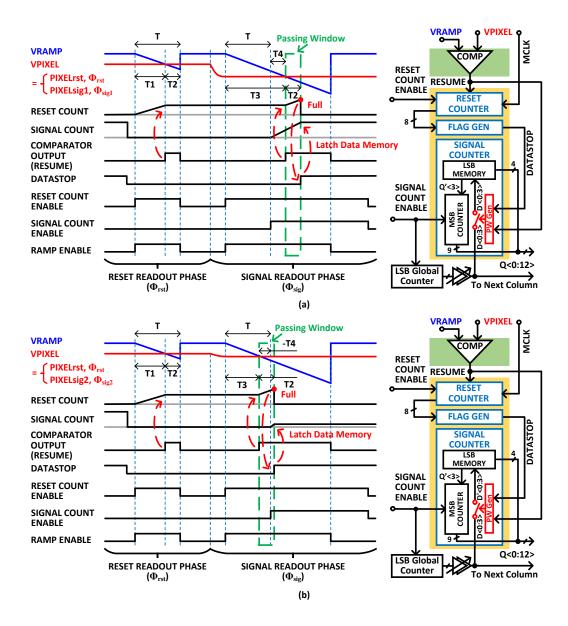

| Fig. 3.3. CDS timing scheme for one horizontal scan: (a) under bright illumination condition; (b) under dark illumination condition.                                                                                                                                                                                                                                                                   | 43 |

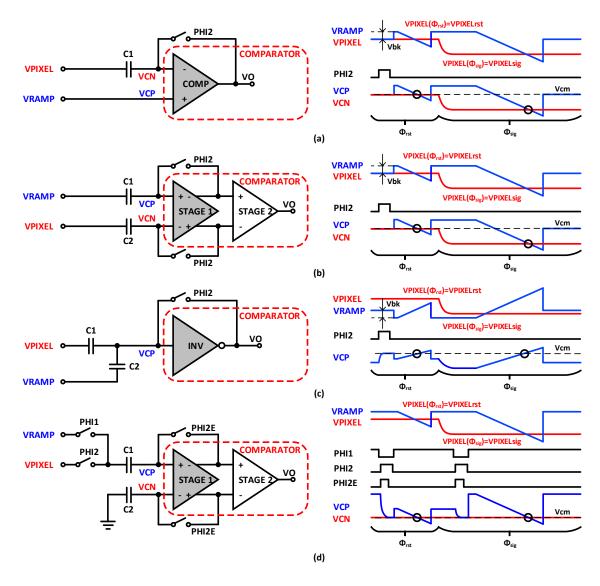

| Fig. 3.4. Column comparator topologies.                                                                                                                                                                                                                                                                                                                                                                | 45 |

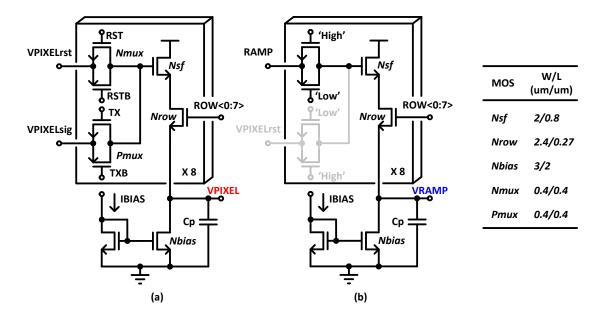

| Fig. 3.5. (a) Pixel source follower; (b) Ramp buffer                                                                                                                                                                                                                                                                                                                                                   | 48 |

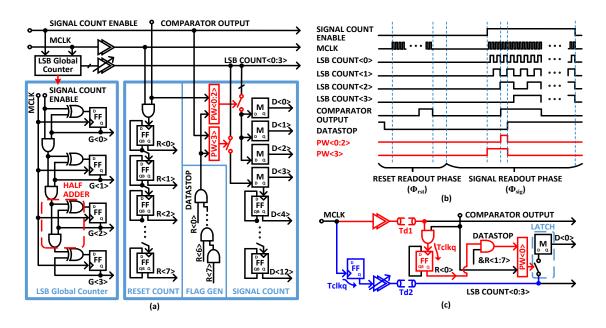

| Fig. 3.6. Proposed digital counter: (a) architecture; (b) timing scheme; (c) delay paths.                                                                                                                                                                                                                                                                                                              | 49 |

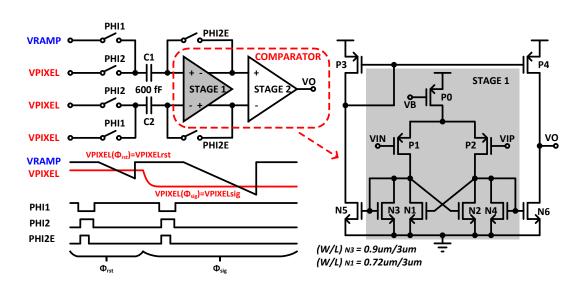

| Fig. 3.7. Proposed comparator with double AZ scheme.                                                                                                                                                                                                                                                                                                                                                   | 52 |

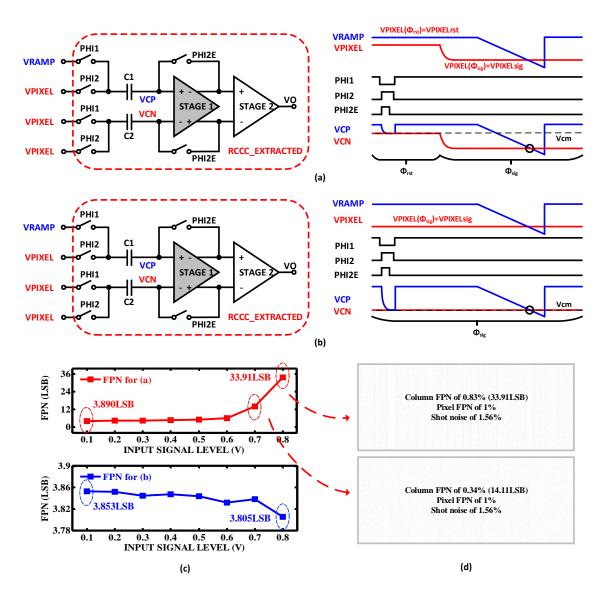

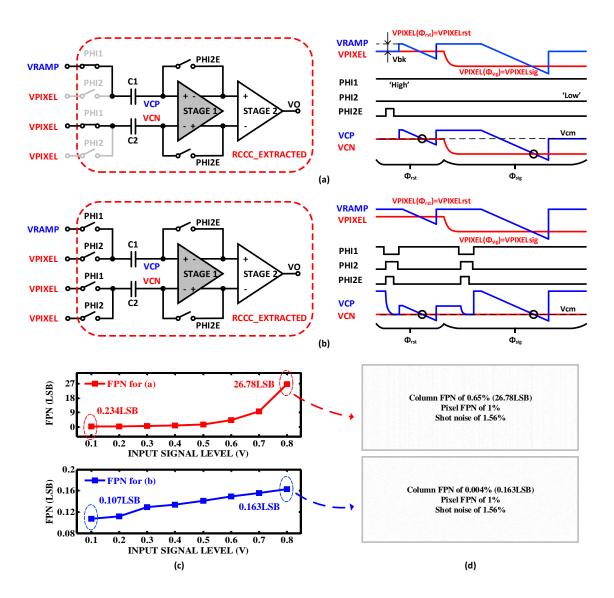

| <ul> <li>Fig. 3.8. Column FPN caused by comparator delay variations without CDS: (a) VCP/VCN does not cross at comparator common-mode voltage Vcm;</li> <li>(b) VCP/VCN crosses at comparator common-mode voltage Vcm;</li> <li>(c) column FPN under various input signal level for (a) and (b); (d) sample images with column FPN of 0.83% (33.91 LSB) and 0.34% (14.11 LSB) respectively.</li> </ul> | 54 |

| <ul> <li>Fig. 3.9. Column FPN caused by comparator delay variations with CDS: (a) VCP/VCN does not cross at comparator common-mode voltage Vcm;</li> <li>(b) VCP/VCN crosses at comparator common-mode voltage Vcm;</li> <li>(c) column FPN under various input signal level for (a) and (b); (d) sample images with column FPN of 0.65% (26.78 LSB) and 0.004% (0.163 LSB) respectively.</li> </ul> | 55 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

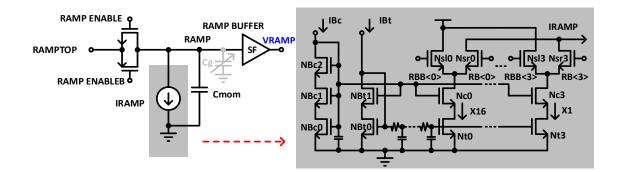

| Fig. 3.10. Proposed ramp generator.                                                                                                                                                                                                                                                                                                                                                                  | 56 |

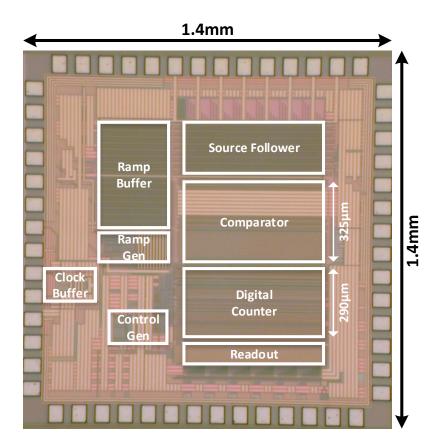

| Fig. 3.11. Microphotograph of image sensor digitizer chip.                                                                                                                                                                                                                                                                                                                                           | 57 |

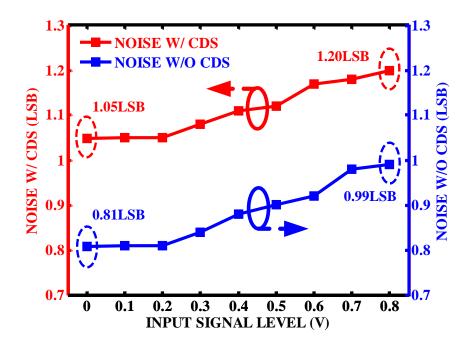

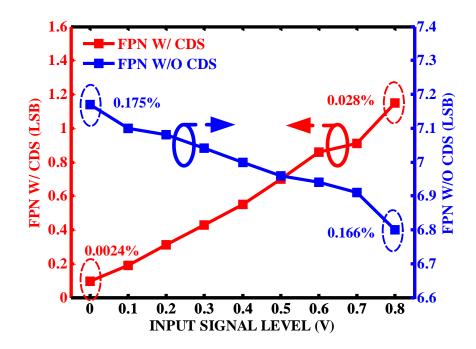

| Fig. 3.12. Measured random noise performance.                                                                                                                                                                                                                                                                                                                                                        | 59 |

| Fig. 3.13. Measured column FPN performance.                                                                                                                                                                                                                                                                                                                                                          | 59 |

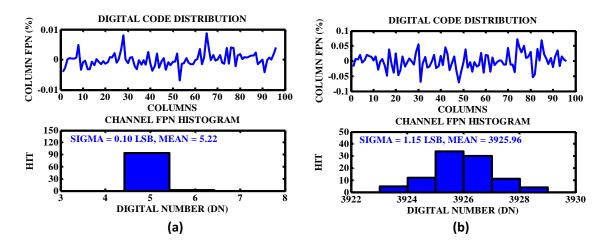

| Fig. 3.14. Measured column FPN under condition of (a) dark illumination; (b) bright illumination.                                                                                                                                                                                                                                                                                                    | 60 |

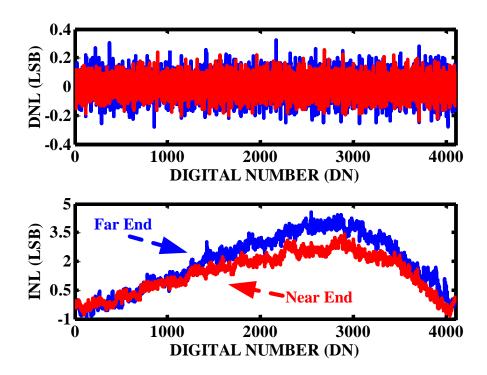

| Fig. 3.15. Measured linearity performance.                                                                                                                                                                                                                                                                                                                                                           | 61 |

| Fig. 3.16. Power consumption of single-column digital counter.                                                                                                                                                                                                                                                                                                                                       | 62 |

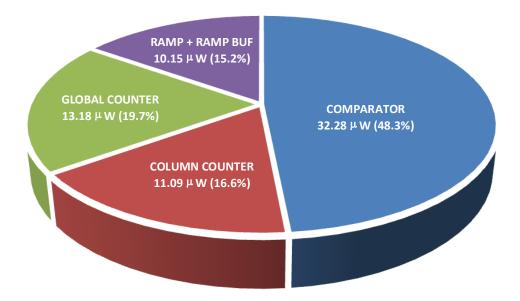

| Fig. 3.17. Power breakdown of single-column digitizer.                                                                                                                                                                                                                                                                                                                                               | 63 |

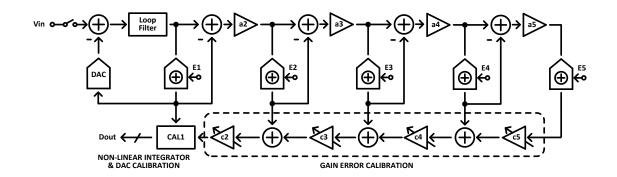

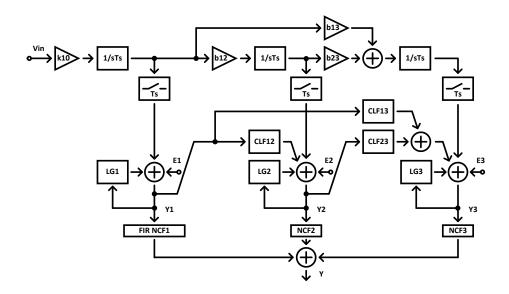

| Fig. 4.1. Architecture of a MASH 1-1-1 CT-ΔΣM including all inter-stage connection possibilities                                                                                                                                                                                                                                                                                                     | 71 |

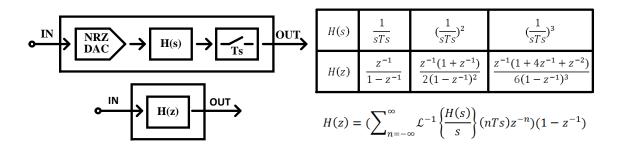

| Fig. 4.2. Equivalent circuit to compute equivalent discrete loop transfer function using impulse invariant transformation.                                                                                                                                                                                                                                                                           | 74 |

| Fig. 4.3. Equivalent model of the CT- $\Delta\Sigma$ M shown in Fig 4.1 with NCFs                                                                                                                                                                                                                                                                                                                    | 75 |

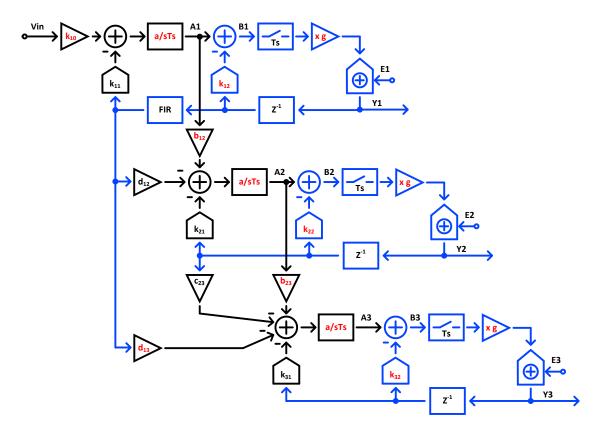

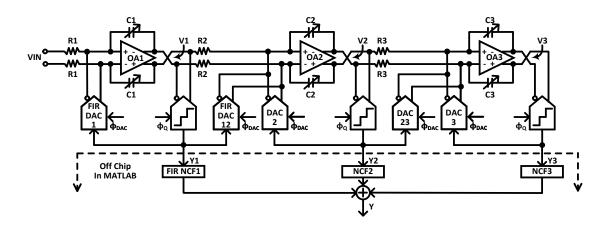

| Fig. 4.4. The proposed MASH 1-1-1 CT- $\Delta\Sigma$ M                                                                                                                                                                                                                                                                                                                                               | 75 |

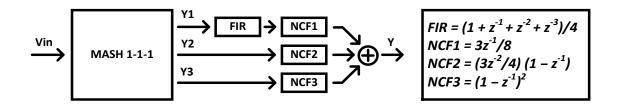

| Fig. 4.5. NCFs of the proposed MASH 1-1-1 CT- $\Delta\Sigma M$ .                                                                                                                                                                                                                                                                                                                                     | 76 |

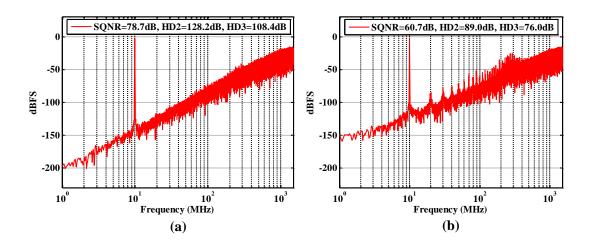

| Fig. 4.6. Simulated output spectrum of the proposed MASH 1-1-1 CT-ΔΣM: (a)<br>w/ FIR compensation logic in NCF1; (b) w/o FIR compensation logic in<br>NCF1.                                                                                                                                                                                                                                          | 77 |

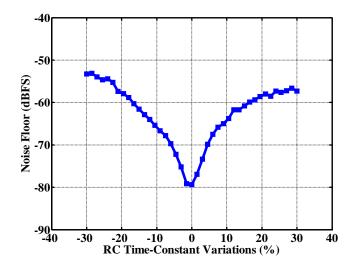

| Fig. 4.7. Quantization NF as function of RC time-constant variations                                                                                                                                                                                                                                                                                                                                 | 78 |

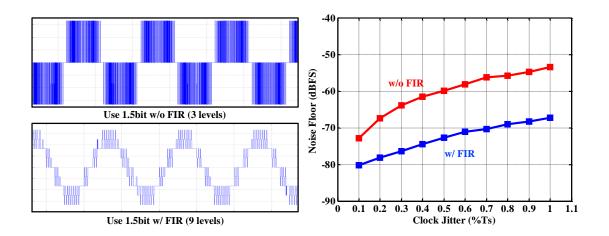

| Fig. 4.8. Clock jitter effect on the NF with and without FIR DAC                                                                                                                                                                                                                                                                                                                                     | 79 |

| Fig. 4.9. Top-level circuit implementation of the proposed MASH 1-1-1 CT- $\Delta\Sigma M$ .                                                                                                                                                                                                                                                                                                         | 80 |

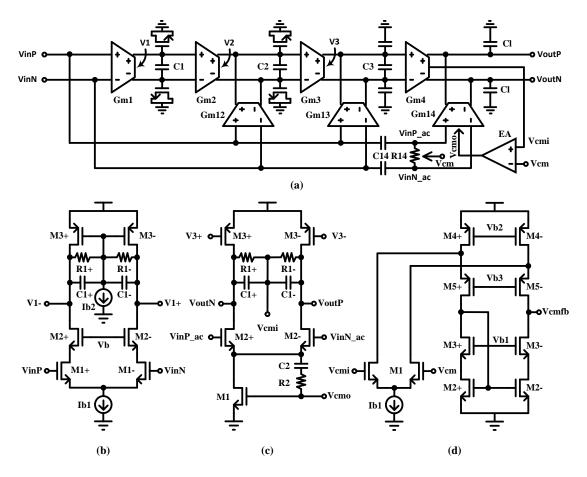

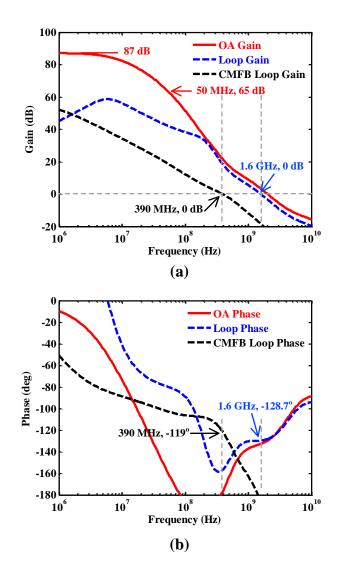

| Fig. 4.10. Circuit implementation for OA: (a) NCFF topology; (b) transconductor Gm1; (c) transconductor Gm4 and Gm14; (d) error amplifier (EA)                                       |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| required for CMFB loop                                                                                                                                                               | 82 |

| Fig. 4.11. Post-layout simulated OA1's Bode plot: (a) gain; (b) phase.                                                                                                               | 83 |

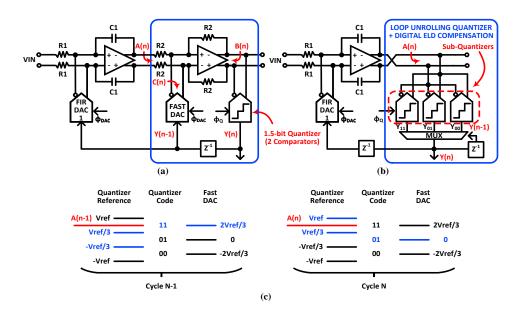

| <ul><li>Fig. 4.12. ELD compensation path: (a) with conventional analog implementation;</li><li>(b) with loop-unrolling digital implementation; (c) operation flow example.</li></ul> | 87 |

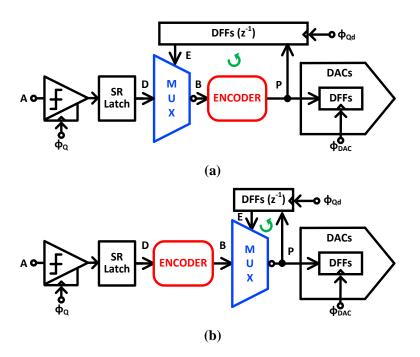

| Fig. 4.13. Loop-unrolling quantizer employing: (a) MUX-ENCODER topology;<br>(b) ENCODER-MUX topology                                                                                 | 89 |

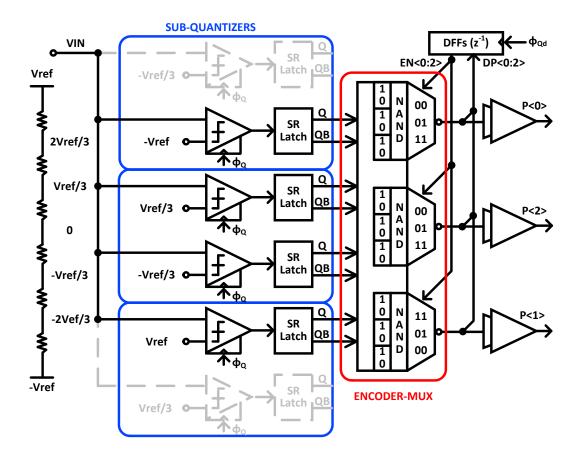

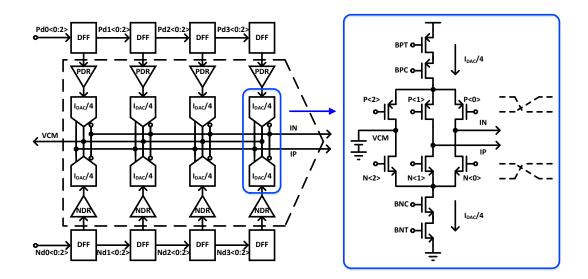

| Fig. 4.14. 1.5-bit encoder-embedded loop-unrolling (EELU) quantizer topology                                                                                                         | 90 |

| Fig. 4.15. 1.5-bit FIR DAC implementation.                                                                                                                                           | 91 |

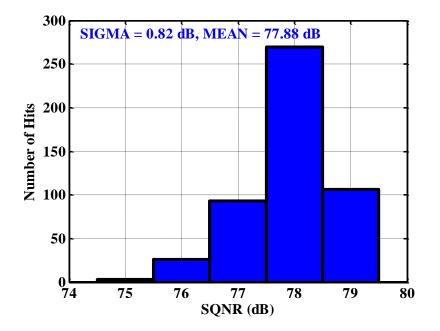

| Fig. 4.16. 500-run Monte-Carlo simulated distribution of SQNR with 1% current mismatch among segments of FIR DAC.                                                                    | 92 |

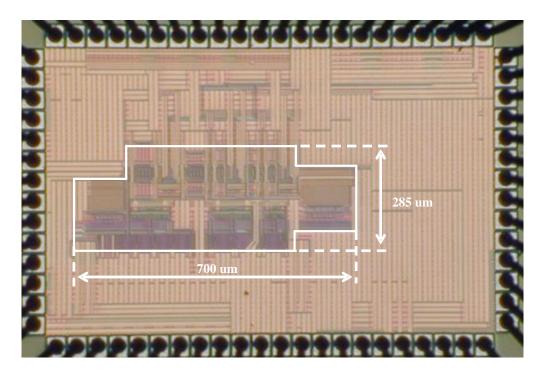

| Fig. 4.17. Microphotograph of the prototype chip.                                                                                                                                    | 93 |

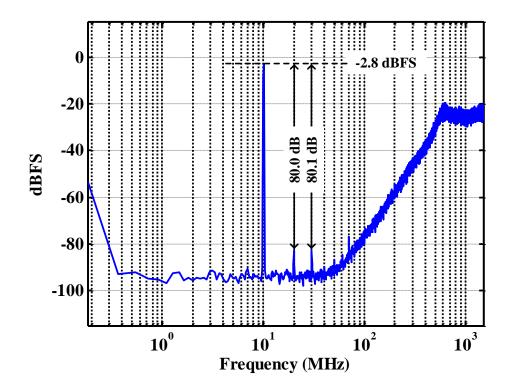

| Fig. 4.18. Measured single-tone FFT spectrum.                                                                                                                                        | 94 |

| Fig. 4.19. Measured SNR and SNDR versus the modulator's input signal level                                                                                                           | 95 |

| Fig. 4.20. Measured two-tone FFT spectrum.                                                                                                                                           | 96 |

| Fig. 4.21. Measured NF versus the first stage RC time-constant control code                                                                                                          | 97 |

| Fig. 4.22. Measured power consumption breakdown.                                                                                                                                     | 98 |

# LIST OF TABLES

| ]                                                                                         | Page |

|-------------------------------------------------------------------------------------------|------|

| Table 3.1: Performance summary and comparison with the state of the art                   | 64   |

| Table 4.1: Coefficients for the proposed MASH 1-1-1 CT- $\Delta\Sigma M$                  | 74   |

| Table 4.2: Digitally tunable capacitors                                                   | 84   |

| Table 4.3: Performance summary and comparison with state-of-the-art CT- $\Delta\Sigma$ Ms | 99   |

#### I. INTRODUCTION

### 1.1. Motivation

At a time of the information technology revolution, one of the main driving sources for the revolution of modern human society is the trend of moving functionality into the digital domain. Faster digital signal processers (DSPs) capable of performing numerous complex functions are developed thanks to advanced CMOS technologies. However, the "bridge" between the analog and the digital world, analog-to-digital converters (ADCs), are facing design challenges to meet the wide-bandwidth, high-resolution and low-power consumption targets. With the added speed of new generations of DSPs implemented in advanced technology nodes, the bandwidth of ADCs is becoming the bottleneck for the overall system. Reduced supplies mean reduced signal range, which generally demands higher accuracy for the same dynamic range (DR) target. As a potentially power hungry component, the ADC power needs to be reduced to improve the battery life of portable devices.

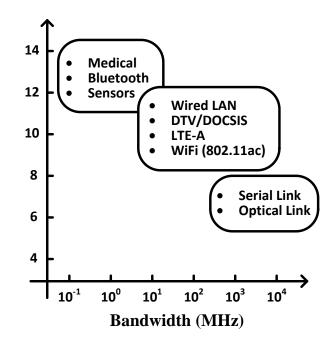

ADCs are widely used in the market for sensors, wireline/wireless communication, computers and consumer electronics. The resolution and bandwidth requirement for different applications are shown in Fig. 1.1. Different applications demand different ADC topologies and the specifications and design challenges are also different.

Fig. 1.1 Resolution and bandwidth requirements for different applications.

One focus of the dissertation is on low-power ADC design for image sensor readout applications where the demanded resolution is around 12 bit. If global ADC architecture is employed for the entire 16-Mpixel, 8000 (H) x 2000 (V) array at a frame rate of 60 fps, the ADC sampling speed needs to be close to GHz Sample/s range. The simple calculation assumes the entire readout period is used for the analog-to-digital conversion. However this is not the real case in the application and thus even higher speed ADCs may be demanded. Another topology of using one single-slope ADC dedicated for each column can significantly lower down the speed requirement. The single-slope ADC array topology has the benefit of being very simple with only the comparator and the ramp as analog circuits. The counter and the logic are all implemented in digital. As an ADC array, the ramp can be shared and generated globally which can further improve

the power efficiency of the topology. However, even with such benefits, the readout circuit still consumes a large portion of power in the image sensor chip especially under high-frame mode, due to the high-speed refreshing scheme in conventional counter implementation. Thus, to be able to achieve low-power readout for the next generation imagers operating at 120 fps or higher, effective techniques are demanded.

Another application of focus is on the low-power ADC design in mobile/wireless receivers. In LTE-Advanced, with the carrier aggregation technique added to conventional LTE, the up and down link speed has been improved based on aggregating the component carriers with bandwidth of 1.4, 3, 5, 10, 15 or 20 MHz. The same carrier aggregation concept is applied to WiFi 802.11ac to boost its link speed. The next generation 5th-Generation (5G), further improvement in the link speed is demanded which mains wider band ADCs in receivers will be in huge demand. Conventionally, single-loop continuous-time delta-sigma ADC is the most popular choice in the mobile/wireless receiver due to its high dynamic range capability, implicit anti-aliasing behavior, and tolerance of out-of-band blockers. However, there is still stability and overload recovery issue in high-order modulators demanding new techniques to handle.

## **1.2. Research Contribution**

The dissertation presents system and circuit solutions to improve the power efficiency and address high-speed design issues of ADCs in advanced CMOS technologies.

For image sensor applications, a high-performance digitizer prototype based on columnparallel single-slope ADC (SS-ADC) topology for readout of a back-illuminated 3D-stacked CMOS image sensor is presented. To address the high power consumption issue in highspeed digital counters, a passing window (PW) based hybrid counter topology is proposed. In this approach, the memory cells in the digital counters of SS-ADCs are disconnected from the global bus during non-relevant timing. To address the high column FPN under bright illumination conditions, a double auto-zeroing (AZ) scheme is proposed. In this technique, the AZ process is employed twice at reset and signal level, respectively. The double AZ scheme not only allows the comparator to serve as a crossing detector around the commonmode level, but it also enables low-voltage comparator design. The proposed techniques are experimentally verified in a prototype chip designed and fabricated in the TSMC 40 nm lowpower CMOS process. The PW technique saves 52.8% of power consumption in the hybrid digital counters. Dark/bright column fixed pattern noise (FPN) of 0.0024%/0.028% is achieved employing the proposed double AZ technique for digital correlated double sampling (CDS). A single-column digitizer consumes total power of 66.8µW and occupies an area of 5.4  $\mu$ m x 610  $\mu$ m.

For mobile/wireless receiver applications, this dissertation presents a low-power wide-bandwidth multistage noise-shaping (MASH) continuous-time delta-sigma modulator (CT- $\Delta\Sigma$ M) employing finite impulse response (FIR) digital-to-analog converters (DACs) and encoder-embedded loop-unrolling (EELU) quantizers. The proposed MASH 1-1-1 topology is a cascade of three single-loop first-order CT- $\Delta\Sigma$ M stages, each of which consists of an active-RC integrator, a current-steering DAC, and an EELU quantizer. An FIR filter in the main 1.5-bit DAC improves the modulator's

jitter sensitivity performance. FIR's effect on the noise transfer function (NTF) of the modulator is compensated in the digital domain thanks to the MASH topology. Instead of employing a conventional analog direct feedback path, a 1.5-bit EELU quantizer based on multiplexing comparator outputs is proposed; this approach is suitable for high-speed operation together with power and area benefits. Fabricated in a 40-nm low-power CMOS technology, the modulator's prototype achieves a 67.3 dB of signal-to-noise and distortion ratio (SNDR), 68 dB of signal-to-noise ratio (SNR), and 68.2 dB of dynamic range (DR) within 50.5 MHz of bandwidth (BW), while consuming 19 mW of total power (P). The proposed modulator features 161.5 dB of figure-of-merit (FOM), defined as FOM = SNDR + 10 log10 (BW/P).

### **1.3. Dissertaton Organization**

The dissertation is organized as follows: Chapter II discusses about different ADC implementation topologies. Chapter III presents a low power digitizer for backilluminated 3D-stacked CMOS image sensor readout with passing window and double auto-zeroing techniques. Chapter IV presents A 50-MHz BW 67.3-dB SNDR MASH 1-1-1 CT  $\Delta\Sigma$  modulator with FIR DAC and EELU quantizer. Chapter V concludes the dissertation.

#### II. ANALOG-TO-DIGITAL CONVERTER TOPOLOGIES

### **2.1. Introduction**

There are several major types of ADC architectures that could be used for broadband communications. Each type entails different trade-offs among resolution, speed, power and area. Overall, there are two main categories to classify these ADCs according to the ratio between the sampling frequency and signal bandwidth: Nyquist ADCs and Oversampling ADCs. In recent years, Hybrid ADCs combining different stand-alone ADC topologies have shown great potential to achieve better performance for certain application areas.

## 2.2. Nyquist ADCs

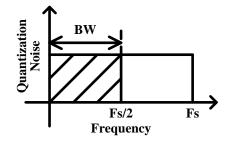

In Nyquist ADCs the sampling frequency is twice the value of the maximum input frequency wanted to be digitized as shown in Fig. 2.1.

Fig. 2.1. Quantization noise ADC.

There are many different types of Nyquist ADCs that can be used. The most popular ones are, sloping, flash, successive approximation register (SAR), and pipeline ADCs.

### 2.2.1. Sloping ADC

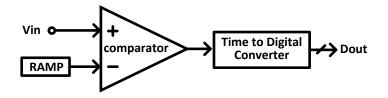

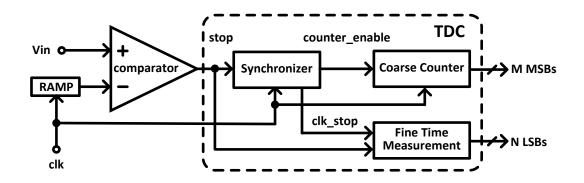

In a sloping ADC as shown in Fig. 2.2, the voltage signal is first compared with a reference of ramp signal and thus converted into a pulse width signal. The pulse width signal is measured and converted into digital bits through a time-to-digital (TDC) converter. One simple example of TDC is a ripple counter which starts counting at start of the ramp signal and ends when the input voltage crosses with the ramp signal.

Fig. 2.2. Sloping ADC architecture.

The sloping ADC typically provides benefits of high-resolution and low area. However, the speed of operation is usually low due to the monotonic thermometer code like counting behavior. The worst condition happens when the input signal is full-scale. The counter needs to count up to close to its full-count, which takes time and power. One clear target to address the issue is to lower down the number of counting cycles to complete the conversion process. In [1], a pulse position modulation sloping ADC architecture employing two-step TDC topology is proposed, as shown in Fig. 2.3. The 5 bit course time quantizer, formed using a counter measures the number of reference clock cycles while the counter\_enable signal is high, thus measures  $t_c$ . The fine TDC measures the time  $t_f$  defined as the time between the stop signal and clk\_stop rising edges. The timing scheme is shown in Fig. 2.4 and the reference clock frequency is lowered by 16 times to achieve the same time resolution. Another possible solution is to employ a multiple ramp topology [2]. The basic concept of a multi-ramp single slope ADC is that the ramp voltage, which spans the entire input voltage range in the single slope architecture, is divided into m steps, each of which spans 1/m of the input range. The timing operation of the multi-ramp architecture is shown in Fig. 2.5. In the coarse phase, the comparator is connected to a single course ramp voltage, and the first conversion is performed. Next, the coarse conversion result is fed back into the ramp generator to decide the range for the fine conversion range. In the fine conversion, the ramp only has to span 1/m times the ADC input range, and therefore the conversion can be much faster.

Fig. 2.3. Pulse-position modulation sloping ADC architecture (adapted from [1]).

Fig. 2.4. Pulse-position modulation sloping ADC timing scheme (adapted from [1]).

Fig. 2.5. Multi-ramp single-slope ADC timing scheme (adapted from [2]).

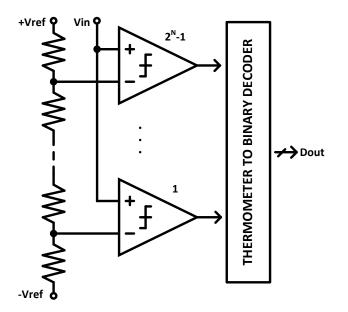

#### 2.2.2. Flash ADC

A flash ADC uses parallel comparators to compare the input signal with all transition points between adjacent quantization intervals. The result of these comparisons highlights the limit at which the input is larger than on of the thresholds giving information that can then be transformed into digital codes. The output is obtained in thermometer code, which is typically converted into a binary digital output. Since the comparators operate in parallel, the latency of the output is less than one clock cycle, making this architecture suitable for speeds of several GHz. However, a flash ADC suffers from limited resolution, the number of comparators and references required increases exponentially with the number of bits. For an N-bit flash ADC,  $(2^{N}-1)$ comparators and reference voltages are required as shown in Fig. 2.6.

Also, the offset requirement for the comparators and matching of the references increases exponentially, demanding more area and power consumption making the design of high resolution flash unreliable. Thus, it is not practical to implement a flash ADC with resolution higher than 7 bit.

Fig. 2.6. Flash ADC architecture.

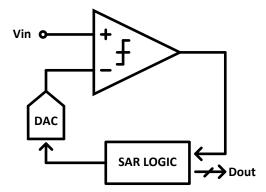

2.2.3. SAR ADC

A SAR ADC uses a single comparator to quantize the input signal based on binary search algorithm. As shown in Fig. 2.7, the ADC consists of a comparator, a SAR digital decision logic, and DAC. During the conversion process, the DAC output gradually approaches the input voltage.

SAR ADCs require multiple clock cycles to complete the digital output. For N-bit SAR ADC, N clock cycles are necessary. Therefore, the SAR ADCs are typically slower compared to flash ADCs. The SAR logic adjusts the reference voltage provided the DAC, which defines the resolution of the ADC and is normally implemented by capacitors or resistors. Thus, for high resolution the area of the SAR is dominated by the DAC, which is sized depending on the matching requirements. To achieve high-speed

operation, however, smaller capacitor array is more desirable. Thus, there is a fundamental trade-off between speed and accuracy for SAR ADCs.

Fig. 2.7. SAR ADC architecture.

The conventional implementation of the SA logic relies on a synchronous clock to divide the time into a signal tracking phase and conversion phase which processes from the MSB to the LSB as shown in Fig. 2.8. Each clock cycle has to tolerate the worst case comparison time, which is composed of maximum DAC settling time and comparator resolving time depending on the minimum resolvable input level. Therefore, the power and speed limitation of a synchronous SAR design come largely from the high-speed internal clock. Using asynchronous processing of the internal comparisons removes the need for such a clock and substantially improves the power efficiency of SAR ADCs. The concept of asynchronous processing is to trigger the internal comparison from MSB to LSB like dominoes [3]. As shown in Fig. 2.9, whenever the current comparison is complete, a ready signal is generated to trigger the next comparison process.

Fig. 2.8. Synchronous conversion for SAR ADCs (adapted from [3]).

Fig. 2.9. Asynchronous conversion for SAR ADCs (adapted from [3]).

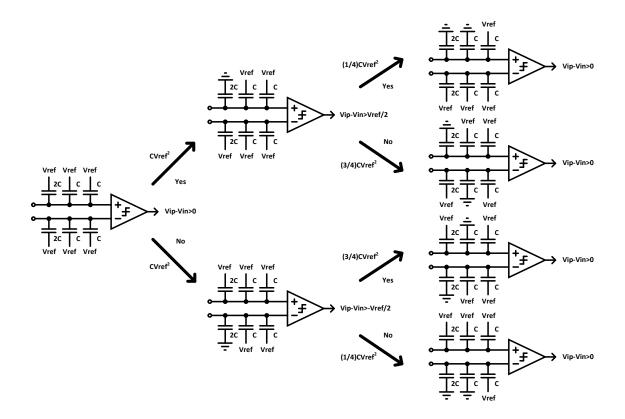

Efforts have also been made in the SAR algorithm to improve its switching energy efficiency and reduce the total capacitance. In [4], a monotonic capacitor switching procedure is proposed as shown in Fig. 2.10. After the sampling switches turn off, the comparator directly performs the first comparison without switching any capacitor. The subsequent switching subsequent switching sequence is also more efficient than the conventional scheme which leads to an average switching energy saving of 81%. However, in the monotonic switching topology the input common-mode gradually converges to ground. Thus a comparator with low sensitivity to the signal-dependent offset caused by the input common-mode voltage variation is demanded.

Fig. 2.10. Monotonic capacitor switching procedure (adapted from [4]).

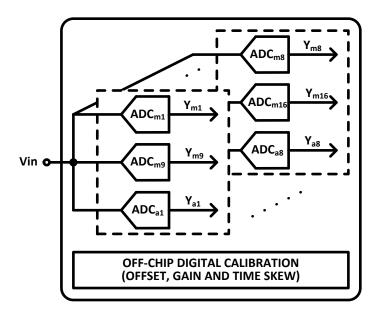

Compared with flash ADC, SAR topology is very attractive for its superior power efficiency. Time interleaving techniques are proposed to speed up the operation of SAR ADCs into GHz Sample/s. In [5], a 10 bit time-interleaved SAR ADC with background time-slew calibration in 40 nm CMOS technology is presented, as shown in Fig. 2.11. The entire interleaved ADC consists of 16 main ADCs and 8 auxiliary ADCs for skew correction, which operate at 1/16 and 1/8 of the sampling frequency, respectively. The reported ADC demonstrates a digital timing-skew correction technique incorporated with a delta-sampling technique, and achieves a 2.6 GHz sampling rate and a wide signal bandwidth up to Nyquist.

Fig. 2.11. Time-interleaved SAR ADC (adapted from [5]).

### 2.2.4. Pipeline ADC

A pipeline ADC takes advantage of the speed of a flash ADC, and eliminates the exponential increase in complexity by cascading multiple stages of low resolution flash ADCs. A sample and hold (S&H) function in each stage allows all stages to operate concurrently, giving a throughput of one output sample per clock cycle. Fig. 2.12 shows that besides the sub ADC, a DAC, a subtractor, and an OpAmp are required for each stage.

The operation is described as follow: First, the input signal is quantized by the sub ADC each stage includes a DAC to convert the quantized signal to analog, a residue calculator obtains the difference between the analog input signal and the quantized signal, then the residue is amplified to adjust the swing for the full-scale of the next stage, the amplified residue becomes the input of the next stage. The process is successively replicated until the last pipelined stage. The number of stages depends on the number of bits solved per stage, and the total number of bits target. Since all pipelined stages work simultaneously, the conversion speed of the pipeline ADC is close to the conversion speed of its single stage. However, since the input signal is quantized successively by the stages, the output has a latency delay equal to the number of stages. The limitation of the pipeline ADC is the high power consumption required for the calculation of the residue. Pipeline ADCs can reach resolution between 8 bit to 12 bits and speeds up to several GHz Sample/s.

Fig. 2.12. Pipeline ADC architecture.

In early implementations, the resolution of the sub-ADC is typically chosen to be 1.5 bit per stage for two reasons [6]. The first reason in to maximize the bandwidth of the S&H/residue-amp switched capacitor circuit which limits the overall conversion rate. Second, with the use of digital correction algorithm in 1.5 bit per stage pipeline architecture, the overflow of present stage output from the input range of the following stage can be prevented even with the presence of a large comparator offset up to 1/4 of the reference voltage, so that this offset error amplified down the pipeline can be detected for correction.

However, in recent implementations, 3 or 4 bit per stage topology gains more popularity. Compared with 1.5 bit per stage implementations, adding more bits in the first stage leads to less requirement on latter stages and thus results in lower power dissipation overall. However, as the feedback factor for the residue amplifier drops, higher gain-bandwidth product (GBW) is demanded. Thus, precision amplifiers dominate the power consumption in most high-speed pipeline ADCs. In [7], a digital background calibration technique is proposed, enabling to replace precision amplifiers by simple power efficient open-loop stages. In the multibit first stage of a 12-bit 75-MS/s proof-of-concept prototype, 60% residue amplifier power savings over a conventional implementation is achieved.

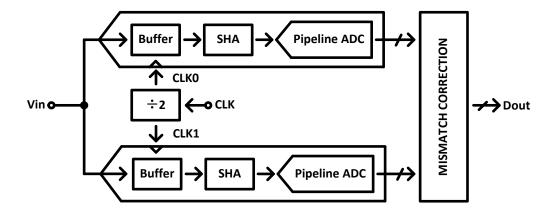

Pipeline ADC can also be time-interleaved to further improve the operation speed. In [8], a 5.4 GS/s 12 bit two-way interleaved pipeline ADC is presented, as shown in Fig. 2.13. It employs a complementary switched-capacitor amplifier topology to double the GBW without increasing power. The ping-pong amplifier sharing configuration doubles

17

the sampling rate, whereas the sub DAC equalization digitally corrects the settling error and other dynamic errors in the ping-pong architecture.

Fig. 2.13. Time-interleaved pipeline ADC architecture (adapted from [8]).

## 2.3. Oversample ADCs

In oversample ADCs, the bandwidth of the input signal is less than half the bandwidth of the sampling frequency. However, the most widely-used architecture taking good advantage of the oversampling benefit is delta-sigma ADC.

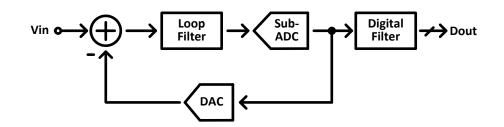

A delta-sigma ADC achieves high resolution by combining the techniques of: oversampling and closed loop noise shaping. Fig. 2.14 shows the basic architecture of a delta-sigma ADC. A delta-sigma modulator consists of a loop filter, a sub ADC, a DAC, and a digital filter.

<sup>2.3.1.</sup> Delta-Sigma ADC

Fig. 2.14. Delta-Sigma ADC.

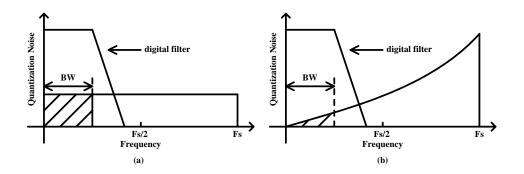

The effect of oversampling spreads the quantization from the sub ADC over a wider frequency. Therefore, if the oversampling ratio increases the quantization noise inside the desired bandwidth will reduce as shown in Fig. 2.15 (a). Moreover, the quantization noise level inside the desired bandwidth is shaped by the effect of the feedback loop around the sub ADC, such that most of the noise is shifted out of the bandwidth of interest as shown in Fig. 2.15 (b). The former made the delta-sigma ADC a perfect architecture for high resolution applications. However, the speed of the ADC is typically limited comparing with Nyquist ADCs due to the oversample behavior. Nonetheless, advance in process technology has allowed delta-sigma ADCs to reach the hundreds of MHz of bandwidth range, employing continuous-time implementation topologies.

Fig. 2.15. Quantization noise: (a) oversample ADC; (b) delta-sigma ADC.

#### 2.3.2. Discrete-Time Delta-Sigma Modulator (DT- $\Delta \Sigma M$ )

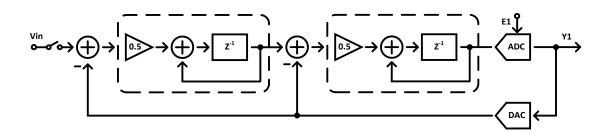

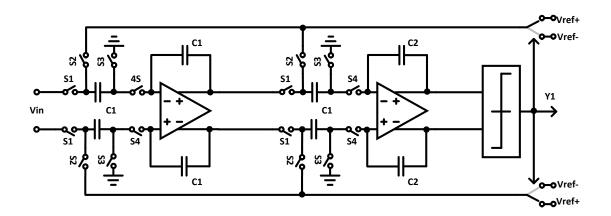

In discrete-time delta-sigma modulators, the input voltage is sampled first and then processed by the modulator. Fig. 2.16 shows the block diagram of the second-order discrete-time delta-sigma modulator ( $\Delta\Sigma M$ ). A forward path delay is included in both integrators, thus simplifying the implementation of the modulator with straightforward sampled-data analog circuits. Each integrator is preceded by an attenuation of 0.5, to address the swing issue at the integrator output nodes. The circuit implementation of the  $\Delta\Sigma M$  employing switch capacitor integrators and a single-bit comparator is shown in Fig. 2.17. The comments on the non-idealities affecting the performance of the DT- $\Delta\Sigma M$  are as follows [9]:

- a. OFFSET: Offset is minor concern in many signal acquisition systems, as long as the quantization is uniform. The offset at the input of the first integrator is the only significant contributor because offsets in the second stage and comparator are suppressed by the large low-frequency gain of the integrator.

- b. SAMPLING JITTER: Oversampled ADC put considerably less stringent requirements on the filter than Nyquist ADCs since the signal is sampled at a frequency far exceeding its bandwidth.

- c. NOISE: Noise injected at the modulator input is the dominant source. Inputreferred noise from the comparator undergoes the same second-order noise shaping as the quantization noise. The noise sources at the input of the second integrator are subjected to first-order noise shaping behavior. Out-of-band noise

is eliminated by the decimation filter, but high-frequency noise at multiples of the sampling frequency will be aliased in band.

- d. INTEGRATOR DC GAIN: The performance penalty incurred is on the order of 1 dB when the integrator dc gain is comparable to the oversampling ratio (OSR).

- e. INTEGRATOR BANDWIDTH: Integrator implementations using operational amplifiers (OPAMP) with bandwidths considerably lower than the sampling frequency, thus with correspondingly inaccurate settling, will not impair the  $\Delta\Sigma$ M performance as long as the settling process is linear.

- f. INTEGRATOR SLEW: Slewing distortion appears when the peak rate of change in the impulse response exceeds the maximum slew rate the integrator can support.

- g. COMPARATOR HYSTERESIS: The sensitivity of  $\Delta\Sigma$ Ms to comparator hysteresis is several orders of magnitude smaller than that of Nyquist ADCs attributed to the negative feedback with high loop gain topology.

Fig. 2.16. Block diagram of second-order DT- $\Delta\Sigma$ M.

Fig. 2.17. Second-order DT- $\Delta\Sigma M$  implementation.

#### 2.3.3. Continuous-Time Delta-Sigma Modulator ( $CT-\Delta\Sigma M$ )

As mentioned above, in DT- $\Delta\Sigma$ Ms, high-frequency noise, aliases and blockers at multiples of the sampling frequency will fold in band. However, in CT- $\Delta\Sigma$ M, the situation is quite different. The CT- $\Delta\Sigma$ M does not demand a dedicated sampler at the ADC input since the loop filter directly process the input signal. The impulse sampling operation occurs at the input of the quantizer after the loop filter. In addition, the feedback path is operating to convert the quantized impulse into time-domain waveforms for integration in the loop filter. A simple example on the analysis of a first order CT- $\Delta\Sigma$ M is possible based on the time-domain model shown in Fig. 2.18 (a). By splitting the feedforward path for the signal and the feedback path for the output impulse sequence, the model in Fig. 2.18 (a) can be redrawn as in Fig. 2.18 (b). In the feedback path, based on impulse invariant, it is possible to find z-domain filter H(z) equivalent to the original s-domain paths including the DAC, s-domain loop filter H(s) and the impulse sampler at the quantizer input. The impulse invariant methodology significantly simplifies the analysis and is widely used in the design of  $CT-\Delta\Sigma Ms$ .

Fig. 2.18. Block diagram of first order CT- $\Delta\Sigma$ M: (a) time-domain model; (b) linearized time-domain model splitting signal feedforward and output feedback paths.

Compared to DT- $\Delta\Sigma$ Ms, the main advantages of CT- $\Delta\Sigma$ Ms [10] are:

- a. Implicit anti-aliasing filter

- b. Noise shaping on S&H

- c. Possibly higher sampling rate

- d. Less digital switching noise

For the reasons above,  $CT-\Delta\Sigma Ms$  are generally more favored in mobile/wireless applications. However, there are still design challenges mainly in the following aspects:

- a. Sensitive to clock jitter

- b. Sensitive to excessive loop delay (ELD)

- c. Sensitive to DAC waveform error

- d. Less accurate analog transfer function

# 2.4. Hybrid ADCs

Different ADC topologies were briefly discussed highlighting their architecture, advantages and issues. Rather than stick to certain fixed ADC topology, designers have the option to break the boundary and combine some of the topologies and techniques to further improve the ADC performance.

## 2.4.1. Pipelined SAR ADC

SAR ADC architectures are popular for achieving high energy efficiency but they suffer from resolution and speed limitations. On the other hand, pipeline ADC architectures usually achieve high resolution and speed but have lower energy-efficiency. Fig. 2.19 shows one possible combination of the two topologies named pipelined SAR ADC [11]. The flash sub-ADC of a conventional pipeline ADC is replaced by a SAR sub-ADC. The sub-DAC input sampling capacitor array is also utilized by the SAR sub-ADC by connecting a single comparator to the top plate of the input capacitor array. The problem of sampling path mismatch in conventional pipeline ADC is eliminated because the SAR sub-ADC and the sub-DAC share the same sampling path. The single comparator quantizes the static signal stored on the capacitor array, hence aperture error is also absent. The sub-DAC capacitor array is also used for sampling purpose and there is no need for an active front-end S&H circuit. At the end of the entire successive approximating cycle, the voltage left as the input of the comparator is the residue which needs to be amplified and processed by later stages.

Fig. 2.19. Pipelined SAR ADC (adapted from [11]).

Fig. 2.19 shows a state-of-the-art implementation of a 13 bit 50 MS/s pipelined-SAR ADC in 65 nm CMOS [11], A fully differential ring amplifier with high gain, fast slew based charging and an almost rail-to-rail swing is used for a switched capacitor (SC) inter-stage residue amplifier to achieve accurate amplification without calibration. A floated detect-and-skip (FDAS) witching scheme is introduced to reduce the switching energy loss and improve the linearity of the SAR capacitor DAC. The prototype ADC achieves signal to noise and distortion ratio (SNDR), signal to noise ratio (SNR) of 70.9 dB and 71.3 dB, respectively at Nyquist input frequency.

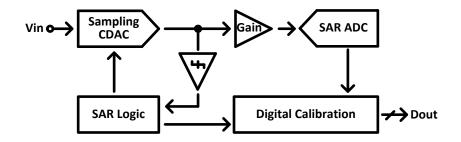

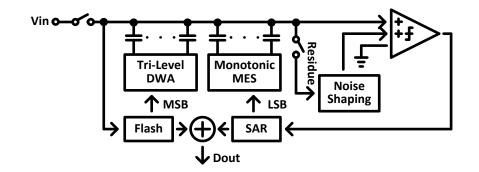

#### 2.4.2. Noise Shaping SAR ADC

Although SAR ADCs are highly efficient, comparator noise and other effects limit the most efficient operation to below 10 to 12 bit effective number of bits (ENOB). In [12], a noise-shaping concept from  $\Delta\Sigma M$  is introduced to filter out the in-band noise, as shown in Fig. 2.20. The noise shaping scheme shapes both comparator noise and quantization noise, thereby decoupling comparator noise from ADC performance. The loop filter is comprised of a cascade of a two-tap charge-domain finite impulse response (FIR) filter and infinite impulse response (IIR) based on a low-quality integrator.

Fig. 2.20. Noise-shaping SAR using FIR and IIR filter (adapted from [12]).

In [13], a similar noise shaping concept together with mismatch error shaping for the capacitor DAC are employed to achieve 105 dB of in-band spurious free dynamic range (SFDR) without calibration, as shown in Fig. 2.21. The prototype incorporates the concepts of flash, SAR and  $\Delta\Sigma M$  and can be configured into conventional and oversampling modes.

Fig. 2.21. Noise and mismatch shaping SAR with segmented DAC (adapted from [13]).

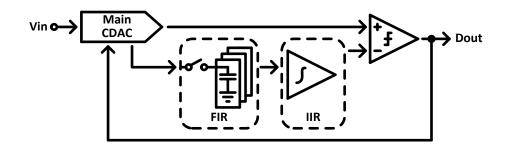

## 2.4.3. Delta-Sigma Modulator Employing SAR as Quantizer

Conventionally, flash ADC is typically the choice to implement the quantizer inside of  $\Delta\Sigma M$ . However, replacing the flash quantizer with an a-synchronous SAR quantizer has shown potential to further improve the power efficiency of CT- $\Delta\Sigma M$  [14], [15]. In [14], by using a 6 bit a-synchronous SAR quantizer, the sampling frequency is lowered, which reduces the design efforts both in system level and circuit level as shown in Fig. 2.22. However, as it is not practical to feedback a 64 level DAC signal, a digital deltasigma truncator is employed to truncate the feedback into only 9 levels. Compared with the same order loop filter without delta-sigma truncation, only 2 dB of 2 dB degradation in in-band noise is noticed.

Fig. 2.22. A-synchronous SAR based CT- $\Delta\Sigma$ M with digital delta-sigma truncator (adapted from [14]).

The noise shaping SAR concept can also be used to build the quantizer inside a CT- $\Delta\Sigma$ M. Fig. 2.23 shows the block diagram of the modulator using a 4th-order feed-forward architecture with a 4-bit asynchronous SAR quantizer [15]. The 2nd-order noise coupling and ELD structures are integrated into the 4-bit asynchronous SAR. Thus, 6th-order of total noise shaping is obtained and the measured SNDR of the CT- $\Delta\Sigma$ M is improved from 53.9 dB to 75.3 dB enabling noise coupling and DAC calibration.

Fig. 2.23. SAR-assisted CT- $\Delta\Sigma M$  with 2<sup>nd</sup>-order noise shaping (adapted from [15]).

## 2.4.4. Hybrid Delta-Sigma/Pipelined Modulator

Similar to employing a SAR ADC as the quantizer of a  $\Delta\Sigma M$ , pipeline ADC can also be integrated in a delta-sigma loop and operates as a high-resolution quantizer. In [16], a hybrid delta-sigma/pipelined (HDSP) modulator is presented. The proposed modulator takes advantage of the high resolution and distributed pipelined quantization and combines it with the noise shaping property of a  $\Delta\Sigma M$ . The latency issue of the pipeline ADC is addressed by adding additional feedback paths from the last stage of the pipeline ADC to its internal nodes as shown in Fig. 2.24. Since the quantizer noise of the pipeline ADC is available in analog form as the residue, it can be used for generating the feedback terms.

Fig. 2.24. Hybrid delta-sigma/pipelined (HDSP) modulator (adapted from [16]).

## 2.4.5. 0-N/N-0 MASH Delta-Sigma ADC

Instead of allocating a pipeline ADC as the quantizer of  $\Delta\Sigma M$ , other topologies by cascading  $\Delta\Sigma M$  and Nyquist ADC is presented in [17], [18]. There are basically two category of topologies, namely 0-N MASH and N-0 MASH. Fig. 2.25 shows the block diagram of a 0-N MASH concept [17]. The first stage is a zero-order quantizer, while the second stage is an N-th order single-loop  $\Delta\Sigma M$  with an internal quantizer. The main benefit of 0-N MASH topology is allowing a larger input-signal which results in an improvement in the achievable performance and an enhancement in the modulator efficiency. In addition, its ability to let the  $\Delta\Sigma M$  process quantization noise only, relaxes the headroom and linearity requirements of its opamps.

Fig. 2.25. The 0-N MASH  $\Delta\Sigma M$  concept (adapted from [17]).

Fig. 2.26 shows a 15 MHz 1-0 MASH  $\Delta\Sigma$ M with nonlinear memory error calibration [18]. A two-tap sequential polynomial derived from an output-referred error analysis accurately models the no-ideality of a first-order  $\Delta\Sigma$ M. The model parameters are extracted by correlating various moments of the ADC digital output with a one-bit pseudorandom noise (PN) superimposed on the input, largely reducing the circuit overhead associated with the nonlinear calibration. The proposed calibration scheme effectively improves the third-order intermodulation product (IM3) by 30 dB to 87.1 dBc.

Fig. 2.26. The 1-0 MASH  $\Delta\Sigma M$  with nonlinear memory error calibration (adapted from [18]).

## 2.5. Conclusion

In this section, various ADC topologies are visited including both conventional stand-alone ADC and Hybrid ADC topologies. Each type of ADC has its own unique advantage and shortcoming. In image sensing readout applications, implementation based on different ADC topologies, like sloping, SAR, pipeline, pipelined SAR,  $\Delta\Sigma M$

and so on, have been reported in literature. In mobile/wireless communication receivers, even though  $CT-\Delta\Sigma M$  is the current dominant option, there is still fierce competition from other ADC topologies, like SAR, pipeline, pipelined SAR etc. In addition, processing analog signal in the domains other than voltage, like time, charge, and current, also adds more diversity in architectures for the analog-to digital conversion.

# III. A LOW POWER DIGITIZER FOR BACK-ILLUMINATED 3D-STACKED CMOS IMAGE SENSOR READOUT WITH PASSING WINDOW AND DOUBLE AUTO-ZEROING TECHNIQUES

# **3.1. Introduction**

Recent innovations on back-illuminated 3D-stacked process for CMOS image sensors [19]–[30] have stimulated a new leap forward in the image sensor industry. The separation of the conventional image sensor process for pixels and the logic process for the readout circuits enables independent performance optimization leading to cost reduction. Instead of sticking to an image sensor process, advanced logic technology nodes are applicable choices for the image sensor digitizer which infers both power and benefits with process scaling.

<sup>\*</sup> Reprinted, with permission, from "A low power digitizer for back-illuminated 3D-stacked CMOS image sensor readout with passing window and double auto-zeroing techniques," Q. Liu, A. Edward, M. Kinyua, E. G. Soenen, and J. Silva-Martinez, IEEE Journal of Solid-State Circuits, accepted in Jan 2017 and to be published. © 2017 IEEE.

The most critical building block of an image sensor digitizer is the analog-to-digital converter (ADC). Diverse topologies of ADCs integrated at different levels have been reported targeting high-speed, low-power and area-efficient implementation [19], [22], [28]–[30], [31]–[39]. Binary-search algorithm-based ADCs like cyclic [30], [31], [32] and successive approximation registers (SARs) [35]–[37] are typically faster compared with ramp-based ADCs [19], [21], [28], [29], [38], [39] and oversampling ADCs [33], [34]. However, cyclic ADCs demand amplifiers with precise gain while SAR ADCs require well-matched capacitor digital-to-analog converters (DACs) to achieve high resolution. Forcing cyclic/SAR ADCs into a column-parallel array with a small pixel pitch results in significant layout complexity and column non-uniformity [35]. Furthermore, issues in reference voltage and power supply distribution can degrade farend ADC performance [37]. Employing a single chip-level pipelined SAR ADC to read out the entire pixel array avoids the area and the analog voltage distribution issues, but the frame rate of the image sensor is limited by the speed of the ADC [36]. Columnparallel oversampling ADCs with noise filtering can achieve low random noise and wide dynamic range, but complicated decimation filters are usually demanded. On the contrary, single-slope ADCs (SS-ADCs), working in column-parallel array and sharing the same ramp signal, have superior fitness for fine-pitch-pixel readout. With only comparators in the analog domain, SS-ADCs benefit from the 3D-stacked process revolution because of their simplicity. Another advantage of an SS-ADC is its good differential non-linearity (DNL) performance without large spikes, which is common problem in cyclic/SAR ADCs [37]. In addition, the digital CDS technique has proven effective in SS-ADC, resolvisng a number of limiting issues like resetting KT/C noise, pixel and readout FPN, clock skew, and ramp delay [38].

However, employing SS-ADC architecture as a digitizer for CMOS image sensor application comes with two obstacles. A high-speed SS-ADC demands a fast-counting clock, which implies high power consumption in the digital counters lumped to each column [38]. In [29], [39], by sharing a global 5-bit least significant bit (LSB) counter between every 248 columns and put memory cells in columns, the power consumption of the digital counter was reduced. However, if the memory cells in columns are implemented as transparent standard-cell latches [29], the continuous refreshing of the memory cells before the real latching moment will lead to large amount of power waste. Secondly, in the conventional CDS scheme [38], during auto-zeroing (AZ), the offset and delay information stored for cancellation purpose only corresponds to small pixel information levels. Nevertheless, under bright illumination conditions, the input of the comparator [38] crosses at a much lower voltage level which corresponds to a different offset and delay information. For the aforementioned reasons, the digital CDS subtraction introduces a cancelation error, which results in large column fixed pattern noise (FPN) left under bright illumination conditions.

In this paper, passing window (PW) and double auto-zeroing (AZ) techniques are presented to address these two issues. The LSB memory cells in the hybrid digital counters of SS-ADCs are only connected to the global buses during an auto-generated PW. This allows power saving in both LSB memories and global data bus drivers. First attempt of employing double AZ concept to solve bright column FPN was made in this design. The AZ process of comparator is employed twice during reset and signal readout phase, respectively, such that the comparator operates as a crossing detector only around the same common-mode level. With a double AZ scheme, an effective comparator offset and delay cancelation with digital CDS can be achieved even under bright illumination. Normally dark image column FPN is more visible than bright column FPN. However, as when designers lower down the power supply aiming to save power, the bright column FPN performance gets worse and becomes more noticeable.

The paper is organized as follows: Section II describes the overall architecture of the image sensor chip. Section III describes the proposed PW and double AZ techniques. The circuit-level implementations of the most relevant building blocks of the digitizer are detailed in Section IV. The measurement results are discussed in Section V, and Section VI concludes this paper.

## **3.2. Sensor Architecture**

A typical CMOS image sensor system consists of a pixel array, a digitizer, a row decoder and driver, a timing controller, a phase-locked loop, and a data transfer circuit. In a conventional 2D implementation, the pixel array is arranged at the center of the chip and the peripheral circuits have to be designed using the same process optimized for the pixels. This arrangement limits the performance of the peripheral circuits and degrades the silicon area efficiency. The first commercial product of a back-illuminated 3D-stacked image sensor was reported in [19]. The connection between the interconnect layers between the top and bottom parts was realized with through-silicon vias (TSVs)

outside the pixel array. In [28]–[30], [40], with direct connection of top and bottom wafers with Cu-Cu bonding, the pixel array to chip area ratio is improved because the connection position can be under the pixel array.

Fig. 3.1 (a) shows a back-illuminated 3D-stacked CMOS image sensor with direct interconnection between top and bottom wafers [28]. While the design techniques are eventually targeting at entire multi-megapixel image sensor readout, in this prototype, only 96 columns of readout circuits are implemented as shown in Fig. 3.1 (b), in order to focus on the characterization of the digitizer design. The source followers, together with switches multiplexing between reset voltage and signal voltage, are employed to mimic the pixel operation. No column gain amplifiers are used and the source follower outputs are directly connected to the column SS-ADCs. The main counting 1.7 GHz clock is generated externally and buffered on chip, while both the timing control and the global ramp are generated on chip.

Fig. 3.1. Block diagram of (a) 3D image sensor chip; (b) 96-column digitizer prototype.

# **3.3. Proposed Techniques**

The column-parallel digital counters and comparators are critical blocks for digitizing the analog pixel information level into digital numbers (DNs). The two proposed techniques, passing window (PW) and double auto-zeroing (AZ), are dedicated to improving the performance of digital counters and comparators, respectively.

# 3.3.1. Passing Window Compatible with CDS

In the conventional SS-ADC, the ripple counter topology [38] is a popular choice for the digital counter. First, the architecture is simple with only a single line of cascaded Dflip flops resulting in an area efficient solution. Second, no synchronization circuits are demanded. Thirdly, a ripple counter capable of doing both up and down counting makes digital CDS subtraction possible in every column. However, a main issue with ripple counter topology in high-speed SS-ADCs is that the lower-bit D-flip flops are always counting at high frequency until the STOP signal from the comparator is generated.

To address this issue, a hybrid column counter scheme was proposed first in [39]. The digital counter is divided into two parts: 1) a lower 5-bit global counter shared by 248 column memories and 2) an upper 9-bit column-based ripple counter. In this partitioning manner, replacing 5-bit continuous running D-flip flops with memory cells sharing one global counter, power can be saved. However, if the memory cells in columns are implemented as transparent standard-cell latches [29], before the comparator output flips, the high-speed LSB data buses are always refreshing the memory cells. As the comparator output can flip at any time, the memory cells in [29] needs to be connected to the global LSB counter bus all the time before the latching moment. The power needed for charging and discharging the capacitors in the memory cells is wasted, as the relevant counting information is only captured at the latching instant STOP as shown in Fig. 3.2 (a). Only after the latching signal is generated can the memory cells be latched to the data and saved for readout before the next horizontal scan.

Fig. 3.2 (b) shows the improved latching scheme with the proposed PW technique. The PW digital switch disconnects the memory cells from the global data bus during non-relevant timing which not only allows power minimization in the column memories, but also enables power savings due to the lower capacitance driven by the data bus drivers. It is possible to generate a PW based on delaying the comparator output [20] as shown in Fig. 3.2 (b). However, with this method, the real latching moment is also delayed which introduces a PVT dependent offset and affects the performance of the SS-ADC. In [28], a look-ahead (LA) circuit consisting of a dynamic comparator (D-CMP) and logic in each column together with a globally shared early ramp generator, was proposed to cut unnecessary power consumed by the static comparator (S-CMP) and digital counter. This approach, however, requires complex circuitry. Moreover, the power saved through gating the high-speed clock until decision of D-CMP is limited.

Fig. 3.2. Global counter latching scheme: (a) without passing window; (b) with passing window.

In this design, the hold-and-go counting scheme as defined in [41] is adjusted to generate the PW, which makes the proposed PW technique fully compatible with the digital CDS. Fig. 3.3 (a) and (b) show the proposed CDS timing scheme of the SS-ADC within one horizontal scan under bright and dark illumination condition, respectively. The column-parallel digital counter contains a FLAG generation circuit, a reset counter

and a signal counter composed of LSB memories and a most significant bit (MSB) counter. The conventional digital CDS operation demands the following procedures: 1) Quantize the reset information corresponding to T1 in the reset readout phase ( $\Phi_{rst}$ ); 2) Quantize the signal information corresponding to T3 in the signal readout phase ( $\Phi_{sig}$ ); 3) Subtract the reset information (T1) from the signal information (T3) in the digital domain. In the proposed CDS scheme, by splitting T into T1 and T2, T3 into T and T4, the real pixel information level can be expressed as:

$$Tpixel = T3 - T1 = (T4 + T) - (T - T2) = T4 + T2$$

(3.1)

where T is the full counting time of the reset counter, T2 is the time left for the reset counter to count to full starting from T1. T4 is defined as the time difference from the moment when the signal counter start counting to the moment when the comparator output flips during  $\Phi_{sig}$ . Based on this definition, T4 is always equal to T3 – T and can become negative when T3 < T under dark illumination condition as shown in Fig. 3.3 (b). Thus instead of quantizing T1 and T3 separately, single capture of T4 + T2 in the signal counter is possible following the procedures below:

- 1) During  $\Phi_{rst}$ , the reset counter is enabled at the same moment that the ramp starts and stops when VRAMP crosses with VPIXELrst. T1 is then saved on the reset counter.

- 2) During  $\Phi_{sig}$ , the signal counter and the LSB global counter start counting time of T later than the start of the ramp. When VRAMP crosses with VPIXELsig, the reset counter resumes counting from saved T1. The PW switches are then closed allowing

the LSB data buses to refresh the LSB memory cells in the signal counter.

3) During  $\Phi_{sig}$ , the state when the reset counter counts to its full range is detected by the FLAG generation circuit. The generated DATASTOP signal opens the PW switches and disconnects the LSB memory cells from the LSB data buses. As the LSB memory cells are latched, the cascaded MSB counter also stops.