# DESIGN TECHNIQUES FOR HIGH PERFORMANCE SERIAL LINK TRANSCEIVERS

A Dissertation

by

## **BYUNGHO MIN**

Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

Chairs of Committee, Samuel Palermo Sebastian Hoyos

Laszlo B. Kish

Duncan M Walker

Head of Department, Miroslav Begovic

May 2017

Major Subject: Electrical Engineering

Copyright 2017 Byungho Min

#### **ABSTRACT**

Increasing data rates over electrical channels with significant frequency-dependent loss is difficult due to excessive inter-symbol interference (ISI). In order to achieve sufficient link margins at high rates, I/O system designers implement equalization in the transmitters and are motivated to consider more spectrally-efficient modulation formats relative to the common PAM-2 scheme, such as PAM-4 and duobinary.

The first work, reviews when to consider PAM-4 and duobinary formats, as the modulation scheme which yields the highest system margins at a given data rate is a function of the channel loss profile, and presents a 20Gb/s triple-mode transmitter capable of efficiently implementing these three modulation schemes and three-tap feed-forward equalization. A statistical link modeling tool, which models ISI, crosstalk, random noise, and timing jitter, is developed to compare the three common modulation formats operating on electrical backplane channel models. In order to improve duobinary modulation efficiency, a low-power quarter-rate duobinary precoder circuit is proposed which provides significant timing margin improvement relative to full-rate precoders.

Also as serial I/O data rates scale above 10 Gb/s, crosstalk between neighboring channels degrades system bit-error rate (BER) performance. The next work presents receive-side circuitry which merges the cancellation of both near-end and far-end crosstalk (NEXT/FEXT) and can automatically adapt to different channel environments and variations in process, voltage, and temperature.

NEXT cancellation is realized with a novel 3-tap FIR filter which combines two traditional FIR filter taps and a continuous-time band-pass filter IIR tap for efficient crosstalk cancellation, with all filter tap coefficients automatically determined via an on-die sign-sign least-mean-square (SS-LMS) adaptation engine. FEXT cancellation is realized by coupling the aggressor signal through a differentiator circuit whose gain is automatically adjusted with a power-detection-based adaptation loop.

In conclusion, the proposed architectures in the transmitter side and receiver side together are to be good solution in the high speed I/O serial links to improve the performance by overcome the physical channel loss and adjacent channel noise as the system becomes complicated.

#### **DEDICATION**

To my parents, brother, sister and parents-in-law, and to my dearest wife, Jina, and adorable daughter and son, Boyoung and Seungchan

I dedicate my dissertation work to my family and many friends. Especially, I am grateful to my lovely wife and two children, Jina, Boyoung, and Seungchan for their love, encouragement, patience and sacrifice during the challenges of graduate school and life. I am truly thankful for having you in my life. This work is also dedicated to my loving parents, Eui-Sik and Sae-geun, who have always loved me unconditionally. I would not have successively finished this long journey without them.

#### **ACKNOWLEDGMENTS**

I would like to express my gratitude to my advisor, Dr. Samuel Palermo, whose expertise, understanding, and patience, added considerably to my graduate experience. I appreciate his vast knowledge and skills in analog and mixed circuit and system design in serial link I/O, and his assistance in writing papers. I also want to thank my PhD committee members, Dr. Kish, Dr. Peter, and Dr. Duncan M Walker, for agreeing to serve on my committee and for taking time out from their busy schedule.

I would like to thank the graduate students who worked with me on my research projects at Texas A&M University; namely, Noah Hae Yang, Keetaek Kim.

I also want to express my appreciation to all my colleagues, Younghoon, and Ehsan Zhian-Tabasy, in the TAMU Analog and Mixed Signal Center (AMSC) for helpful conversations regarding research and course projects. Furthermore, special thanks goes to the secretary of AMSC group, Ella Gallagher, for her kind help.

I wish to thank my internship mentor, Jongshin at Samsung electronics, and Jeff at Freescale to give me deep insight into the serdes IO.

I would also like to thank my family for the support they provided me through my entire life and in particular, my wife, Jina, Kids Boyoung and Seungchan for giving me strength to work and live. I owe them especial thank for their patience and love to keep me staying on this journey. I would like to dedicate this thesis to them.

## **NOMENCLATURE**

CMOS Complementary Metal Oxide Semiconductor

I/O Input and Output

ISI Inter-Symbol Interference

MUX Multiplexing

DMUX De-Multiplexing

CML Current Mode Logic

DJ Deterministic Jitter

RJ Random Jitter

PAM Pulse-amplitude modulation

CTLE Continuous Time Linear Equalization

UI Unit Interval

BER Bit Error Rate

FFE Feed-forward equalization

TX Transmitter

RX Receiver

PRBS Pseudo-Random Binary Sequency

FIR Finite Impulse Response

PCB Printed Circuit Board

DAC Digital-to-Analog Converter

NEXT Near-end crosstalk

FEXT Far-end crosstalk

FIR Finite impulse response

IIR Infinite impulse response

Serdes Serilaizer/Deserializer

PJ Periodic jitter

DDJ Data dependent jitter

DCD duty cycle jitter

ZFE Zero forcing equalizer

LMS Least mean square

DFE Decision feedback equalization

MSLE Maximum likelihood sequence estimator

## **TABLE OF CONTENTS**

|                                                                                            | Page |

|--------------------------------------------------------------------------------------------|------|

| ABSTRACT                                                                                   | ii   |

| DEDICATION                                                                                 | iv   |

| ACKNOWLEDGMENTS                                                                            | V    |

| NOMENCLATURE                                                                               | vi   |

| TABLE OF CONTENTS                                                                          | viii |

| LIST OF FIGURES                                                                            | xi   |

| LIST OF TABLES                                                                             | xv   |

| I. INTRODUCTION                                                                            | 1    |

| I.1. MotivationI.2. Dissertation Organization                                              |      |

| II. BACKGROUND                                                                             | 5    |

| II.1.Transceiver Design Consideration                                                      |      |

| II.1.2. Channel Loss.                                                                      |      |

| II.1.2.1. Propagation Constant                                                             |      |

| II.1.2.1.1. Loss due to Metal Conductivity II.1.2.1.2. Loss due to Dielectric Loss Tangent |      |

| II.1.2.1.3. Loss due to Conductivity of Dielectric                                         |      |

| II.1.2.1.4. Loss due to Radiation                                                          |      |

| II.1.3. Crosstalks                                                                         |      |

| II.1.3.1. Near-end Crosstalk                                                               |      |

| II.1.3.2. Far-end Crosstalk.                                                               |      |

| II.1.4. Jitter                                                                             |      |

| II.1.4.1. Random Jitter (RJ)                                                               | 16   |

| II.1.4.2. Deterministic Jitter (DJ)                                                        |      |

| II.2. Transmitter Design Consideration                                                     | 18   |

| II.2.1. Transmitter Equalization Techniques                                                | 18   |

| II.2.1.1. Linear Transmitter Equalizer                                                     | 20   |

| II.2.1.1.1. Zero Forcing Equalizer (ZFE)                                                   |      |

| II.2.1.1.2. Least Mean Square (LMS) Equalizer                                              | 21   |

| II.2.1.2. Non-Linear Transmitter Equalizer                             | 22  |

|------------------------------------------------------------------------|-----|

| II.2.1.2.1. Decision Feedback Equalization (DFE)                       | 22  |

| II.2.1.2.2. Maximum Likelihood Sequence Estimator (MSLE)               | 22  |

| II.2.2. Transmitter Modulation Technique                               |     |

| II.3. Receiver Design Consideration                                    |     |

| II.3.1. Continuous-Time Linear Equalizer                               |     |

| II.3.2. Non-Linear Equalizer (Decision Feedback Equalizer)             | 30  |

| II.3.2.1. Full-rate DFE                                                | 30  |

| II.3.2.2. Half-rate DFE                                                | 31  |

| III. TRANSMITTER DESIGN                                                | 33  |

| III.1. Introduction                                                    | 33  |

| III.2. Modulation Techniques                                           |     |

| III.2.1.Overview of PAM-2, PAM-4, and Duobinary Signaling              |     |

| III.2.2. Modulation Selection.                                         |     |

| III.3. Statistical BER Modeling                                        |     |

| III.4. Transmitter Design                                              |     |

| III.4.1. System Architecture                                           |     |

| III.4.2. Duobinary Precoder Design.                                    |     |

| III.5. Experimental Results                                            |     |

| IV. RECEIVE-SIDE NEAR-END AND FAR-END CROSSTALK CANCELLATION CIRCUITRY | 73  |

| IV.1. Introduction                                                     |     |

| IV.2.NEXT/FEXT Cancellation System Architecture                        |     |

| IV.2.1. Channel Model                                                  |     |

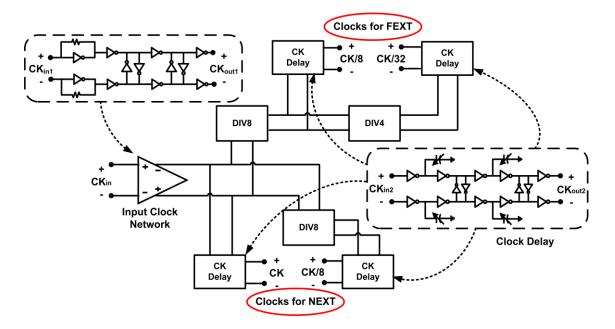

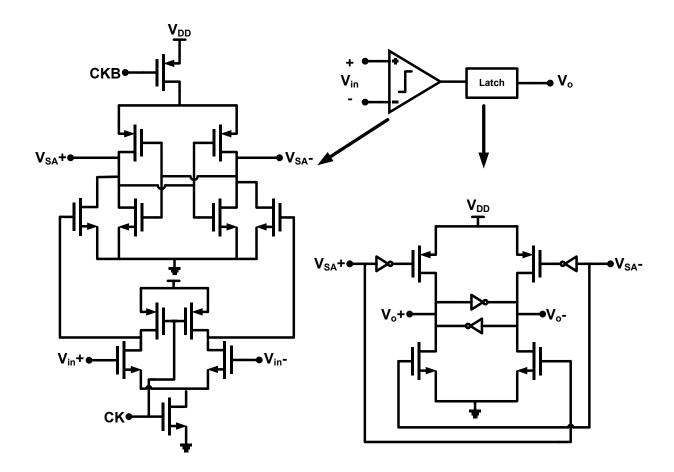

| IV.2.2. Clock Distribution.                                            |     |

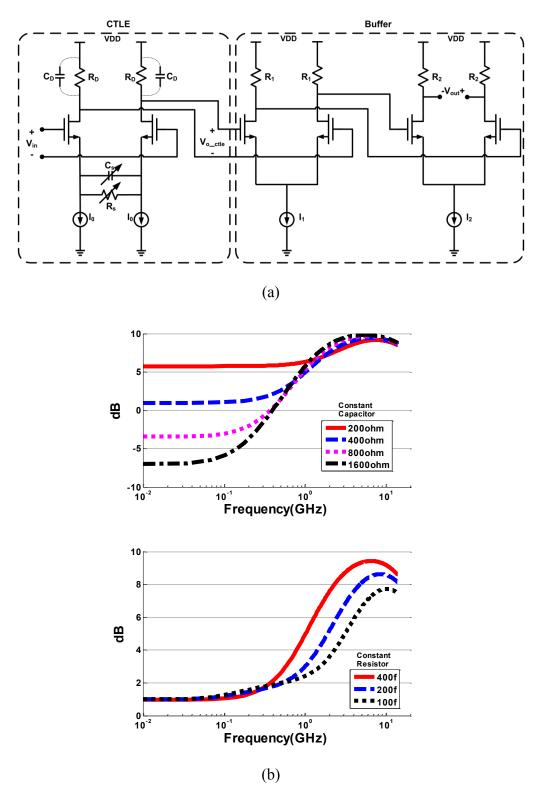

| IV.2.3. CTLE & Buffer.                                                 |     |

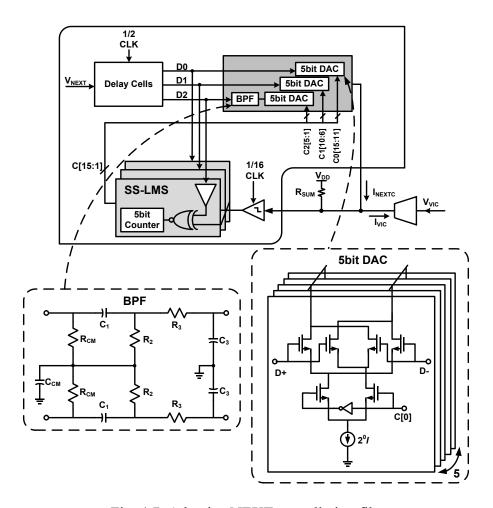

| IV.3. Proposed NEXT Architecture                                       |     |

| IV.3.1. Input Delay Cell                                               |     |

| IV.3.2. DAC & Band Pass Filter.                                        |     |

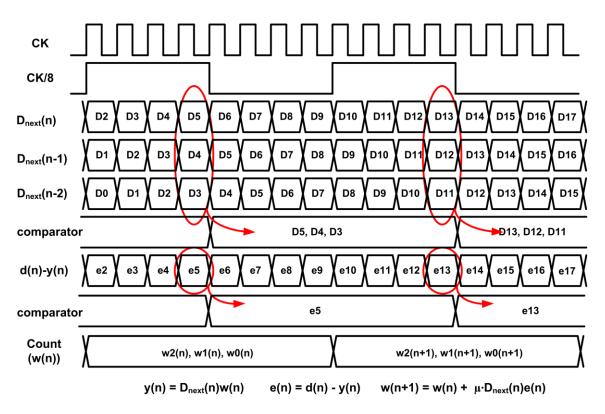

| IV.3.3. Comparator Block                                               |     |

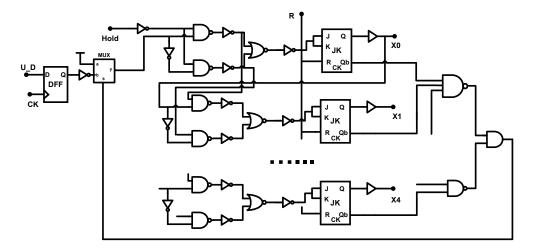

| IV.3.4. Counter Block                                                  |     |

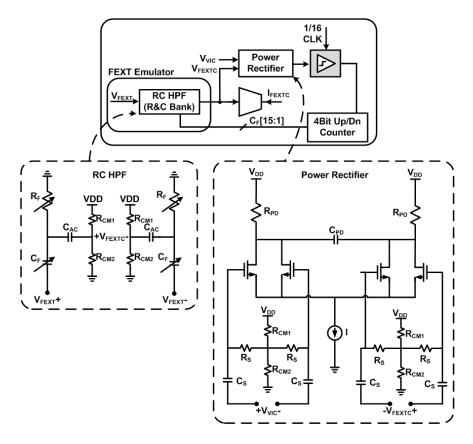

| IV.4. Proposed FEXT Architecture                                       |     |

| IV.4.1. RC Bank                                                        |     |

| IV.4.2. Power Rectifier & Comparator                                   |     |

| IV.4.3. Counter Block                                                  |     |

| IV.5. Experimental Results.                                            | 99  |

| IV.6. Summary                                                          |     |

| V. CONCLUSION AND FUTURE WORK                                          | 105 |

| V.1. Conclusion                       | 105 |

|---------------------------------------|-----|

| V.2. Recommendations For Future Work. | 107 |

|                                       |     |

| REFERENCES                            | 109 |

## LIST OF FIGURES

|            |                                                                                                 | Page |

|------------|-------------------------------------------------------------------------------------------------|------|

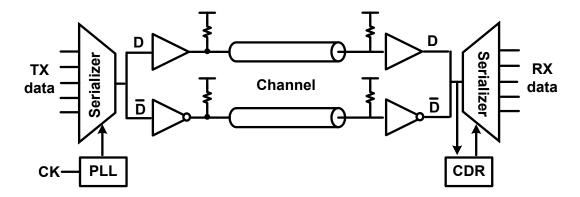

| Fig. 2.1.  | Block diagram of the Serdes transceiver                                                         | 6    |

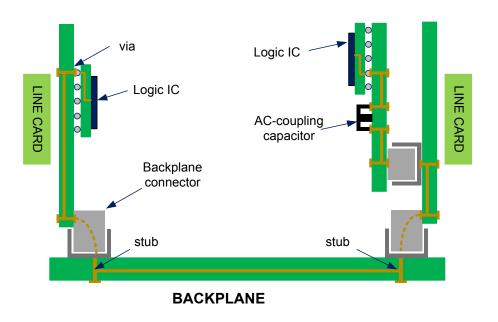

| Fig. 2.2.  | Backplane channel                                                                               | 7    |

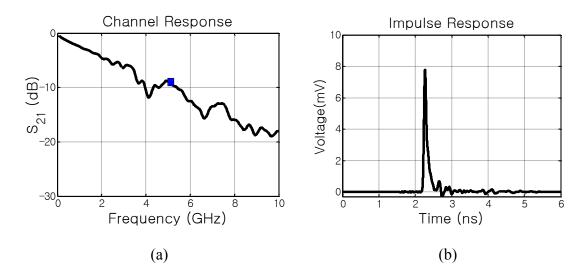

| Fig. 2.3.  | (a) Channel response, (b) Impulse response                                                      | 8    |

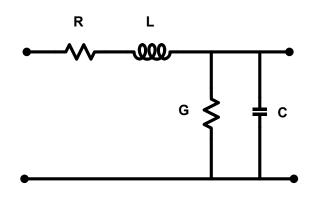

| Fig. 2.4.  | RLGC network                                                                                    | 8    |

| Fig. 2.5.  | Block diagram of crosstalk noise                                                                | 13   |

| Fig. 2.6.  | (a) Next channel, (b) Next impulse response                                                     | 14   |

| Fig. 2.7.  | (a) Fext channel, (b) Fext impulse response                                                     | 15   |

| Fig. 2.8.  | (a) Channel response, (b) Unequalized and equalized impulse response.                           | 18   |

| Fig. 2.9.  | (a) Raw data, (b) 3-tap Equalized data                                                          | 18   |

| Fig. 2.10. | (a) Unequalized eye-diagram, (b) Equalized eye-diagram                                          | 19   |

| Fig. 2.11. | The structure of a maximum likelihood sequence equalizer (MLSE) with an adaptive matched filter | 23   |

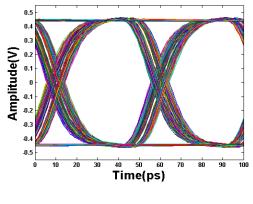

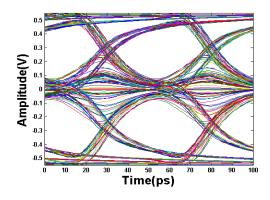

| Fig. 2.12. | Eye diagrams of the three common modulation formats (a) PAM-2, (b) PAM-4, (c) duobianry         | 25   |

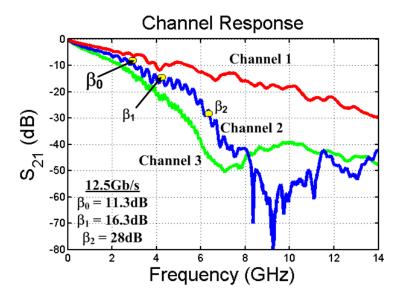

| Fig. 2.13. | Frequency response of three backplane channels                                                  | 27   |

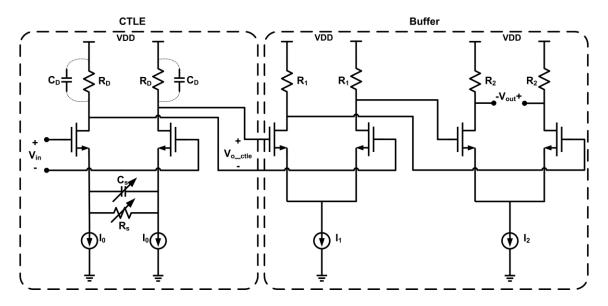

| Fig. 2.14. | CTLE & Buffer schematic                                                                         | 29   |

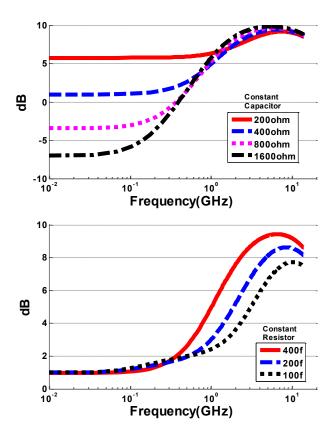

| Fig. 2.15. | CTLE simulation results                                                                         | 29   |

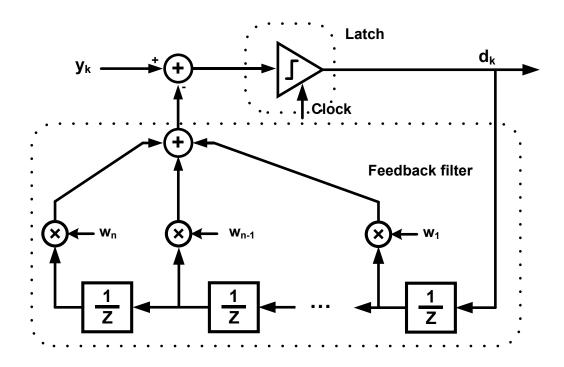

| Fig. 2.16. | Full-rate Decision Feedback Equalizer                                                           | 30   |

| Fig. 2.17. | Half-rate Decision Feedback Equalize.                                                           | 31   |

| Fig. 3.1.  | High-Speed link block diagram with triple-mode transmitter and ADC-based receiver               | 33   |

| Fig. 3.2.  | Eye diagrams and power-spectral density of the three common modulation formats of PAM-2.                                                                                      | 36 |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig. 3.3.  | Eye diagrams and power-spectral density of the three common modulation formats of PAM-4                                                                                       | 37 |

| Fig. 3.4.  | Eye diagrams and power-spectral density of the three common modulation formats of duobinary                                                                                   | 38 |

| Fig. 3.5.  | Frequency response of three backplane channels                                                                                                                                | 40 |

| Fig. 3.6.  | Maximum achievable data rate with channel 3 based on the number of TX-FFE taps for the three modulation schemes                                                               | 44 |

| Fig. 3.7.  | 10Gb/s eye diagrams with channel 1. Solid lines are transient 1k-bit simulations and dashed lines are BER=10 <sup>-12</sup> contours obtained from the statistical link model | 47 |

| Fig. 3.8.  | 10Gb/s eye diagrams with channel 2. Solid lines are transient 1k-bit simulations and dashed lines are BER=10 <sup>-12</sup> contours obtained from the statistical link model | 48 |

| Fig. 3.9.  | 8Gb/s eye diagrams with channel 3. Solid lines are transient 1k-bit simulations and dashed lines are BER=10 <sup>-12</sup> contours obtained from the statistical link model  | 49 |

| Fig. 3.10. | 8Gb/s eye height degradation with crosstalk for channel 3                                                                                                                     | 52 |

| Fig. 3.11. | 8Gb/s eye degradation vs. random jitter for channel 3                                                                                                                         | 52 |

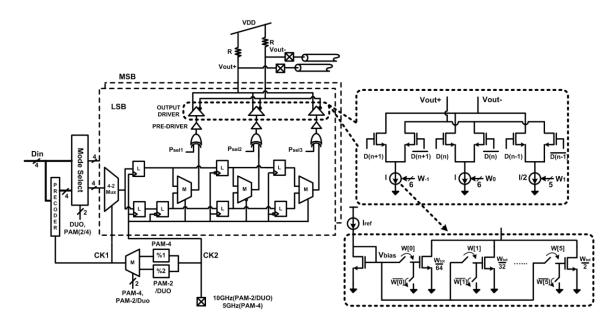

| Fig. 3.12. | Triple-mode transmitter architecture                                                                                                                                          | 53 |

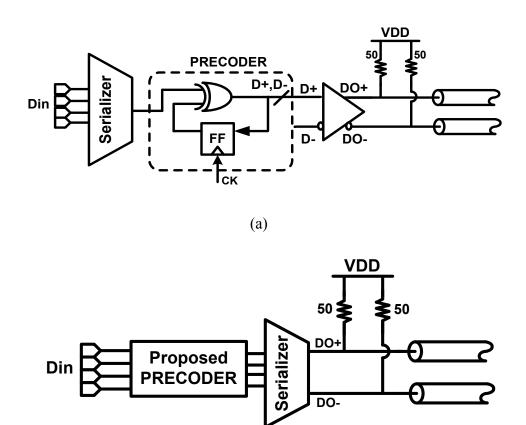

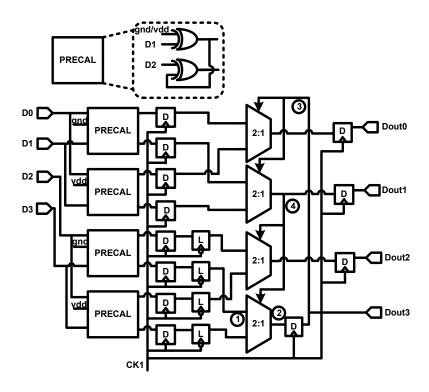

| Fig. 3.13. | Precoder implementations. (a) Full-rate architecture. (b) Proposed parallel quarter-rate architecture.                                                                        | 56 |

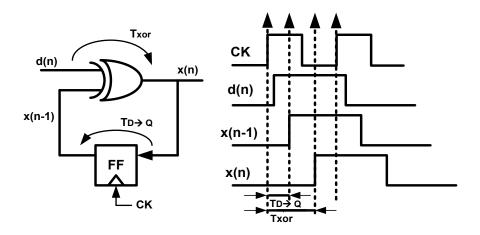

| Fig. 3.14. | General full-rate precoder timing diagram                                                                                                                                     | 56 |

| Fig. 3.15. | Modified full-rate precoder timing diagram                                                                                                                                    | 57 |

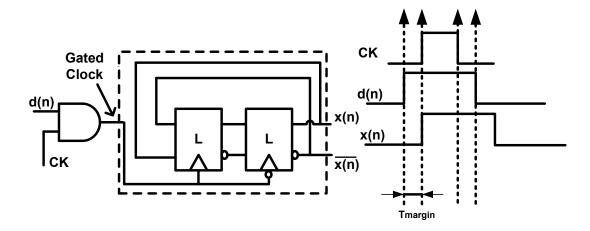

| Fig. 3.16. | Parallel quarter-rate precoder circuit.                                                                                                                                       | 58 |

| Fig. 3.17. | Parallel quarter-rate precoder timing diagram.                                                                                                                                | 59 |

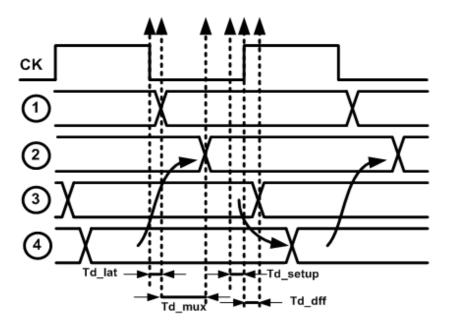

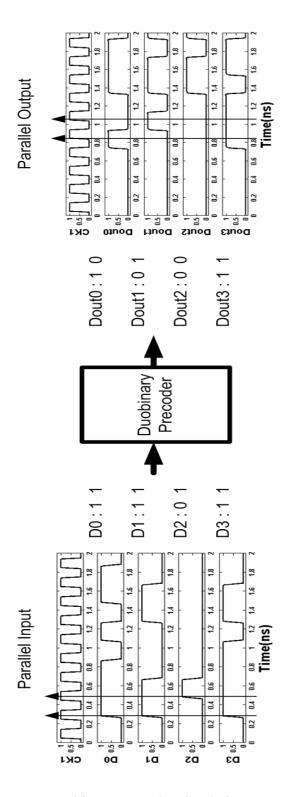

| Fig. 3.18. | Duobinary precoder simulation at 5GHz                                                                                                                                         | 61 |

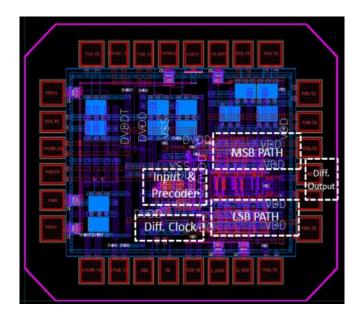

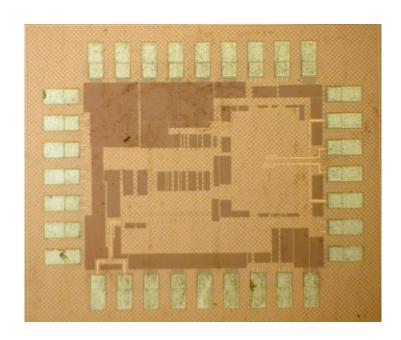

| Fig. 3.19. | Triple-mode transmitter chip layout                                                                          | 62 |

|------------|--------------------------------------------------------------------------------------------------------------|----|

| Fig. 3.20. | Microphotograph of chip                                                                                      | 62 |

| Fig. 3.21. | 10Gb/s PAM-2 eye diagram from designed transmitter operating with channel 1                                  | 64 |

| Fig. 3.22. | 10Gb/s PAM-4 eye diagram from designed transmitter operating with channel 2                                  | 64 |

| Fig. 3.23. | 8Gb/s duobinary eye diagram from designed transmitter operating with channel 3                               | 64 |

| Fig. 3.24. | 20Gb/s eye diagrams from designed transmitter operating with an ideal channel                                | 65 |

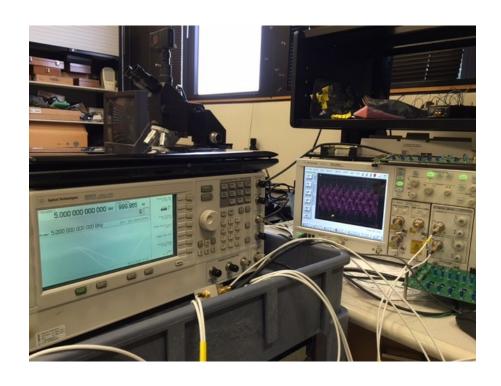

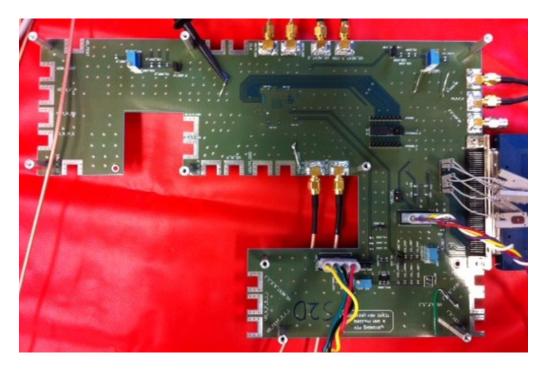

| Fig. 3.25. | Testing PCB board                                                                                            | 66 |

| Fig. 3.26. | Measurement setup                                                                                            | 67 |

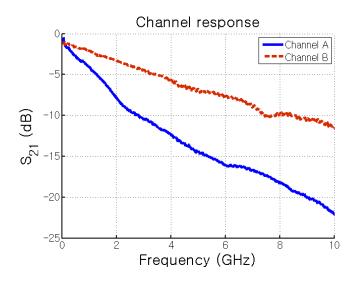

| Fig. 3.27. | Channel response (a) short channel (Channel A), and (b) long channel (Channel B)                             | 67 |

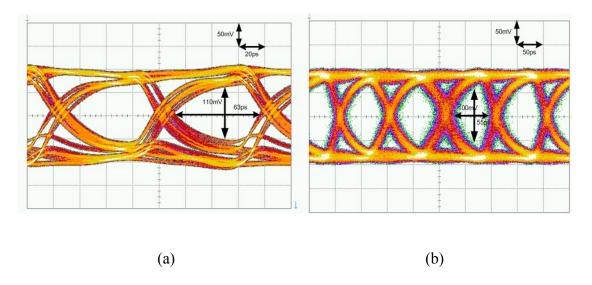

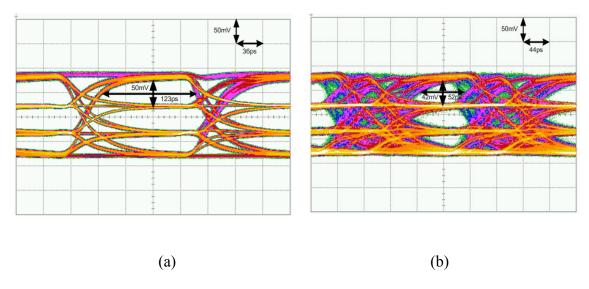

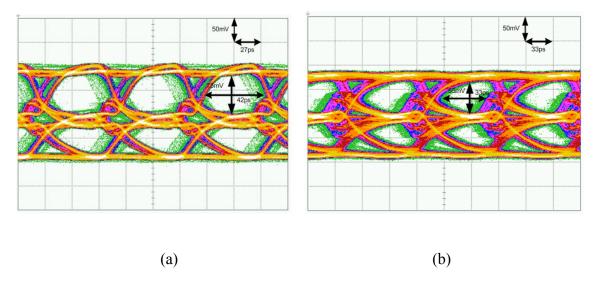

| Fig. 3.28. | (a)12.5Gb/s PAM-2 eye diagram with short channel, and (b) 10Gb/s PAM-2 eye diagram with long channel         | 69 |

| Fig. 3.29. | (a)12.5Gb/s PAM-4 eye diagram with short channel, and (b) 10Gb/s PAM-4 eye diagram with long channel         | 69 |

| Fig. 3.30. | (a)12.5Gb/s Duobinary eye diagram with short channel, and (b) 10Gb/s Duobinary eye diagram with long channel | 70 |

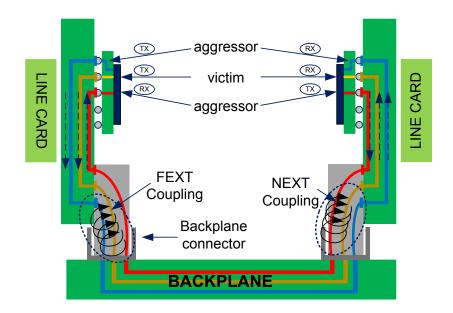

| Fig. 4.1.  | NEXT and FEXT crosstalk in a backplane channel environment                                                   | 76 |

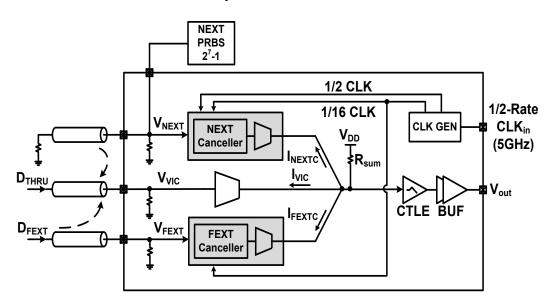

| Fig. 4.2.  | Receive-side adaptive NEXT and FEXT cancellation circuitry                                                   | 76 |

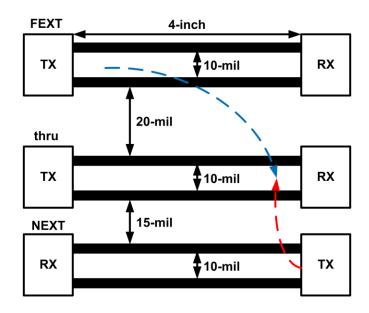

| Fig. 4.3.  | Channel environment                                                                                          | 79 |

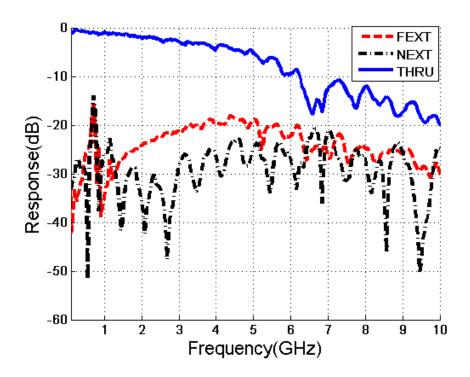

| Fig. 4.4.  | Channel response                                                                                             | 80 |

| Fig. 4.5.  | Clock distribution                                                                                           | 81 |

| Fig. 4.6.  | (a) CTLE & Buffer schematic, and (b) CTLE simulation results                                                 | 83 |

| Fig. 4.7.  | Adaptive NEXT cancellation filter                                                                            | 84 |

| Fig. 4.8.  | Timing Diagram for SS-LMS algorithm                                                                                              | 86  |

|------------|----------------------------------------------------------------------------------------------------------------------------------|-----|

| Fig. 4.9.  | NEXT cancellation filter input retiming block                                                                                    | 87  |

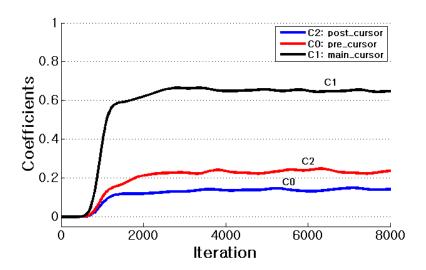

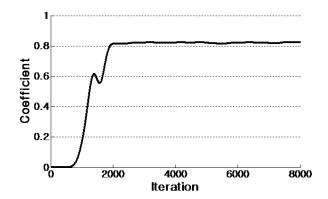

| Fig. 4.10. | NEXT cancellation filter coefficients convergence behavior with the SS-LMS adaptation loop.                                      | 88  |

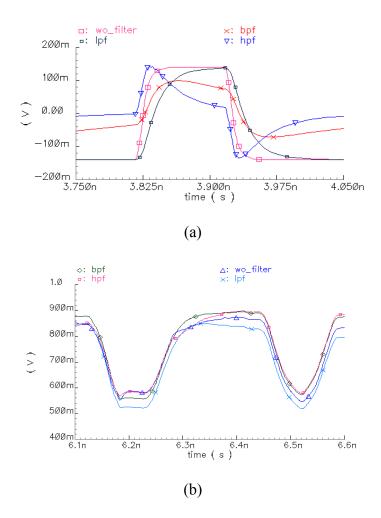

| Fig. 4.11. | (a) Inputs to DAC, and (b) Outputs after noise cancellation                                                                      | 90  |

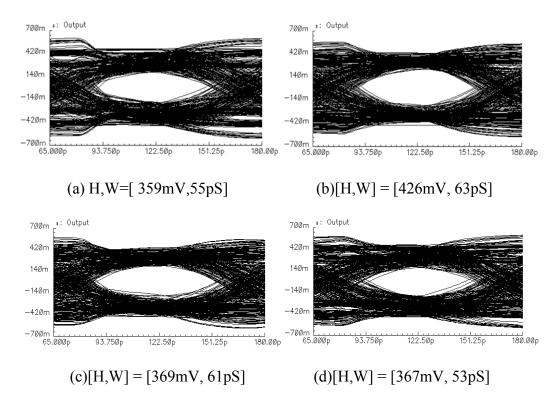

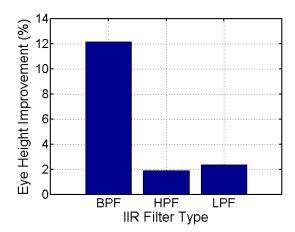

| Fig. 4.12. | Eye diagram of (a) without filter, (b) with BPF, (c) with HFP, and (d) with LFP                                                  | 91  |

| Fig. 4.13. | 10Gb/s eye height improvement, relative to a traditional 3-tap FIR filter, by including an IIR tap                               | 92  |

| Fig. 4.14. | Low-power dynamic comparator used in the NEXT and FEXT adaptation loop.                                                          | 93  |

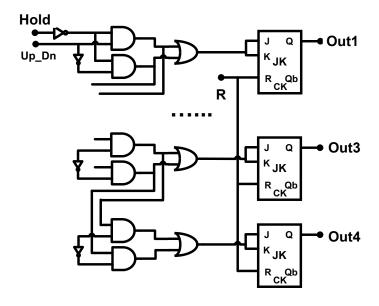

| Fig. 4.15. | 5bit counter                                                                                                                     | 94  |

| Fig. 4.16. | FEXT canceller                                                                                                                   | 95  |

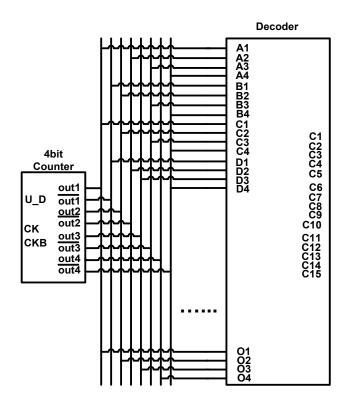

| Fig. 4.17. | 4bit counter                                                                                                                     | 98  |

| Fig. 4.18. | Thermometer decoder                                                                                                              | 98  |

| Fig. 4.19. | FEXT cancellation filter digitally-controlled capacitor bank convergence behavior with the power-detection-based adaptation loop | 99  |

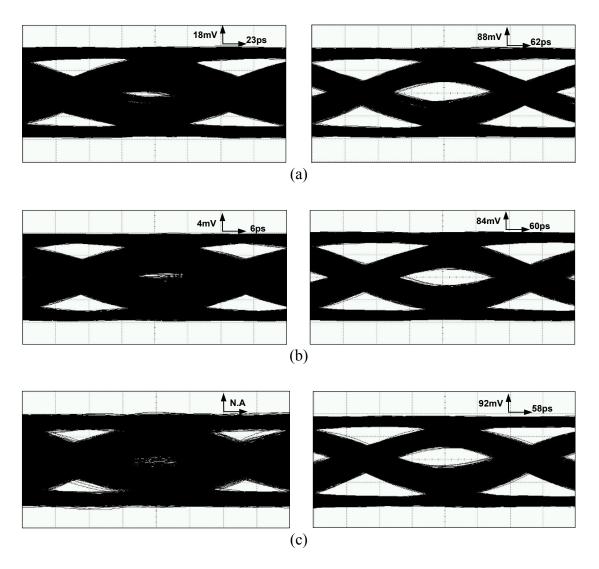

| Fig. 4.20. | Eye-diagrams of (a) NEXT canceller off vs. on, (b) FEXT canceller off vs. on, and (c)Both cancellers off vs. on                  | 100 |

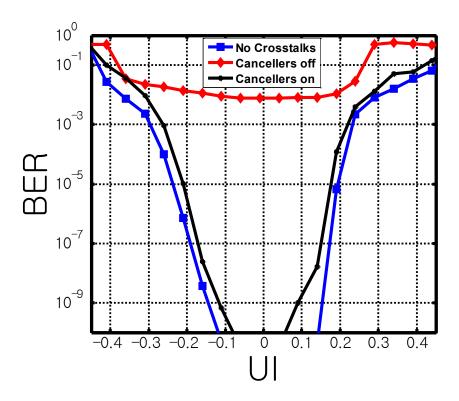

| Fig. 4.21. | Bath-tub plot                                                                                                                    | 102 |

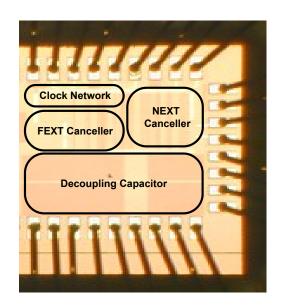

| Fig. 4.22. | Microphotograph of chip                                                                                                          | 102 |

| Fig. 4.23. | PCB board                                                                                                                        | 103 |

## LIST OF TABLES

|            |                                                        | Page |

|------------|--------------------------------------------------------|------|

| Table 3.1. | Modulation selection                                   | 42   |

| Table 3.2. | 10Gb/s FFE coefficients and link margin with channel 1 | 44   |

| Table 3.3. | 10Gb/s FFE coefficients and link margin with channel 2 | 45   |

| Table 3.4. | 8Gb/s FFE coefficients and link margin with channel 3  | 46   |

| Table 3.5. | Summary of results                                     | 63   |

| Table 3.6. | Transmitter comparison                                 | 63   |

| Table 3.7. | Test results                                           | 71   |

| Table 4.1. | Performance comparison                                 | 104  |

| Table 4.2. | CHIP Power Breakdown                                   | 104  |

#### I. INTRODUCTION

#### I.1. Motivation

Inter-chip communication at high data rates over standard electrical channels is challenging due to excessive frequency-dependent channel attenuation which causes large amounts of inter-symbol interference (ISI). Transmitters with feed-forward equalization (FFE) are often employed in order to operate reliably over such channels at high data rates [1], [2]. However, due to transmit peak-power limitations imposed by shrinking CMOS power supplies, only incremental performance improvement is achieved by increasing transmitter equalization complexity past two or three taps [3]. This motivates I/O system designers to consider modulation techniques which provide spectral efficiencies higher than simple binary PAM2 signaling in order to increase data rates over band-limited channels, with the most commonly proposed modulation schemes being PAM4 and duobinary. However, again due to transmit peak-power limitations, the optimal modulation which yields the best system margins is a function of the channel loss profile and the desired data rate. Examples of high-speed serial I/O transmitters which implement these different modulation formats include [2], [4], [5].

The work of [2], [4] implements a transmitter which is compatible with PAM2 and PAM4 modulation, but does not support duobinary due to the absence of the precoder necessary to avoid error propagation. Custom designed transmitters for each modulation scheme are compared in [5], which implements the duobinary transmitter with a full-rate precoder. A transmitter which could efficiently support all three of these modulation formats would provide a high degree of flexibility to support different channel

environments and, for a given platform, the ability to scale to high data rate during periods of peak I/O bandwidth demand.

In addition, at data rates at or above 10 Gb/s, both intersymbol interference (ISI) due to channel frequency-dependent loss and crosstalk interference due to multi-channel coupling must be considered in order to ensure adequate system bit-error rate (BER). While equalizers are effective in cancelling ISI, topologies such as receive-side FIR filters and continuous-time linear equalizers (CTLE) don't improve the signal-to-crosstalk ratio, motivating the use of dedicated circuitry to cancel both near-end crosstalk (NEXT) and far-end crosstalk (FEXT).

An effective approach to cancel NEXT involves passing the known aggressor transmit data through an FIR filter to sum with the incoming signal at the victim receiver. One key limitation of this approach is that the NEXT signal is only canceled out to the span of the FIR filter, leading to relatively long 5-7 tap implementations [1], [2]. At the receiver side, efficient cancellation of FEXT is possible by passing the aggressor signal through a high-pass filter which acts as a differentiator to emulate the FEXT signal [3]-[5]. With these crosstalk cancellation schemes, in order to seamlessly support operation with different channels and allow for robustness to variations in process, voltage, and temperature, adaptive tuning of all the filter coefficients is required.

The main purpose of this dissertation was to understand both the achievements and limitations of previous works and to develop new design techniques for overcoming channel loss from transmitter side, and ISI from the receiver side.

### **I.2 Dissertation Organization**

This dissertation starts with the overview of serial link transceiver architectures in order to understand how the serial I/O transceivers can be implemented both systemically and in circuitry to overcome the physical channel loss and noise sources in Section II.

Section III discusses the modulation techniques to overcome the physical channel loss in the transmitter side. The proposed transmitter, which to the authors' knowledge, is the first to implement a triple mode (NRZ,PAM-4, and Duobinary)-supported architecture in one transmitter and it is detailed in this section.

Also, it discusses the use of precoder design, which has been shown in previous work [5] as an efficient technique to generate Duobinary data format. In addition, this section presents how the triple mode is implemented in an architecture using mode selection. Statistical analysis is included in order to understand and analyze each modes according to various physical channels. The transmitter experimental results from GP 90nm process are presented and summary is included.

Section IV presents a receive-side near-end and far-end crosstalk cancellation circuitry, which reduces both crosstalks, allowing for a significant reduction in clock distribution circuitry complexity and power. The proposed next architecture utilizes low frequency clock to save power and circuit complexity, which are presented comparing with the previous work. In addition, the newly proposed fext architecture shows the RC components are adaptively found in the feedback loop comparing to the previous works. Also, experimental results from GP 65 nm CMOS prototype are presented.

Finally, Section V summarizes the contributions of this dissertation and proposes suggestions for future works.

#### II. BACKGROUND<sup>1</sup>

## **II.1. Transceiver Design Consideration**

Increasing data rates over electrical channels with significant frequency dependent loss is difficult due to excessive inter-symbol interference (ISI) in the transceiver architecture like Fig. 2.1. In order to achieve sufficient link margins at high rates, I/O system designers implement equalization in the transmitters and are motivated to consider more spectrally-efficient modulation formats relative to the common PAM2 scheme, such as PAM4 and duobinary. Inter-chip communication at high data rates over standard electrical channels is challenging due to excessive frequency-dependent channel attenuation which causes large amounts of inter-symbol interference (ISI).

Transmitters with feed-forward equalization (FFE) are often employed in order to operate reliably over such channels at high data rates [1], [2]. However, due to transmit peak-power limitations imposed by shrinking CMOS power supplies, only incremental performance improvement is achieved by increasing transmitter equalization complexity past two or three taps [3]. This motivates I/O system designers to consider modulation techniques which provide spectral efficiencies higher than simple binary PAM2 signaling in order to increase data rates over band-limited channels, with the most commonly proposed modulation schemes being PAM4 and duobinary. However, again due to transmit peak-power limitations, the optimal modulation which yields the best system margins is a function of the channel loss profile and the desired data rate.

-

<sup>1.</sup> Reprinted with permission from "A 20Gb/s triple-mode(PAM-2,PAM-4, and duobinary) transmitter" by Byungho Min, Samuel Palermo, 2011, IEEE International Midwest Symposium on Circuits and Systems, pp.1-4, Copyright 2011 IEEE

Fig. 2.1. Block diagram of the Serdes transceiver.

Also at data rates at or above 10 Gb/s, crosstalk interference due to multi-channel coupling must be considered in order to ensure adequate system bit-error rate (BER). While equalizers are effective in cancelling ISI, topologies such as receive-side FIR filters and continuous-time linear equalizers (CTLE) don't improve the signal-to-crosstalk ratio, motivating the use of dedicated circuitry to cancel both near-end crosstalk (NEXT) and far-end crosstalk (FEXT). An effective approach to cancel NEXT involves passing the known aggressor transmit data through an FIR filter to sum with the incoming signal at the victim receiver. One key limitation of this approach is that the NEXT signal is only canceled out to the span of the FIR filter, leading to relatively long 5-7 tap implementations [6], [7]. At the receiver side, efficient cancellation of FEXT is possible by passing the aggressor signal through a high-pass filter which acts as a differentiator to emulate the FEXT signal [8]-[10]. With these crosstalk cancellation schemes, in order to seamlessly support operation with different channels and allow for

robustness to variations in process, voltage, and temperature, adaptive tuning of all the filter coefficients is required.

## II.1.1. Channel

Fig. 2.2. Backplane channel.

A traditional backplane implementation is shown in Fig. 2.2. For backplane channel, the issues of impedance, losses, via stubs, lumped parasitics have decreased system performance. As data rates have risen, the aforementioned defects are to be deleterious significantly, and I/O circuit design complexity increases. The device-to-package solder bump and package-to-board (line card) solder ball interfaces are high impedance signal path that cannot be controlled easily. Also backplane connector and stub can cause the impedance discontinuity.

Fig. 2.3. (a) Channel response, (b) Impulse response

Fig. 2.4. RLGC network

As shown in Fig. 2.3 (a), the channel frequency response has low-pass filter characteristic as the attenuation increases with distance, and it generates nulls in frequency response due to impedance discontinuity by via-stub or impedance mismatching. In addition, the impulse response will disperse in a general low-pass nature in Fig. 2.3. This causes inter-symbol interference (ISI) which creates the pre-

cursors and post-cursors. As pre-cursors interfere with previously sent bits, while post-cursors interfere with the following bits, ISI from multiple bits reduces timing and voltage margin in receiver.

#### II.1.2. Channel Loss

Skin effect is the tendency of an alternating electric current (AC) to become distributed within a conductor such that the current\_density is largest near the surface of the conductor, and decreases with greater depths in the conductor. The electric current flows mainly at the "skin" of the conductor, between the outer surface and a level called the skin depth. The skin effect causes the effective resistance of the conductor to increase at higher frequencies where the skin depth is smaller, thus reducing the effective cross-section of the conductor [10], [11], [12].

The cause of the skin effect is electromagnetic induction. A magnetic field is accompanied by an induced electric field, which in turn creates secondary currents and a secondary magnetic field. Consequently, both the total magnetic field and induced currents inside conductors are reduced when compared with the dc case. The skin effect and the dielectric loss can be analyzed with all the RLGC parameters in Fig. 2.4.

## II.1.2.1 Propagation Constant

Lossy copper transmission line is given by:

$$H(j\omega) = e^{-\gamma l} \tag{2-1}$$

where l is the length of the cable, and H(jw) is defined as the ratio between the output and input voltages of the cable ( $V_{out}$  and  $V_{in}$  respectively):

$$H(j\omega) = \frac{V_{out}(j\omega)}{V_{in}(j\omega)}$$

(2-2)

The complex propagation constant  $\gamma$  is defined in [10], [11], [12].

$$\gamma = \sqrt{(R + j\omega l)(G + j\omega C)} = \alpha + j\beta$$

(2-3)

where R is the distributed series resistance ( $\Omega/m$ ), L is the distributed inductance (H/m), G the distributed parallel conductance (S/m), C the distributed capacitance (F/m),  $\alpha$  the attenuation constant, and  $\beta$  the phase constant.

Losses in transmission lines are categorized into at least four elements such as metal loss, dielectric loss, conductivity loss, and loss due to radiation [11], [12].

$$\alpha = \alpha_c + \alpha_D + \alpha_G + \alpha_R \tag{2-4}$$

where  $\alpha_c$  is metal loss,  $\alpha_D$  dielectric loss,  $\alpha_G$  conductivity loss, and  $\alpha_R$  loss due to radiation.

## II.1.2.1.1 Loss due to Metal Conductivity

The metal loss is the most dominant one in the transmission lines. This element is proportional to  $\sqrt{f}$ . So the frequency goes higher, it will dominate overall loss. The sheet resistance is calculated as:

$$R_{SHEET} = \left(\frac{\pi f \mu_0 \mu_R}{\sigma}\right)^{1/2} \tag{2-5}$$

where Sigma ( $\sigma$ ) is the metal's conductivity,  $\mu 0$  permittivity in the air, and  $\mu R$  permittivity in the resistance.

$$\alpha_c = \frac{R'}{2Z_0} \tag{2-6}$$

R' is converted from  $R_{SHEET}$ , and  $Z_0$  is the characteristic impedance of the conductor.

$$R' = 0.8 * \frac{R_{SHEET}}{W} + 0.2 * \frac{R_{SHEET}}{W} = \frac{R_{SHEET}}{W}$$

(2-7)

where W is the width of the conductor. The first term is from the top of the strip, and the second one is from the bottom of the strip [11], [12].

## II.1.2.1.2 Loss due to Dielectric Loss Tangent

The loss due to dielectric loss tangent is one of important losses at high speed data rate. It is shown in a printed circuit board (PCB) design option as dissipation factor, "DF" as an abbreviation. This term is proportional to frequency; therefore it can be dominant factor in the total loss [11], [12].

$$\alpha_D = \tan(\delta) \frac{\omega C' Z_0}{2} \quad (\frac{Nepers}{meter})$$

(2-8)

where C' is Farads/meter. In this equation,  $tan(\delta)$  is expressed like the below.

Permittivity:

$$\varepsilon = \varepsilon' - j\varepsilon''$$

(2-9)

Loss tangent :

$$tan(\delta) = \varepsilon'/_{\varepsilon''}$$

(2-10)

## II.1.2.1.3 Loss due to conductivity of dielectric

$$\alpha_G = \frac{G' \cdot Z_0}{2} \quad (\frac{Nepers}{meter}) \tag{2-11}$$

where G' is siemens/meter.

The loss due to substrate conductivity term is often ignored because it's very small due to low conductivity [11], [12]. However silicon has relatively poor electrical insulating properties, so it should be considered in the total loss.

#### II.1.2.1.4 Loss due to Radiation

This is another attenuation mechanism that has a very small effect. It's more or less a leakage loss. It's hard to explain in the transmission line model, therefore 3D electromagnetic simulator is needed [12].

## II.1.3. Crosstalks

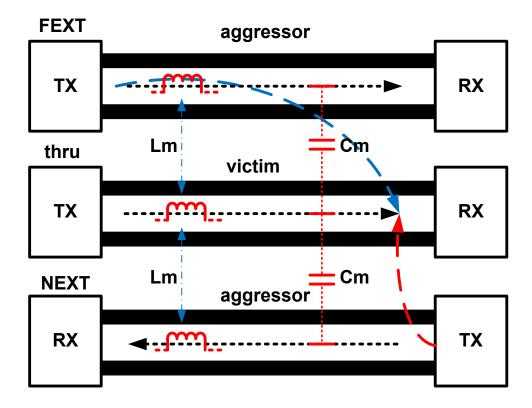

Crosstalk is the unwanted coupling of energy between two or more adjacent channels [10], [13]. It occurs when energy is coupled capacitively or inductively during data transition between them. Aggressor channel causes the crosstalk into the adjacent channel called the victim channel. As it is shown in the Fig. 2.5, there are two kinds of crosstalks such as near-end and far-end ones.

Fig. 2.5. Block diagram of crosstalk noise

## II.1.3.1 Near-end Crosstalk

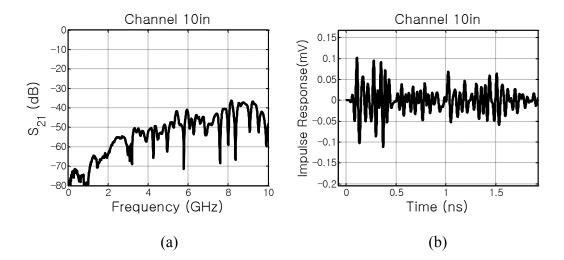

The energy coupled from the active signal line, the aggressor, onto a quiet passive victim line is transferred to the end of the victim line. This is known as near-end crosstalk in Fig. 2.6, which shows next channel response and next impulse response respectively. The frequency response has high-pass filter characteristic as it is shown in Fig. 2.6 (a).

Fig. 2.6. (a) Next channel, (b) Next impulse response

The magnitude of it is dependent on the mutual capacitance (Cm) and inductance (Lm) between the adjacent lines.

$$Next = \frac{1}{4} \left( \frac{C_m}{C} + \frac{L_m}{L} \right) \tag{2-12}$$

where Cm is the mutual capacitance between lines per unit length, Lm is the mutual inductance between lines per unit length, C is the capacitance per unit length, and L is the inductor per unit length of line.

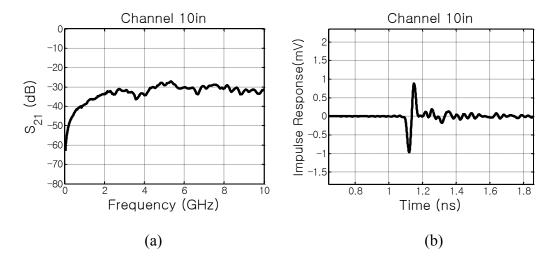

#### II.1.3.2 Far-end Crosstalk

Fig. 2.7. (a) Fext channel, (b) Fext impulse response

The coupled energy from the aggressor onto the victim line is travelling forward to the end of the victim line. It is called far-end crosstalk. Its magnitude is dependent on the Cm and –Lm between the adjacent lines.

$$Fext = \frac{1}{4} \left( \frac{C_m}{C} + \frac{-L_m}{L} \right) \tag{2-13}$$

where Cm is the mutual capacitance between lines per unit length, Lm is the mutual inductance between lines per unit length, C is the capacitance per unit length, and L is the inductor per unit length of line. Fig. 2.7 shows fext channel response and fext impulse response respectively, which shows fext channel response and fext impulse response respectively. The frequency response has band-pass filter characteristic as it is shown in Fig. 2.7 (a).

#### II.1.4. Jitter

Jitter is the deviation from true periodicity of a presumed periodic signal, often in relation to a reference clock source [10], [13], [14]. Jitter falls into two broad categories: random jitter and deterministic jitter which consists of data dependent jitter and periodic jitter. It can be described as a variation in the period of the signal. If we have a sine wave clock, it can be written like the below.

$$Clock = \sin(w * t) \tag{2-14}$$

which is a perfect clock without jitter.

Then jittery clock can be described like the below.

$$Clcok = \sin(w * t + j(t)) \tag{2-15}$$

where j(t) is a function of the jitter.

## II.1.4.1 Random Jitter (RJ)

This jitter is timing noise that cannot be predicted, because it's not caused by specific patterns. This is random process, so it is assumed to have a Gaussian distribution for the modeling. This results from differential and common mode stochastic noise processes such as power supply noise and thermal noise [15].

## II.1.4.2 Deterministic Jitter (DJ)

This jitter is also timing jitter that is repeatable and predictable. It is attributable to specific patterns or events. It's from sources such as rise/fall times, ISI, power supply feed through, oscillator wand, and cross-talk from other signals [13], [14], [15].

This consists of periodic jitter (PJ), data dependent jitter (DDJ), and duty cycle Jitter (DCD).

PJ repeats in a cycle fashion. Since any periodic waveform can be decomposed into a Fourier series of harmonic sinusoids, so it is called sinusoidal jitter. It's typically caused by external deterministic noise sources coupling into a system, such as switching power supply noise or a strong local RF carrier. It may also be caused by an unstable clock-recovery PLL [14].

DDJ is correlated with the bit sequence in a data stream. And it is often caused by the frequency response of a channel. It's also known as ISI [15].

DCD is predicted based on whether the associated edge is rising or falling. These are two common causes of DCD [14]. The one is the slew rate for the rising edges are different from the falling edges. The other is the decision threshold for a waveform is higher or lower than it should be.

# II.2. Transmitter Design Consideration

## II.2.1.Transmitter Equalization Techniques

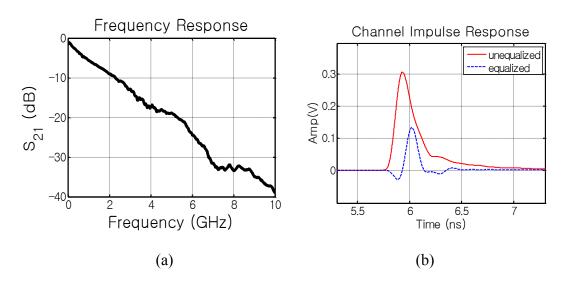

Fig. 2.8. (a) Channel response, (b) Unequalized and equalized impulse response

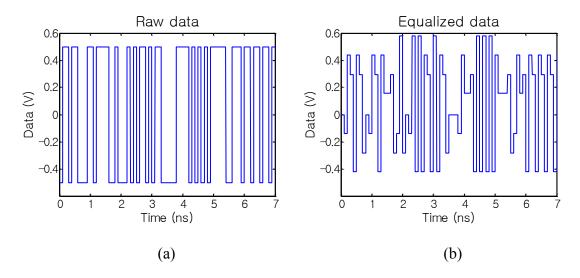

Fig. 2.9. (a) Raw data, (b) 3-tap Equalized data

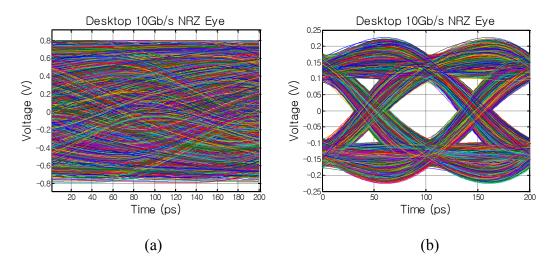

A high-speed signal travelling through an electrical channel is subject to high-frequency losses such as skin effect and dielectric losses as mentioned before. Fig. 2.8 shows a channel response in frequency domain and pulse responses with and without equalization techniques in time domain. The equalized data is made up with 3 taps as shown in Fig. 2.9. The channel losses can severely degrade and attenuate the high-frequency content of the signal, making it difficult for the receiver to detect the signal without error. Therefore transmitter equalizer technique improves the high-speed signal quality. Fig. 2.10 (a) shows that data through lossy channel become dispersive, and eye-diagram is totally closed. But equalized data overcome the ISI effects, and make the eye wide open in Fig. 2.10 (b).

Fig. 2.10. (a) Unequalized eye-diagram, (b) Equalized eye-diagram

## II.2.1.1. Linear Transmitter Equalizer

An ideal signal for a receiver without ISI completes the transition within a symbol interval. However, when the signal travels through a lossy channel, the transition expands to adjacent intervals. This effect is called as inter-symbol interference (ISI). The purpose of pre-cursor and post-cursor emphasis is to apply delays and inversions to the signal and add them back to the original signal with the proper weight.

In case of three tap equalizer implementation [16], the feed-forward equalization is implemented by spreading the symbol's energy over three bit periods, one pre-cursor, one main-cursor, and one post-cursor tap, with the tap weights. Two main techniques for formulating the filter coefficients are Zero forcing equalizer (ZFE) and Least mean square (LMS) equalizer.

## II.2.1.1.1. Zero Force Equalizer (ZFE)

It is computationally efficient method of forming an inverse filter. A training signal is transmitted over the channel in order to formulate a set of FIR inverse filter coefficients. A set of coefficients can be determined by solving a set of equations based on the received sample values, and force all but the center tap of the filtered response to 0.

$$C_i = \sum_{n=-K}^{K} e_n u_{i-n} \tag{2-13}$$

$$C_k = \begin{cases} 1, & k = 0 \\ 0, & k \neq 0 \end{cases}$$

(2-14)

$$\begin{bmatrix} u(-k) & 0 & 0 \\ u(-k+1) & u(-k) & 0 & \vdots \\ 0 & \dots & 0 \\ 0 & 0 & \dots & u(k) \end{bmatrix} \begin{bmatrix} e_{-k} \\ \vdots \\ \vdots \\ e_k \end{bmatrix} = \begin{bmatrix} C_{-2k} \\ \vdots \\ \vdots \\ C_{2k} \end{bmatrix}$$

(2-15)

This means the N-1 samples around the center tap does not contribute to ISI. The main advantage of this technique is that the solution to the set of equations is reduced to a simple matrix inversion. But the major drawback is that since ZFE is simply an inverse filter, it applies high gain to the high frequencies, which tends to amplify noise [16], [17].

## II.2.1.1.2. Least Mean Square (LMS) Equalizer

The least mean squared equalizer is a more general approach to automatic system. Instead of solving a set of N equations as was done in the ZFE, the coefficients are gradually adjusted to minimize the error between the equalized signal and the reference. The LMS equalizer [18] is shown to have better noise performance than the ZFE.

Equalization coefficients for all data formats are acquired with a minimum-mean-square-error algorithm.

$$\begin{bmatrix} y(0) \\ y(1) \\ \dots \\ y(l+k-2) \end{bmatrix} = \begin{bmatrix} p(0) & 0 & 0 & \dots & 0 & 0 \\ p(1) & p(0) & 0 & \dots & 0 & 0 \\ \dots & \dots & \dots & \dots & \dots & \dots \\ 0 & 0 & \dots & p(k-1) & p(k-2) \\ 0 & 0 & \dots & 0 & p(k-1) \end{bmatrix} \begin{bmatrix} h(0) \\ h(1) \\ \dots \\ h(l-1) \end{bmatrix}$$

(2-16)

$$H_{ls} = (P^T P)^{-1} P^T Y_{des} (2-17)$$

where here y is the desired pulse response with an l-tap equalizer, h, and p is the unequalized pulse response with k samples.

#### II.2.1.2 Non-Linear Transmitter Equalizer

These techniques are used in applications where the channel distortion is too severe. We assume that the channel is linear time-invariant, then ISI can be described as a deterministic superposition of time-shifted dispersive pulses.

### II.2.1.2.1. Decision Feedback Equalization (DFE)

DFE is based on the principle that once you have determined the value of the current transmitted symbol, ISI contribution of that symbol to future received symbols can be exactly removed by estimating and substracting out before detection of subsequent symbols. This postcursor ISI removal is accomplished by the use of filter. The details are descripted in the receiver side. DFE can only remove post-cursor ISI, or ISI introduced by future bits. In order to eliminate pre-cursor ISI, FFE must be utilized [19].

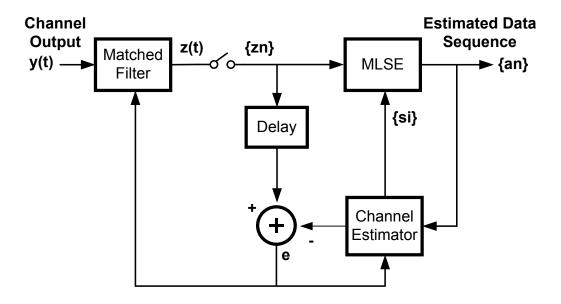

### II.2.1.2.2. Maximum Likelihood Sequence Estimator (MLSE)

The optimal equalizer, in the sense that it with the highest probability correctly detects the transmitted sequence, is the maximum-likelihood sequence estimator (MLSE) in Fig. 2.11. MLSE tests all possible data sequences, and choose the data sequence with the maximum probability as the output. MLSE is used like in the below architecture to find out noise-free received data with a matched filter [20].

Fig. 2.11. The structure of a maximum likelihood sequence equalizer (MLSE) with an adaptive matched filter

## II.2.2. Transmitter Modulation Technique

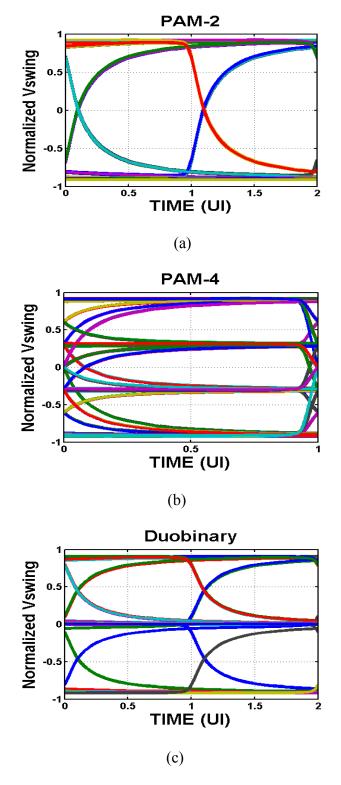

Increasing data rates over electrical channels with significant frequency dependent loss is difficult due to excessive inter-symbol interference (ISI). In order to achieve sufficient link margins at high rates, I/O system designers implement equalization in the transmitters and are motivated to consider more spectrally-efficient modulation formats relative to the common PAM2 scheme, such as PAM4 and duobinary in Fig. 2.12. Examples of high-speed serial I/O transmitters which implement these different modulation formats include [2], [4], [5]. The work of [2], [4] implements a transmitter which is compatible with PAM2 and PAM4 modulation, but does not support duobinary due to the absence of the precoder necessary to avoid error propagation. Custom designed transmitters for each modulation scheme are compared in [5], which

implements the duobinary transmitter with a full-rate precoder. A transmitter which could efficiently support all three of these modulation formats would provide a high degree of flexibility to support different channel environments and, for a given platform, the ability to scale to high data rate during periods of peak I/O bandwidth demand.

In order to consider when a certain modulation format will yield higher link margins, it is possible to compare the channel loss at an effective Nyquist frequency. As PAM4 sends two bits/symbol, the symbol period is twice as long as the PAM2 symbol or bit period,  $T_b$ . Thus, relative to the PAM2 Nyquist frequency of  $1/(2T_b)$  and for the same data rate, the PAM4 Nyquist frequency is at one-half this value or  $1/(4T_b)$ .

However, due to the transmitter's peak-power limit, the voltage margin between symbols is 3x (9.5dB) lower with PAM4 versus simple binary PAM2 signaling. The signal at the output of a linear channel can be represented as

$$y(t) = \sum_{k=-\infty}^{n} (b_k - b_{k-1})S(t - kT)$$

(2-18)

where T - symbol interval, bk, bk-1 are symbol values which are {-1,+1} for NRZ and {-1, -1/3, 1/3, 1} for PAM4; S(t) is the channels' step response. Encoding more data into the same timeframe can be done using different signaling levels. Such multi-level signaling (MLS) or pulse amplitude modulation (PAM) can have multiple distinct levels. Actually, NRZ is a two-level MLS or PAM-2 system. PAM-4 has four distinct levels to encode two bits of data, essentially doubling the bandwidth of a connection. Generating or decoding more than two levels is typically more difficult, and often requires better or more complex hardware.

Fig. 2.12. Eye diagrams of the three common modulation formats (a) PAM-2, (b) PAM-4, (c) duobinary

Likewise, for high-speed signals, random and induced noise becomes a significant factor. In this scheme there are three slicers to detect each of the 4 logic levels: symbol 0 for 00 bit pattern; symbol 1 for a 01 bit pattern; symbol 2 for a 11 bit pattern and symbol 3 for a 10 bit pattern. This means more complex receiver circuitry and reduction of voltage margin/eye height in the eye diagram for a given bit rate. However less equalization is needed for a given bit rate, since the required speed is only half the bit rate. High-speed link designs have started using PAM4 instead of binary (PAM2) signaling in an attempt to make better use of the high signal-to noise ratio in the available bandwidth of the low-pass high-speed link channel.

Duobinary modulation in [5] allows for a controlled amount of ISI, such that the received signal at time n is

$$y_n = x_n + x_{n-1} (2-19)$$

Ideally, this produces a three-level waveform at the receiver which has an effective Nyquist frequency of  $1/(3T_b)$  at the cost of a 2x reduction in voltage margin (6dB) relative to PAM2 signaling. Thus, as shown in Table 1, if the PAM2 Nyquist frequency channel loss is greater than 6dB relative to the effective duobinary Nyquist frequency channel loss,  $\beta_1$ , then duobinary can potentially offer higher SNR. In comparing duobinary versus PAM4, if the channel loss profile is not overly steep, such that there is less than 3.54dB of loss at  $\beta_1$  relative to the PAM4 Nyquist frequency loss,  $\beta_0$ , then duobinary should provide an advantage over PAM4. If the channel loss profile is steep and displays more than 9.54dB separation between  $\beta_2$  and  $\beta_0$ , then PAM4 has the potential to offer the most margin in Fig. 2. 13. When the modulation is used jointly with

equalization, the total receiver signal magnitude depends on the highest channel attenuation in the Nyquist band. Since the modulation with higher Nyquist links channels are predominantly low-pass, this means that Nyquist frequency (for example PAM2 over PAM4, for same bit rate) will incur more loss. On the other hand, due to the peak-power constraint, the multi-level PAM has to fit all the signal levels within the same headroom thereby decreasing the distance between the signal levels and therefore the received eye opening.

Fig. 2.13. Frequency response of three backplane channels.

#### **II.3. Receiver Design Consideration**

#### II.3.1. Continuous-Time Linear Equalizer

CTLE is another signal equalizer to overcome high-frequency losses through an electrical channel. It acts as a bandpass filter, which boosts the components inside a band

of frequencies and attenuates both the low and high frequency components outside. A continuous-time linear equalizer (CTLE) as shown in Fig. 2.14 is utilized after the crosstalk interferences are removed to reduce the inter-symbol interference (ISI) caused by channel loss and boost high-frequency components [21].

The transfer function of CTLE is

$$H(S) = \frac{A_p(s + w_z)}{(s + w_{p1})(s + w_{p2})}$$

(2-20)

where

$$A_p = \frac{g_m}{C_D}$$

$$w_z = \frac{1}{R_s C_s}$$

$$w_{p1} = (1 + g_m R_s/2)/R_s C_s$$

$$w_{p2} = \frac{1}{R_D C_D}$$

$R_s$  and  $C_s$  are source degeneration resistor and capacitor, and  $R_D$  and  $C_D$  are loading resistor and capacitor respectively.  $g_m$  is the transconductance of the input transistor, and  $A_p$  is the DC gain of the CTLE stage in Fig. 2.15.

Fig. 2.14. CTLE & Buffer schematic

Fig. 2.15. CTLE simulation results

## II.3.2. Non-Linear Equalizer (Decision Feedback Equalizer)

The nonlinear adaptive equalizer called decision feedback equalizer (DFE) in Fig. 2.16 is based on the principle that once it has determined the value of the present symbol, it can remove the ISI contribution of that symbol to future received symbols [19]. The nonlinear feature is due to the latch used in the decision period, which attempts to determine which signals of discrete levels were transmitted. Once the present symbol has been determined, the following structure can calculate the ISI effect that it would be added to the following data. This postcursor ISI removal is accomplished by the use of feedback structure like the figure.

## II.3.2.1. Full-rate DFE

Fig 2.16. Full-rate Decision Feedback Equalizer

The requirements on the latch setup and hold times, and for the settling time of the feedback signals at the summer output in Fig. 2.16 is

$$t_{CK2Q} + t_{pd,w1-wn} + t_{summer} + t_{setup} < 1 U.I.$$

(2-21)

where  $t_{CK2Q}$  is the clock-to-Q delay of the flip-flop,  $t_{pd,w1-wn}$  is the propagation delay through the tap (w1-wn),  $t_{sumner}$  is the summer propagation delay, and  $t_{setup}$  is the flip-flop setup time [22].

# II.3.2.2. Half-rate DFE

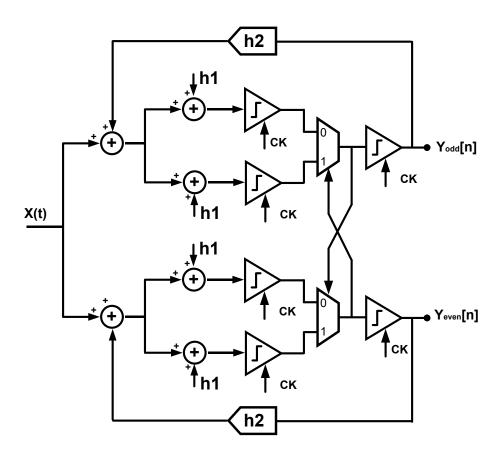

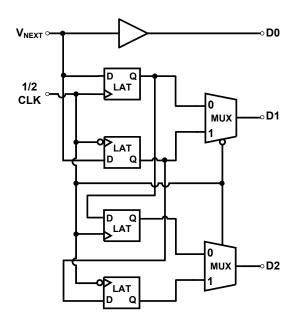

Fig 2.17. Half-rate Decision Feedback Equalizer

The requirements on the latch setup and hold times, and for the settling time of the feedback signals at the summer output in Fig. 2.17 is

$$t_{CK2Q} + t_{pd,h2} + t_{mux} + t_{summer} + t_{setup} < 1 U.I.$$

(2-22)

where  $t_{CK2Q}$  is the clock-to-Q delay of the flip-flop,  $t_{pd,h2}$  is the propagation delay through the tap,  $t_{mux}$  is the mux propagation delay,  $t_{sumner}$  is the summer propagation delay, and  $t_{setup}$  is the flip-flop setup time [23], [24].

#### III. TRANSMITTER DESIGN<sup>2</sup>

#### **III.1. Introduction**

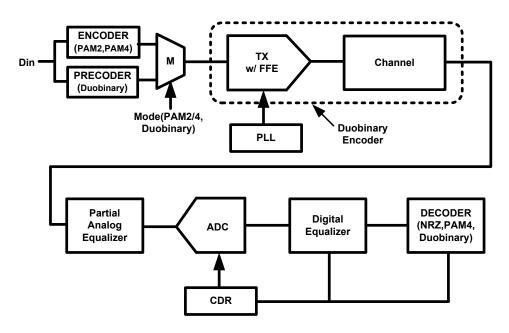

Fig. 3.1. High-Speed link block diagram with triple-mode transmitter and ADC-based receiver.

High-performance computing applications require I/O data rates to scale well past 10Gb/s to meet the demand of future systems. However, inter-chip communication at high data rates over standard electrical channels is challenging due to excessive frequency-dependent channel attenuation which causes large amounts of inter-symbol interference (ISI).

-

<sup>2 .</sup> Reprinted with permission from "10 Gb/s Adaptive Receive-Side Near-End and Far-End Crosstalk Cancellation Circuitry" by Byungho Min, Noah Hae-Woong Yang, Samuel Palermo, 2014, IEEE International Midwest Symposium on Circuits and Systems, pp. 77-80, Copyright 2014 IEEE

In order to scale data rates, high-performance I/Os are evolving into sophisticated communication links, as shown in Fig. 3.1. Transmitters with feed-forward equalization (FFE) are often employed [1], [2]. However, due to transmit peak-power limitations imposed by shrinking CMOS power supplies, only incremental performance improvement is achieved by increasing transmitter equalization complexity past two or three taps [3]. This motivates I/O system designers to consider modulation techniques which provide spectral efficiencies higher than simple binary PAM-2 signaling in order to increase data rates over band-limited channels, with the most commonly proposed modulation schemes being PAM-4 and duobinary. At the receiver, analog equalization with continuous-time linear equalizers or FIR filters can also help mitigate ISI. The use of an ADC-based front-end allows for additional equalization in the digital domain and the support of multiple modulation formats. However, again due to transmit peak-power limitations, the optimal modulation which yields the best system margins is a function of the channel loss profile and the desired data rate.

For applications such as data centers, storage, and computer networking, high-speed links must typically achieve a bit-error rate (BER) from 10<sup>-12</sup> to 10<sup>-15</sup> for acceptable system performance. Under this low BER requirement, empirical analysis is impractical due to current hardware performance limitations. However, simple worst-case analysis techniques, such as peak-distortion analysis, yield highly pessimistic performance estimations which map to inefficient designs that consume excessive power and chip area [4]. This has lead to the development of statistical analysis methods [4], [5], [25],

[26], which utilize the statistical properties of noise and distortion to rapidly estimate link performance and trade-offs in equalization complexity and modulation format.

Examples of high-speed serial I/O transmitters which implement different modulation formats include [2], [28], [30]. The work of [2], [28] implements a transmitter which is compatible with PAM-2 and PAM-4 modulation, but does not support duobinary due to the absence of the precoder necessary to avoid error propagation. Custom designed transmitters for each modulation scheme are compared in [27], [29], [30], which implements the duobinary transmitter with a full-rate precoder. A transmitter which could efficiently support all three of these modulation formats would provide a high degree of flexibility to support different channel environments and, for a given platform, the ability to scale to high data rates during periods of peak I/O bandwidth demand.

#### III.2. Modulation Techniques

#### III.2.1. Overview of PAM-2, PAM-4, and Duobinary Signaling

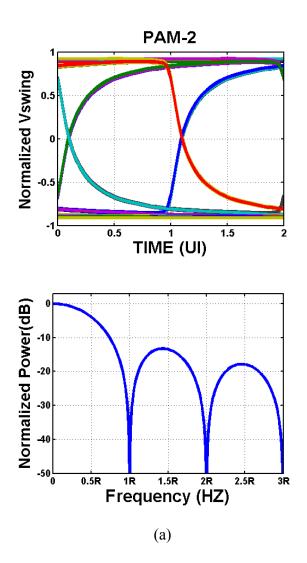

Fig. 3.2 compares random data eye diagrams and frequency spectrums for the three common modulation formats. PAM-2 or binary signaling is the simplest to implement at both the transmitter and receiver, and thus is the most commonly used modulation format. Here the binary bits are directly transmitted over the channel, requiring only a single comparator at the receiver to recover the data. The PAM-2 random data power-spectral density can be expressed as

$$S_{PAM2} = T_b sinc^2(T_b f), (3-1)$$

where  $T_b$  is the bit period equal to the inverse of the data rate, R. Here, more than 95% of the cumulative signal power is contained in a bandwidth R [27].

Fig. 3.2. Eye diagrams and power-spectral density of the three common modulation formats of PAM-2

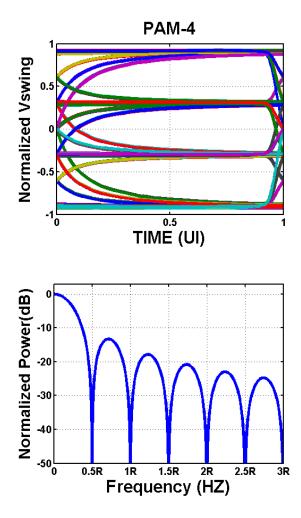

Fig. 3.3. Eye diagrams and power-spectral density of the three common modulation formats of PAM-4

PAM-4 modulation in Fig. 3.3 transmits two-bits per symbol by utilizing four signal levels, reducing the baud rate by a factor of two. This increases the complexity of the receiver to a two-bit ADC, which is typically implemented with three comparators. The reduced baud rate modifies the PAM-4 random data power-spectral density to

$$S_{PAM4} = (10/9) T_b sinc^2 (2T_b f),$$

(3-2)

with the majority of the cumulative signal power contained in half the bandwidth relative to PAM-2 modulation.

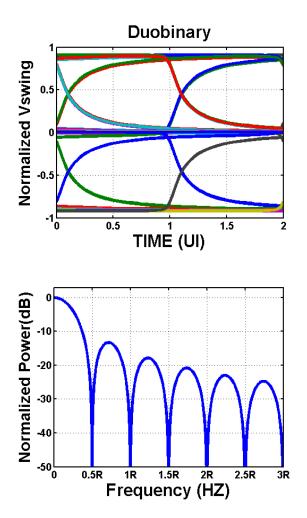

Fig. 3.4. Eye diagrams and power-spectral density of the three common modulation formats of duobinary

Duobinary modulation in Fig. 3.4 uses the same PAM-2 baud rate equal to the bit rate, but allows for a controlled amount of ISI, such that the received signal at time n is

$$y_n = x_n + x_{n-1}. (3-3)$$

where  $x_n$  is the transmitted signal which is a one-to-one mapping of the data  $d_n$ . Here, the duobinary encoding is implemented by leveraging the channel response to provide a portion of this ISI, along with the transmit equalizer. This ideally produces a three-level waveform at the receiver, requiring two comparators at the receiver to decode the data using the previous decision. In order to prevent error propagation at the receiver, often data precoding is implemented in the transmitter, with a modified transmitted signal of

$$x_n = d_n \oplus x_{n-1}. \tag{3-4}$$

After this precoded signal experiences the duobinary encoding, the receiver decoding no longer requires the previous decision, with the mapping

$$\hat{d}_n = \begin{cases} 1 & \text{if } y_n = 0\\ 0 & \text{if } y_n = -1, 1 \end{cases}$$

(3-5)

This controlled ISI results in a duobinary random data power-spectral density of

$$S_{duo} = T_b sinc^2(T_b f) * cos^2(\pi T_b f) = T_b sinc^2(2T_b f)$$

(3-6)

which for a given data rate provides the same factor of two signal bandwidth reduction as PAM-4 modulation.

## III.2.2 Modulation Selection

In order to consider when a certain modulation format will yield higher link margins, it is possible to compare the channel loss at an effective Nyquist frequency. As PAM-4 sends two bits/symbol, the symbol period is twice as long as the PAM-2 symbol or bit period,  $T_b$ . Thus, relative to the PAM-2 Nyquist frequency of  $1/(2T_b)$  and for the same

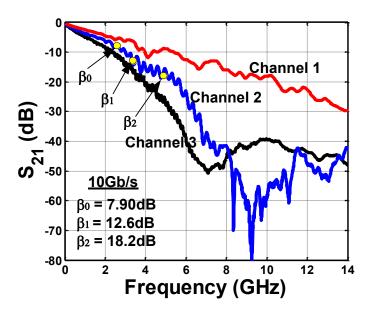

Fig. 3.5. Frequency response of three backplane channels.

data rate, the PAM-4 Nyquist frequency is at one-half this value or  $1/(4T_b)$ . However, due to the transmitter's peak-power limit, the voltage margin between symbols is 3x (9.54dB) lower with PAM-4 versus simple binary PAM-2 signaling. While duobinary modulation has the same baud rate as PAM-2, the introduction of controlled ISI reduces the effective Nyquist frequency to  $1/(3T_b)$  at the cost of a 2x reduction in voltage margin (6dB) due to the three-level waveform at the receiver [5]. Thus, as shown in Table 1, if the PAM-2 Nyquist frequency channel loss,  $\beta_2$ , is greater than 6dB relative to the effective duobinary Nyquist frequency channel loss,  $\beta_1$ , then duobinary can potentially offer higher SNR. In comparing duobinary versus PAM-4, if the channel loss profile is not overly steep, such that there is less than 3.54dB of loss at  $\beta_1$  relative to the PAM-4

Nyquist frequency loss,  $\beta_0$ , then duobinary should provide an advantage over PAM-4. If the channel loss profile is steep and displays more than 9.54dB separation between  $\beta_2$  and  $\beta_0$ , then PAM-4 has the potential to offer the most margin.

The frequency responses of the three backplane channels considered in this work are shown in Fig. 3.5. Channel 1, consisting of  $\sim$ 5" (12.7cm) of traces on line cards and only 1" (2.54cm) on the backplane board, displays the lowest frequency-dependent loss due to both its short length and the use of the bottom backplane signaling layer to minimize impedance discontinuities. The impact of channel length is evident in the increased loss of channel 2, which has  $\sim$ 6" (15.24cm) of traces on line cards and 10" (25.4cm) on the top layer of the backplane board. The backplane via stubs associated with signaling on the top layer introduce a capacitive impedance discontinuity that causes severe loss in this channel near 9GHz. Channel 3 is the longest channel, with  $\sim$ 6" (15cm) line card traces and 20" (50.8cm) of top-layer backplane traces. It also displays a resonant null in the frequency response near 7GHz.

An example of applying the Table 1 modulation selection methodology is shown in Fig. 3.5 for channel 2 at 10Gb/s. The loss at  $\beta_2$ ,  $\beta_1$ , and  $\beta_0$  is 18.2, 12.6, and 7.9dB, respectively. Using Table 1 predicts that PAM-4 will provide the maximum link margin. This will be verified in the simulation results of Section 3. Note, it should be mentioned here that the modulation selection guide provides an initial check as to whether a modulation other than PAM-2 should be considered. Other system considerations, such as cross-talk sources and receiver CDR complexity, should also be considered for the final modulation choice.

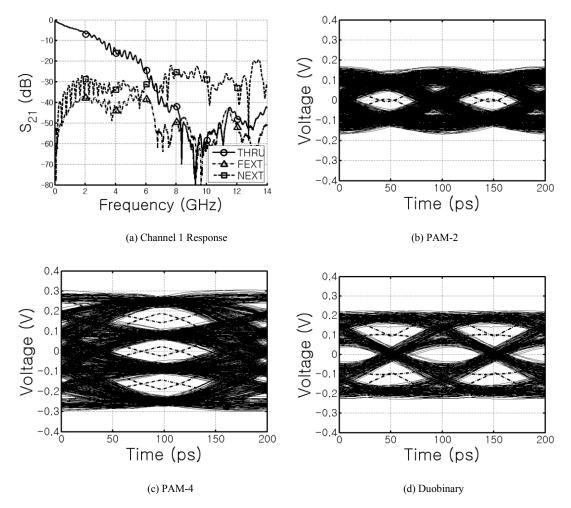

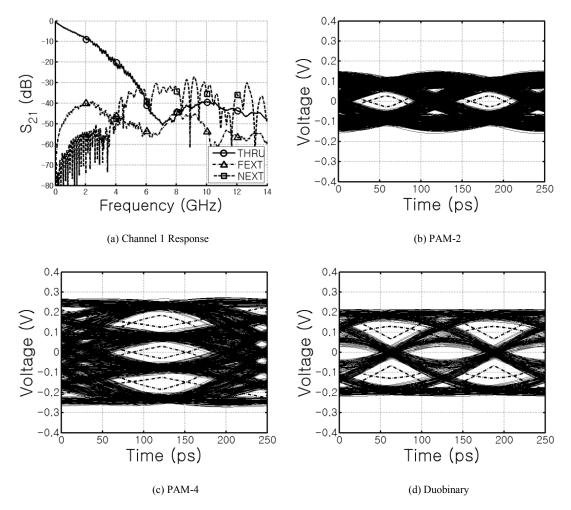

#### III.3. Statistical BER Modeling

While the channel loss-slope parameters of Table. 3.1 serve as an initial guide in modulation choice, other link system effects, such as sensitivity to crosstalk and jitter should be considered. In order to accurately estimate the system BER, a link modeling tool which statistically models voltage and timing noise and ISI and crosstalk distortion is utilized. Both far-end crosstalk (FEXT) and near-end crosstalk (NEXT) models are included for the three backplane channels under consideration, as shown in Fig. 5(a), 6(a) and 7(a).

Table. 3.1. Modulation selection.

| $\beta_2$ - $\beta_1$ > 6dB   | $\beta_2$ - $\beta_1$ < 6dB    |  |  |

|-------------------------------|--------------------------------|--|--|

| $\beta_1 - \beta_0 < 3.54$ dB | $\beta_2 - \beta_0 > 9.54 dB$  |  |  |

| →Duobinary                    | →PAM-4                         |  |  |

| $\beta_1 - \beta_0 > 3.54 dB$ | $\beta_2$ - $\beta_0$ < 9.54dB |  |  |

| →PAM-4                        | →PAM-2                         |  |  |

$\beta_0$ : PAM-4 Nyquist frequency(1/(2Tb)) channel loss

$\beta_1$ : Effective duobinary Nyquist frequency(1/(3Tb)) channel loss

$\beta_2$ : PAM-2 Nyquist frequency(1/(4Tb)) channel loss

The "thru" and crosstalk channels are assumed as linear time-invariant (LTI) [25] and the received signal  $y_k$  is described in the PAM-2 and PAM-4 case as,

$$y_k = I_{k,THRU} h_{k,THRU} + \sum_{i \neq k}^{N} I_{i,THRU} h_{i,THRU} + \sum_{m}^{N} I_{m,FEXT} g_{i,FEXT}$$

$$+\sum_{m}^{N}I_{m,NEXT}g_{i,NEXT} + Z_{k}$$

(3-7)

where k is the cursor index,  $I_{i,THRU}$ ,  $I_{i,FEXT}$  and  $I_{i,NEXT}$  are the transmitting symbols through corresponding channels,  $h_{i,THRU}$ ,  $g_{i,FEXT}$  and  $g_{i,NEXT}$  are the sampled pulse responses of N-tap equalized thru, FEXT, and NEXT channels, respectively, and  $Z_k$  is a random noise component. Since (7) consists of a linear combination of independent random variables, the received signal PDF is obtained by convolving the independent random variables PDFs. In the duobinary case, as both the cursor and first post-cursor are utilized for a decision, the received signal expression is modified to,

$$y_{k} = \pm I_{k,THRU} h_{k,THRU} \pm I_{k-1,THRU} h_{k-1,THRU} + \sum_{i \neq k,k-1}^{N} I_{i,THRU} h_{i,THRU}$$

$$+ \sum_{m}^{N} I_{m,FEXT} g_{i,FEXT} + \sum_{m}^{N} I_{m,NEXT} g_{i,NEXT} + Z_{k}$$

(3-8)

where  $\pm I_k h_k \pm I_{k-1} h_{k-1}$  are four possible cursor values to represent three symbols(-2, 0, 2) [29]. Timing jitter is introduced with a dual-Dirac receiver-side jitter model, which modifies the received signal PDF as

$$p(v,t) = p(v|t)p(t)$$

(3-9)

where p(t) is the time-domain jitter probability model and p(v|t) is the received signal PDFs at a given sampling time t [26].

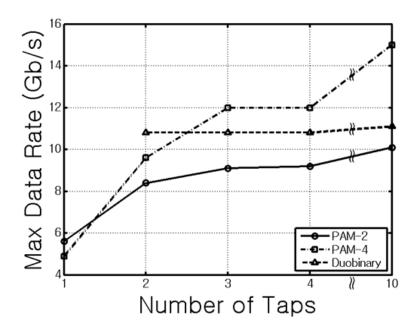

This statistical link modeling tool can be utilized to rapidly explore trade-offs in modulation schemes and equalization partitioning and complexity. Fig. 4 shows that the maximum achievable data rate versus TX equalization taps for channel 3 (Fig 7(a)), with

the system modeling parameters of  $1\text{mV}_{rms}$  random noise, 1% bit ( $T_b$ ) deterministic jitter (DJ) and  $\sigma$ =1%  $T_b$  random jitter (RJ). Also, the transmitter equalization taps are optimized in a minimum mean-squared error manner, the transmit signal dynamic range is constrained to  $1\text{V}_{ppd}$ , and a minimum receiver eye height margin of 10mV at a BER= $10^{-12}$  is used to set the maximum data rate.

Fig. 3.6. Maximum achievable data rate with channel 3 based on the number of TX-FFE taps for the three modulation schemes.

Table 3.2. 10Gb/s FFE coefficients and link margin with channel 1.

|      | a        | a      | <i>a</i> | BER=10 <sup>-12</sup> |       |

|------|----------|--------|----------|-----------------------|-------|

|      | $a_{-1}$ | $a_0$  | $a_1$    | H(mV)                 | W(ps) |

| PAM2 | -0.0492  | 0.7177 | -0.2331  | 220.4                 | 56    |

| PAM4 | -0.0179  | 0.8824 | -0.0997  | 117.8                 | 80    |

| DUO  | 0.4951   | 0.3273 | -0.1776  | 154.7                 | 57    |

For the PAM-2 and PAM-4 cases of Fig. 3.6, significant improvements in data rate are achieved by including transmit equalization with two taps. While scaling to three taps provides some additional performance benefits, improvements with four or more taps is somewhat incremental. As doubinary modulation includes ISI by definition, a two-tap equalizer is necessary. While duobinary achieves the highest data rate with two-taps of equalization, adding more taps doesn't dramatically improve the achievable data rate.

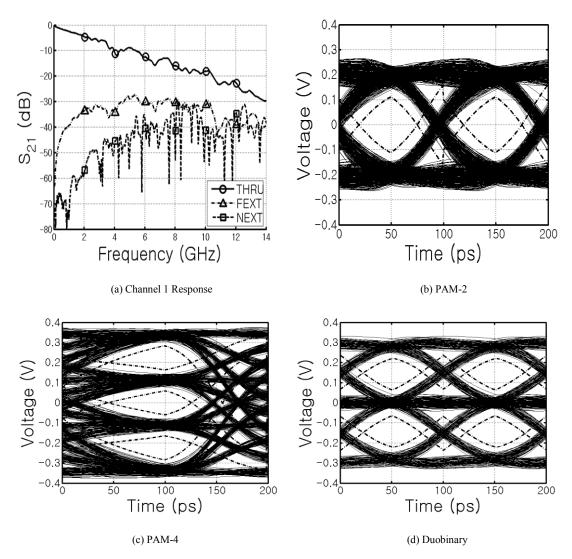

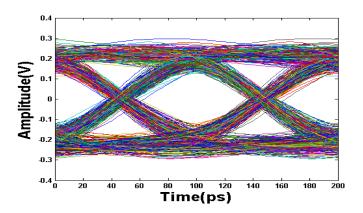

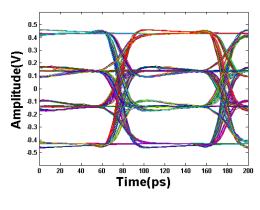

Simulations are performed with the three backplane channels to illustrate the relative performance of the three modulation formats with the inclusion of a three-tap transmit equalizer with a pre-cursor tap,  $\alpha_{-1}$ , cursor tap,  $\alpha_0$ , and post-cursor tap,  $\alpha_1$ . Two crosstalk aggressor channels, one FEXT and one NEXT, are included with the same input power as the main "thru" transmitted signal. Fig. 3.7 (b)-(d) shows 10Gb/s transient random 1k-bit eye diagrams and the BER=10<sup>-12</sup> eye contour from the statistical link model with channel number 1, where the loss profile is 4.5, 6.8, and 9.1dB for  $\beta_0$ ,  $\beta_1$ , and  $\beta_2$ , respectively. Table 3.2 confirms that PAM2 modulation yields the largest voltage margin,

Table 3.3. 10Gb/s FFE coefficients and link margin with channel 2.

|      | <i>a</i> | a   a   |         | BER=10 <sup>-12</sup> |       |

|------|----------|---------|---------|-----------------------|-------|

|      | $a_{-1}$ | $a_0$   | $a_1$   | H(mV)                 | W(ps) |

| PAM2 | -0.1669  | 0.5994  | -0.2337 | 14.2                  | 13    |

| PAM4 | -0.0470  | 0.7972  | -0.1559 | 44.4                  | 36    |

| DUO  | 0.7246   | -0.2669 | 0.0086  | 8.3                   | 7     |

Table 3.4. 8Gb/s FFE coefficients and link margin with channel 3.

|      | <i>a</i> | a       | a       | BER=10 <sup>-12</sup> |       |

|------|----------|---------|---------|-----------------------|-------|

|      | $a_{-1}$ | $a_0$   | $a_1$   | H(mV)                 | W(ps) |

| PAM2 | -0.1685  | 0.5917  | -0.2398 | 54.2                  | 41.25 |

| PAM4 | -0.0459  | 0.7767  | -0.1774 | 58.4                  | 65    |

| DUO  | 0.7302   | -0.2297 | -0.0401 | 62                    | 47.5  |

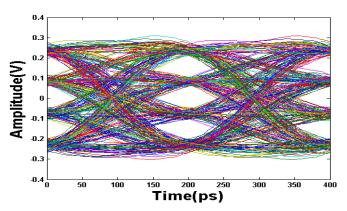

as expected with this low loss channel. Note the performance degradation from the 1k-bit transient simulation to the BER= $10^{-12}$  eye contour. The statistical link model allows rapid performance analysis to this low error rate with the consideration of the different link system effects, something that is not feasible with transient simulations. Fig. 3.8 (b)-(d) shows 10Gb/s results with channel number 2, where the loss profile is 7.9, 12.6, and 18.2dB for  $\beta_0$ ,  $\beta_1$ , and  $\beta_2$ , respectively. Table 3.3 confirms that PAM4 modulation yields the largest voltage and also timing margin, as expected with this high loss channel with a steep loss slope around this data rate.

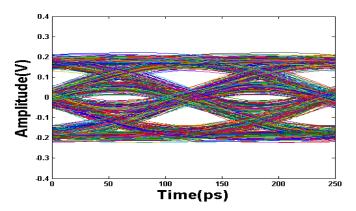

In order to illustrate a scenario where duobinary modulation provides superior voltage margin, 8Gb/s operation over channel 3 is considered. Channel 3 has overall high loss, but relatively moderate loss slope around this data rate, with a loss profile of 8.5, 11.5, and 21.5dB for  $\beta_0$ ,  $\beta_1$ , and  $\beta_2$ , respectively. Fig. 3.9 (b)-(d) shows the 8Gb/s results and Table 3.4 confirms that duobinary modulation yields the largest voltage margin.

Fig. 3.7. 10Gb/s eye diagrams with channel 1. Solid lines are transient 1k-bit simulations and dashed lines are BER=10<sup>-12</sup> contours obtained from the statistical link model.

Fig. 3.8. 10Gb/s eye diagrams with channel 2. Solid lines are transient 1k-bit simulations and dashed lines are BER=10<sup>-12</sup> contours obtained from the statistical link model.

Fig. 3.9. 8Gb/s eye diagrams with channel 3. Solid lines are transient 1k-bit simulations and dashed lines are BER=10<sup>-12</sup> contours obtained from the statistical link model.

Sensitivity to crosstalk and timing jitter are important considerations in the selection of the modulation format. In order to gain intuition on these effects, the distortion variance due to ISI and crosstalk is derived for the three modulation formats. Assuming PAM-2 symbols with value 1,-1, the distortion variance is

$$\sigma_{PAM2}^{2} = \sum_{i \neq k}^{N} \left\{ \frac{1}{2} \left( 1 \cdot h_{i,PAM2} \right)^{2} + \frac{1}{2} \left( -1 \cdot h_{i,PAM2} \right)^{2} \right\}$$

$$+ \sum_{i}^{M \cdot N} \left\{ \frac{1}{2} \left( 1 \cdot g_{i,PAM2} \right)^{2} + \frac{1}{2} \left( -1 \cdot g_{i,PAM2} \right)^{2} \right\}$$

$$= \sum_{i \neq k}^{N} h_{i,PAM2}^{2} + \sum_{i}^{M \cdot N} g_{i,PAM2}^{2}$$

(3-10)

where N is the channel length, M is the number of crosstalk channels,  $h_{i,PAM2}$  are the equalized and sampled thru channel pulse response and  $g_{i,PAM2}$  are the sampled crosstalk pulse responses filtered by a transmitted FIR equalizer.

Likewise, with the same peak signal level, the distortion variance for duobinary modulation is

$$\sigma_{\text{DUO}}^2 = (|\mathbf{h}_{k,\text{DUO}}| - |\mathbf{h}_{k-1,\text{DUO}}|)^2 + \sum_{i \neq k,k-1}^{N} \mathbf{h}_{i,\text{DUO}}^2 + \sum_{i}^{M \cdot N} \mathbf{g}_{i,\text{DUO}}^2,$$

(3-11)

where the first term is due to mismatch between cursor and precursor.

For PAM-4,

$$\begin{split} \sigma_{PAM4}^2 &= \sum_{i \neq k}^N \left\{ \frac{1}{4} \left( 1 \cdot h_{i,PAM4} \right)^2 + \frac{1}{4} \left( \frac{1}{3} \cdot h_{i,PAM4} \right)^2 + \frac{1}{4} \left( -\frac{1}{3} \cdot h_{i,PAM4} \right)^2 \right. \\ &\quad + \frac{1}{4} \left( -1 \cdot h_{i,PAM4} \right)^2 \right\} \\ &\quad + \sum_{i \neq k}^N \left\{ \frac{1}{4} \left( 1 \cdot g_{i,PAM4} \right)^2 + \frac{1}{4} \left( \frac{1}{3} \cdot g_{i,PAM4} \right)^2 + \frac{1}{4} \left( -\frac{1}{3} \cdot g_{i,PAM4} \right)^2 \right. \\ &\quad + \frac{1}{4} \left( -1 \cdot g_{i,PAM4} \right)^2 \right\} \end{split} \tag{3-12}$$

$$= \frac{5}{9} \sum_{i \neq k}^{N} h_{i,PAM4}^2 + \frac{5}{9} \sum_{i}^{M \cdot N} g_{i,PAM4}^2$$

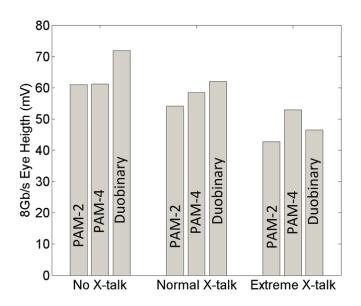

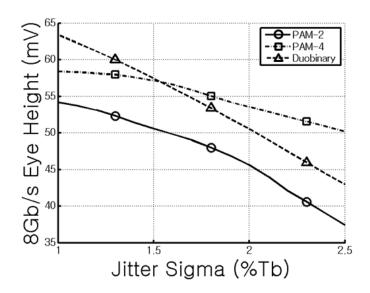

Interestingly, the PAM-4 distortion variance crosstalk term is smaller relative to the PAM-2 and duobinary cases, implying that PAM-4 will display less sensitivity to increased levels of crosstalk. In order to illustrate this, the statistical link modeling tool is utilized to simulate 8Gb/s operating over channel 3 with the three modulation formats and crosstalk levels ranging from none, one FEXT and one NEXT aggressor from Fig. 3.9 (a), and with these crosstalk channels boosted by 6dB. The eye height results of Fig. 3.10 confirm that relative to the no crosstalk case, PAM-4 displays the least amount of degradation due to increased levels of crosstalk. While duobinary modulation displays the most eye height with no and normal crosstalk, when the crosstalk is boosted by 6dB PAM-4 achieves superior eye height.

The longer symbol period of PAM-4 also allows for reduced jitter sensitivity, as illustrated in Fig. 3.11. While the nominal 1% DJ and  $\sigma$ =1% RJ assumptions result in duobinary displaying the most 8Gb/s eye height, when jitter is increased PAM-2 and duobinary performance degrades at a similar rate that is more severe than the PAM-4 reduction. When jitter levels are increased to near  $\sigma$ =2% RJ, PAM-4 displays superior eye height.

Fig. 3.10. 8Gb/s eye height degradation with crosstalk for channel 3.

Fig. 3.11. 8Gb/s eye degradation vs. random jitter for channel 3.

Fig. 3.12. Triple-mode transmitter architecture.

# III.4. Transmitter Design