#### Universidade de Santiago de Compostela

Centro de Investigación en Tecnoloxías da Información

#### Tesis doctoral

# TIME-OF-FLIGHT SENSORS IN STANDARD CMOS TECHNOLOGIES

Presentada por:

Julio Illade Quinteiro

Dirigida por:

Paula López Martínez

Víctor Manuel Brea Sánchez

Febrero 2017

Paula López Martínez, Profesora Titular de Universidad del Área de Electrónica de la Universidad de Santiago de Compostela

**Víctor Manuel Brea Sánchez**, Profesor Titular de Universidad del Área de Electrónica de la Universidad de Santiago de Compostela

#### HACEN CONSTAR:

Que la memoria titulada **TIME-OF-FLIGHT SENSORS IN STANDARD CMOS TECHNOLO-GIES** ha sido realizada por **D. Julio Illade Quinteiro** bajo nuestra dirección en el Centro Singular de Investigación en Tecnoloxías da Información de la Universidad de Santiago de Compostela, y constituye la Tesis que presenta para optar al título de Doctor.

Febrero 2017

Paula López Martínez

Directora/Codirectora tesis

Víctor Manuel Brea Sánchez

Codirector de la tesis

Julio Illade Quinteiro

Autor de la tesis

#### A mi familia

Fairy tales are more than true: not because they tell us that dragons exist, but because they tell us that dragons can be beaten.

Neil Gaiman

If you think education is expensive, try ignorance.

Derek Curtis Bok

#### Agradecimentos/Acknowledgments

No podría haber llevado a cabo el trabajo de esta tesis sin la ayuda de un montón de gente, a la que quiero que agradecer por ello. En primer lugar a mis directores de tesis, Paula López Martínez y Víctor Manuel Brea Sánchez. Siempre supieron enseñarme por donde seguir cuando la investigación se atascaba y no sabía cómo solucionarlo. También quiero agradecer a mis compañeros del CiTIUS, en especial a Esteban Ferro Santiago, Beatriz Blanco Filgueira y José Manuel Abuín Mosquera por todas las conversaciones que mantuvimos, las referentes a la tesis y las que no. Por supuesto agradecer a mi familia, en especial a mis padres y a mi hermana, que me apoyaran de manera incondicional durante estos cuatro años. Todo lo bueno que he conseguido es gracias a ellos y todo lo malo a pesar de ellos. A mis amigos quiero darles las gracias por recordarme que es bueno salir a la calle de vez en cuando, y obligarme a hacerlo.

También tengo que agradecer a los proyectos que financiaron esta tesis: EM2013/038, TEC2012-38921-C02, TEC2015-66878-C3-3-R MINECO, GPC2013/040 (FEDER), ED431 G/08 y European Regional Development Fund (ERDF).

Febrero 2017

## **Contents**

| Resumen de la tesis |                                                                    |                |                            |    |  |  |  |

|---------------------|--------------------------------------------------------------------|----------------|----------------------------|----|--|--|--|

| Introduction        |                                                                    |                |                            |    |  |  |  |

| 1                   | Background and Related Work Fundamentals of Time-of-Flight Sensors |                |                            |    |  |  |  |

| 2                   |                                                                    |                |                            |    |  |  |  |

|                     | 2.1                                                                | Indire         | ct ToF Techniques          | 20 |  |  |  |

|                     |                                                                    | 2.1.1          | Modulated Time-of-Flight   | 20 |  |  |  |

|                     |                                                                    | 2.1.2          | Pulsed Time-of-Flight      | 22 |  |  |  |

|                     | 2.2                                                                | Noise          | Related Distance Error     | 25 |  |  |  |

|                     |                                                                    | 2.2.1          | Shot Noise                 | 26 |  |  |  |

|                     |                                                                    | 2.2.2          | Thermal Noise              | 27 |  |  |  |

|                     | 2.3                                                                | Signal         | and Background Estimations | 31 |  |  |  |

|                     |                                                                    | 2.3.1          | Light Power Considerations | 31 |  |  |  |

|                     |                                                                    | 2.3.2          | Signal Accumulation        | 32 |  |  |  |

|                     | 2.4                                                                | rical Examples | 34                         |    |  |  |  |

|                     |                                                                    | 2.4.1          | Shot Noise Results         | 36 |  |  |  |

|                     |                                                                    | 2.4.2          | Thermal Noise Results      | 38 |  |  |  |

xii CONTENTS

|                        | 2.5                  | Selecte                              | ed Topology                                           | 42 |  |  |  |

|------------------------|----------------------|--------------------------------------|-------------------------------------------------------|----|--|--|--|

| 3                      | Devi                 | ice Simulations                      |                                                       |    |  |  |  |

| 3.1 Studied Structures |                      |                                      | d Structures                                          | 44 |  |  |  |

|                        | 3.2                  | 2 Layout Optimization in terms of DC |                                                       |    |  |  |  |

|                        |                      | 3.2.1                                | Thermal DC                                            | 50 |  |  |  |

|                        |                      | 3.2.2                                | Surface DC                                            | 51 |  |  |  |

|                        |                      | 3.2.3                                | Band-to-Band Tunneling DC                             | 51 |  |  |  |

|                        |                      | 3.2.4                                | Layout Parameters Optimization                        | 51 |  |  |  |

|                        | 3.3                  | 3 Reset Transistor                   |                                                       |    |  |  |  |

|                        |                      | 3.3.1                                | Thermal noise                                         | 60 |  |  |  |

|                        |                      | 3.3.2                                | Clock feedthrough                                     | 60 |  |  |  |

|                        |                      | 3.3.3                                | Dependence of the reset voltage with the illumination | 61 |  |  |  |

|                        |                      | 3.3.4                                | Leakage current                                       | 62 |  |  |  |

|                        | 3.4                  | .4 Transient Analysis                |                                                       |    |  |  |  |

|                        | 3.5                  | Conclusions                          |                                                       |    |  |  |  |

| 4                      | Time-of-Flight Pixel |                                      |                                                       |    |  |  |  |

| 4                      |                      | ime-of-Flight Pixel                  |                                                       |    |  |  |  |

|                        | 4.1                  |                                      | Operation                                             | 71 |  |  |  |

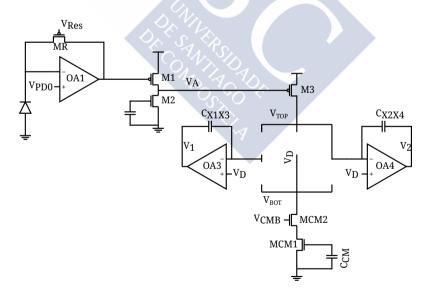

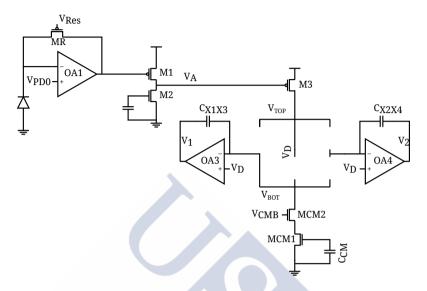

|                        | 4.2                  | Circuit                              | Description                                           | 74 |  |  |  |

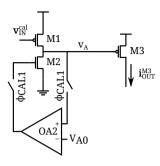

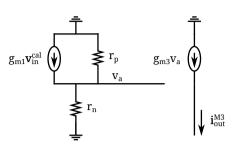

|                        |                      | 4.2.1                                | Transimpedance Converter                              | 74 |  |  |  |

|                        |                      | 4.2.2                                | Calibration Subcircuit                                | 79 |  |  |  |

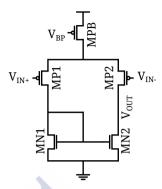

|                        |                      | 4.2.3                                | Background Suppression Subcircuit                     | 85 |  |  |  |

|                        |                      | 4.2.4                                | Integrator Subcircuit                                 | 88 |  |  |  |

|                        |                      | 4.2.5                                | ADC Subcircuit                                        | 90 |  |  |  |

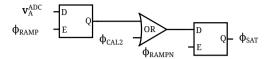

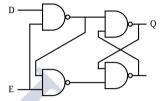

|                        |                      | 4.2.6                                | Adaptive Number of Accumulations Subcircuit           | 95 |  |  |  |

|                        | 4.3                  | Measurement Steps                    |                                                       |    |  |  |  |

| CC | ONTE  | ENTS                    |                                           | xiii  |

|----|-------|-------------------------|-------------------------------------------|-------|

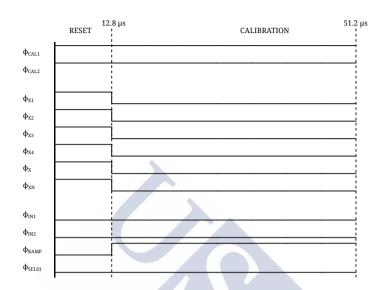

|    |       | 4.3.1                   | Reset and Calibration Phases              | . 97  |

|    |       | 4.3.2                   | Signal Integration                        | . 99  |

|    |       | 4.3.3                   | Analog to Digital Conversion              | . 106 |

|    | 4.4   | Conclu                  | asions                                    | . 109 |

| 5  | Chij  | o Test                  |                                           | 111   |

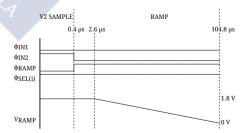

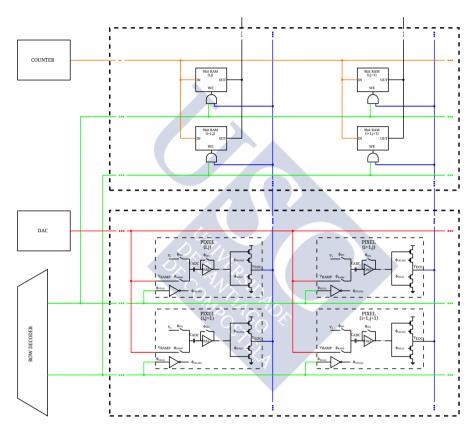

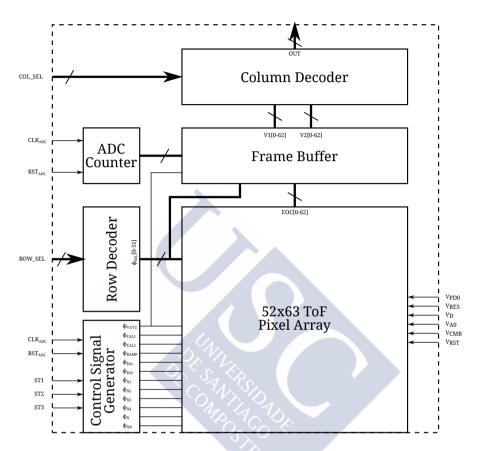

|    | 5.1   | Chip F                  | Floorplan                                 | . 112 |

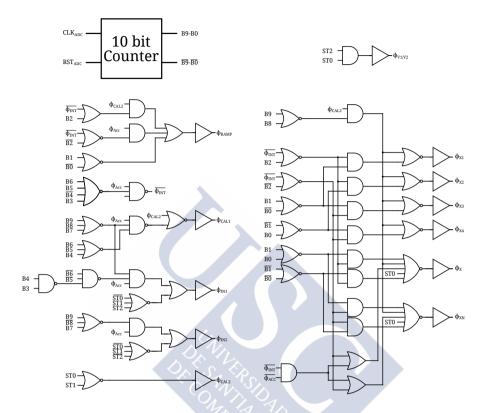

|    |       | 5.1.1                   | Control Signal Generator                  | . 114 |

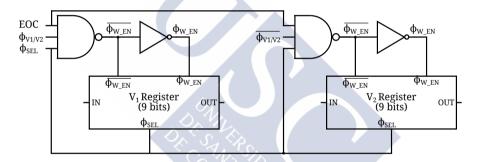

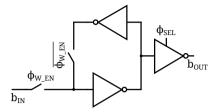

|    |       | 5.1.2                   | Frame Buffer                              | . 116 |

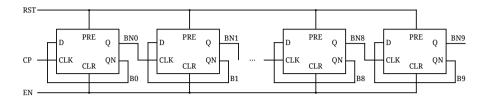

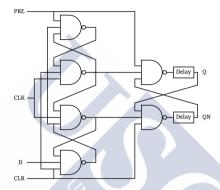

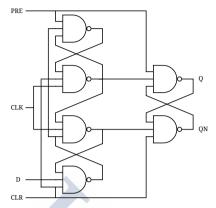

|    |       | 5.1.3                   | ADC Counter                               | . 117 |

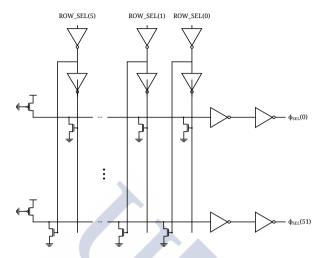

|    |       | 5.1.4                   | Row decoder                               | . 117 |

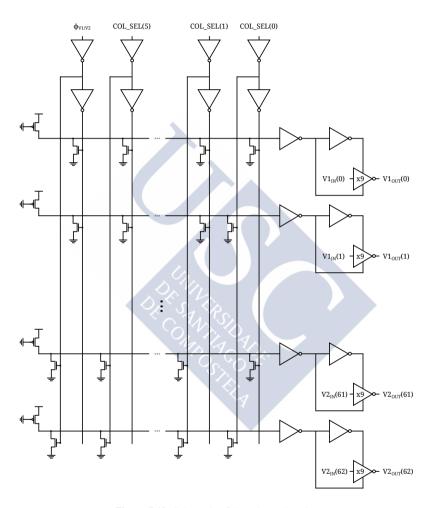

|    |       | 5.1.5                   | Column decoder                            |       |

|    | 5.2   | 5.2 Experimental Set-up |                                           |       |

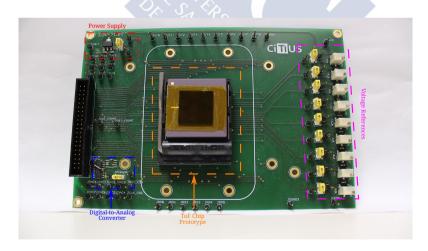

|    |       | 5.2.1                   | Chip PCB                                  | . 119 |

|    |       | 5.2.2                   | Illumination PCB                          | . 119 |

|    |       | 5.2.3                   | Lens and Case                             | . 122 |

|    |       | 5.2.4                   | FPGA                                      | . 122 |

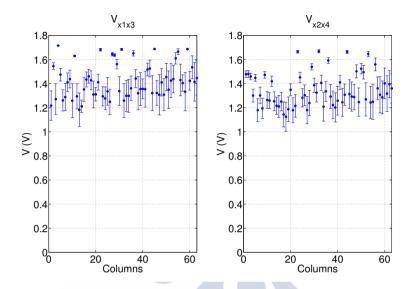

|    | 5.3   | Experi                  | mental Results                            | . 123 |

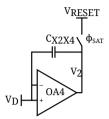

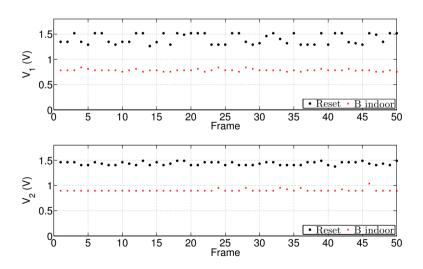

|    |       | 5.3.1                   | Reset Topology                            | . 124 |

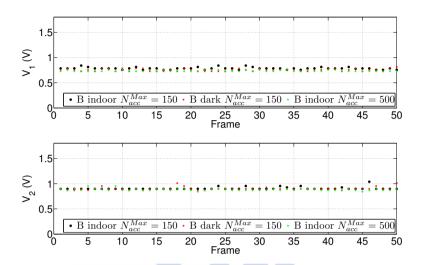

|    |       | 5.3.2                   | Sensor response to background light       | . 125 |

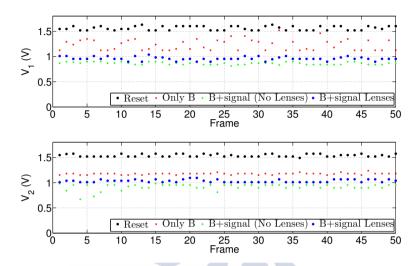

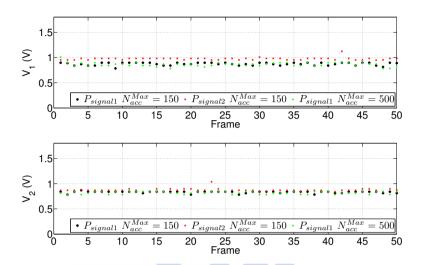

|    |       | 5.3.3                   | Sensor response to light pulses           | . 127 |

|    | 5.4   | Experi                  | mental Results Conclusion                 | . 130 |

| Co | nclus | sions                   |                                           | 135   |

| A  | The   | rmal No                 | oise Related Distance Error Demonstration | 139   |

xiv CONTENTS

143

#### B Maximum Charge Integration for Every ToF Technique Demonstration

\*

Siguiendo el reglamento de los estudios de tercer ciclo de la Universidad de Santiago de Compostela, aprobado en la Junta de Gobierno del día 7 de abril de 2000 (DOG de 6 de marzo de 2001) y modificado por la junta de Gobierno de 14 de noviembrede 2000, el Consejo de Gobierno de 22 de noviembre de 2003, de 18 de julio de 2005 (artículos 30 a 45), de 11 de noviembre de 2008, de 14 de mao de 2009; y, concretamente, cumpliendo con las especificaciones indicadas en el capítulo 4, artículo 30, apartado 3 de dicho reglamento, se muestra a continuación el resumen de la tesis.

Desde principios de los años 70 la industria de los semiconductores ha seguido el camino marcado por la "ley de Moore" y el número de transistores por procesador se ha ido duplicando de forma continua aproximadamente cada dos años. Esto ha permitido la aparición de dispositivos electrónicos con mayores velocidades de operación, mayor capacidad de procesado y menor coste de fabricación. Sin embargo en los últimos años ha aumentado la importancia de los sistemas que además de procesar información también son capaces de captarla y transmitirla, en lo que se conoce como "More-than-Moore".

Estos avances permiten vislubrar un futuro en el que el llamado internet-de-las-cosas tiene cada vez más importancia. Este concepto define la interconexión a través de internet de dispositivos electrónicos integrados en objetos de uso diario. Estos dispositivos tendrían la capacidad de captar indormación de su entorno, procesarla y comunicarse entre ellos para,

así mejorar su funcionamiento.

Además de esto, dos de los sectores relacionados con la electrónica con mayor potencial de crecimiento que existen ahora mismo son el de los sistemas avanzados de asistencia a la conducción (ADAS por sus siglas en inglés) y el de la realidad virtual/realidad aumentada. Para el primero de ellos se estima que alcanzará los 10 mil millones de dolares de beneficios en todo el mundo para 2020 y para el segundo esta estimación supera los 100 mil millones. A esto hay que añadir el gran interés que están despertando en la actualidad los vehículos aéreos no tripulados (UAVs por sus siglas en inglés), también llamados drones. En todos los casos citados hasta ahora la capatación de información, en particular inforamcion 3D, sobre el entorno en el que se encuentran es fundamental.

Para captar la información 3D del entorno existen diferentes tecnologías todas ellas basadas en el uso de ondas, ya sea luz, microondas o ultrasonidos. De todas estas opciones las ópticas son las que tienen mayor potencial para obtener esta información de manera precisa, rápida y en dispositivos de tamaño compacto.

En general se pueden usar dos técnicas distintas para el obtener la información 3D de un entorno con métodos ópticos: por triangulación o por Tiempo de Vuelo (ToF por sus siglas en inglés). El primero usa dos o mas perspectivas para determinar las distancias del sensor a los objetos de su entorno. Los sensores ToF miden el tiempo que tarda una señal luminosa en ir y volver para calcular estas distancias.

En el caso de sistemas que usan triangulación existen dos técnicas diferentes para hacerlo. La primera usa al menos dos cámaras en dos posiciones diferentes para captar la escena desde distintas perspectivas. Después, cada píxel de una de las cámaras se relaciona con el píxel de la otra cámara que está captando el mismo punto de la escena y la distancia hasta ese punto es calculada en base a la posición relativa de estos píxeles. El problema de esta técnica es que muy exigente en términos de potencia de computación porque para cada píxel de una cámara es necesario encontrar el equivalente en la otra. Además, el proceso puede fallar si la escena tiene poca información visual o si ésta es muy ambigua. La otra técnica que se puede utilizar

para calcular la información 3D de una escena mediante triangulación se basa en sustituir una de las cámaras por un sistema de iluminación. Si este sistema proyecta un patrón de luz conocido la técnica se denomina "de luz estructurada". Esta técnica tiene la ventaja de que se evita el proceso de correlación entre píxeles pero, en general, consigue poca resolución. Otra forma es utilizar como sistema de iluminación un láser e ir moviéndolo por la escena para escanearla. Sin embargo, las partes mecánicas extra que esto conlleva complican el sistema e incrementan su precio.

En contraste con esto, los sensores de tiempo de vuelo tienen el potencial para obtener la información 3D de la escena completa de forma rápida y sin necesidad de partes móviles o una gran potencia de computación. La luz que usan estos sensores es infrarroja de forma que no moleste a las personas moviéndose por dicho entorno y, normalmente, se utilizan láseres o diodos LED para generarla. El sistema emite señales luminosas que son reflejadas por los objetos de la escena y enfocadas en el sensor de tiempo de vuelo por un sistema de lentes. Cada píxel del sensor mide el tiempo que tardan dichas señales en llegar y, como la velocidad de la luz es una constante conocida, calculan la distancia desde la que se reflejan.

Sin embargo, los sensores de tiempo de vuelo tienen sus propias desventajas. Las más importantes están relacionadas los requisitos que tienen en términos de velocidad, ruido y bajos niveles de señal que tienen que medir. La razón de esto es que la potencia luminosa máxima que pueden emitir está restringida para evitar lesiones oculares. Por esta razón todos los sensores de tiempo de vuelo accumulan un gran número de medidas sobre las señal emitida para calcular la información de la distancia. Otro problema típico de estos sensores es que captan no sólo la luz que ellos mismos emiten sino también toda la demás luz que hay en el entorno, denominada luz de fondo. Esta luz de fondo degrada la calidad de las medidas de los sensores de tiempo de vuelo hasta el punto de que, si es muy alta como, por ejemplo en exteriores, puede que las medidas no sean posibles.

Las técnicas usadas por los sensores de tiempo de vuelo puede clasificarse en directas e indirectas. Las primeras miden el tiempo que tardan las señales, que generalmente son pul-

sos de luz, en ir y volver directamente. Los píxeles de estos sensores tienen relojes de alta precisión que se inician con la emisión de la señal y se paran cuando la señal es captada. Como necesitan mucha precisión en la medida del tiempo de llegada de la señal suelen usar como sensores pfotodiodos de efecto avalancha (SPAD por sus siglas en inglés). Los sensores que usan técnicas de tiempo de vuelo indirectas extrapolan la información de tiempo de vuelo de otras medidas. Estas medidas, generalmente, son integraciones de la luz captada sincronizadas con la emisión de la señal. El trabajo de esta tesis está centrado en técnicas de tiempo de vuelo indirectas.

El capítulo 1 da una idea general sobre los sensores de tiempo de vuelo resume el estado del arte actual respecto a ellos. La publicaciones de tiempo de vuelo que se detallan en este capítulo se clasifican en dos tipos diferentes dependiendo de la forma en la que solucionan la necesidad de realizar medidas a muy alta velocidad. Algunas de ellas utilizan tecnologías CMOS no estándar o modifican alguno de las etapas de fabricación en dichas tecnologías. Otras, las que ulizan tecnologías CMOS de fabricación estándar, necesitan circuitería extra dentro del pixel para conseguir la suficiente velocidad de respuesta. Las primersa tienen la ventaja de un menor tamaño de píxel, lo que les permite obtener una mayor resolución. Las segundas se benefician del hecho de que las tecnologías estandar son mucho más baratas.

En el capítulo 2 se describen las distintas técnicas indirectas de tiempo de vuelo. Éstas se pueden dividir en moduladas o pulsadas. Las primeras utilizan señales luminosas periodicas, generalmente de tipo sinusoidal. Las segundas utilizan luz pulsada com señal luminosa. Dentro de las técnicas de tiempo de vuelo de luz pulsada existen diversos métodos para obtener la información de la distancia. Estos métodos se diferencian, fundamentalmente, la sincronización entre la emisión de los pulsos de luz y las integración de la luz recibida que realizan.

En este capítulo, además, se comparan entre sí las técnicas presentadas. Esta comparación se hace en términos del efecto del ruido en la medida de la distancia. En particular, el ruido de disparo (shot noise en inglés) y el ruido térmico en los condensadores de almacenamiento. El

primero de ellos surge de la naturaleza discreta de los fotones, que hace que el flujo de ellos, la intensidad luminosa, no sea constante sino que varíe de un instante a otro. Dado que este ruido es intrínseco a la señal luminosa y la luz de fondo está presente en todos los sensores de tiempo de vuelo, independientemente de la topología usada para implementarlos. Esta es la razón por la que la comparación de técnicas de tiempo de vuelo indirectas se haga en términos de su efecto sobre la medida de la distancia. El ruido térmico en las capacidades de almacenamiento va a limitar el tamaño maximo de dichas capacidades. Como se demuestra en este capítulo, aumentar la capacidad de almacenamiento aumenta también el efecto de este ruido en la medida. Sin embargo, reducir mucho su valor puede crear situaciones en las que el píxel se satura por exceso de carga integrada y la información de la distancia se pierde. Un forma de conciliar estos dos efectos es utilizar topologías que, primero, eliminen el efecto de la luz de fondo antes de integrar la señal luminosa. Y segundo, implementen la técnica del número adaptativo de accumulaciones. En esta técnica, el número de veces que la señal luminosa es integrada es controlado de manera individual para cada píxel. De esta forma si un píxel está próximo a saturar deja de integrar la señal, mientras que el resto de ellos pueden continuar haciéndolo. El capítulo finaliza con una comparación numérica entre las distintas técnicas de tiempo de vuelo, para seleccionar la optima para nuestro diseño.

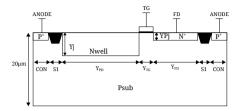

En el capítulo 3 se estudia la posibilidad de fabricar un sensor de tiempo de vuelo en tecnología CMOS estándar que realice la integraciones a nivel de dispositivo. Como ya se ha mecionado, estas tecnologías no disponen de foto-sensores con esta capacidad. Para su implementación sería necesario violar algunas reglas de diseño. Dados los riesgos que esto implica se realizó un estudio a nivel de dispositivo con el software comercial ATLAS de Silvaco. En particular el foto-sensor estudiado fue el "pinned" con puertas de transmisión para controlar las integraciones y difusiones flotantes para el almacenamiento de la carga. Este estudio se centró en tres parámetros distintos: la corriente oscura del dispositivo, el effecto del transistor de reset en la medida y la velocidad de transmisión de cargas. Las reglas de diseño que ignoran para la febricación de este dispositivo son geométricas, ya que los per-

files de dopado no se pueden modificar por usuarios externos a la fábrica. Las partes del mismo que se ven afectadas por estas reglas geométricas están en zona de alta generación de corriente oscura, con lo que se ha estudiado el comportamiento de dicha corriente con respecto a las modificaciones el el dispositivo propuestas. El transistor de reset afecta a la medida introduciendo ruido en las difusiones flotantes y reduciendo el rango dinámico de las mismas. El alcance de estos efectos también se estudió en este captítulo. Por último, el tercer parámetro estudiado, es la velocidad de transmisión de cargas del dispositivo. Estas simulaciones muestran que, sin un control sobre los perfiles de dopado, el dispositivo fabricado no sería lo suficientemente rápido en esta transmisión como para trabajar a la velocidad exigida por los sensores de tiempo de vuelo.

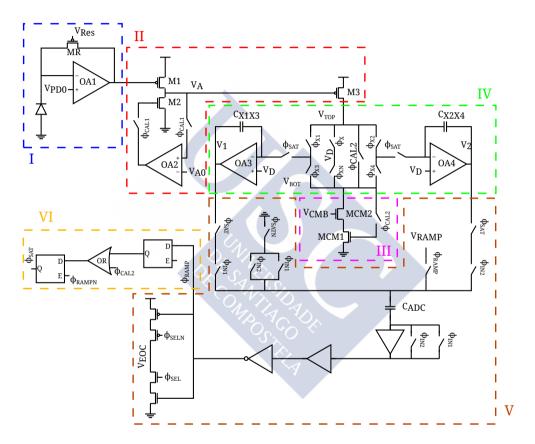

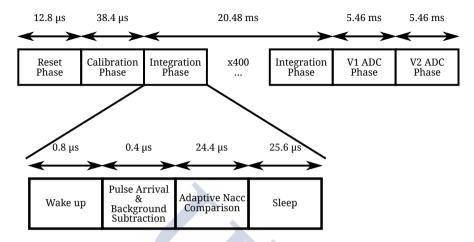

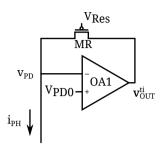

Descartada la opción de realizar un sensor de tiempo de vuelo que realice las integraciones a nivel de dispositivo se optó por diseñar un píxel con circuitería extra para aumentar su velocidad. El diseño de dicho píxel, en tecnología CMOS estandar de 0.18 μm, está recogido en el capítulo 4. El foto-diodo utilizado en este píxel es propio de la tecnología utilizada y está formado por un pozo N sobre sustrato P. Además, la técnica de tiempo de vuelo que selecionada utiliza pulsos de luz como señal luminosa. Aunque la anchura de dichos pulsos puede modificarse de manera externa, en el diseño de nuestro píxel siempre se asumieron pulsos de luz de 50 ns. Para aumentar la potencia luminosa de dichos pulsos sin aumentar la potencia media de luz emitida, y por lo tanto cumplir con las regulaciones sobre seguridad ocular, estos pulsos se emiten cada 50 μs.

El píxel amplifica la corriente generada por la señal luminosa antes de integrarla en las capacidades de almacenamiento. Debido a la baja potencia de dicha señal y las altas velocidades a las que se deben realizar las integraciones, la amplificación de la señal no es posible en modo corriente. Por esta razón, la señal es, primero convertida a voltaje por un amplificador a transimpedacia, es amplificada, y, después, convertida otra vez en corriente para su integración. En la etapa en la que la señal de voltaje es amplificada su valor de corriente continua es fijado a un valor concreto seleccionable desde el exterior del píxel. Dado que la

corriente continua de esta señal viene determinada por la luz de fondo captada por el sensor esto es equivalente a eliminar dicha luz de fondo de la señal que se va a integrar. Las simulaciones muestran que esto permite a nuestro píxel trabajar bajo niveles luminosos de hasta 20 kluxes. Despues de la integración de cada pulso de luz el píxel compara la señal acumulada con una tensión externa, para saber si las capacidades de almacenamiento están cerca de saturar. Si ese es el caso el píxel deja de integrar pulsos evitando así la pérdida de la información de la distancia. El píxel diseñado ucupa un área de  $62\times62~\mu\text{m}^2$  con un foto-sensor de  $50\times50~\mu\text{m}^2$ .

Un array de 52×63 de dichos píxeles fue fabricado. Además de este array el chip incluye toda la circuitería extra necesaria para su funcionamiento. En primer lugar un banco de memorias digitales para almacenar la información digitalizada de cada pixel antes de que ésta pueda ser extraída fuera del chip. Además de esto también incluye un selector de filas y un selector de columnas para controlar el proceso de digitalización y extracción de la información del chip. Otro circuito implementado en el chip es un contador digital utilizado como parte del proceso de digitalización. Finalmente, también se diseño dentro del chip un bloque de control que se ocupa del funcionamiento completo del array. En el capítulo 5 se describen con detalle estos circuitos.

El capítulo también muestra el montaje experimental utilizado para testear el chip. Este montaje incluye, en primer lugar, la placa de cirucito impreso (PCB por sus siglas en inglés) en donde va montado el chip. Esta place tiene, además toda la circuitería necesaria para generar las tensiones de alimentación y de referencia del chip. También, dentro del montaje experimental, fue necesario el diseño de otra PCB con el módulo de iluminación, esto es, el sistema que genera las señales luminosas que serán después recibidas por el chip. Esta placa contiene tres láseres infrarrojos con la circuitería necesaria para su control y alimentados por un regulador de voltaje. Controlando la tensión de alimentación se puede controlar la potencia luminosa emitida. Otros componentes necesarios para el testeo del chip fueron la lente y su marco para enfocala sobre el chip. Éste último fue diseñado e impreso en 3D. Finalmente

el control sobre todos los componentes se ejecute utilizando una FPGA que, además lee los datos obtenidos y calcula a partir de ellos la información tridimensional de la escena.

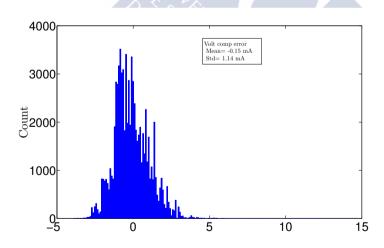

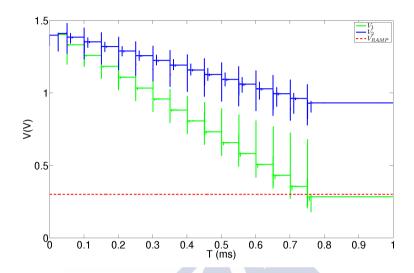

Este capítulo también incluye las medidas experimentales realizadas sobre el chip. En primer lugar muestra un error en el diseño del chip con respecto al reseteo de las capacidades de almacenamiento. Dicho error evita que todas las capacidades se reseteen a un valor conocido y, en lugar de ello, hace que cada una se tenga su propio valor, cambiando éste de fotograma a fotograma y de píxel a píxel. Para corregir este error se propone digitalizar el valor de reset de cada píxel antes de iniciar las integraciones de los pulsos de luz. El efecto que esto tendría sobre la medida sería el de reducir el número de fotogramas por segundo del sistema. A mayores de esto el funcionamiento del chip no concuerda con el mostrado por simulaciones. El valor de tensión final en las capacidades de almacenamiento de cada píxel tiende a converger a un valor fijo, independiente de el número de acumulaciones realizado, de la potencia luminosa de los pulsos de luz o, incluso, de la logitud de dichos pulsos. Después de exahustivas medidas para descartar cualquier otro fenómeno se ha concluído que la razón de este fallo está en el solapamiento de cuatro señales de control durante la integración de los pulsos. Dichas señales son críticas para el funcionamiento de nuestro sensor de tiempo de vuelo y, en caso de solaparse, se produciría pérdida de carga en las capacidades de almacenamiento llegando a un estado estable en pocos pulsos.

El capítulo final de este trabajo resume todas las conclusiones extraídas de la investigación realizada y comenta la dirección que se tomará en el futuro para continuar con ella.

## Introduction

Several methods exist to capture the 3D information of an entire scene. The greatest potential to achieve good distance resolution without expensive set-ups is achived by the ones that use optical based techniques and, among them, Time-of-Flight sensors provide good accuracy, fast response and a compact measuring system simultaneously. These sensors extract the distance information by measuring the time a light signal needs to travel back and forth the target. This work introduces a Time-of-Flight pixel design in standard CMOS technology with improved robustness to the background light.

#### **Contributions**

The primary contributions of this dissertation are:

A study of the performance of the different indirect Time-of-Flight techniques in terms

of the effect of the shot and thermal noise in the distance calculation.

This contribution can be found in the following publication:

Distance Measurement Error in Time-of-Flight Sensors Due to Shot Noise. Julio Illade-Quinteiro, Víctor Manuel Brea, Paula López, Diego Cabello and Ginés Doménech-Asensi in Sensors Journal. • A study of the possibility of performing the demodulation of the Time-of-Flight signal at device level in standard CMOS technologies.

The publications where this contribution can be found are listed below.

- Comparison of Photosensing Structures in CMOS Standard Technology for Timeof-Flight Sensors. Julio Illade-Quinteiro, Víctor Manuel Brea, Paula López, Diego Cabello and Ginés Doménech-Asensi in 28th Intenational Conference on the Design of Circuits and Integrated Systems (DCIS 2013).

- Dark current in standard CMOS pinned photodiodes for Time-of-Flight sensors

Julio Illade-Quinteiro, Víctor Manuel Brea, Paula López, Bea Blanco-Filguiera, Diego

Cabello and Ginés Doménech-Asensi in 2014 IEEE Workshop On Microelectronics

And Electron Devices (WMED 2014).

- Custom design of pinned photodiodes in standard CMOS technologies for Timeof-Flight sensors Julio Illade-Quinteiro, Víctor Manuel Brea, Paula López, Diego Cabello and Ginés Doménech-Asensi in 14th International Workshop on Cellular Nanoscale Networks and their Applications (CNNA 2014).

- Dark Current Optimization of 4-Transistor Pixel Topologies in Standard CMOS

Technologies for Time-of-Flight Sensors Julio Illade-Quinteiro, Víctor Manuel Brea,

Paula López and Diego Cabello in IEEE International Symposium on Circuits and

Systems (ISCAS 2015).

- Four-Transistor Pinned Photodiodes in Standard CMOS Technologies for Timeof-Flight Sensors Julio Illade-Quinteiro, Víctor Manuel Brea, Paula López, Diego Cabello and Ginés Doménech-Asensi in Semiconductor Science and Technology.

- A ToF pixel in standard CMOS technology design with in-pixel background suppression and adaptive number of accumulations.

Introduction 11

This contribution can be found in the following publication:

Time-of-flight chip in standard CMOS technology with in-pixel adaptive number of accumulations. Julio Illade-Quinteiro, Víctor Manuel Brea, Paula López and Diego Cabello in *IEEE International Symposium on Circuits and Systems (ISCAS 2016)*.

#### **Outline**

This thesis is divided in five chapters. Chapter 1 gives a context of the state-of-the-art in indirect ToF sensors. Chapter 2 explains in detail the Time-of-Flight techniques used by these sensors. A comparison between them in terms of the error in the distance measurement introduced by the shot and thermal noise is also made in this chapter. The possibility of a device level demodulation pixel in standard CMOS technologies is explored in Chapter 3. In Chapter 4 a detailed description of the designed pixel together with circuit level simulations to check its viability is presented. Finally, the experimental results of the fabricated device, together with the set-up implemented to obtain them are presented in Chapter 5.

## **Chapter 1**

## **Background and Related Work**

Contactless range measurement sensors are of great interest in areas such as safety, robotics, virtual reality or automotive. Among all the methods available optical based are the ones with greater potential to provide good accuracy, fast response and a compact measuring set-up simultaneously. Two different techniques are usually employed in these sensors: triangulation and Time-of-Flight (ToF). The first one uses multiple points of view to determine the distance to a target. ToF extracts the distance information by measuring the time a light signal needs to travel back and forth the target.

The acquisition of the distance information for an entire frame can be done in two different ways for a triangulation-based system. The first one is to use two or more cameras in two different positions to capture the scene from different points of view. After that, each pixel of one of the cameras is correlated with the pixel of the other camera acquiring the same point of the scene and the distance to that point is calculated based on the relative position of these pixels. This process is computationally very expensive because, for each pixel of one of the cameras the corresponding one from the other camera must be found. In addition to this, if the scene has low level or ambiguous features, the distance calculation can fail. The

second way to proceed in a triangulation-based system is by substituting one of the cameras with a light emitter. In this case, if the light emitter is a projector illuminating the scene with a known light pattern it is called structured light technique. This technique has the advantage of avoiding the pixel correlation problem but in general the spatial resolution achieved is low. Another way is to use a laser and move it through the entire scene to scan it, but the mechanical parts involved increase the complexity and cost of the system.

In contrast to this, ToF sensors have the potential of providing the distance information of an entire scene at a fast frame rate without the need of neither moving parts nor image matching algorithms [1]. However, ToF sensors have disadvantages of their own. The most problematic are the ones concerning their design demands as they have severe requirements in terms of speed, noise and minimum measurable levels for the pixels used in the sensor [2]. The reason for this comes from the fact that the power of the emitted light signal is limited by eye safety regulations [3]. In addition to this, the light not related to the emitted signal present in the scene, called background light, is also acquired by the ToF sensors and it degrades the distance measurement. If this background light is too high, for example in outdoor scenarios, the deterioration of the measurement can be so bad that the distance determination is not possible at all.

It is worth mentioning that the frequency of the light signal used is going to affect the accuracy of the ToF measurement and the maximum measurable distance by the sensor. Increasing this frequency improves the accuracy but reduces the measurable range. In [4] and [5] methods to improve the ToF measurement accuracy by increasing the frequency of the light signal used without diminishing the maximum distance range are presented.

ToF systems use a light source, usually a laser or LED, to illuminate the scene with infrared light, so the operation is unobtrusive to the people around it. This light signal is reflected by the objects on the scene and a set of lenses focus it in an array of ToF pixels. Each pixel measures the time difference between the emission and the reception of the signal, called Time-of-Flight,  $T_{oF}$ . Since the speed of light is a known constant, the distance to the

target can be easily calculated from this.

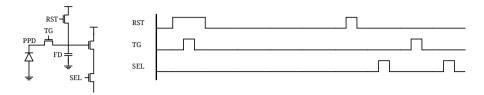

ToF methods can be divided between direct and indirect. The first ones measure the  $T_{oF}$  directly and the light signal they use are square pulses. Their pixels have a highly accurate counter that is started synchronized with the emission of the pulse and stops with its arrival. Because of their need of high time-of-arrival resolution almost all the ToF pixels employ single-photon avalanche diodes (SPAD) as sensors [2]. On the other hand, indirect ToF methods extrapolate the  $T_{oF}$  parameter from other measurements. These measurements are usually integrations of the light being received synchronized with the signal emission. This work is centered on indirect ToF methods and an extensive explanation of how they work will be given in Chapter 2.

According to the type of the light signal, indirect ToF methods can be classified in modulated or pulsed ToF. The first ones use continuous wave signals, usually sinusoidal ones, while the second ones use light pulses. Different ToF sensors have been reported in the literature both using modulated and pulsed techniques.

Regardless of the ToF technique, all the sensors must address the need of fast integration measurements. This can be achieved by two different means, either these integrations are performed at device level, or extra circuitry is added to the pixels. In the first case standard CMOS technologies can not be used or expensive modifications to them must be done. However, in the second case the extra circuitry increases the pixel size and reduces its fill-factor.

The first examples of ToF pixels designed in non-standard technologies can be found in [6], [7] and [8]. The sensors here presented were fabricated in mixed CCD/CMOS technology. The signal is sensed by a photogate and several transmission gates attached to it in a CCD style will drive the generated current to different regions for their integration. In [9] extra circuitry to subtract the component of the background light from the integrated signal is proposed for these pixels.

In [10] the sensor is also a photogate and two transmission gates are added to drive the generated current to the integration nodes. However, in this case the fabrication technology

is a  $0.35 \mu m$  standard CMOS one. Since the sensors fabricated in this technology are not fast enough an extra buried N-layer was added to the process.

Other means of improving the speed of the sensor were presented in the literature. For example, in [11] the doping profile of the sensor is modified to create a lateral electric field inside. In other implementations the lateral electric field is achieved by adjusting the voltage in several points around the photo sensor. Such is the case of [12], [13] and [14] were one, two and six transmission gates, respectively, are situated around a pinned photodiode. By modifying the voltage in these gates the generated charges are driven to the current nodes to be integrated. Other example can be seen in [15] where also a pinned photodiode is used as photosensor, but instead of transmission gates polysilicon extended gates are used to direct the photocurrent.

In [4] extra fabrication layers are also added. In this case two photogates are used as photosensors, so one of them can be read while the other is integrating the signal and, thus, the speed is improved. Although the device is fabricated in 0.13 µm standard CMOS technology the p<sup>+</sup> layer between the photogates was modified to increase the isolation between them. In this pixel extra circuitry is added to subtract the background light component from the integrated signal and thus, improving the pixels robustness in high background ambients.

The most straightforward approach to increase the sensor performance is to design the ToF pixel in CIS technology and use a pinned photodiode with several transmission gates as photosensor. This is done in [16], [17], [18] and [19]. The pixels shown in these articles have the extra advantage of also performing conventional image acquisition on the same chip. The first three ones have photosensors that can alternate between the conventional and the ToF measurement while the last one mixes ToF pixels and conventional ones in the same array. The topology proposed in these articles is improved in [20], [21] and [22] by adding extra circuitry to deal with the background light component of the signal.

As explained before, if standard CMOS technology is used, extra circuitry must be added to improve the response of the photosensors. Further explanations of this can be found in [23].

One way to do this is to duplicate the photosensor and the acquisition circuitry so one of them can integrate the signal while the information of the other is being processed. This happens in [24], [25], [26] for a pixel topology very similar to the 3-transistors configuration and in [27] for another similar to the 4-transistors one. Another example of ToF pixel fabricated in standard CMOS technology can be found in [28].

The pixels fabricated in standard CMOS technology until now rely on intermediate storage capacitances to integrate the signal while is being received and then transfer it to a final storage node to accumulate it. The pixel presented in [29] uses a series of switches to drive the photocurrent generated by the light signal to the final storage capacitance directly, without intermediate storage nodes. This idea is improved in [30], [31] and [32] where current mirrors are added to eliminate the background component before the storage.

The objective of this work is to design a pixel in standard CMOS technology with improved robustness to the background light. To fulfill this, techniques like in-pixel background suppression and adaptive number of accumulations are used. Chapter 2 provides a review of the existing indirect ToF techniques and analyze them in terms of noise impact in the measurement. In Chapter 3 the possibility of performing the demodulation of the signal at device level in standard CMOS technologies is explored through simulations. Chapter 4 gives a detailed description of the designed ToF pixel. Finally, Chapter 5 shows the experimental set-up to measure the sensor fabricated and summarizes the experimentally obtained results.

### Chapter 2

# Fundamentals of Time-of-Flight Sensors

Optical ToF methods can be classified in direct and indirect [2]. The first ones measure directly the time delay between the emitted and the received light signals. In the indirect ones the time is extrapolated from other measurements. This work is centered on indirect ToF methods. In this chapter the different techniques used to perform indirect ToF are described.

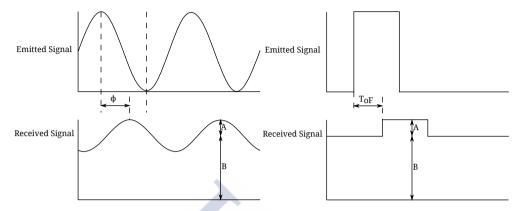

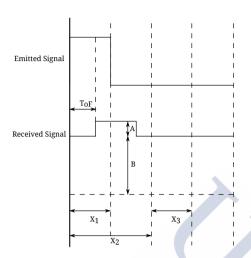

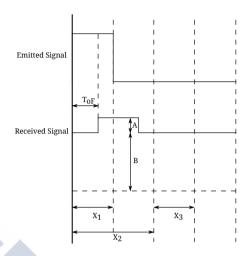

According to the light signal, indirect ToF methods can be divided in modulated, if the signal is a continuous wave, or pulsed ToF, if light pulses are used. Fig. 2.1 and Fig. 2.2 show the operation modes for modulated and pulsed ToF sensors, respectively. As it can be seen, besides the phase,  $\phi$ , or time delay,  $T_{oF}$ , two more parameters are unknown in the incoming signal, namely, its amplitude, A, and the background light of the scene, B. This is the reason why at least three measurements in a cycle or pulse are needed to calculate a distance. In indirect ToF sensors, these measurements are integrations of the photocharges generated by the sensor in response to the incident light for different time intervals.

Figure 2.1: Light emission in modulated ToF sensors.

Figure 2.2: Light emission in pulsed ToF sensors.

In Section 2.1 the working principle of each ToF technique will be explained. Regardless of the technique, ToF measurements are severrily affected by from noise effects, with shot and thermal noise as the most relevant ones. The effect of this noise in the distance calculation is described in Section 2.2. The selection of the ToF technique to be implemented in this work will be based on the effect of noise. Section 2.3 provides the theoretical background needed to calculate realistic values for the parameters used in the noise equations. In Section 2.4 a comparison of different techniques is performed and, finally, in Section 2.5 the selected topology is detailed. Part of the material presented in this chapter was published in [33].

#### 2.1 Indirect ToF Techniques

#### 2.1.1 Modulated Time-of-Flight

In the modulated ToF operation the emitted signal is a continuous-wave signal modulated in time, usually a sinusoid. The phase difference between the emitted and the received light signals,  $\phi$ , depends on the distance traveled by the light, from the sensor to the object and

21

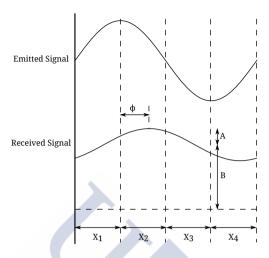

Figure 2.3: Measurements to perform indirect ToF with modulated light signal.

back again. The separation between the sensor and the object can then be calculated as:

$$L = \frac{c}{2} \frac{\phi}{\omega} = \frac{c}{2} \frac{\phi \tilde{T}}{2\pi} \tag{2.1}$$

where c is the speed of light,  $\omega$  the angular frequency and  $\tilde{T}$  the period of the signal. Fig. 2.3 shows the technique to measure the phase difference. In this figure A is the amplitude in number of photons per second reaching the photosensor due to the signal, and B the photons per second reaching the photosensor because of the background. Each  $x_i$  measurement is the integration of these photons in the time interval  $X_i$ . Four measurements are performed, instead of the minimum three, to simplify the calculation. After repeating these integrations  $N_{acc}$  times, the number of photons integrated in each  $x_i$  measurement is:

$$x_{1} = \frac{N_{acc}B\tilde{T}}{4} + \frac{\sqrt{2}A\tilde{T}N_{acc}}{2\pi}sin(\phi)$$

(2.2a)

$$x_2 = \frac{N_{acc}B\tilde{T}}{4} + \frac{\sqrt{2}A\tilde{T}N_{acc}}{2\pi}cos(\phi)$$

(2.2b)

$$x_3 = \frac{N_{acc}B\tilde{T}}{4} - \frac{\sqrt{2}A\tilde{T}N_{acc}}{2\pi}sin(\phi)$$

(2.2c)

$$x_4 = \frac{N_{acc}B\tilde{T}}{4} - \frac{\sqrt{2}A\tilde{T}N_{acc}}{2\pi}cos(\phi)$$

(2.2d)

(2.2e)

from which, the distance can be obtained as:

$$L_{Mod} = \frac{c}{2} \frac{\tilde{T}}{2\pi} a tan \frac{x_3 - x_1}{x_4 - x_2}$$

(2.3)

#### 2.1.2 Pulsed Time-of-Flight

Pulsed ToF employs square wave signals. The time delay between the emitted and received light pulses,  $T_{oF}$ , depends on the distance traveled by the light, that can be calculated as:

$$L = \frac{c}{2}T_{oF} \tag{2.4}$$

Two measurement techniques exist for the determination of the distance using pulsed ToF, Phase Shift Determination (PSD), and Multiple Double Short Time Integration (MDSI). As in the case of modulated ToF, *A* and *B* are the number of photons per second hitting the photosensor because of the signal and the background, respectively.

#### **Phase Shift Determination**

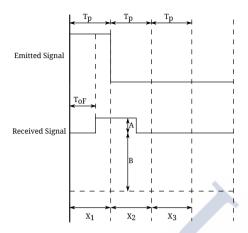

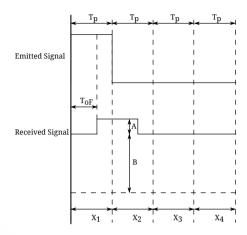

In the PSD case all the measurements have a duration equal to that of the emitted pulse,  $T_p$ . From Fig. 2.4 and Fig. 2.5, it can be seen that the PSD technique can be realized in two different ways, with either three, Fig. 2.4, or four measurements, Fig. 2.5. In both cases, the first measurement interval,  $X_1$ , is synchronized with the emitted pulse, while the second,  $X_2$ ,

Figure 2.4: Measurements for pulsed PSD-1B ToF.

Figure 2.5: Measurements for pulsed PSD-2B ToF.

comes right after it. The third and fourth measurements are carried out without light signal in order to sense the background light. We will refer to the technique depicted in Fig. 2.4 as PSD with one background measurement (PSD-1B) and to the one on Fig. 2.5 as PSD with two background measurements (PSD-2B). For PSD-1B it is easy to show that the number of photons in each measurement interval, after  $N_{acc}$  accumulations, is:

$$x_1 = N_{acc}BT_p + N_{acc}A(T_p - T_{oF})$$

(2.5a)

$$x_2 = N_{acc}BT_p + N_{acc}AT_{oF} (2.5b)$$

$$x_3 = N_{acc}BT_p \tag{2.5c}$$

From (2.5),  $T_{oF}$  can be calculated and the distance will be:

$$L_{PSD-1B} = \frac{c}{2} T_p \frac{x_2 - x_3}{(x_1 - x_3) + (x_2 - x_3)}$$

(2.6)

For the PSD-2B case (2.5a-2.5c) are modified to:

$$x_1 = N_{acc}BT_p + N_{acc}A(T_p - T_{oF})$$

(2.7a)

$$x_2 = N_{acc}BT_p + N_{acc}AT_{oF} (2.7b)$$

$$x_3 = N_{acc}BT_n \tag{2.7c}$$

$$x_4 = N_{acc}BT_p \tag{2.7d}$$

and the distance calculation changes to,

$$L_{PSD-2B} = \frac{c}{2} T_p \frac{x_2 - x_4}{(x_1 - x_3) + (x_2 - x_4)}$$

(2.8)

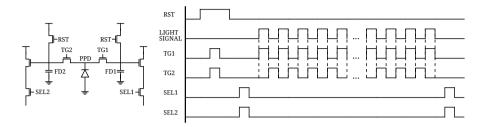

### **Multiple Double Short Time Integration**

In the MDSI technique [34], the first measurement is also synchronized with the emitted pulse and has the same duration, while for the second its duration is doubled in order to ensure that the entire received pulse is measured during  $X_2$ . As in PSD, the third and fourth measurements are performed without light signal to sense the background. The time diagram for these measurements are shown in Fig. 2.6 for MDSI-1B, and in Fig. 2.7 for MDSI-2B.

For MDSI-1B the number of photons at the photosensor,  $x_i$ , in each measurement interval  $X_i$ , when they are repeated  $N_{acc}$  times, can be inferred from Fig. 2.6 as:

$$x_1 = N_{acc}BT_p + N_{acc}A(T_p - T_{oF})$$

(2.9a)

$$x_2 = 2N_{acc}BT_p + N_{acc}AT_p (2.9b)$$

$$x_3 = N_{acc}BT_p (2.9c)$$

Using (2.9a-2.9c) and (2.4), the distance can be calculated as:

$$L_{MDSI-1B} = \frac{c}{2} T_p \frac{x_2 - x_1 - x_3}{x_2 - 2x_3}$$

(2.10)

For the MDSI-2B technique (2.9a)-(2.9c) are modified to take into account the extra background measurement:

Figure 2.6: Measurements for pulsed MDSI-1B ToF.

**Figure 2.7:** Measurements for pulsed MDSI-2B ToF.

$$x_1 = N_{acc}BT_p + N_{acc}A(T_p - T_{oF})$$

(2.11a)

$$x_2 = 2N_{acc}BT_p + N_{acc}AT_p (2.11b)$$

$$x_3 = N_{acc}BT_p (2.11c)$$

$$x_4 = 2N_{acc}BT_p (2.11d)$$

In this case, the distance becomes:

$$L_{MDSI-2B} = \frac{c}{2} T_p \frac{(x_2 - x_4) - (x_1 - x_3)}{x_2 - x_4}$$

(2.12)

# 2.2 Noise Related Distance Error

In the last section, the different indirect ToF techniques were shown. Each one of these techniques needs the integration of the photons reaching the sensor in three or four  $X_i$  time windows. These integrations will suffer from noise, being the most relevant ones the shot

and the thermal noise. This section models these noises in the sensor and their effect on the distance calculation.

### 2.2.1 Shot Noise

Because of the discrete nature of photons, the measurements  $x_i$  previously described suffer from shot noise [35]. In this case, each one of the measurements comes from the integration of the flow of photons reaching the sensor. These integrations follow a Poisson probability distribution, so its variance is:

$$(\delta x_i)^2 = x_i \tag{2.13}$$

To understand how this noise affects the distance measurement, error propagation can be applied as:

$$\Delta L = \sqrt{\sum_{i} \left(\frac{\partial L}{\partial x_{i}}\right)^{2} (\delta x_{i})^{2}}$$

(2.14)

In the modulated ToF case, applying (2.14) to (2.3) yields [8]:

$$\Delta L_{mod}^{SN} = \frac{c}{2} \frac{\sqrt{TB}}{2\sqrt{8}A\sqrt{N_{acc}}}$$

(2.15)

For PSD techniques, using (2.6) and (2.8) gives:

$$\Delta L_{PSD-1B}^{SN} = \frac{c}{2} \frac{\sqrt{2BT_p^2 - (6B - A)T_{oF}(T_p - T_{oF})}}{A\sqrt{N_{acc}}\sqrt{T_p}}$$

(2.16)

$$\Delta L_{PSD-2B}^{SN} = \frac{c}{2} \frac{\sqrt{2BT_p^2 - (4B - A)T_{oF}(T_p - T_{oF})}}{A\sqrt{N_{acc}}\sqrt{T_p}}$$

(2.17)

as the uncertainties in the distance measurements. Similarly, for MDSI techniques, their distance error caused by the shot noise are derived from (2.10) and (2.12) as:

$$\Delta L_{MDSI-1B}^{SN} = \frac{c}{2} \frac{\sqrt{(4B+2A)T_p^2 + (6B+A)T_{oF}^2 - (8B+3A)T_pT_{oF}}}{A\sqrt{N_{acc}}\sqrt{T_p}}$$

(2.18)

|           | Distance                                                              | Distance error due to shot noise                                                                              |  |  |

|-----------|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|--|--|

| Modulated | $\frac{c}{2}\frac{T}{2\pi}\operatorname{atan}\frac{x_3-x_1}{x_4-x_2}$ | $rac{c}{2}rac{\sqrt{	ilde{T}B}}{2\sqrt{8}A\sqrt{N_{acc}}}$                                                  |  |  |

| PSD-1B    | $\frac{c}{2}T_{p}\frac{x_{2}-x_{3}}{(x_{1}-x_{3})+(x_{2}-x_{3})}$     | $\frac{c}{2} \frac{\sqrt{2BT_p^2 - (6B - A)T_{oF}(T_p - T_{oF})}}{A\sqrt{N_{acc}}\sqrt{T_p}}$                 |  |  |

| PSD-2B    | $\frac{c}{2}T_{p}\frac{x_{2}-x_{4}}{(x_{1}-x_{3})+(x_{2}-x_{4})}$     | $\frac{c}{2} \frac{\sqrt{2BT_p^2 - (4B - A)T_{oF}(T_p - T_{oF})}}{A\sqrt{N_{occ}}\sqrt{T_p}}$                 |  |  |

| MDSI-1B   | $\frac{c}{2}T_p \frac{x_2 - x_1 - x_3}{x_2 - 2x_3}$                   | $\frac{c}{2} \frac{\sqrt{(4B+2A)T_{p}^{2}+(6B+A)T_{oF}^{2}-(8B+3A)T_{p}T_{oF}}}{A\sqrt{N_{acc}}\sqrt{T_{p}}}$ |  |  |

| MDSI-2B   | $\frac{c}{2}T_p \frac{(x_2 - x_4) - (x_1 - x_3)}{x_2 - x_4}$          | $\frac{c}{2} \frac{\sqrt{(6B+2A)T_{p}^{2}+(4B+A)T_{oF}^{2}-(8B+3A)T_{p}T_{oF}}}{A\sqrt{N_{acc}}\sqrt{T_{p}}}$ |  |  |

Table 2.1: Distance and its shot noise related error equations for different indirect ToF techniques.

$$\Delta L_{MDSI-2B}^{SN} = \frac{c}{2} \frac{\sqrt{(6B+2A)T_p^2 + (4B+A)T_{oF}^2 - (8B+3A)T_pT_{oF}}}{A\sqrt{N_{acc}}\sqrt{T_p}}$$

(2.19)

Table 2.1 gathers the distance equations and their shot noise related error for all the ToF techniques studied in this work. As it can be seen, this error is, in all cases, inversely proportional to the square root of  $N_{acc}$ . This means that the distance accuracy will improve if more accumulations are performed. Also, the shot noise related error is proportional to B, which means that higher values of background light will worsen the distance calculation.

### 2.2.2 Thermal Noise

To perform the ToF techniques, the light signal reaching the sensor must be transformed in an electrical one. One or more photosensors inside the pixel convert the received photons in charges, so the flux of photons reaching the sensor is converted in a current. This current is usually accumulated in storage capacitances. Because of their thermal energy, the electrons stored in these capacitances can flow in and out of them. This movement is random and generates a noise in the capacitor called thermal noise [36]. In this section the effect that this thermal noise has on the distance calculation is described.

Since the thermal noise affects the voltage signal accumulated in the storage capacitances, the distance calculation equations of Section 2.1 have to be modified to use these voltages instead of the photons integrated during the corresponding  $X_i$  measurement window. After that, the effect of the thermal noise in the distance calculation can be determined.

As it has been said, the photosensor converts the incoming flux of photons in a current. The relation between the number of photons per second, N, and the generated current,  $I_{ph}$ , is [37]:

$$I_{ph} = q \ QE \ N \tag{2.20}$$

where q is the electron charge and QE the quantum efficiency of the photosensor. This current integrated during an interval of time  $T_{integ}$  generates a voltage difference in the storage capacitor,  $C_{storage}$ , of:

$$V_{swing} = \frac{I_{ph} T_{integ}}{C_{storage}}$$

(2.21)

Using this equation the voltage swing generated in each  $x_i$  measurement can be calculated as:

$$V_{xi} = \frac{q \ QE}{C_{storage}} x_i \tag{2.22}$$

As it can be seen,  $V_{xi}$  is proportional to  $x_i$ , which means that, to calculate the distance with any of the ToF techniques described in Section 2.1,  $V_{xi}$  can be used instead of  $x_i$ . The second column of Table 2.2 shows the distance calculation equation for each technique using  $V_{xi}$  instead of  $x_i$ .

Any time the signal is updated in the storage capacitances thermal noise is added. The variance of this noise,  $\delta V_{xi}$ , depends on the capacitance value,  $C_{storage}$ , the temperature,  $T_{emp}$  and  $N_{acc}$ :

$$(\delta V_{xi})^2 = \frac{N_{acc} k T_{emp}}{C_{storage}}$$

(2.23)

|           | Distance                                                                                 | Distance error due to thermal noise                                                                                                      |

|-----------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Modulated | $\frac{c}{2} \frac{T}{2\pi} \operatorname{atan} \frac{V_{x3} - V_{x1}}{V_{x4} - V_{x2}}$ | $\frac{c}{2} \frac{1}{2q \ QE \ A} \sqrt{\frac{C_{storage}kT_{emp}}{N_{acc}}}$                                                           |

| PSD-1B    | $\frac{c}{2}T_{p}\frac{V_{x2}-V_{x3}}{(V_{x1}-V_{x3})+(V_{x2}-V_{x3})}$                  | $\frac{c}{2} \frac{\sqrt{T_{oF}^2 + (T_p - T_{oF})^2 + (T_p - 2T_{oF})^2}}{q \ QE \ A \ T_p} \sqrt{\frac{C_{storage}kT_{emp}}{N_{acc}}}$ |

| PSD-2B    | $\frac{c}{2}T_{p}\frac{V_{x2}-V_{x4}}{(V_{x1}-V_{x3})+(V_{x2}-V_{x4})}$                  | $\frac{c}{2} \frac{\sqrt{T_{oF}^2 + (T_p - T_{oF})^2}}{q \ QE \ A \ T_p} \sqrt{\frac{C_{storage}kT_{emp}}{N_{acc}}}$                     |

| MDSI-1B   | $\frac{c}{2}T_{p}\frac{V_{x2}-V_{x1}-V_{x3}}{V_{x2}-2V_{x3}}$                            | $\frac{c}{2} \frac{\sqrt{T_p^2 + (T_p - T_{oF})^2 + (T_p - 2T_{oF})^2}}{q \ QE \ A \ T_p} \sqrt{\frac{C_{storage}kT_{emp}}{N_{acc}}}$    |

| MDSI-2B   | $\frac{c}{2}T_{p}\frac{(V_{x2}-V_{x4})-(V_{x1}-V_{x3})}{V_{x2}-V_{x4}}$                  | $\frac{c}{2} \frac{\sqrt{T_p^2 + (T_p - T_{oF})^2}}{q \ QE \ A \ T_p} \sqrt{\frac{C_{storage}kT_{emp}}{N_{acc}}}$                        |

Table 2.2: Distance and its thermal noise related error equations for different indirect ToF techniques.

where k is the Boltzmann constant. Applying error propagation to the distance equations of Table 2.2 the effect of this noise can be calculated. These calculations are shown in Appendix A and the obtained results are shown in the third column of Table 2.2. As it can be seen, the thermal noise related distance error is inversely proportional to A and the square root of  $N_{acc}$ . This means that higher power light signals or more cycles or pulses of signal accumulated over time will reduce the thermal noise effect. Also, this distance error is proportional to the square root of  $C_{storage}$ , so larger storage capacitances increases the error in the distance calculation.

From the results collected in Table 2.2 it may seem that using small storage capacitances will benefit the pixel performance, but there is a maximum value of charge that a capacitance can store, so using small capacitances will increase the risk of saturation. If this happens the distance information is lost for that pixel.

The minimum value of capacitance that ensures that the voltage at  $C_{storage}$  will not reach saturation depends on the maximum amount of charge that is accumulated in the  $x_i$  integration window, as it can be seen from (2.21). The charge generated during each  $x_i$  measurement,  $Q_{xi}$ , can be calculated as:

$$Q_{xi} = q \ QE \ x_i \tag{2.24}$$

| Measurement Technique | Maximum charge integration                                                 |  |

|-----------------------|----------------------------------------------------------------------------|--|

| Modulated ToF         | $Q_{max}^{Mod} = rac{q \; QE \; N_{acc}A^{max}	ilde{T}}{\pi}$             |  |

| PSD-1B                | $Q_{max}^{PSD-1B} = q \ QE \ N_{acc} \left( B^{max} + A^{max} \right) T_p$ |  |

| PSD-2B                | $Q_{max}^{PSD-2B} = q \ QE \ N_{acc} A^{max} T_p$                          |  |

| MDSI-1B               | $Q_{max}^{MDSI-1B} = q \ QE \ N_{acc} \left(2B^{max} + A^{max}\right) T_p$ |  |

| MDSI-2B               | $Q_{max}^{MDSI-2B} = q \ QE \ N_{acc} A^{max} T_p$                         |  |

Table 2.3: Maximum charge accumulated in the storage capacitances for the different ToF techniques.

The expressions for the charges stored after  $N_{acc}$  accumulations for each indirect ToF technique are formulated in Appendix B. With these equations the maximum charge that the storage capacitances can accumulate can be calculated. Table 2.3 shows this result for each technique. The calculated value will depend, in addition to the selected technique, on the maximum number of photons per second of the ToF signal,  $A^{max}$ , and of the background,  $B^{max}$ , and on the selected number of accumulations  $N_{acc}$ . Using these equations together with (2.21) the minimum storage capacitance needed in a ToF pixel can be calculated. In Section 2.4 numerical examples will be provided using realistic values for  $A^{max}$ ,  $B^{max}$  and  $N_{acc}$ . Table 2.3 shows that for the pulsed ToF techniques with two background measurements (PSD-2B and MDSI-2B) and for the modulated ToF technique the maximum charge integrated during an  $x_i$  measurement does not depend on the background light. The reason for this is that, for these techniques, the charges from the  $x_3$  and  $x_4$  measurements are subtracted from the charges from  $x_1$  and  $x_2$ , respectively, before the storage, so ideally the charges saved are  $x_1 - x_3$  and  $x_2 - x_4$  and no background is accumulated. This has the added benefit of using only two storage capacitances, while in the pulsed ToF techniques with one background measurement (PSD-1B and MDSI-1B) three capacitors are needed, one for every  $x_i$  integration window.

One important thing to take into account is that the thermal noise is not present in ToF sensors where the demodulation is performed at sensor level using pinned photodiodes, like, for example, in [16, 18]. The reason for this is the voltage drop between the photodiode and the floating diffusions that act as storage capacitances, which does not allow electrons to flow between both structures just by their thermal energy. In Chapter 3 the viability of this type of structures in standard CMOS technology will be studied.

Summarizing, the thermal noise related distance error improves if  $N_{acc}$  or A are increased and worsens if  $C_{storage}$  is made larger, as it can be seen from the equations gathered in Table 2.2. On the other hand, there is a minimum  $C_{storage}$  value that ensures that these capacitances do not saturate and loose distance information. A solution to this trade-off is the adaptive number of accumulations [27]. This technique will be explained in Section 2.4.2 along with some numerical examples of the effect of the thermal noise in the distance calculation.

In this section, the effect of the shot and thermal noise in the distance calculation in ToF sensors was presented. To provide quantitative estimations of these effects from the equations of Table 2.1 and Table 2.2, realistic values A, B and  $N_{acc}$  must be provided. In the next section, equations for the estimation of these parameters are presented.

# 2.3 Signal and Background Estimations

# 2.3.1 Light Power Considerations

In ToF operation the light signal emitted by the source will reach the sensor after being reflected by the target. In order to calculate the distance error,  $\Delta L$ , for the different ToF techniques, it is necessary to determine the amplitude in number of photons reaching the photosensor due to the reflected signal, A, and the number of photons due to the background light, B, in terms of the emitted light power source and the ambient illuminance, respectively.

The maximum light power that reaches the target is determined by eye safety regulations [3]. After hitting the target, the light power density reflected by the target can be calculated as,

$$p_d(L) = \frac{\rho P_{light}}{4Ltan(\theta_{\parallel}/2)tan(\theta_{\perp}/2)}$$

(2.25)

where  $\rho$  is the target reflectivity,  $P_{light}$  the light source power, L the distance between the source and the target and  $\theta_{||}$  and  $\theta_{\perp}$  the emitter beam divergences parallel and perpendicular to the ground, respectively. After being reflected by the target this light signal hits the sensor, and the light power at the pixel,  $P_{pix}(L)$ , can be calculated as [15],

$$P_{pix}(L) = \frac{\tau_{opt} A_{PS} p_d(L)}{4F\#^2}$$

(2.26)

where  $\tau_{opt}$  is the optics transmission efficiency,  $A_{PS}$  the area of the photosensor and F# the F-number of the lenses. After obtaining the light power density at the sensor site from a specific distance, it can be extended to any distance as,

$$P_{pix}(L_2) = P_{pix}(L_1) \left(\frac{L_1}{L_2}\right)^2$$

(2.27)

With (2.26) the value of A can be calculated as:

$$A = \frac{\lambda}{hc} P_{pix}(L) \tag{2.28}$$

where  $\lambda$  is the wavelength of the incident light and h the Planck's constant. Finally, B can be calculated using the light power from typical values of luminance and conversion factors,  $P_B$ , see, for example, [37]. Thus,

$$B = \frac{\lambda}{hc} P_B \tag{2.29}$$

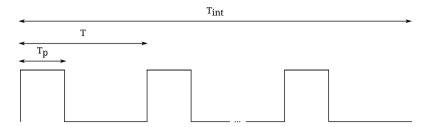

# 2.3.2 Signal Accumulation

As explained, regardless of the ToF technique, signal averaging by means of several accumulations is needed in order to reduce the shot noise of a single distance measurement and,

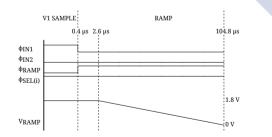

**Figure 2.8:** Time diagram showing  $T_p$ , T and  $T_{int}$  for pulsed ToF techniques.

consequently the uncertainty in the distance measurement,  $\Delta L$ . In this section we will calculate the value of  $N_{acc}$  for each ToF technique in a given integration time,  $T_{int}$ , defined as the period of time during which the samples  $x_i$  are accumulated. To do so, it is necessary to take into account whether or not the studied design needs to reset part of the pixel nodes between  $x_i$  measurements. Examples of designs that need this are [27] or [38]. On the other hand, pixels like the ones presented in [39] and [16] can perform all the samples  $x_i$  one after the other, without the need of a reset.

To calculate  $N_{acc}$  we first define T as the time between two successive light pulses in pulsed ToF techniques. We also define the duty cycle in the pulsed-ToF case as the ratio of the pulse width,  $T_p$ , to T. Fig. 2.8 shows the relation between  $T_p$ , T and  $T_{int}$ . If the reset is necessary, at least two cycles or pulses need to be used to obtain all the  $x_i$  measurements. This means that the time for the distance calculation is doubled or  $N_{acc}$  reduced to a half. The same problem appears in the MDSI techniques, since  $x_1$  and  $x_2$  are performed simultaneously (see Fig. 2.6 and Fig. 2.7). Table 2.4 summarizes the number of accumulations for every technique. As seen, increasing the integration time can to reduce the shot noise as it increases the number of signal accumulations for a given ToF technique and frequency of the emitted signal.

|                       | Number of accumulations, $N_{acc}$ |                      |  |

|-----------------------|------------------------------------|----------------------|--|

| Measurement Technique | No need of reset                   | Need of reset        |  |

| Modulated ToF         | $\frac{T_{int}}{T}$                | $\frac{T_{int}}{2T}$ |  |

| PSD                   | $\frac{T_{int}}{T}$                | $\frac{T_{int}}{2T}$ |  |

| MDSI                  | $\frac{T_{int}}{2T}$               | $\frac{T_{int}}{2T}$ |  |

Table 2.4: Number of accumulations for different ToF techniques.

# 2.4 Numerical Examples

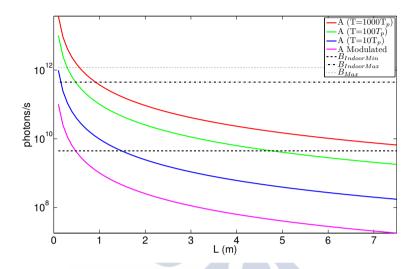

In this section numerical examples comparing the different indirect ToF modes of operation are presented. These examples are intended to be as general as possible, but some values must be set. In particular, the wavelength of the light signal is set to  $\lambda=850$  nm. Also, in all cases we used  $\tilde{T}=50$  ns and  $T_p=50$  ns in modulated and pulsed ToF, respectively, which means that the maximum distance measurable by the sensor is 7.5 m ((2.1) and (2.4)). The integration time was set to  $T_{int}=20$  ms, during which the accumulations of  $x_i$  are stored in the pixel. This leaves more than 10 ms for A/D conversion and read-out to comply with the time constraint of video rate: 33 frames per second. In addition to this, assuming an NWell over Psubstrate photodiode in standard 0.18  $\mu$ m CMOS technology, the quantum efficiency of the photosensor was calculated from the experimental data provided in [40]. The area of the photosensor is set to  $50 \times 50 \ \mu$ m<sup>2</sup>. These assumptions affect the final values, but not the comparison between the different ToF techniques.

Three different ambient light illuminations were studied: a poorly illuminated indoor scenario, with a background light power density of  $p_{BIndoorMin} = 6.25 \times 10^{-4} \text{ W/cm}^2$ , a well illuminated indoor scenario with  $p_{BIndoorMax} = 6.25 \times 10^{-2} \text{ W/cm}^2$  and outdoor illumination in midsummer with  $p_{BMax} = 0.167 \times \text{ W/cm}^2$ . This background comprises light of different

|           | Duty Cycle | Light Power (W) |

|-----------|------------|-----------------|

| Pulsed    | 0.1        | 33              |

| Pulsed    | 1          | 9               |

| Pulsed    | 10         | 0.87            |

| Modulated | _          | 0.09            |

**Table 2.5:** Maximum emitted power to comply with eye safety regulations for a distance of 25 cm or more

wavelengths but for the calculation of B using (2.29)  $\lambda = 630$  nm was used since around this wavelength the silicon has higher sensitivity. The obtained values are:  $B_{IndoorMin} = 4.46 \times 10^9$ ,  $B_{IndoorMax} = 4.46 \times 10^{11}$  and  $B_{Max} = 1.19 \times 10^{12}$  photons per second.

The maximum light power that can reach the eye without safety glasses depends on several factors [3] such as the width of the emitted pulse, its wavelength or the frequency of the signal. In general, for infrared radiation with the signal frequency that ToF sensors operate, the light power limit is defined by the average power that can reach an unprotected eye. This means that bursts of pulses with low duty cycle will allow to operate at higher instant light power without violating the maximum average light power set by eye safety regulations. Table 2.5 shows the maximum light power allowed for the different situations studied in this chapter. These values were calculated assuming that safety regulations are satisfied for every distance to the sensor greater than 25 cm and setting  $\rho = 0.5$ ,  $\theta_{||} = 9^{\circ}$ ,  $\theta_{\perp} = 25^{\circ}$ ,  $\tau_{opt} = 1$  and F# = 1.7. The values of these parameters were selected based on the experimental setup designed to test the sensor, that will be described in Chapter 5.

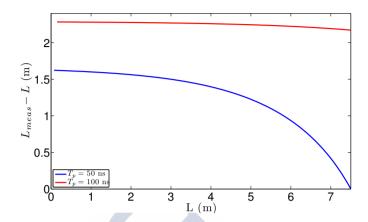

From this, and using (2.25), (2.26) and (2.28), the maximum value of A as a function of the distance between the sensor and the target can be calculated, as seen in Fig. 2.9. This figure shows that in modulated ToF techniques A is severely reduced for longer distances,

**Figure 2.9:** A value as a function of the distance between the target and the sensor. In the pulsed ToF case, values are shown for three different duty cycles.

which in turn results in higher shot noise. On the other hand, in pulsed ToF the value of *A* depends on the duty cycle selected. Lower duty cycles result in higher *A* due to the fact that by decreasing the duty cycle it is possible to increase the light power of the pulse without increasing the average light power. It should also be noted that in modulated ToF the number of photons reaching the sensor because of the background is bigger than those from the signal in all the cases except for the lowest background situations and, even in that case, only at distances smaller than 0.5 m. In pulsed ToF, the signal power exceeds every background one, only for small duty cycles and distances to the target smaller than 1 m.

### 2.4.1 Shot Noise Results

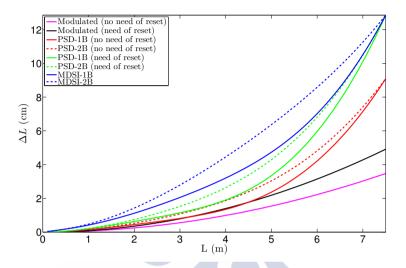

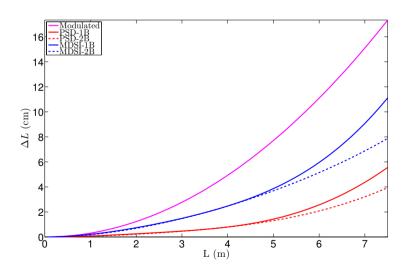

Having calculated realistic values for *A* and *B*, the distance error due to shot noise can be obtained. Fig. 2.10 and Fig. 2.11 show this error for all the different ToF techniques for

37

$B_{IndoorMin}$ . Duty cycles of 10% and 0.1% were used for the pulsed ToF techniques, respectively, whereas the period for the modulated ToF was set to  $\tilde{T} = 50$  ns. By comparing both figures, the fact that the shot noise in pulsed ToF is reduced with smaller duty cycles is apparent, despite the fact that the number of accumulations is reduced. The reason for this, as explained before, is that, by reducing the duty cycle, higher light power can be used in each pulse, without increasing the average light power and, thus, complying with eye safety regulations. It can also be seen that, because of the reduction of A for greater distances, the shot noise, and thus the accuracy, worsens with the distance. In addition, a comparison between ToF techniques can be performed. First of all, for the same ToF technique, those topologies that do not need to perform a reset operation between consecutive  $x_i$  integrations, always present less error due to shot noise than the ones that need it. The reason for this can be inferred from Table 2.4. The number of accumulations in both modulated and PSD ToF for a given integration time, when the reset between  $x_i$  is no needed, is twice the number of those used when the reset is required because, in this case, two light pulses per measurement are needed. The MDSI technique always needs two light pulses per measurement. Finally, for the same technique, 1B measurements present lower shot noise than 2B measurements.

There exist four ways of reducing shot noise related distance errors. The first one is to increase the light power of the pulse, however, this will make the sensor violate eye safety regulations for longer distances. The second option is to use larger photosensors, as increasing the photosensors area by a factor of four reduces the shot noise uncertainty by two, but larger photosensors have slower responses and the photosensor area used in these calculations was of  $50 \times 50 \, \mu\text{m}^2$ , which is already large. The third option is to increase the integration time of the sensor  $(T_{int})$ , which increases  $N_{acc}$  and hence reduces  $\Delta L$  by a factor  $1/\sqrt{N_{acc}}$ . Alternatively, for pulsed ToF, decreasing the duty cycle, and thus increasing A, reduces the distance uncertainty as  $\Delta L \propto \sqrt{A}/A$ . Finally, the last option is to minimize the background light reaching the pixel, which in practice is usually accomplished placing optical filters in front of the sensor that restrict the incident light to the wavelength of the light source.

**Figure 2.10:** Distance error due to shot noise for the different ToF techniques. In pulsed ToF, duty cycle was set to 10%.

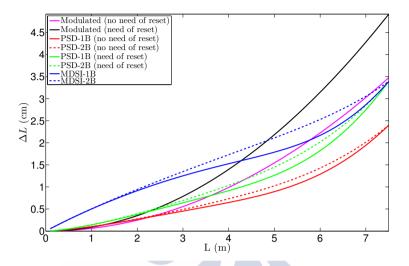

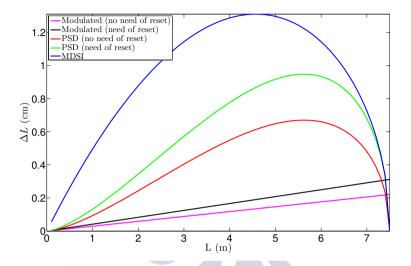

The same situation as in Fig. 2.11, but without background light (B=0) is shown in Fig. 2.12. This represents the minimum achievable error of the ToF sensor. In the ideal situation of no background light there is no difference between 1B and 2B measurement techniques. Also, as it can be seen, for most distances, with no background noise, the ToF technique that achieves better distance resolution is the modulated one.

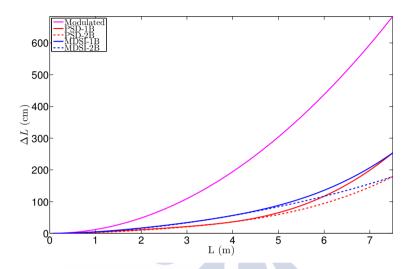

### 2.4.2 Thermal Noise Results

As explained in Section 2.2.2 there is a trade-off when selecting the storage capacitances value. If a small value is used, there is a risk of voltage saturation at the capacitors when high light power reaches the pixel. If large capacitances are used, the distance error because of the thermal noise will increase. Using the equations from Table 2.3 the minimum capacitances to avoid saturation can be calculated. Assuming that the maximum light power for the back-

39

**Figure 2.11:** Distance error due to shot noise for the different ToF techniques. In pulsed ToF, duty cycle was set to 0.1%.

ground is  $\bar{p}_{BIndoorMin}$  and that the minimum distance from which the light signal is reflected is 0.5 m these values were calculated as:

- For the modulated ToF:  $C_{mod} = 400 \text{ fF}$

- For the PSD ToF:  $C_{PSD} = 450 \text{ fF}$

– For the MDSI ToF:  $C_{MDSI} = 230 \text{ fF}$

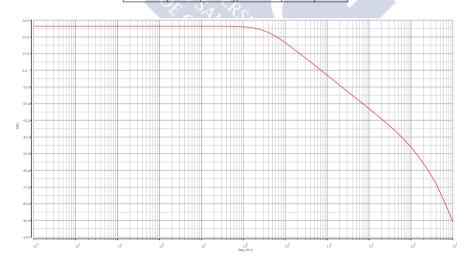

For the pulsed ToF techniques a duty cycle of 0.1% was selected. Fig. 2.13 shows the thermal noise related distance error for the all the studied techniques. Even with these light power values it can be seen that the thermal error generated is unacceptable for almost any application. As said before, one way to avoid this is to use an adaptive number of accumulations, where  $T_{int}$  and, thus,  $N_{acc}$  for each pixel is not fixed. Instead, a pixel continues to accumulate measurements until a certain voltage in the storage capacitors is reached. If

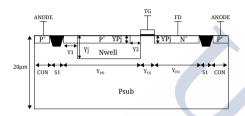

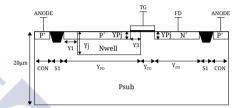

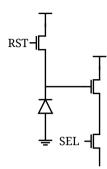

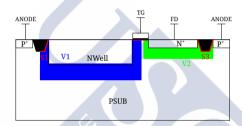

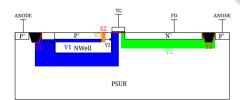

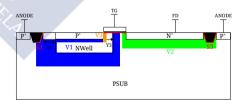

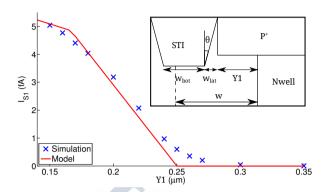

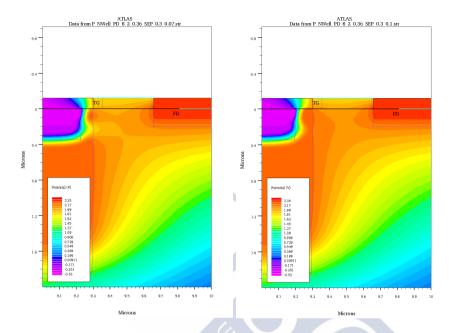

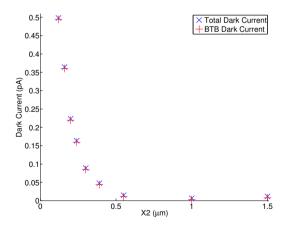

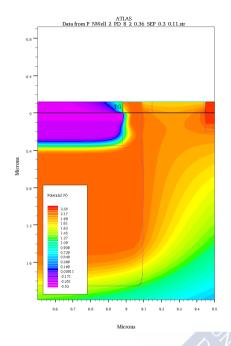

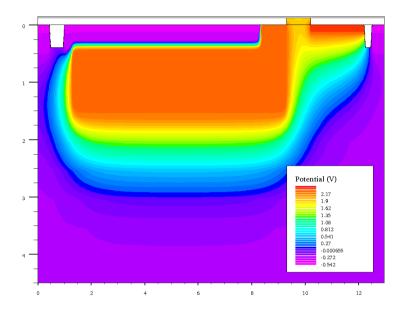

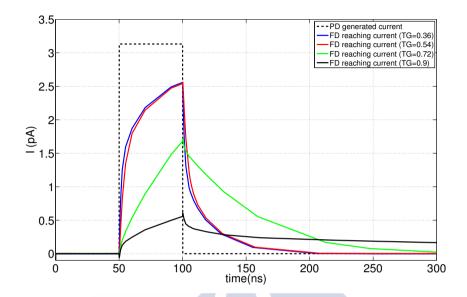

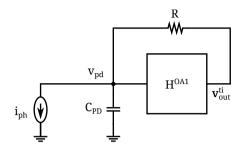

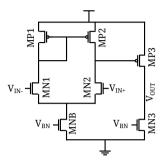

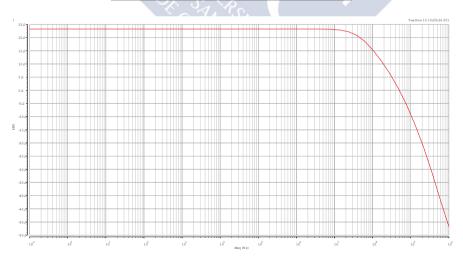

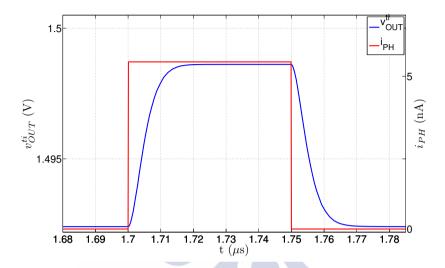

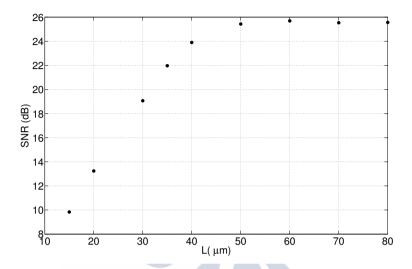

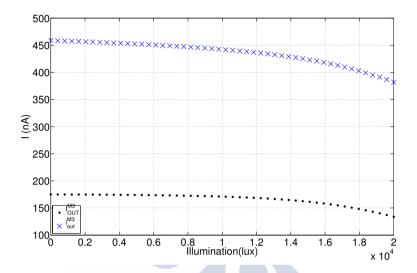

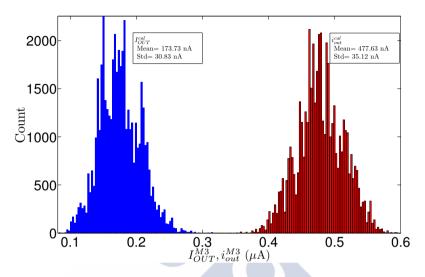

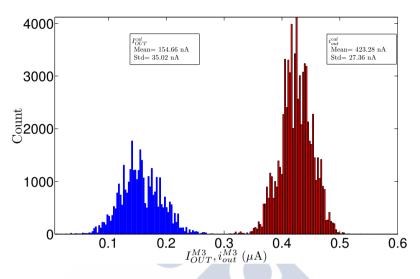

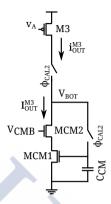

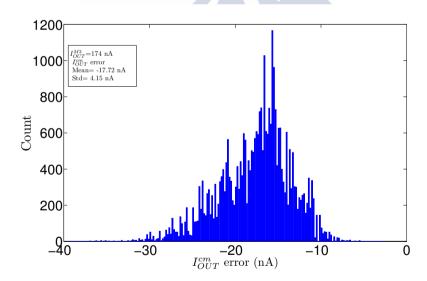

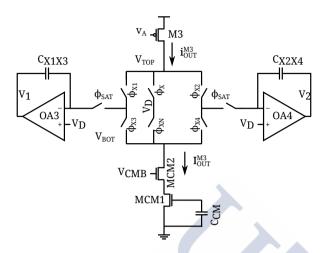

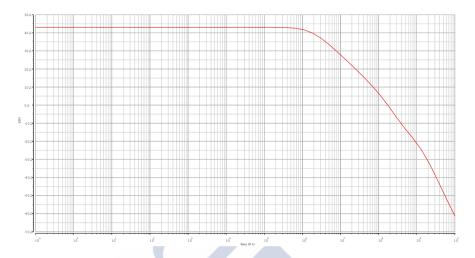

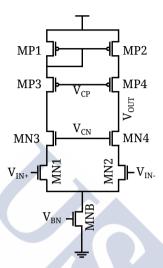

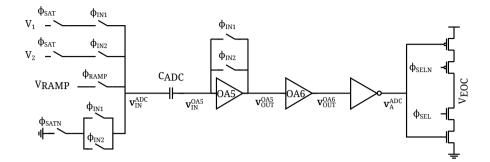

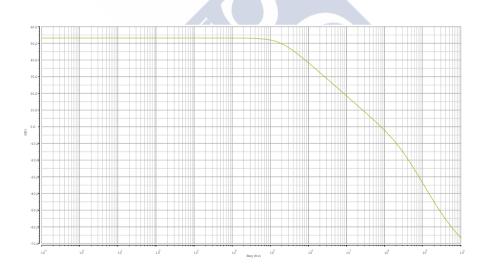

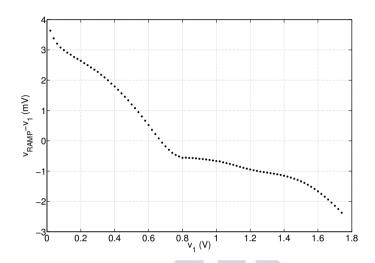

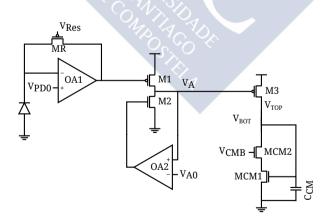

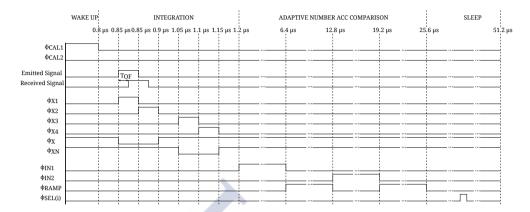

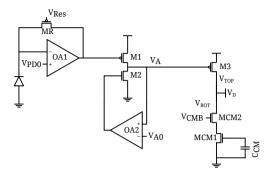

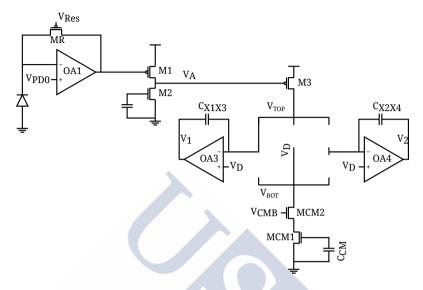

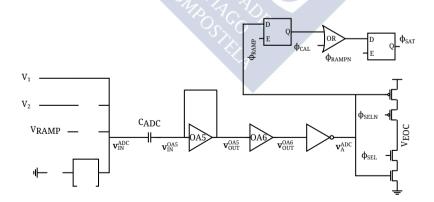

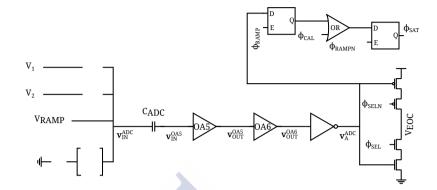

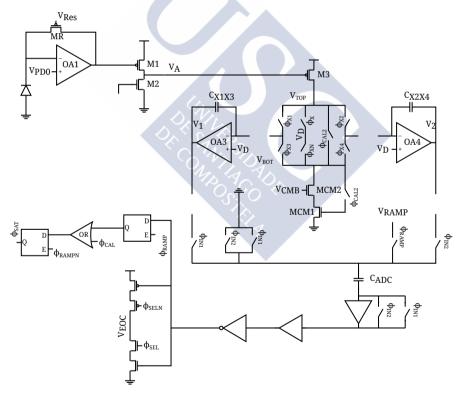

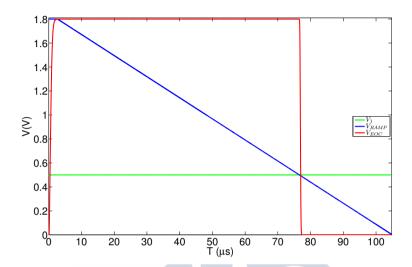

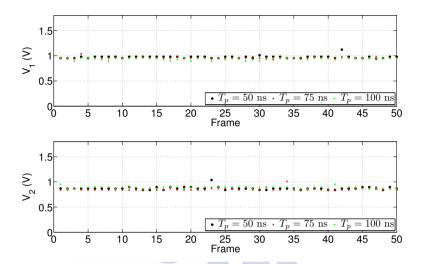

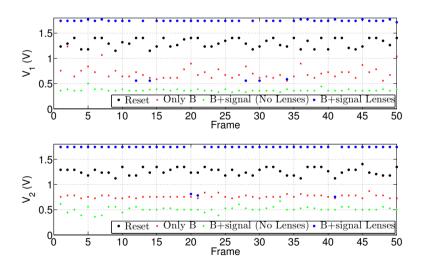

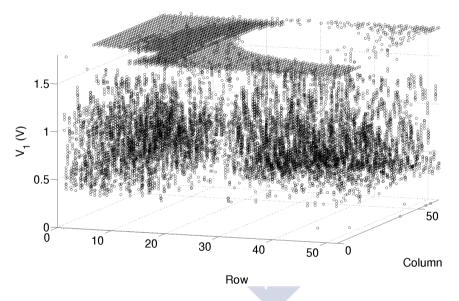

**Figure 2.12:** Distance error due to shot noise for the different ToF techniques with no background light. In pulsed ToF, duty cycle was set to 0.1%.