#### **Durham E-Theses**

## Application of bit-slice microprocessors to digital correlation in spread spectrum communication systems

Ismail, Nabil Abd-el-wahid

#### How to cite:

Ismail, Nabil Abd-el-wahid (1983) Application of bit-slice microprocessors to digital correlation in spread spectrum communication systems, Durham theses, Durham University. Available at Durham E-Theses Online: http://etheses.dur.ac.uk/698/

#### Use policy

The full-text may be used and/or reproduced, and given to third parties in any format or medium, without prior permission or charge, for personal research or study, educational, or not-for-profit purposes provided that:

- a full bibliographic reference is made to the original source

- a link is made to the metadata record in Durham E-Theses

- the full-text is not changed in any way

The full-text must not be sold in any format or medium without the formal permission of the copyright holders.

Please consult the full Durham E-Theses policy for further details.

# APPLICATIONS OF BIT-SLICE MICROPROCESSORS TO DIGITAL CORRELATION IN SPREAD SPECTRUM COMMUNICATION SYSTEMS

by

Nabil Abd-el-wahid Ismail, B.Sc., M.Sc.

A thesis submitted in accordance with the regulation for the degree of Doctor of Philosphy in the University of Durham Department of Applied Physics & Electronics

1982

The copyright of this thesis rests with the author.

No quotation from it should be published without his prior written consent and information derived from it should be acknowledged.

### Applications of Bit-Slice Microprocessors to Digital Correlation in Spread Spectrum Communication Systems

#### Nabil Abd-el-wahid Ismail

#### **ABSTRACT**

This thesis describes the application of commercially available microprocessors and other VLSI devices to high-speed real-time digital correlation in spread spectrum and related communication applications. Spread spectrum communications are a wide-band secure communication system that generate a very broad spectral bandwidth signal that is therefore hard to detect in noise. They are capable of rejecting intentional or unintentional jamming, and are insensitive to the multipath and fading that affects conventional high frequency systems. The bandwidth of spread spectrum systems must be large to obtain a significant performance improvement. This means that the sequence rate must be fast and therefore very fast microprocessors will be required when they are used to perform spread spectrum correlation. multiplication cannot be performed efficiently by microprocessors considerable work, since 1974, has been published in the literature which is devoted to minimising the requirement of multiplications in digital correlation and other signal These fast techniques are investigated processing algorithms. and implemented using general-purpose microprocessors. restricted-bandwidth problem in microprocessor-based digital correlator has been discussed. A new implementation is suggested which uses bit-slice devices to maintain the flexibility of microprocessor-based digital correlation without sacrificing speed. This microprocessor-based system has been found to be efficient in implementing the correlation process at the baseband in the digital domain as well as the post-correlation signal processing- demodulation, detection and tracking, especially for low rate signals. A charge coupled-device is used to obtain spectral density function. An all-digital technique which is programmable for any binary waveform and can be used for achieving initial acquisition and maintaining synchronisation in spread spectrum communications is described. Many of the practical implementation problems are discussed. The receiver performance, which is measured in terms of the acquisition time and the bit-error rate, is also presented and results are obtained which are close to those predicted in the system simulations.

#### **ACKNOWLEDGEMENTS**

I would like to express my gratitude for the consistent guidance and the constructive criticism of Dr C.T.Spracklen during the project. I am indebted to him for his supervision, encouragement, and helpful advice and for his help in securing equipment.

I would also like to thank Professor G.G.Roberts for allowing me to use the facilities of the Department of Applied Physics and Electronics, the University of Durham, and I am grateful to members of the workshop for their willingness to provide their skill and advice.

My thanks are also due to my colleagues in the Digital Electronics Group for many useful discussions and times spent together. The help of the staff of the Computer Unit of the University of Durham as well as the staff of the Science Library is also gratefully acknowledged.

My appreciation is also extended to the Egyptian Mission

Department and the University of Menoufia for an award of a research studentship and for providing financial support over more than three years.

Finally, I am particularly indebted to my wife Afrah for her understanding, patience and support and to my parents, brothers and sisters for moral and financial support and to my daughter Marwa for her unceasing distraction which formed a source of much relaxation.

To Afrah, Marwa and Aeimn

#### CONTENTS

#### **ABSTRACT**

#### **ACKNOWLEDGEMENTS**

#### Glossary of Terms

| Introduction |

|--------------|

|              |

|              |

- 1.1 History

- 1.2 Spread spectrum techniques

- 1.3 Problems of spread spectrum systems

- 1.4 Synchronisation problems

- 1.5 Practical implementation problems

- 1.6 Bit-slice microprocessors and spread spectrum systems

- 1.7 Conclusion

#### CHAPTER 2 Digital Correlation Techniques Using Microprocessors

- 2.1 Introduction

- Digital correlation 2.2

- 2.3 Transform analysis

- 2.3.1 Correlation using rectangular transforms

- 2.4 Implementations

- 2.4.1 Implementation using an Intel-8080 microprocessor system

- 2.4.2 Correlation on TMS9900 microcomputer

- 2.5 Binary correlation

- Real-time power spectrum density

- 2.6.1 Chirp-Z transform algorithm

- 2.6.2 Hardware implementation

- 2.7 Conclusion

#### CHAPTER 3 Bit-Slice Microprocessor System

- 3.1 Introduction

- 3.2 System organisation

- 2901 ALU/Register slices 3.3

- 3.3.1 Architecture3.3.2 2901-slices interconnection

- 3.4 Microprogram control

- 3.4.1 Microprogram memory3.4.2 Microprogram counter

- Condition code select logic

- 3.6 I/O external registers handling 3.6.1 The 'To' decoder

- 3.6.2 The 'From' decoder

- 3.6.3 The control decoder

- 3.7 Input/Output buffer memory

- 3.8 System clock

- 3.9 Conclusion

#### System Microprogramming Features CHAPTER 4

- 4.1 Microprogramming

- Microinstruction format

- 4.3 Microinstruction implementation

- 4.4 Microinstruction sequencing

- 4.4.1 Sequential execution

- 4.4.2 Skip control

- 4.4.3 Multiple sequences

- 4.4.4 Start address

- 4.5 Special microassembler

- 4.6 Software simulator

- 4.7 PROM programming

- 4.8 Development test equipments

- 4.9 Test software

- 4.9.1 Control decoder test

- 4.9.2 "To" and "From" decoder test

- 4.9.3 2901-slices internal registers test

- 4.9.4 Up shift test

- 4.9.5 Down shift test

- 4.9.6 2901 ALUs arithmetic operation test

- 4.9.7 Carry control test

- 4.9.8 FIFO control tests

- 4.9.9 FIFO data tests

- 4.9.10 Output enable test

- 4.10 Conclusion

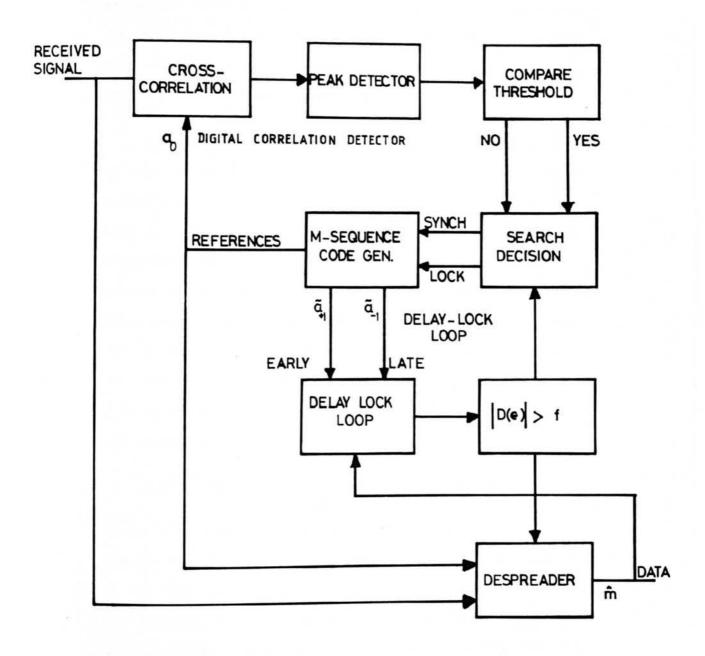

#### CHAPTER 5 Implementation of Direct Sequences by Microprocessors

- 5.1 Introduction

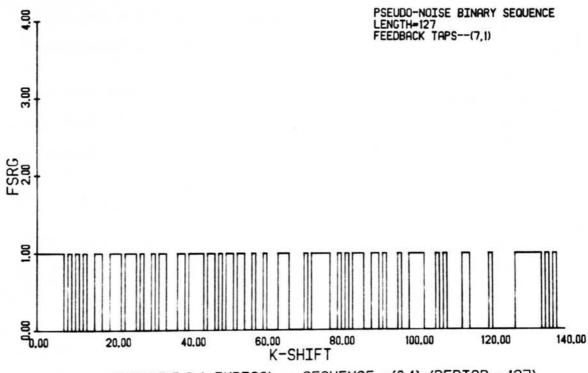

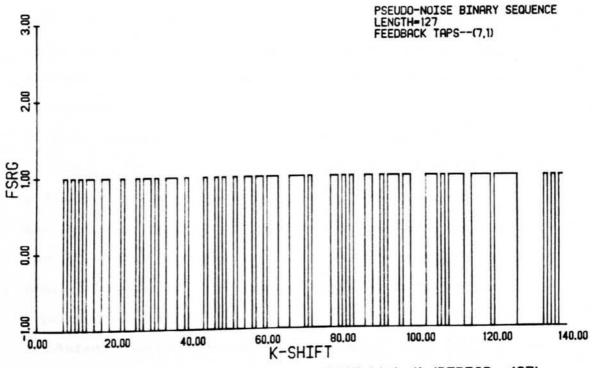

- 5.2 Pseudo-noise sequences

- 5.2.1 Generation and properties

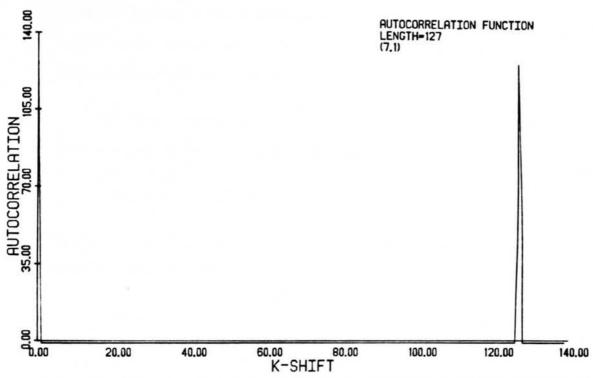

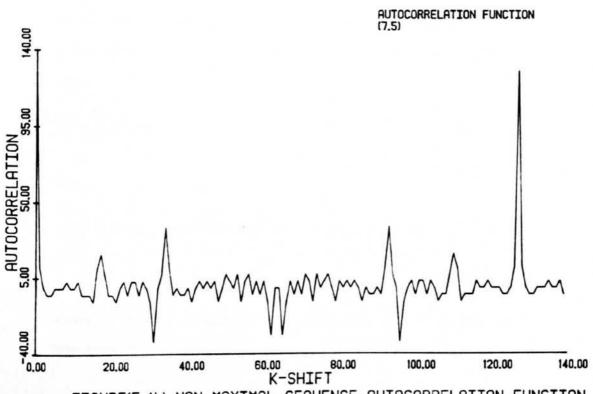

- 5.2.2 Correlation functions and power spectra of codes

- 5.3 Implementing the feedback shift register on a microprocessor

- 5.4 Sequence inversion keying (SIK) modulation

- Synchronisation

- 5.5.1 Initial acquisition techniques

- 5.5.2 Correlation process

- 5.6 Tracking

- 5.6.1 Delay-lock loop correlator5.6.2 Implementation

- 5.7 Conclusion

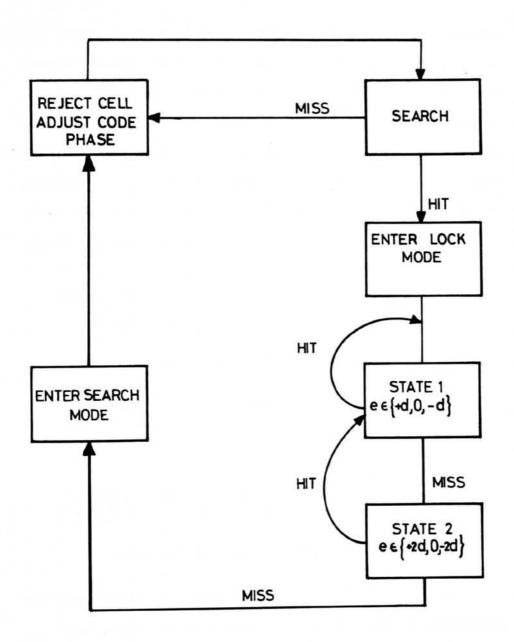

#### CHAPTER 6 Transmitter and Receiver Design

- 6.1 Introduction

- 6.2 Transmitter

- 6.2.1 Data acquisition

- 6.2.2 FIFO on transmit

- 6.3 Spreading

- 6.4 Transmitter software

- 6.5 Receiver

- 6.5.1 FIFO on receive

- 6.5.2 Search/lock strategy

- 6.5.3 Receiver software

- 6.6 Clock frequency effects

6.7 Data recovery

6.8 Conclusion

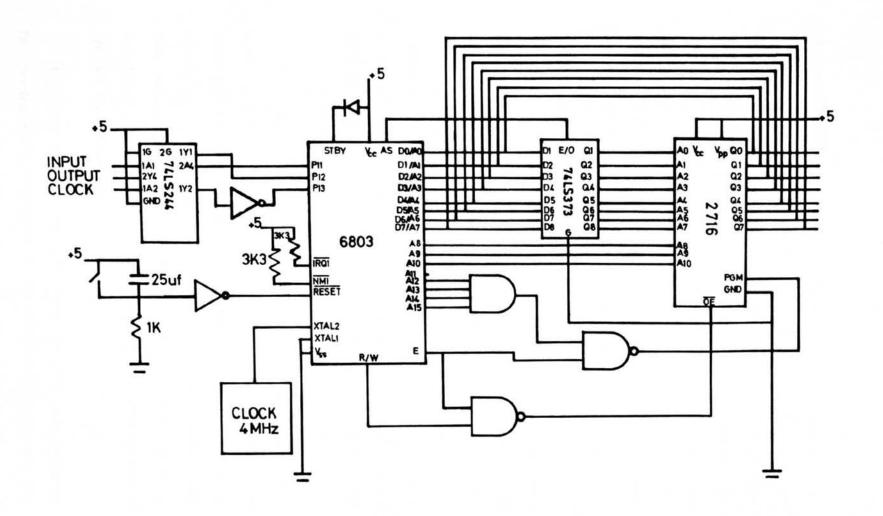

#### CHAPTER 7 System Performance & Experimental Results

- 7.1 Introduction

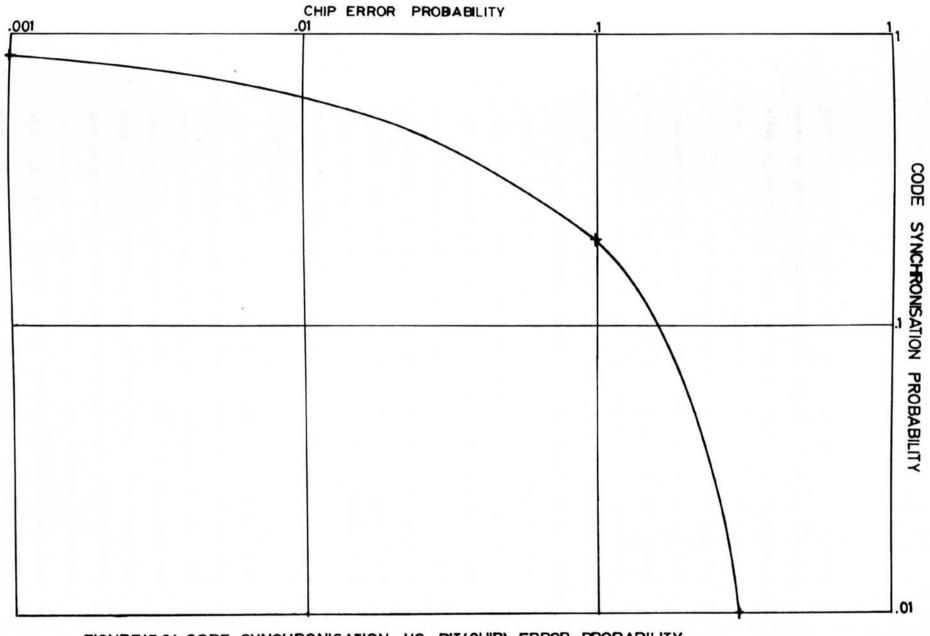

- System performance

- 7.2.1 Acquisition time measurements7.2.2 Bit error-rate measurements

- 7.3 Noise channel simulation

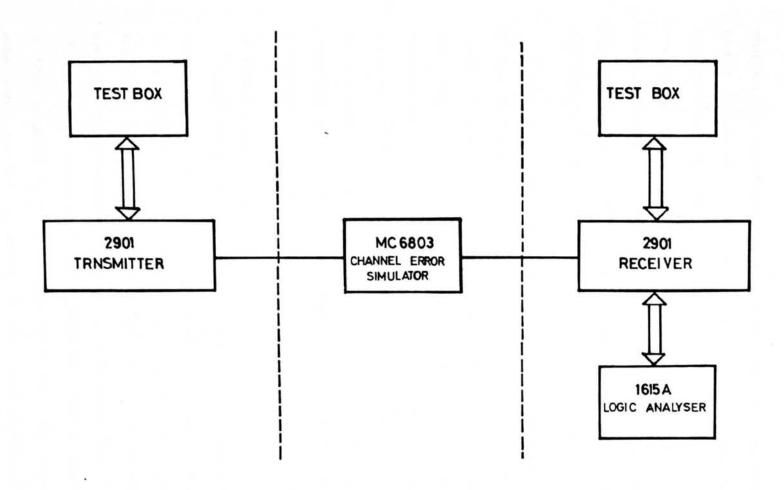

- 7.3.1 The microprocessor7.3.2 Hardware description7.3.3 Implementation

- 7.4 Experimental results7.5 Conclusion

CHAPTER 8

Conclusion

APPENDIX A

References

APPENDIX B

Program Listings

#### Glossary of Terms

ADC Analogue to Digital Converter

A/D Analogue to Digital

AJ Antijamming

ALU Arithmetic Logic Unit

BER Bit Error Rate

BPSK Biphase Phase Shift Keying

CCD Charge Coupled Device

CCP Cyclic Convolution Property

CPE Central Processing Element

CPU Central Processing Unit

CRT Chineese Remainder Theorem

CZT Chirp-Z Transform

DAC Digital to Analogue Converter

D/A Digital to Analogue

DFT Discrete Fourier Transform

DLL Delay-Lock Loop

DMA Direct Memory Access

FFT Fast Fourier Transform

FIFO First Input First Output

FIS Fixed Instruction Set

Gp Process Gain of Spread Spectrum System

IC Integrated Circuit

I/O Input/Output

LSB Least Significant Bit

LSI Large Scale Integration

m-sequence Maximal Length Pseudonoise Sequence

MSI Medium Scale Integration

NTT Number Theoretic Transform

P<sub>D</sub> Probability of Detection

P<sub>E</sub> Probability of Error

PIA Peripheral Interface Adapter

PN Pseudo-Noise Sequence

PROM Programmable Read Only Memory

PSK Phase Shift Keying

QPSK Quadriphase Phase Shift Keying

RAM Random Access Memory

ROM Read Only Memory

SIK Sequence Inversion Keying

SAW Surface Acoustic Wave

TDMA Time-Division Multiple Access

VCO Voltage Controlled Oscillator

VLSI Very Large Scale Integration

WFTA Winograd Fourier Transform Algorithm

#### CHAPTER 1

#### Introduction

#### 1.1 History

The spread spectrum technique has evolved from a desire by communication system users to protect their messages against detection by unauthorised users and provide reasonable immunity to interference for the desired user. Spread spectrum is a means of transmission in which the basic signal characteristics are:

- (i) The carrier is a pseudonoise, wide-band signal.

- (ii) The bandwidth of the carrier is much wider than the minimum bandwidth required to transmit the information being sent. As a minimum, a voice signal can be sent with amplitude modulation (AM) in a bandwidth only twice that of the information itself. A spread spectrum system, on the other hand, has a modulated signal bandwidth that is at least 10 to 100 times that of the information bandwidth.

- (iii) Reception is achieved by crosscorrelation of the received wide-band signal with a synchronously generated replica of the wide-band carrier. This is used for despreading and subsequent data recovery. Furthermore, in a spread spectrum system, the information data rate does not dictate the bandwidth of the modulated signal.

The concept of spread spectrum technology has been known since Shannon's theorem (1) came to the light in 1940's. Costas work in 1959 (2) indicates that the idea of employing coded wide-band signals for communicating in the presence of noise

1 Z MAY 1983

could be implemented in some systems. Golomb's work (3) in the area of codes used in communication and pseudonoise generation which was started in 1956 has offered a further recognition to The first high performance electronic correlator by the field. Lee which was decribed with other correlation techniques by Lange (4) in the early 1960's, was the important step towards the ability to mechanise the correlation operation precisely, which is essential in building high-performance spread spectrum At that time, the initial application have been to systems. military antijamming (AJ) communications, to guidance systems and other related applications which were employed with conventional vacuum tube technology. The prime advances in spread spectrum performance have come about primarily as a result of the availability of solid state components. The advent of high speed, high gain transistors in the 1960's gained the subject a new area of applications such as the navigation (ranging and direction finding) area and space exploration programs. investigations and systems were carried out, mainly in the United States, during the 1960's and early 1970's (5)-(8), but were largely abandoned in favour of satellite and satellite-aircraft communications.

The recent advances in digital integrated circuits (IC) technology and VLSI (very large scale integration)/LSI (large scale integration) packages have enabled substantial reductions to be made in both the size and the cost of communication systems. At the same time, new analogue device developments, such as surface acoustic wave (SAW) and charge coupled devices (CCD),

have been introduced. It seems only logical that spread spectrum systems also benifit from such developments (9). On the other hand, much work (10), (11) has been performed in the area of developing special "acquirable" codes which have the required length for the system under question, but which also have synchronisation properties (excellent autocorrelation and crosscorrelation properties) that permit acquisition to be searched out without traversing the entire code length.

Although the current application for spread spectrum continue to be primarily for military communications, there is an increasing interest in the use of this techniques such as for mobile radio networks and some specialised applications in satellites. Most recently they have been successfully applied to multiple access situations involving many users simultaneously (12).

At present there is a limited amount of information (unclassified) in the published literature which outlines the applications of the spread spectrum concept to a communication system from an overall system viewpoint. The general details on practical performance are few with isolated theoretical investigations of some of the problems.

In this thesis we confine ourselves to principles related to the applications of VLSI technology to the design and analysis of those parts of a spread spectrum communications system concerned with synchronisation acquisition and tracking. For this complete transmitter and receiver systems were developed using the latest state-of-the-art technology, the bipolar bit-slice

microprocessors. It is shown that those parts of the receiver which previously required large amounts of expensive analogue or discrete equipment can be realised at lower cost and with increased flexibility using all digital techniques.

#### 1.2 Spread Spectrum Techniques

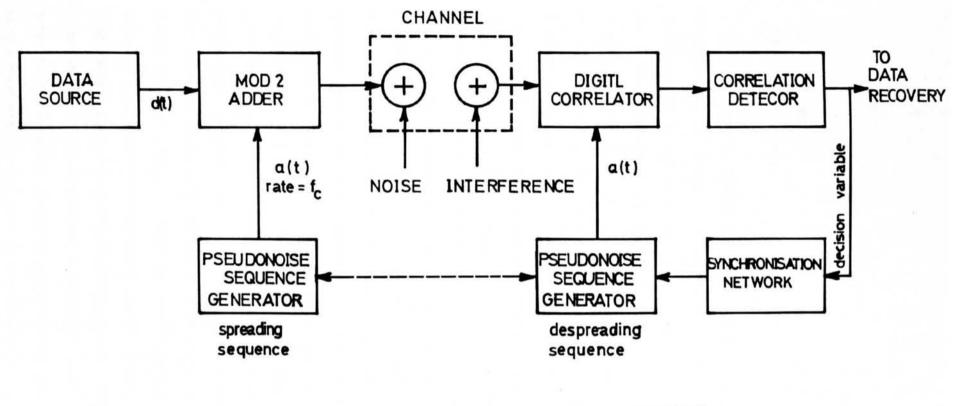

To illustrate the principle of a spread spectrum system the block diagram of a transmitter and receiver is shown in Figure (1.1). When viewed as a system composed of many sub-systems the individual units of a spread spectrum system are in many ways identical with sub-systems in conventional communication systems. From a theoretical viewpoint there is no reason why analogue waveforms should not be considered for bandwidth expansion in spread spectrum systems. There are, however, constraints on the desired correlation properties of spreading waveforms. In an ideal spread spectrum system, waveforms with good autocorrelation properties and orthogonality between the various waveforms are desired. It is generally accepted that in practical systems the best that can be achieved is waveforms which exhibit a two level autocorrelation function and low values of crosscorrelation.

The study of binary sequences is comprehensive in the literature (3), (10), (11). It is mainly due to this, and the ease of generation of maximal length pseudonoise sequences (m-sequence) using shift registers, that digital spreading waveforms are widely used. There are many techniques to achieve spectrum spreading (6), these are;

- (1) direct sequence modulated its

- (2) frequency hopping

TRANSMITTER

RECEIVER

FIGURE (1.1) DIRECT SEQUENCE SPREAD SPECTRUM SYSTEM FOR TRANSMITTING A BINARY DATA (BASEBAND).

- (3) time hopping

- (4) pulse-FM or chirp

In a direct sequence system (which is also called PN-sequence), as shown in Figure (1.1), the data information is combined with a high clock rate m-sequence before modulation on the carrier, resulting in direct bandwidth expansion. Frequency hopping (FH) has evolved from the idea that a good way to prevent an unintended receiver from receiving a message, or to prevent interference, is to move the carrier frequency of the information signal in a pseudorandom manner. Instead of directly modulating the carrier, the code sequence is used to switch the carrier frequency in a pseudorandom manner. The synchronisation acquisition in a frequency hopping scheme is faster due to a larger duration of the hopping chip. However, this is a disadvantage when the overall system requires any form of accurate time of arrival measurements. The hardware required to implement such schemes is always far more complicated and expensive to implement. Like frequency hopping, time hopping systems control their transmission time and period from a pseudonoise sequence. Time hopping is generally not used alone but is always employed in conjunction with frequency hopping and direct sequence methods to eliminate time dependent interference or allow time-division multiple-access (TDMA) system. other spread spectrum systems, pulse-FM or chirp does not employ m-sequences. The operation is based on pulse compression achieved by frequency sweep at the transmitter and compression using a dispersive matched filter at the receiver.

Hybrid spread spectrum systems are possible by combining these basic techniques.

There are many advantages for spreading a signal's bandwidth and then collapsing it through correlation with a stored reference signal contained in the receiver:

- (a) selective addressing

- (b) low power density signals

- (c) inherent message privacy

- (d) code division multiple user access

- (e) high resolution ranging

- (f) interference rejection

- (g) possible operation with adverse transmission distortion

- (h) accurate universal timing

Selective addressing is possible through the assignment of a particular m-sequence (code) to a receiver. The low power density of spread spectrum signals results from the wideband for transmission and causes low interference to other users. The coded format of spread spectrum systems offers privacy in communication from the casual listener. The use of different codes allows multiple users in a spread spectrum communication system. The good correlation properties of m-sequences in conjunction with the wide bandwidth used for transmission allow accurate ranging of transmitter or receiver. The interference rejection occurs as a result of the despreading necessary for the operation of a spread spectrum receiver. In a particular system, the ratio of spread or transmitted bandwidth to the rate of the information sent is called the "process gain"  $(G_{\bf p})$  (7) of that

system. This factor is the measure of the interference rejection in that system. The large bandwidth of spread spectrum systems suggests that a form of frequency diversity is available in the system which may combat distortions due to the transmission medium. It should be noted that these advantages are not always available and rely on reasonable synchronisation of the receiver with respect to the transmitter.

#### 1.3 Problems of Spread Spectrum Systems

Most of the problems discussed in this section are not unique to spread spectrum systems. Some of them are associated with communication via the propagation medium. The object is to provide an appreciation of the general problems relevant to the subsequent practical limitations in spread spectrum receiver system. The main problems are:

- (1) Interference and noise

- (2) Distortion due to the transmission medium

- (3) Synchronisation problems

- (4) Practical implementation problems

These problems are of equal concern in that; either they corrupt the received data or they affect the system performance. Interference and noise in spread spectrum systems are a result of:

- (1) Interference due to other spread spectrum users; this is increases as more users utilise the same RF band. It is required to devise orthogonal spreading functions for the numerous users using the same frequency band.

- (2) Interference due to the geometry of links; in certain

instants an interfering transmitter may be closer to a receiver than the desired transmitter. In this situation the wanted signal will be received in a high level of interference. This is known as the "near-far" problem.

- (3) Interference from conventional radio systems; to a considerable extent a spread spectrum system has the ability to reject interference from narrowband systems. This is possible within the jamming margin of the spread spectrum. The jamming margin is the power level above the spread spectrum signal that a narrowband interferer can be discriminated against, for a desired output signal to noise ratio, including implementation losses (7).

- (4) Man-made impulsive noise; this is produced from machinary, fluorescent lights, power switching appliances etc.

- (5) Atmospheric and receiver noise; this may need consideration as in a conventional receiver system, depending on the frequency band of interest.

Distortions due to the transmission medium, on the other hand, are dependent on the propagation mechanisms of radio waves in a known environment.

#### 1.4 Synchronisation Problems

The problem of synchronisation is of major concern in the design and implementation of spread spectrum systems. This is because the interference rejection capabilities rely on adequate synchronisation of the spreading and despreading waveforms. By synchronisation we mean that, the signal seen by the receiver must be precisely correlated in time with a locally generated

reference signal.

The main sources of uncertainty, with respect to synchronisation, in spread spectrum systems are those that are time or frequency dependent. Time uncertainty includes any propagation time delay due to unknown range. Frequency uncertainty is due to the instability of the frequency sources used in both transmitter and receiver. Code, phase, and carrier frequency are the frequency uncertainty. Doppler-related frequency errors often cannot be predicted and may be affect both code rate and carrier frequency. Another consequence of frequency uncertainty may also exist, any clock rate offset is accumulated in code phase offset. These factors lead to a degradation of the synchronisation performance because; (i) not all main correlation peaks are detected, i.e., the detection probability Pp, and (ii) false set impulses occur, as false alarms are generated at instants at which correlation subpeaks are above a certain threshold away from the main peaks.

The time required for achieving synchronisation between transmitting and receiving units has become the major factor limiting usage of spread spectrum systems. Reduction of synchronisation time is limited by the maximum search rate a receiving unit is capable of achieving and the length of the m-sequence to be used. Maximum search rate, is limited by the recognition time of the receiver's correlation detection circuits. The receiver must be able to recognise correlation and stop the search process before the point of code synchronisation is passed. This requires that the bandwidth of the correlation

detectors must be commensurate with the autcorrelation requirements of the m-sequence used.

The synchronisation process is generally separated into two phases, initial synchronisation and tracking. The initial synchronisation phase determines the timing of an incoming signal and brings the receiver into initial alignment, the tracking phase holds it in alignment. Initial synchronisation is frequently achieved by means of a single synchronisation preamble at the beginning of each transmission. The structure of the preamble is known to all users, and is usually fixed. alternative is to intersperse synchronising signals within the structure of the transmission, so that receipt of the beginning of the transmission is not necessary to achieve synchronisation and receivers which lose synchronisation during the transmission For security reasons and ease of implementation can reacquire. the transmitting signal itself can be used to achieve initial acquisition. Tracking is generally accomplished by a feedback loop which adjusts the receiver's time base to track the incoming signal.

Most of these synchronisation methods, especially for low data rate systems, have been performed using digital techniques (5). The advent of analogue SAW devices and CCD technology has led to synchronisation schemes with fast acquisition characteristics. These are mainly used for very high data rate systems (13)-(15).

#### 1.5 Practical Implementation Problems

The code sequences that are used for spectrum spreading must fulfill two criteria; (i) denying any information about future sequence k-tuples to the unintended user, and (ii) permitting practical implementation, including convenient code changes. Sometimes it is desirable for the sequence autocorrelation behaviour to have a high peak-to-sidelobe ratio, for acquisition synchronisation purposes. It is also desirable that the code sequence has a proper k-tuple statistics. Practical and effecient implementation techniques for PN sequences centre around use of shift-registers (3). High speed shift register implementation has been improved over the years from the use, in 1959, of large lumped-constant delay networks to present use of integrated circuits. A special LSI/MSI packages capable of operation at bit rates in excess of more than 300 Mbps has been developed especially for code sequence generation in spread spectrum systems. Increasing the code rate requires a significant improvement in the speed of integrated circuit technology. On the other hand, high speed logic circuits tend toward noise sensitivity and are more susceptible to error. reason, in addition to the problems of spectrum occupancy, system synchronisation, and propagation constraints tend to limit the code rates used for spectrum spreading, and hence to improve system process gain.

In principle, it is possible for spread spectrum receivers to use matched filter or correlator structures to synchronise to the incoming signal. Sliding correlator (7) and sequential

estimation (16) methods have been used for acquisition which employ techniques to bring the transmitter and receiver code sequences into a range in which digital correlator or matched filter may be used. A time-complexity tradeoff exists. using a bank of correlator or matched filters provides a means for rapid acquisition, a considerable reduction in complexity, size, and receiver cost can be achieved by using a single correlator or a single matched filter. However, these reductions are paid for by the increased acquisition time needed when performing a serial rather than a parallel operation. obvious practical implementation problem is therefore the determination of the tradeoff between the number of parallel correlators (or matched filters) used and the cost and time to acquire. It is important to note that this tradeoff may become a major point, recently, as a result of the rapidly advancing VLSI technology.

Practical system considerations such as those encountered when operating at, HF, VHF, or UHF, and technology considerations, such as the role of surface acoustic wave devices and charge-coupled devices in the design of spread spectrum systems are not included in this work.

#### 1.6 Bit-Slice Microprocessors and Spread Spectrum Systems

Microprocessors are one of the most significant products of VLSI technology previously mentioned. It is a monolithic device which can be obtained at low cost and which may be made to perform a wide range of instructions. The microprocessor system is configured such that it may perform most of the digital signal

processing tasks by appropriate choice of a sequence of instructions, 'software', stored in a read-only memory (ROM) space. Under the user control, the microprocessor may access the stored instructions and executes them sequentially. A microprocessor system may be made adaptive by determining that the order of execution of the instruction sequence is dependent on previous and/or present events. Because these devices are fabricated using MOS technologies, the instruction execution time is relatively long. In addition, their word length is limited and instructions are fixed. The inflexibility might prevent their use in applications where high speed or special instructions are essential.

A bit-slice microprocessor is a bipolar device which is designed to achieve high performance, flexible instruction format, and much longer word lengths. It is configured such that its control should be microprogrammed. A set of programmable read-only memory (PROM) or ROM are used to store the program instructions or 'microinstructions' which supervises the central processing unit (CPU) and the other auxiliary logic circuits. The CPU is where data is processed and it consists of one or more bit-slice microprocessors connected in cascade. A program counter may be used to access the stored microinstructions which are executed sequentially or in adaptive order. Usually the microinstruction is a dedicated user design.

This thesis describes the applications of bit-slice microprocessors to synchronisation and other aspects of digital spread spectrum communication systems.

The next chapter describes the different digital correlation techniques to be implemented with the aid of a microprocessor, and the implementation of other discrete-time signal processing techniques which are used in subsequent chapters in this thesis.

Chapter 3 describes the hardware configuration of the bit-slice microprocessor system, based on the 2901 bit-slice devices, that has been used in the subsequent chapters.

Chapter 4 continues the description of the microinstruction design of the system and introduces timing considerations. It describes the microprogram support tools; special assembler, software simulator, and other development and test equipments.

Chapter 5 discusses the analysis and implementation, in both software and hardware, of the functions which are concerned with direct sequence spread spectrum systems.

Chapter 6 describes how the 2901 microprocessor can be applied to perform the signal processing for the spreading, synchronising, and despreading of the transmitter and the receiver.

The ideas and results obtained from previous chapters in this thesis were combined in chapter 7 to discuss the performance of the receiving system in the presence of a channel noise simulator process. Formulas for estimating the synchronisation time have been given and results obtained using the equipment which was previously described are discussed.

#### 1.7 Conclusion

Although the current applications for spread spectrum techniques continue to be primarily for military communications, there is a growing interest, during the last decade, in the use of these techniques for other commercial applications such as mobile radio networks, code division multiple access, and timing and positioning systems.

The problems associated with implementing this technique in data communications systems are considerable because of the cost, complexity, and the constraints on the information. Most of these problems are related to the technology to be used and the applications under question. One of the main tasks, which can be all digital, to be accomplished at the receiving end of a spread spectrum system is the synchronisation of the pseudonoise signal generated locally at the receiver with the pseudonoise signal contained in the received signal. This synchronisation process must be achieved in minimum time which requires high speed digital circuitry.

With the advent of microprocessors a relatively cheap and powerful digital signal processor has now become available. These microprocessors are well suited to communication systems which require adaptability since they are cheaper than analogue processing methods and take up less space.

This thesis describes the applications of these devices to synchronisation process and other digital signal processing requirements which are related to the present communication systems. It shows that considerable savings in cost and hardware requirements may be made by using a primarily software-based approach to system design.

#### CHAPTER 2

#### Digital Correlation Techniques Using Microprocessors

#### 2.1 Introduction

Correlation techniques have been widely used in signal processing systems such as spread spectrum communications, radar, In all these systems correlation must be performed and others. in real-time, requiring the use of electronic circuits that are compatible with the system in question. Electronic systems that perform correlation have been around for years, but they have been bulky and inefficient. The development of VLSI and microprocessors have changed this; now correlation can be performed efficiently with a minimum number of components (17). A digital correlation circuit should be able to achieve the three functions of correlation: time delay, multiplications, and summation, respectively. In binary correlation, on the other hand, the shift register, the exclusive NOR gates, and the summer fulfill the three functions.

A microprocessor has been found to be efficient in implementing digital correlation signal processing, especially for low rate signals. Recent work of Cooley, Tukey (18), (19), Winograd (20), (21), Agarwal, and Burrus (22), (23) has been devoted to minimising the requirement of multiplications in convolution and correlation algorithms to be implemented using microprocessors, because multiplication cannot be performed efficiently by microprocessors.

Many of the correlation signal processing requirements of spread spectrum communications systems may be realised using high speed digital techniques. Spread spectrum bandwidth must be large to obtain significant performance improvement. This means that the sequence rate must be fast and very fast microprocessors will be required when they are used to perform spread spectrum correlations. This is one of the reasons that the bit-slice technology is very attractive in this application.

This chapter introduces the different digital correlation techniques to be implemented with the aid of microprocessors. Digital correlation plays an important role in the analysis, the design, and the implementation of digital signal processing systems concerned with spread spectrum systems and is used in several of the parts described in following chapters. Software implementation of efficient algorithms for the computation of digital correlation is investigated. The possibility of applying the other alternative, binary correlation, using the bit-slice technology is also presented. The theory and hardware construction of a real-time spectral analyser based on the most recent charge coupled devices (CCD) technology is also included.

#### 2.2 Digital Correlation

It is well known that when a received spread spectrum signal r(t) is the transmitted signal s(t) corrupted by additive white Gaussian noise, n(t), the optimal receiver is a correlator receiver which computes correlation according to the equation

$$c(\tau) = 1/T \int_{0}^{T} r(t)s(t + \tau) dt$$

(2.1)

where  $c(\tau)$  represents the crosscorrelation between the received signal and a replica of the transmitted signal. In many spread spectrum communications systems, the signal s(t) is a pseudonoise (PN) sequence.

In general, correlation between two functions is a measure of their similarity, i.e., it is a comparison process. Equation (2.1) is determined by multiplying the received signal r(t), by the transmitted signal shifted in time,  $s(t+\tau)$ , and then taking the integral of the product. Thus correlation involves time shifting, multiplication, and integration. The correlation of a function s(t) with a time-delayed replica of itself is called autocorrelation.

Digital signal processing requires functions to be represented in discrete form, where the time scale and amplitude are quantised into discrete steps. The PN spread spectrum receiver, when implemented digitally, performs the correlation function as follows:

$$c(nT) = 1/N \sum_{i=0}^{N-1} r(iT)s((i+n)T)$$

$n=0,1,....N-1$  (2.2)

where the original time functions are approximated by sequences of length N. The N selected will depend on the durations of the two functions and of their sampled portions, and on their periodicities (if any). One guide often used in determining the sampling rate  ${}^{\dagger}T_0{}^{\dagger}$  is the sampling theorem which states that an input signal with a highest frequency component of  ${}^{\dagger}f^{\dagger}$  can be

recovered without distortion using a sampling frequency 2f (24).

A sampling rate (which is also known as Nyquist sampling rate) of 2f or greater will therefore minimise the likelihood that analogue information is being lost in the quantising process.

A microprocessor may be perform correlation, operating according to the discrete summation equation (2.2). samples of an input voltage waveforms can be collected using an analogue-to-digital (A/D) converter. These data samples can either be put through some interface (input/output (I/O) ports or perhaps a peripheral interface adapter (PIA)) and sent to the microprocessor, or they can be stored in read access memory RAM directly by using each successive "conversion done" output of the analogue to digital converter (ADC) to initiate a direct memory access (DMA) cycle. After all the desired samples have collected, the data can be processed. For a fixed data record, the memory information is held for N complete recirculations before being replaced by a new record. With a varying input signal, after each recirculation the oldest memory sample is replaced by a new input sample. Since all the data samples are available for subsequent processing, multiplying each sample of the recirculating data with a fast reference signal and summing over N samples provides one point of the correlation function. Further points are obtained on successive recirculation. method requires 2N memory space locations, N multiplications and N additions for each term of the correlation. If all terms of correlation function were desired,  $N^2$  multiplications plus  $N^2$ additions would be required. In a microprocessor system which

does not contain a hardware multiplier or employing a single hardware multiplier (rather than a bank of external multipliers) the multiplication operation can take up to 300 microseconds (u.sec). As a result of adopting this method, the signal bandwidth will be very limited.

#### 2.3 Transform Analysis

Certain transforms possess the cyclic-convolution property (CCP) which may be stated as; the transform of cyclic convolution of two sequences is equal to the product of their transform. Transforms with the discrete Fourier transform (DFT) structure possess the CCP. Such transforms can be applied to the discrete correlation transform pair theorem (25) which stated as,

$$c(n) = \sum_{i=0}^{N-1} r(i).s(n+i)$$

$n=0,1,...N-1$

and

$$C(k) = R^{*}(k) \times S(k) \quad k=0,1,...N-1$$

(2.3)

are transform pair, where 'x' denotes pointwise multiplication.

This implies that a correlation can be calculated by

$$c(n) = T^{-1} (R^{*}(k) \times S(k))$$

(2.4)

using two transforms, N multiplications, and one inverse transform. While the direct calculation of correlation according to the defining equation (2.2) would require a number of complex multiplications and additions proportional to  $N^2$ , use of such transforms have been able to reduce this number tremendously.

#### Fast Fourier Transform (FFT) Correlation

Fast Fourier transform (FFT) is an algorithm for efficiently computing the discrete Fourier transform (DFT) of a finite length sequence. The development and the computation aspects of the FFT algorithm have taken a great stride since the Cooley-Tukey algorithm appeared in 1965 (18). The FFT derivation will not be discussed here (24), only technique for using the FFT for high speed correlation computation.

To apply the FFT to the computation of equation (2.2), N may be chosen to fulfill the required transform length,  $N=2^{v}$ . If the data sequence length is less than N, zeros are appended to r(n) and s(n) to eliminate the overlap or end effects. According to equation (2.4), we compute the following;

Compute the DFT of r(n) and s(n) using the FFT algorithm:

$$R(k) = \sum_{n=0}^{N-1} r(n) W^{nk} \qquad k=0,1, ... \quad (N-1)$$

(2.5)

$$S(k) = \sum_{n=0}^{N-1} s(n) W^{nk}$$

(2.6)

Change the sign of the imaginary part of R(k) to obtain  $R^*(k)$ .

Compute the product;

$$C(k) = R^{*}(k) \times S(k)$$

(2.7)

Compute the inverse transform using the forward transform;

$$c(n) = N^{-1} \sum_{k=0}^{N-1} C^{*}(k) W^{-nk}$$

(2.8)

where  $W = e^{-j2\pi/N}$ .

From the computation time point of view, the use of FFT correlation technique would require a time proportional to (3.(N/2)logN + N), complex multiplications, when N is a power of 2. It is generally faster to use this technique to compute digital correlation rather than computing equation (2.2) directly. Exactly how much faster the FFT approach is than the direct method depends on the microprocessor being employed and the extra supported hardware (i.e., single or parallel-processing scheme with either software or hardware multiplier). It should be noted that the efficient computation of correlation using FFT algorithm involves intermediate quantities, i.e., stored or generated sines and cosines, which are irrational numbers, so making exact results without roundoff errors is impossible on a microprocessor.

In 1975, Winograd (20) developed a new algorithm for computing short length DFT's known as the Winograd Fourier transform algorithm (WFTA). This algorithm uses fewer multiplications than the FFT, and about the same number of additions (26).

#### Correlation using Number Theoretic Transforms

Since 1972, Rader (27), Agarwal and Burrus (22), (28) have developed many transforms with the DFT structure (i.e. FFT and WFTA algorithms can be applied) which can be used for fast and exact calculation of finite digital convolution or correlation, and do not require storage of basis functions (sines and cosines). These transforms are collectively known as number theoretic transforms (NTT's), that are ideally compatable with

microprocessors. In these transforms an integer ' $\alpha$ ' of order N replaces W = exp(-j2  $\pi$ /N) used in the DFT, and both ' $\alpha$ ' and N are defined on finite fields and rings of integers with all the arithmetic operations to be carried out modulo an integer M, e.g. if we have a sequence of length N, x(n) with modulo M we define the NTT of this sequence as:

$$X(k) = \sum_{n=0}^{N-1} x(n) \alpha^{nk} \mod (M) \quad k=0,1,...N-1$$

and by analogy to DFT, the inverse NTT is;

$$x(n) = N^{-1} \sum_{k=0}^{N-1} X(k) \alpha^{-nk} \mod (M) \quad n=0,1,...N-1$$

where the modulus, M, and the sequence length, N, have no common factors and where N is a divisor of O(M) (the number of prime integers in M).  $\alpha$  is chosen to be mutually prime to M and to have order N (22), (27), (28). These NTT's are truly digital transforms, taking into account the quantisation in amplitude and the finite precesion of digital signals.

Microprocessors are becoming available with fast-multiply instructions, and for these that do not have this facility, fast hardware multiplier chips are available which allowing non-simple moduli and  $\alpha$ 's and so many NTT's become practicable for microprocessor implementation (29). The main disadvantage of these transforms is that there is a relation between the sequence length N and the required word length that can require long word lengths for long sequence lengths.

## 2.3.1 Correlation Using Rectangular Transforms

Agrawal and Cooley (23) have derived a very efficient short term convolution algorithms (N=2,3,....,9) based on the recent work of Winograd (26), which can be used to generate a very useful tool to compute digital correlation. The new technique which was derived is called the rectangular transform technique. Like the FFT method, it significantly reduces the number of multiplications relative to the N<sup>2</sup> multiplies of the direct method. The authors have described a method, by which long length convolutions can be derived using two or more shorter convolutions, known as multidimensional convolutions. As an example, the derivation of a two-factor algorithm for cyclic N=15 correlation will be given here, according to this rectangular transformation technique.

Consider, in this example (to avoid any misleading due to symbol variations), that the correlation equation is

$$y_i = \sum_{k=0}^{14} h_{i+k} x_k = i=0,1,....,14$$

and let each of the vectors H, X contains the sequence elements  $h_i$  and  $x_i$ , and the vector Y contains the correlation sequence  $y_i$ . It should be noted that if the discussion in this section will be carried out on the discrete convolution equation only the  $h_i$  indices are needed to be taken in the backward direction to represent the discrete correlation equation.

Let N to be a composite number with mutually prime factor,  $N=r_1\cdot r_2$ , where  $r_1=5$  and  $r_2=3$ . By using the Chineese

Remainder Theorem (CRT) (23) to define the one-to-one mapping;

$$i \longrightarrow (i_1, i_2)$$

i.e.,

$$i = r_2 \cdot q_1 \cdot i_1 + r_1 \cdot q_2 \cdot i_2 \mod (15)$$

(2.9)

where  $\mathbf{q}_1$  and  $\mathbf{q}_2$  are given by

$$r_2 \cdot q_1 = 1 \mod r_1 \qquad q_1 < r_1$$

and

$$r_1 \cdot q_2 = 1 \mod r_2 \qquad q_2 < r_2$$

one would obtain

$$q_1 = 2 \text{ and } q_2 = 2$$

substituting  $\boldsymbol{q}_1$  and  $\boldsymbol{q}_2$  in equation (2.9), we get

$$i = 6i_1 + 10i_2 \mod (15)$$

(2.10)

Table (2.1) illustrates how the index i is mapped to  $(i_1,i_2)$ ,

Table(2.1) Correspondence between one-and two-dimensional indexing in the prime factor algorithm for the case  $i_1=5$ ,  $i_2=3$  and N=15.

Let  $y_i$ ,  $h_i$ , and  $x_i$ , respectively be indexed by the index pair  $(i_1, i_2)$  as shown in table (2.1). The two-dimensional algorithm can be represented, in this case, as

$$y_{i_1,i_2} = \sum_{k_2=0}^{2} \sum_{k_1=0}^{4} h_{i_1+k_1,i_2+k_2} x_{k_1k_2}$$

(2.11)

In vector-matrix notation equation (2.11) may be written as

$$Y = C_5C_3(A_3A_5H)x(B_3B_5X)$$

(2.12)

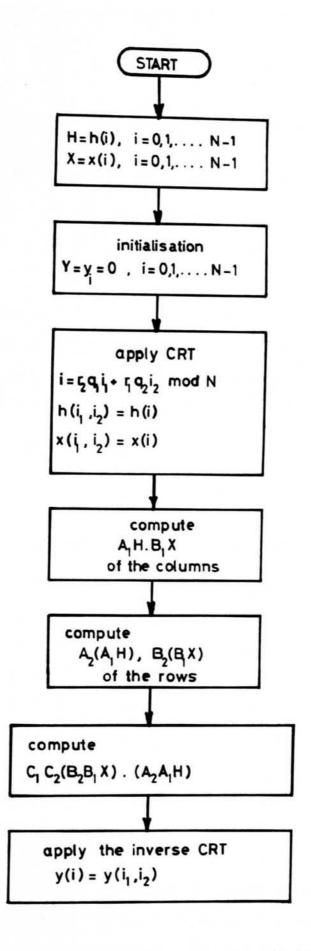

The notation A3A5H means that, one computes the transform  $A_5$  of the columns of H; that is, each column contains 5-elements which can be computed using an optimal algorithm (23) of length N=5, the result is a rectangular array of 10x3. Similarly A3 denotes a rectangular transformation of length 3. The final result is then a rectangular transform of 10x4. notation  $B_3B_5X$  means that, one computes the transform  $B_5$  of the columns of X and then the transformation B, of the rows of the result. This will give a rectangular array of 10x4. element by element multiplication is also a rectangular array of In the same way the operator  $C_3$  reduces the dimensionality, in reverse order, on the array on which it operates; that is, it transforms the 10x4 array to 10x3, and the operator  $C_5$  transforms the 10x3 array to 5x3 array whose elements are the sequences  $y_{i_1,i_2}$ . By applying the inverse CRT, this will yields the one-dimensional correlation of length 15. The above algorithm can be summarised in the flowchart shown in Figure (2.1).

FIGURE(2.1) TWO DIMENSIONAL RECTANGULAR TRANSFORM FLOWCHART.

The rectangular transform approach is applicable for both real and modular arithmetic, depending upon the sort of the transform which is used in each dimension. In most cases the his sequences represent a reference signal and remain fixed for many blocks of the xi sequence, the received signal. Therefore, A.H can be precomputed and used many times.

#### 2.4 Implementations

Two methods for implementing the digital correlation using the direct technique and the rectangular transformation algorithm were investigated in software using the FORTH programming technique (30), (31):

- (i) implementation using Intel-8080 microprocessor system,

- (ii) implementation using TMS9900 microcomputer.

#### 2.4.1 Implementation Using an Intel-8080 microprocessor system

The Intel-8080 microprocessor system (32) which was used is an 8-bit microprocessor with some instructions which operate on 16-bit data. The 8080 system has an instruction cycle about 2 u.sec, it does not contain multiply or divide instructions, and these functions must be performed using software which takes about 250 u.sec. Since it is capable of performing 16-bit arithmetic, the FORTH programming technique was used. This permits the routines to be made very flexible and efficient. In performing arithmetic with reasonably complex expressions it is convenient to use reverse Polish Notation (33) (as in FORTH) which requires a stack to store temporary variables and to pass arguments. Such a stack need not be large, but there should be a reasonable set of instructions for transfering and manipulating

data in conjunction with it, which was available in the Intel-8080 system. FORTH programming is a very efficient technique, since it is an interactive, high level language compact with high speed performance that was suitable to use on the system. However, it was very attractive because the other alternatives, 8080 cross-assembler or any other high level language interpreter, were not readily available at that time.

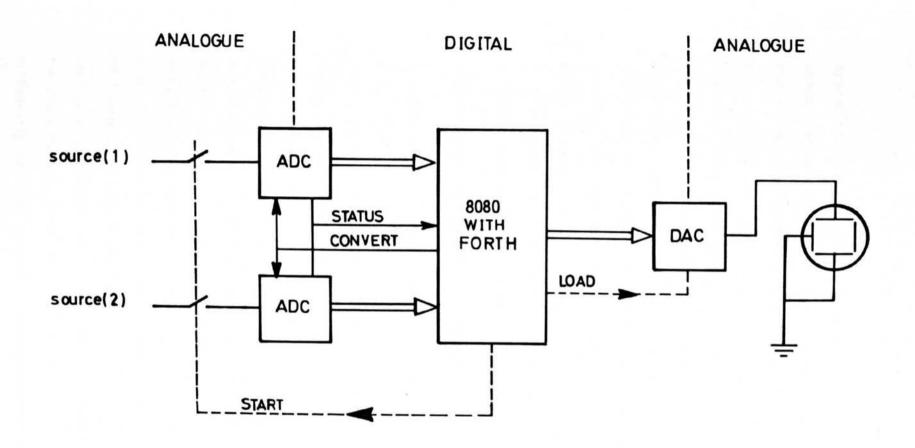

An 8-bit ADC (Ferranti ZN425E type) was used to convert the analogue signals into sequence as shown in the system block diagram of Figure (2.2). In operation a 'start conversion' signal, a negative going pulse of at least 500 nanoseconds (n.sec) duration, was sent to the ADC from the microprocessor. The conversion takes a finite time and only when it is complete can the digital output be read. The converter produces a 'status' signal, which when high informs the microprocessor that a conversion is in progress, and when the data valid informs the microprocessor that the converter's output latches certain valid converted. One output port and two input ports were required in this case.

A simple digital-to-analogue converter (DAC) is incorporated in the Ferranti ZN425E chip. This was used to display the output using an oscilloscope. Two output ports were necessary, in this case, one for the converter data (8-bit) and the other for the 'load' pulse.

Real-time correlation programs were written for an Intel-8080 using FORTH programming language, in which two special

FIGURE(2.2) BLOCK DIAGRAM OF THE CORRELATION MEASUREMENTS SYSTEM USING INTEL 8080 MICROPROCESSOR.

operations were developed in order to keep the correlation computation accurate. These are; a 16-bit by 16-bit multiply and divide the result (32-bit) by a 16-bit number, and the second is a routine to store the summation of the multiplication of two sequences. A complete list of the FORTH programs on the 8080 system is shown in the listing of programs in Appendix B. The correlation function scaling was necessary in order to get a resolution of 8-bits. The execution time for an example requiring 100 correlation points using the direct technique was estimated to be about 4.5 seconds. Hence the speed is important in this application, even using the low level feature (assembly) of FORTH language, the system was impractically slow.

# 2.4.2 Correlation on TMS9900 microcomputer

The TMS9900 microcomputer is an efficient 16-bit machine (34), since it includes the capabilities offered by a full minicomputer. Its powerful instruction set including multiply and divide providing the possibility of computing correlation using fast transformation algorithms, such as the rectangular transforms, in short execution time. In addition, it is highly compatible with the FORTH programming technique, especially since during that time there was no cross-assembler for the 9900 system available. The main block diagram which was used is similar to that of Figure (2.2), except that the 8080 system was replaced by 9900 system. A program was written using the FORTH programming technique to compute 100 equally spaced correlation points using the direct method. Each point required two memory words to have sufficiently accurate results. The approximate speed of the

execution was estimated (excluding the input/output overhead time) by determining the total instruction-execution time. This time was found to be approximatly 1 second.

When computing a 15 point correlation by using the rectangular transforms, (note that 16-bit modular operations was used) according to the flow-chart of Figure (2.1), it was found that the execution time is about 15 milliseconds (m.sec). Although there was a great improvements of the execution time when using the TMS9900, the overall requirements cannot be fulfilled by using a single microprocessor system implemented using software only. However, it was envisaged that using binary correlation implemented with the aid of fast bipolar bit-slice technology would fulfill the speed required.

## 2.5 Binary Correlation

In contrast to general-purpose microprocessors, bit-slice microprocessors (35) can be dedicated to the execution of a special task, for which they may be then prove very efficient. This procedure is especially powerful in combination with microprogramming. The bit-sliced processors are microprogrammed devices that can be realised with two basic types of devices: cascadable bit-slices with the arithmetic/logic unit and the register file on one hand, and a microprogram control memory, which may be arranged to constitute a microprocessor with almost any instruction set, on the other. This gives us the possibility of writing the required algorithms as close as possible to their hardware realisation and to get very high performance but with a 'hard-to-write' microprogram.

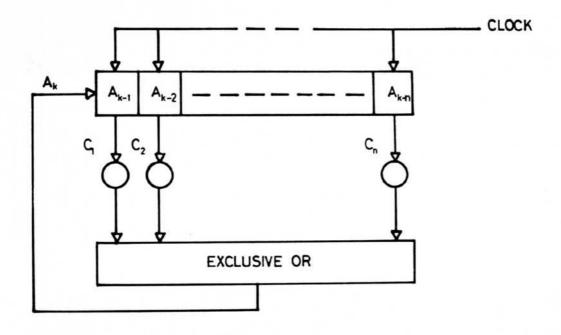

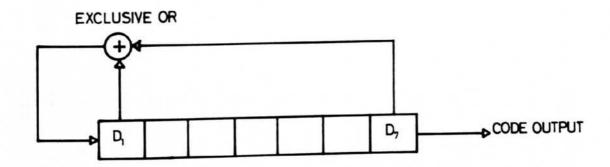

An alternative digital correlator using such a bit-slice processor was implemented, which demonstrates the feasibility of using bit-slice microprocessors for digital spread spectrum signal processing. In contrast to the previous methods, the realised processor was tailored for this application, which it therefore fulfills very efficiently. The received signal is normally a binary modulated sequence on which the information was embedded. Therefore, equation (2.2) simply implies a comparison process between the respective bits in the received sequence, r(i), and the shifted stored sequence, s(i+n). The number of agreement bits can be obtained by an exclusive-NOR operation and a Hamming weight function generator, whose outputs are summed. So, the main three operations in the correlation process are replaced by shifter, exclusive-NOR, and summer operations which were implemented at very high speed using the bit-slice approach. Thus for a digital correlator to be effective in this application it must be expandable to accomodate variations in the sequence length. The next chapter will introduce the bit-slice microprocessor chosen for the subsequent work in this thesis.

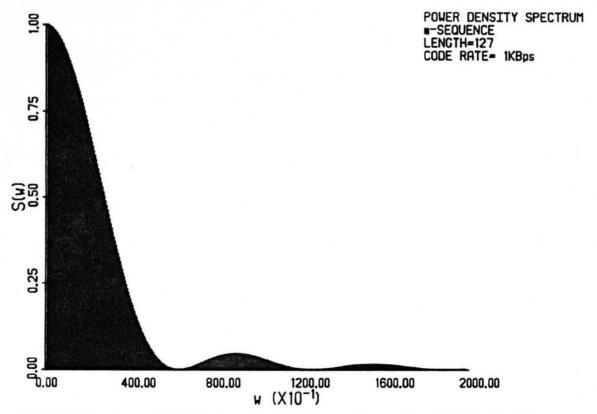

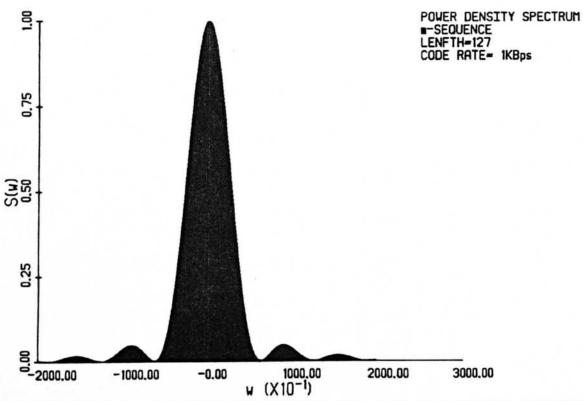

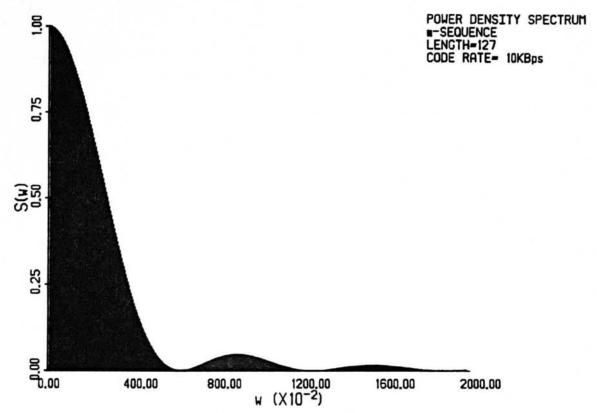

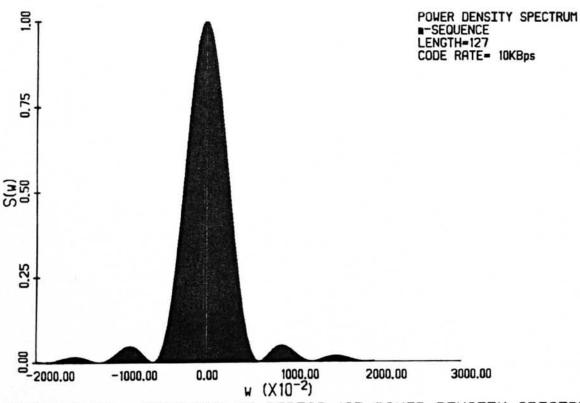

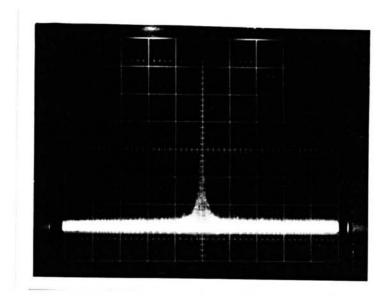

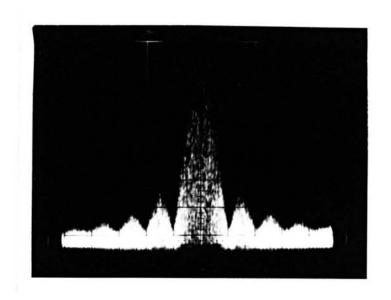

### 2.6 Real-time Power Spectral Density

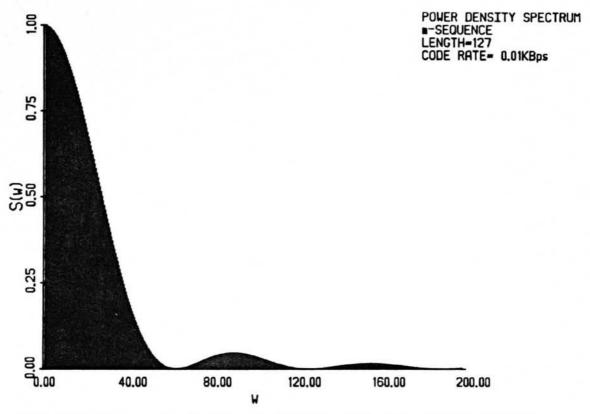

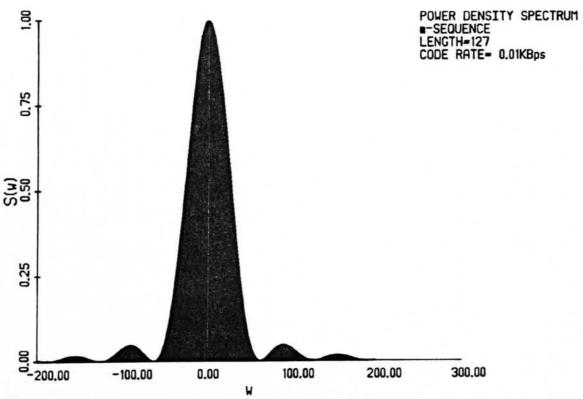

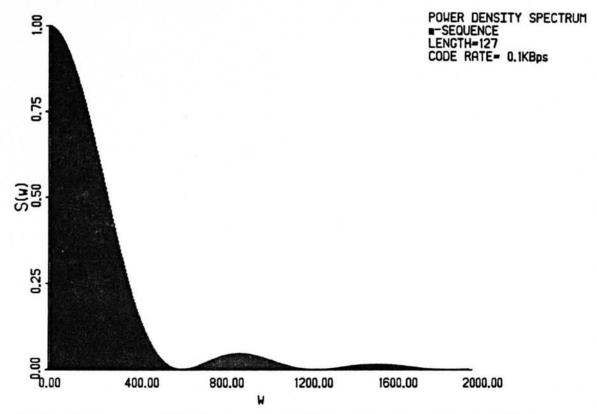

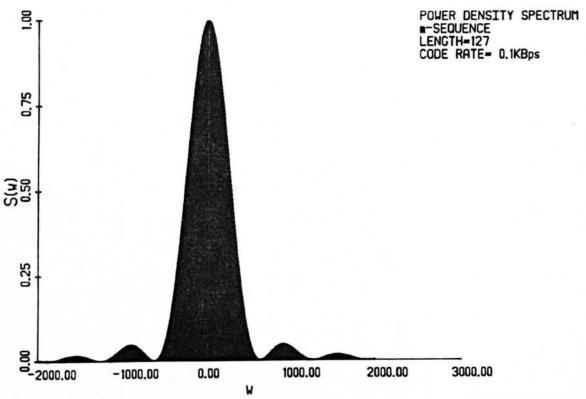

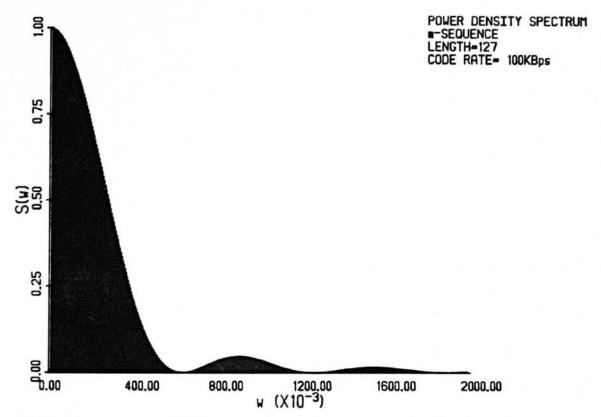

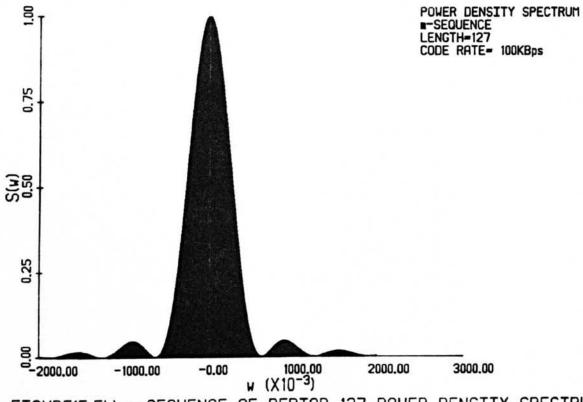

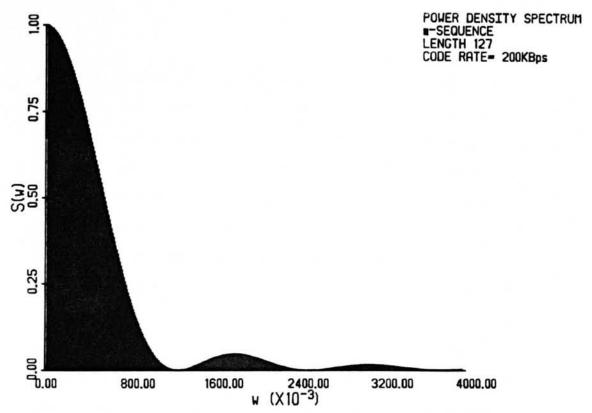

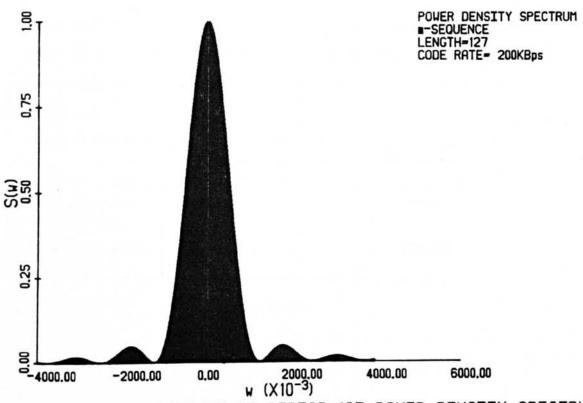

In spread spectrum communication it is desirable to determine the spectral content of signals in real-time. It is very expensive to do this on general-purpose microprocessors, and only special array processors can provide the required digital computing power. However, analogue circuit technology, such as charge-coulped devices, have been widely used in such cases. An evaluation module containing the Reticon R5601 quad chirped

transversal filter (36) was available, which included additional circuitry necessary to compute the power spectrum of an analogue input signal by the Chirp-z transform algorithm (37). Simply, the device and interface system form a discrete-time spectrum analyser, selecting and outputing the magnitude and frequencies of the spectral components of an analogue input signal. The analysis band in the normal situation extends from zero to the Nyquist frequency (one-half the sample frequency). A mirror image also appears extending from the sample frequency (equivalent to dc) down to the Nyquist frequency. The resolution bandwidth in general is approximately (1/512) of the sample frequency. The overall performance is limited to obtaining the power spectral density and to a maximum sample rate of 200 KHz.

#### 2.6.1 Chirp-Z Transform Algorithm

In 1969, Rabiner and Schafer (37) derived an algorithm for evaluating the DFT, which was called the "chirp-z" transform (CZT), in which the bulk of the computation is performed in a chirp transversal filter, and for this reason it is particularly attractive for CCD implementation (38). When implemented digitally, the CZT has no advantages over the conventional FFT algorithm (39).

The CZT algorithm can be derived by starting with the definition of the DFT

$$X(k) = \sum_{n=0}^{N-1} x(n)e^{-j2\pi nk/N}$$

,  $k=0,1, ... N-1$

where either or both x(n) and X(k) may be complex.

Using the substitution

$$2nk = n^2 + k^2 - (n-k)^2$$

the following equation results:

$$X(k) = e^{-j2\pi k^2/N} \sum_{n=0}^{N-1} (x(n)e^{-j\pi n^2/N}) e^{j\pi(k-n)^2/N}$$

$$= e^{-j\pi k^2/N} \sum_{n=0}^{N-1} g(n)e^{-j\pi(k-n)^2/N}$$

(2.13)

Equation (2.13) represents the CZT. Three operations are required

- (i) Multiply each term, x(n), by the complex factor,  $\exp(-j\pi n^2/N)$  to produce a new sequence g(n).

- (ii) Perform a discrete convolution between the sequence g(n) and the sequence  $\exp(j\pi n^2/N)$ .

- (iii) Multiply the resulting output sequence by the factor  $\exp(-j\pi k^2/N)$  for each point of X(k).

The CZT gets its name from the fact that; the sequences  $\exp(-j\pi n^2/N)$  and  $\exp(-j\pi k^2/N)$  can be thought of as complex exponential sequences with linearly increasing frequency. Such signals are called "chirp" (linear FM) signals.

## 2.6.2 Hardware Implementation

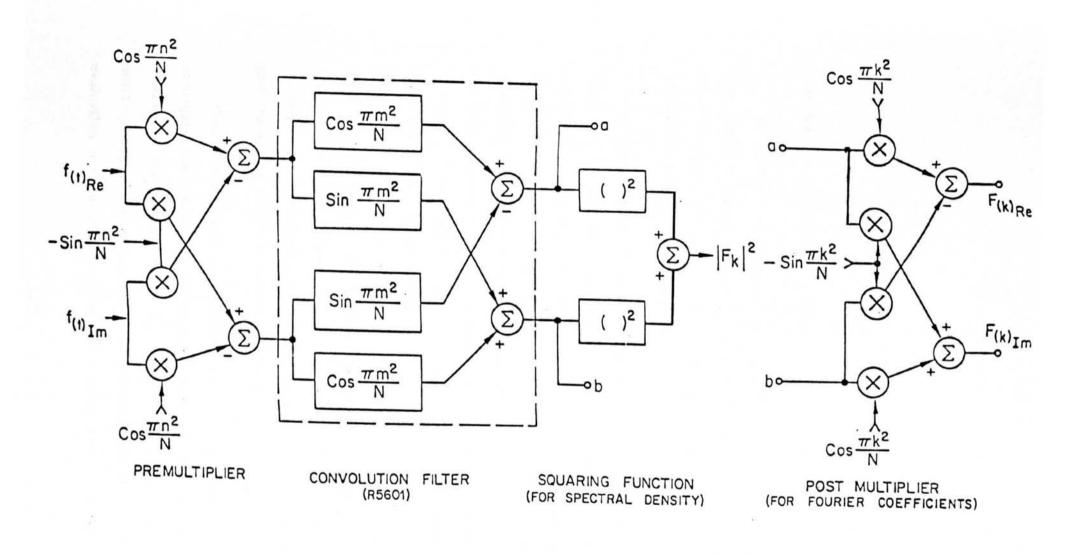

The above discussion shows that the CZT algorithm involves three stages of computation: pre-multiplication, convolution, and

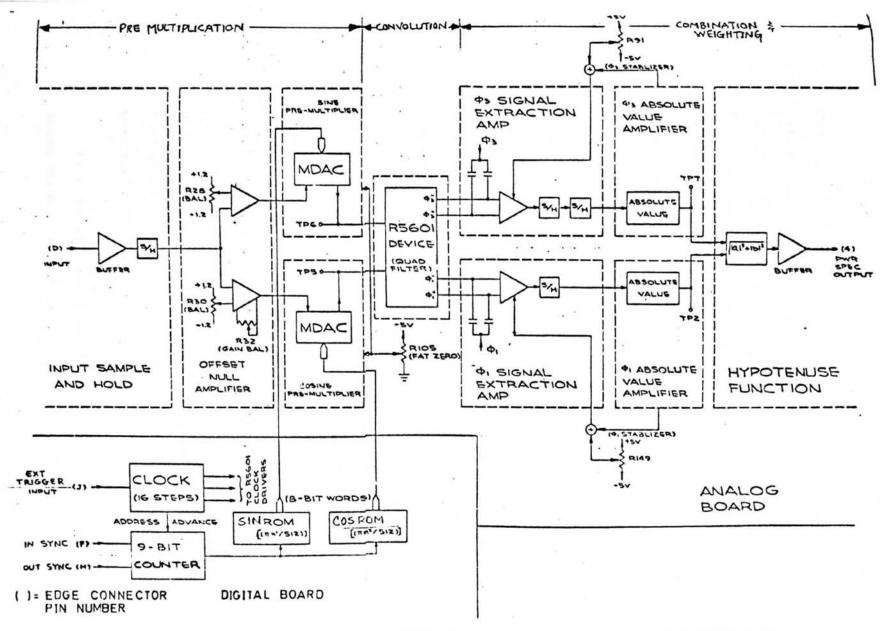

post-multiplication. The block diagram of a complete transform based on the CZT algorithm of equation (2.13) is shown in Figure Pre-multiplication is accomplished by the multipliers to the left in Figure (2.3) and post-multiplication by those on the The major computing task is the convolution portion; this right. task is performed by the Reticon R5601 quad chirped transversal filter (36). This device contains two separate 512-stage MOS charge-coupled devices which are used to implement four transversal filters using a split-electrode technique (40). filter weighting coefficients and internal circuit connections are configured so that the device, in conjunction with additional off-chip components, can implement the CZT algorithm to calculate a 512-point DFT (38), (41).

The evaluation module which contained the R5601 device can be used to compute the power spectrum of an analogue signal. No phase information is obtainable with this module, as the post-multiplier unit is replaced with a hypotenuse function which recovers the spectral amplitude from the component cosine and sine terms. From equation (2.13), the squared spectral amplitude of a sequence x(n) can be expressed as

$$X(k) = \sum_{n=0}^{N-1} x(n)e^{-j\pi n^2/N} e^{j\pi (k-n)^2/N}$$

(2.14)

The final phase multiplier term,  $e^{-j\pi k^2/N}$ , has been deleted because it has unit magnitude and so does not affect the amplitude. The input data is stepped each time a new spectral component is calculated. Equation (2.14) then becomes:

FIGURE (2.3) BLOCK DIAGRAM OF THE CHIRP-Z TRANSFORM ALGORITHM.

$$x_s(k) = \sum_{n=0}^{N-1} x_{(n+k)e^{-j\pi n^2/N}} e^{-j\pi(k-n)^2/N}$$

The notation  $X_s(k)$  indicates a "sliding" CZT.

A further simplification in implementation is possible if the input is purely real, as it is in this case. The imaginary input is always zero so that two of the input multipliers may be deleted and the input circuit simplified.

A block diagram of the evaluation module is shown in Figure (2.4). The analogue (real) input signal is buffered and converted to discrete-time samples by the input sample-and-hold, then split into the direct and quadrature (real and imaginary) channels. The sample values are multiplied by the appropriate chirped waveform using multiplying digital-to-analogue converters. The digital inputs to these converters are derived from two 512-by-8 bit ROMs which contain the sampled chirped sine and cosine waveforms. The sampled analogue products are then used for the input to the R5601 four-channel convolution filter. Outputs from the filter are sampled and held to give time coincidence of all outputs, and then combined on an rms basis to give the spectral density of the input waveform.

Four clock phases are required by the filter device to propagate the discrete signal packets through the CCD channels. These are designated  $\Phi_1$  -  $\Phi_4$  and are generated by a multi-phase clock generator circuit incorporated in the evaluation module which may be driven either from a 1.6 MHz

FIGURE(2.4) BLOCK DIAGRAM OF POWER SPECTRUM EVALUATION MODULE.

internal oscillator or from an external trigger source. The sample rate with the on-board oscillator is a nominal 100 KHz, but lower rates are attainable with external triggering. The "address advance" pulse increments a 9-bit counter which addresses the weighting factor ROMs.

#### 2.7 Conclusion

To apply digital techniques directly to the correlation process would seem to require high speed circuitry, in contrast to the rather slow FIS microprocessor systems. Much ongoing research is devoted to minimising the requirement of multiplications in signal processing algorithms, because multiplications cannot be performed efficiently by microprocessors. The applications of efficient algorithms such as FFT, WFTA, and NTTs for digital correlation have been described. The idea of using a general-purpose microprocessor system rather than dedicated processors for digital correlation computation using a fast transform techniques, such as a rectangular transforms, has been implemented and investigated, this will not lead to a very practical bandwidth capability. The use of a dedicated bit-slice microprocessor has been found very efficient in implementing binary correlation and other signal processing applications related to PN spread spectrum system described elsewhere in this thesis.

An investigation into power spectrum using charge-coupled devices has been demonstrated.

#### CHAPTER 3

### Bit-Slice Microprocessor System

#### 3.1 Introduction

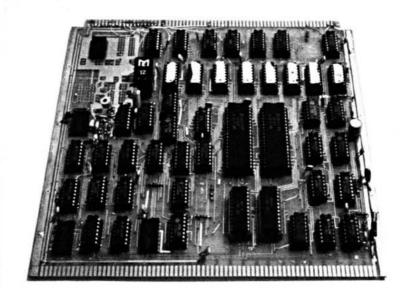

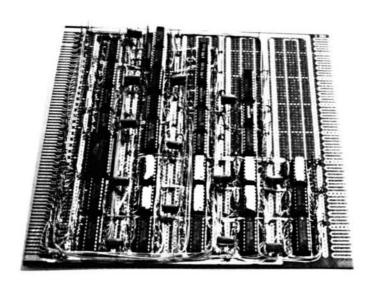

In the late 1970's, bipolar LSI devices including the four-bit microprocessor slice became readily available (42), (43), (44). These devices have been used in the design of 4-bit, 8-bit, 16-bit, 32-bit, and even larger CPU's (45). The structures function under the control of a microprogrammed memory. The microprogram memory is an N word by M bit memory used to hold the microinstructions, e.g. 1K x 32 bits in the present system. The data output from the microprogram memory are distributed to most parts of the system and these constitute the control signals.

The bit-slice approach requires each central processing element (CPE) chip to contain a 2-bit or 4-bit slice of every register in the CPU of the system. For a CPU constructed of bipolar microprocessor slices, the difference between a CPE and a CPU is that the CPE is the bit-sliced element that is used to form the complete CPU by paralleling two or more CPE's in order to obtain the desired microprocessor word length. A bit-sliced CPE contains a bit group of the working register set or RAM, a very high-speed ALU and status indicators. Multiple buses are used to interconnect the parallel bit-sliced chips and form the microprocessor system. Bipolar microprocessors of this type can be used to form systems with 125 n.sec cycle times. MOS

microprocessor equivalents are slower, with cycle times of the order of 1-2 u.sec. When instruction times are given for a MOS microprocessor, the instruction is a machine level instruction. To compare this with a bit-slice system macroinstruction execution times must be used, where a macroinstruction is a machine instruction which the microprogram supports. The bit-slice microprocessor developed for this project has an effective macroinstruction time of 330 n.sec or less.

This chapter describes the hardware of the bit-slice microprocessor system that has been used in the following chapters.

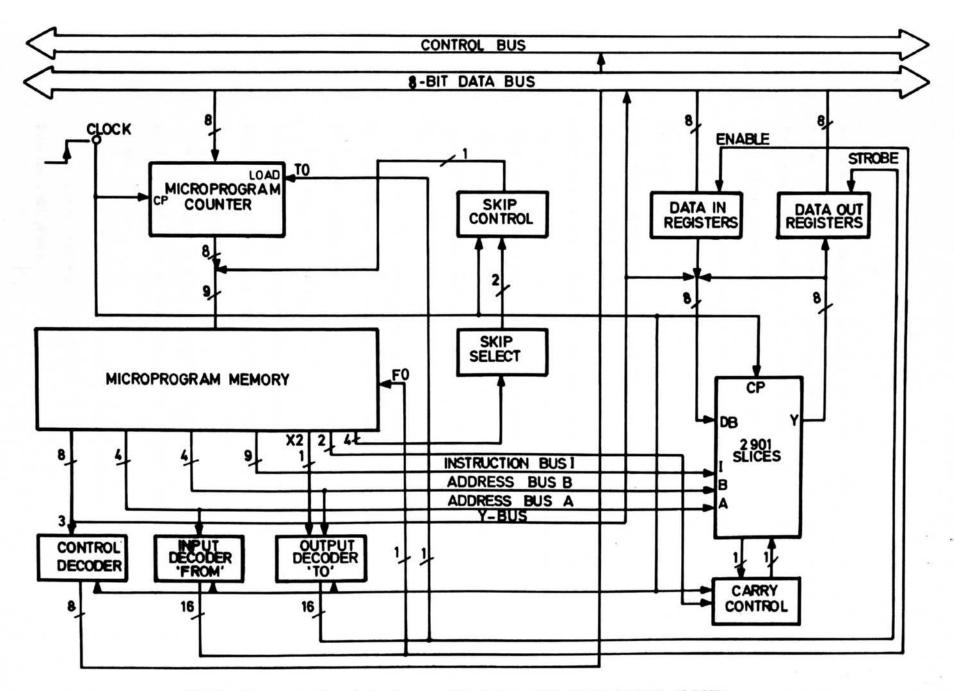

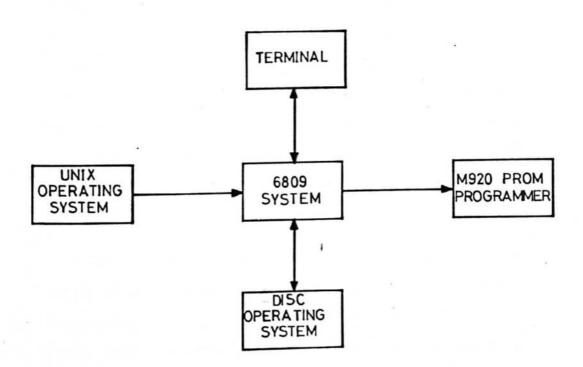

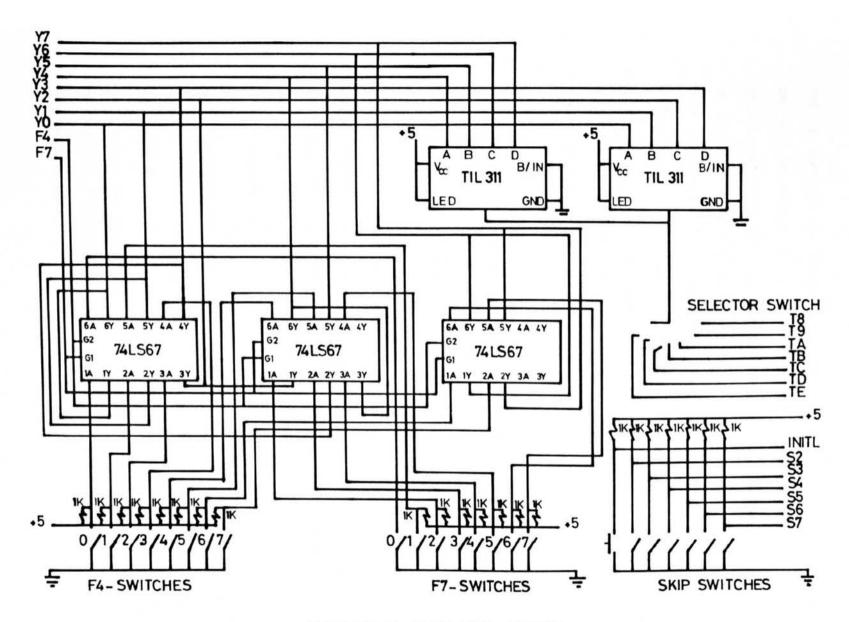

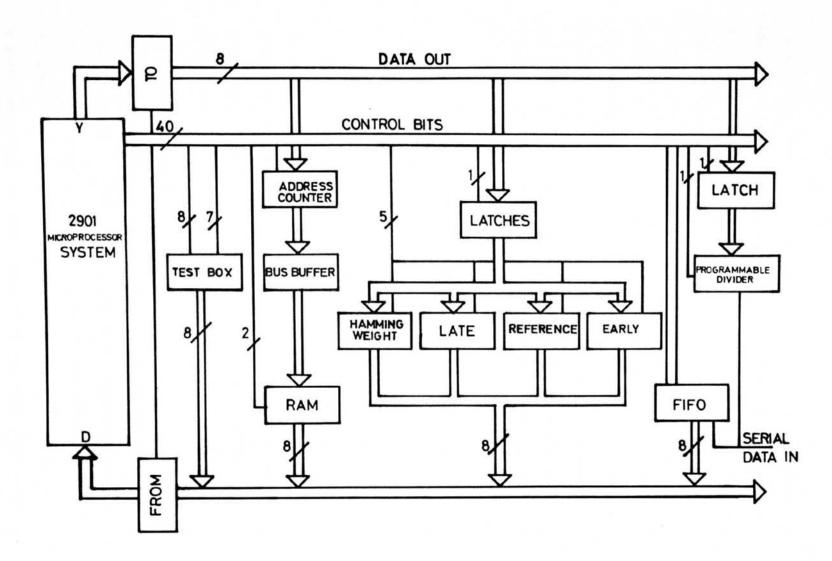

#### 3.2 System Organisation

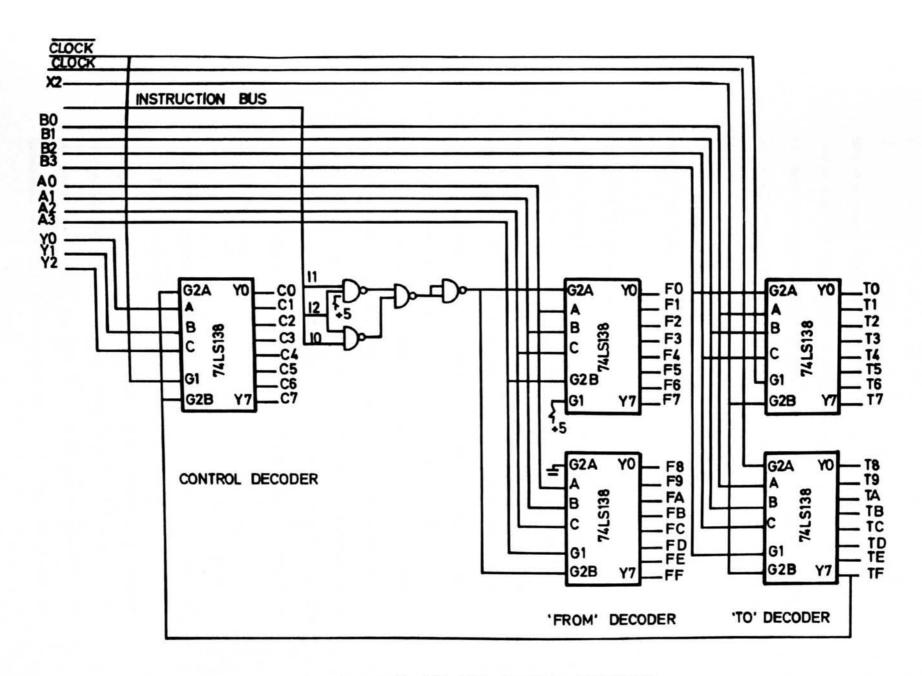

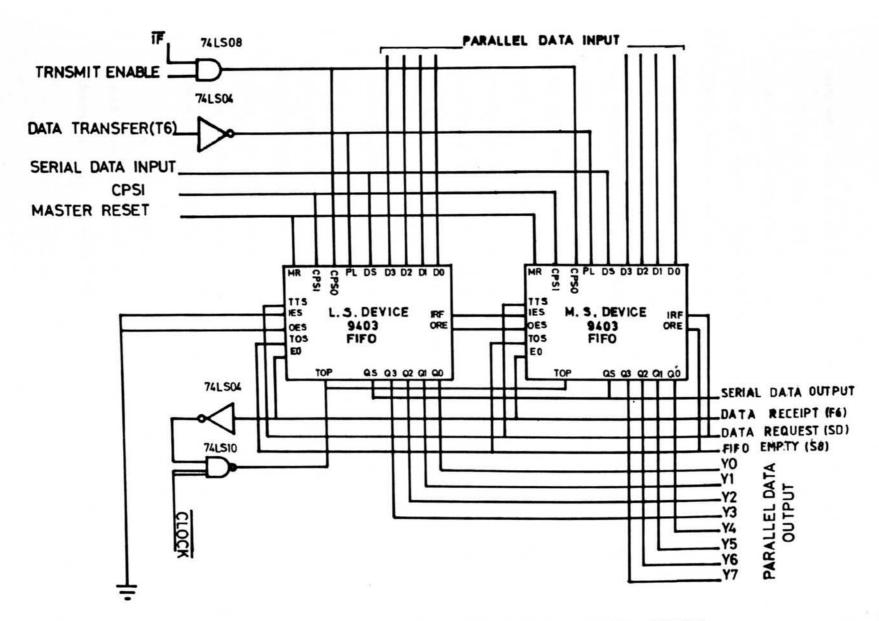

Since the required speed cannot be obtained using MOS microprocessors, a bit-slice approach was chosen for this project.

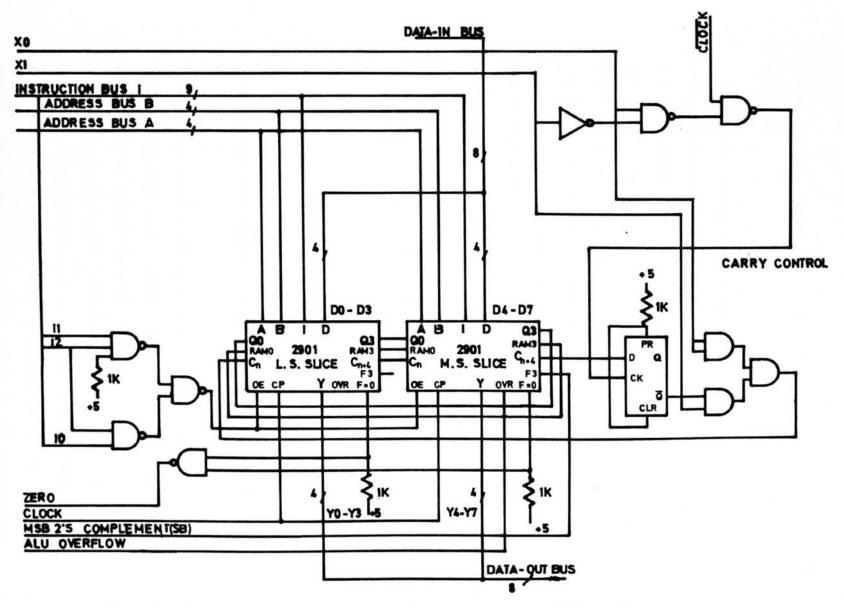

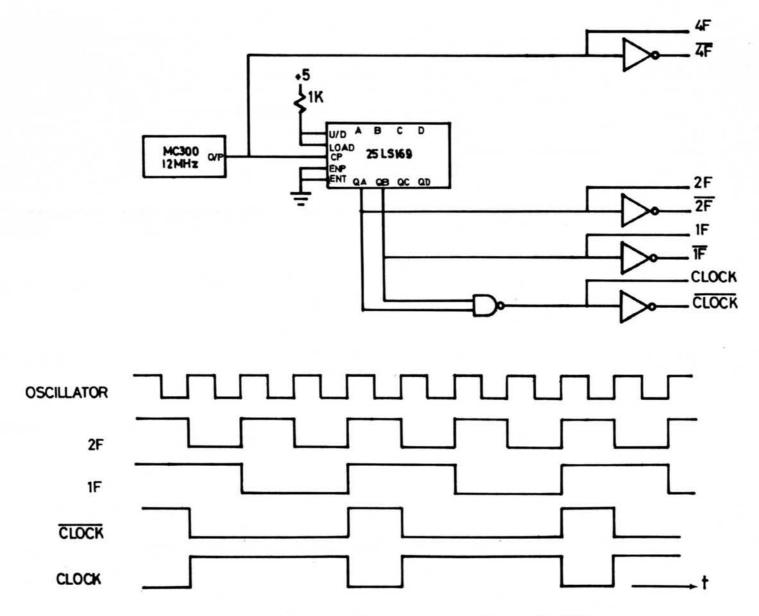

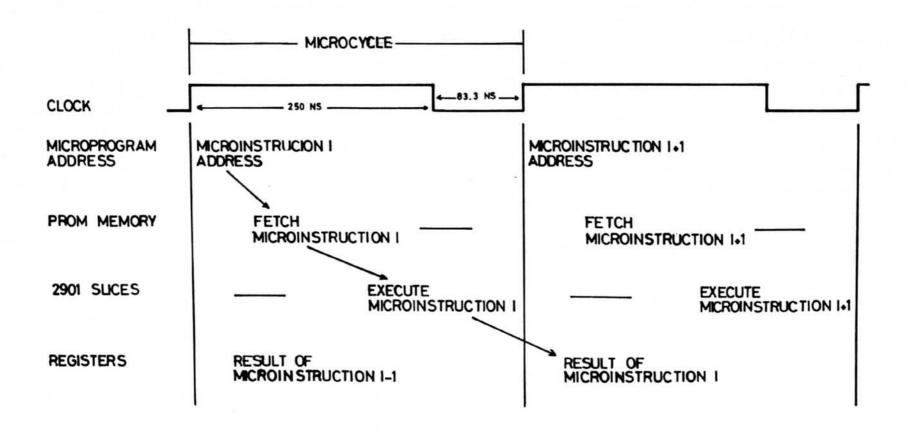

The architecture of the bit-slice microprocessor system is shown in Figure (3.1). It is an 8-bit microprogrammed processor made up of two 4-bit 2901 bit-slice devices with a microprogram control unit constructed from a PROM and a counter. Other subsystems consist of auxiliary logic control circuits which support the execution of the microinstructions; these are the carry control, the skip select, and the skip control. The system also contains various decoders and external registers which were used for interfacing the system to the external world through an 8-bit data bus and eight control flags. The system operates synchronously under the control of a clock which runs at 3 MHz

FIGURE (3. 1) ARCHITECTURE OF BIT-SLICE MICROPROCESSOR SYSTEM.

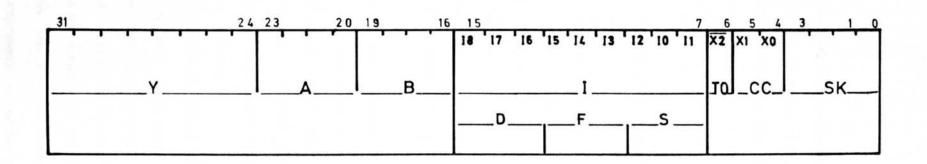

and produces a low level for 83.3 n.sec and a high level for 250 n.sec. Before operation the microprogram is loaded into PROM. The size of the PROM is 512 words, with each word being 32 bits long (one microinstruction in length). In operation the microprogram counter outputs an address to the PROM memory, and this address is used to fetch the next microinstruction that is to be executed (a microinstruction will be assumed to execute in one clock cycle). In this case the next microinstruction address is always equal to the current microinstruction address plus 1. After a time delay equal to the read access time of the memory, the memory outputs the control signals to the rest of the system. Each microinstruction contains information blocked out in fields, where each microinstruction field directs or controls one or more specific hardware elements in the system, as shown in Figure (3.1).

The 'Y' field (8-bits) is used to provide constant parameters for the microprogram as well as the address of the destination in the branch instruction.

Two four bit fields, A and B, are used for addressing the internal registers, source and destination. A and B are also used to address the 'From' (data-in) and 'To' (data-out) registers, respectively.

An 'I' field (9-bits) is used to control the source, function, and the destination of any external or internal data in the 2901 slices.

X2 (1-bit) when low, enables one of 16 'To' registers.

The carry control field (2-bits) is used to control the carry into the 2901 slices.

The skip control field (4-bit) is used to control the LSB of the microprogram counter. It is worth mentioning here that the two flags 'TO' and 'FO' have special uses in the system which will be discussed later.

The following sections of this chapter will describe the connection of each IC used in this design.

### 3.3 2901 ALU/Register slices

The Am2901 bipolar 4-bit microprocessor slice is designed to be used in microprogrammed systems (46), (47). It was first produced by Advanced Micro Devices and is now second-sourced by many other firms. It is the most widely used bit-slice device, because of the flexible structure of the slice's microinstruction. The 9-bit microinstruction code consists of three 3-bit groups that either control or determine the internal arithmetic-logic unit's source operand, ALU function and destination register. This breakdown reduces delays; it permits parallel decoding of different groups of the same microinstruction. The three groups lead to 512 possible microinstructions.

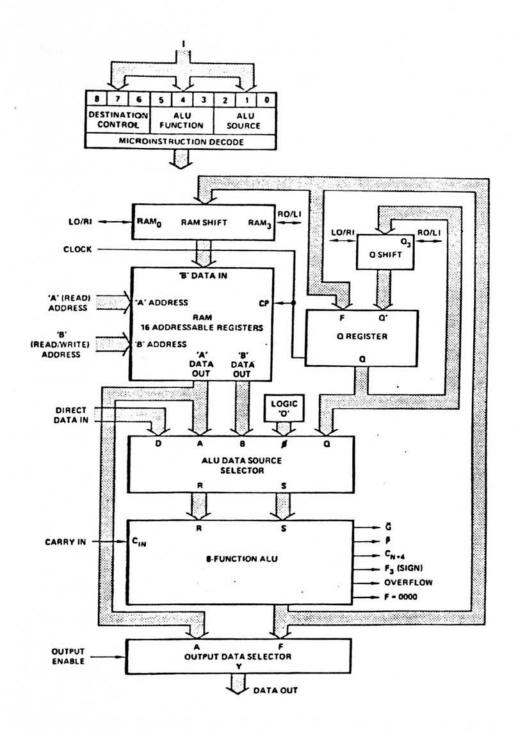

#### 3.3.1 Architecture

The architecture of the 2901 is shown in Figure (3.2) (46). All data paths are 4-bits wide. One key element is the 16-word RAM forming a bank of 16 4-bit registers. It is a 2-port RAM, meaning that two words (registers) can be selected simultaneously. Data in any of the 16 registers of the RAM can be read from the A-port which is controlled by the 4-bit A address

FIGURE (3.2) THE AM 2901 MICROPROCESSOR SLICE.

field input. Likewise, data in any of the 16 registers of the RAM as defined by the B address field input can be simultaneously read from the B-port of the RAM. The A and B busses feed two latches. When the clock input to the slice is HIGH, the selected registers are enabled into the A and B busses and pass through the latches. When the clock input is LOW, the latches hold the RAM data. This eliminates any possible race conditions that could occur while new data is being written into the RAM. 4-bit high-speed ALU can perform three binary arithmetic and five logic operations. The R port of the ALU is fed from a multiplexer, allowing us to gate the A register, the D bus (an external bus coming into the 2901), or zeros into the R port. Likewise, the S port of the ALU is fed by a multiplexer, allowing us to gate the A register, B register, Q register, or zeros into the S port. These multiplexers and the characteristics of the register array allow us to perform operations such as:

but not

$$R4 = R2 + R3 + 0/1$$

$R3 = Q + Q + 0/1$

where the meaning of 0/1 is that the carry condition can be added to the operation.

The ALU has three other status outputs. These are F3, F=0, and the overflow (OVR). The F3 output is the sign bit. F=0 output is used for zero detect, F=0 is HIGH when all outputs are

LOW. The overflow (OVR) output is used to flag arithmetic operations that exceed the available two's complement number range. The chip also contains another register, the Q register. It can be used for 8-bit shift up or down operations.

The output of the ALU can be gated to several destinations. A 3-state output bus (Y) can be fed with the ALU output (the F bus) or with the value of the register selected as the A register. The ALU output can also be gated into the register array (the register currently selected as the B register), passing through a shifter as well as being gated into the Q register, passing first through another shifter.

The nine I inputs control the source operands, the ALU function, the shifters, and the routing of data. The microinstruction inputs used to select the ALU source operands are  $I_0$ ,  $I_1$ , and  $I_2$ . The  $I_3$ ,  $I_4$ , and  $I_5$  microinstruction inputs are used to specify the function of the ALU. The remaining three microinstruction inputs,  $I_6$ ,  $I_7$  and  $I_8$  control the two shifters, the Q-register multiplexer, and the Y-bus multiplexer.

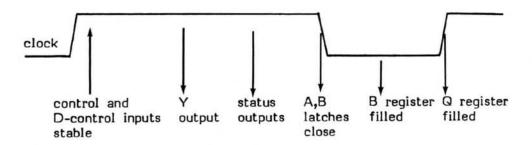

The clock input to the 2901 controls the registers array, the Q register, and the A and B latches to the ALU. Data is clocked into the Q register on the LOW-to-HIGH transition of the clock. When the clock input is HIGH, the latches are open and pass the values of the registers selected as the A and B registers. When the clock input is LOW, the latches close and retain the last data entered. New data can be fed into the B

register when the clock input is LOW. Figure (3.3) is a simplified view of the timing of the 2901, the clock timing of the system will be described in the following sections. Notice that the control inputs must be stabilised at their required states at the beginning of the cycle. These times are called set-up times; these are expressed relative to the transitions of the clock input. As an example, the I signals from the current microinstruction must be present at the 2901's pins at least 80 n.sec before the LOW-to-HIGH transition of the clock pulse. Another timing consideration is propagation delays, the time from when an input signal is established to when a particular output is stable (46).

FIGURE (3.3) SIMPLIFIED VIEW OF 2901 TIMING.

### 3.3.2 2901-Slices Interconnection

Two 2901's were connected to form a CPU with a data-path width of eight bits. The 16 registers and the Q register are 8-bits wide and reside in the 2901's, a half in each 2901 as shown in Figure (3.4). An 8-bit data-in bus feeds both 2901's in parallel, and the 2901's feed an 8-bit data-out bus. Figure (3.4) also shows the connection of the control signals and the

FIGURE (3.4) TWO 2901'S USE TO CONSTRUCT 8-BIT CPU WITH CARRY CONTROL.

status outputs. Most of the control signals feed the 2901's in parallel.

It was mentioned in the previous section that the microinstruction inputs,  $I_0$ ,  $I_1$ , and  $I_2$  are used to select the ALU source. One of these source operands is the direct data input (D). To select D the data output (Y) must be in the high-impedance state. This can be done by using the group inputs,  $I_0$ ,  $I_1$ , and  $I_2$  to control the output enable (OE) as shown in Figure (3.5), when OE is HIGH, the Y outputs are in the high-impedance state.

|          | micro code     |   |                |               | ALU source operand |   |    |

|----------|----------------|---|----------------|---------------|--------------------|---|----|

| mnemonic | <sup>I</sup> 2 | ľ | I <sub>0</sub> | octal<br>code | R                  | S | OE |

| DA       | н              | L | н              | 5             | D                  | Α | н  |

| DQ       | Н              | Н | L              | 6             | D                  | Q | Н  |

| DZ       | Н              | Н | Н              | 7             | D                  | О | Н  |

FIGURE (3.5) ALU DIRECT INPUTS (D) SOURCE SELECT CONTROL.

On the least-significant slice, the carry-in is an input from an external carry control source. Two bits XO and X1 determine the carry-in state as shown in Figure (3.6). On the other slice, the carry-in is connected to the carry-out of the first slice, enabling the ALUs to work as a single, ripple carry, 8-bit ALU. Notice also the interconnection of the shifters, enabling the Q shifter and RAM shifter to act as two 8-bit

shifters. Most of the status output are taken only from the most-significant slice. The F=0 output is an open-collector output, meaning that it can be wire-AND'ed, with a pull-up resistor, between slices to indicate whether the output from both ALUs is zero. The look-ahead carry pins on both slices were not used, since the look-ahead carry logic was not used in this design.

| X1 | X0 | carry-in         |                 |

|----|----|------------------|-----------------|

| 0  | 0  | 1                | carry set       |

| 0  | 1  | 0                | carry hold      |

| 1  | 0  | C <sub>n+4</sub> | carry propagate |

| 1  | 1  | 0                | carry clear     |

FIGURE (3.6) CARRY CONTROL LOGIC.

From Figure (3.4) we can analyse the minimum microcycle time for this system as follows:

The guaranteed, or worst-case, propagation times for the Am2901B slice are (43), (42);

| From inputs A, B to output Y           | 60 n.sec |

|----------------------------------------|----------|

| From inputs A, B to last status output | 70 n.sec |

| From inputs A, B to C <sub>n+4</sub>   | 59 n.sec |

| From input Cn to last status output    | 37 n.sec |

| From input C <sub>n</sub> to outpud Y  | 30 n.sec |

The propagation delay due to the ripple carry between the slices (i.e. the carry-in to the most-significant slice is not stable until  $t\,+\,59\,$  n.sec) means that the output of this slice will not

stabilise until t + 59 + 37 n.sec. By adding the propagation and set-up times of the external carry control (60 n.sec) this system could not operate faster than one microcycle per 160 n.sec.

### 3.4 Microprogram Control

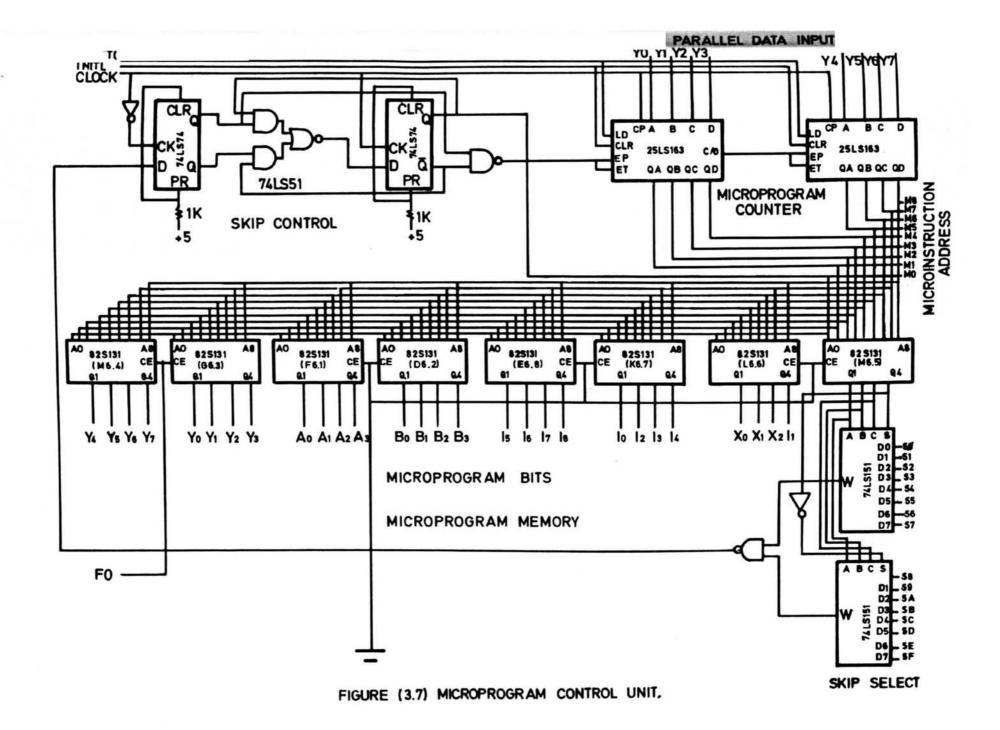

The microprogram control unit is the part of the system that controls the other subsystems, synchronises the internal and external events and fetches and decodes the microprogram residing in the microprogram memory. A microprogram control unit consists of the microprogram memory and the structure required to determine the address of the next microinstruction; in our case this structure is the microprogram counter. The logic diagram of the microprogram control together with the skip control and the skip select is shown in Figure (3.7).

Unlike the main memory in MOS microprocessor systems, the microprogram memory is referred to once each microcycle during the execution of a microinstruction. Therefore, to gain the necessary speed, the microprogram memory is always implemented using bipolar memory devices. This memory contains sequences of microinstructions, 32 bits wide, which apply the proper control signals to the 2901's and the other subsystems, to execute the desired operation. The address lines of the microprogram memory are driven from the microprogram counter. This counter has facilities for storing an address, incrementing an address, and jumping to any address. The microprogram counter is controlled by bits from the microprogram memory.

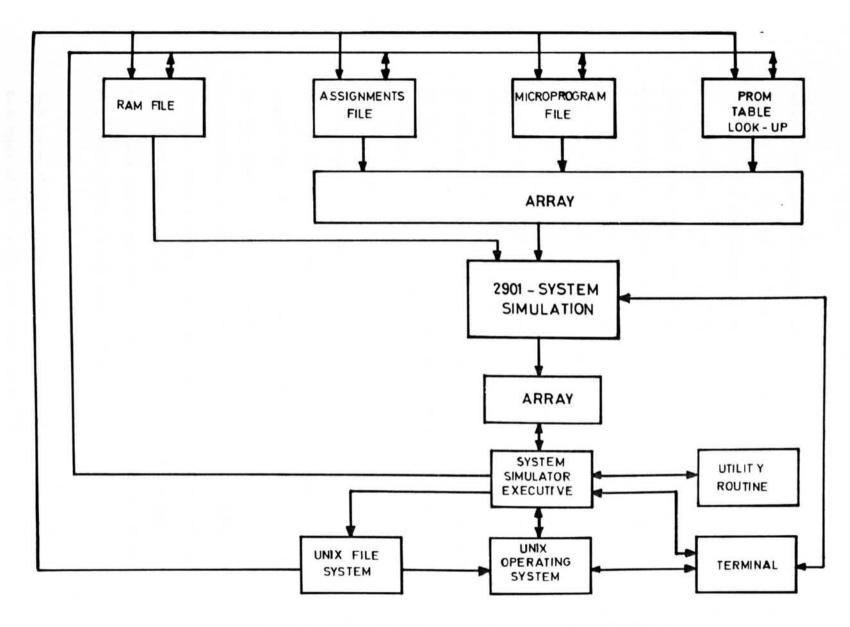

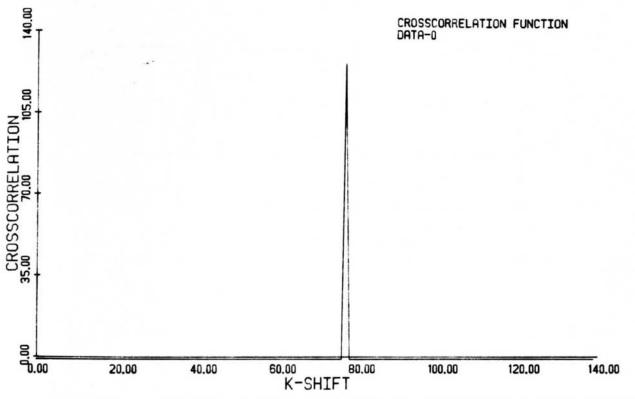

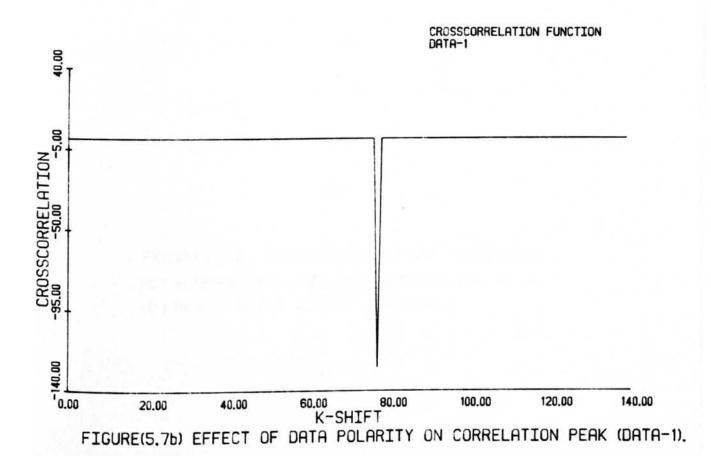

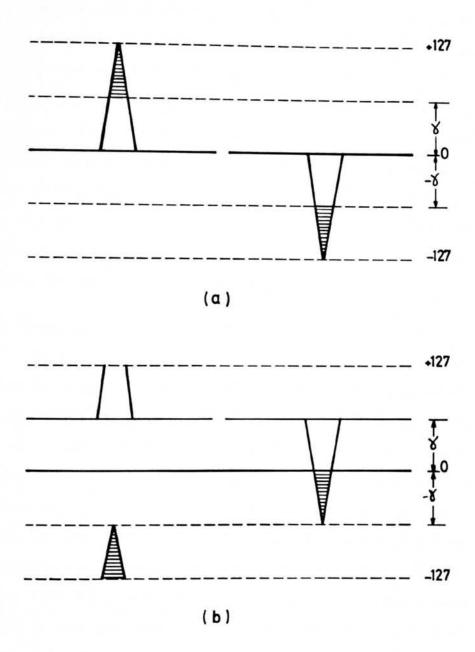

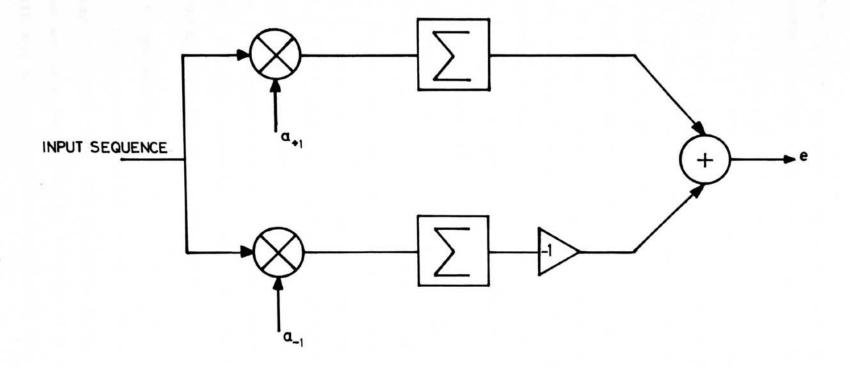

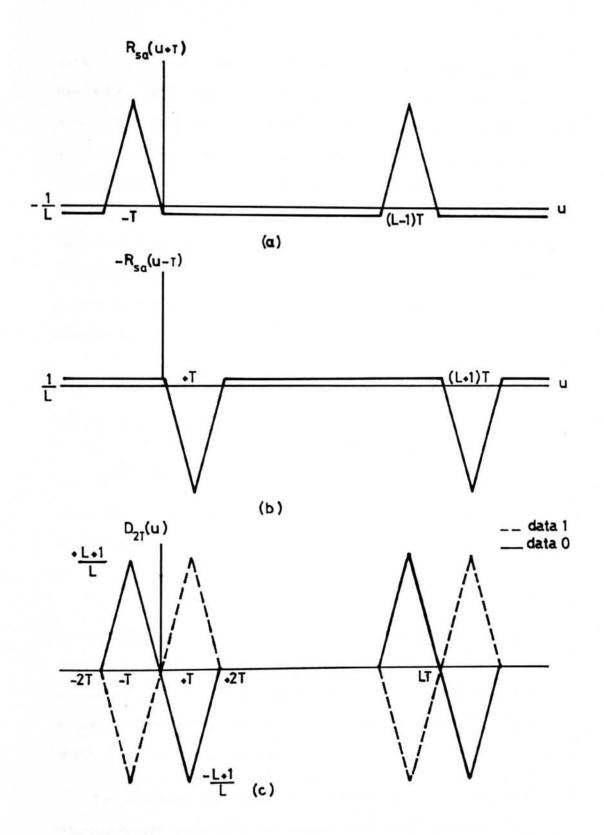

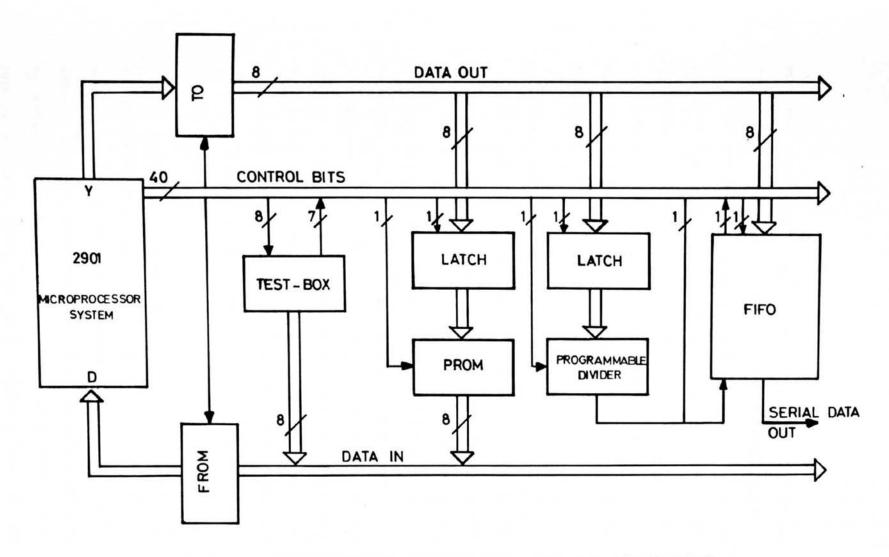

## 3.4.1 Microprogram Memory