| Title                       | Temperature and frequency dependent electrical characterization of HfO2/InxGa1-xAs interfaces using capacitance-voltage and conductance methods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Author(s)                   | O'Connor, Éamon; Monaghan, Scott; Long, Rathnait D.; O'Mahony, Aileen; Povey, Ian M.; Cherkaoui, Karim; Pemble, Martyn E.; Brammertz, G.; Heyns, M.; Newcomb, Simon B.; Afanas'ev, V. V.; Hurley, Paul K.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| Publication date            | 2009                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| Original citation           | O'Connor, É., Monaghan, S., Long, R. D., O'Mahony, A., Povey, I. M., Cherkaoui, K., Pemble, M. E., Brammertz, G., Heyns, M., Newcomb, S. B., Afanas'ev, V. V. and Hurley, P. K. (2009) 'Temperature and frequency dependent electrical characterization of HfO2/InxGa1–xAs interfaces using capacitance-voltage and conductance methods', Applied Physics Letters, 94(10), pp. 102902. doi: 10.1063/1.3089688                                                                                                                                                                                                                                                        |  |  |  |

| Type of publication         | Article (peer-reviewed)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| Link to publisher's version | http://aip.scitation.org/doi/abs/10.1063/1.3089688 http://dx.doi.org/10.1063/1.3089688 Access to the full text of the published version may require a subscription.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| Rights                      | © 2009 American Institute of Physics. This article may be downloaded for personal use only. Any other use requires prior permission of the author and AIP Publishing. The following article appeared in O'Connor, É., Monaghan, S., Long, R. D., O'Mahony, A., Povey, I. M., Cherkaoui, K., Pemble, M. E., Brammertz, G., Heyns, M., Newcomb, S. B., Afanas'ev, V. V. and Hurley, P. K. (2009) 'Temperature and frequency dependent electrical characterization of HfO2/InxGa1-xAs interfaces using capacitance-voltage and conductance methods', Applied Physics Letters, 94(10), pp. 102902 and may be found at http://aip.scitation.org/doi/abs/10.1063/1.3089688 |  |  |  |

| Item downloaded from        | http://hdl.handle.net/10468/4363                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

## Temperature and frequency dependent electrical characterization of $HfO_2/In_xGa_{1-x}As$ interfaces using capacitance-voltage and conductance methods

É. O'Connor', S. Monaghan, R. D. Long, A. O'Mahony, I. M. Povey, K. Cherkaoui, M. E. Pemble, G. Brammertz, M. Heyns, S. B. Newcomb, V. V. Afanas'ev, and P. K. Hurley

Citation: Appl. Phys. Lett. 94, 102902 (2009); doi: 10.1063/1.3089688

View online: http://dx.doi.org/10.1063/1.3089688

View Table of Contents: http://aip.scitation.org/toc/apl/94/10

Published by the American Institute of Physics

## Articles you may be interested in

An investigation of capacitance-voltage hysteresis in metal/high-k/ln<sub>0.53</sub>Ga<sub>0.47</sub>As metal-oxide-semiconductor capacitors

Journal of Applied Physics **114**, 144105 (2013); 10.1063/1.4824066

Atomic-layer-deposited  $HfO_2$  on  $In_{0.53}Ga_{0.47}As$ : Passivation and energy-band parameters Applied Physics Letters **92**, 072901 (2008); 10.1063/1.2883967

Characteristic trapping lifetime and capacitance-voltage measurements of GaAs metal-oxide-semiconductor structures

Applied Physics Letters 91, 133510 (2007); 10.1063/1.2790787

1-nm-capacitance-equivalent-thickness HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>/InGaAs metal-oxide-semiconductor structure with low interface trap density and low gate leakage current density

Applied Physics Letters **100**, 132906 (2012); 10.1063/1.3698095

Comparison of methods to quantify interface trap densities at dielectric/III-V semiconductor interfaces Journal of Applied Physics **108**, 124101 (2010); 10.1063/1.3520431

Border traps in  $Al_2O_3/In_{0.53}Ga_{0.47}As$  (100) gate stacks and their passivation by hydrogen anneals Applied Physics Letters **96**, 012906 (2010); 10.1063/1.3281027

## Temperature and frequency dependent electrical characterization of $HfO_2/In_xGa_{1-x}As$ interfaces using capacitance-voltage and conductance methods

É. O'Connor, <sup>1,a)</sup> S. Monaghan, <sup>1</sup> R. D. Long, <sup>1</sup> A. O'Mahony, <sup>1</sup> I. M. Povey, <sup>1</sup> K. Cherkaoui, <sup>1</sup> M. E. Pemble, <sup>1</sup> G. Brammertz, <sup>2</sup> M. Heyns, <sup>2</sup> S. B. Newcomb, <sup>3</sup> V. V. Afanas'ev, <sup>4</sup> and P. K. Hurley <sup>1</sup>

(Received 14 November 2008; accepted 25 January 2009; published online 11 March 2009)

Electrical properties of metal-oxide-semiconductor capacitors using atomic layer deposited  $HfO_2$  on n-type GaAs or  $In_xGa_{1-x}As$  (x=0.53, 0.30, 0.15) epitaxial layers were investigated. Capacitance-voltage (CV) measurements indicated large temperature and frequency dispersion at positive gate bias in devices using n-type GaAs and low In content (x=0.30, 0.15)  $In_xGa_{1-x}As$  layers, which is significantly reduced for devices using  $In_{0.53}Ga_{0.47}As$ . For  $In_{0.53}Ga_{0.47}As$  devices, the CV response at negative gate bias is most likely characteristic of an interface state response and may not be indicative of true inversion. The conductance technique on  $Pd/HfO_2/In_{0.53}Ga_{0.47}As/InP$  shows reductions in interface state densities by  $In_{0.53}Ga_{0.47}As$  surface passivation and forming gas annealing (325 °C). © 2009 American Institute of Physics. [DOI: 10.1063/1.3089688]

One of the main technological challenges associated with the fabrication of devices incorporating high dielectric constant (k) gate materials on III-V channels is the understanding of electrically active interface state defects and their passivation. Recent studies investigating high-k oxides on Si reveal interface state defects similar to those observed in the SiO<sub>2</sub>/Si system. However, the interface chemistry for high-k materials on III-V substrates is a more complex system, with the possibility for more than one substrate element, and its native oxides, to contribute to interfacial defects. The detrimental effect of high interface state density  $(D_{it})$  on high-k/III-V device characteristics has motivated extensive research on both in situ and ex situ passivation of the high-k/III-V interface in an attempt to reduce  $D_{it}$ . In this work we examine the electrical properties of atomic layer deposited (ALD) HfO2 thin films on n-type GaAs or  $In_xGa_{1-x}As$  (x=0.53, 0.30, 0.15) layers with Pd metal gates. The motivation for this approach is to assess whether the change of energy gap from GaAs (~1.42 eV) to  $In_{0.53}Ga_{0.47}As$  (~0.75 eV) is reflected in a change in electrically active interface defects. A detailed  $D_{\rm it}$  analysis for unpassivated and passivated Pd/HfO<sub>2</sub>/n-In<sub>0.53</sub>Ga<sub>0.47</sub>As/InP structures using the conductance method developed for the SiO<sub>2</sub>/Si system is also presented.<sup>8</sup> In addition, the effect of low temperature forming gas annealing (FGA) on the electrical properties of unpassivated Pd/HfO<sub>2</sub>/n-In<sub>0.53</sub>Ga<sub>0.47</sub>As/ InP structures is examined.

The  $In_xGa_{1-x}As$  device stacks employed InP substrates [S:  $(1-3)\times 10^{18}$ ], for x=0.53, or GaAs substrates (Si:  $5\times 10^{17}$ ), for x=0.30 and 0.15, on which buffer layers were grown prior to growth of the epitaxial layers. The buffer layers (and doping concentrations) for  $In_xGa_{1-x}As$  were 0.1  $\mu$ m InP (S:  $2\times 10^{18}$ ), 0.35  $\mu$ m GaAs (Si:  $1\times 10^{17}$ / cm<sup>3</sup>), 1  $\mu$ m GaAs (Si:  $1\times 10^{17}$ / cm<sup>3</sup>), for x of 0.53, 0.30,

and 0.15, respectively. The epitaxial layer thickness (and doping) of the  $In_xGa_{1-x}As$  was 2  $\mu$ m (S:  $4\times10^{17}$ ), 0.05  $\mu$ m (Si:  $1 \times 10^{17}$ /cm<sup>3</sup>), 0.03  $\mu$ m (Si:  $1 \times 10^{17}$ /cm<sup>3</sup>), for x of 0.53, 0.30, and 0.15, respectively. The  $In_rGa_{1-r}As$ (x=0.53, 0.15) epitaxial layers were grown by metalorganic vapor-phase epitaxy, as was the InP buffer layer, whereas the In<sub>0.30</sub>Ga<sub>0.70</sub>As epitaxial layer and all GaAs layers were grown by molecular beam epitaxy. In the case of the GaAs (Si:  $5 \times 10^{17}$ ) sample, no subsequent growth of a buffer layer was performed. All HfO2 layers were deposited in a separate ALD reactor at 250 °C by alternating pulses of  $H_2O$  and the  $HfO_2$  precursor TDMA-Hf ( $Hf[N(CH_3)_2]_4$ ), the first pulse being that of the Hf precursor. Capacitor structures were completed by vacuum evaporation of ~100 nm of Pd (deposition rate of  $\sim 2.5$  Å/s) using a lift-off process. No Ohmic back contacts to the devices were formed. The ex situ three-stage passivation was performed prior to ALD growth as follows: 3.7% HCl, 3 min at 25 °C; 3% NH<sub>4</sub>OH, 3 min at 25 °C; 1% (NH<sub>4</sub>)<sub>2</sub>S, 5 min at 75 °C; rinse in de-ionized water; and blow dry wafers with  $N_2$ . FGA  $(5\%H_2/95\%N_2)$ was performed cumulatively after gate metallization at 250 and 325 °C for 30 min.

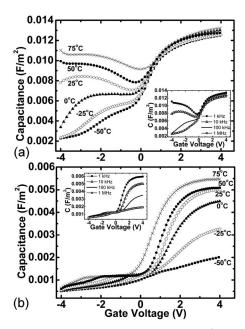

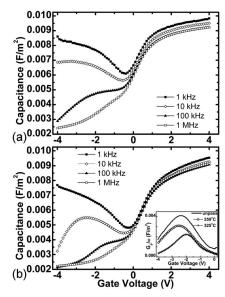

Figures 1(a) and 1(b) present CV responses (10 kHz) for a range of measurement temperatures (-50 to 75 °C) for  $In_{0.53}Ga_{0.47}As$  and GaAs devices, respectively. By varying the measurement temperature, it has been shown to be possible to access interface defects over an increased portion of the semiconductor energy gap and assess their effect on the CV characteristics. Room temperature CV multifrequency responses for the  $In_{0.53}Ga_{0.47}As$  and GaAs devices are shown as the insets to Figs. 1(a) and 1(b), respectively. Devices fabricated on  $In_{0.15}Ga_{0.85}As$  and  $In_{0.30}Ga_{0.70}As$  epitaxial layers display very similar temperature dependent and multifrequency CV profiles (not shown) to that of the GaAs. The average percentage capacitance dispersions per decade of frequency at a gate voltage  $V_{\rm gate}$ =4 V are  $\sim 30\%$ , 15%, and 23%, for GaAs,  $In_{0.15}Ga_{0.85}As$ , and  $In_{0.30}Ga_{0.70}As$ , respec-

<sup>&</sup>lt;sup>1</sup>Tyndall National Institute, University College Cork, Lee Maltings, Prospect Row, Cork, Ireland <sup>2</sup>Interuniversity Microelectronics Center (IMEC vzw), Kapeldreef 75, B-3001 Leuven, Belgium <sup>3</sup>Glebe Scientific Ltd., Newport, County Tipperary, Ireland

<sup>&</sup>lt;sup>4</sup>Catholic University of Leuven, Celestijnenlaan 200d, B-3001 Leuven, Belgium

<sup>&</sup>lt;sup>a)</sup>Electronic mail: eamon.oconnor@tyndall.ie.

FIG. 1. 10 kHz CV response with varying temperature (-50 to 75 °C) of (a) unpassivated Pd/9.5 nm ALD  ${\rm HfO_2/n\text{-}In_{0.53}Ga_{0.47}As/InP}$  and (b) unpassivated Pd/11.4 nm ALD  ${\rm HfO_2/n\text{-}GaAs}$ . The average percentage capacitance dispersions per 25 °C step of the temperature (-50 to 75 °C) at  $V_{\rm gate}$ =4 V are 1.7% ( ${\rm In_{0.53}Ga_{0.47}As}$ ), 8.5% ( ${\rm In_{0.30}Ga_{0.70}As}$ ), 6.9% ( ${\rm In_{0.15}Ga_{0.85}As}$ ), and 16.7% (GaAs). Insets (a) and (b) show corresponding room temperature CV frequency variation (1 kHz to 1 MHz) in unpassivated  ${\rm In_{0.53}Ga_{0.47}As}$  and GaAs devices, respectively. The thicknesses of the [HfO<sub>2</sub>, and interface oxide layer (IL)] for unpassivated  ${\rm In_{x}Ga_{1.x}As}$  and GaAs devices measured by transmission electron microscopy are as follows:  ${\rm In_{0.53}Ga_{0.47}As}$  (9.5 nm, 1.0 nm),  ${\rm In_{0.30}Ga_{0.70}As}$  (9.2 nm, 0.9 nm),  ${\rm In_{0.15}Ga_{0.85}As}$  (14.0 nm, 1.1 nm), and GaAs (11.4 nm, 1.3 nm).

tively. This is reduced to <3% for  $In_{0.53}Ga_{0.47}As$  devices. It should be noted that the In<sub>0,30</sub>Ga<sub>0,70</sub>As epitaxial layer  $(0.05 \mu \text{m})$  is beyond the critical thickness  $(0.012 \mu \text{m})$  contributing to a higher number of dislocations in this epitaxial layer. For the  $In_{0.53}Ga_{0.47}As$  devices, there is little variation in capacitance at  $V_{\rm gate}$ =4 V with either temperature [Fig. 1(a)] or frequency [Fig. 1(a) inset], indicating that the devices are most likely in accumulation and that it is possible to move the Fermi level  $(E_f)$  at the  $In_{0.53}Ga_{0.47}As/HfO_2$  interface to the conduction band edge  $(E_c)$ . However, for the GaAs substrate, the large capacitance dispersion with temperature [Fig. 1(b)] and frequency [Fig. 1(b) inset] at  $V_{\text{gate}}$ =4 V suggests that the interface state capacitance  $(C_{it})$ dominates the semiconductor  $(C_s)$  and oxide capacitance  $(C_{ox})$ . For this case of  $C_{it} \gg C_{ox}$ , the fact that the measured capacitance can approach the value of  $C_{ox}$  does not necessarily imply that the devices are in accumulation. 2,11,12 The observation that we can achieve accumulation for  $In_{0.53}Ga_{0.47}As$ , but not for  $In_{0.30}Ga_{0.70}As$ ,  $In_{0.15}Ga_{0.85}As$ , and GaAs, suggests the presence of interface defects, which become electrically inactive as the energy gap of the semiconductor is changed from GaAs to  $In_{0.53}Ga_{0.47}As$ . Theeten et al. 13 observed a similar effect where a defect response, which is dominant in the case of lower In content (<0.35) devices, becomes insignificant for higher In content devices. The values of the energy gap and electron affinity are  $In_{0.53}Ga_{0.47}As$  (0.75 and 4.5 eV),  $In_{0.30}Ga_{0.70}As$  (1.01 and 4.31 eV), In<sub>0.15</sub>Ga<sub>0.85</sub>As (1.21 and 4.19 eV), and GaAs (1.43 and 4.07 eV). These values indicate the defects responsible for the observed frequency dispersion at positive gate

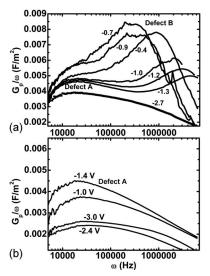

FIG. 2.  $G_p/\omega$  vs  $\omega$  ( $\omega$ =2 $\pi$ ×frequency) at 75 °C for selected and representative gate voltage bias points (indicated), for (a) unpassivated and (b) three-stage *ex situ* passivated Pd/10.3 nm ALD HfO<sub>2</sub>/n-In<sub>0.53</sub>Ga<sub>0.47</sub>As/InP. IL thickness for the passivated In<sub>0.53</sub>Ga<sub>0.47</sub>As device is 1.3 nm.

bias for GaAs and  $In_xGa_{1-x}As$  (x=0.15, 0.30) devices, are located in the range 4.07 to 4.5 eV from the vacuum level. Atomic identification of the defects is beyond the capabilities of the electrical characterization techniques used in the present study.<sup>16</sup>

In the case of the  $In_{0.53}Ga_{0.47}As$  stack, the dispersion observed in the CV as a function of both temperature and frequency, for  $V_{\rm gate}$  in the range of -1~V to -4~V, is characteristic of interface defects and is unlikely to be representative of true inversion at the  $HfO_2/In_{0.53}Ga_{0.47}As$  interface. Similar frequency dependent CV profiles to those in the inset to Fig. 1(a) have previously been reported irrespective of the high-k layer, passivation approach, and  $In_{0.53}Ga_{0.47}As$  growth method, suggesting that these interface states originate from the  $In_{0.53}Ga_{0.47}As$  surface or interfacial oxides. With respect to GaAs, frequency dispersion in the depletion region has been observed by Brammertz et~al. for devices at temperatures higher than 120 °C, which are attributed to mid-gap interface states in GaAs.

In quantifying the interface state defect density contributions to the CV and GV responses, the conductance technique, as developed for  $\mathrm{Si/SiO_2}$  systems, is applied here to the  $\mathrm{Pd/HfO_2/In_{0.53}Ga_{0.47}As/InP}$  devices. <sup>8,19,20</sup> The technique involves measuring the capacitance and conductance at a constant  $V_{\mathrm{gate}}$  while applying a logarithmic frequency sweep from 50 Hz to 1 MHz. The analysis inherently assumes the  $\mathrm{HfO_2/In_{0.53}Ga_{0.47}As}$  surface is in depletion where only majority carriers interact with the interface traps, and an accurate estimate of  $D_{\mathrm{it}}$  can be extracted. If the  $\mathrm{HfO_2/In_{0.53}Ga_{0.47}As}$  surface is in weak inversion, the analysis will significantly overestimate the  $D_{\mathrm{it}}$  value. <sup>21</sup>

Figures 2(a) and 2(b) show estimates of  $G_p/\omega$  versus  $\omega$  curves for unpassivated and three-stage passivated Pd/HfO<sub>2</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As/InP structures, respectively. The measurement temperature is 75 °C for all devices, as no  $G_p/\omega$  peaks were observed at -50 and 25 °C. The plot in Fig. 2(a) shows two maximum peak profiles at low and high angular frequencies, and at different gate voltages within depletion, which may possibly be characteristic of two defects with distinct energy levels, termed (A) and (B), re-

FIG. 3. Room temperature CV frequency variation (1 kHz to 1 MHz) in (a) unpassivated and (b) post-325 °C FGA, Pd/HfO<sub>2</sub>/n-In<sub>0.53</sub>Ga<sub>0.47</sub>As/InP devices. The average percentage capacitance dispersions per decade of frequency (1 kHz to 1 MHz) at  $V_{\rm gate}$ =4 V are 2.4%, 2.4%, and 1.8% for the unannealed, post-250 °C FGA, and post-325 °C FGA devices, respectively. The inset to (b) shows  $G_p/\omega$  vs  $V_{\rm gate}$  for an unpassivated In<sub>0.53</sub>Ga<sub>0.47</sub>As device, and following 250 and 325 °C postmetallization FGA.

spectively. Similar methods have been used to analyze multiple defects in  $\mathrm{SiO_2/Si}$  systems. <sup>22</sup> A peak  $D_{\mathrm{it}}$  of 1.7  $\times 10^{13}$  cm<sup>-2</sup> eV<sup>-1</sup> is calculated for defect (A) and 1.5  $\times 10^{13}$  cm<sup>-2</sup> eV<sup>-1</sup> for defect (B). Figure 2(b) shows the  $G_p/\omega$  versus  $\omega$  plots for the three-stage passivated  $\mathrm{In_{0.53}Ga_{0.47}As}$  devices, with similarly broad profiles to those reported by Mui  $et\ al.^{20}$  for  $\mathrm{Si_3N_4/In_{0.53}Ga_{0.47}As}$  interfaces. No peak for defect (B) is evident, while for defect (A)  $D_{\mathrm{it}}$  is estimated to be  $1.6\times 10^{13}$  cm<sup>-2</sup> eV<sup>-1</sup>. The similarity in the defect (A)  $D_{\mathrm{it}}$  indicates that the three-stage surface passivation has had little impact on this defect, while it significantly reduces the contribution of defect (B).

Figures 3(a) and 3(b) show room temperature CV multifrequency responses for unpassivated and post-325 °C FGA, Pd/HfO<sub>2</sub>/n-In<sub>0.53</sub>Ga<sub>0.47</sub>As/InP devices, respectively. The FGA results in a noticeable reduction in the frequency dispersion both at  $V_{\text{gate}}=4$  V and also in the transition region from depletion to accumulation at  $V_{\rm gate}\!\sim\!0$  to 1 V. The CVdispersion for  $V_{\text{gate}}$  in the range of -1 to -4 V, which is characteristic of interface defects, is also visibly reduced following 325 °C FGA. The inset to Fig. 3(b) shows the relative reductions in the maximum peaks of  $G_p/\omega$  versus  $V_{\rm gate}$ for an unpassivated In<sub>0.53</sub>Ga<sub>0.47</sub>As device, and following 250 and 325 °C postmetallization FGAs. We see a reduction in the maximum peak magnitude of  $G_p/\omega$  from the pre-FGA unpassivated device to the post-FGA at 325 °C device, as well as a change in peak profile, corresponding to a total estimated  $D_{\rm it}$  of  $1.0 \times 10^{13}~{\rm cm}^{-2}~{\rm eV}^{-1}$  from defect (A) only, for the 325 °C post-FGA device, with no clear evidence of a peak for defect (B). Similar improvements in the CV frequency dispersion and in the relative peaks of  $G_p/\omega$  versus  $V_{\text{gate}}$  have also been observed in post-325 °C FGA devices employing a Pt gate electrode.

In summary, it is found that the large temperature and frequency dispersion in CV responses at positive gate bias for devices with  $HfO_2$  layers on n-type GaAs and low In content (x=0.30, 0.15)  $In_xGa_{1-x}As$  is significantly reduced

using high In content (x=0.53) epitaxial layers, suggesting that it is only possible to achieve true accumulation for the In<sub>0.53</sub>Ga<sub>0.47</sub>As devices. However, the CV responses at negative gate bias indicate a significant interface state contribution and may not be representative of true inversion at the HfO<sub>2</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As interface. An estimation of  $D_{it}$  using the conductance technique indicates that densities for these HfO<sub>2</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As devices remain too high for practical device applications, but it has been shown that a three-stage In<sub>0.53</sub>Ga<sub>0.47</sub>As surface passivation and postmetallization FGA at 325 °C can provide a significant reduction in interface state defect densities.

The authors thank Dan O'Connell, Tyndall National Institute, for sample processing. The authors would like to acknowledge the following for financial support of this work: Science Foundation Ireland (Grant Nos. 05/IN/1751 and 07/SRC/I1172, FORME); IRCSET; Intel Ireland.

K. Hurley, K. Cherkaoui, E. O'Connor, M. C. Lemme, H. D. B. Gottlob, M. Schmidt, S. Hall, Y. Lu, O. Buiu, B. Raeissi, J. Piscator, O. Engstrom, and S. B. Newcomb, J. Electrochem. Soc. 155, G13 (2008).

C. L. Hinkle, A. M. Sonnett, E. M. Vogel, S. McDonnell, G. Hughes, M. Milojevic, B. Lee, F. S. Aguirre-Tostado, K. J. Choi, and R. M. Wallace, Appl. Phys. Lett. 91, 163512 (2007).

<sup>3</sup>E. O'Connor, R. D. Long, K. Cherkaoui, K. K. Thomas, F. Chalvet, I. M. Povey, M. E. Pemble, P. K. Hurley, B. B. Brennan G. Hughes, and S. Newcomb, Appl. Phys. Lett. **92**, 022902 (2008).

<sup>4</sup>N. Goel, P. Majhi, W. Tsai, M. Warusawithana, D. G. Schlorn, M. B. Santos, D. Choi, J. S. Harris, and Y. Nishi, Appl. Phys. Lett. **91**, 093509 (2007).

<sup>5</sup>Y. C. Chang, M. L. Huang, K. Y. Lee, Y. J. Lee, T. D. Lin, M. Hong, J. Kwo, T. S. Lay, C. C. Liao, and K. Y. Cheng, Appl. Phys. Lett. **92**, 072901 (2008).

<sup>6</sup>H. S. Kim, I. Ok, M. Zhang, T. Lee, F. Zhu, L. Yu, and J. C. Lee, Appl. Phys. Lett. **89**, 222903 (2006).

<sup>7</sup>B. Shin, D. Choi, J. S. Harris, and P. C. McIntyre, Appl. Phys. Lett. **93**, 052911 (2008).

H. Nicollian and A. Goetzberger, Bell Syst. Tech. J. 156, 1055 (1967).

C.-C. Cheng, C.-H. Chien, G.-L. Luo, C.-K. Tseng, H.-C. Chiang, C.-H. Yang, and C.-Y. Changa, J. Electrochem. Soc. 155, G56 (2008).

<sup>10</sup>G. Brammertz, K. Martens, S. Soincke, A. Delabie, M. Caymax, M. Meuris, and M. Heyns, Appl. Phys. Lett. 91, 133510 (2007).

<sup>11</sup>H. Hasegawa and T. Sawada, IEEE Trans. Electron Devices 27, 1055 (1980).

<sup>12</sup>L. Dobaczewski, S. Bernardini, P. Kruszewski, P. K. Hurley, V. P. Markevich, I. D. Hawkins, and A. R. Peaker, Appl. Phys. Lett. **92**, 242104 (2008).

<sup>13</sup>J. B. Theeten, S. Gourrier, P. Friedel, M. Tallepied, O. Arnoult, and G. Benarroche, Mater. Res. Soc. Symp. Proc. 38, 499 (1985).

<sup>14</sup>D. J. Arent, K. Deneffe, C. Van Hoof, J. De Boeck, and G. Borghs, J. Appl. Phys. **66**, 1739 (1989).

<sup>15</sup>Y. A. Goldberg and N. M. Schmidt, in *Handbook Series on Semiconductor Parameters*, 2, edited by M. Levinshtein, S. Rumyanstev, and M. Shur (World Scientific, Singapore, 1999), p. 62.

<sup>16</sup>W. E. Spicer, I. Lindau, P. Skeath, and C. Y. Su, J. Vac. Sci. Technol. 17, 1019 (1980).

<sup>17</sup>H. J. Wadsworth, S. Bhattacharya, D. W. McNeill, F. H. Ruddell, B. M. Armstrong, H. S. Gamble, and D. Denvir Mater. Sci. Semicond. Process. 9, 685 (2006).

<sup>18</sup>G. Brammertz, H. C. Lin, K. Martens, D. Mercier, C. Merckling, J. Penaud, C. Adelmann, S. Sioncke, W. E. Wang, M. Caymax, M. Meuris, and M. Heyns, J. Electrochem. Soc. 155, H945 (2008).

<sup>19</sup>E. H. Nicollian and J. R. Brews, MOS Physics and Technology (Wiley, New York, 1982).

D. S. L. Mui, Z. Wang, and H. Morkoc, Thin Solid Films 231, 107 (1993).

K. Martens, C. O. Chu, G. Brammertz, B. De Jaeger, D. Kuzum, M. Meuris, M. M. Heyns, T. Krishnamohan, K. Saraswat, H. E. Maes, and G.

Groeseneken, IEEE Trans. Electron Devices 55, 547 (2008).

22 A. Inoue, M. Shimada, and J. Shirafuii, Jnn. J. Appl. Phys., Part 1, 35

<sup>22</sup>A. Inoue, M. Shimada, and J. Shirafuji, Jpn. J. Appl. Phys., Part 1 35, 5915 (1996).